# AD9891/AD9895

## 特長

AD9891:10ビット、20MHz

AD9895:12ビット、30MHz

20MSPSの相関ダブルサンプラー(CDS)を内蔵

4dB ± 6dBのピクセル・ゲイン・アンプ(PxGA®)

2~36dBの10ビット可変ゲイン・アンプ(VGA)

10ビット20MHzのA/Dコンバータ(AD9891)

12ビット30MHzのA/Dコンバータ(AD9895)

可変レベル制御付きブラック・レベル・クランプ

オンチップの完全なタイミング・ジェネレータ

1ns分解能のPrecision Timing™コアを内蔵

5Vの水平ドライバとRGドライバを内蔵

2相Hクロック・モードおよび4相Hクロック・モード

4相垂直転送クロック

電子シャッター・モードおよび機械式シャッター・モード

外部クリスタル・オシレーター用ドライバを内蔵

外部同期オプション付き同期ジェネレータを内蔵

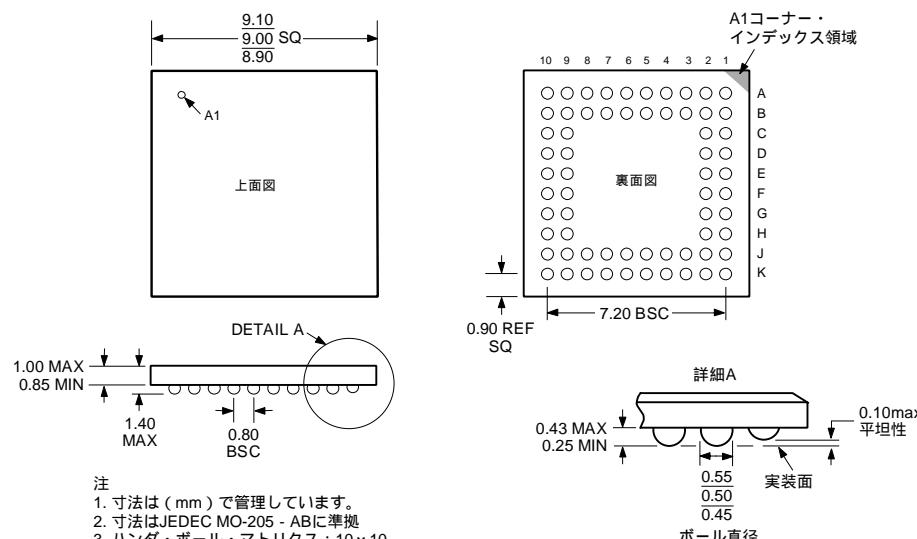

64ピンLFBGAパッケージ

## アプリケーション

デジタル・カメラ

デジタル・ビデオ・カメラ

工業用画像処理

## 概要

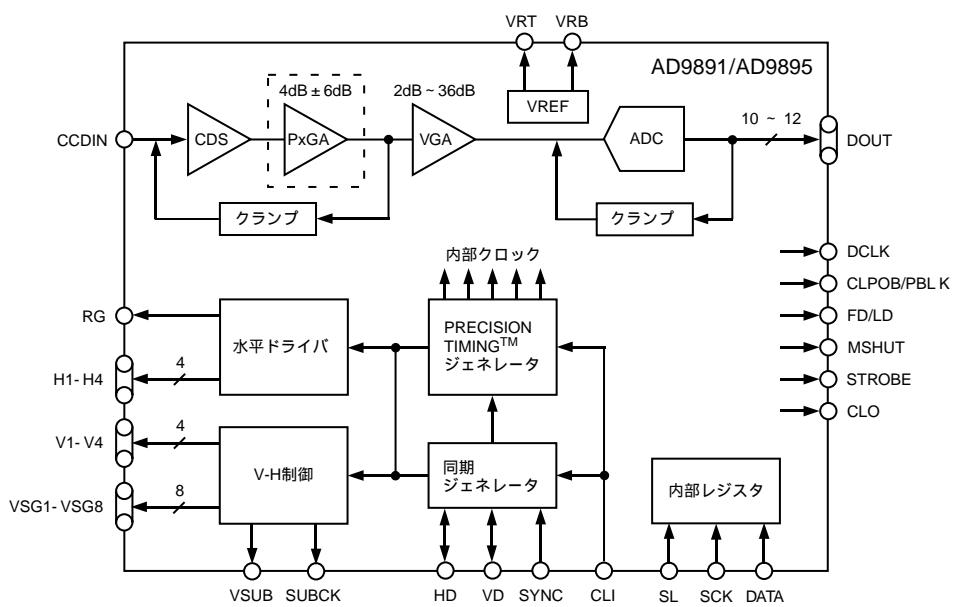

AD9891およびAD9895は、デジタル・カメラ・アプリケーション向けの高集積CCD信号プロセッサです。A/D変換付きの完全なアナログ・フロントエンドとフル機能のプログラマブルなタイミング・ジェネレータを内蔵しています。Precision Timingコアの使用により、高速クロックの調整が20MHz動作に対して1nsの分解能、30MHz動作に対して700psの分解能で可能です。

AD9891は最大20MHzのピクセル・レート、AD9895は30MHzのピクセルレートで仕様規定されています。アナログ・フロントエンドには、ブラック・レベルへのクランプ機能、CDS、PxGA、VGA、10ビット(AD9891)、または12ビット(AD9895)のA/Dコンバータが含まれています。タイミング・ジェネレータは、RG、Hクロック、Vクロック、センサー・ゲート・パルス、サブストレート・クロック、サブストレート・バイアス・パルスからなる必要なすべてのCCDクロックを発生します。動作は、3線式シリアル・インターフェースを介して設定します。

AD9891は、省スペースの64ピンLFBGAパッケージを採用し、温度範囲 -20 ~ +85 で仕様規定されています。

機能ブロック図

PxGAおよびPrecision Timingは、Analog Devices, Inc.の登録商標です。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、その情報の利用または利用したことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものではありません。

REV.0

アナログ・デバイセズ株式会社

本 社 / 東京都港区海岸1-16-1 電話03(5402)8200 〒105-6891

ニューピア竹芝サウスタワービル

大阪営業所 / 大阪市淀川区宮原3-5-36 電話06(6350)6868(代) 〒532-0003

新大阪第二森ビル

# AD9891/AD9895

## 目次

|                               |    |                            |    |

|-------------------------------|----|----------------------------|----|

| 仕様                            | 3  | フレーム転送CCDモード               | 24 |

| デジタル特性                        | 3  | 垂直センサー・ゲート(シフト・ゲート)のタイミング  | 25 |

| AD9891アナログ特性                  | 4  | シャッター・タイミングの制御             | 26 |

| AD9895アナログ特性                  | 5  | 通常シャッター・モード                | 26 |

| タイミング特性                       | 6  | 高精度シャッター・モード               | 26 |

| パッケージ熱特性                      | 6  | 低速シャッター・モード                | 26 |

| 絶対最大定格                        | 6  | SUBCKの停止                   | 26 |

| オーダー・ガイド                      | 6  | 露光後の読み出し                   | 27 |

| ピン配置 - AD9891                 | 7  | VSUBの制御                    | 27 |

| ピン機能の説明 - AD9891              | 7  | MSHUTとSTROBEの制御            | 27 |

| ピン配置 - AD9895                 | 8  | インターレース・フレームの露光と読み出しの例     | 29 |

| ピン機能の説明 - AD9895              | 8  | アナログ・フロントエンドの説明と動作         | 30 |

| 仕様の定義                         | 9  | DCの再生                      | 30 |

| 等価回路                          | 9  | 相關ダブル・サンプラー                | 30 |

| 代表的な性能特性                      | 10 | 入力のクランプ                    | 30 |

| システム概要                        | 11 | PxGA                       | 30 |

| 代表的なシステム・ブロック図                | 11 | PxGAカラー・セッティング・モード・タイミング   | 31 |

| Precision Timingによる高速タイミングの生成 | 12 | 可変ゲイン・アンプ                  | 33 |

| タイミング分解能                      | 12 | PxGAゲインとVGAゲインのカーブ         | 33 |

| 高速クロックのプログラマブル性               | 12 | 光学的ブラック・クランプ               | 33 |

| HドライバとRG出力                    | 13 | A/Dコンバータ                   | 33 |

| デジタル・データ出力                    | 13 | パワーアップと同期                  | 34 |

| 水平クランピングとプランкиング              | 15 | マスター・モードに推奨されるパワーアップ・シーケンス | 34 |

| CLPOB、CLPDM、PBLKの各シーケンス       | 15 | マスター・モードの同期                | 35 |

| 各HBLKシーケンス                    | 15 | スレーブ・モードの同期                | 35 |

| 水平シーケンスの制御                    | 15 | パワーダウン・モード動作               | 35 |

| 垂直タイミングの生成                    | 17 | 水平タイミング・シーケンスの例            | 37 |

| 個々の垂直シーケンス                    | 18 | 垂直タイミングの例                  | 39 |

| 個々の垂直領域                       | 19 | 回路レイアウト情報                  | 40 |

| フィールドの完成：領域の結合                | 20 | シリアル・インターフェースのタイミング        | 41 |

| 垂直シーケンス・オルタネーション              | 21 | ダブル幅レジスタ・アクセスについての注意       | 42 |

| VSGラインでの2番目の垂直シーケンス           | 22 | レジスタ・リストに関する注意事項           | 43 |

| 垂直スイープ・モード動作                  | 22 | 外形寸法                       | 56 |

| 垂直マルチプライヤモード                  | 24 |                            |    |

# AD9891/AD9895 - 仕様

## 一般的な特性

| パラメータ                                                                                                                                | Min                                      | Typ                                    | Max                                      | 単位                         |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------|----------------------------|

| 温度範囲<br>動作<br>保管                                                                                                                     | - 20<br>- 65                             |                                        | + 85<br>+ 150                            |                            |

| 電源電圧<br>AVDD1、AVDD2 (AFEアナログ電源)<br>TCVDD (タイミング・コアのアナログ電源)<br>RGVDD (RGドライバ)<br>HVDD (H1~H4ドライバ)<br>DRVDD (データ出力ドライバ)<br>DVDD (デジタル) | 2.7<br>2.7<br>4.75<br>4.75<br>2.7<br>2.7 | 3.0<br>3.0<br>5.0<br>5.0<br>3.0<br>3.0 | 3.5<br>3.5<br>5.25<br>5.25<br>3.5<br>3.5 | V<br>V<br>V<br>V<br>V<br>V |

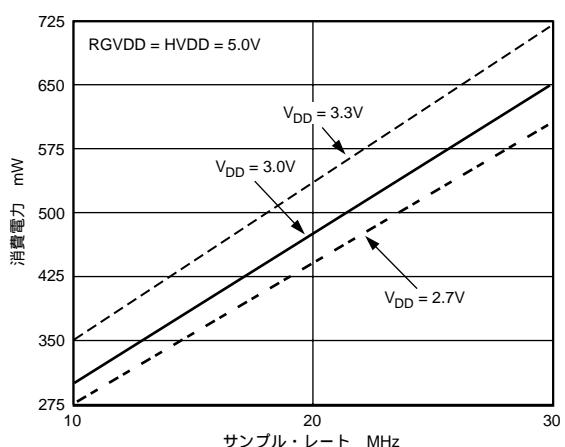

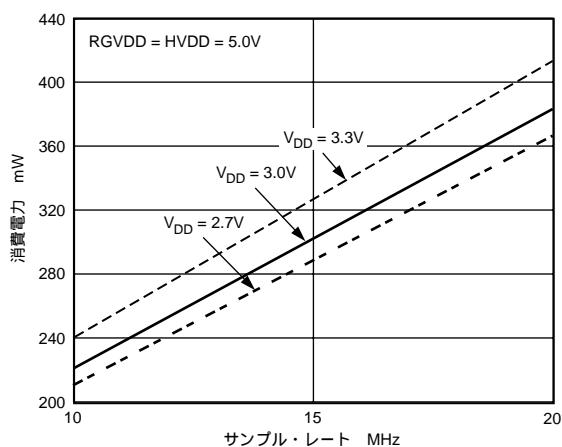

| AD9891:20MHzでの消費電力 (特性1の消費電力カーブ参照)<br>(電源レベルTyp値、H1~H4 100pF負荷)                                                                      |                                          | 380                                    |                                          | mW                         |

| AD9895:20MHzでの消費電力 (特性1の消費電力カーブ参照)<br>(電源レベルTyp値、H1~H4 100pF負荷)                                                                      |                                          | 500                                    |                                          | mW                         |

| CLI最大クロック・レート<br>AD9891<br>AD9895                                                                                                    | 20<br>30                                 |                                        |                                          | MHz<br>MHz                 |

仕様は予告なく変更されることがあります。

## デジタル特性 (特に指定のない限り、RGVDD = HVDD = 4.75V ~ 5.25V、DVDD = DRVDD = 2.7 ~ 3.5V、C<sub>L</sub> = 20pF、T<sub>MIN</sub> ~ T<sub>MAX</sub>)

| パラメータ                                                                                    | 記号                                 | Min                    | Typ | Max | 単位                 |

|------------------------------------------------------------------------------------------|------------------------------------|------------------------|-----|-----|--------------------|

| ロジック入力<br>ハイレベル入力電圧<br>ローレベル入力電圧                                                         | V <sub>IH</sub><br>V <sub>IL</sub> | 2.1                    |     | 0.6 | V<br>V             |

| ハイレベル入力電流<br>ローレベル入力電流                                                                   | I <sub>IH</sub><br>I <sub>IL</sub> | 10                     |     | 10  | μA<br>μA           |

| 入力容量                                                                                     | C <sub>IN</sub>                    | 10                     |     |     | pF                 |

| ロジック出力 (HとRGを除く)<br>I <sub>OH</sub> = 2mAでのハイレベル出力電圧<br>I <sub>OL</sub> = 2mAでのローレベル出力電圧 | V <sub>OH</sub><br>V <sub>OL</sub> | 2.2                    |     | 0.5 | V<br>V             |

| RGおよびHドライバ出力 (H1~H4)<br>最大電流でのハイレベル出力電圧<br>最大電流でのローレベル出力電圧<br>最大出力電流 (プログラマブル)<br>最大負荷容量 | V <sub>OH</sub><br>V <sub>OL</sub> | VDD - 0.5<br>24<br>100 |     | 0.5 | V<br>V<br>mA<br>pF |

仕様は予告なく変更されることがあります。

# AD9891/AD9895

## AD9891 - アナログ特性 (特に指定のない限り、AVDD1、2 = 3.0V、f<sub>CLI</sub> = 20MHz、T<sub>MIN</sub> ~ T<sub>MAX</sub>)

| パラメータ                                                                                                                                  | Min                                               | Typ                      | Max                           | 単位                                       | 注                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------|-------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| CDS<br>ゲイン<br>許容CCDリセット過渡電圧<br>非飽和の最大入力範囲<br>CCDブラック・ピクセルの最大振幅                                                                         |                                                   | 0<br>500<br>1.0<br>± 200 |                               | dB<br>mV<br>V p-p<br>mV                  | 入力特性<br>注1に定義                                                                                                                      |

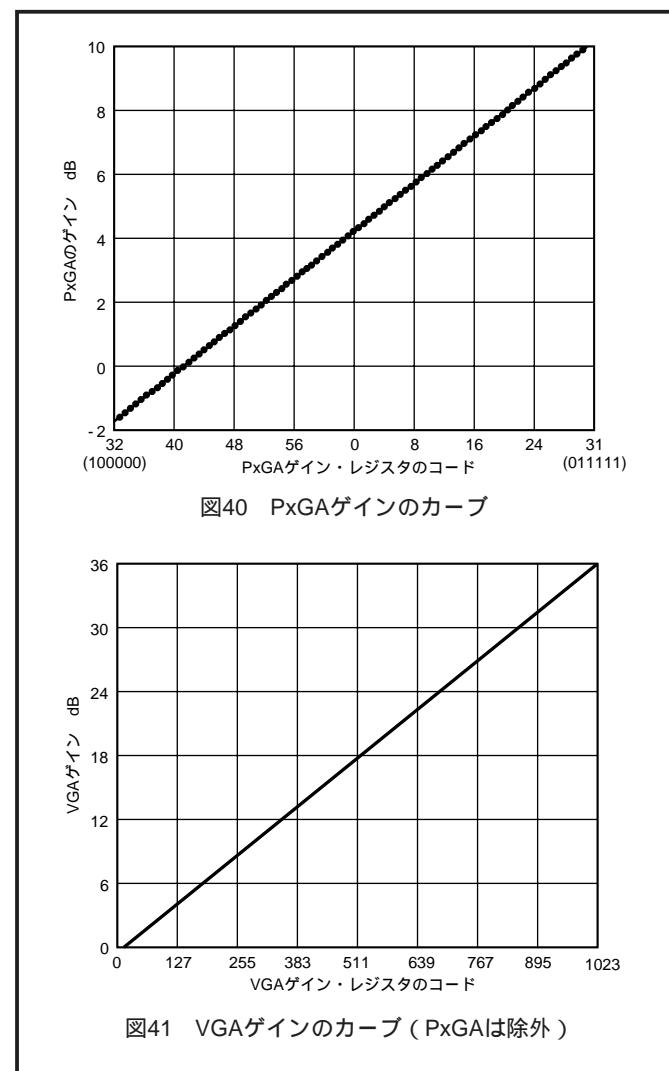

| ピクセル・ゲイン・アンプ (PxGA)<br>最大入力範囲<br>最大出力範囲<br>ゲイン制御の分解能<br>ゲインの単調性<br>ゲイン範囲<br>最小ゲイン (PxGAコード32)<br>中心ゲイン (PxGAコード0)<br>最大ゲイン (PxGAコード31) | 1.0<br>1.6<br>64<br>保証<br>- 2.5<br>+ 3.5<br>+ 9.5 |                          |                               | V p-p<br>V p-p<br>ステップ<br>dB<br>dB<br>dB |                                                                                                                                    |

| 可変ゲイン・アンプ (VGA)<br>最大入力範囲<br>最大出力範囲<br>ゲイン制御の分解能<br>ゲインの単調性<br>ゲイン範囲<br>低ゲイン (VGAコード70)<br>最大ゲイン (VGAコード1023)                          | 1.6<br>2.0<br>1024<br>2<br>36                     |                          |                               | V p-p<br>V p-p<br>ステップ<br>dB<br>dB       | デフォルト設定<br>保証                                                                                                                      |

| ブラック・レベル・クランプ<br>クランプ・レベルの分解能<br>クランプ・レベル<br>最小クランプ・レベル<br>最大クランプ・レベル                                                                  |                                                   | 256                      |                               | ステップ<br>LSB<br>LSB                       | ADC出力で測定                                                                                                                           |

| A/Dコンバータ<br>分解能<br>微分非直線性 (DNL)<br>ノー・ミスコード<br>フルスケール入力電圧                                                                              | 10                                                | ± 0.4<br>保証<br>2.0       | ± 1.0                         | ビット数<br>LSB<br>V                         |                                                                                                                                    |

| リファレンス電圧<br>上側リファレンス電圧 (VRT)<br>下側リファレンス電圧 (VRB)                                                                                       |                                                   | 2.0<br>1.0               |                               | V<br>V                                   |                                                                                                                                    |

| システム性能<br>ゲイン精度<br>低ゲイン (VGAコード70)<br>最大ゲイン (VGAコード1023)<br>ピーク非直線性、500mV入力信号<br>総合出力ノイズ<br>電源除去比 (PSR)                                | 5<br>38.5                                         | 6<br>39.5                | 7<br>40.5<br>0.2<br>0.6<br>40 | dB<br>dB<br>%<br>LSB rms<br>dB           | シグナル・チェーン全体を含む。<br>4dBのデフォルトPxGAゲインを含む。<br>ゲイン = (0.035 × コード) + 3.55dB<br>12dBゲインを使用。<br>ACグラウンドを入力、6dBゲインを使用。<br>電源をステップ変化させて測定。 |

### 注

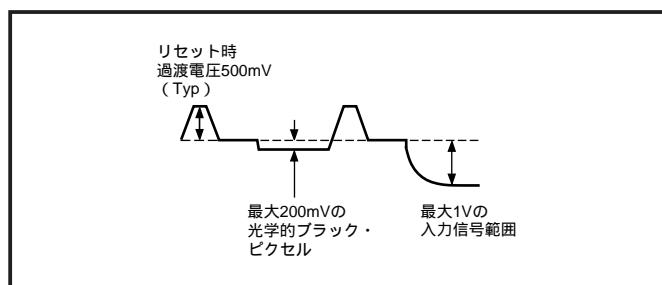

1 入力特性は次のように定義します。

仕様は予告なく変更されることがあります。

AD9895 - アナログ特性 (特に指定のない限り、AVDD1、2 = 3.0V、f<sub>CLL</sub> = 20MHz、T<sub>MIN</sub> ~ T<sub>MAX</sub>)

| パラメータ               | Min  | Typ  | Max  | 単位      | 注                                        |

|---------------------|------|------|------|---------|------------------------------------------|

| CDS                 |      |      |      |         |                                          |

| ゲイン                 |      | 0    |      | dB      |                                          |

| 許容CCDリセット過渡電圧       |      | 500  |      | mV      |                                          |

| 非飽和の最大入力範囲          | 1.0  |      |      | V p-p   | 入力特性                                     |

| CCDブラック・ピクセルの最大振幅   |      | ±200 |      | mV      | 注1に定義                                    |

| ピクセル・ゲイン・アンプ (PxGA) |      |      |      |         |                                          |

| 最大入力範囲              | 1.0  |      |      | V p-p   |                                          |

| 最大出力範囲              | 1.6  |      |      | V p-p   |                                          |

| ゲイン制御の分解能           |      | 64   |      | ステップ    |                                          |

| ゲインの単調性             |      |      |      |         | 保証                                       |

| ゲイン範囲               |      |      |      |         |                                          |

| 最小ゲイン (PxGAコード32)   |      | -2.5 |      | dB      |                                          |

| 中心ゲイン (PxGAコード0)    |      | +3.5 |      | dB      | デフォルト設定                                  |

| 最大ゲイン (PxGAコード31)   |      | +9.5 |      | dB      |                                          |

| 可変ゲイン・アンプ (VGA)     |      |      |      |         |                                          |

| 最大入力範囲              | 1.6  |      |      | V p-p   |                                          |

| 最大出力範囲              | 2.0  |      |      | V p-p   |                                          |

| ゲイン制御の分解能           |      | 1024 |      | ステップ    |                                          |

| ゲインの単調性             |      |      |      |         | 保証                                       |

| ゲイン範囲               |      |      |      |         |                                          |

| 低ゲイン (VGAコード70)     |      | 2    |      | dB      |                                          |

| 最大ゲイン (VGAコード1023)  |      | 36   |      | dB      |                                          |

| ブラック・レベル・クランプ       |      |      |      |         |                                          |

| クランプ・レベルの分解能        |      | 256  |      | ステップ    |                                          |

| クランプ・レベル            |      |      |      |         | ADC出力で測定                                 |

| 最小クランプ・レベル          |      | 0    |      | LSB     |                                          |

| 最大クランプ・レベル          |      | 255  |      | LSB     |                                          |

| A/Dコンバータ            |      |      |      |         |                                          |

| 分解能                 | 12   |      |      | ビット数    |                                          |

| 微分非直線性 (DNL)        |      | ±0.5 | ±1.0 | LSB     |                                          |

| ノー・ミスコード            |      | 保証   |      |         |                                          |

| フルスケール入力電圧          |      | 2.0  |      | V       |                                          |

| リファレンス電圧            |      |      |      |         |                                          |

| 上側リファレンス電圧 (VRT)    |      | 2.0  |      | V       |                                          |

| 下側リファレンス電圧 (VRB)    |      | 1.0  |      | V       |                                          |

| システム性能              |      |      |      |         |                                          |

| ゲイン精度               |      |      |      |         | シグナル・チェーン全体を含む。                          |

| 低ゲイン (VGAコード70)     | 5    | 6    | 7    | dB      | 4dBのデフォルトPxGAゲインを含む。                     |

| 最大ゲイン (VGAコード1023)  | 38.5 | 39.5 | 40.5 | dB      | ゲイン = (0.035 × コード) + 3.55dB             |

| ピーク非直線性、500mV入力信号   |      | 0.2  |      | %       |                                          |

| 総合出力ノイズ             |      | 0.8  |      | LSB rms | 12dBゲインを使用。                              |

| 電源除去比 (PSR)         |      | 40   |      | dB      | ACグラウンドを入力、6dBゲインを使用。<br>電源をステップ変化させて測定。 |

## 注

1 入力特性は次のように定義します。

仕様は予告なく変更されることがあります。

# AD9891/AD9895

**タイミング特性** (特に指定のない限り、 $C_L = 20\text{pF}$ 、 $\text{AVDD} = \text{DVDD} = \text{DRVDD} = 3.0\text{V}$ 、 $f_{\text{CLI}} = 20\text{MHz}$  [ AD9891 ] または $30\text{MHz}$  [ AD9895 ])

| パラメータ                                                                                                                                                                                       | 記号                                                                                                               | Min                              | Typ        | Max | 単位                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|-----|-----------------------------------|

| マスター・クロック、CLI (図7)<br>CLIクロック周期 (AD9891)<br>CLIハイレベル／ローレベル・パルス幅 (AD9891)<br>CLIクロック周期 (AD9895)<br>CLIハイレベル／ローレベル・パルス幅 (AD9895)<br>CLIの立ち上がりエッジから内部ピクセル・ポジション0までの遅延                          | $t_{\text{CONV}}$                                                                                                | 50<br>20                         | 25         |     | ns<br>ns                          |

|                                                                                                                                                                                             | $t_{\text{CONV}}$                                                                                                | 33.3<br>13                       | 16.7       |     | ns<br>ns                          |

|                                                                                                                                                                                             | $t_{\text{CLIDLY}}$                                                                                              | 6                                |            |     | ns                                |

| AFEクランプ・パルス <sup>1</sup> (図13)<br>CLPDMパルス幅<br>CLPOBパルス幅 <sup>2</sup>                                                                                                                       |                                                                                                                  | 4<br>2                           | 10<br>20   |     | ピクセル<br>ピクセル                      |

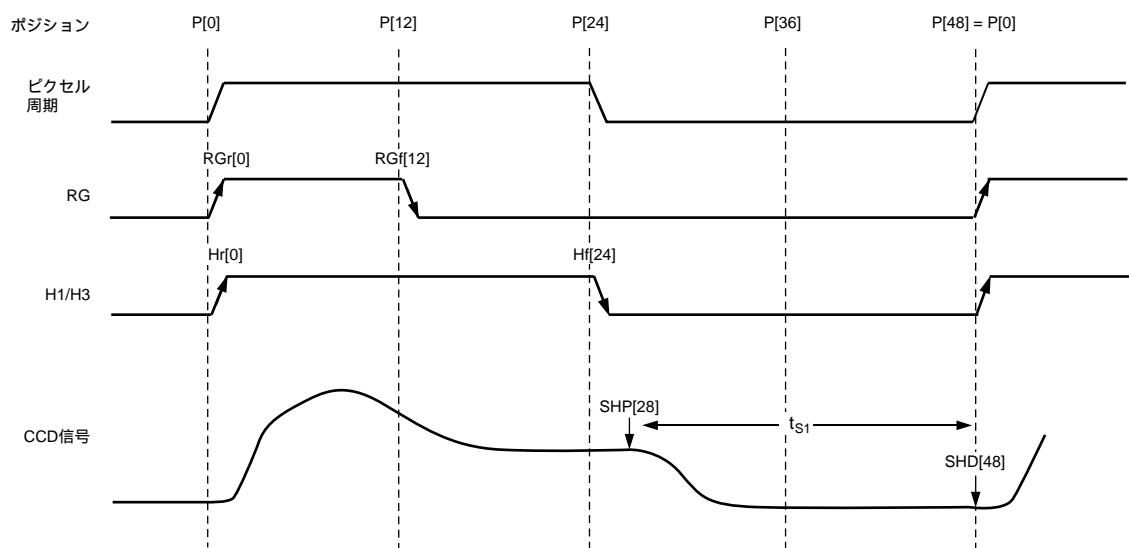

| AFEサンプル・ロケーション <sup>1</sup> (図10)<br>SHPサンプル・エッジからSHDサンプル・エッジまで (AD9891)<br>SHPサンプル・エッジからSHDサンプル・エッジまで (AD9895)                                                                             | $t_{\text{S1}}$                                                                                                  | 20<br>13                         | 25<br>16.7 |     | ns<br>ns                          |

| データ出力 (図12)<br>DCLKの立ち上がりエッジから出力までの遅延<br>SHP/SHDサンプリングからのパイプライン遅延                                                                                                                           | $t_{\text{OD}}$                                                                                                  |                                  | 8<br>9     |     | ns<br>サイクル数                       |

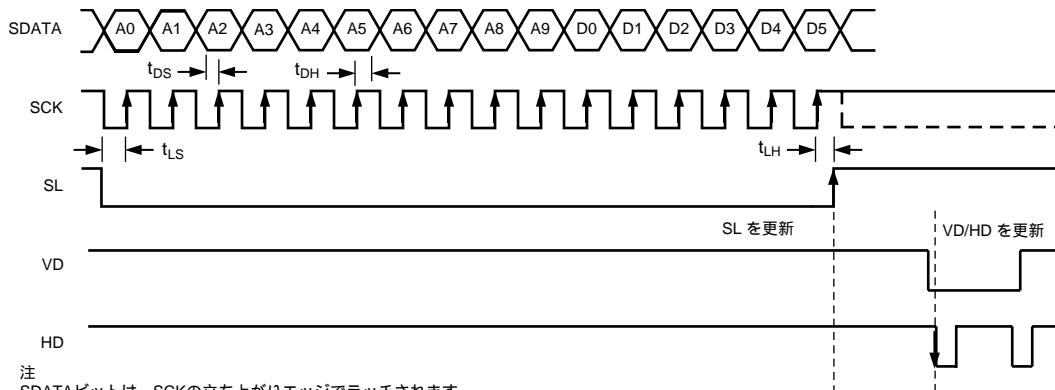

| シリアル・インターフェース (図52および53)<br>最大SCK周波数<br>SLからSCKまでのセットアップ・タイム<br>SCKからSLまでのホールド・タイム<br>SDATA有効からSCKの立ち上がりエッジまでのセットアップ・タイム<br>SCKの立ち下がりエッジからSDATA有効までのホールド・タイム<br>SCKの立ち下がりエッジからSDATA有効読み出しまで | $f_{\text{SCLK}}$<br>$t_{\text{LS}}$<br>$t_{\text{LH}}$<br>$t_{\text{DS}}$<br>$t_{\text{DH}}$<br>$t_{\text{DV}}$ | 10<br>10<br>10<br>10<br>10<br>10 |            |     | MHz<br>ns<br>ns<br>ns<br>ns<br>ns |

## 注

1 パラメータはプログラマブルです。

2 最小CLPOBパルス幅は機能動作の場合のみ。良いクランプ性能を得るために幅の広いパルスの使用が推奨されます。

## 絶対最大定格\*

| パラメータ           | 基準    | Min   | Max         | 単位 |

|-----------------|-------|-------|-------------|----|

| AVDD1、2         | AVSS  | - 0.3 | + 3.9       | V  |

| TCVDD           | TCVSS | - 0.3 | + 3.9       | V  |

| HVDD            | HVSS  | - 0.3 | + 5.5       | V  |

| RGVDD           | RGVSS | - 0.3 | + 5.5       | V  |

| DVDD            | DVSS  | - 0.3 | + 3.9       | V  |

| DRVDD           | DRVSS | - 0.3 | + 3.9       | V  |

| RG出力            | RGVSS | - 0.3 | RGVDD + 0.3 | V  |

| H1～H4出力         | HVSS  | - 0.3 | HVDD + 0.3  | V  |

| デジタル出力          | DVSS  | - 0.3 | DVDD + 0.3  | V  |

| デジタル入力          | DVSS  | - 0.3 | DVDD + 0.3  | V  |

| SCK、SL、SDATA    | DVSS  | - 0.3 | DVDD + 0.3  | V  |

| VRT、VRB         | AVSS  | - 0.3 | AVDD + 0.3  | V  |

| BYP1～BYP3、CCDIN | AVSS  | - 0.3 | AVDD + 0.3  | V  |

| 接合温度            |       | 150   |             |    |

| ピン温度、10秒        |       | 350   |             |    |

## パッケージ熱特性

### 熱抵抗

$$J_A = 61 \text{ } ^\circ\text{C/W}$$

$$J_C = 29.7 \text{ } ^\circ\text{C/W}$$

## オーダー・ガイド

| 製品モデル     | 温度範囲        | パッケージ | パッケージ・オプション* |

|-----------|-------------|-------|--------------|

| AD9891KBC | - 20 ~ + 85 | LFBGA | BC-64        |

| AD9895KBC | - 20 ~ + 85 | LFBGA | BC-64        |

## 注意

ESD (静電放電) の影響を受けやすいデバイスです。4000Vもの高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることがあります。本製品には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や機能喪失を回避するために、適切なESD予防措置をとるようお奨めします。

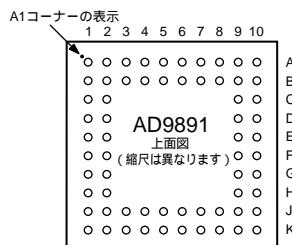

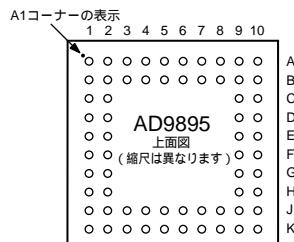

## AD9891 ピン配置

ピン機能の説明<sup>1</sup>

| ピン | 記号         | タイプ <sup>2</sup> | 説明                                         | ピン  | 記号    | タイプ <sup>2</sup> | 説明                  |

|----|------------|------------------|--------------------------------------------|-----|-------|------------------|---------------------|

| A1 | VD         | DO               | 垂直同期パルス(スレーブ・モードで入力、マスター・モードで出力)           | K9  | VSG5  | DO               | CCDセンサー・ゲート・パルス5    |

| B1 | HD         | DO               | 水平同期パルス(スレーブ・モードで入力、マスター・モードで出力)           | J9  | VSG6  | DO               | CCDセンサー・ゲート・パルス6    |

| C1 | SYNC       | DI               | 外部システム同期入力                                 | K10 | VSG7  | DO               | CCDセンサー・ゲート・パルス7    |

| C2 | LD/FD      | DO               | ラインまたはフィールド識別出力                            | J10 | VSG8  | DO               | CCDセンサー・ゲート・パルス8    |

| D1 | DCLK       | DO               | データ・クロック出力                                 | H10 | H1    | DO               | CCD水平クロック1          |

| D2 | CLPOB/PBLK | DO               | CLPOB出力またはPBLK出力                           | H9  | H2    | DO               | CCD水平クロック2          |

| E1 | NC         |                  | 内部で接続なし                                    | G10 | HVDD  | P                | H1~H4ドライバの電源        |

| E2 | NC         |                  | 内部で接続なし                                    | G9  | HVSS  | P                | H1~H4ドライバのグラウンド     |

| F2 | DO/SDO     | DO               | データ出力(LSB)(シリアル・データ出力としても使用 <sup>3</sup> ) | F10 | H3    | DO               | CCD水平クロック3          |

| F1 | D1         | DO               | データ出力                                      | F9  | H4    | DO               | CCD水平クロック4          |

| G2 | D2         | DO               | データ出力                                      | E10 | RGVDD | P                | RGドライバの電源           |

| G1 | D3         | DO               | データ出力                                      | E9  | RGVSS | P                | RGドライバのグラウンド        |

| H2 | D4         | DO               | データ出力                                      | D9  | RG    | DO               | CCDリセット・ゲート・クロック    |

| H1 | D5         | DO               | データ出力                                      | D10 | CLO   | DO               | 水晶発振子用リファレンス・クロック出力 |

| J2 | D6         | DO               | データ出力                                      | C10 | CLI   | DI               | リファレンス・クロック入力       |

| J1 | D7         | DO               | データ出力                                      | B10 | TCVDD | P                | タイミングコア用アナログ電源      |

| K2 | D8         | DO               | データ出力                                      | C9  | TCVSS | P                | タイミングコア用アナログ・グラウンド  |

| K1 | D9         | DO               | データ出力(MSB)                                 | A10 | AVDD1 | P                | AFE用アナログ電源          |

| K3 | DRVDD      | P                | データ出力ドライバの電源                               | B9  | AVSS1 | P                | AFE用アナログ・グラウンド      |

| K4 | DRVSS      | P                | データ出力ドライバのグラウンド                            | A9  | BYP1  | AO               | アナログ回路バイパス          |

| J3 | VSUB       | DO               | CCDサブストレート・バイアス                            | B8  | BYP2  | AO               | アナログ回路バイパス          |

| J4 | SUBCK      | DO               | CCDサブストレート・クロック(Eシャッター)                    | A8  | CCDIN | AI               | CCD信号入力             |

| K5 | V1         | DO               | CCD垂直転送クロック1                               | A7  | BYP3  | AO               | アナログ回路バイパス          |

| J5 | V2         | DO               | CCD垂直転送クロック2                               | B7  | AVDD2 | P                | AFE用アナログ電源          |

| K6 | V3         | DO               | CCD垂直転送クロック3                               | B6  | AVSS2 | P                | AFE用アナログ・グラウンド      |

| J6 | V4         | DO               | CCD垂直転送クロック4                               | A6  | REFB  | AO               | リファレンス上側バイパス        |

| K7 | VSG1/V5    | DO               | CCDセンサー・ゲート・パルス1(V5 <sup>4</sup> としても使用)   | A5  | REFT  | AO               | リファレンス下側バイパス        |

| J7 | VSG2/V6    | DO               | CCDセンサー・ゲート・パルス2(V6 <sup>4</sup> としても使用)   | B5  | SL    | DI               | 3線式シリアル負荷パルス        |

| K8 | VSG3/V7    | DO               | CCDセンサー・ゲート・パルス3(V7 <sup>4</sup> としても使用)   | A4  | SDI   | DI               | 3線式シリアル・データ入力       |

| J8 | VSG4/V8    | DO               | CCDセンサー・ゲート・パルス4(V8 <sup>4</sup> としても使用)   | B4  | SCK   | DI               | 3線式シリアル・クロック        |

## 注

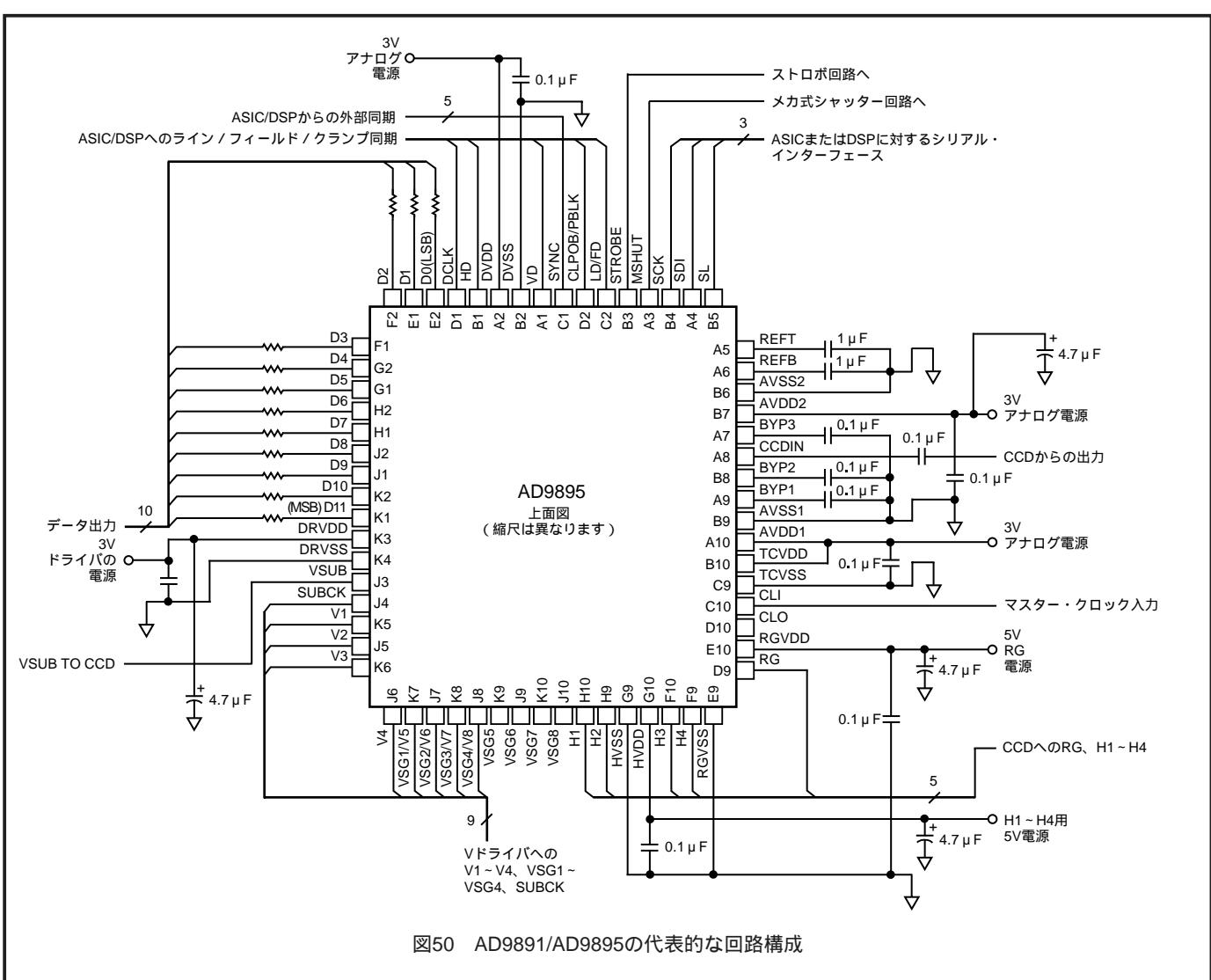

<sup>1</sup> 回路構成については図50参照。<sup>2</sup> AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力、DIO = デジタル入/出力、P = 電源。<sup>3</sup> レジスタ・リードバック・モード。<sup>4</sup> フレーム転送CCDモード。

# AD9891/AD9895

AD9895 ピン配置

ピン機能の説明<sup>1</sup>

| ピン | 記号          | タイプ <sup>2</sup> | 説明                                       | ピン  | 記号    | タイプ <sup>2</sup> | 説明                  |

|----|-------------|------------------|------------------------------------------|-----|-------|------------------|---------------------|

| A1 | VD          | DO               | 垂直同期パルス(スレーブ・モードで入力、マスター・モードで出力)         | K9  | VSG5  | DO               | CCDセンサー・ゲート・パルス5    |

| B1 | HD          | DO               | 水平同期パルス(スレーブ・モードで入力、マスター・モードで出力)         | J9  | VSG6  | DO               | CCDセンサー・ゲート・パルス6    |

| C1 | 同期          | DI               | 外部システム同期入力                               | K10 | VSG7  | DO               | CCDセンサー・ゲート・パルス7    |

| C2 | LD/FD       | DO               | ラインまたはフィールド識別出力                          | J10 | VSG8  | DO               | CCDセンサー・ゲート・パルス8    |

| D1 | DCLK        | DO               | データ・クロック出力                               | H10 | H1    | DO               | CCD水平クロック1          |

| D2 | CLPOB/ PBLK | DO               | CLPOB出力またはPBLK出力                         | H9  | H2    | DO               | CCD水平クロック2          |

| E2 | DO          | DO               | データ出力(LSB)                               | G10 | HVDD  | P                | H1~H4ドライバの電源        |

| E1 | D1          | DO               | データ出力                                    | G9  | HVSS  | P                | H1~H4ドライバのグラウンド     |

| F2 | DO/SDO      | DO               | データ出力(シリアル・データ出力としても使用 <sup>3</sup> )    | F10 | H3    | DO               | CCD水平クロック3          |

| F1 | D1          | DO               | データ出力                                    | F9  | H4    | DO               | CCD水平クロック4          |

| G2 | D2          | DO               | データ出力                                    | E10 | RGVDD | P                | RGドライバの電源           |

| G1 | D3          | DO               | データ出力                                    | E9  | RGVSS | P                | RGドライバのグラウンド        |

| H2 | D4          | DO               | データ出力                                    | D9  | RG    | DO               | CCDリセット・ゲート・クロック    |

| H1 | D5          | DO               | データ出力                                    | D10 | CLO   | DO               | 水晶発振子用リファレンス・クロック出力 |

| J2 | D6          | DO               | データ出力                                    | C10 | CLI   | DI               | リファレンス・クロック入力       |

| J1 | D7          | DO               | データ出力                                    | B10 | TCVDD | P                | タイミングコア用アナログ電源      |

| K2 | D8          | DO               | データ出力                                    | C9  | TCVSS | P                | タイミングコア用アナログ・グラウンド  |

| K1 | D9          | DO               | データ出力(MSB)                               | A10 | AVDD1 | P                | AFE用アナログ電源          |

| K3 | DRVDD       | P                | データ出力ドライバの電源                             | B9  | AVSS1 | P                | AFE用アナログ・グラウンド      |

| K4 | DRVSS       | P                | データ出力ドライバのグラウンド                          | A9  | BYP1  | AO               | アナログ回路バイパス          |

| J3 | VSUB        | DO               | CCDサブストレート・バイアス                          | B8  | BYP2  | AO               | アナログ回路バイパス          |

| J4 | SUBCK       | DO               | CCDサブストレート・クロック(Eシャッター)                  | A8  | CCDIN | AI               | CCD信号入力             |

| K5 | V1          | DO               | CCD垂直転送クロック1                             | A7  | BYP3  | AO               | アナログ回路バイパス          |

| J5 | V2          | DO               | CCD垂直転送クロック2                             | B7  | AVDD2 | P                | AFE用アナログ電源          |

| K6 | V3          | DO               | CCD垂直転送クロック3                             | B6  | AVSS2 | P                | AFE用アナログ・グラウンド      |

| J6 | V4          | DO               | CCD垂直転送クロック4                             | A6  | REFB  | AO               | リファレンス下側バイパス        |

| K7 | VSG1/V5     | DO               | CCDセンサー・ゲート・パルス1(V5 <sup>4</sup> としても使用) | A5  | REFT  | AO               | リファレンス上側バイパス        |

| J7 | VSG2/V6     | DO               | CCDセンサー・ゲート・パルス2(V6 <sup>4</sup> としても使用) | B5  | SL    | DI               | 3線式シリアル負荷パルス        |

| K8 | VSG3/V7     | DO               | CCDセンサー・ゲート・パルス3(V7 <sup>4</sup> としても使用) | A4  | SDI   | DI               | 3線式シリアル・データ入力       |

| J8 | VSG4/V8     | DO               | CCDセンサー・ゲート・パルス4(V8 <sup>4</sup> としても使用) | B4  | SCK   | DI               | 3線式シリアル・クロック        |

注

1 回路構成については図50参照。

2 AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力、DIO = デジタル入/出力、P = 電源。

3 レジスタ・リードバック・モード。

4 フレーム転送CCDモード。

## 仕様の定義

### 微分非直線性 ( DNL )

理想的なADCでは、各コード遷移は1 LSBだけ離れた位置で発生します。DNLとは、この理想値からの最大偏差をいいます。したがって、各コードには有限の幅があります。ノーミスコードで10ビット分解能を保証するとは、全動作状態で1024コードすべてが出力されることを表します。

### ピーク非直線性

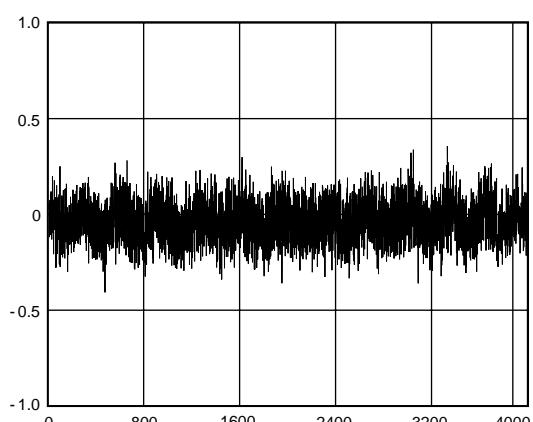

ピーク非直線性はシグナル・チェーン全体に対する仕様です。理論直線からのAD9891出力の最大偏差を意味します。“ゼロ・スケール”として使用されるポイントは、最初のコード遷移より0.5 LSBだけ下に存在します。“正フルスケール”は、最後のコード遷移より $1 + 0.5$  LSBだけ上のレベルと定義されます。偏差は各コード出力の中央の位置と直線の間の距離として測定されます。したがって、誤差は $2V$ ADCフルスケール信号のパーセント値として表されます。入力信号は常にADCのフルスケール範囲に一致するように増幅されます。

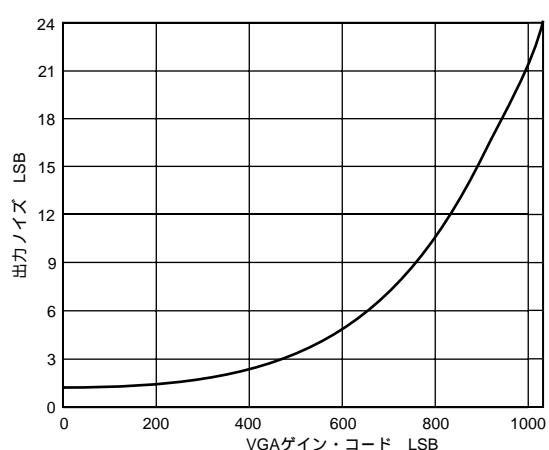

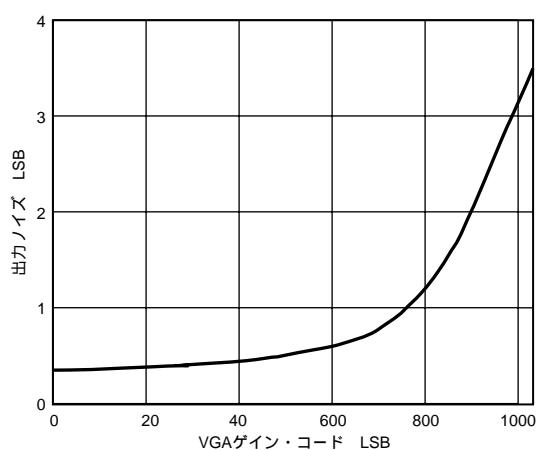

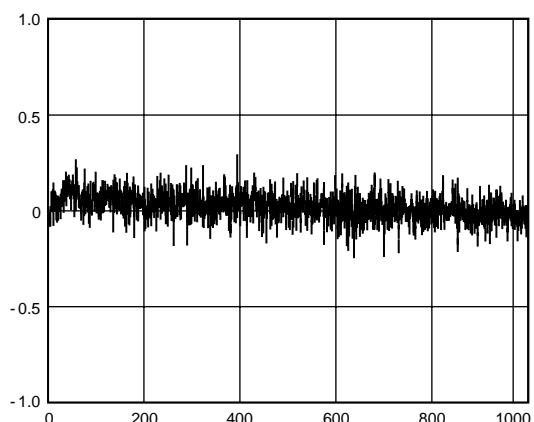

## 総合出力ノイズ

RMS出力ノイズはヒストグラム手法を使って測定されます。ADC出力コードの標準偏差をLSB数として算出し、規定ゲイン設定でのシグナル・チェーン全体のrmsノイズ・レベルを表します。出力ノイズは、1 LSB = ( $\text{ADCフルスケール}/2^n$ ) の関係を使って等価な電圧に変換することができます ( $n$ はADCのビット分解能)。AD9891では、1 LSB = 2mVになります。AD9895では1 LSB = 0.5mVになります。

## 電源除去比 ( PSR )

PSRは、電源ピンにステップ変化を入力して測定します。PSR仕様は、電源電圧でのステップ変化に対するデータ出力の変化から計算されます。

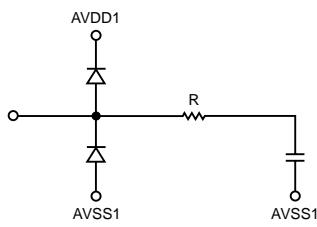

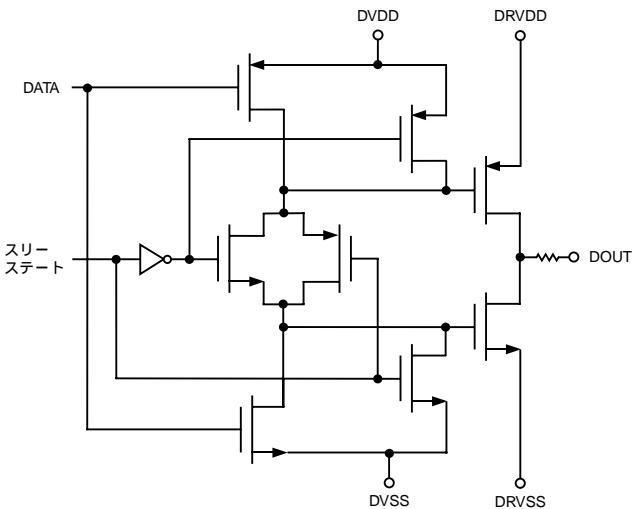

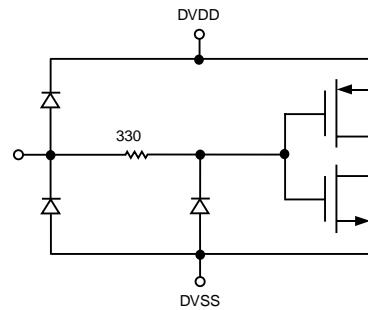

等価回路

図1 CCDIN

図2 デジタル・データ出力

図3 デジタル入力

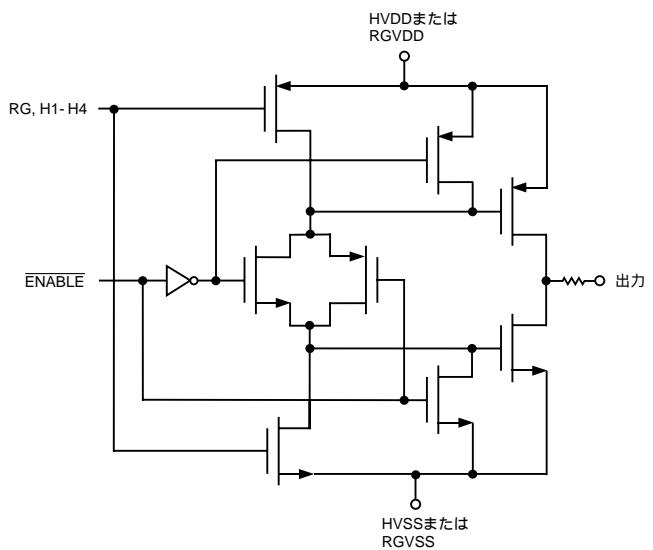

図4 H1~H4, RG ドライバ

# AD9891/AD9895 - 代表的な性能特性

## システム概要

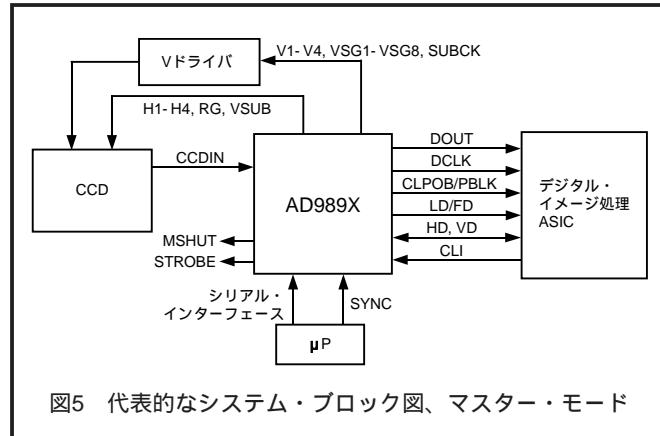

図5に、マスター・モードのAD9891/AD9895に対する代表的なシステム・ブロック図を示します。CCD出力はAD9891/AD9895のAFE回路により処理され、このAFE回路はCDS、PxGA、VGA、ブラック・レベル・クランプ、A/Dコンバータから構成されています。デジタル化されたピクセル情報はデジタル・イメージ・プロセッサ・チップに送られ、このチップはポスト処理と圧縮を実行します。CCDを動作させるためには、システム・マイクロプロセッサから3線式シリアル・インターフェースを介してすべてのCCDタイミング・パラメータをAD9891/AD9895に書き込む必要があります。イメージ・プロセッサまたは外部水晶発振子から供給されるシステム・マスター・クロック(CL)から、AD9891/AD9895はCCDの水平クロックと垂直クロックおよびすべての内部AFEクロックを発生します。外部同期機能はマイクロプロセッサからのSYNCパルスにより実現されます。マイクロプロセッサは内部カウンタをリセットしてVD出力とHD出力を再同期します。

図5 代表的なシステム・ブロック図、マスター・モード

AD9891/AD9895はスレーブ・モードでも動作することができます。このモードではVDとHDが外部のイメージ・プロセッサから供給され、すべてのAD9891/AD9895タイミングがVDとHDに同期されます。

AD9891/AD9895にはH1～H4に対するHドライバが内蔵されているため、これらのクロックを直接CCDに接続できます。

H駆動電圧は最大5Vまで対応しています。垂直転送クロック、センサー・ゲート・パルス、サブストレート・クロックに対しては、外付けVドライバが必要です。

また、AD9891/AD9895にはプログラマブルなMSHUT出力とSTROBE出力が用意されており、メカシャッターやストロボ(フラッシュ)回路の起動に使うことができます。

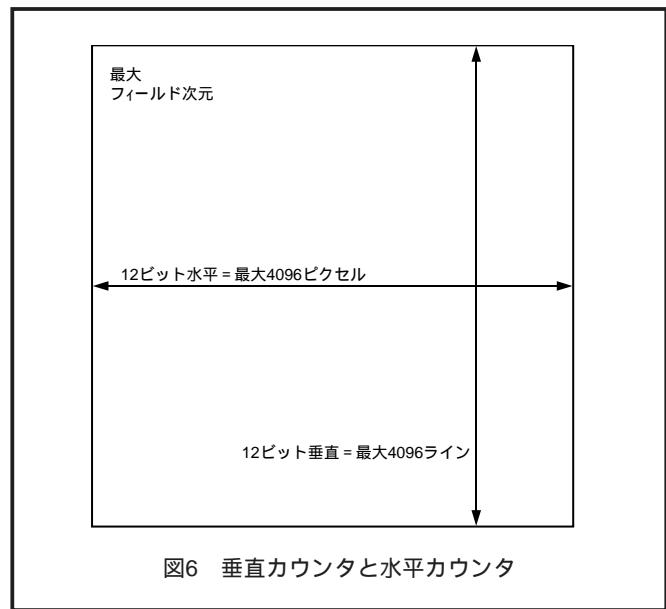

図6に、AD9891/AD9895の水平と垂直のカウンタ次元を示します。ライン数とピクセル数を指定するときは、これらの次元を使って、すべての内部水平クロックと内部垂直クロックを書き込む必要があります。

図6 垂直カウンタと水平カウンタ

# AD9891/AD9895

## Precision Timingによる高速タイミングの生成

AD9891/AD9895はPrecision Timingコアを使って柔軟な高速タイミング信号を生成します。このコアは、CCDとAFEに対して使用するタイミングの基となるリセット・ゲートRG、水平ドライバH1～H4、SHP/SHDサンプル・クロックを発生します。独自のアーキテクチャの採用により、水平CCD読み出しとAFE相関ダブル・サンプリングに対して高精度の制御を提供することにより、システム設計者は、画像品質の最適化を行います。

AD9891/AD9895の高速タイミングはマスター・モード設定とスレーブ・モード設定に対して同じ動作をします。

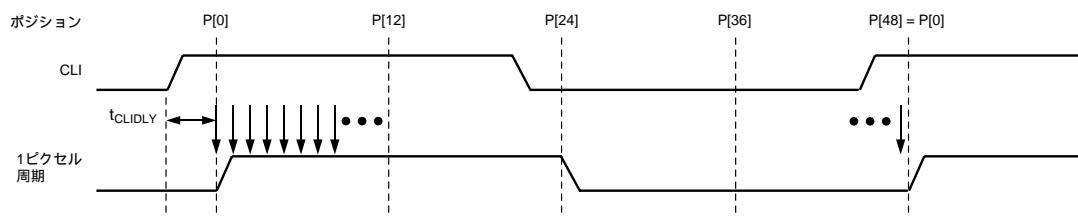

## タイミング分解能

Precision Timingコアは1倍マスター・クロック入力 (CLI) を基準として使います。このクロックは、CCDピクセル・クロック周波数と同じです。図7に、内部タイミング・コアがマスター・クロック周期を48ステップ (エッジ・ポジション数) に分割する方法を示します。20MHzのCLI周波数の場合、Precision Timingコアのエッジ分解能は1nsになります。1倍システム・クロックが使用できない場合は、CLIDIVIDEレジスタ (addr x01F) に書き込みを行って、2倍リファレンス・クロックを使うことができます。この場合、AD9891/AD9895はCLI周波数を内部で2分周します。また、AD9891/AD9895はCLIを反転したマスター・クロック出力

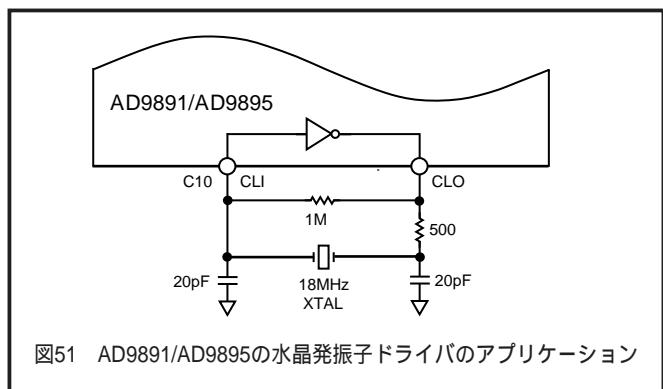

(CLO) も用意しています。この出力は水晶発振子ドライバとして使用することを目的にしています。水晶発振子をCLIピンとCLOピンの間に接続してAD9891/AD9895のマスター・クロックを発生します。水晶発振子の詳細については、図51を参照してください。

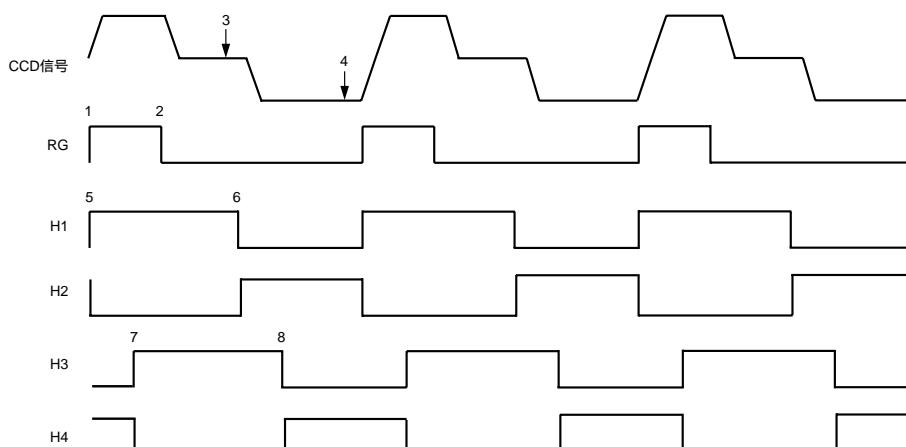

## 高速クロックのプログラマブル性

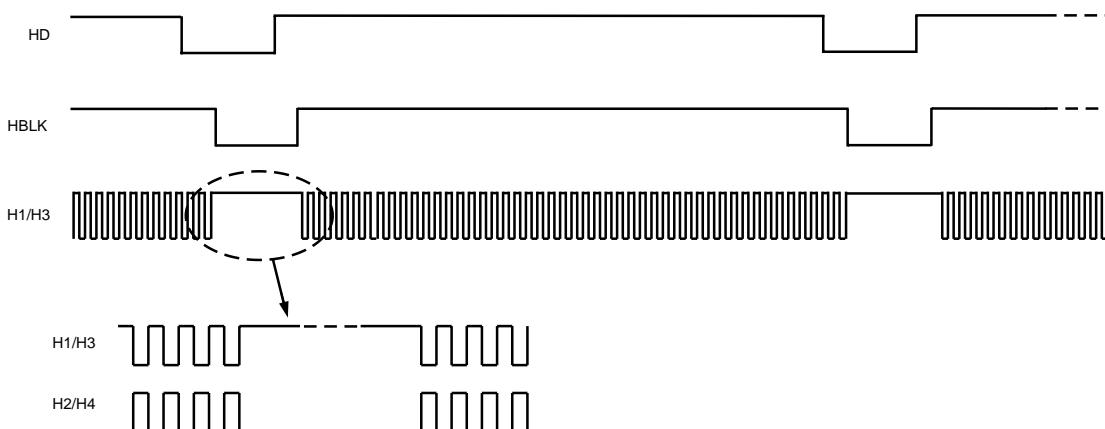

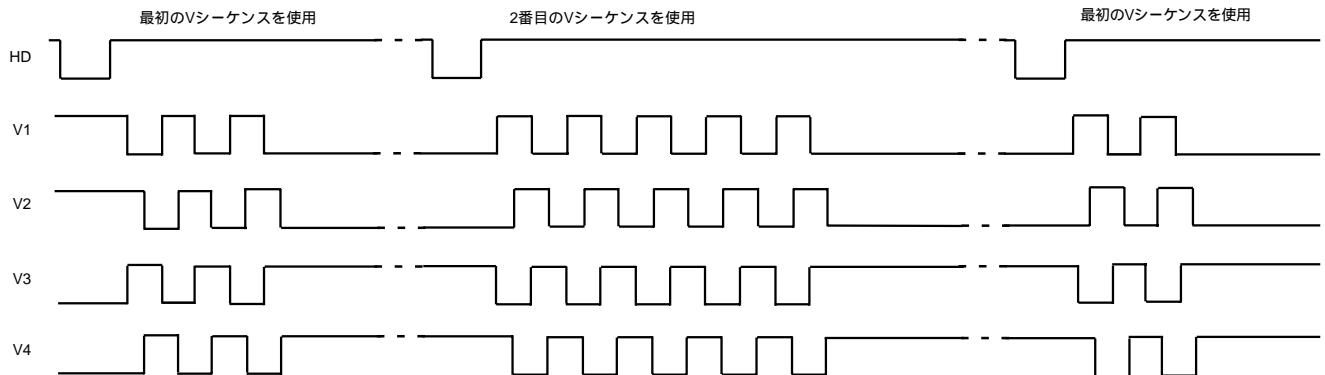

図8に、高速クロックRG、H1～H4、SHP、SHDの発生方法を示します。RGパルスは、立ち上がりエッジと立ち下がりエッジがプログラマブルであり、極性制御を使って反転することができます。水平クロックH1とH3は、立ち上がりエッジ、立ち下がりエッジ、極性制御がプログラマブルです。H2クロックとH4クロックは、常にそれぞれH1とH3の反転になります。表Iに、高速タイミング・レジスタとパラメータをまとめています。図9に、代表的な2相Hクロックの配置を示します。ここでは、H3とH4はH1およびH2と同じエッジ位置に設定してあります。

エッジ位置レジスタは6ビット幅ですが、48個の有効エッジ位置までしか使用しません。したがって、レジスタ値は4個のグループに配置され、各グループは12個のエッジ位置を持ちます。表IIに、対応するエッジ位置に対するレジスタ値を示します。図10に、高速クロック信号の範囲とデフォルト位置を示します。

注

ピクセル・クロック周期は48ポジションに分割され、高速クロックの細かいエッジ分解能を提供します。

CLI入力から内部ピクセル周期ポジションまでは、固定の遅延が存在します ( $t_{CLIDLY} = 6\text{ns TYP}$ )。

図7 CLIマスター・クロック入力からの高速クロック分解能

プログラマブルなクロック・ポジション：

1 : RGの立ち上がりエッジ

2 : RGの立ち下がりエッジ

3 : SHPサンプル位置

4 : SHDサンプル位置

5 : H1の立ち上がりエッジ・ポジションAND 6 : H1の立ち下がりエッジ・ポジション (H2はH1の反転)

7 : H3の立ち上がりエッジ・ポジションAND 8 : H3の立ち下がりエッジ・ポジション (H4はH3の反転)

図8 高速クロックのプログラマブルな位置設定

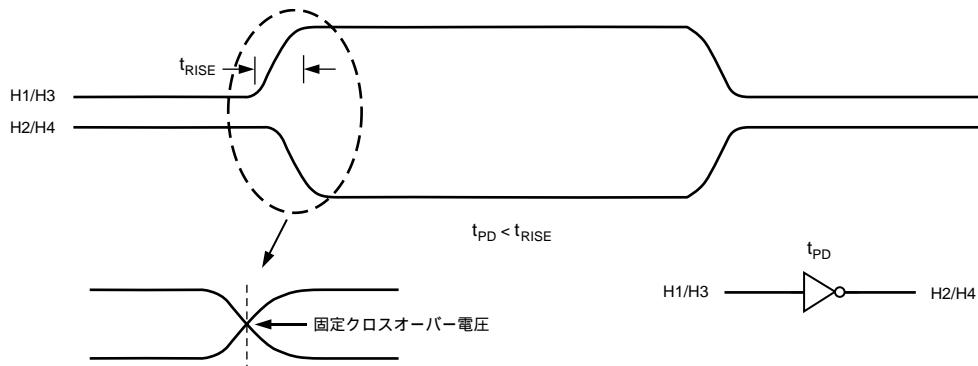

## HドライバとRG出力

プログラマブルなタイミング・ポジションの他に、AD9891/AD9895はRG出力とH1～H4出力に対する出力ドライバも内蔵しています。これらのドライバは、CCDを直接駆動できる十分な能力を持っています。Hドライバ電流はDRVレジスタ (addr x0E1～x0E4) を使って、特定の負荷に対して最適な立ち上がり / 立ち下がり時間を調整することができます。RG駆動電流はRGDRVレジスタ (addr x0E8) を使って調整することができます。3ビットの各DRVレジスタは3.5mA単位で調整可能であり、最小設定0はOFFすなわちスリーステートに、最大設定7は24.5mAに、それぞれ対応します。図11に示すように、H2出力とH4出力はそれぞれH1とH3の反転になっています。信号反転に起因する内部伝搬遅延は1ns未満であり、CCD負荷を駆動する代表的な立ち上がり時間よりはるかに小さい値です。このため、出力振幅の約50%でH1/H2電圧がクロスオーバーします。このクロスオーバー電圧は設定できません。

表I H1～H4、RG、SHP、SHDのタイミング・パラメータ

| レジスタ   | ビット数 | 範囲            | 説明                                   |

|--------|------|---------------|--------------------------------------|

| POL    | 1b   | ハイレベル / ローレベル | H1、H3、RGの極性制御 (0 = 非反転、1 = 反転)       |

| POSLOC | 6b   | 0～47エッジ位置     | H1、H3、RGの立ち上がりエッジ位置、SHPとSHDのサンプリング位置 |

| NEGLOC | 6b   | 0～47エッジ位置     | H1、H3、RGの立ち下がりエッジ位置                  |

| DRV    | 3b   | 0～47電流ステップ    | H1～H4出力とRG出力の駆動電流 (3.5mA / ステップ)     |

図9 2相Hクロックの動作

表II Precision Timingのエッジ位置

| グループ | エッジ位置 (10進) | レジスタ値 (10進) | レジスタ値 (2進)    |

|------|-------------|-------------|---------------|

| I    | 0～11        | 0～11        | 000000～001011 |

| II   | 12～23       | 16～27       | 010000～011011 |

| III  | 24～35       | 32～43       | 100000～101011 |

| IV   | 36～47       | 48～59       | 110000～111011 |

# AD9891/AD9895

すべての信号エッジは、1ピクセル周期内で48位置の内の任意の1位置に設定することができます。

図は各信号のデフォルト・ポジションを示しています。

図10 高速クロックのデフォルト設定とプログラマブルな設定

図11 Hクロック反転位相の関係

注

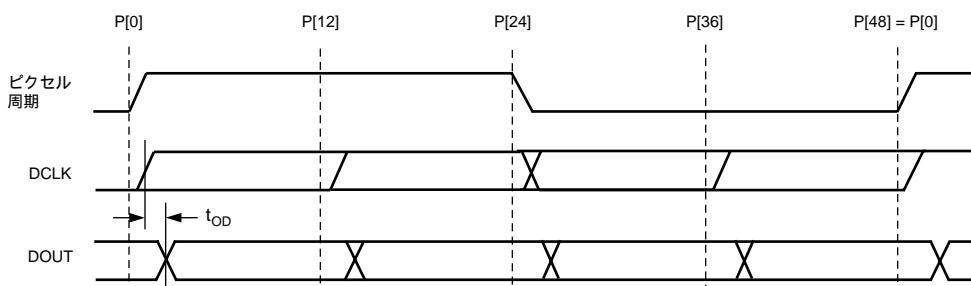

データ出力 (DOUT) とDCLK位相は、ピクセル周期に対して調整可能です。1クロック周期内で、

データ変化を48箇所の位置に設定することができます。

DCLKの立ち上がりエッジからDOUTの立ち上がりエッジまでの出力遅延 ( $t_{OD}$ ) はプログラマブルです。

図12 デジタル出力の位相調整

## 水平クランプとプランキング

AD9891/AD9895の水平クランプとプランキング・パルスは、多様なアプリケーションに合わせて設定できます。垂直タイミング発生の場合と同様に、個々のシーケンスが各信号に対して定義されており、画像読み出し時に複数の領域に構成されます。この機能を使うと、さまざまな画像転送タイミングと高速なライン・シフトを可能にするため、ブロック・レベルへのピクセル・クランプとプランキング・パターンを読み出しの各ステージで変更することができます。

### CLPOB、CLPDM、PBLKの各シーケンス

AFE水平タイミングはCLPOB、CLPDM、PBLKから構成されています（図13）。この3本の信号は表IIIに示すレジスタを使って独立して設定することができます。SPOLは信号のスタート極性であり、TOG1とTOG2はパルスの最初および2番目のトグル・ポジションです。3本の信号はすべてアクティブ・ローであり、これに従って設定する必要があります。各信号に対して最大4種類のシーケンスを設定することができます。

プログラミング条件を簡単にするために、デフォルトでCLPDM信号はCLPOB信号と同じです。CLPDM信号の個別

制御が必要な場合は、SINGLE\_CLAMPレジスタ（addr x031）をローレベルに設定します。

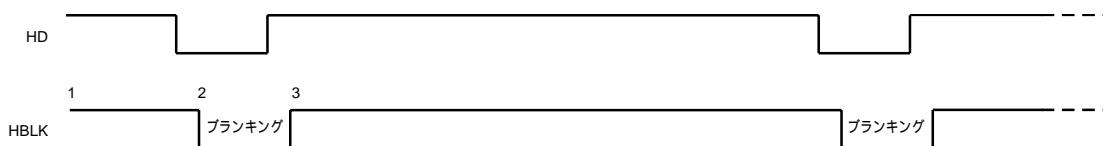

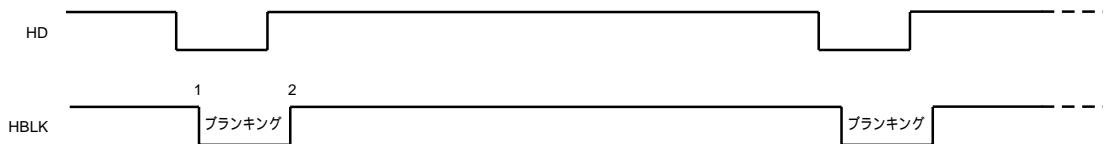

### 各HBLKシーケンス

図14に示すHBLKのプログラマブルなタイミングはCLPOB、CLPDM、PBLKと同じです。ただし、スタート極性制御は存在しません。プランキング期間のスタート・ポジションとトップ・ポジションを指定するときは、トグル・ポジションのみを使います。さらに、HBLKMASKという極性制御レジスタがあり、プランキング期間の水平クロック信号H1～H4の極性を指定します。

HBLKMASKをハイレベルに設定すると、プランキング期間はH1 = H3 = ローレベルに、H2 = H4 = ハイレベルに、それぞれ設定されます（図15）。HBLKに対して最大4種類のシーケンスを指定することができます。

### 水平シーケンスの制御

AD9891/AD9895はシーケンスチェンジポジション（SCP）とシーケンス・ポインタ（S PTR）を使って各水平シーケンスを構成します。

- 設定項目：

- 1：スタート極性（クランプ領域とプランク領域はアクティブ・ロー）

- 2：最初のトグル・ポジション

- 3：2番目のトグル・ポジション

図13 クランプ・パルスとプリプランク・パルスの配置

- 設定項目：

- 1：最初のトグル・ポジション = プランキングのスタート

- 2：2番目のトグル・ポジション = プランキングの終わり

図14 水平プランキング（HBLK）パルスの配置

注

プランキング時のH1の極性はプログラマブルです（H2は、H1と反対極性）。

図15 HBLKマスクの制御

# AD9891/AD9895

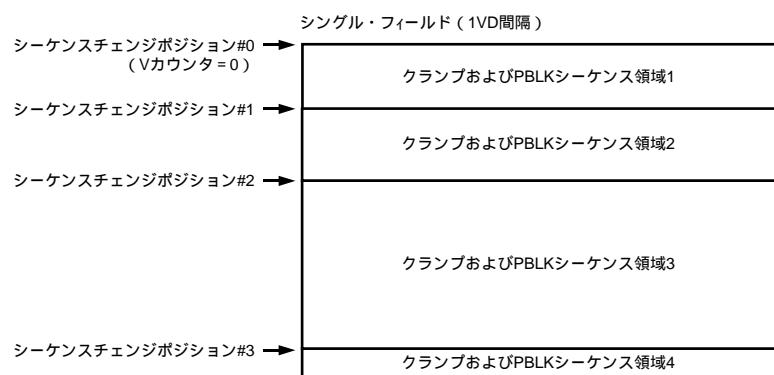

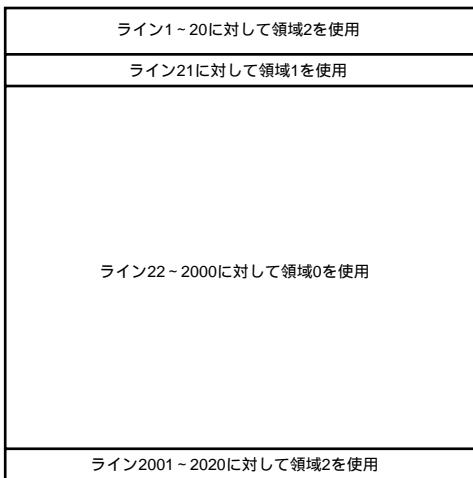

読み出し部分を4つの領域に分割するために、最大4つのSCPを使うことができます（図16）。SCP0は常にライン0の固定コードに設定され、SCP1～SCP3はレジスタを使って設定します。SCPにより分割された各領域では、SPTRレジスタが各信号により使用されるシーケンスを指定します。CLPOBとCLPDMは同じSCPを共用し、PBLKは個別のSCPセットを持ち、HBLKは垂直RCPを共用しているため、最大8個の領域が存在し、8個のHBLKS PTRレジスタを使って、HBLKシーケンスを変更できます。

に対して領域0を定義し、その領域内で4種類のCLPOBおよびCLPDMシーケンスから任意の1つをSPTRレジスタを使って選択することができます。次のSCPは新しい領域を定義し、その領域内で、各信号を個々のシーケンスに割り当てることができます。HBLKは垂直RCPを共用しているため、最大8個の領域が存在し、8個のHBLKS PTRレジスタを使って、HBLKシーケンスを変更できます。

表III CLPOB、CLPDM、PBLKの各シーケンスのパラメータ

| レジスタ | ビット幅 | 範囲                | 説明                             |

|------|------|-------------------|--------------------------------|

| SPOL | 1b   | ハイレベル / ローレベル     | シーケンス0～3に対する垂直転送パルスのスタート極性     |

| TOG1 | 12b  | 0～4095ピクセル・ロケーション | シーケンス0～3に対するライン内の最初のトグル・ポジション  |

| TOG2 | 12b  | 0～4095ピクセル・ロケーション | シーケンス0～3に対するライン内の2番目のトグル・ポジション |

表IV HBLKの各シーケンス・パラメータ

| レジスタ     | ビット幅 | 範囲                | 説明                                            |

|----------|------|-------------------|-----------------------------------------------|

| HBLKMASK | 1b   | ハイレベル / ローレベル     | シーケンス0～3に対するH1のマスク極性<br>(0=H1ローレベル、1=H1ハイレベル) |

| HBLKTOG1 | 12b  | 0～4095ピクセル・ロケーション | シーケンス0～3に対するライン内の最初のトグル・ポジション                 |

| HBLKTOG2 | 12b  | 0～4095ピクセル・ロケーション | シーケンス0～3に対するライン内の2番目のトグル・ポジション                |

表V CLPOB、CLPDM、PBLKの水平シーケンス制御パラメータ

| レジスタ        | ビット幅 | 範囲          | 説明                         |

|-------------|------|-------------|----------------------------|

| SCP1～SCP3   | 12b  | 0～4095ライン番号 | 水平領域0～3を定義するCLPOB/PBLK SCP |

| SPTR0～SPTR3 | 2b   | 0～3シーケンス番号  | 水平領域0～3のシーケンス・ポインタ         |

表VI HBLKの水平シーケンス制御パラメータ

| レジスタ                  | ビット幅 | 範囲          | 説明                      |

|-----------------------|------|-------------|-------------------------|

| VTPRCP1～VTPRCP7       | 12b  | 0～4095ライン番号 | 垂直領域変更ポジション（表IX参照）      |

| HBLKS PTR0～HBLKS PTR7 | 2b   | 0～3シーケンス番号  | HBLK領域0～7に対するシーケンス・ポインタ |

注

シーケンスチェンジポジションを使って、最大4種類の水平クランプおよびブランкиング領域を1つのフィールド内で設定することができます。

図16 クランプおよびブランкиング・シーケンスの柔軟性

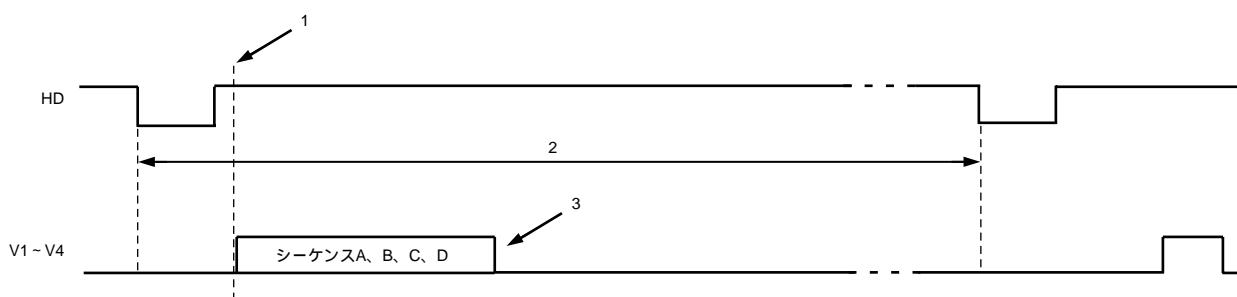

## 垂直タイミングの生成

AD9891/AD9895は垂直CCDタイミングの生成に対して非常に柔軟なソリューションを提供し、複数のCCDとさまざまなシステム・アーキテクチャに対応できます。4相の垂直転送クロックV1~V4は、ピクセルの各ラインをCCDの水平出力レジスタにシフト入力するときに使います。AD9891/AD9895では、これらの出力を個々に設定してさまざまなパルス・パターンを発生することができます。垂直シーケンス・コントロール・レジスタは、個々の垂直パルスを希望のCCD垂直タイミング配置に構成します。

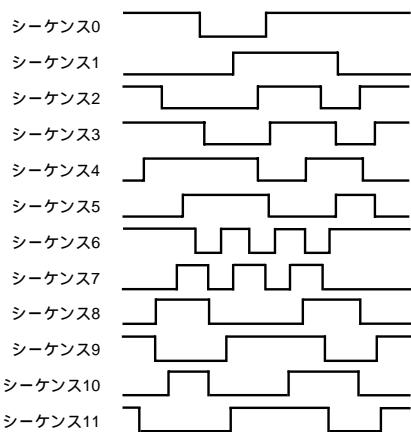

図17に、3つの基本ステップで垂直タイミングを発生する方

法の概要を示します。先ず、個々のパルス・パターンまたはシーケンスを垂直転送パルス（VTP）レジスタを使って生成します。これらのシーケンスは、V1~V4出力の内の1つに割り当てるができるパルス・パターンの“プール”です。次に、シーケンスを各V1~V4出力に割り当てて、個々の領域をつくります。最大5個の領域を指定することができます。最後に、個々の領域の1個または複数個をシーケンシャルに組み合わせて、フィールド全体の読み出しを構成します。最大8個の領域を使用して、高速ライン・シフトや垂直イメージ転送などのさまざまなステップの読み出しに対応できます。

① 個々の垂直シーケンスの構成

(最大12シーケンス)

② 各シーケンスをV1~V4出力に割り当てて個々の垂直領域を作成

(最大5領域)

③ 複数の領域を組み合わせてフィールド全体の読み出しを構成

(最大8種類の組み合わせ)

注

\*シーケンスのシフトおよび／または反転が可能です。

図17 垂直タイミング発生の概要

# AD9891/AD9895

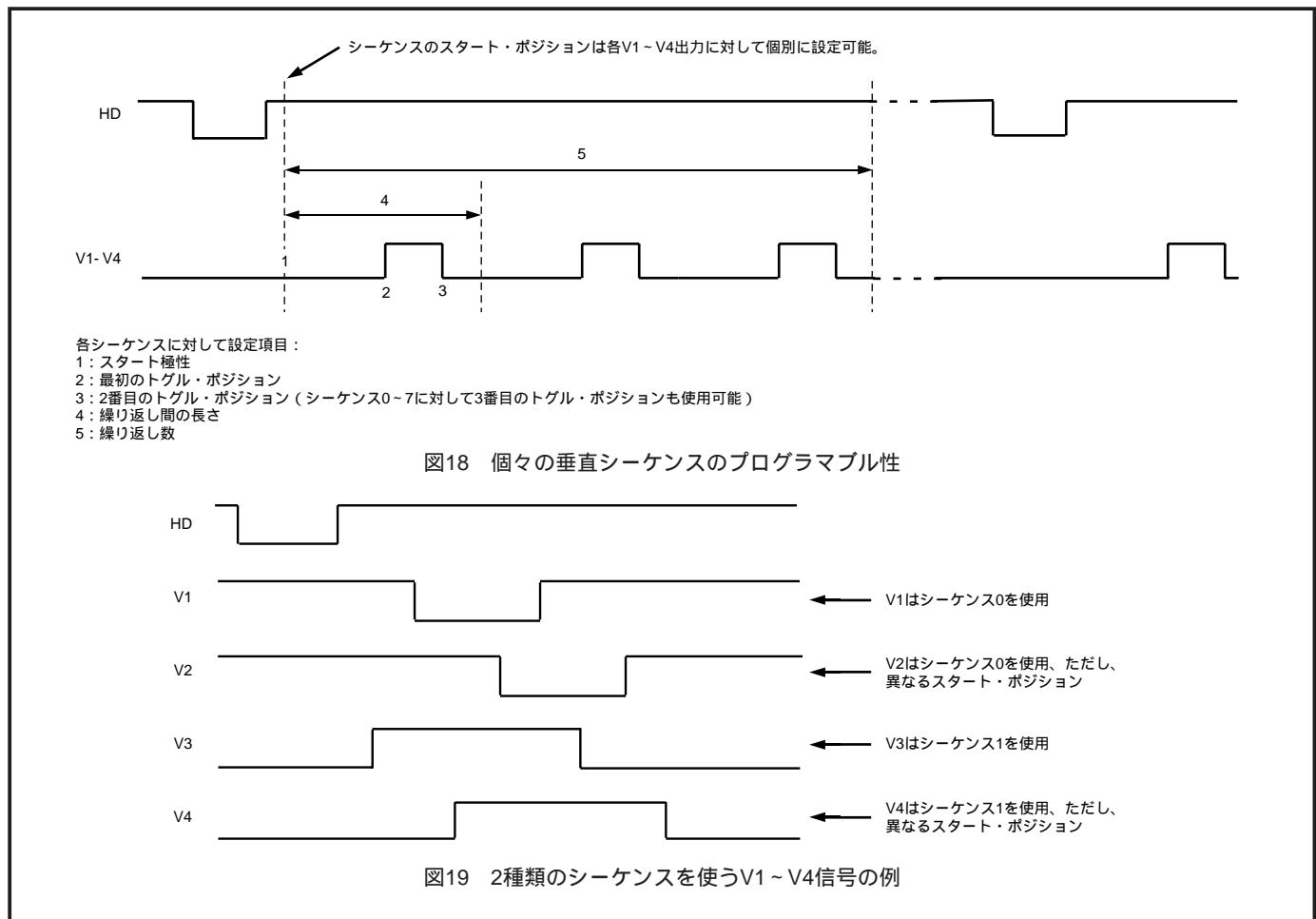

## 個々の垂直シーケンス

図18に示す個々の垂直シーケンスまたはパターンを発生するためには、各シーケンスに対して5個のレジスタが必要です。表VIIに、これらのレジスタとそれぞれのビット幅をまとめます。スタート極性 (VTPPOL) は、垂直シーケンスのスタート極性を指定し、ハイレベルまたはローレベルに設定することができます。最初のトグル・ポジション (VTPTOG1) と2番目のトグル・ポジション (VTPTOG2) はライン内のピクセル位置で、ここでパルスの極性が変化します。3番目のトグル・ポジション (VTPTOG3) もシーケンス0~7に対して使用できます。すべてのトグル・ポジションは10ビット値、この値がパルス位置を1ライン内の1024ピクセルに制限します。別のレジスタVSTARTが、そのライン内のシーケンスのスタート・ポジションを指定します（個々の垂直領域参照）。長さ (VTPLEN) レジスタは、繰り返しを設定している場合に、各パルス繰り返し間のピクセル数を指定します。繰り返し数 (VTPREP) は、単に1つのライン内でのパルス繰り返し数を指定します。VTPREP

に“1”を書き込むとシングル・パルスが、“0”を書き込むとスタート極性値に基づいて固定のDCが、それぞれ出力されます。合計12種類のシーケンスを設定することができます。

各領域を指定するとき、各シーケンスをV1~V4出力の任意の1つに割り当てることができます。例えば、図19に、代表的な4相Vクロックの配置を示します。異なるパルス幅を発生するときは、2種類のシーケンスが必要です。V1~V4に対して個々のスタート・ポジションを使用すると、2つのシーケンスから4つの出力を発生することができます。図20に、少し異なるVクロック配置を示します。ここでは、V2、V3、V4が単純にシフトされ、またはV1の反転になっています。すべての信号が同じパルス幅を持つため、1個のシーケンスしか必要としません。シーケンス反転レジスタ (VINV) はV3とV4に対して使います（表VII）。

柔軟性を大きくするため、VTPPOLレジスタ（スタート極性）を追加トグル・ポジションとして使うこともできることに注意してください。

表VII 個々のVTPシーケンスのパラメータ

| レジスタ    | ビット幅 | 範囲            | 説明                              |

|---------|------|---------------|---------------------------------|

| VTPPOL  | 1b   | ハイレベル / ローレベル | シーケンス0~11に対する垂直転送パルスのスタート極性     |

| VTPTOG1 | 10b  | 0~1023ピクセル位置  | シーケンス0~11に対するライン内の最初のトグル・ポジション  |

| VTPTOG2 | 10b  | 0~1023ピクセル位置  | シーケンス0~11に対するライン内の2番目のトグル・ポジション |

| VTPTOG3 | 10b  | 0~1023ピクセル位置  | シーケンス0~7に対するライン内の3番目のトグル・ポジション  |

| VTPLEN  | 10b  | 0~1023ピクセル    | シーケンス0~11に対するパルス繰り返し間の長さ        |

| VTPREP  | 12b  | 0~4095パルス     | シーケンス0~11に対するパルス繰り返し数 (0=DC出力)  |

### 個々の垂直領域

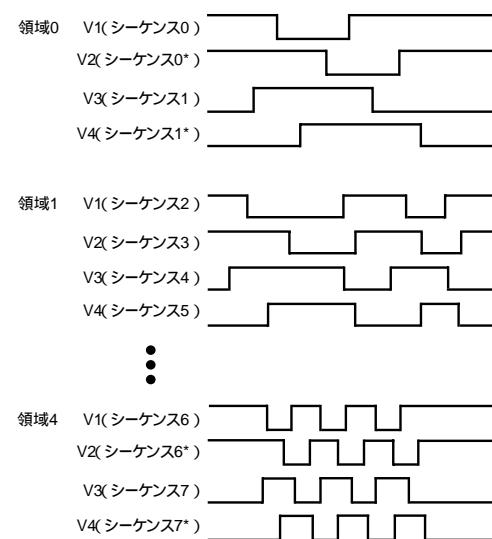

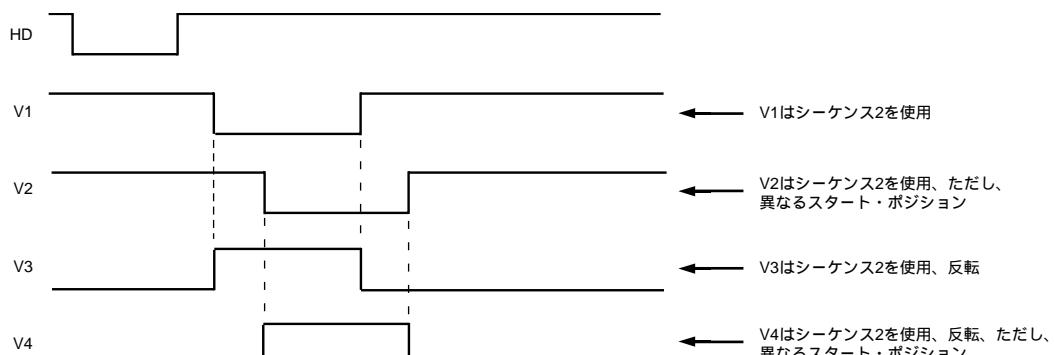

AD9891/AD9895は、個々のシーケンスをシーケンス・ポインタ（S PTR）を使って各領域に配置します。各領域内で、異なるシーケンスを各Vクロック出力に割り当てることができます。図21に各領域のプログラマブル性を、表VIIIに各領域の生成に必要なレジスタを、それぞれ表します。

各領域に対して、HDLENレジスタを使ってライン長（ピクセル数）を設定することができます。各領域は異なるライン長を持つことができ、あらゆる画像読み出し方法に対応します。1ライン当たりの最大ピクセル数は4096です。また、VSTARTレジスタを使って、独自に各領域に対する各V出力に対するシーケンス・スタート・ポジションを設定します。各VSTARTは12ビット値であるため、スタート・ポジションはライン内の任意の位置に配置できます。各領域に対して、5個のHDLENレジスタが存在します。

異なる5領域の各V1～V4出力に対して1個ずつ合計20個のVSTARTが存在します。

フィールドの最後のラインはHDLASTLENレジスタを使って

個別に設定できることに注意してください。

シーケンス・ポインタ・レジスタVxSPTRFIRSTとVxSPTRSECONDは、指定された領域内で、個々の垂直シーケンスを各Vクロック出力（V1～V4）に割り当てます。一般に、SPTRSECONDレジスタはライン毎のオルタネーション発生のためにとっておき、SPTRFIRSTレジスタだけが使用されます（垂直シーケンスの変更参照）。VxINVFIRSTレジスタとVxINVSECONDレジスタを使って、12個のシーケンスの任意の1つを反転することもできます。これにより使用可能なシーケンス数が2倍になります。各V出力に対して1個のSPTRFIRSTレジスタが存在し、1領域当たり合計4個のレジスタになります。5個の領域すべてを使う場合は、合計20個のSPTRFIRSTレジスタになります。また、オルタネーションを行う場合には、同数のSPTRSECONDレジスタが存在します。11より大きな値を書き込むと、SPTRレジスタは4ビット幅になり、Vx出力はVxINVレジスタで指定されるレベルのDCになることに注意してください。

図20 反転を持つ1個のシーケンスを使ったV1～V4信号反転の例

各領域に対してのレジスタ設定：

- 1: 選択したシーケンスのスタート・ポジションは各出力に対して個別に設定可能。

- 2: HDライン長

- 3: 各出力に対して個別シーケンスを選択するためのシーケンス・ポインタ（S PTR）

- 4: 柔軟性を強化するため任意のシーケンスをオルタネーションすることも可能。

図21 個々の垂直領域のプログラマブル性

# AD9891/AD9895

表VIII 各垂直領域のパラメータ

| レジスタ         | ビット幅 | 範囲                  | 説明                                                                       |

|--------------|------|---------------------|--------------------------------------------------------------------------|

| HDLEN        | 12b  | 0 ~ 4095ピクセル        | 各領域0 ~ 4内のラインに対するHDライン長                                                  |

| VxSTART      | 12b  | 0 ~ 4095ピクセル・ロケーション | 各領域0 ~ 4内の各Vx出力に対するシーケンス・スタート・ポジション                                      |

| VxS PTRFIRST | 4b   | シーケンス0 ~ 11         | 各領域0 ~ 4内のVx出力に対するシーケンス・ポインタ（オルタネーションに対してはS PTRSECONDと組み合わせて使用可能、テキスト参照） |

| VxINVFIRST   | 1b   | ハイレベル / ローレベル       | ハイレベルのとき、シーケンスVxS PTRFIRSTの極性は反転。                                        |

注

xは1 ~ 4からのV出力。

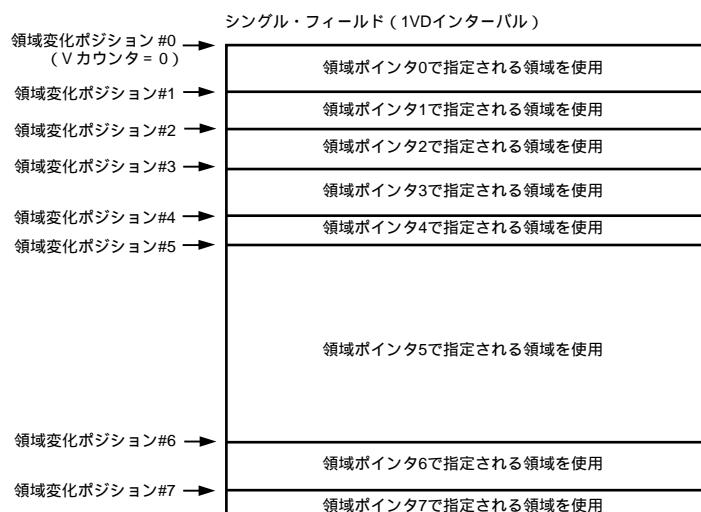

フィールドの完成：領域の結合

領域チェンジポジション (RCP) と領域ポインタ (REGPTR) を使って、個々の領域を結合して、フィールド全体の読み出しを完成させます。図22に、各フィールドを複数の領域に分割する方法を示します。この機能を使うと、イメージ読み出しのさまざまなステージで垂直タイミングを変化させることができます。各領域の境界は、シーケンス変更ポジション (RCP) により指定されます。各RCPは12ビット値で、領域の境界を定めるライン数番号を表します。合計7個の

RCPにより、フィールド内に最大8個の領域を定めることができます。最初のRCPは常にゼロに固定されており、残りの7個がレジスタで設定可能です。定義できる個別領域は5個までですが、8個の領域を使用することにより、フィールド内の複数の場所に同じ領域を使うことが可能になることに注意してください。各領域内では、領域ポインタが5個の領域の中から使用する領域を指定します。各領域に対して1つずつ、8個の領域ポインタがあります。表IXに、領域変化ポジションと領域ポインタのレジスタをまとめます。

注

領域変化ポジションと領域ポインタを使って、1フィールド内に最大8個のVクロック領域を定義できます。

図22 1つのフィールド内で複数の領域を使用

表IX 垂直フィールド・レジスタ

| レジスタ      | ビット幅 | 範囲                 | 説明                        |

|-----------|------|--------------------|---------------------------|

| VTPRCP    | 12b  | 0 ~ 4095ライン・ロケーション | フィールド内の各領域に対する領域チェンジポジション |

| VTPREGPTR | 3b   | 領域0 ~ 4            | フィールドの各領域に対する領域ポインタ       |

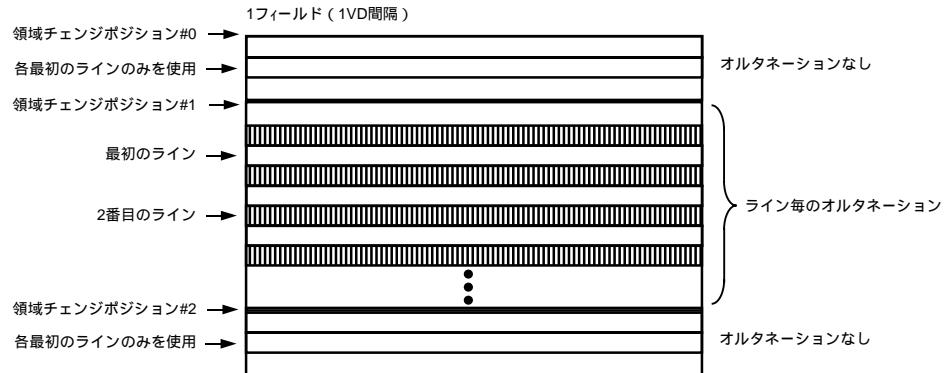

### 垂直シーケンス・オルタネーション

AD9891/AD9895は、任意の領域内で垂直シーケンスのライン毎のオルタネーションに対応しています（図23）。表Xに、さまざまなオルタネーション・パターンに対応するために使うその他のレジスタをまとめます。オルタネーションの垂直パターンを作るときは、VxSPTRFIRSTレジスタと

VxSPTRSECONDレジスタに、オルタネートするシーケンスを書き込みます。VTPALTレジスタは、オルタネーションを使う領域に対してハイレベルを設定します。VTPALTがローレベルの場合、VxSPTRSECONDレジスタは無視されます。図24に、ライン毎のオルタネーションの例を示します。

注

VTPALTレジスタがローレベル（オルタネーションなし）のとき、各最初のラインのみ使用されます。

図23 垂直シーケンスでのライン・オルタネーションの使用

注

SPTRFIRSTレジスタとSPTRSECONDレジスタを使って、領域内でシーケンスのオルタネーションが可能。

図24 領域内でのライン・オルタネーションの例

表X 垂直シーケンス・オルタネーションのパラメータ

| レジスタ         | ビット幅 | 範囲              | 説明                              |

|--------------|------|-----------------|---------------------------------|

| VTPALT       | 1b   | イネーブル / ディスエーブル | ライン毎のオルタネーションをイネーブル (1 = イネーブル) |

| VxSPTRFIRST  | 4b   | シーケンス0~11       | 最初のラインの各領域0~4でのVx出力に対するSPTR     |

| VxINVFIRST   | 1b   | ハイレベル / ローレベル   | ハイレベルのとき、VxSPTRFIRSTの極性を反転      |

| VxSPTRSECOND | 4b   | シーケンス0~11       | 2番目のラインの各領域0~4でのVx出力に対するSPTR    |

| VxINVSECOND  | 1b   | ハイレベル / ローレベル   | ハイレベルのとき、VxSPTRSECONDの極性を反転     |

注

xは1~4からのV出力。

# AD9891/AD9895

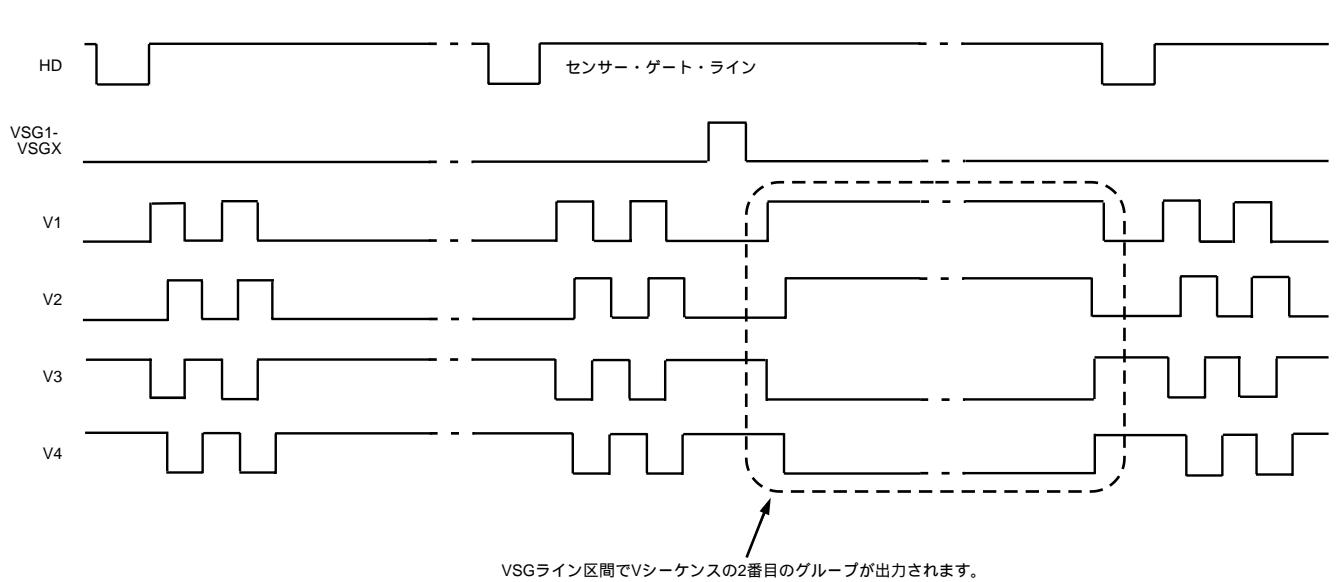

## VSGラインでの2番目の垂直シーケンス

多くのCCDは、センサー・ゲート・ラインで垂直タイミングの追加を必要とします。AD9891は、センサー・ゲートVSG1～VSG4がアクティブのとき、ライン上のV1～V4に対するシーケンスの2番目のセットを出力するオプションに対応しています。図25に、V1～V4に対する垂直シーケンスの2組のセットを含む代表的なVSGラインを示します。ラインのスタートでのシーケンスは、前のラインの場合と同じです。しかし、2番目のシーケンスはVSG信号がアクティブであるラインでのみ発生します。2番目のシーケンスで使用するシーケンスを選択するときは、表XIのレジスタを使います。VSGラインでシーケンスの2番目をイネーブルにするときは、VTP\_SGLINEMODEをハイレベルに設定します。通常の垂直領域の場合と同様に、各V1～V4出力は個々のスタート・ポジションを持ち、VxSTART\_SGLINEレジスタに書き込みます。各V1～V4出力は、個別シーケンス・ポインタ・レジスタVxSPTR\_SGLINEを使って、12種類のシーケンスのプールから選択できます。また、VxINV\_SGLINEレジスタを使って、特定のV1～V4出力に対して任意のシーケンスを反転することもできます。

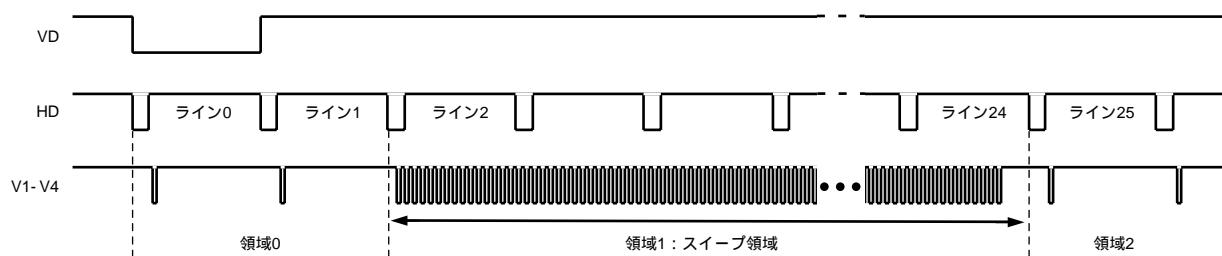

## 垂直スイープ・モード動作

AD9891/AD9895は、スイープ・モードと呼ばれる垂直タイミング動作の特別なモードを持っています。このモードは、複数のHDラインに跨る多数の繰り返しパルスを発生するときに使います。このモードが必要となる1つの例は、CCD読み出し動作の開始のときです。露光が終った後で、セン

サー・ゲート・パルスにより画像データが転送される前に、垂直インターラインCCDレジスタは全電荷を“掃き出す”必要があります。この動作は、V1～V4出力上の長い一連のパルスを使って電荷を高速にシフト出力することにより行われます。CCDの垂直分解能に応じて、各垂直CCDラインから電荷をシフト出力するためには、最大2千個または3千個のクロック・サイクルが必要です。この動作は、複数のHDライン長に跨ります。通常、AD9891/AD9895シーケンスは1 HDライン長内に収まりますが、スイープ・モードがイネーブルにされると、その領域が終わるまでHD境界は無視されます。任意の領域内でスイープ・モードをイネーブルにするときは、該当するSWEEP(0～4)レジスタにハイレベルを書き込みます。

図26に、スイープ・モード動作の例を示します。必要となる垂直パルス数はCCDの垂直分解能に依存します。V1～V4出力信号は、個別垂直シーケンス・レジスタ(表VII)を使って発生します。最初、2番目、3番目のトグル・ポジションを使って1個のパルスを発生し、繰り返し数をCCDが必要とする垂直シフト数に設定します。VTPREPレジスタを使うこのモードでの最大繰り返し数は4096です。これにより、該当する長さのパルス列が発生されます。通常、パルス列はHDライン長の終わりで切り詰められますが、この領域に対してスイープ・モードがイネーブルにされていると、HD境界が無視されます。図26では、スイープ領域は23本のHDラインを占めています。スイープ・モード領域が終わった後、次の領域で、通常のシーケンス動作が再開されます。

表XI SGライン上の2番目の垂直シーケンス・レジスタ

| レジスタ           | ビット幅 | 範囲                | 説明                                    |

|----------------|------|-------------------|---------------------------------------|

| VTP_SGLINEMODE | 1b   | ハイレベル / ローレベル     | SGライン上で2番目のシーケンスをターンオンするときは、ハイレベルを設定  |

| VxSTART_SGLINE | 12b  | 0～4095ピクセル・ロケーション | SGライン・シーケンスの各Vx出力に対するシーケンス・スタート・ポジション |

| VxSPTR_SGLINE  | 4b   | 0～11シーケンス#        | 2番目のSGライン・シーケンスのVx出力に対するシーケンス・ポインタ    |

| VxINV_SGLINE   | 1b   | ハイレベル / ローレベル     | ハイレベルのとき、シーケンスVxSPTRFIRSTの極性は反転。      |

注

xは1～4からのV出力。

図25 センサー・ゲート・ライン区間での2番目のシーケンスの例

図26 高速垂直シフトに対するスイープ領域の例

# AD9891/AD9895

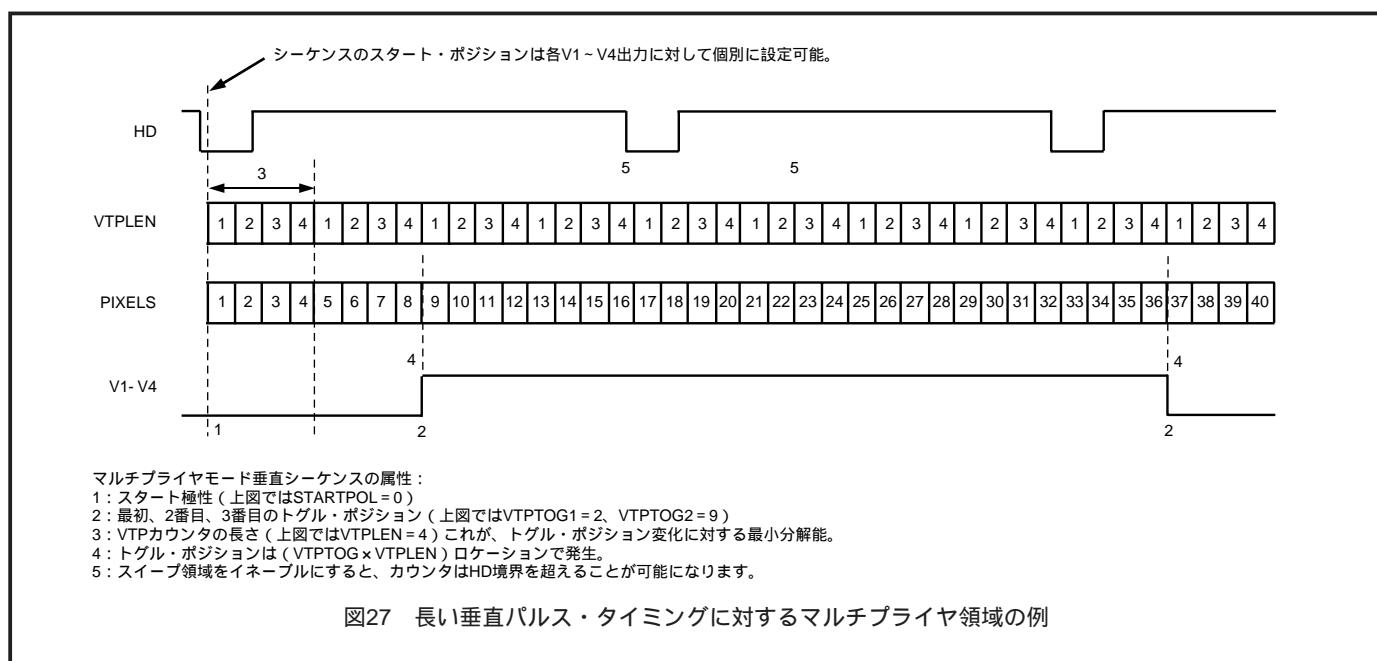

## 垂直マルチプライヤモード

非常に広い幅の垂直タイミング・パルスを発生するときは、垂直領域をマルチプライヤモードに設定することができます。このモードは、垂直シーケンス・レジスタを少し異なる方法で使います。マルチプライヤモードは1 HDライン長より広い垂直パルス幅などの、通常とは異なるCCDタイミング条件に対応するときに使用できます。

スタート極性とトグル・ポジションは通常のシーケンス発生の場合と同じ使い方をしますが、長さの使い方は異なります。ピクセル・カウンタ(HDカウンタ)を使ってシーケンスのトグル・ポジション・ロケーション(VTPTOG1, 2, 3)を指定する代わりに、VTP長(VTPLEN)とVTP-TOGポジションのマルチプライヤを行って、非常に長いシーケンスを発生します。正確なトグル・ポジションを計算するために、スタート・ポジション後のピクセル数を次のように計算します。

$$\text{マルチプライヤ・トグル・ポジション} = \text{VTPTOG} \times \text{VTPLEN}$$

VTPTOGレジスタとVTPLENが乗算されるため、トグル・ポジション配置の分解能は低下します。VTPLEN=4の場合、トグル・ポジション精度はシングル・ピクセル・ステップから4ピクセル・ステップに減ります。表XIIに、個別垂直シーケンス・レジスタをマルチプライヤモード動作に設定する方法をまとめます。VTPTOGレジスタとVTPREPレジスタのビット範囲は、表VIIに示す通常動作と異なることに注意してください。マルチプライヤモードでは、VTPREPレジスタに、常に最大のトグル・ポジション・レジスタと同じ値を書き込むことが必要で

す。

図27に、この動作の例を示します。最初のトグル・ポジションは2で、2番目のトグル・ポジションは9です。マルチプライヤではないモードでは、この設定により、1つのHDライン内でVシーケンスがピクセル2とピクセル9でそれぞれトグルします。しかし、ここではトグル・ポジションとVTPLEN=4が乗算されるため、最初のトグルはピクセル・カウント=8で発生し、2番目のトグルはピクセル・カウント=36で発生します。トグル・ポジションがHDラインの境界を超えることを可能にするため、スイープ・モードをイネーブルにしておく必要があります。

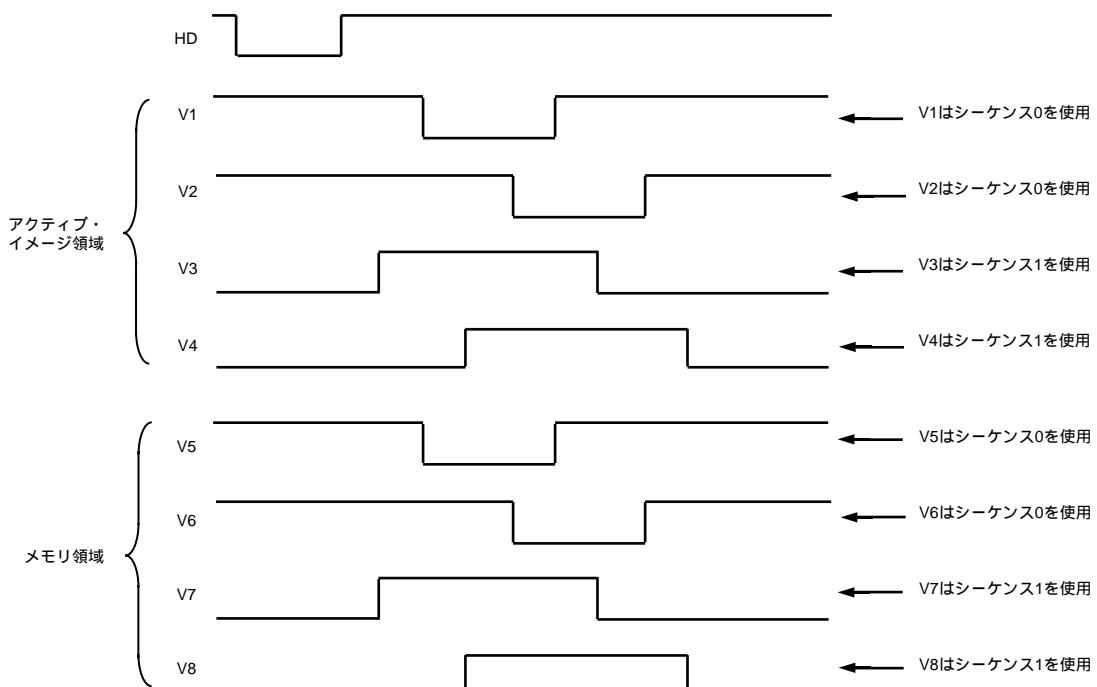

## フレーム転送CCDモード

またAD9891/AD9895をフレーム転送CCDで使用するように設定することも可能です。

フレーム転送CCD(FTCCD)モードでは、更に4個の垂直出力を使用でき、合計8個の出力(V1~V8)が使用可能です。このケースでは、V1~V4はアクティブ・イメージ領域のクロックに、V5~V8はメモリ領域のクロックに、それぞれを使います。FTCCDモードでは、V1~V4出力に割り当てられたシーケンスをV5~V8出力にも使用して、メモリ領域とイメージ領域を一緒にクロック駆動できるようにします。V1~V4出力とV5~V8出力の個別マスキング機能により、イメージ領域からメモリ領域への転送時に垂直間引き技術の使用が可能になります。4本のセンサー・ゲート出力ビューバスVSG1~VSG4に対して、追加出力V5~V8を使用することができます。図28に、フレーム転送CCDでの使用用に設定された8個のVクロックの例を示します。

表XII マルチプライヤモードとシーケンス・レジスタのパラメータ

| レジスタ    | ビット幅 | 範囲                | 説明                                       |

|---------|------|-------------------|------------------------------------------|

| MULTI   | 1b   | ハイレベル / ローレベル     | 各領域0~4に対してマルチプライヤモードをイネーブルにするときはハイレベルを設定 |

| VTPPOL  | 1b   | ハイレベル / ローレベル     | シーケンス0~11に対する垂直転送パルスのスタート極性              |

| VTPTOG1 | 12b  | 0~4095ピクセル・ロケーション | 各シーケンス0~11に対する最初のトグル・ポジション               |

| VTPTOG2 | 12b  | 0~4095ピクセル・ロケーション | 各シーケンス0~11に対する2番目のトグル・ポジション              |

| VTPTOG3 | 12b  | 0~4095ピクセル・ロケーション | 各シーケンス0~7に対する3番目のトグル・ポジション               |

| VTPLEN  | 10b  | 0~1023ピクセル        | 繰り返しカウンタに対する“マルチプライヤ”係数                  |

| VTPREP  | 12b  | 0~4096            | 最大のトグル・ポジションと同じ値の書き込みが必要                 |

図28 V1 ~ V8を使用したフレーム転送CCDモードの例

また、プレビュー・モード用の画像取り込みのために間引きを行うとき、フレーム転送CCDは更なるタイミング制御を必要とします。AD9891/AD9895は、V1～V4出力を継続させたままV5～V8出力動作を独立して停止させる、またはV5～V8出力を動作させたまま、V1～V4出力を停止させるためのレジスタを内蔵しています。FREEZEレジスタとRESUMEレジスタは、V1～V4クロック出力またはV5～V8クロック出力が状態維持を開始し、さらに通常動作を再開する領域内の各ライン上のピクセル・ロケーションを指定します。FREEZEとRESUMEは、フレーム読み出し時に任意の領域内で使用することができます。

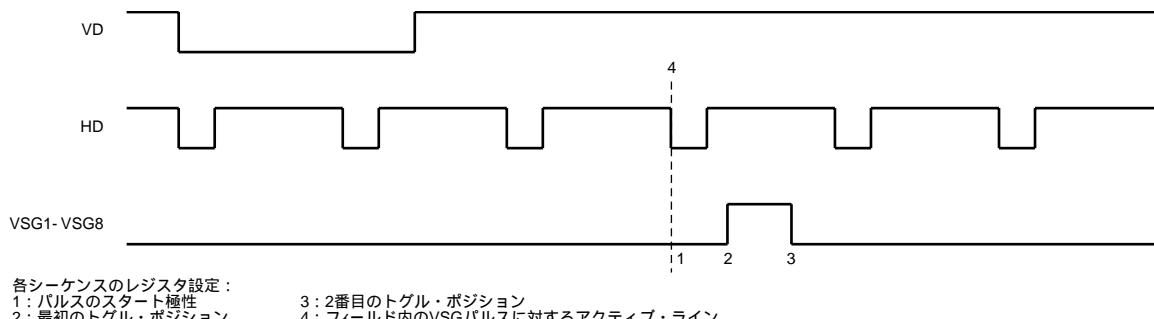

垂直センサー・ゲート（シフト・ゲート）のタイミング

インターラインCCDで、垂直センサー・ゲート（VSG）を使って受光領域から光からシールドされた垂直レジスタへピクセル電荷を転送します。メカシャッターを使用しない場合、この転送が画像取り込み時の露光期間を効果的に設定できます。垂直転送パルスV1～V4と高速水平クロックを使って、次に光からシールドされた垂直レジスタから電荷がライン毎に読み出されます。

図29 垂直センサー・ゲート・パルスの配置

表XIII センサー・ゲート・レジスタ・パラメータ

| レジスタ      | ビット幅 | 範囲                | 説明                                  |

|-----------|------|-------------------|-------------------------------------|

| SGPOL     | 1b   | ハイレベル/ローレベル       | シーケンス0～3に対するセンサー・ゲート・スタート極性         |

| SGTOG1    | 12b  | 0～4095ピクセル・ロケーション | シーケンス0～11に対する最初のトグル・ポジション           |

| SGTOG2    | 12b  | 0～4095ピクセル・ロケーション | シーケンス0～11に対する2番目のトグル・ポジション          |

| SGACTLINE | 12b  | 0～4095ピクセル・ロケーション | VSG1～VSG8がアクティブなフィールド内のライン          |

| SGSEL     | 2b   | シーケンス0～3          | VSG1～VSG8に対してシーケンス0～3を選択            |

| SGMASK    | 8b   | 8個の個別ビット          | VSG1～VSG8の任意の信号に対するマスク (0=オン、1=マスク) |

# AD9891/AD9895

表XIIIに、VSGレジスタのまとめを示します。AD9891/AD9895は8個のSG出力VSG1～VSG8を持っています。各出力はSGSEL1～SGSEL8のレジスタを使って、4種類のプログラム・シーケンスの内の1つに割り当てることができます。各シーケンスは個別垂直シーケンスと同じ方法で発生され、プログラマブルなスタート極性( SGPOL )、最初のトグル・ポジション( SGTOG1 )、2番目のトグル・ポジション( SGTOG2 )を持ちます。VSG1～VSG8パルスが発生するアクティブ・ラインは、2個のSGACTLINEレジスタを使って設定することができます。さらに、SGMASKレジスタを使って任意のVSG1～VSG8パルスを個別にディスエーブルすることができます。マスクを使うと、すべての異なるSGシーケンスの設定が可能になり、奇数フィールドまたは偶数フィールドに対する該当するパルスをマスクすることができます。

## シャッター・タイミングの制御

CCDイメージ露光時間はサブストレート・クロック信号( SUBCK )を使って制御します。この信号は、CCDサブストレートにパルスを与えて蓄積電荷をクリアします。AD9891/AD9895は、通常シャッター・モード、高精度シャッター・モード、低速シャッター・モードの3タイプの電子シャッターに対応しています。SUBCKパルス配置と同様に、AD9891/AD9895はさまざまなプログラシブ読み出しモードとインターレース読み出しモードにも対応しています。さらに、AD9891/AD9895は、外部のメカシャッター、ストロボ( フラッシュ )スチルモード読み出し用のCCDバイアス( VSUB )を制御する出力信号も提供します。

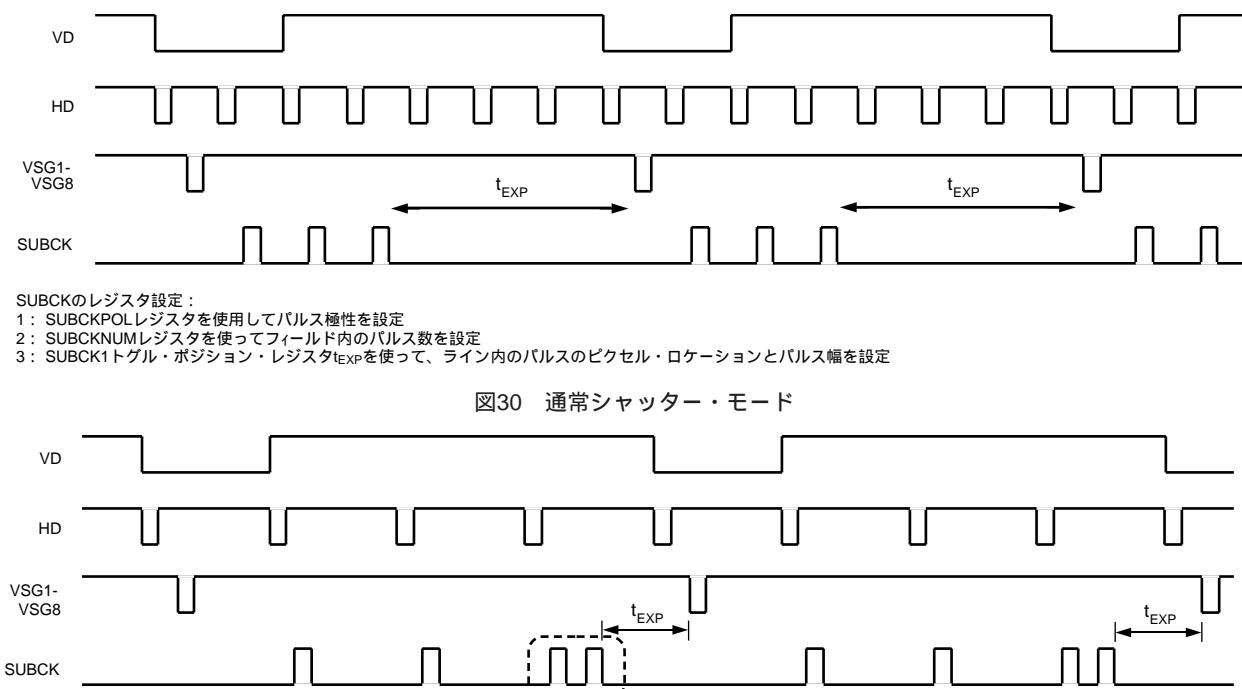

## ノーマルシャッター・モード

図30に、ノーマルシャッター・モードに対するVD出力とSUBCK出力を示します。SUBCKはライン毎に1パルスを発生し、フィールド内の合計繰り返し回数を設定できます。パルスの極性、幅、ライン・ロケーションは、SUBCKPOLレジスタ、SUBCK1TOG1レジスタ、SUBCK1TOG2レジスタを使って設定することができます( 表XIV )。フィールド当たりのSUBCKパルス数はSUBCKNUMレジスタに設定されます。図30に示すように、SUBCKパルスは常にSGACTLINEレ

ジスタ addr x265とx266 )により指定された、センサー・ゲートが発生した後のラインから開始されます。SUBCKPOLレジスタ、SUBCK1TOG1レジスタ、SUBCK2TOG1レジスタ、SUBCKNUMレジスタは、センサー・ゲート・ライン後の、ラインの開始で更新されます。その他のすべてのシャッター・モード・レジスタは、VD/HDの立ち下がリエッジで大部分のAD9891のレジスタと一緒に更新されます。

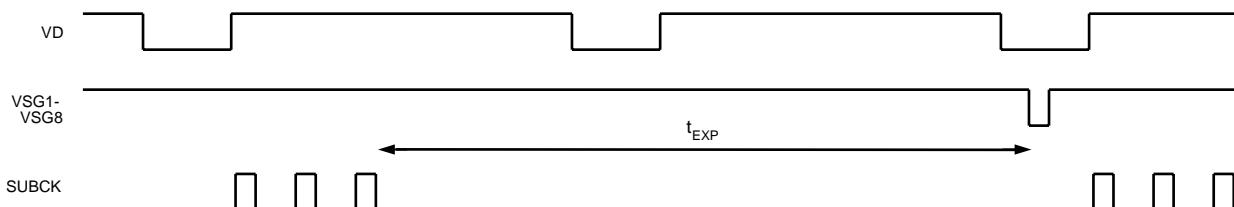

## 高精度シャッター・モード

高精度シャッターはノーマルシャッターと同じ方法で制御されますが、トグル・レジスタの2番目のセットが必要です。このモードでは、SUBCKはライン毎に1パルスを発生しますが、フィールド内の最後のSUBCKのラインに追加のSUBCKパルスを持ちます。これらのパルスのロケーションはSUBCK2TOG1レジスタとSUBCK2TOG2レジスタにより指定します( 図31 )。このモードを使うと、露光時間の分解能を高くすることができます。両SUBCK2TOGレジスタを4095( x3F )に設定すると、高精度モード( デフォルト設定 )がディスエーブルになります。

## 低速シャッター・モード

フィールド期間より短い通常の露光時間に対しては、EXPOSUREレジスタを0に設定します。1フィールド区間より長い露光時間は、EXPOSUREレジスタに0より大きい1値を書き込むことにより可能になります。図32に示すように、このシャッター・モードはSUBCK出力とVSG出力を最大4095フィールド間( VD周期 )停止させます。VD出力とHD出力は、VDHDOFFレジスタに1を書き込むことにより、露光期間中に停止させることができます。

## SUBCKの停止

通常、SUBCKはセンサー・ゲートライン( VSG )の後のライン上からクロック動作を行います。CCDによっては、VSGラインの後に1ラインまたは複数ライン間SUBCKを停止させる必要があるものがあります。SUBCKSUPPRESSレジスタを使うと、VSGラインの後で最大63ライン間SUBCKパルスを停止させることができます。

図30 通常シャッター・モード

図31 高精度シャッター・モード

## 露光後の読み出し

EXPOSUREレジスタに書き込みを行うことにより、露光時間 ( $t_{EXP}$ ) のフィールド数0~4095を指定します。露光後に、CCDデータの読み出しが行われます。読み出し時、読み出しが完了するまでに、さらにSUBCK出力を停止することが必要な場合もあります。READOUTレジスタは、SUBCKの停止を続ける、露光後の追加フィールド数を指定します。READOUTに0から7のフィールド数を書き込むことができます。これは、露光の書き込みと同時にを行うのではなく、スタートアップ時に予め書き込んでおく必要があります。代表的なインターレースCCDのフレーム読み出しモードでは、一般に、SUBCK停止に2フィールドの追加が必要です(読み出し=2)。EXPOSUREレジスタへの書き込は、露光完了後に読み出しへトリガーとして機能することに注意してください。EXPOSUREレジスタに書き込みを行わない場合は、READOUTレジスタには影響ありません。図35に、露光とそれに続く読み出しのトリガーの例を示します。

## VSUBの制御

CCD読み出しバイアス(VSUB)を設定して、さまざまなCCDに対応できます。図35に、使用可能な2つのモードを示します。モード0では、露光が開始されたとき、最後のSUBCKのフィールドでVSUBがアクティブになります。オ

ン・ポジション(図35の立ち上がりエッジ)は、フィールド内の任意のラインに設定できます。イメージ読み出しが終わるまで、VSUBはアクティブのままになります。モード1では、読み出しが開始されるまでVSUBはアクティブになりません。

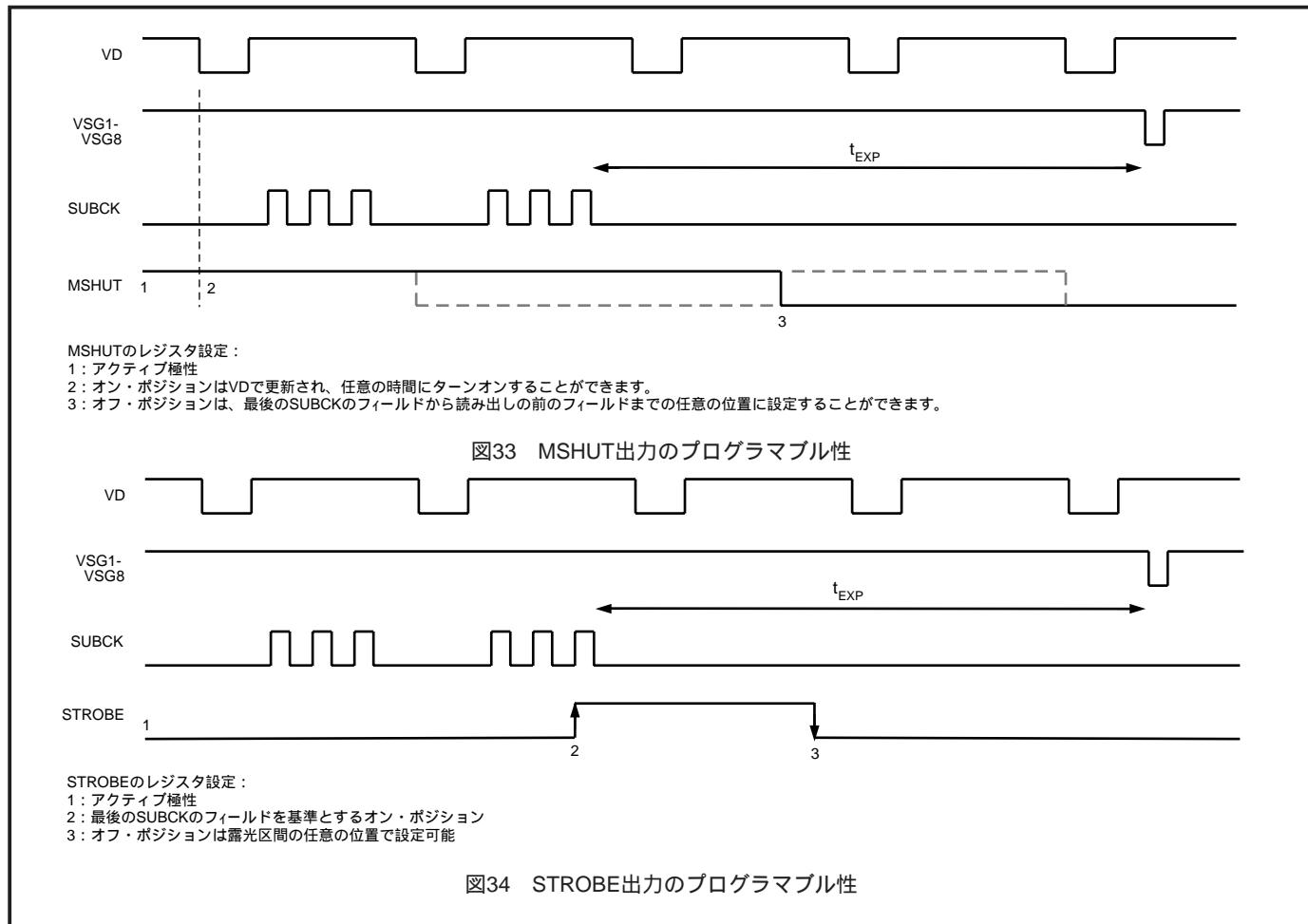

## MSHUTとSTROBEの制御

MSHUTとSTROBEの動作を図33、図34、図35に示します。表XVIには、MSHUT出力とSTROBE出力を制御するためのレジスタ・パラメータを示します。MSHUT出力はMSHUTONレジスタと一緒にオンになり、MSHUTOFFレジスタで指定されるロケーションになるまでオン状態を維持します。MSHUTOFFのロケーションは、FD(フィールド)レジスタ、LN(ライン)レジスタ、PX(ピクセル)レジスタを使って、露光期間内の任意の位置に設定できます。STROBEパルスは、オン/オフのポジションにより指定されます。STROBON\_FDはSTROBEがオンになるフィールドで、露光が開始される前の、最後のSUBCKを含むフィールドからカウントされます。STROBON\_LNレジスタとSTROBON\_PXレジスタは、STROBON\_FDを基準とするライン・ポジションとピクセル・ポジションを与えます。STROBEのオフ・ポジションは、最後のSUBCKのフィールドを基準として任意のフィールド、ライン、ピクセル・ロケーションに設定できます。

## 注

1. EXPOSUREレジスタにゼロより大きい値を設定して、SUBCKを複数フィールド間停止させることができます。

2. 上図ではEXPOSURE = 1を使用。

3. VDHDOFFレジスタ = 1を使って、VD/HD出力も停止できます。

図32 EXPOSUREレジスタを使う低速シャッター・モード

表XIV 電子シャッター・モード・レジスタのパラメータ

| レジスタ           | ビット幅 | 範囲                | 説明                                           |

|----------------|------|-------------------|----------------------------------------------|

| SUBCKPOL*      | 1b   | ハイレベル / ローレベル     | SUBCK1とSUBCK2に対するSUBCKのスタート極性                |

| SUBCK1TOG1*    | 12b  | 0~4095ピクセル・ロケーション | SUBCKの最初のトグル・ポジション                           |

| SUBCK1TOG2*    | 12b  | 0~4095ピクセル・ロケーション | SUBCKの2番目のトグル・ポジション                          |

| SUBCK2TOG1*    | 12b  | 0~4095ピクセル・ロケーション | 2番目のSUBCKの最初のトグル・ポジション(高精度モード)               |

| SUBCK2TOG2*    | 12b  | 0~4095ピクセル・ロケーション | 2番目のSUBCKの2番目のトグル・ポジション(高精度モード)              |

| SUBCKNUM*      | 12b  | 0~4095のパルス数       | フィールド当たりの合計SUBCK数(ライン毎に1パルス)                 |

| SUBCKSUPPRESS* | 6b   | 0~63のパルス数         | VSGラインの後に停止されるSUBCK数                         |

| 露光             | 12b  | 0~4095のフィールド数     | SUBCKとVSGを停止させるフィールド数; $t_{EXP}$ 後に読み出しをトリガー |

| VDHDOFF        | 1b   | オン / オフ           | 露光時のVD/HD出力をディスエーブル(1=オン、0=オフ)               |

| 読み出し           | 3b   | 0~7のフィールド数        | 露光後にSUBCKを停止させるフィールド数(読み出し)                  |

\*レジスタはVD/HDで更新されず、センサー・ゲート・ラインの後のラインの開始で更新されます。

# AD9891/AD9895

表XV VSUBレジスタ、MSHUTレジスタ、STROBEレジスタのパラメータ

| レジスタ          | ビット幅 | 範囲                   | 説明                                           |

|---------------|------|----------------------|----------------------------------------------|

| TRIGGER       | 3b   | 3信号に対するオン / オフ       | VSUB[0]、MSHUT[1]、STROBE[2]に対する1ビット・トリガー      |

| VSUBMODE      | 1b   | ハイレベル / ローレベル        | VSUBモード (0 = モード0、1 = モード1) (図27参照)          |

| VSUBKEEPON    | 1b   | ハイレベル / ローレベル        | ハイレベルのとき、読み出し後にアクティブを維持するVSUBを設定             |

| VSUBPOL       | 1b   | ハイレベル / ローレベル        | VSUBのアクティブ極性                                 |

| VSUBON        | 12b  | 0 ~ 4095ライン・ロケーション   | VSUBのオン・ポジション。フィールドの任意のラインでアクティブを開始          |

| MSHUTON       | 1b   | オン / オフ              | MSHUT信号をイネーブル (1 = アクティブすなわち“オープン”)          |

| MSHUTONPOS_LN | 12b  | 0 ~ 4095ライン・ロケーション   | MSHUTのライン・ロケーション                             |

| MSHUTONPOS_LN | 12b  | 0 ~ 4095ピクセル・ロケーション  | MSHUTのオン・ピクセル・ロケーション                         |

| MSHUTPOL      | 1b   | ハイレベル / ローレベル        | MSHUTのアクティブ極性                                |

| MSHUTOFF_FD   | 12b  | 0 ~ 4095フィールド・ロケーション | MSHUTをターンオフするフィールド・ロケーション (非アクティブすなわち“クローズ”) |

| MSHUTOFF_LN   | 12b  | 0 ~ 4095ライン・ロケーション   | MSHUTをターンオフするライン・ロケーション (非アクティブすなわち“クローズ”)   |

| MSHUTOFF_PX   | 12b  | 0 ~ 4095ピクセル・ロケーション  | MSHUTをターンオフするピクセル・ロケーション (非アクティブすなわち“クローズ”)  |

| STROBEPOL     | 1b   | ハイレベル / ローレベル        | STROBEのアクティブ極性                               |

| STROBON_FD    | 12b  | 0 ~ 4095フィールド・ロケーション | 最後のSUBCKフィールドを基準とするSTROBEのオン・フィールド・ロケーション    |

| STROBON_LN    | 12b  | 0 ~ 4095ライン・ロケーション   | STROBEのオン・ライン・ロケーション                         |

| STROBON_PX    | 12b  | 0 ~ 4095ピクセル・ロケーション  | STROBEのオン・ピクセル・ロケーション                        |

| STROBOFF_FD   | 12b  | 0 ~ 4095フィールド・ロケーション | 最後のSUBCKフィールドを基準とするSTROBEのオフ・フィールド・ロケーション    |

| STROBOFF_LN   | 12b  | 0 ~ 4095ライン・ロケーション   | STROBEのオフ・ロケーション                             |

| STROBOFF_PX   | 12b  | 0 ~ 4095ピクセル・ロケーション  | STROBEのオフ・ロケーション                             |

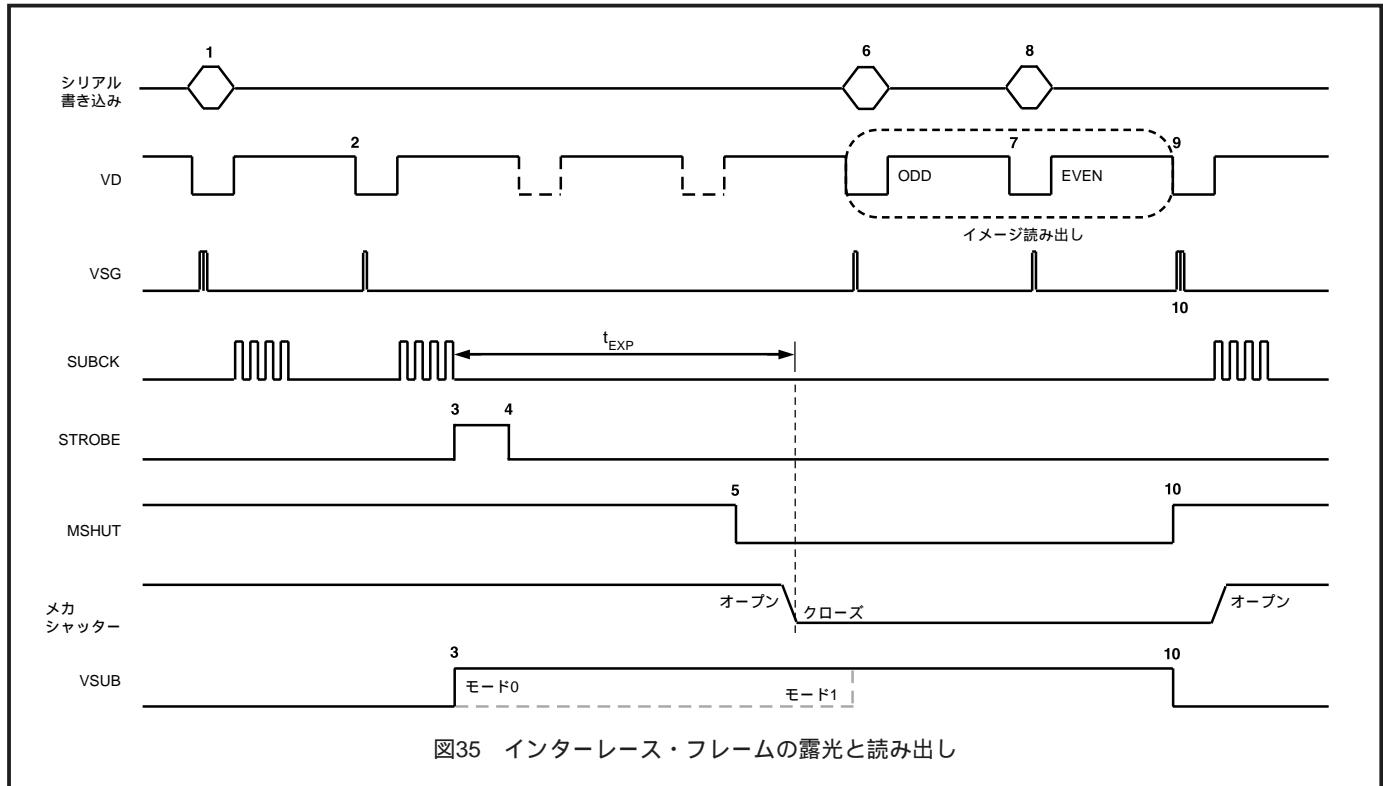

**インターレース・フレームの露光と読み出しの例**

図35に、メカシャッターとストロボを使う代表的な露光と読み出し動作に対するイベント・シーケンスを示します。VSUB、MSHUT、STROBEの各トグル・ポジションのレジスタ値は、これらの機能をトリガーする前に、いつでも設定できます。その他のレジスタに対する書き込みは、ここでは説明しない垂直クロック出力V1～V4を設定するために必要です。

0. READOUTレジスタ (addr x281) に書き込みを行い、CCDデータの読み出し時にSUBCKをさらに停止するフィールド数を指定します。この例では、READOUT = 2。

1. EXPOSUREレジスタ (addr x27D) に書き込みを行い、露光を開始させ、露光時にSUBCK出力とVSG出力を停止させるフィールド数を指定します。この例では、EXPOSURE = 2。

TRIGGERレジスタ (addr x280) に書き込みを行い、STROBE信号、MSHUT信号、VSUB信号をイネーブルにします。3信号すべてをトリガーするときは(図36の場合) TRIGGER = 7。

SGACTLINEレジスタ (addr x265とx266) とSGMASKレジスタ (addr x26Fとx270) に書き込みを行い、センサー・ゲートを奇数フィールド読み出しに設定します(インターレースCCD)。

2. VD/HDの立ち下がりエッジで、シリアル書き込みを1から更新します。

3. VSUBモード = 0の場合、VSUBONレジスタ (addr x272とx273) で指定されるラインでVSUB出力がオンになります。

STROBONレジスタ (addr x294～x299) で指定されるロケーションでSTROBE出力がオンになります。

4. STROBEOFFレジスタ (addr x29A～x29F) で指定されるロケーションで、STROBE出力がオフになります。

5. MSHUTOFFレジスタ (addr x28D～x292) で指定されるロケーションでMSHUT出力がオフになります。

6. SGACTLINEレジスタ (addr x253とx254) とSGMASKレジスタに書き込みを行い、センサー・ゲートを偶数フィールド読み出しに設定します。

7. VD/HDの立ち下がりエッジで、シリアル書き込みを6から更新します。

8. SGACTLINEレジスタとSGMASKレジスタに書き込みを行い、センサー・ゲートをドラフト/プレビュー・モード出力に再設定します。

MSHUTONレジスタ (addr x287) に書き込みを行い、ドラフト/プレビュー・モード用にメカシャッターを再度オープンします。

9. VD/HDの立ち下がりエッジで、シリアル書き込みを8から更新します。

10. VSUB出力は、ドラフト/プレビュー・モード・タイミングに戻ります。

SUBCK出力が動作を再開します。

MSHUT出力がオン・ポジションに戻ります(アクティブなわち“オープン”)。

VSUB出力がオフ・ポジションに戻ります(非アクティブ)。

# AD9891/AD9895

## アナログ・フロントエンド (AFE) の説明と動作

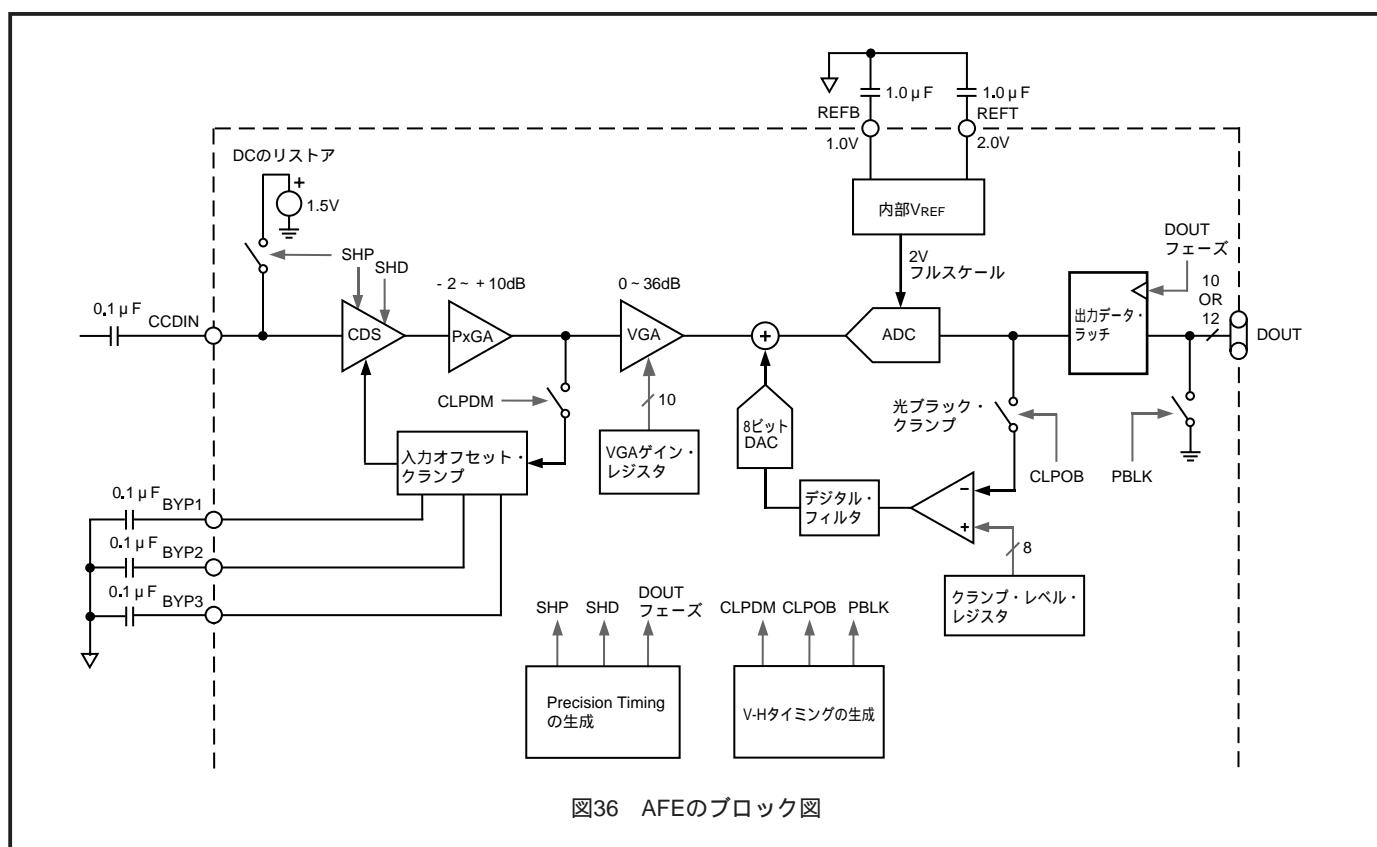

AD9891/AD9895のAFEシグナル・チェーンを図36に示します。各処理ステップは、生のCCDピクセル・データから高品質イメージを得るために不可欠です。AFEレジスタの詳細を表XXVIVに示します。

### DCの再生

CCD出力信号の大きなDCオフセットを小さくするために、DC再生回路を外付けの $0.1\text{ }\mu\text{F}$ の直列カップリング・コンデンサと一緒に使います。この回路はCCD信号のDCレベルを約1.5Vに再生して、AD9891/AD9895の3Vアナログ電源と互換性を持つようにします。

### 相關ダブル・サンプラー (CDS)

CDS回路は各CCDピクセルを2回サンプルして信号情報を取り出し、低周波数ノイズを除去します。図10に示すタイミングは、内部で発生された2個のCDSクロックSHPとSHDを使ってCCD信号のそれぞれリファレンス・レベルとデータ・レベルをサンプリングする方法を説明しています。SHPとSHDのサンプリング・エッジの配置は、アドレス0xE9と0xEAにあるそれぞれSHPPOSLOCレジスタとSHDPOSLOCレジスタにより指定されます。これら2クロック信号の配置は、CCDから最適な性能を取り出すために重要です。

### 入力のクランプ

ライン・レート入力クランプ回路は、CCDの光学的ブラック・オフセットを除去するために使います。このオフセットは、CCDのシールドされたブラック・リファレンス・ピクセルの中に存在します。AD9891/AD9895は入力ステージでこのオフセットを除去して、システム・ブラック・レベルでのゲイン変化（“ゲイン・ステップ”と呼ばれるこ

とあります）の影響を小さくします。このオフセットを入力ステージで除去するもう1つの利点は、システム・ヘッドルームを大きくできることです。ある領域でCCDが大きなブラック・レベル・オフセット電圧を持つ場合、入力ステージでそれを補正しないと、高いVGAゲイン設定を使うときに内部回路のヘッドルームが大幅に少なくなってしまいます。

入力クランプは、設定可能なCLPDM信号により制御されます（水平クランピングとプランギングの節参照）。水平タイミング・シーケンスの例の節に、システム・タイミング例を示します。CLPDMパルスはCCDの有効なブラックピクセルのとき使用することをお薦めします。CLPDMは、光学的ブラック・ピクセルのとき、CLPOBと一緒に、または別々に使用することができます。CLPDMパルスは、最小4ピクセル幅である必要があります。

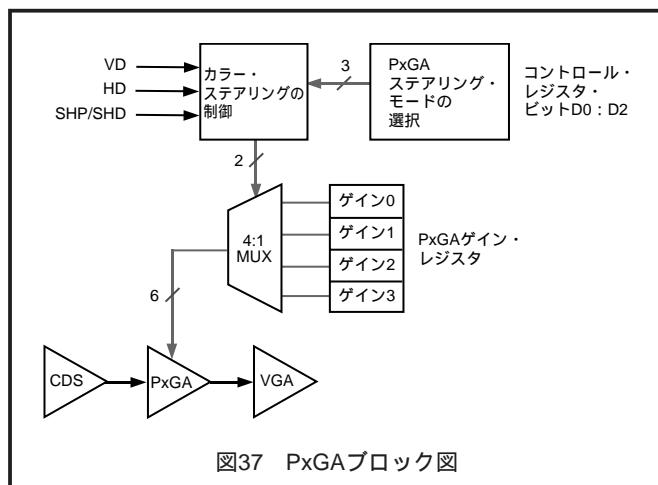

### PxGA

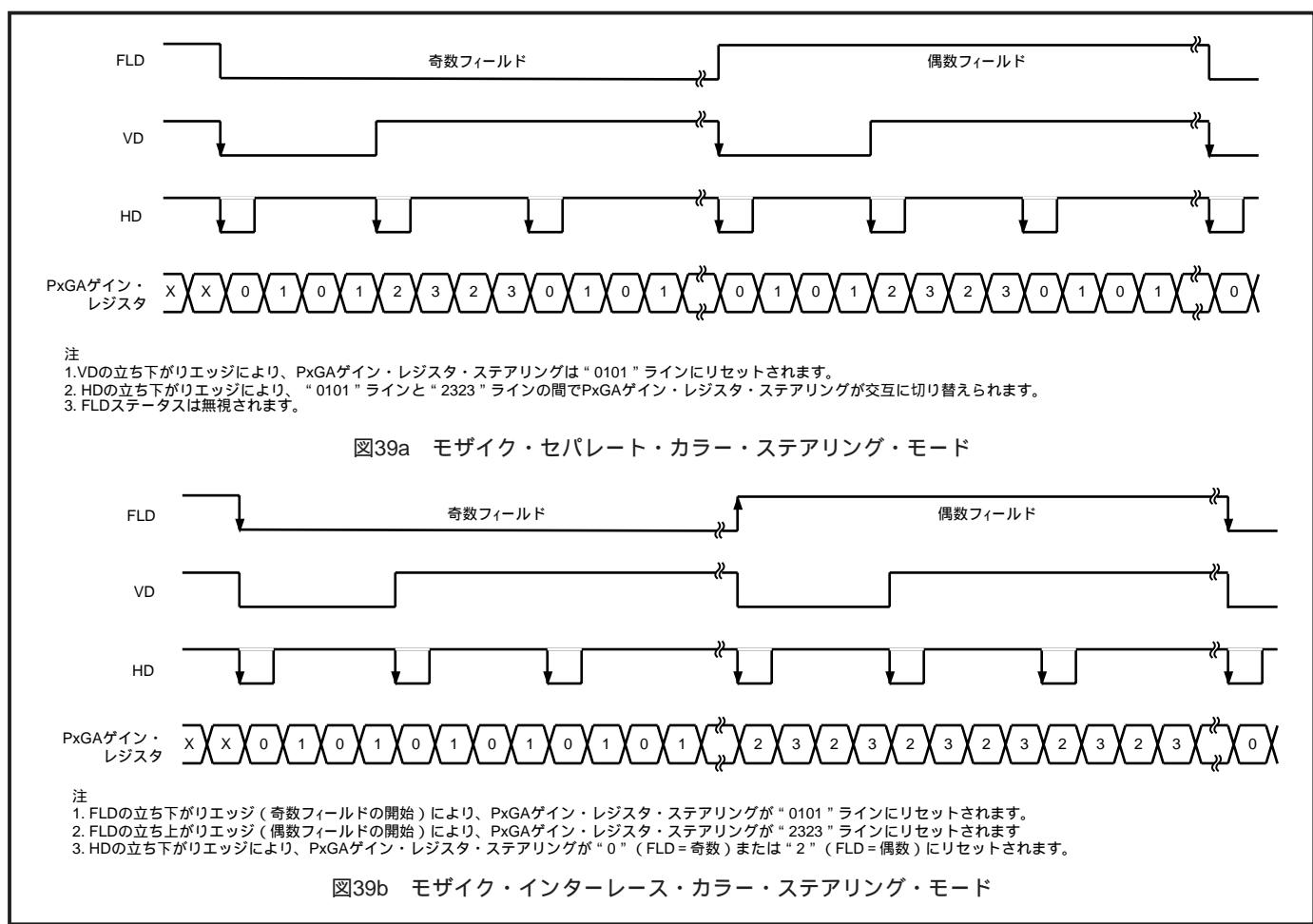

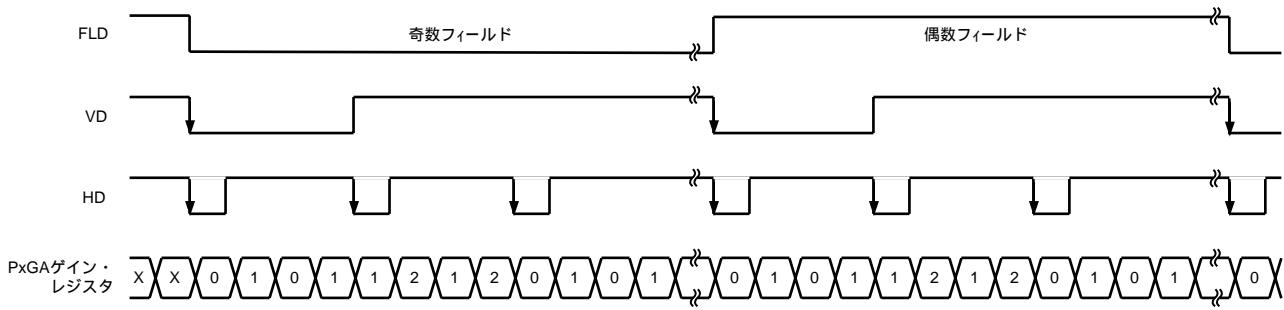

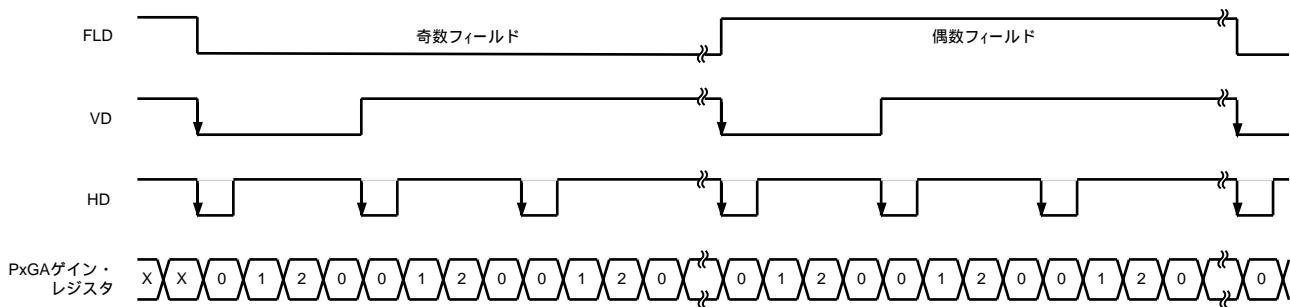

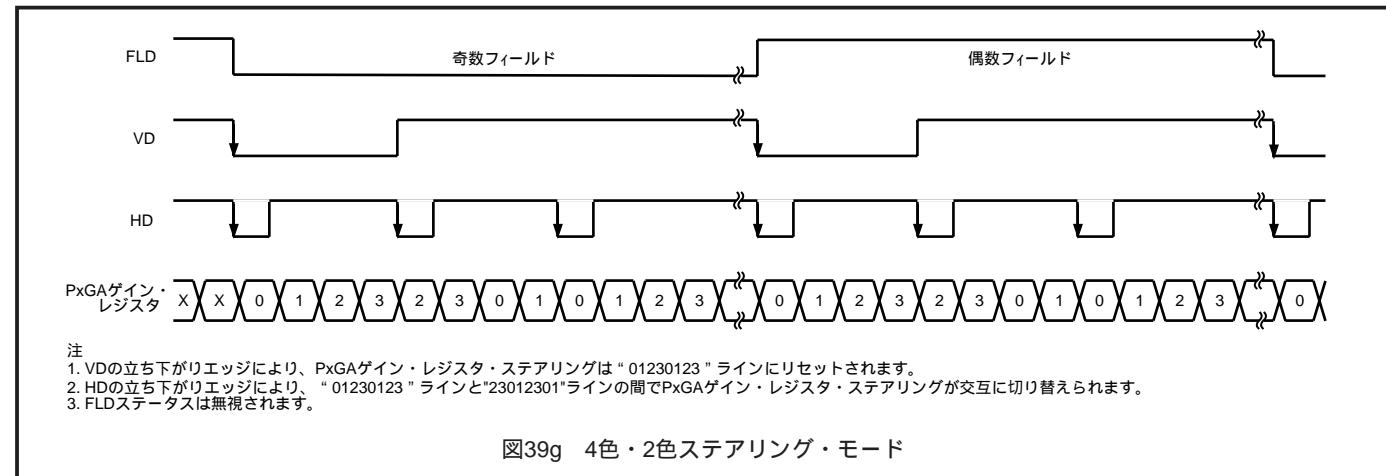

PxGAは、個別カラー・ピクセルに別々にゲイン調整を提供します。4個の個別な値を持つプログラマブル・ゲイン・アンプPxGAは、ピクセル単位でゲイン値を“マルチプレクス”する機能を持っています（図37）。この機能により、低レベルの出力カラー・ピクセルを増幅して、高レベルの出力カラー・ピクセルに一致させることができます。また、PxGAを使ってカラーを調整してホワイト・バランスをとることにより、必要となるデジタル処理を減らすことができます。“カラー・ステアリング”回路に従って、4種類のゲイン値を切り替えます。CCDカラー・フィルタ・アレイのさまざまなタイプに対する7種類のカラー・ステアリング・モードが、アドレス0x06にあるAD9891/AD9895AFE CTLMODE・レジスタに設定されます（内部カラー・ステアリング・タイミングについては図39a～図39gを参照してください）。

図36 AFEのブロック図

例えば、モザイク・セパレート・ステアリング・モードは、Rフィルタ、Gフィルタ、Bフィルタの広く使用されている“ベイヤー”配列に対応します（図38a）。

同じベイヤー・パターンはインターレースすることもできるため、このタイプのCCDを使うときはモザイク・インターレース・モードを使います（図38b）。カラー・ステアリング機能は、R、G、Bの各ゲイン値（PxGAゲイン・レジスターにロード）のマルチプレクスを行い、垂直（VD）同期パルスと水平（HD）同期パルスに同期化します。各4チャンネルに対するPxGAゲインは-2～+10dBの範囲で可変であり、シリアル・インターフェースを介して64ステップの制御ができます。PxGAのゲイン・カーブを図40に示します。

|                    |                               |                               |

|--------------------|-------------------------------|-------------------------------|

| CCD : プログレッシブ・ペイサー | モザイク・セパレート・カラー・<br>ステアリング・モード |                               |

| R      Gr          | R      Gr                     | ライン0 → ゲイン0、ゲイン1、ゲイン0、ゲイン1... |

| Gb    B            | Gb    B                       | ライン1 → ゲイン2、ゲイン3、ゲイン2、ゲイン3... |

| R      Gr          | R      Gr                     | ライン2 → ゲイン0、ゲイン1、ゲイン0、ゲイン1... |

| Gb    B            | Gb    B                       |                               |

図38a CCDカラー・フィルタの例：プログレッシブ・スキャン

|                               |                                 |   |    |                               |

|-------------------------------|---------------------------------|---|----|-------------------------------|

| CCD : インターレース・<br>ベイバー偶数フィールド | モザイク・インターレース・カラー・<br>ステアリング・モード |   |    |                               |

| R                             | Gr                              | R | Gr | ライン0 → ゲイン0、ゲイン1、ゲイン0、ゲイン1... |

| R                             | Gr                              | R | Gr | ライン1 → ゲイン0、ゲイン1、ゲイン0、ゲイン1... |

| R                             | Gr                              | R | Gr | ライン2 → ゲイン0、ゲイン1、ゲイン0、ゲイン1... |

| R                             | Gr                              | R | Gr |                               |

| 奇数フィールド |   |    |   |

|---------|---|----|---|

| Gb      | B | Gb | B |

| Gb      | B | Gb | B |

| Gb      | B | Gb | B |

| Gb      | B | Gb | B |

| Gb      | B | Gb | B |

図38b CCDカラー・フィルタの例：インター-レース

# **AD9891/AD9895**

注

1. **VDの立ち下がりエッジ**により、PxGAゲイン・ステアリングが“0101”ラインにリセットされます。

2. **HDの立ち下がりエッジ**により、“0101”ラインと“1212”ラインの間でPxGAゲイン・ステアリングが交互に切り替えられます。

3. すべてのファイルが同じPxGAゲイン・ステアリング・パターンを持ちます（FLDステータスは無視されます）。

図39c モザイクリピートカラー・ステアリング・モード

注

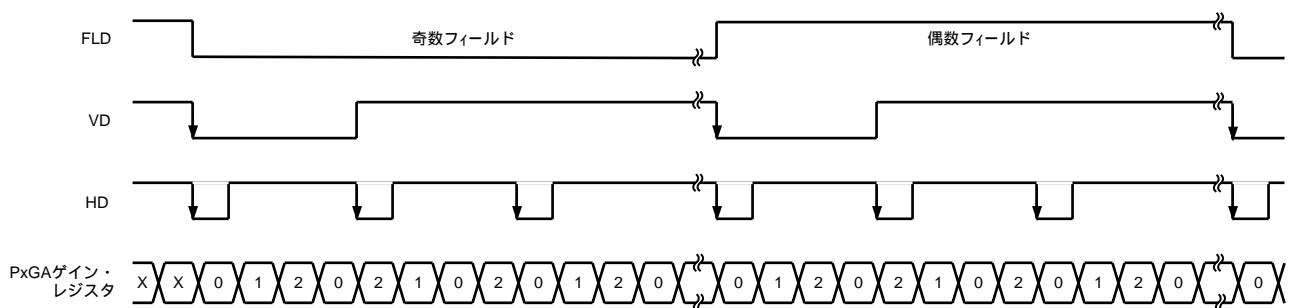

1. 各ラインは “012012” ステアリング・パターンに従います。

2. VDとHDの立ち下がりエッジにより、PxGAゲイン・レジスタ・ステアリングがゲイン・レジスタ “0” にリセットされます。

3. F1/D1ステータスは無視されます。

図39d 3色・1色ステアリング・モード

注

- は

1. **VDの立ち下がりエッジ**により、PxGAゲイン・レジスタ・ステアリングは“012012”ラインにリセットされます。

2. **HDの立ち下がりエッジ**により、“012012”ラインと“210210”ラインの間でPxGAゲイン・レジスタ・ステアリングが交互に切り替えられます。

3. **FLDステータス**は無視されます。

図39e 3色・2色ステアリング・モード

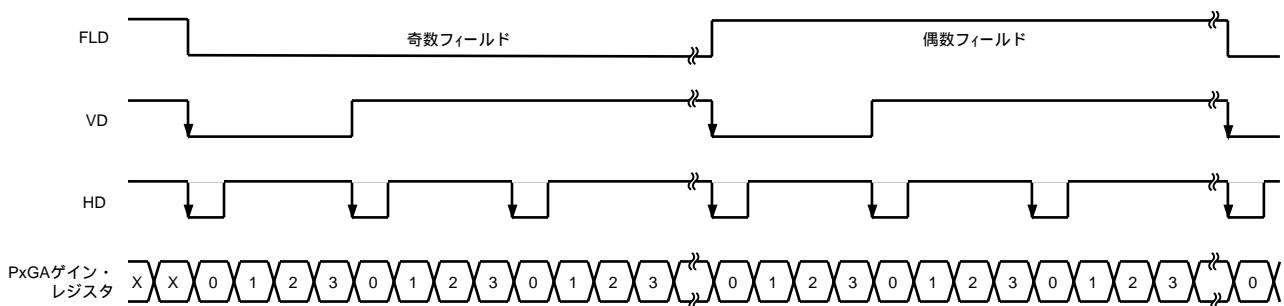

注

- 各ラインは “01230123” ステアリング・パターンに従います。

- VDとHDの立ち下がりエッジにより、PxGAゲイン・レジスタ・ステアリングがゲイン・レジスタ “0” にリセットされます。

- FLDステータスは無視されます。

図39f 4色・1色ステアリング・モード

## 可変ゲイン・アンプ

VGAステージは2~36dBのゲイン範囲を提供し、シリアル・デジタル・インターフェースを介して10ビット分解能で設定できます。PxGAステージからの4dBと組み合わせて、AD9891/AD9895の合計ゲイン範囲は6~40dBになります。1Vの入力信号と2VのADCフルスケール範囲を一致させるためには少なくとも6dBのゲインが必要です。1Vのフルスケール・システム(例えばアナログ・デバイセズのAD9803)と比べると、等価なゲイン範囲は0~34dBになります。

VGAゲイン・カーブは、“dBで直線”の特性に従います。正確なVGAゲインは、任意のゲイン・レジスタ値に対して次式を使って計算できます。

$$\text{ゲイン} = (0.035 \times \text{コード}) + 3.55$$

ここで、コード範囲は0~1023。PxGAデフォルト・ゲインが含まれています。ゲイン精度仕様には、合計ゲイン範囲6~40dBに対して4dBのPxGAゲインを含んでいます。

## オプティカルブラック・クランプ

オプティカルブラック・クランプ・ループはシグナル・チェーン内の残留オフセットを除去するために使い、CCDのブラック・レベルにおける低周波数変動に追従します。各ライン上のオプティカルブラック（シリルド）ピクセル区間で、ADC出力がクランプ・レベル・レジスタを使ってユーザーが選択した固定のブラック・レベル・リファレンスと比較されます。0 ~ 255 LSBの任意の値を8ビット分解能で書き込むことができます。得られた誤差信号はフィルタによってノイズが除去されて、補正值がD/Aコンバータを介してADC入力に与えられます。通常、オプティカルブラック・クランプ・ループは水平ライン当たり1回オンにされますが、このループは特定のアプリケーションに合わせるため、さらに低速で更新できます。ポスト処理で外部デジタル・クランピングを使う場合、動作レジスタのビットD5を使ってAD9891のオプティカルブラック・クランピングをディスエーブルにできます（シリアル・インターフェース・タイミングの節とレジスタ・リストの節を参照してください）。ループがディスエーブルにされても、クランプ・レベル・レジスタを使ってプログラマブルなオフセット調整を提供できます。

オプティカルブラック・クランプは、設定可能なCLPOB信号により制御されます( 水平クランピングとプランギングのセクション参照 )。水平タイミング・シーケンスの例の節に、システム・タイミング例を示します。CLPOBパレスは、CCDのオプティカルブラック・ピクセル区間に配置する必要があります。CLPOBパレスは、少なくとも20ピクセル幅継続させることをお薦めします。これより短いパレス幅も使用することはできますが、ブラック・レベルにおける低周波数変動の追従機能が低下します。

A/Dコンバータ

AD9891/AD9895は、高速と低消費電力向けに最適化された高性能10ビットADCアーキテクチャを使っています。微分非直線性(DNL)性能のtyp値は、0.5 LSBより優れています。ADCは2Vの入力範囲を使っています。ADCのフルスケール範囲が大きいほど、良いノイズ性能が得られます。

# AD9891/AD9895

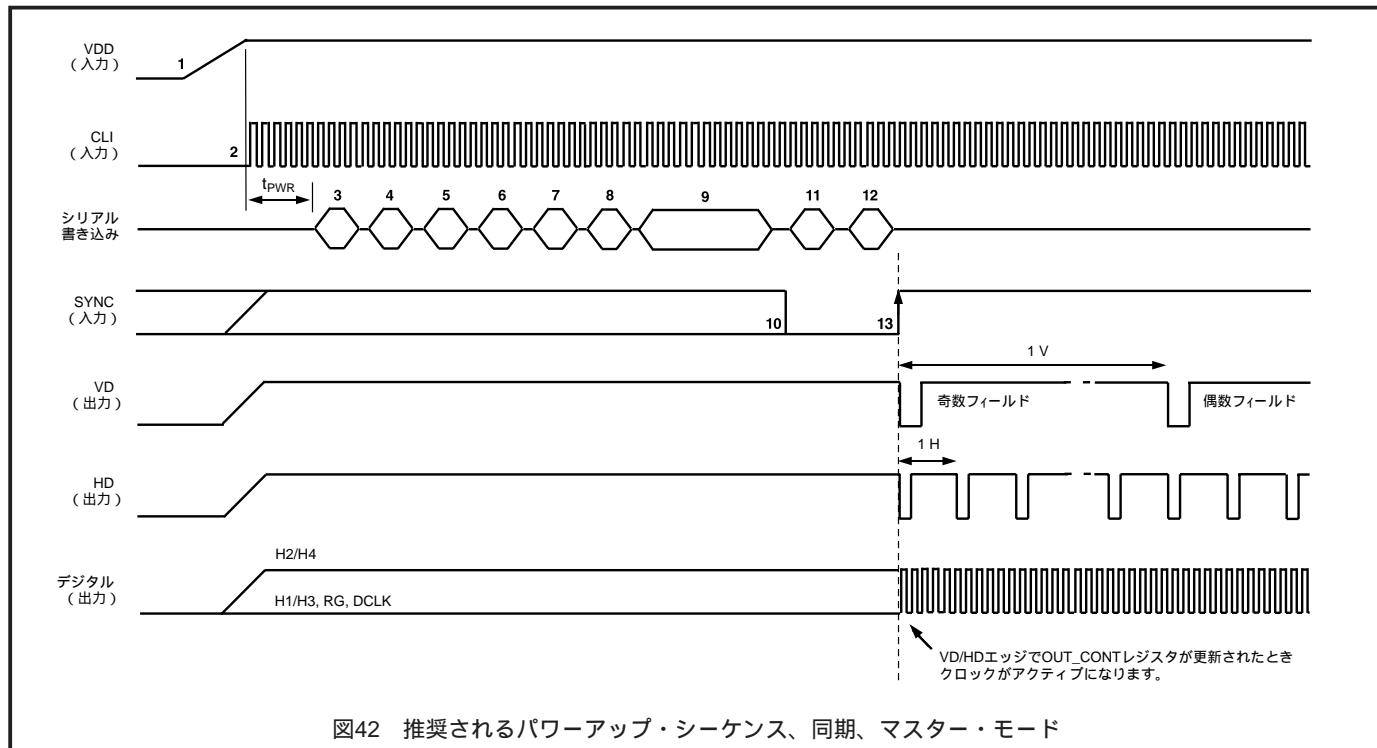

図42 推奨されるパワーアップ・シーケンス、同期、マスター・モード

## パワーアップと同期

マスター・モードに推奨されるパワーアップ・シーケンス

AD9891/AD9895のパワーアップ時に、次のシーケンスが推奨されます（各ステップについては図42参照）。

1. AD9891/AD9895の電源をオンにします。

2. マスター・クロック入力CLIを入力します。

3. 内部AD9891/AD9895レジスタをリセットします。すなわち、SW\_RESETレジスタ(addr x017)に“1”を書き込み、次に“0”を書き込みます。次に、INITIAL1レジスタ(addr x02B)に‘110101’(53decimal)を書き込み、INITIAL2レジスタ(addr x010)に‘000100’(4decimal)を書き込みます。この書き込みシーケンスは、常に次の順番で行われます。

```

addr x017      data 000001

addr x017      data 000000

addr x02B      data 110101

addr x010      data 000100

```

4. MASTERレジスタ(addr × OEB)に“1”を書きこむことにより、AD9891/AD9895は、マスターモードに設定されます。

5. デフォルトでは、TGCORE\_RSTBレジスタ = “0”により、内部タイミング・コアがリセット状態に維持されています。“1”をTGCORE\_RSTBレジスタ(addr x029)に書き込んで、内部タイミング・コアを起動します。

6. PREVENTUPDATEレジスタ(addr x01B)に“1”を書き込みます。この動作により、シリアル・レジスタ・データの更新が停止されます。

7. “1”をSYNCENABLEレジスタ(addr x024)に書き込みます。この動作により、外部SYNCの使用が可能になります。

8. “1”をSYNCSUSPENDレジスタ(addr x026)に書き込みます。この動作により、SYNC動作中のクロック出力が停止します（図43）。

9. 希望のレジスタに書き込みを行い、高速タイミング、水平タイミング、垂直タイミング、シャッター・タイミングを設定します。

10. パワーアップ時にSYNCがハイレベルの場合、SYNC入力をローレベルにします。また、パワーアップからSYNCをローレベルに維持することも可能です。

11.“1”をOUT\_CONTレジスタ(addr x018)に書き込みます。この動作により、SYNCの立ち上がりエッジの後に出力がアクティブになります。

12.“0”をPREVENTUPDATEレジスタ(addr x01B)に書き込みます。この動作により、次のVD/HDの立ち下がりエッジでシリアル情報を更新できるようになります。

13.SYNCをハイレベルに戻します。この動作により、内部カウンタが“0”にリセットされて、VD/HD動作が開始されます。VD/HDエッジにより、すべてのクロック出力をイネーブルにするOUT\_CONTなどのレジスタの更新が行われます。

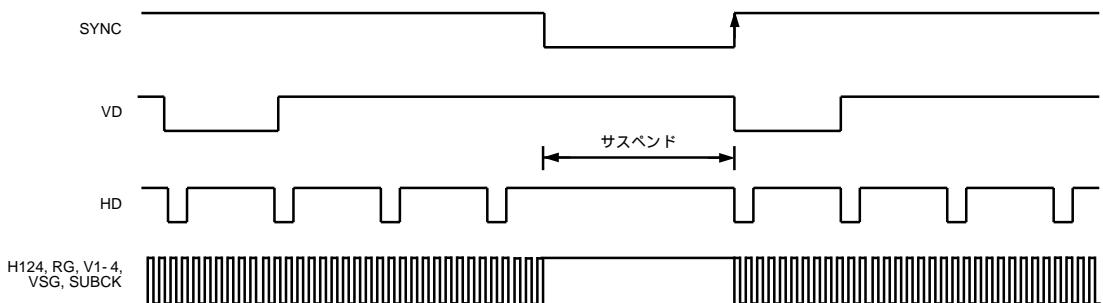

## マスター・モード動作時のSYNC

図43に示すとおり、このSYNC入力は、AD9891/AD9895カウンタを外部タイミングで再同期する動作の間いつでも使用できます。デジタル出力の動作はSYNCSUSPENDレジスタ(addr x026)を“1”に設定することによって、SYNC動作中いつでもサスペンダ�습니다。

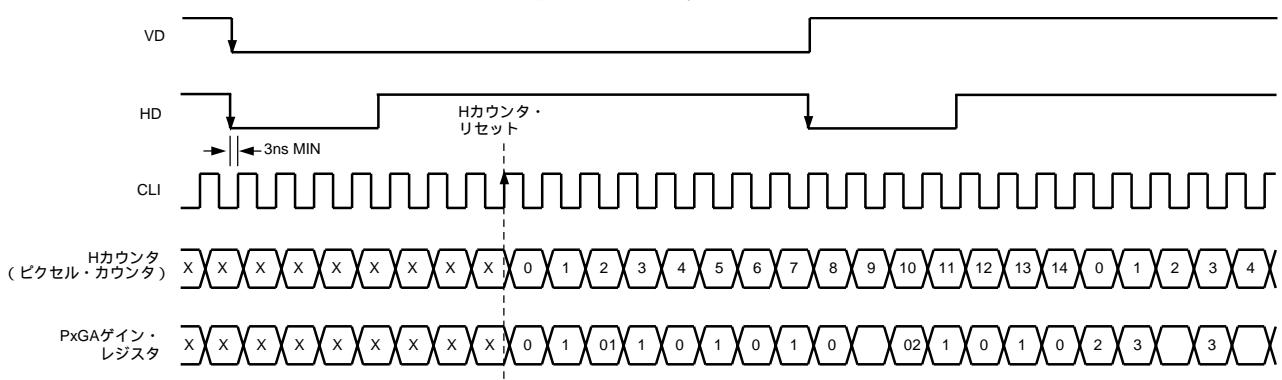

## スレーブ・モードでの同期

AD9891/AD9895をスレーブ・モードで使用しているとき、VDおよびHD入力は内部カウンタを同期させるために使用されます。VDの立ち下がりエッジに続き、Hカウンタがリセットされるまで、HDの立ち下がりエッジの後8マスター・クロック周期(CLI)の遅延が起こります。

注

1. SYNCの立ち上がりエッジにより、VD/HDおよびカウンタがゼロにリセットされます。

2. SYNC極性は、SYNCPOLレジスタ (ADDR x025) を使って設定可能です。

3. SYNCのローレベル時に、すべての内部カウンタがリセットされ、VD/HDはSYNCSUSPENDレジスタ (ADDR x026) を使って停止させることができます。

4. SYNC\_SUSPEND = 1の場合、垂直クロック、H1 ~ H4、RGはデフォルトの極性になります。

5. SYNC\_SUSPEND = 0の場合、すべてのクロック出力はSYNCリセット・エッジまで通常動作を続けます。

図43 AD989xを外部タイミングに同期するSYNCのタイミング

注

1. HDの立ち下りエッジの後、内部Hカウンタは8クロック・サイクル間リセットされます。

2. PxGAステアリングは、内部Hカウンタのリセットに同期されます（モザイク・セパレート・モードを表示）。

図44 外部VD/HDと内部Hカウンタとの同期、スレープ・モード

## パワーダウン・モード動作

AD9891/AD9895は、特定のアプリケーションで全体の消費電力を最適化する3つのパワーダウン・モードを持っています。OPRMODEレジスタのビット[1 : 0]が、デバイスのパワーダウン状態を次のように制御します。

OPR\_MODE [1 : 0] = 00 = 通常動作 (フル消費電力)

OPR\_MODE[1 : 0] = 01 = パワーダウン1モード

OPR\_MODE[1 : 0] = 10 = パワーダウン2モード

OPR\_MODE[1 : 0] = 11 = パワーダウン3モード

(最小の全体消費電力)

表XVIIに、各パワーダウン・モードの動作をまとめます。どのモードでも、OUT\_CONTレジスタは、デジタル出力状態が関係するパワーダウン・モードより高い優先順位を持つことに注意してください。パワーダウン3モードは最小の消費電力であり、CLIとCLOの間に接続された水晶発振子回路もパワーダウンします。したがって、CLIとCLOを使って水晶発振子がマスター・クロックを発生している場合、この回路がパワーダウンされるため、クロック信号がなくなります。パワーダウン3モードから通常動作に戻るとき、OPR\_MODEレジスタに書き込みが行われた後、少なくとも500 μs間、タイミング・コアをリセットしておく必要があります。この動作により、水晶発振子回路が安定するため十分な時間が確保されます。

# AD9891/AD9895

表XVI パワーダウン・モードの動作

| I/Oブロック    | OUT_CONT == LO <sup>1</sup> | パワーダウン1 <sup>1</sup> | パワーダウン2 <sup>1、2</sup> | パワーダウン3 <sup>1、3、4</sup> |

|------------|-----------------------------|----------------------|------------------------|--------------------------|

| AFE        | オン                          | オフ                   | オフ                     | オフ                       |

| タイミング・コア   | オン                          | オン                   | オフ                     | オフ                       |

| CLOオシレータ   | オン                          | オン                   | オン                     | オフ                       |

| V1         | LO                          | LO                   | LO                     | LO                       |

| V2         | LO                          | LO                   | LO                     | LO                       |

| V3         | HI                          | HI                   | HI                     | LO                       |

| V4         | HI                          | HI                   | HI                     | LO                       |

| VSG1       | HI                          | HI                   | HI                     | LO                       |

| VSG2       | HI                          | HI                   | HI                     | LO                       |

| VSG3       | HI                          | HI                   | HI                     | LO                       |

| VSG4       | HI                          | HI                   | HI                     | LO                       |

| VSG5       | HI                          | HI                   | HI                     | LO                       |

| VSG6       | HI                          | HI                   | HI                     | LO                       |

| VSG7       | HI                          | HI                   | HI                     | LO                       |

| VSG8       | HI                          | HI                   | HI                     | LO                       |

| SUBCK      | HI                          | HI                   | HI                     | LO                       |

| VSUB       | LO                          | LO                   | LO                     | LO                       |

| MSHUT      | LO                          | LO                   | LO                     | LO                       |

| STROBE     | LO                          | LO                   | LO                     | LO                       |

| H1         | LO                          | LO                   | LO ( 3.5mA )           | Hi-Z                     |

| H2         | HI                          | HI                   | HI ( 3.5mA )           | Hi-Z                     |

| H3         | LO                          | LO                   | LO ( 3.5mA )           | Hi-Z                     |

| H4         | HI                          | HI                   | HI ( 3.5mA )           | Hi-Z                     |

| RG         | LO                          | LO                   | LO ( 3.5mA )           | Hi-Z                     |

| LD/FD      | LO                          | LO                   | LO                     | LO                       |

| CLPOB/PBLK | HI                          | HI                   | HI                     | LO                       |

| VD         | vdhdpol                     | 動作                   | vdhdpol                | LO                       |

| HD         | vdhdpol                     | 動作                   | vdhdpol                | LO                       |

| DCLK       | LO                          | 動作                   | LO                     | LO                       |

| CLO        | 動作                          | 動作                   | 動作                     | HI                       |

| DOUT       | LO                          | LO                   | LO                     | LO                       |

## 注

1 1列目は、OUT\_CONT == LO ( OUT\_CONTが優先 ) のときデフォルトを表します。パワーダウン1、2、3は、OPRMODEレジスタ・ビット[1 : 0]を直接デコードしたものです。これらの極性はOUT\_CONT == HIの場合です。

2 パワーダウン2では、H[1,2,3,4]DRVがセットされ、RGDRVが3'h1 ( 3.5mA ) に設定されます。パワーダウン3では、HクロックとRGクロックがトライアステートになります ( H[1,2,3,4]DRVがセットされ、RGDRVが3'h0に設定されます )。

3 パワーダウン3では、タイミング・コアとCLOオシレータがパワーダウンされます。.

4 パワーダウン3を抜け出るときは、先ず2'b00をOPRMODE[1 : 0]に書き込み ( オシレータとタイミング・コアをウェイクアップ ) 次にロックを保証するために約500 μs後にタイミング・コアをリセットします。

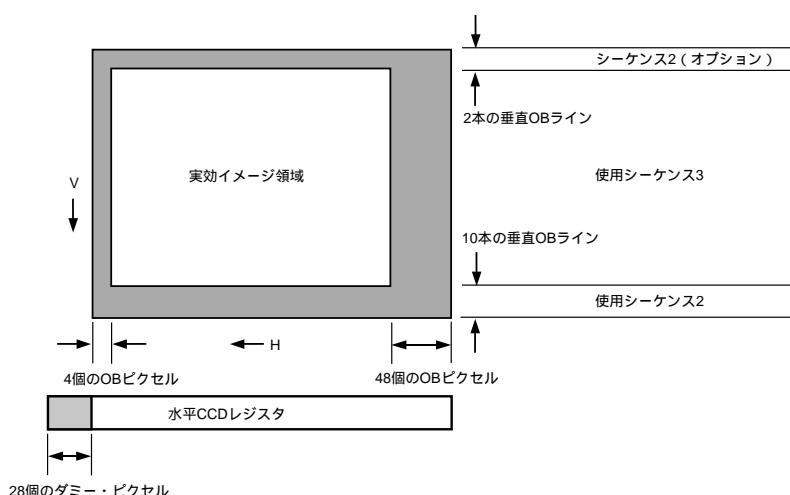

## 水平タイミング・シーケンスの例

図45に、CCDレイアウト例を示します。水平レジスタには28個のダミー・ピクセルが格納されており、CCDからクロック駆動される各ライン上でこれらのダミー・ピクセルが使用されます。垂直方向では、読み出しの前と読み出しの後に10本の光学的ブラック（OB）ラインがあります。水平方向には、前側に4個のOBピクセル、後ろ側に48個のOBピクセルがあります。

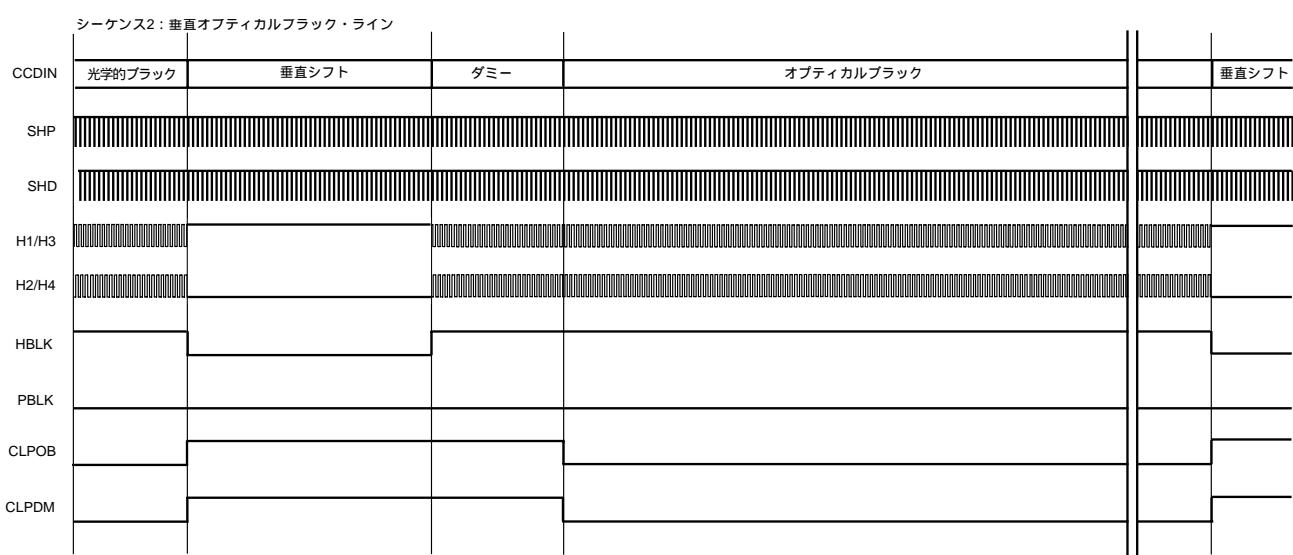

このCCDに対してAD9891/AD9895の水平信号を設定するときは、3つのシーケンスを使うことができます。図46に、垂直プランキングで使う最初のシーケンスを示します。この区間では、センサーからの有効なOBピクセルがないため、

CLPOB信号とCLPDM信号は使用されません。ケースによっては、水平クロックをこの区間で使用する場合に、CLPDM信号を使ってAD9891/AD9895の入力クランプの部分的な整定を維持できるものもあります。この区間に、有効データがないため、PBLKをイネーブルすることができます。

図47に、垂直OB区間にに対する推奨シーケンスを示します。クランプ信号をライン全体に使用して、AD9891/AD9895のクランプ・ループを安定させます。

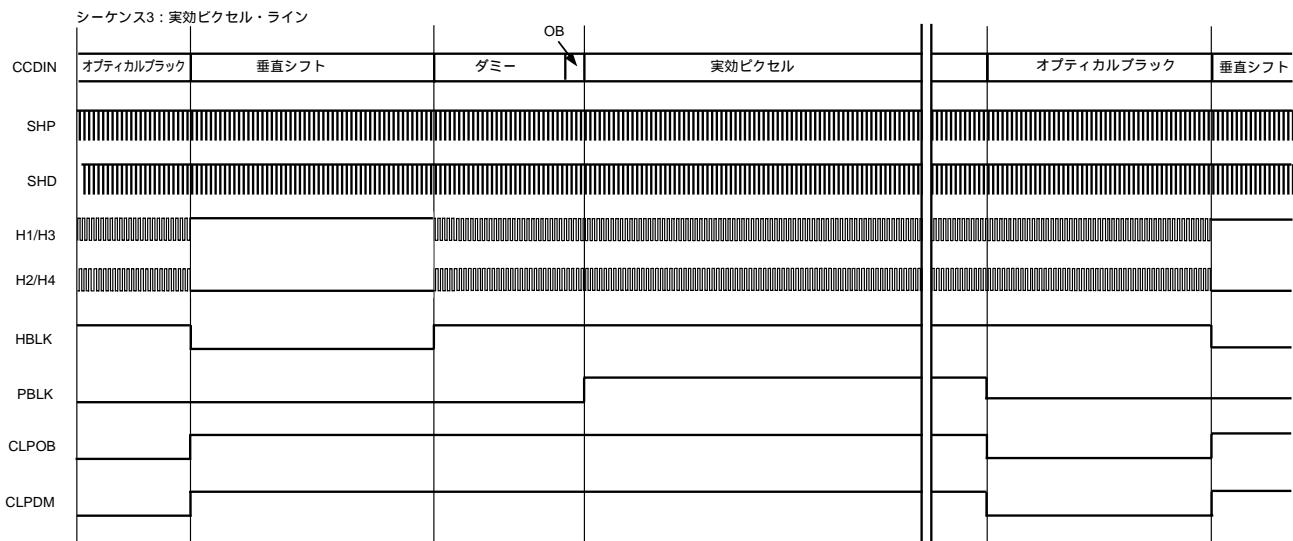

図48に、実効ピクセル読み出しに対する推奨シーケンスを示します。各ラインの終わりの48個のOBピクセルは、CLPOB信号とCLPDM信号に対して使います。

図45 CCD設定の例

| シーケンス1：垂直ブランディング |        |       |       |        |

|------------------|--------|-------|-------|--------|

|                  | 無効ピクセル | 垂直シフト | ダミー   | 無効ピクセル |

| CCDIN            |        |       |       |        |

| SHP              |        |       |       |        |

| SHD              |        |       |       |        |

| H1/H3            |        |       |       |        |

| H2/H4            |        |       |       |        |

| HBLK             |        |       |       |        |

| PBLK             |        |       |       |        |

| CLPOB            |        |       |       |        |

| CLPDM            |        |       | ----- |        |

**注** 垂直プランキングでHクロックを使う場合、水平ダミー・ピクセル区間にCLPDMパルスを使うことができます。

図46 垂直プランキングでの水平シーケンス

# AD9891/AD9895

図47 垂直オプティカルブラック・ピクセル区間での水平シーケンス

図48 実効ピクセル区間での水平シーケンス

### 垂直タイミングの例

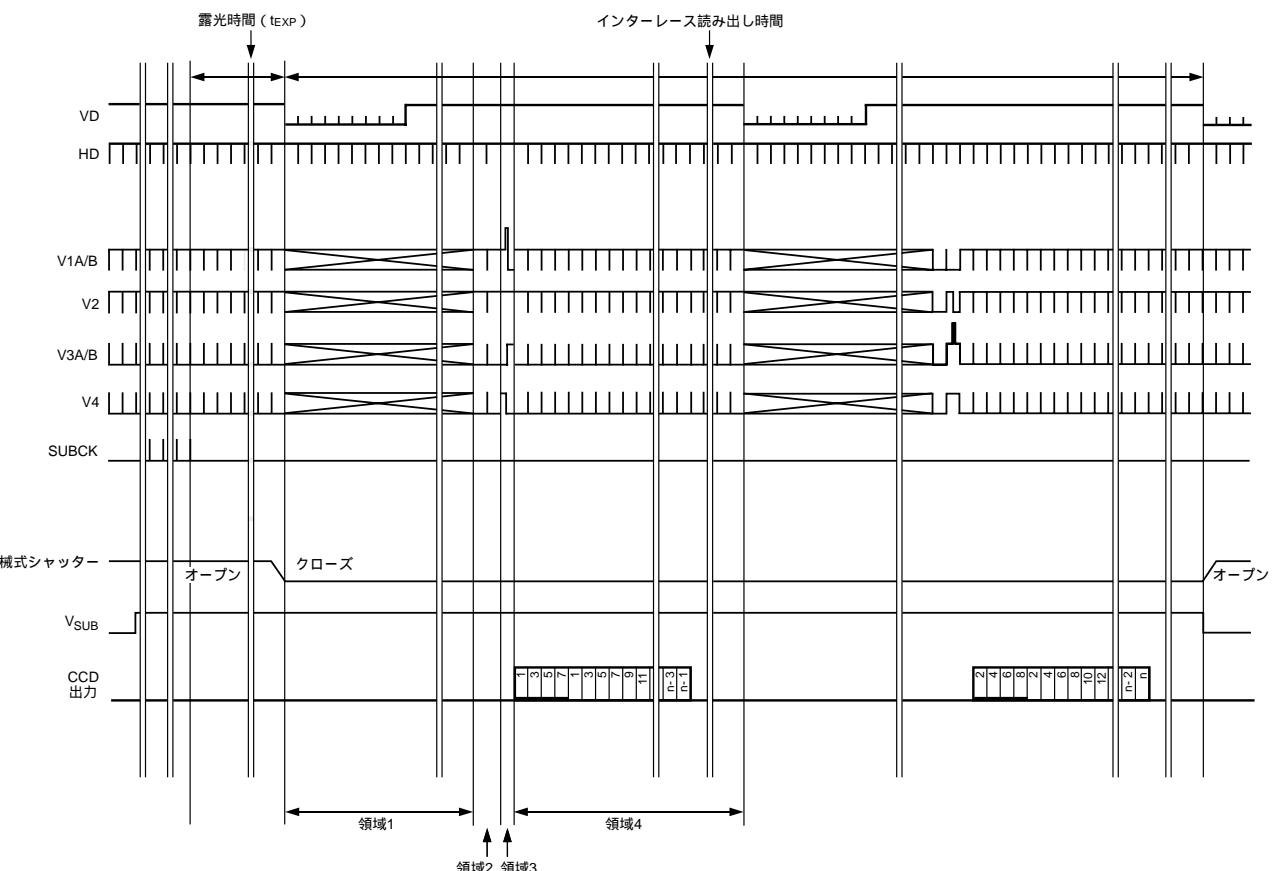

図49に、CCD例でのインターレース読み出しのタイム・チャートを示します。各フィールドは、4つの領域に分割されます。垂直領域チェンジポジション（RCP）は各領域のライン境界を設定し、領域ポインタは各領域に固有の領域を割り当てます。

領域0は高速垂直シフト領域です。スイープ・モードを使って、CCDの垂直レジスタから電荷を“スイープ”するために必要な高速垂直パルス数でこのタイミング動作を発生させることができます。

領域1は2本のラインだけで構成され、標準のシングル・ライン垂直シフト・タイミングを使います。この領域のこのタイミングは、領域3のタイミングと同じです。

領域2はセンサー・ゲート・ラインで、ここでVSGパルスがイメージを垂直CCDレジスタに転送します。この領域は、SGラインに対して2番目の垂直シーケンスの使用を必要とします。

領域3でも標準のシングル・ライン垂直シフト・タイミングを使い、領域1と同じタイミングです。

つまり、領域1と領域3が同じタイミングを使うため、3つのユニークな領域が4つの領域に対応するために必要となります。

センサー・ゲート・パルスやライン・ロケーションなどの幾つかのタイミング・パラメータは、2番目のフィールドを読み出すために調整が必要です。

図49 垂直タイミングの例 領域分割

# AD9891/AD9895

## 回路レイアウト情報

AD9891/AD9895の代表的な回路接続を図50に示します。PCBレイアウトは、AD989X製品から優れた画像品質を得るために重要です。すべての電源ピン、特にAVDD1、TCVDD、RGVDD、HVDDは、高品質の高周波数用チップ・コンデンサを使ってグラウンドからデカップリングする必要があります。デカップリング・コンデンサは電源ピンのできるだけ近くに配置し、非常に小さいインピーダンス・パスで連続したグラウンド・プレーンに接続する必要があります。また、4.7 μF以上の値を持つバイパス・コンデンサも各メイン電源ピンAVDD、RGVDD、HVDD、DRVDDに接続する必要があります（各個別ピンには必要ありません）。多くのアプリケーションで、RGVDDとHVDDの間で電源を共用することは可能ですが、これは個別電源ピンが別々にバイパスされている場合にのみ可能です。別の3V電源をDRVDDに使うこともできますが、この電源ピンもチップの他の部分と同様に、同じグラウンド・プレーンにデカップリングする必要があります。DRVSSに対しては別のグラウンドの使用は推奨されません。

アナログ・バイパス・ピン（BYP1～BYP3、VRB、VRT）も、それぞれのピンのできるだけ近くで注意深くグラウンドへデカップリングする必要があります。アナログ入力（CCDIN）コンデンサもピンの近くに配置する必要があります。

H1～H4パターンとRGパターンは、信号歪みを避けるため

低インダクタンスとなるようにデザインする必要があります。CCDから大きな過渡電流がH1～H4に流れるため、太いパターンにすることを推奨します。可能な場合、AD9891/AD9895をCCDの近くに配置すると、これらのラインのインダクタンスを押さえられます。常に、配線バスはAD9891/AD9895からCCDへ可能な限り真っ直ぐにします。

また、AD9891/AD9895は、外部水晶発振子を駆動するための発振回路も内蔵しています。図51に、代表的な18MHz水晶発振子を使ったアプリケーション例を示します。外付け抵抗とコンデンサの値については、水晶発振子メーカーのデータシートを参照してください。

図51 AD9891/AD9895の水晶発振子ドライバのアプリケーション

図50 AD9891/AD9895の代表的な回路構成

### シリアル・インターフェースのタイミング

AD9891/AD9895のすべての内部レジスタは3線式シリアル・インターフェースを介してアクセスされます。各レジスタは、10ビット・アドレスと6ビット・データ・ワードで構成されています。10ビット・アドレスと6ビット・データ・ワードは、LSB先頭で書き込まれます。各レジスタに対する書き込みでは、16ビット動作が必要です(図52)。多くのレジスタが6ビット幅以下ですが、6ビットすべてを各レジスタに書き込む必要があります。レジスタが2ビット幅の場合、上位4ビットは無視され、シリアル書き込み動作時に“0”で埋めることができます。6ビット未満が書き込まれると、レジスタは新しいデータで更新されません。

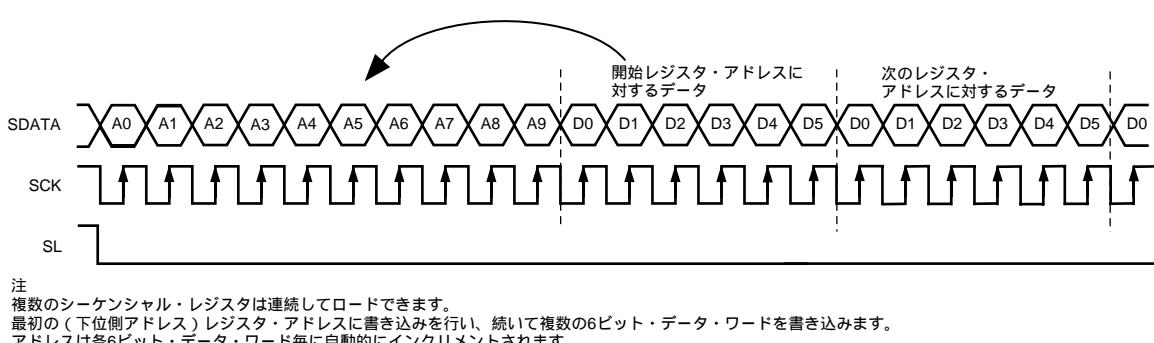

AD9891/AD9895内には多くのレジスタが存在するため、図53に、AD9891/AD9895のアドレス自動インクリメント機能を使うレジスタに対する効率良い書き込み方法を示します。この方法を使うと、最下位の希望アドレスに先に書き込みを行い、次に6ビット・データ・ワードを書き込みます。各新しい6ビット・データ・ワードが自動的に次のレジスタ・アドレスに書き込まれます。書き込み対象の各10ビット・アドレスを不要にすることにより、レジスタのロードを高速化できます。アドレス自動インクリメント機能は任意のレジスタ・アドレスから開始することができます、最小2本のレジスタから全レジスタまでに対する書き込みに対して利用できます。

### ダブル幅レジスタ・アクセスについての注意

AD9891/AD9895には多くのダブル幅レジスタがあります。これらのレジスタは2個の6ビット・レジスタを接続して構成し

ており、下位6ビットが2つのアドレスの下位側に、残りの上位ビットが2つのアドレスの上位側に、それぞれ配置されています。例えば、OPRMODEレジスタの下位6ビットOPRMODE[5:0]はアドレス0x00に配置されています。OPRMODEレジスタの上位6ビットOPRMODE[11:6]は、アドレス0x1に配置されています。ダブル幅レジスタをアクセスするときは、次のルールに従う必要があります。

1. ダブル幅レジスタをアクセスするときは、両アドレスを書き込む必要があります。