# AD9884A

## 特長

**最大変換レート** : 140MSPS

**アナログ帯域幅** : 500MHz

**アナログ入力範囲** : 0.5 ~ 1.0V

**PLLクロック・ジッター** : 400ps p-p

**パワーダウン・モード**

**電源電圧** : 3.3V

**3ステートCMOS出力** : 2.5 ~ 3.3V

**ディマルチプレックス出力ポート**

**データ・クロック出力供給**

**低消費電力** : 570mW Typ.

**内部PLLによるHSYNCからのクロック生成**

**シリアル・ポート・インターフェース**

**完全プログラマブル構成**

**高解像度アプリケーション用交互ピクセル・サンプリング対応**

## アプリケーション

**RGBグラフィック処理**

**LCDモニター／プロジェクタ**

**プラズマ・ディスプレイ・パネル**

**スキャン・コンバータ**

## 概要

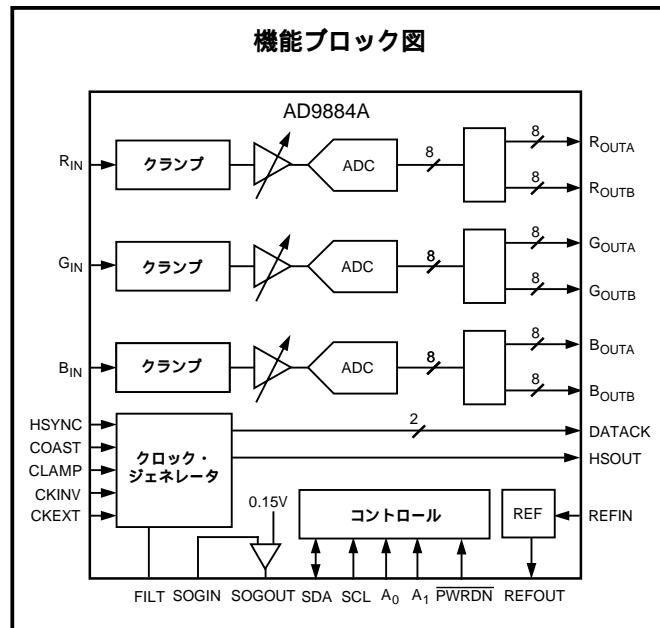

AD9884Aは、PCとワークステーションからのRGBグラフィック信号のキャプチャに最適化された、完全な8ビット、140MSPSのモノリシック・アナログ・インターフェースです。140MSPSのエンコード・レートと、500MHzのフルパワー・アナログ帯域幅によって、75Hzで1280×1024 (SXGA)までのディスプレイ解像度をサポートし、十分な帯域幅で高精度な各ピクセルの取り込みとデジタル化を行います。

システム・コストと消費電力を最小限に抑えるため、AD9884Aは、+1.25Vのリファレンス、HSYNCからピクセル・クロックを生成するPLL、プログラマブル・ゲイン、オフセット、クランプ回路を内蔵しています。3.3V電源、アナログ入力、HSYNC信号を供給するだけで使用可能です。2.5 ~ 3.3V電源で、3ステートのCMOS出力が可能です。

AD9884Aの内蔵PLLは、HSYNC入力からピクセル・クロックを生成します。ピクセル・クロックの出力周波数範囲は、

20 ~ 140MHzです。PLLのクロック・ジッターは、リファレンス入力に対して400 ps p-p (typ) です。HSYNC入力がない場合でも、COAST信号が存在すれば、PLLは出力周波数をそのまま維持できます。32段階のサンプリング位相調整が可能です。データ、HSYNC、データ・クロックの出力位相の関係は、常に一定です。内部PLLをディスエーブルにして、外部クロックをピクセル・クロックとして入力することもできます。

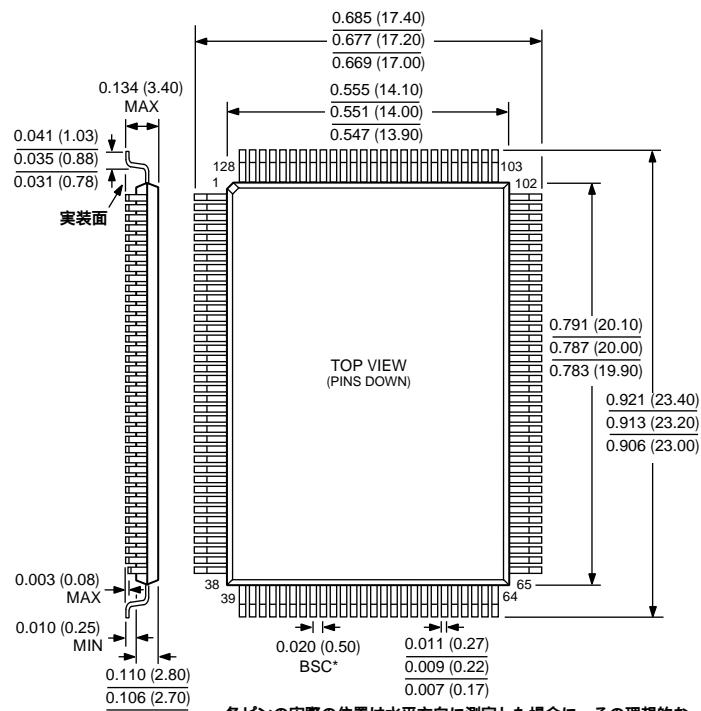

クランプ信号は、内部生成と、ユーザーによるCLAMP入力ピン経由の外部入力が選択できます。AD9884Aは、2線式シリアル・ポート経由で、完全にプログラマブルです。AD9884Aは、先進的CMOSプロセスで製造されています。省スペース128ピンMQFP表面実装パッケージで供給され、動作温度範囲は0 ~ 70 °Cです。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、その情報の利用または利用したことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものではありません。

# AD9884A 仕様

( $V_D = +3.3V$ 、 $V_{DD} = +3.3V$ 、 $PV_D = +3.3V$ 、A/DCクロック周波数 = 最大、PLLクロック周波数 = 最大、コントロール・レジスタをデフォルト状態に設定)

| パラメータ                       | 温度   | テスト・レベル | AD9884AKS-100  |                   |        | AD9884AKS-140  |                   |        | 単位     |

|-----------------------------|------|---------|----------------|-------------------|--------|----------------|-------------------|--------|--------|

|                             |      |         | Min            | Typ               | Max    | Min            | Typ               | Max    |        |

| 分解能                         |      |         | 8              |                   |        | 8              |                   |        | ピット    |

| DC精度                        |      |         |                |                   |        |                |                   |        |        |

| 微分非直線性誤差                    | + 25 | I       | ± 0.5          | ± 1.0             |        | ± 0.5          | ± 1.15 / - 1.0    |        | LSB    |

|                             | 全温度  | VI      |                | ± 1.0             |        |                | ± 1.25 / - 1.0    |        | LSB    |

| 積分非直線性誤差                    | + 25 | I       | ± 0.50         | ± 1.25            |        | ± 0.8          | ± 1.4             |        | LSB    |

|                             | 全温度  | VI      |                | ± 1.75            |        |                | ± 2.5             |        | LSB    |

| ノーミス・コード                    | 全温度  | VI      | 保証             |                   |        | 保証             |                   |        |        |

| アナログ入力                      |      |         |                |                   |        |                |                   |        |        |

| 入力電圧範囲                      |      |         |                |                   |        |                |                   |        |        |

| 最小                          | 全温度  | VI      |                | 0.5               |        |                | 0.5               |        | Vp-p   |

| 最大                          | 全温度  | VI      | 1.0            |                   |        | 1.0            |                   |        | Vp-p   |

| ゲイン温度係数                     | + 25 | V       | 100            |                   |        | 280            |                   |        | ppm/   |

| 入力バイアス電流                    | + 25 | I       |                | 1                 |        |                | 1                 |        | μA     |

|                             | 全温度  | VI      |                | 1                 |        |                | 1                 |        | μA     |

| 入力オフセット電圧                   | 全温度  | VI      | 7              | 50                |        | 7              | 50                |        | mV     |

| 入力フル・スケール・マッチング             | 全温度  | VI      | 1.5            | 5.0               |        | 1.5            | 5.0               |        | %FS    |

| オフセット調整範囲                   | 全温度  | VI      | 22             | 23.5              | 25     | 22             | 23.5              | 25     | %FS    |

| リファレンス出力                    |      |         |                |                   |        |                |                   |        |        |

| 出力電圧                        | 全温度  | VI      | + 1.20         | + 1.25            | + 1.30 | + 1.20         | + 1.25            | + 1.30 | V      |

| 温度係数                        | 全温度  | V       |                | ± 50              |        |                | ± 50              |        | ppm/   |

| スイッチング性能                    |      |         |                |                   |        |                |                   |        |        |

| 最大変換レート                     | 全温度  | VI      | 100            |                   |        | 140            |                   |        | MSPS   |

| 最小変換レート                     | 全温度  | IV      |                | 10                |        |                | 10                |        | MSPS   |

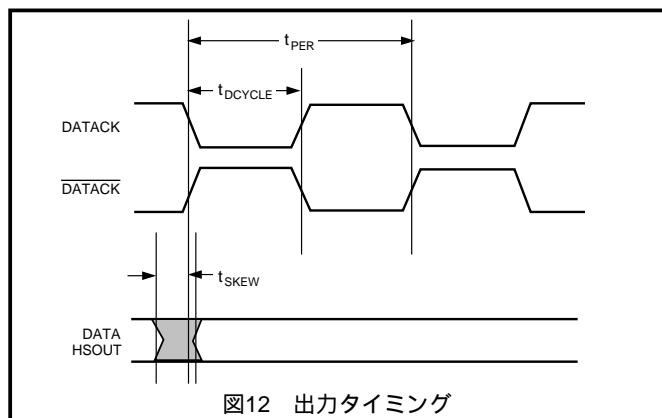

| データ対クロック・スキュー、 $t_{SKew}$   | 全温度  | IV      | - 0.5          | 2.0               |        | - 0.5          | 2.0               |        | ns     |

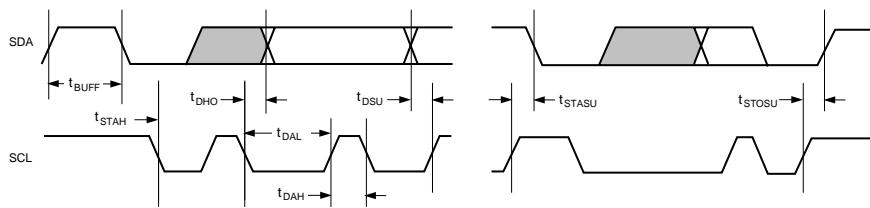

| $t_{BUFF}$                  | 全温度  | VI      | 4.7            |                   |        | 4.7            |                   |        | μs     |

| $t_{STAH}$                  | 全温度  | VI      | 4.0            |                   |        | 4.0            |                   |        | μs     |

| $t_{DHO}$                   | 全温度  | VI      | 0              |                   |        | 0              |                   |        | μs     |

| $t_{DAL}$                   | 全温度  | VI      | 4.7            |                   |        | 4.7            |                   |        | μs     |

| $t_{DAH}$                   | 全温度  | VI      | 4.0            |                   |        | 4.0            |                   |        | μs     |

| $t_{DSU}$                   | 全温度  | VI      | 250            |                   |        | 250            |                   |        | ns     |

| $t_{STASU}$                 | 全温度  | VI      | 4.7            |                   |        | 4.7            |                   |        | μs     |

| $t_{STOSU}$                 | 全温度  | VI      | 4.0            |                   |        | 4.0            |                   |        | μs     |

| H SYNC入力周波数                 | 全温度  | IV      | 15             | 110               |        | 15             | 110               |        | KHz    |

| 最大PLLクロック・レート               | 全温度  | VI      | 100            |                   |        | 140            |                   |        | MHz    |

| 最小PLLクロック・レート               | 全温度  | IV      |                | 20                |        |                | 20                |        | MHz    |

| PLLジッター                     | + 25 | IV      | 400            | 700 <sup>1</sup>  |        | 475            | 750 <sup>2</sup>  |        | ps p-p |

|                             | 全温度  | IV      |                | 1000 <sup>1</sup> |        |                | 1000 <sup>2</sup> |        | ps p-p |

| サンプリング位相温度係数                | 全温度  | IV      | 15             |                   |        | 15             |                   |        | ps/    |

| デジタル入力                      |      |         |                |                   |        |                |                   |        |        |

| 入力電圧、ハイ ( $V_{IH}$ )        | 全温度  | VI      | 2.5            |                   |        | 2.5            |                   |        | V      |

| 入力電圧、ロー ( $V_{IL}$ )        | 全温度  | VI      |                | 0.8               |        |                | 0.8               |        | V      |

| 入力電流、ハイ ( $I_{IH}$ )        | 全温度  | VI      |                | - 1.0             |        |                | - 1.0             |        | μA     |

| 入力電流、ロー ( $I_{IL}$ )        | 全温度  | VI      |                | 1.0               |        |                | 1.0               |        | μA     |

| 入力容量                        | + 25 | V       | 3              |                   |        | 3              |                   |        | pF     |

| デジタル出力                      |      |         |                |                   |        |                |                   |        |        |

| 出力電圧、ハイ ( $V_{OH}$ )        | 全温度  | VI      | $V_{DD} - 0.1$ |                   |        | $V_{DD} - 0.1$ |                   |        | V      |

| 出力電圧、ロー ( $V_{OL}$ )        | 全温度  | VI      |                | 0.1               |        |                | 0.1               |        | V      |

| デューティ・サイクル                  |      |         |                |                   |        |                |                   |        |        |

| DATACK、 $\overline{DATACK}$ | 全温度  | IV      | 45             | 50                | 55     | 45             | 50                | 55     | %      |

| 出力コーディング                    |      |         |                | バイナリ              |        |                | バイナリ              |        |        |

| パラメータ                                   | 温度   | テスト・レベル | AD9884AKS-100 |      |     | AD9884AKS-140 |      |     | 単位  |

|-----------------------------------------|------|---------|---------------|------|-----|---------------|------|-----|-----|

|                                         |      |         | Min           | Typ  | Max | Min           | Typ  | Max |     |

| 電源                                      |      |         |               |      |     |               |      |     |     |

| $V_D$ 電源電圧                              | 全温度  | IV      | 3.0           | 3.3  | 3.6 | 3.0           | 3.3  | 3.6 | V   |

| $V_{DD}$ 電源電圧                           | 全温度  | IV      | 2.2           | 3.3  | 3.6 | 2.2           | 3.3  | 3.6 | V   |

| $PV_D$ 電源電圧                             | 全温度  | IV      | 3.0           | 3.3  | 3.6 | 3.0           | 3.3  | 3.6 | V   |

| $I_D$ 電源電流 ( $V_D$ )                    | + 25 | V       |               | 125  |     |               | 135  |     | mA  |

| $I_{DD}$ 電源電流 ( $V_{DD}$ ) <sup>3</sup> | + 25 | V       |               | 33   |     |               | 47   |     | mA  |

| $IPV_D$ 電源電流 ( $PV_D$ )                 | + 25 | V       |               | 15   |     |               | 15   |     | mA  |

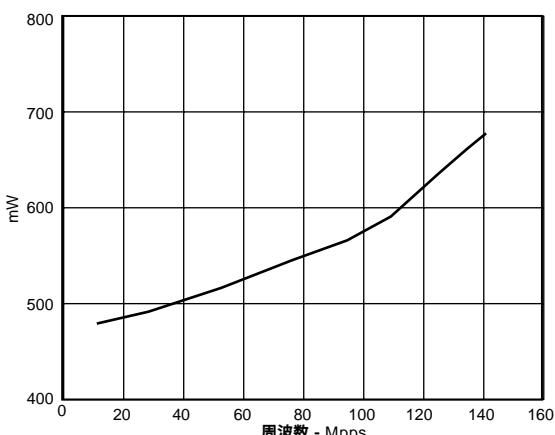

| 全消費電力                                   | 全温度  | VI      |               | 570  | 675 |               | 650  | 775 | mW  |

| パワーダウン電源電流                              | 全温度  | VI      |               | 2.0  | 3.0 |               | 2.0  | 3.0 | mA  |

| パワーダウン消費電力                              | 全温度  | VI      |               | 6.6  | 9.9 |               | 6.6  | 9.9 | mW  |

| ダイナミック性能                                |      |         |               |      |     |               |      |     |     |

| アナログ帯域幅、フル・パワー                          | + 25 | V       |               | 500  |     |               | 500  |     | MHz |

| 過渡応答                                    | + 25 | V       |               | 2    |     |               | 2    |     | ns  |

| 過電圧回復時間                                 | + 25 | V       |               | 1.5  |     |               | 1.5  |     | ns  |

| S/N比 (SNR) <sup>4</sup>                 | + 25 | I       | 44.0          | 46.5 |     | 43.5          | 46.2 |     | dB  |

| (高調波なし)                                 | 全温度  | V       |               | 46.0 |     |               | 45.0 |     | dB  |

| $f_{IN} = 40.7\text{MHz}$               |      |         |               |      |     |               |      |     |     |

| クロストーク                                  | 全温度  | V       |               | 60   |     |               | 60   |     | dBc |

| 熱特性                                     |      |         |               |      |     |               |      |     |     |

| $J_C$ 接合対ケース熱抵抗                         |      | V       |               | 8.4  |     |               | 8.4  |     | /W  |

| $J_A$ 接合対周辺環境熱抵抗                        |      | V       |               | 35   |     |               | 35   |     | /W  |

## 注記

1 VCORNGE = 01、CURRENT = 001、PLLDIV = 1693<sub>10</sub>2 VCORNGE = 10、CURRENT = 110、PLLDIV = 1600<sub>10</sub>

3 DEMUX = 1、DATAACK、DATAACK負荷 = 15pF、Data負荷 = 5pF.

4 外部ピクセル・クロックを使用した場合

仕様は予告なく変更することがあります。

## オーダー・ガイド

| モデル           | 温度範囲     | パッケージ | パッケージ・オプション |

|---------------|----------|-------|-------------|

| AD9884AKS-140 | 0 ~ + 70 | MQFP  | S-128       |

| AD9884AKS-100 | 0 ~ + 70 | MQFP  | S-128       |

| AD9884A/PCB   | + 25     | 評価ボード |             |

## テスト・レベルの解説

## テスト・レベル

- I. 100%製造テスト済み。

- II. 100%製造テスト (+ 25) および仕様規定温度におけるサンプル・テスト済み。

- III. サンプル・テストのみ。

- IV. パラメータは設計および特性テストによって保証済み。

- V. パラメータはtyp.値のみ。

- VI. 100%製造テスト (+ 25)。パラメータは設計および特性テストによって保証済み。

## 注意

ESD ( 静電放電 ) の影響を受けやすいデバイスです。4000Vもの高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることがあります。本製品には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や機能喪失を回避するために、適切なESD予防措置をとるようお奨めします。

## 絶対最大定格\*

|                |                |

|----------------|----------------|

| $V_D$ 、 $PV_D$ | - 0.5 ~ + 4V   |

| $PV_D$ 対 $V_D$ | ± 0.5V         |

| $V_{DD}$       | - 0.5 ~ + 4V   |

| アナログ入力         | $V_D$ ~ - 0.5V |

| REFIN          | $V_D$ ~ 0.0V   |

| デジタル入力         | $V_D$ ~ 0.0V   |

| デジタル出力電流       | 20mA           |

| 動作温度           | - 20 ~ + 85    |

| 保管温度           | - 65 ~ + 150   |

| 最高接合温度         | + 175          |

| 最高ケース温度        | + 150          |

## 注記

\* 上記の絶対最大定格を超えるストレスを加えると、デバイスに永久的な損傷を与えることがあります。この定格はストレス定格の規定のみを目的とするものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長期間絶対最大定格条件に置くと、デバイスの信頼度に影響を与えることがあります。

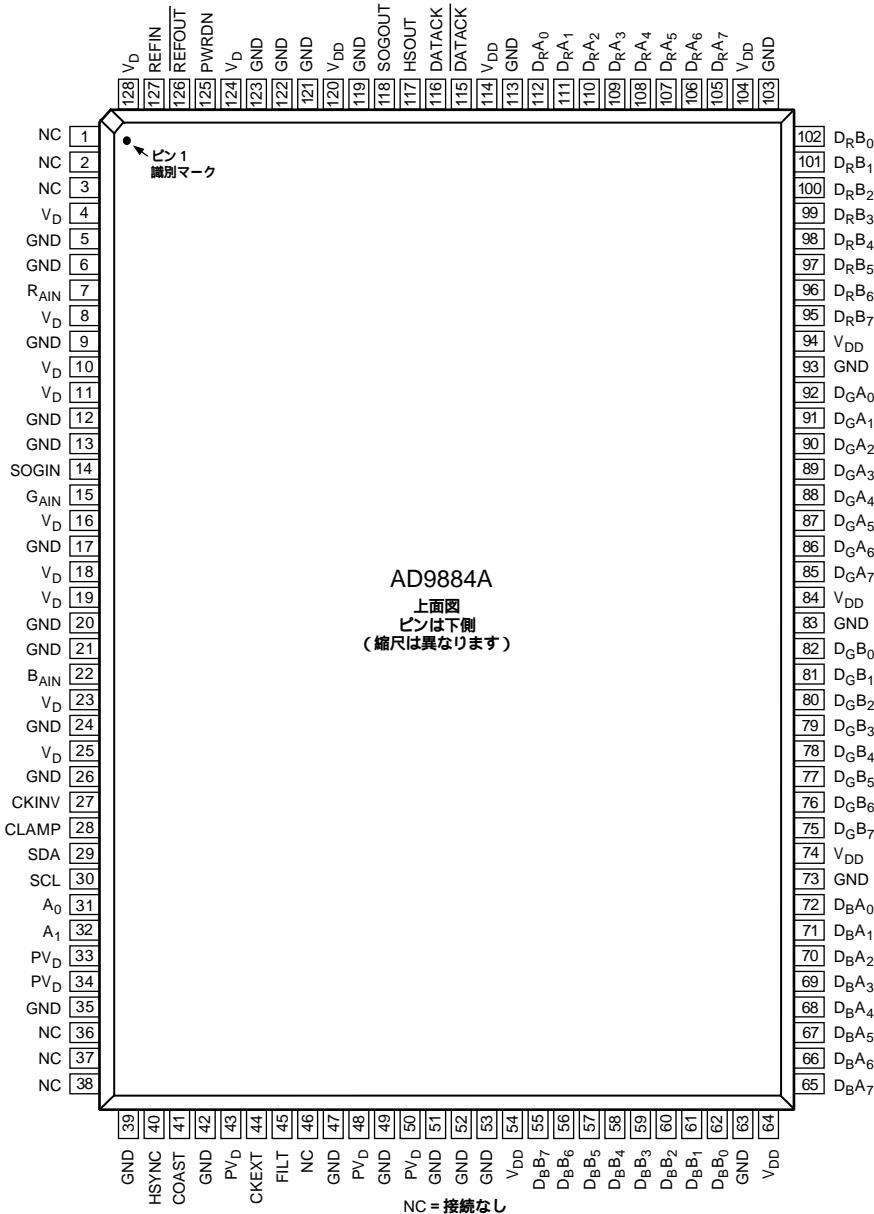

# AD9884A - 仕様<sup>1,2</sup>

表I. パッケージ接続

| 信号タイプ         | ピン名                             | 機能                        | 値                | パッケージ・ピン番号                                                                                                           |

|---------------|---------------------------------|---------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|

| 入力            | R <sub>AIN</sub>                | REDチャンネル・アナログ入力           | 0.5 ~ 1.0V FS    | 7                                                                                                                    |

|               | G <sub>AIN</sub>                | GREENチャンネル・アナログ入力         | 0.5 ~ 1.0V FS    | 15                                                                                                                   |

|               | B <sub>AIN</sub>                | BLUEチャンネル・アナログ入力          | 0.5 ~ 1.0V FS    | 22                                                                                                                   |

|               | H <sub>SYNC</sub>               | 水平同期入力                    | 3.3V CMOS        | 40                                                                                                                   |

|               | C <sub>OAST</sub>               | クロック・ジェネレータ・コースト入力(オプション) | 3.3V CMOS        | 41                                                                                                                   |

|               | C <sub>LAMP</sub>               | 外部クランプ入力(オプション)           | 3.3V CMOS        | 28                                                                                                                   |

|               | S <sub>OGIN</sub>               | Greenスライサ入力同期(オプション)      | 0.5 ~ 1.0V FS    | 14                                                                                                                   |

|               | C <sub>KEXT</sub>               | 外部クロック入力(オプション)           | 3.3V CMOS        | 44                                                                                                                   |

|               | C <sub>KINV</sub>               | サンプリング・クロック反転(オプション)      | 3.3V CMOS        | 27                                                                                                                   |

|               | D <sub>R</sub> A <sub>7-0</sub> | データ出力、Redチャンネル、ポートA       | 3.3V CMOS        | 105 ~ 112                                                                                                            |

| 出力            | D <sub>R</sub> B <sub>7-0</sub> | データ出力、Redチャンネル、ポートB       | 3.3V CMOS        | 95 ~ 102                                                                                                             |

|               | D <sub>G</sub> A <sub>7-0</sub> | データ出力、Greenチャンネル、ポートA     | 3.3V CMOS        | 85 ~ 92                                                                                                              |

|               | D <sub>G</sub> B <sub>7-0</sub> | データ出力、Greenチャンネル、ポートB     | 3.3V CMOS        | 75 ~ 82                                                                                                              |

|               | D <sub>B</sub> A <sub>7-0</sub> | データ出力、Blueチャンネル、ポートA      | 3.3V CMOS        | 65 ~ 72                                                                                                              |

|               | D <sub>B</sub> B <sub>7-0</sub> | データ出力、Blueチャンネル、ポートB      | 3.3V CMOS        | 55 ~ 62                                                                                                              |

|               | D <sub>A</sub> TACK             | データ出力クロック                 | 3.3V CMOS        | 115                                                                                                                  |

|               | D <sub>A</sub> TACK             | データ出力クロック補完               | 3.3V CMOS        | 116                                                                                                                  |

|               | H <sub>SOUT</sub>               | 水平同期出力                    | 3.3V CMOS        | 117                                                                                                                  |

| 制御            | S <sub>O</sub> GOUT             | Greenスライサ出力同期             | 3.3V CMOS        | 118                                                                                                                  |

|               | S <sub>DA</sub>                 | シリアル・データI/O               | 3.3V CMOS        | 29                                                                                                                   |

|               | S <sub>CI</sub>                 | シリアル・インターフェース・クロック        | 3.3V CMOS        | 30                                                                                                                   |

|               | A <sub>0,A</sub> <sub>1</sub>   | シリアル・ポート・アドレス LSB         | 3.3V CMOS        | 31,32                                                                                                                |

| アナログ・インターフェース | P <sub>WRDN</sub>               | パワー・ダウン制御入力               | 3.3V CMOS        | 125                                                                                                                  |

|               | R <sub>EFO</sub> UT             | 内部リファレンス出力                | + 1.25V          | 126                                                                                                                  |

|               | R <sub>EFIN</sub>               | リファレンス入力                  | + 1.25V ± 10%    | 127                                                                                                                  |

| 電源            | FILT                            | 外部フィルタ接続                  |                  | 45                                                                                                                   |

|               | V <sub>D</sub>                  | 主電源                       | 3.3V ± 10%       | 4,8,10,11,16,18,19,23,<br>25,124,128                                                                                 |

|               | V <sub>DD</sub>                 | デジタル出力電源                  | 2.5 ~ 3.3V ± 10% | 54,64,74,84,94,<br>104,114,120                                                                                       |

|               | PV <sub>D</sub><br>GND          | クロック・ジェネレータ電源<br>グラウンド    | 3.3V ± 10%<br>0V | 33,34,43,48,50<br>5,6,9,12,13,17,20,21,24,<br>26,35,39,42,47,49,51,52,<br>53,63,73,83,93,103,113,<br>119,121,122,123 |

| 接続なし          | NC                              |                           |                  | 1 ~ 3,36 ~ 38,46                                                                                                     |

## ピン配置

# AD9884A

## ピン機能説明

| ピン名                                                            | 機能                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 入力<br>R <sub>AIN</sub><br>G <sub>AIN</sub><br>B <sub>AIN</sub> | REDチャンネル・アナログ入力<br>GREENチャンネル・アナログ入力<br>BLUEチャンネル・アナログ入力<br>それぞれ、RED、GREEN、BLUEチャンネルのグラフィック信号を受け入れる高インピーダンスの入力。3つのチャンネルは同一の構成で、どの色についても使用可能なので、この色の割り当ては便宜的なものです。これらは、0.5~1.0Vフル・スケールの信号入力が可能です。信号は、クランプ動作をサポートするために、ACカップリングする必要があります。                                                                                                                                                                               |

| HSYNC                                                          | 水平同期入力<br>水平同期タイミングのリファレンスを確立するためのロジック信号入力で、ピクセル・クロック生成用の周波数リファレンスを提供します。このピンのロジック検出はHSPOLによって制御されます。HSYNCの立ち上がりエッジのみがアクティブです。HSPOL=0の場合には、HSYNCの立ち下りエッジが使用されます。HSPOL=1の場合には、立ち上がりエッジがアクティブとなります。ノイズに対する耐性を確保するため、入力に公称入力スレッショルド1.5Vのシミット・トリガを採用しています。ESD ( ElectroStatic Discharge ) 保護用ダイオードは、3.3V電源を0.5V以上上回る電圧（または、グラウンドを0.5V以上下回る電圧）が印加された場合に、抵抗値が急激に低下します。5Vの信号ソースによってこのピンをドライブする場合には、信号をクランプするか電流制限を行う必要があります。 |

| COAST                                                          | クロック・ジェネレータ・コースト入力（オプション）<br>この入力を使ってピクセル・クロック・ジェネレータのHSYNCとの同期動作を停止させ、そのままの周波数と位相でクロックの生成を続行できます。これは、垂直インターバル中で水平同期信号を生成できないようなソースを処理する場合に有効です。一般的に、PCによって生成された信号については、COAST信号は不要です。このピンのロジックの判定は、CSTPOLによって制御されます。COASTは任意のタイミングでアサートできます。このピンを使用しない場合には、グラウンドに接続しCSTPOL = 1に設定します。CSTPOLは、パワーアップの時点でデフォルト値の1に設定されます。                                                                                               |

| CLAMP                                                          | 外部クランプ入力（オプション）<br>このロジック入力を使って、入力信号をグラウンドにクランプしておく期間を設定して、黒色のリファレンスを確立できます。この操作は、グラフィック信号のパック・ポーチ期間のように、アナログ入力チャンネルに黒色の信号が存在する場合に必要です。CLAMPピンは、コントロール・ビットEXTXLMP = 1（パワーアップ時のデフォルト値は0）に設定してイネーブルになります。ディスエーブル時にはこのピンは無視され、クランプのタイミングは、遅延とHSYNC入力の立ち下りエッジからの経過時間によって内部で決定されます。このピンのロジック判定はCLAMPOLで制御されます。このピンを使用しない場合には、グラウンドに接続してEXTCLMP = 0に設定します。                                                                  |

| SOGIN                                                          | Greenスライサ同期入力（オプション）<br>この入力は、主にGREENチャンネルなどの、組み込み同期（embedded sync）信号を処理するために設けられています。このピンは、内部で生成される0.15Vのスレッショルドを備えた高速コンパレータに接続されます。組み込み同期信号とDCカップリングされたグラフィック信号に接続される場合には、非反転のデジタル出力がSOGOUTピンに出力され、この出力の状態は入力信号が0.15Vのスレッショルドを横切るたびに変化します。これは、多くの場合コンポジット同期信号であり、垂直信号をHYSYNCに受け渡す前に分離する必要のある、水平および垂直の両方の同期情報を含んでいます。SOGスライサ・コンパレータはAD9884Aがパワー・ダウンになっても動作を続行します。このピンを使用しない場合には、グラウンドに接続します。                         |

| CKEXT                                                          | 外部クロック入力（オプション）<br>HSYNCが内部で生成するクロックの代わりに、このピンを経由してAD9884Aに外部クロックを供給できます。このピンは、EXTCLK = 1に設定することによってイネーブルにできます。外部クロックを使用する場合にも、他のすべての内部機能が正常に動作します。このピンを使用しない場合には、10k の抵抗経由でグラウンドに接続し、EXTCLK = 0に設定します。このクロック位相の調整機能は、外部クロックソースが使用される場合にも動作します。                                                                                                                                                                       |

| CKINV                                                          | サンプリング・クロック反転（オプション）<br>このピンを使ってピクセル・クロックを反転させ、サンプリングの位相を180度転換できます。これは、交互ピクセル・サンプリング・モード（Alternate Pixel Sampling Mode）をサポートするもので、高い周波数の入力信号（最大280MSPS）を、最初のサンプリングで奇数番目ピクセルをキャプチャし、次に偶数番目のピクセルをキャプチャするサンプリングです。位相をシフトするため、いくつかのサンプルにわたりデータが無効となることがあるので、このピン操作はプランギング・インターバル（典型例として垂直プランギング）でのみ行ってください。CKINVを使用しない場合には、グラウンドに接続します。                                                                                  |

## ピン機能説明（続き）

| ピン名                             | 機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 出力                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D <sub>R</sub> A <sub>7-0</sub> | データ出力、Redチャンネル、ポートA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D <sub>R</sub> B <sub>7-0</sub> | データ出力、Redチャンネル、ポートB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D <sub>G</sub> A <sub>7-0</sub> | データ出力、Greenチャンネル、ポートA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D <sub>G</sub> B <sub>7-0</sub> | データ出力、Greenチャンネル、ポートB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D <sub>B</sub> A <sub>7-0</sub> | データ出力、Blueチャンネル、ポートA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D <sub>B</sub> B <sub>7-0</sub> | データ出力、Blueチャンネル、ポートB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                 | これらは、メイン・データの出力です。ビット7がMSBです。各チャンネルは2つのポートを持っています。AD9884Aがシングル・チャンネル・モード（DEMUX = 0）で動作している場合、すべてのデータはポートAに渡され、ポートBは高インピーダンス状態になります。DEMUX = 1に設定するとデュアル・チャンネル・モードが選択されて、ピクセルは各チャンネルのポートAとポートBに交互に渡されます。PAR = 1（パラレル・モード）に設定されている場合には、これらのデータは同時に現れ、1入力ピクセルおきに出力されます。PAR = 0に設定されている場合には、ピクセル・データは2つのポートに交互に現れ、入力ピクセル毎に1つの新しいサンプルが出来ます（インターリーブ・モード）。デュアル・チャンネル・モードでは、HSYNCがポートAにルートされてから最初のピクセルがサンプルされます。2番目のピクセルはポートBに、3番目のピクセルはポートAに、というように振り分けられます。ピクセルのサンプリングから出力までの遅延は一定です。PHASEレジスタの設定変更によりサンプリング時間が変化した場合には、出力のタイミングもシフトされます。DATACK、DATACK、HSOUTの各出力もシフトされるので、各信号間のタイミングの関係は保たれます。 |

| DATACK                          | データ出力クロック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DATACK                          | データ出力クロック補間                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 | これらの差動データ・クロック信号は、出力データとHSOUTをストローブして外部ロジックに出力されます。これらは、内部クロック・ジェネレータによって生成され、内部のピクセル・サンプリング・クロックと同期しています。AD9884Aがシングル・チャンネル・モードで動作している場合には、出力される周波数はピクセルのサンプリング・クロックに等しくなります。デュアル・チャンネル・モードでは、データ出力クロックと出力データはピクセル・レートの半分のレートで出力されます。PHASEレジスタの設定変更によりサンプリング時間が変化した場合には、出力のタイミングもシフトされます。DATACK、DATACK、HSOUTの各出力もシフトされるため、信号間におけるタイミングの関係は保たれます。タイミング・モードとインターフェースの設計に応じ、これらの信号の一方または双方を使用することができます。                                                                                                                                                                                   |

| HSOUT                           | 水平同期出力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                 | HSYNC入力を再構成し、位相を一致させた信号です。この信号は常にアクティブ・ハイの状態にあります。DATACK、DATACK、データを一致させておくことにより、水平同期に対するタイミングは明確に決定されます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SOGOUT                          | Greenスライサ出力同期                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                 | Greenスライサ出力同期コンパレータの出力です。SOGINが、コンポジット同期信号を含みグラウンドをリファレンスとしてDCカッピングされたアナログ・グラフィック信号と共に存在した場合、SOGOUTがデジタル・コンポジット同期信号を生成します。この信号はAD9884Aの他の処理を受けません。SOGスライサ・コンパレータは、AD9884Aのパワーダウン時にも動作を続行します。                                                                                                                                                                                                                                                                                                                                                                                            |

| 制御                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SDA                             | シリアル・データI/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 | シリアル・インターフェース・ポートに対する双方向のデータ・ポートです。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SCL                             | シリアル・インターフェース・クロック。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                 | シリアル・インターフェース・ポートに対するクロック入力です。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A <sub>1-0</sub>                | シリアル・ポート・アドレスのLSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                 | シリアル・ポート・アドレスの LSB は、これらのピンのロジック・レベルで設定されます。ピンをグラウンドに接続するとアドレス・ビットが0に、ハイに接続（10k を介して V <sub>DD</sub> に接続）するとアドレス・ビットが1に設定されます。これらのピンを使用してシリアル・アドレスを4Chから4Fhまでの任意の値に設定できます。これらのビットを適切に設定して、最大4個までのAD9884Aを同一のシリアル・バスで使用できます。バス上で他のデバイスとの競合が発生した場合にも、これらのビットを使ってAD9884Aのアドレスを変更できます。                                                                                                                                                                                                                                                                                                      |

| PWRDN                           | パワーダウン制御入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 | このピンをローにすることにより、AD9884Aの消費電力を極めて小さくできます。出力バッファは高インピーダンス状態になります。クロック・ジェネレータは停止します。制御レジスタの内容は保持されます。Greenスライサ（SOGOUT）と内部リファレンスは動作を続行します。                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# AD9884A

## ピン機能説明（続き）

| ピン名                  | 機能                                                                                                                                                                                                                                                 |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>アナログ・インターフェース</b> |                                                                                                                                                                                                                                                    |

| REFOUT               | 内部リファレンス出力<br>内部1.25Vバンドギャップ・リファレンスの出力です。この出力は比較的軽い負荷を想定しています。AD9884Aのリファレンス入力は直接ドライブできますが、他の負荷をドライブする場合には、外部のバッファが必要です。この出力の絶対精度は±4%、温度係数は±50ppmなので、AD9884Aの殆どのアプリケーションには十分です。より高精度が必要な場合には、外部リファレンスを使用できます。その場合、このピンを0.1uFのコンデンサを介してグラウンドに接続します。 |

| REFIN                | リファレンス入力<br>リファレンス入力は、AD9884Aのすべての内部回路へのマスター・リファレンス（1.25V ± 10%）を受け入れます。このピンは、REFOUTピンによって直接ドライブできます。このピンは高インピーダンスなので、リファレンスのソース側への負荷が非常に軽くなります。このピンは、0.1uFのコンデンサによってグラウンドにバイパスする必要があります。                                                          |

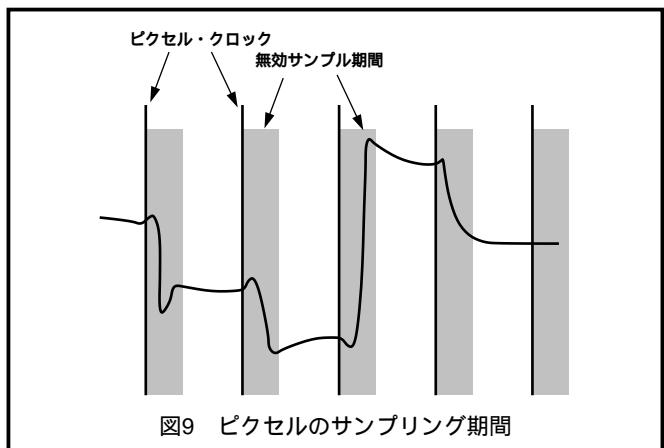

| FILT                 | 外部フィルタ接続です。<br>より適切な動作のためには、ピクセル・クロック・ジェネレータのPLLに外部フィルタが必要です。図10のフィルタをこのピンに接続します。最適な状態で性能を発揮し、ノイズおよびノードの寄生容量を最小化します。                                                                                                                               |

| <b>電源</b>            | 主電源<br>回路の主要部品に電源を供給します。供給される電圧はできる限り変動が少なく、フィルタ処理されていることが望されます。                                                                                                                                                                                   |

| V <sub>D</sub>       | デジタル出力電源<br>多くの出力ピン（最大52）が高速で（最高140MHz）スイッチング動作をすることによって、電源に大きな過渡波形（ノイズ）が現れます。これらの電源ピンはV <sub>D</sub> ピンから離して、敏感なアナログ回路に出力ノイズが伝播されないよう、細心の注意を払う必要があります。AD9884Aを低電圧のロジックにインターフェースする場合には、互換性の確保のためV <sub>DD</sub> を低い電圧電源（最低2.5V）に接続できます。            |

| PVD                  | クロック・ジェネレータ電源<br>AD9884Aにおいて最も敏感な部分はクロック生成回路です。これらのピンはクロックPLLに電源を供給し、最適な動作設計を可能とします。設計にあたっては、これらのピンにできる限り変動やノイズのない“安定した”電源を供給する必要があります。                                                                                                            |

| GND                  | グラウンド<br>チップ上のすべての回路に対するグラウンド<br>AD9884Aは、単一の一体化されたグラウンド・プレーンの上に、グラウンドの電流経路に注意を払って配置することを推奨します。詳細は設計ガイドを参照してください。                                                                                                                                  |

**制御レジスタ・マップ**

AD9884Aは、動作モードを決定する一連のレジスタによって、初期化され制御されます。コントロール・レジスタは、外部コントローラから2線式シリアル・インターフェース・ポート経由で読み出し／書き込みできます。

**表II 制御レジスタ・マップ**

| レジスタ                 | ビット | デフォルト値    | 記号       | 機能                 |

|----------------------|-----|-----------|----------|--------------------|

| <b>PLL ドライバ制御</b>    |     |           |          |                    |

| 00                   | 7-0 | 01101001  | PLLDIVM  | PLL分割比MSB          |

| 01                   | 7-4 | 1101****  | PLLDIVL  | PLL分割比LSB          |

| 01                   | 3-0 | *****0000 |          | 予約済み、0に設定          |

| <b>入力ゲイン</b>         |     |           |          |                    |

| 02                   | 7-0 | 10000000  | REDGAIN  | Redチャンネル・ゲイン調整     |

| 03                   | 7-0 | 10000000  | GRNGAIN  | Greenチャンネル・ゲイン調整   |

| 04                   | 7-0 | 10000000  | BLUGAIN  | Blueチャンネル・ゲイン調整    |

| <b>入力オフセット</b>       |     |           |          |                    |

| 05                   | 7-2 | 100000**  | REDOFST  | Redチャンネル・オフセット調整   |

| 05                   | 1-0 | *****00   |          | 予約済み、0に設定          |

| 06                   | 7-2 | 100000**  | GRNOFST  | Greenチャンネル・オフセット調整 |

| 06                   | 1-0 | *****00   |          | 予約済み、0に設定          |

| 07                   | 7-2 | 100000**  | BLUOFST  | Blueチャンネル・オフセット調整  |

| 07                   | 1-0 | *****00   |          | 予約済み、0に設定          |

| <b>クランプ・タイミング</b>    |     |           |          |                    |

| 08                   | 7-0 | 10000000  | CLPLACE  | クランプ配置             |

| 09                   | 7-0 | 10000000  | CLDUR    | クランプ期間             |

| <b>一般制御1</b>         |     |           |          |                    |

| 0A                   | 7   | 1*****    | DEMUX    | 出力ポート選択            |

| 0A                   | 6   | *1*****   | PAR      | 出力タイミング選択          |

| 0A                   | 5   | **1*****  | HSPOL    | H SYNC極性           |

| 0A                   | 4   | ***1***** | CSTPOL   | COAST極性            |

| 0A                   | 3   | ****0***  | EXTCLMP  | クランプ信号ソース          |

| 0A                   | 2   | *****1**  | CLAPOL   | クランプ信号極性           |

| 0A                   | 1   | *****0*   | EXTCLK   | 外部クロック             |

| 0A                   | 0   | *****0    |          | 予約済み、0に設定          |

| <b>クロック・ジェネレータ制御</b> |     |           |          |                    |

| 0B                   | 7-3 | 10000***  | PHASE    | クロック位相調整           |

| 0B                   | 2-0 | *****000  |          | 予約済み、0に設定          |

| 0C                   | 7   | 0*****    |          | 予約済み、0に設定          |

| 0C                   | 6-5 | *01*****  | VCORNGE  | VCO範囲選択            |

| 0C                   | 4-2 | ***001**  | CURRENT  | チャージポンプ電流          |

| 0C                   | 1-0 | *****00   |          | 予約済み、0に設定          |

| <b>一般制御2</b>         |     |           |          |                    |

| 0D                   | 7-5 | 000*****  |          | 予約済み、0に設定          |

| 0D                   | 4   | ***0****  | OUTPHASE | 出力ポート位相            |

| 0D                   | 3-1 | ****000*  | REVID    | ダイ・レビジョン番号         |

| 0D                   | 0   | *****0    |          | 予約済み、0に設定          |

| 0E                   | 7-0 | 00000000  |          | 予約済み、0に設定          |

**表III レジスタ・デフォルト値**

| レジスタ | 値        | レジスタ | 値  |

|------|----------|------|----|

| 00   | 01101001 | 69h  | 08 |

| 01   | 11010000 | D0h  | 09 |

| 02   | 10000000 | 80h  | 0A |

| 03   | 10000000 | 80h  | 0B |

| 04   | 10000000 | 80h  | 0C |

| 05   | 10000000 | 80h  | 0D |

| 06   | 10000000 | 80h  | 0E |

| 07   | 10000000 | 80h  | 0F |

**制御レジスタ詳細****PLL ドライバ制御**

|    |     |         |           |

|----|-----|---------|-----------|

| 00 | 7-0 | PLLDIVM | PLL分割比MSB |

|----|-----|---------|-----------|

12ビットPLLの分割比PLLDIVのうちのMSB8ビット。動作時における分割比はPLLDIV+1となります。

PLLは、入力されたH SYNC信号からマスター・クロックを生成します。次にマスター・クロックの周波数は整数値で分割されて、分割器の出力がH SYNCに対して位相ロックされます。このPLLDIVの値によって、ラインあたりのピクセル数（ピクセル+プランギングのオーバーヘッド部分）が決定されます。これは、ディスプレイの中に表示されるアクティブなピクセルの数より通常20~30%大きな値となります。

PLLDIVの12ビットの値は、2~4095の分割比をサポートしています。レジスタにロードされる値が大きくなると、生成されるクロックの周波数は固定のH SYNC周波数に比例して高くなります。

VESAは、いくつかの標準的なタイミングの仕様を確立しており、PLLDIVの値を、ディスプレイの水平／垂直の表示解像度、およびフレーム・レートして求める場合に役立ちます（表VII）。しかし、VESA勧告に正確に準拠していないコンピュータ・システムが多いので、これらの数値は参考として利用すべきです。ディスプレイ・システムのメーカーは、PLLDIVの値を最適化するために、自動またはマニュアル操作の手段を提供することが期待されます。PLLDIVの設定を誤ると、大概1本または何本かの垂直なバー状ノイズがディスプレイに現れます。誤差が大きくなると、現れるバーの数が増えます。

PLLDIVのパワーアップ時のデフォルト値は1693（PLLDIVM = 69h、PLLDIVL = Dxh）です。

|    |     |         |           |

|----|-----|---------|-----------|

| 01 | 7-4 | PLLDIVL | PLL分割比LSB |

|----|-----|---------|-----------|

12ビットPLLの分割比PLLDIVのうちのLSB4ビット。動作時における分割比はPLLDIV+1となります。PLLDIVのパワーアップ時のデフォルト値は1693（PLLDIVM = 69h、PLLDIVL = Dxh）です。

# AD9884A

## 入力ゲイン

|    |     |         |                |

|----|-----|---------|----------------|

| 02 | 7-0 | REDGAIN | Redチャンネル・ゲイン調整 |

|----|-----|---------|----------------|

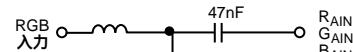

REDチャンネルのゲインを設定する8ビットのワード。AD9884Aは、0.5~1.0Vp-p間のフルスケール・レンジでの入力信号が可能です。REDGAIN = 255に設定すると、入力レンジは1.0Vとなります。REDGAIN = 0では入力レンジは0.5Vになります。REDGAINを増加させると画像のコントラストが低下することにご注意ください（入力信号の利用可能なコンバータのコードが少なくなります）。図8を参照してください。

パワーアップ時のREDGAINのデフォルト値は80hです。

|    |     |         |                  |

|----|-----|---------|------------------|

| 03 | 7-0 | GRNGAIN | Greenチャンネル・ゲイン調整 |

|----|-----|---------|------------------|

GREENチャンネルのゲインを設定する8ビットのワード。REDGAIN ( 02 ) の項を参照してください。

パワーアップ時のGRNGAINのデフォルト値は80hです。

|    |     |        |                 |

|----|-----|--------|-----------------|

| 04 | 7-0 | BLUGAN | Blueチャンネル・ゲイン調整 |

|----|-----|--------|-----------------|

BLUEチャンネルのゲインを設定する8ビットのワード。

REDGAIN ( 02 ) の項を参照してください。

パワーアップ時のBLUGANのデフォルト値は80hです。

## 入力オフセット

|    |     |         |                  |

|----|-----|---------|------------------|

| 05 | 7-2 | REDOFST | Redチャンネル・オフセット調整 |

|----|-----|---------|------------------|

REDチャンネルのDCオフセットを設定する、6ビットのオフセット・バイナリ・ワード。オフセット調整の1つの LSB は、A/Dコンバータのオフセットの LSB とほぼ等しくなります。このため、オフセット調整の大きさの絶対値は、チャンネルのゲインの変化に比例します（図9参照）。公称値の31を設定すると、バック・ポーチが（クランプ・インターバルの間）コード00にクランプされます。オフセットを63に設定すると、チャンネルはA/Dコンバータのコード31にクランプされます。オフセットを0に設定すると、コード - 31にクランプされます（範囲の最低限度を下回る）。REDOFSTの値を増加させると、チャンネルの輝度が低下します。

パワーアップ時のREDOFSTのデフォルト値は80hです。

|    |     |         |                    |

|----|-----|---------|--------------------|

| 06 | 7-2 | GRNOFST | Greenチャンネル・オフセット調整 |

|----|-----|---------|--------------------|

GREENチャンネルのDCオフセットを設定する、6ビットのオフセット・バイナリ・ワード。REDOFST ( 05 ) の項を参照してください。

パワーアップ時のGRNOFSTのデフォルト値は80hです。

|    |     |        |                   |

|----|-----|--------|-------------------|

| 07 | 7-2 | BLUOFS | Blueチャンネル・オフセット調整 |

|----|-----|--------|-------------------|

BLUEチャンネルのDCオフセットを設定する、6ビットのオフセット・バイナリ・ワード。REDOFST ( 05 ) の項を参照してください。

パワーアップ時のBLUOFSのデフォルト値は80hです。

## クランプ・タイミング

|    |     |         |        |

|----|-----|---------|--------|

| 08 | 7-0 | CLPLACE | クランプ位置 |

|----|-----|---------|--------|

内部で生成されるクランプの位置を設定する、8ビットのレジスタ。

EXTCLMP = 0の場合、クランプ信号はCLPLACEで指定された位置に、CLDURで指定された期間にわたり内部生成されます。HSYNCの立ち下りエッジからCLPLACEピクセル周期経過後に、クランプ動作が開始されます。CLPLACEの値は、1~255の任意の値に設定できます。CLPLACE = 0はサポートされていません。

クランプは、入力信号に安定した黒レベルのリファレンスがある間に行う必要があります。通常はHSYNCと画像のバック・ポーチ期間に行われます。通常、08hの値が有効です。EXTCLMP = 1の場合には、このレジスタは無視されます。パワーアップ時のCLPLACEのデフォルト値は80hです。

|    |     |       |        |

|----|-----|-------|--------|

| 09 | 7-0 | CLDUR | クランプ期間 |

|----|-----|-------|--------|

内部で生成されるクランプの期間を設定する、8ビットのレジスタ。

EXTCLP = 0の場合、クランプ信号はCLPLACEで指定された位置に、CLDURで指定された期間にわたり内部生成されます。HSYNCの立ち下りエッジからCLPLACEピクセル周期経過後にクランプ動作が開始され、CLDURピクセル周期にわたって継続します。CLDURの値は、1~255の任意の値に設定できます。CLDUR = 0はサポートされていません。

最良の結果を得るために、HSYNC信号の立ち下りエッジの後の黒リファレンス信号の期間の大部分を占めるように、クランプの期間を設定する必要があります。クランプの期間が十分でないと、画面の上端で輝度の変化が現れ、平均画像レベル（Average Picture Level, APL）や輝度の大幅な変動からの復帰が遅くなります。標準的な信号の大部分は、10~20hの値が有効です。

EXTCLMP = 1の場合には、このレジスタは無視されます。パワーアップ時のCLDURのデフォルト値は80hです。

**一般制御**

|     |   |       |         |

|-----|---|-------|---------|

| 0 A | 7 | DEMUX | 出力ポート選択 |

|-----|---|-------|---------|

すべてのピクセルをシングル・ポート(A)に出力するか、ピクセルを交互にポートAとポートBにディマルチブレックスして出力するかを決定するビット。

| DEMUX | 機能                        |

|-------|---------------------------|

| 0     | すべてのデータがポートAに出力されます。      |

| 1     | ピクセルがポートAとポートBに交互に出力されます。 |

DEMUX=0の場合、ポートBの出力は高インピーダンス状態となります。パワーアップ時のDEMUXの値は1です。

|     |   |          |           |

|-----|---|----------|-----------|

| 0 A | 6 | PARALLEL | 出力タイミング選択 |

|-----|---|----------|-----------|

このビットをロジック・レベル=1に設定すると、ポートAのデータとDATAACK出力を、DATAACK周期の2分の1だけ遅延させてDATAACKの立ち上がりエッジにより、ポートA / B両方からのデータを外部的にラッチすることができます。このビットがロジック・レベルの0に設定されている場合には、DATAACKの立ち上がりエッジによりポートAからのデータのみを外部でラッチでき、DATAACKの立ち上がりエッジによりポートBからのデータを外部でラッチできます。

| PARALLEL | 機能                            |

|----------|-------------------------------|

| 0        | データは各ポートに交互に出力されます。           |

| 1        | 1つおきのDATAACKに対してデータが同期出力されます。 |

シングル・ポート・モード(DEMUX=0)では、このビットは無視されます。

パワーアップ時のPARALLELの値は1です。

|     |   |       |         |

|-----|---|-------|---------|

| 0 A | 5 | HSPOL | HSYNC極性 |

|-----|---|-------|---------|

HSYNC入力に与えられるHSYNC信号の極性を指定するビット。

| HSPOL | 機能       |

|-------|----------|

| 0     | アクティブ・ロー |

| 1     | アクティブ・ハイ |

アクティブ・ローは、通常のネガティブで有効となるHSYNCパルスです。

サンプリングのタイミングはHSYNCのリーディング・エッジであり、この場合立ち下りエッジです。

CLPLACEで指定されるクランプ位置は、立ち下りのエッジを基準としています。

アクティブ・ハイは、通常のHSYNCを反転したものであり、ポジティブで有効となります。これは、HSYNCの立ち上がりエッジを基準としてサンプリングのタイミングが決定されることを意味し、ここでは立ち上がりエッジが基準となり、クランプ位置は立ち下りエッジを基準として決定されます。

このビットの設定が誤っていても、AD9884Aは一応動作はしますが、CLPOSで指定され内部で生成されるクランプが意図した位置に配置されないため、クランプのエラーが発生する場合があります。

パワーアップ時のHSPOLのデフォルト値は1です。

|     |   |        |         |

|-----|---|--------|---------|

| 0 A | 4 | CSTPOL | COAST極性 |

|-----|---|--------|---------|

COAST入力に与えられるCOAST信号の極性を指定するためのビット

| CSTPOL | 機能       |

|--------|----------|

| 0      | アクティブ・ロー |

| 1      | アクティブ・ハイ |

アクティブ・ローは、COASTがローのときにクロック・ジェネレータがHSYNCを無視して、COASTがハイとなるまでの間、同一の公称周波数で動作を続行することを意味します。

アクティブ・ハイは、COASTがハイのときにクロック・ジェネレータがHSYNCを無視して、COASTがローとなるまでの間、同一の公称周波数で動作を続行することを意味します。

パワーアップ時のCSTPOLの値は1です。

|     |   |        |           |

|-----|---|--------|-----------|

| 0 A | 3 | EXTCLP | クランプ信号ソース |

|-----|---|--------|-----------|

クランプ・タイミングのソースを指定するためのビット。

| EXTCLMP | 機能              |

|---------|-----------------|

| 0       | 内部生成されたクランプ     |

| 1       | 外部から供給されたクランプ信号 |

0に設定し、CLPLACEとCLDURが制御するクランプ・タイミング回路がイネーブルになります。クランプの位置と期間は、HSYNCの立ち下りエッジからカウントされます。

1に設定し、外部のCLAMP入力ピンがイネーブルになります。CLAMP信号のアクティブ時には、3つのチャンネルがクランプされます。CLAMPの極性はCLAMPOLビットによって指定されます。

パワーアップ時のEXTCLMPのデフォルト値は0です。

|     |   |         |          |

|-----|---|---------|----------|

| 0 A | 2 | CLAMPOL | クランプ信号極性 |

|-----|---|---------|----------|

外部から供給されるCLAMP信号の極性を指定するためのビット。

| CLAMPOL | 機能       |

|---------|----------|

| 0       | アクティブ・ハイ |

| 1       | アクティブ・ロー |

CLAMPOL=0では、CLAMPがハイのときにクランプ回路がクランプを行い、CLAMPがローのときは信号がA/Dコンバータに印可されます。

CLAMPOL=1では、CLAMPがローのときにクランプ回路がクランプを行い、CLAMPがハイのときは信号がA/Dコンバータに印可されます。

パワーアップ時のCLAMPOLのデフォルト値は1です。

|     |   |        |          |

|-----|---|--------|----------|

| 0 A | 1 | EXTCLK | 外部クロック選択 |

|-----|---|--------|----------|

ピクセル・クロックのソースを指定するためのビット。

| EXTCLK | 機能            |

|--------|---------------|

| 0      | 内部生成されたクロック   |

| 1      | 外部から供給されたクロック |

EXTCLK=0で、外部から供給されるHSYNCからピクセル・クロックを生成する内部PLLをイネーブルにします。

EXTCLK=1で、CKEXT入力ピンをイネーブルにします。このモードでは、PLL分割比(PLLDIV)は無視されます。クロック位相調整(PHASE)は動作状態を保ちます。

パワーアップ時のEXTCLKのデフォルト値は0です。

# AD9884A

## クロック・ジェネレータ制御

|    |     |       |          |

|----|-----|-------|----------|

| 0B | 7-3 | PHASE | クロック位相調整 |

|----|-----|-------|----------|

1ピクセル期間を32に分割したステップでサンプリングの位相を調整する、5つのビット。各ステップは、サンプリング位相での11.25度のシフトに相当します。

パワーアップ時のPHASEのデフォルト値は16です。

|    |     |         |         |

|----|-----|---------|---------|

| 0C | 6-5 | VCORNGE | VCO範囲選択 |

|----|-----|---------|---------|

| VCORNGE | レンジ (MHz) |

|---------|-----------|

| 00      | 20 ~ 60   |

| 01      | 50 ~ 90   |

| 10      | 80 ~ 120  |

| 11      | 110 ~ 140 |

VCORNGEは、意図する動作周波数（入力ピクセル・レート）に対応するように設定する必要があります。

パワーアップ時のVCORNGEのデフォルト値は01です。

|    |     |         |           |

|----|-----|---------|-----------|

| 0C | 4-2 | CURRENT | チャージポンプ電流 |

|----|-----|---------|-----------|

この3つのビットが、クロック・ジェネレータのループ・フィルタをドライブする電流値を指定します。

| CURRENT | 電流 (μA) |

|---------|---------|

| 000     | 50      |

| 001     | 100     |

| 010     | 150     |

| 011     | 250     |

| 100     | 350     |

| 101     | 500     |

| 110     | 750     |

| 111     | 1500    |

CURRENTは、意図する動作周波数（入力ピクセル・レート）に対応するように設定する必要があります。

パワーアップ時のCURRENTのデフォルト値は001です。

|    |   |          |         |

|----|---|----------|---------|

| 0D | 4 | OUTPHASE | 出力ポート位相 |

|----|---|----------|---------|

偶数ピクセル、奇数ピクセルのどちらがポートAに出力されるかを指定するビットです。

| OUTPHASE | HSYNC後の最初のピクセル |

|----------|----------------|

| 0        | ポートA           |

| 1        | ポートB           |

通常の動作（OUTPHASE = 0）では、デュアル・チャンネル出力ポート・モード（DEMUX = 1）で動作しているときに、HSYNCの立ち上がりエッジ後の最初のサンプルがポートAに出力されます。以下、奇数サンプルはポートAに出力され、偶数サンプルは、すべてポートBに出力されます。

OUTPHASE = 1 の場合には、ポートの関係が逆転し、最初のサンプルがポートBに出力されます。

DEMUX = 0の場合には、このビットは無視されます。

OUTPHASEの読み出しは、レジスタ0Dのビット7で行います。

|    |     |       |              |

|----|-----|-------|--------------|

| 0D | 3-1 | REVID | シリコン・リビジョン番号 |

|----|-----|-------|--------------|

この3つのビットを読み込むこめば、AD9884Aのダイのリビジョン番号が分かれます。

## シリアル制御ポート

2線式シリアル制御インターフェースを備えています。最大4個までのAD9884Aを2線式シリアル・インターフェースに接続でき、各デバイスが固有のアドレスを持ちます。

2線式インターフェースは、クロック（SCL）と双方向データ（SDA）ピンで構成されます。アナログ・フラット・パネル・インターフェースは、シリアル・インターフェースを介したデータの送受信において、スレーブとして動作します。シリアル・インターフェースがアクティブでない場合、SCLとSDAのロジック・レベルは、外部プルアップ抵抗によってハイにプルアップされます。

SDAライン経由で送受信されるデータは、SCLパルスのポジティブ有効期間内で安定している必要があります。SDAのデータは、SCLがローのときにのみ変化します。SCLがハイのときにSDAの状態が変化すると、シリアル・インターフェースはその変化を、シーケンスの開始または停止として扱います。

シリアル・バスの動作には、5つの要素があります。

### 開始信号

スレーブ・アドレス・バイト

ベース・レジスタ・アドレス・バイト

書き込み / 読み出しデータ・バイト

### 停止信号

シリアル・インターフェースがアクティブでないとき（SCLとSDAがハイ）には、スタート信号の送出によって通信が開始されます。SCLがハイのときの、SDAのハイからローへの変化がスタート信号となります。この信号が、すべてのスレーブ状態のデバイスに転送シーケンスの開始を予告します。

スタート信号後に転送されるデータの最初の8ビットは、7ビットのスレーブ・アドレス（最初の7ビット）と、1つのR/Wビット（8番目のビット）によって構成されます。R/Wビットはデータ転送の方向を指定し、スレーブのデバイスに対する読み出し（1）書き込み（0）を示します。送信されたスレーブのアドレスがデバイスのアドレス（表IVのSA<sub>1-0</sub>ビットにより設定）と一致すると、AD9884Aは9番目のSCLパルスでSDAをローとして認証します。アドレスが一致しない場合には、AD9884Aは認証を発行しません。

表IV シリアル・ポート・アドレス

| ビット7                 | ビット6           | ビット5           | ビット4           | ビット3           | ビット2           | ビット1                 | ビット0 |

|----------------------|----------------|----------------|----------------|----------------|----------------|----------------------|------|

| A <sub>6</sub> (MSB) | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> (LSB) | R/W  |

| 1                    | 0              | 0              | 1              | 1              | 0              | 0                    |      |

| 1                    | 0              | 0              | 1              | 1              | 0              | 1                    |      |

| 1                    | 0              | 0              | 1              | 1              | 1              | 0                    |      |

| 1                    | 0              | 0              | 1              | 1              | 1              | 1                    |      |

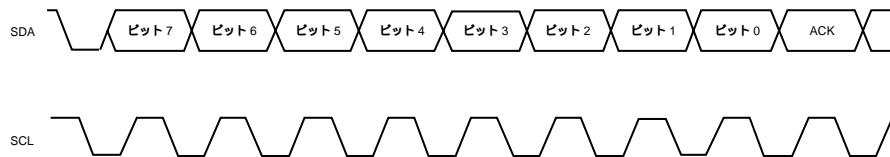

## シリアル・インターフェース経由のデータ転送

読み出し、書き込みデータの各バイトについて、MSBが最初のシーケンスになります。

書き込みシーケンスでAD9884Aがマスター・デバイスへの認証を発行しない場合には、SDAはハイのままとなり、マスターがストップ信号を生成できます。読み取りシーケンスでマスター・デバイスがAD9884Aへの認証を発行しない場合には、AD9884AIは、これを「データの終わり」として解釈します。SDAがハイのままで、マスターが停止信号を生成できます。

AD9884Aの特定の制御レジスタに書き込みを行うためには、スレーブのアドレスが確定した後に、対象の制御レジスタの8ビット・アドレスに書き込む必要があります。この制御レジスタのアドレスが、次の書き込み動作のベース・アドレスになります。

ベース・アドレスは、ベース・アドレスに対して指定されたデータ・バイトが1バイト書き込まれるたびに自動的に1つずつ増加します。利用可能なアドレス領域を超えるバイト数が転送された場合、アドレスは自動的に増加せず、最大値である0Ehのままであります。0Ehを超えるベース・アドレスにへは、認証が発行されません。

データは、AD844Aの制御レジスタから同様の手順によって読み出されます。読み出し動作には、2つの転送動作が必要です。

ベース・アドレスは、スレーブ・アドレス・バイトのR/Wビットをローとして書き込み、シーケンスに応じた読み込み動作を設定する必要があります。

読み込み動作(スレーブ・アドレス・バイトのR/Wビットがハイの状態)は、それまでに設定されたベース・アドレスから開始します。各バイトが転送された後に、読み出しの行われたレジスタのアドレスが自動的に増加されます。

AD9884AIに対する読み出し / 書き込みシーケンスを終了するには、停止信号を出力する必要があります。停止信号は、SCLがハイの状態のときに、SDAがローからハイに変化して生成されます。

シリアル・インターフェースを駆動しているマスター・デバイスが、現状の通信を終了させる停止信号を先に生成することなしにスタート信号を生成することにより、連続したスタート信号の生成が可能です。この手法は、シリアル・インターフェース・ラインを開放することなく、スレーブ / マスター間での通信モード(読み出し / 書き込み)を変更するために使用されます。

## シリアル・インターフェースにおける読み出し / 書き込みの例

### 1つの制御レジスタへの書き込み

開始信号

スレーブ・アドレス・バイト (R/Wビットはロー)

ベース・アドレス・バイト

ベース・アドレスへのデータ・バイト

停止信号

### 4つの連続する制御レジスタへの書き込み

開始信号

スレーブ・アドレス・バイト (R/Wビットはロー)

ベース・アドレス・バイト

ベース・アドレスへのデータ・バイト

(ベース・アドレス + 1)へのデータ・バイト

(ベース・アドレス + 2)へのデータ・バイト

(ベース・アドレス + 3)へのデータ・バイト

停止信号

### 1つの制御レジスタからの読み出し

開始信号

スレーブ・アドレス・バイト (R/Wビットはロー)

ベース・アドレス・バイト

開始信号

スレーブ・アドレス・バイト (R/Wビットはハイ)

ベース・アドレスからのデータ・バイト

停止信号

### 4つの連続する制御レジスタからの読み出し

開始信号

スレーブ・アドレス・バイト (R/Wビットはロー)

ベース・アドレス・バイト

開始信号

スレーブ・アドレス・バイト (R/Wビットはハイ)

ベース・アドレスからのデータ・バイト

(ベース・アドレス + 1)からのデータ・バイト

(ベース・アドレス + 2)からのデータ・バイト

(ベース・アドレス + 3)からのデータ・バイト

停止信号

図1 シリアル・ポートの読み出し / 書き込みタイミング

図2 シリアル・インターフェースの典型的なバイト転送

# AD9884A

図3 消費電力 対 周波数

## 設計ガイド

### 概要

AD9884Aは、アナログRGB信号をキャプチャし、デジタル化してフラット・パネル・ディスプレイやプロジェクタで表示するための、完全に集積化されたソリューションです。HDTVモニター用のコンピュータ・インターフェースを提供し、高性能のビデオ・スキャン・コンバータのフロント・エンドの構成にも理想的です。

高性能なCMOSプロセスによって構成されており、AD9884Aのインターフェースは、ピクセル・レート最大140メガ・ピクセル / 秒 (Mpps) 交互ピクセル・サンプリング・モードでは最大280Mppsの信号をキャプチャできます。

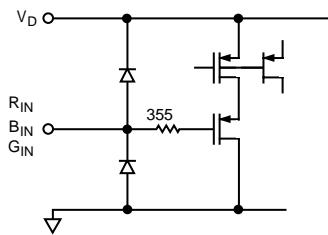

図4 等価アナログ入力回路

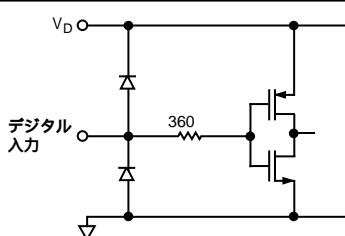

図5 等価デジタル入力回路

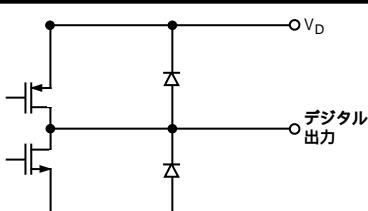

図6 等価デジタル出力回路

AD9884Aは、必要なすべての入力バッファ、信号DC復帰(クランプ)、オフセット / ゲイン調整(輝度とコントラスト)、ピクセル・クロック生成、サンプリング位相制御、出力データ・フォーマットを備えています。すべての制御は、2線式シリアル・インターフェース経由でプログラム可能です。これらのノイズに敏感なアナログ機能を集積することによって、システム設計が簡素になり、物理的、電気的環境に対しても、強い耐性を持った設計が可能です。消費電力はわずか570mW typで、動作温度範囲は0 ~ 70°C、従って、動作環境への特別な配慮も不要です。

### 入力信号の処理

#### アナログ入力

AD9884Aは、red、green、blueの各チャンネルに対する高インピーダンスのアナログ入力ピン3本を備え、0.5 ~ 1.0Vp-pの信号入力が可能です。

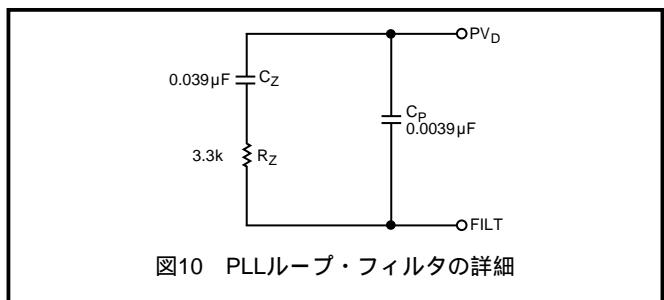

信号は、通常、15ピンのDコネクタ、VESA P&Dコネクタ、DDWG DVIコネクタ、BNCコネクタ経由でインターフェース・ボードに入力されます。AD9884Aは、できる限り入力コネクタの近くに配置する必要があります。信号は、インピーダンスがマッチした経路(通常75Ω)でICの入力ピンに接続する必要があります。

この接続点で、信号を抵抗によって終端(信号グラウンド帰還)に対して75Ωにし、AD9884Aの入力に対して、47nFのコンデンサを使って容量カップリングする必要があります。これらのコンデンサはDC帰還回路の一部を構成します。

インピーダンス・マッチングが完全な状態なら、最大限の信号帯域幅で最大限の性能を引き出せます。AD9884Aの帯域幅は非常に広い(500MHz)ので、入力信号をピクセル毎に連続的に捕捉でき、長く安定したピクセル周期でピクセルのデジタル化が可能です。しかし、多くのシステムで、インピーダンスのミスマッチ、反射、ノイズなどの要因により、入力波形に過大なリンクギングと歪みが見られます。これにより、高画質を得るために必要なサンプリング位相を維持することが一層難しくなります。小さなインダクタを入力と直列に挿入して、入力帯域幅をわずかに丸め込み、より広い条件下で高品質の信号が得られることが知られています。図7のように、Fair-Rite社の高速信号チップ・ビーズ#2508051217Z0を採用すれば、ほとんどのアプリケーションで良い結果が得られるでしょう。

図7 アナログ・入力インターフェース回路

#### HSYNC、VSYNC入力

インターフェースでは、ピクセル・クロックとクランプのタイミングを生成するために、水平同期信号を扱います。HSYNCを供給せずに(外部クロック、外部クランプ、シングル・ポート出力モードを使って)AD9884Aを動作させることも可能ですが、利用できなくなる機能があるので、HSYNCを供給することをお勧めします。これは、グラフィックのソースから直接入力した同期信号でも、TTLやCMOSレベルの前処理を経た信号であっても構いません。

H SYNC入力はシュミット・トリガ・バッファを備えており、ノイズ耐性を確保すると共に、立ち上がり時間の長い信号の取り扱いも可能にします。

一般的なPCベースの映像システムでは、TTLレベルのドライバが同期信号をモニター・ケーブルのシールドのない導線に伝送するだけです。AD9884Aは、3.3V電源から動作し、TTLのソースが

5Vの高レベルをドライブするため、H SYNCとCOASTピンと直列に1kΩの電流制限抵抗を設置することを推奨します。これらのピンが電源電圧範囲から0.5Vを超える電圧でドライブされる場合には、内部のESD保護ダイオードが導通し、同期信号源のインピーダンスが特に低くなると、消費電力が非常に高くなります。ICの電源がオフの状態では、1Vの信号でもESD保護ダイオードが導通します。この場合でも、1kΩの抵抗を設置すれば、デバイスを過度のストレスから保護できます。

### シリアル制御ポート

シリアル制御ポート( SDA、SCL )は、3Vのロジックに対応して設計されています。バス上に5Vのドライバがある場合には、これらのピンを保護する150Ωの抵抗を直列に接続する必要があります。

### 出力信号の取り扱い

デジタル出力は、3.3V電源( V<sub>DD</sub> )から動作するように設計されていますが、他の2.5Vロジックとの互換性を確保するために、最低2.5VのV<sub>DD</sub>でも動作可能です。

### クランプ処理

入力信号の適切なデジタル化のために、入力信号のDCオフセットを、ボード上のA/Dコンバータの電圧範囲に調整する必要があります。

多くのグラフィック・システムでは、RGB信号の黒をグラウンドに、白を約+0.75Vに設定します。しかし、同期信号が映像信号の中に埋め込まれている場合には、同期信号の先端がグラウンドで、黒が+300mVになっていることがあります。この場合には、白は約+1.0Vとなります。いくつかの一般的なRGBラインのアンプでは、信号の分離とドライブ能力の向上のために、エミッタ・フォロワによるバッファを用いています。この場合には、700mVのDCオフセットが加えられているため、AD9884Aでのキャップチャを適切に行うために、このオフセットを除去する必要があります。

クランプ処理で重要なのは、グラフィック・システムが黒信号を発生する信号の分量( 時間 )を特定することです。これにより、オフセットを含んだ黒入力が存在すると分かっているときにA/Dコンバータから黒出力( コード00h )を出力させることができます。このオフセットは他の信号レベルのプロセスでも加えられ、信号全体をシフトしてオフセット誤差を除去することができます。

多くのグラフィック・システムでは、黒はアクティブなビデオ信号ライン間で伝送されます。CRTディスプレイの場合、電子ビームが画面上に1本の水平走査線を描き終えると( 画面の右端 )、ビームは素早く画面の左端に偏向されて( 水平回帰動作 )ビームによる画像への妨害を防止するために黒信号が生成されます。

同期信号が組み込まれたシステムでは、「黒信号よりも黒い信号( 黒信号よりも低電圧の信号 )( H SYNC )がごく短い期間だけ生成されて、CRTに再走査のタイミングを伝えます。これで分かると

おり、H SYNCの先端をクランプしてはいけません。幸い、ほとんどすべてのシステムにおいて、H SYNCの後で、良質な黒リファレンスが得られるバック・ポーチという部分が存在します。ここでクランプの処理が行えます。

クランプのタイミングは、CLAMPピンを適当なタイミングでアクティブにして EXTCLMP=1 確定できます。この信号の極性は、CLAMPOLビットによって設定できます。

より簡単にクランプを行うには、AD9884Aの内部クランプ・タイミング・ジェネレータが使用できます。レジスタCLPLACEは、H SYNCの信号の立ち下りエッジからクランプ動作を開始するまでの時間を、ピクセル周期の数で設定できます。2番目のレジスタ CLDUR )は、クランプの期間を設定します。これらは、両方とも8ビットの値を保持し、極めて柔軟なクランプの生成を可能にします。クランプのタイミングは、H SYNCの立ち下りエッジを基準に決定されます。これは、H SYNCの幅が大きく異なるのに対し、H SYNCの後には必ずバック・ポーチ( 黒リファレンス )が存在するからです。クランプを行うための出発点としては、CLPLACEを08h( グラフィック信号が安定するまでの期間として8ピクセル周期を与えます )に、CLDURを14h( 黒のリファレンスの再獲得のために20ピクセル周期を与えます )に設定します。

クランプは、外部の入力カップリング・コンデンサへの十分な電荷の充電によって行います。このコンデンサの容量が、クランプの特性に影響を与えます。容量が小さすぎると、水平走査の期間内( クランプの間隔内 )に大きな振幅の変動を生じます。容量が大きすぎると、クランプ回路が入力信号のオフセットの大きな変動から回復する時間がかかりすぎます。推奨する容量値では、100mVのステップ誤差から、60HzのSXGA信号の20ピクセル周期のクランプ期間での10本の走査線で、1/2LSB以内に回復することができます。

### ゲインおよびオフセットの制御

AD9884Aは、フルスケール0.5~1.0Vの入力範囲で入力信号を受け入れることができます。このフルスケール範囲は、3つの8ビット・レジスタ REDGAIN、GRNGAIN、BLUGAIN )によって設定します。

ゲイン・レジスタのコードを0に設定すると入力範囲は最小の0.5Vとなり、255は範囲最大の1.0Vに相当します。ゲインの設定値を大きくすると、画像のコントラストが低下することにご注意ください。

オフセット制御によって入力範囲全体がシフトし、画像の輝度が影響を受けます。3つの6ビット・レジスタ REDOFST、GRNOFST、BLUOFST )によって、各チャンネルごとに独立した設定ができます。

オフセット制御の調整範囲は±31LSBです。この範囲は、フルスケール・レンジに接続されているため、入力範囲が2倍になると( 0.5Vから1.0Vに )オフセットのステップも2倍( ステップあたり2mVから4mVに )に拡がります。

図8は、ゲイン制御とオフセット制御が相互に与える影響を表します。

オフセット調整におけるLSBの振幅はフルスケール・レンジに比例するため、フルスケール・レンジの変更に従い、オフセットも変化します。この変化量は、オフセットの設定がスケールの中央付近にあるときに最小となります。オフセットを変更するときは、フルスケール・レンジは影響を受けませんが、フルスケールのレベルは、ゼロ・スケールのレベルと同じ量だけシフトされます。

# AD9884A

図8 ゲインとオフセットの調整

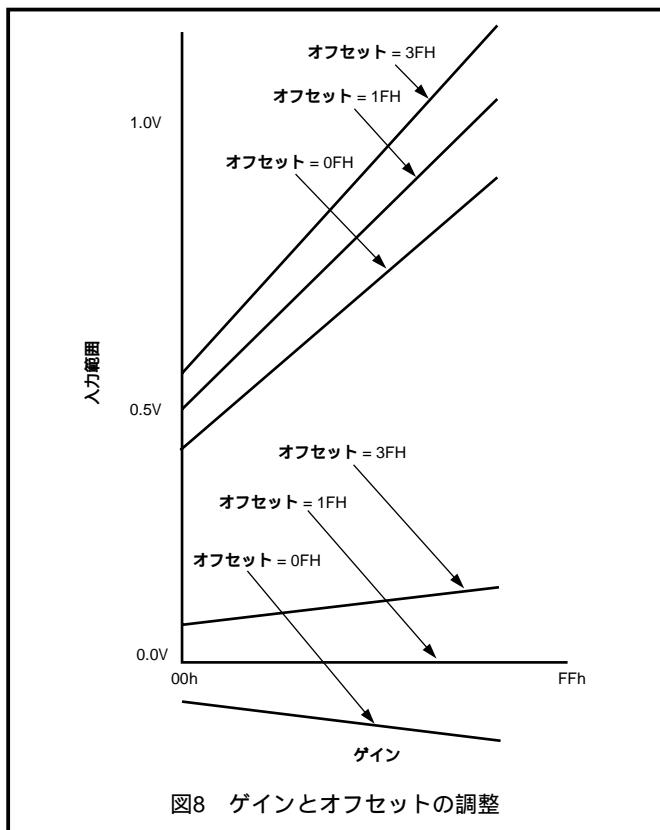

図9 ピクセルのサンプリング期間

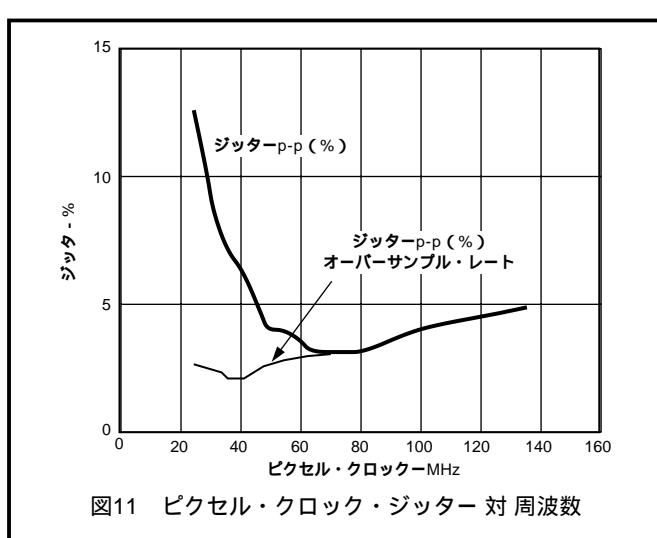

AD9884Aのクロック生成回路は、ジッターを最小限に抑えよう細心の注意を払って設計されています。図11と表VIに示すとおり、AD9884Aのクロック・ジッターは、すべての動作モードでピクセル周期の合計の5%を下回っており、ジッターによる有効なサンプリング期間の減少が殆どありません。

PLLの特性は、ループ・フィルタの設計、PLLのチャージ・ポンプ電流（CURRENT）、VCOの範囲設定（VCORNGE）により決定されます。ループ・フィルタの設計例を図10に示します。VESAの標準ディスプレイ・モードについてのVCORNGEとCURRENTの推奨設定値を表VIIに示します。

表V . VCORNGEから求められる典型的なK<sub>VCO</sub>

| ピクセル・レート  | VCORNGE | K <sub>VCO</sub> (MHz/V) |

|-----------|---------|--------------------------|

| 20 ~ 60   | 00      | 100                      |

| 50 ~ 90   | 01      | 100                      |

| 80 ~ 120  | 10      | 150                      |

| 110 ~ 140 | 11      | 180                      |

図10 PLLループ・フィルタの詳細

## クロック生成

ピクセル・クロックの生成は、フェーズ・ロック・ループ（PLL）が行います。HYSNCが、PLLにリファレンス周波数を供給します。電圧制御オシレータ（VCO）は、さらに高いピクセル・クロック周波数を生成します。このピクセル・クロックは、AD9884AのPLLDIVに設定された値に従って分割されて、HSYNC入力と位相を比較されます。誤差があるとVCO周波数のシフトに使用され、これらの2つの信号間のロックが維持されます。

鮮明で安定した画像の再生のためには、このクロックの安定が非常に重要です。各ピクセル周期の間に、古いピクセルの値は変化して、新しい値でセトリングします。次いで信号が新しい値に変化する前に、入力信号が安定する期間があります（図9参照）。安定している期間に対する変化している期間の比は、グラフィックD/Aコンバータの帯域幅と送信システム（ケーブルと終端）の帯域幅に相關します。また、総合的なピクセル・レートにも相關します。ここで明らかのように、システムのダイナミック特性が一定に保たれる限り、変化およびセトリングの時間も一定に保たれます。この期間をピクセル周期の合計から減算して、安定の期間を算出する必要があります。ピクセル周波数がより高い領域では、サイクル期間の合計値が短くなり、安定のピクセル期間も短くなります。

ピクセル・クロックにジッターが存在すると、サンプリング期間を決定する精度が低下するので、これも安定のピクセル期間から減算する必要があります。

表VII. 標準的なディスプレイ・フォーマット用のVCORNGEとCURRENTの推奨設定値

| 規格   | 解像度         | リフレッシュ・レート | 水平周波数    | ピクセル・レート    | VCORNGE | CURRENT |

|------|-------------|------------|----------|-------------|---------|---------|

| VGA  | 640 × 480   | 60Hz       | 31.5KHZ  | 25.175MHz   | 00      | 000     |

|      |             | 72Hz       | 37.7kHz  | 31.500MHz   | 00      | 000     |

|      |             | 75Hz       | 37.5kHz  | 31.500MHz   | 00      | 000     |

|      |             | 85Hz       | 43.3kHz  | 36.000MHz   | 00      | 001     |

| SVGA | 800 × 600   | 56Hz       | 35.1kHz  | 36.000MHz   | 00      | 001     |

|      |             | 60Hz       | 37.9kHz  | 40.000MHz   | 00      | 001     |

|      |             | 72Hz       | 48.1kHz  | 50.000MHz   | 00      | 010     |

|      |             | 75Hz       | 46.9kHz  | 49.500MHz   | 00      | 001     |

|      |             | 85Hz       | 53.7kHz  | 56.250MHz   | 01      | 010     |

| XGA  | 1024 × 768  | 60Hz       | 48.4kHz  | 65.000MHz   | 01      | 010     |

|      |             | 70Hz       | 56.5kHz  | 75.000MHz   | 01      | 011     |

|      |             | 75Hz       | 60.0kHz  | 78.750MHz   | 01      | 011     |

|      |             | 80Hz       | 64.0kHz  | 85.500MHz   | 10      | 011     |

|      |             | 85Hz       | 68.3kHz  | 94.500MHz   | 10      | 011     |

| SXGA | 1280 × 1024 | 60Hz       | 64.0kHz  | 108.000MHz  | 10      | 011     |

|      |             | 75Hz       | 80.0kHz  | 135.000MHz  | 11      | 100     |

|      |             | 85Hz       | 91.1kHz  | 157.500MHz* | 01      | 100     |

| UXGA | 1600 × 1200 | 60Hz       | 75.0kHz  | 162.000MHz* | 01      | 100     |

|      |             | 65Hz       | 81.3kHz  | 175.500MHz* | 10      | 100     |

|      |             | 70Hz       | 87.5kHz  | 189.000MHz* | 10      | 101     |

|      |             | 75Hz       | 93.8kHz  | 202.500MHz* | 10      | 101     |

|      |             | 85Hz       | 106.3kHz | 229.500MHz* | 10      | 110     |

VESAモニター・タイミング標準とガイドライン、1998年9月17日

\*グラフィックのサンプリングは、交互サンプリング・モードによる1/2入力ピクセル・レート

図11は、AD9884Aのジッターの動作周波数全範囲でのクロック期間の合計に対するパーセンテージです。範囲の大部分にわたって、ジッターが非常に小さく抑えられていますが（ピクセル周期の5%未満）クロック・レートが40MHz以下の領域ではジッターは増加しています。低い周波数では、AD9884Aを意図する周波数の2倍の速度で動作させ、サンプルされたデータを1つあきに使用することにより、ジッターを軽減できます。これは、デバイスをデュアル・チャンネル・モードで動作させ（例：図21参照）、データを出力ポートの一方だけから読み取ることによって簡単に実現できます。DATAACKとDATAACKの出力は、意図した低いサンプル・レートで動作します。

表VI. ピクセル・クロック・ジッター 対 周波数

| ピクセル・レート<br>( MSPS ) | ジッターp-p<br>( ps ) | ジッターp-p<br>( ピクセル周期の%表示 ) |

|----------------------|-------------------|---------------------------|

| 135                  | 350               | 4.7%                      |

| 108                  | 400               | 4.3%                      |

| 94                   | 400               | 3.4%                      |

| 75                   | 450               | 3.4%                      |

| 65                   | 600               | 3.9%                      |

| 50                   | 500*              | 2.4%                      |

| 40                   | 500*              | 2.0%                      |

| 36                   | 550*              | 1.8%                      |

| 25                   | 1000*             | 2.5%                      |

\*AD9884Aはオーバーサンプル・モードです。

# AD9884A

## タイミング

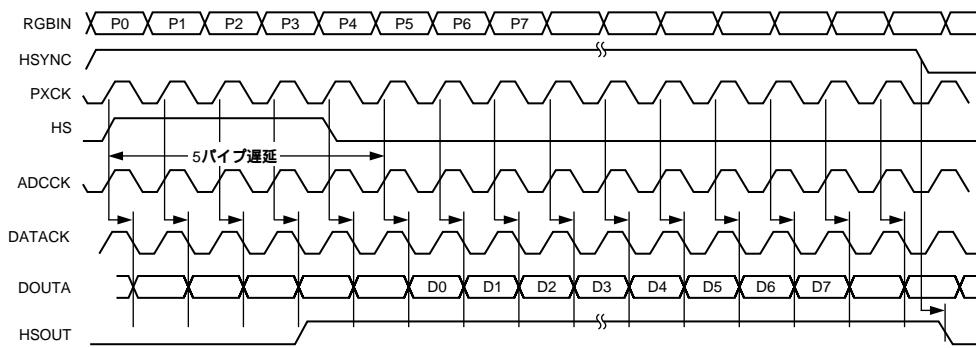

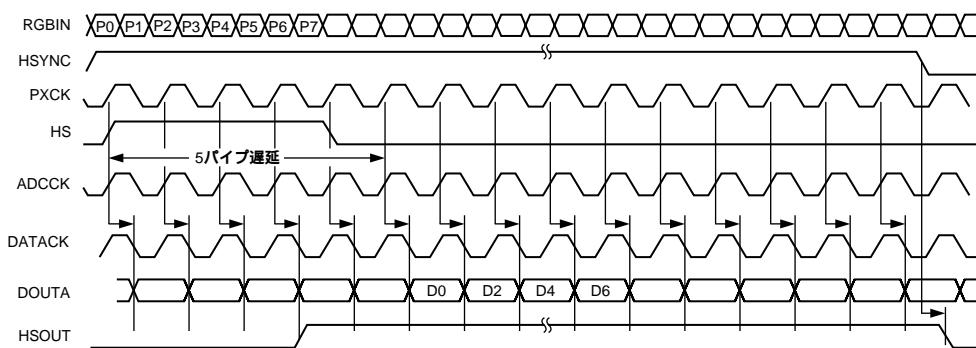

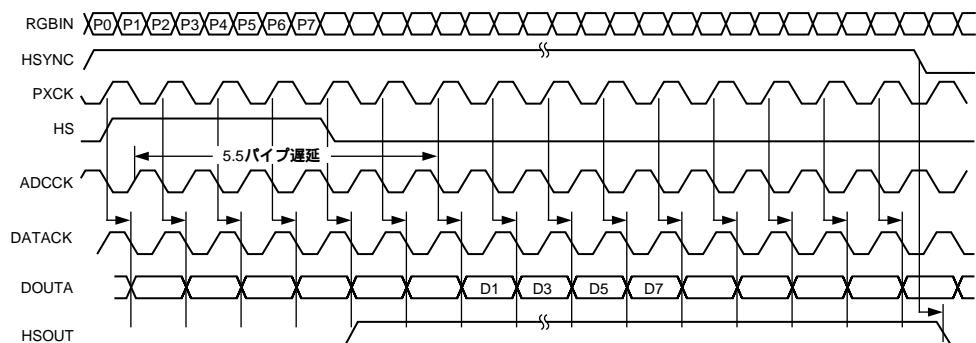

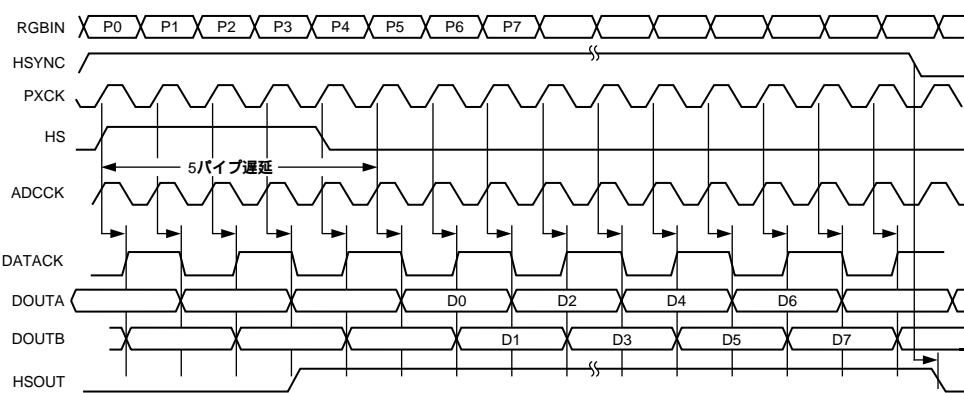

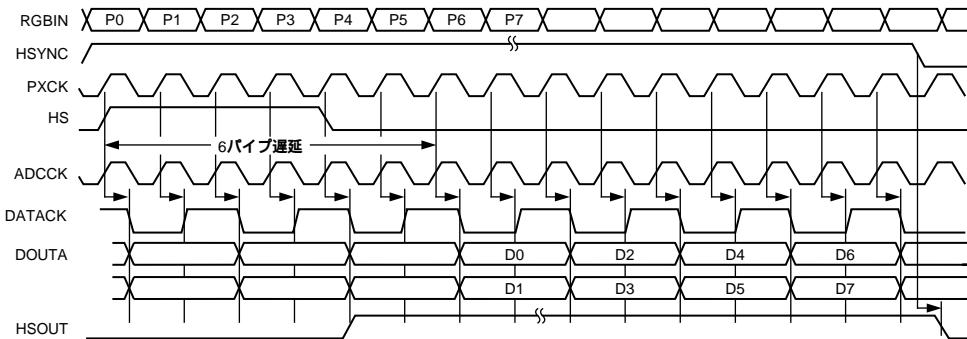

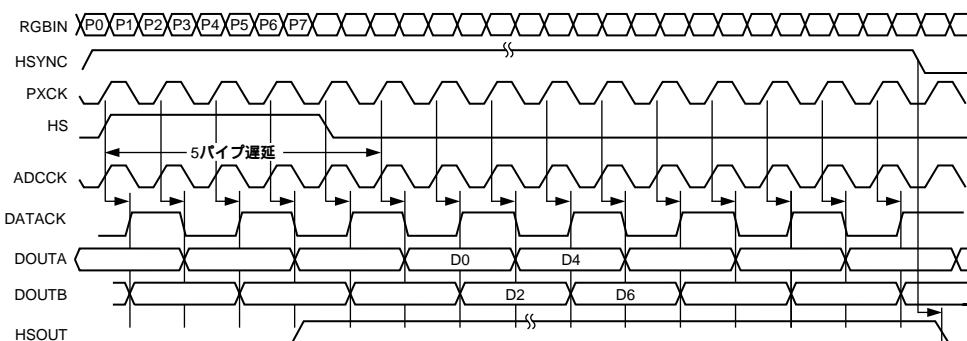

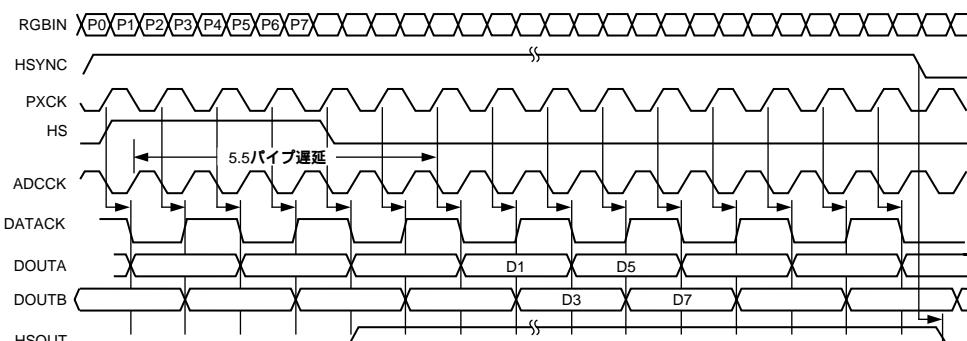

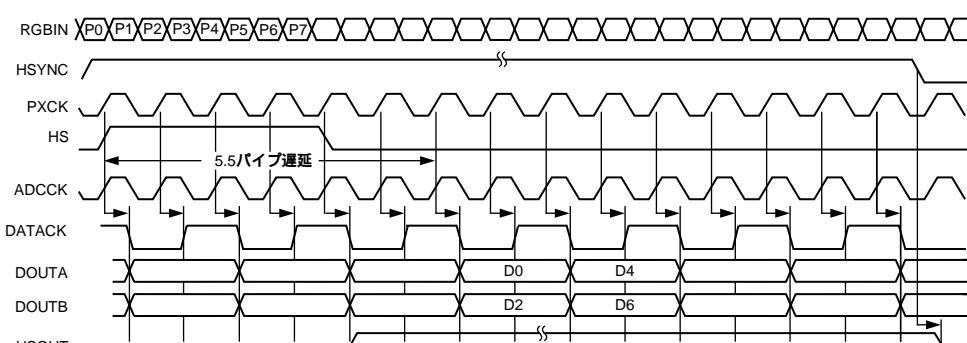

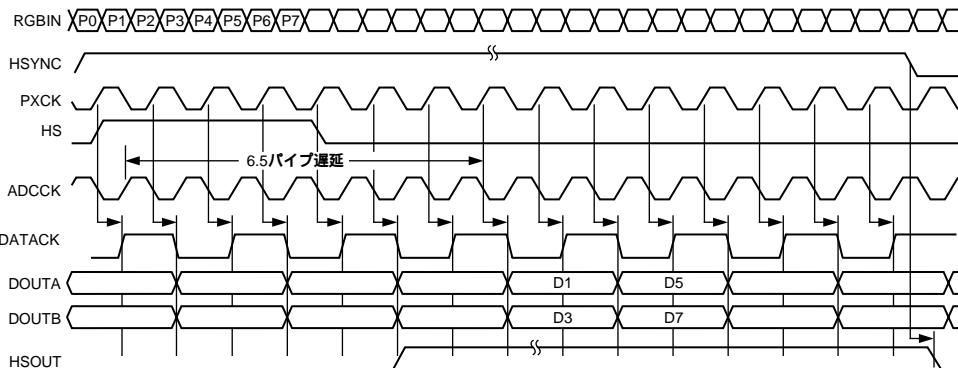

図12は、全クロック・モードにおけるAD9884Aのタイミング動作を示します。デバイスは、HSYNCの立ち上がりエッジにより、デジタル化されたピクセルに対応するサンプルをデータ・ポート“A”( 0Dh のビット4=1 のときはデータ・ポートB )に送出し終えたときにタイミングを確立します。デュアル・チャンネル・モードでは、次のサンプルは、ポート“B”( 0Dh のビット4=1 のときはデータ・ポートA )に送出されます。続くサンプルはデータポート“A”と“B”に交互に送出されます。シングル・チャンネル・モードでは、データはデータ・ポート“A”的みに送出され、ポート“B”は高インピーダンス状態になります。

デュアル・チャンネル・モードでは、HSYNCの後の最初のピクセルは常にポートAに送出されるので、意図する最初のピクセル( 走査線の最初のアクティブなピクセル )が、ポートBに現れることがあります。グラフィック・コントローラまたはメモリ・バッファの制約により最初のビットをポートAに出力する必要がある場合は、OUTPHASE制御ビットを使い、ポートAとBへのデータを交換できます。

出力データ・クロック信号は、その立ち上がりエッジが常に“A”的データ遷移の間に発生するように生成され、出力データの外部でのラッチに使用できます。HSYNC出力は、全シングル・チャンネル・モードにおいて、2つのデータ間の時間関係が一定となるようにパイプライン処理されています。

AD9884Aにはパイプラインが存在しますが、これは、有効なデータが利用可能となる前に廃棄する必要があります。全シングル・チャンネル・モードにおいて、有効なデータが利用可能となる前に4つのデータ・セットが供給されます。全デュアル・チャンネル・モードでは、有効なポート“A”的データが利用可能となる前に、2つのデータ・セットが与えられます。

図12 出力タイミング

## 水平同期タイミング

AD9884Aでは、水平同期の立ち上がりエッジ、位相遅延されたピクセル・クロック、データ間のタイミングのあいまいさを解消するために、水平同期信号が処理されます。

HSYNC入力は、ピクセル・サンプリング・クロックを生成するためのリファレンスとして使用されます。サンプリングの位相は調整可能で、HSYNCとの関係は、PHASEレジスタを介して360度の全周間にわたって32段階で設定できます( これによりピクセルのサンプリング・タイミングが最適化されます )。ディスプレイ・システムでは、メモリとディスプレイのライト・サイクルを一致させるためにHSYNCを利用

するので、HSOUTとDATAACKのタイミング関係を安定させることが重要です。

AD9884Aには、水平同期について2つの問題があります。第一に、HSOUTは常にアクティブ・ハイの状態で生成されるため、HSOUTの最初のエッジは常に立ち上がりエッジとなります。第二に、HSOUTはDATAACKとデータ出力にタイミングが一致しています。これは、ディスプレイ・システムの他の部分のドライブに使用される同期信号となります。

HSOUTの立ち下りエッジは時間的に一致しておらず、入力されるHSYNCにリンクしています。HSOUTの立ち上がりエッジの位置については、タイミング図を参照してください。HSOUTの立ち下りエッジはHSYNC入力の立ち下りエッジと一致しています。HSOUTの立ち下りエッジとDATAACKの間の時間関係は保証されていません。このため、HSOUTの最初のエッジをディスプレイ・システムのタイミングのすべてについて使用する必要があります。

HSOUTは、入力されたHSYNCの立ち下りエッジの到達の有無に関わらず、中線( midline )で強制的にローにされます。HSOUTのデューティ・サイクルが50%である場合( HSYNCのデューティ・サイクルと異なる場合 )には、HSPOLのビットの設定が誤っていることがあります。この性質は、HSPOLの設定を変えて、HSYNCの立ち上がりエッジの代わりに立ち下りエッジを使用するようにして、同期した立ち上がりと立ち下りエッジを持ったHSOUTを生成するために利用できます。この場合、内部のクランプ回路を使用するときには、クランプ位置の測定がHSYNCの立ち上がりエッジを基準とすることに注意し、これに応じたプログラミングをしなければなりません。

## COASTタイミング

多くのコンピュータ・システムでは、HSYNC信号は専用の結線で連続して供給されます。このようなシステムでは、COASTピンの入力と機能は不要で、また使用できません。

一部のシステムでは、HSYNCが垂直同期( VSYNC )期間中に影響を受けます。場合によっては、HSYNCパルスが消滅します。別のシステム例では、コンポジット同期( CSYNC )信号またはGreenチャンネル組み込み同期信号( SOG )を使用する場合があり、VSYNC期間中のHSYNCが等化パルスや、他の歪みを備えています。VSYNCの期間中にクロック・ジェネレータが攪乱されるのを防止するために、これらの歪みを無視する必要があります。ピクセル・クロックのPLLが異質のパルスを検出すると、新しい周波数への同期を試みるため、VSYNC期間の終わりまでに周波数が変更されます。このため、新しいフレームの最初の部分でHSYNCタイミングを修正して復帰するまでに数本の走査線が必要となり、ディスプレイの上端で画像の破断( tearing )が生じます。

COAST入力は、上記の問題を解決するために使用されます。これは、PLLの入力をディスエーブルにし、その時点での周波数でクロックをフリー・ランの状態とするための非同期の入力です。PLLは数本の走査線にわたり、大きな周波数ドリフトを発生させずに、フリー・ランの状態で動作できます。

COASTは、VSYNCの入力から直接にドライブすることができます。また、グラフィック・コントローラによってこれを与えることもできます。

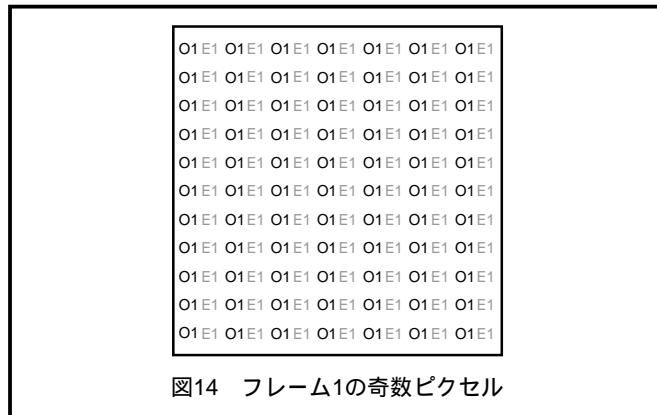

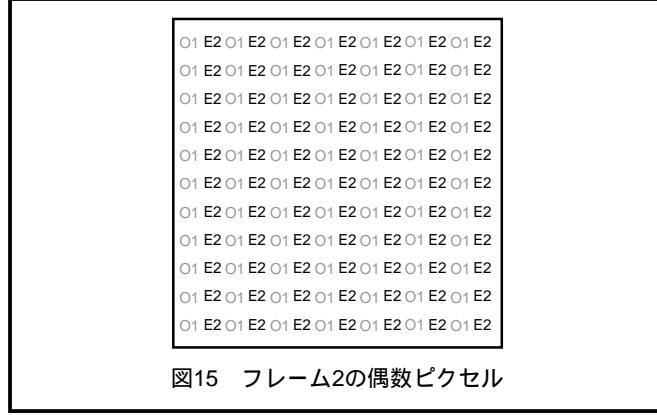

### 交互ピクセル・サンプリング・モード

CLKINV( ピン27 )へのロジック1の入力により、サンプリング位相が180度シフトされます。CKINVは、交互ピクセル・サンプリング・モードを構成するために、フレーム間での切り替えが可能です。これにより、低いピクセル・レートでの有効な画像の解像度を高くできますが、フレーム・レートは低くなります。

|   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

| O | E | O | E | O | E | O | E | O | E | O | E |

図13 フレームの奇数 / 偶数ピクセル

あるフレームでは、偶数ピクセルだけがデジタル化されます。次のフレームでは奇数ピクセルだけがサンプリングされます。グラフィック・コントローラでフレーム全体を復元することによって、画像を完全に再現できます。これは、TV放送で使用されるインターレース処理と非常に良く似たものですが、インターレースは水平方向ではなく垂直方向に行われます。このような処理を行っても、フレーム・データは意図するリフレッシュ・レート( 通常60Hz )で供給されるので、フリッカーは生じません。

|      |      |      |      |      |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|------|------|------|------|

| O1E1 |

| O1E1 |

| O1E1 |

| O1E1 |

| O1E1 |

| O1E1 |

| O1E1 |

| O1E1 |

| O1E1 |

| O1E1 |

| O1E1 |

図14 フレーム1の奇数ピクセル

|      |      |      |      |      |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|------|------|------|------|

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

図15 フレーム2の偶数ピクセル

|      |      |      |      |      |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|------|------|------|------|

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

| O1E2 |

図16 グラフィクス・コントローラからの合成

|      |      |      |      |      |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|------|------|------|------|

| O3E2 |

| O3E2 |

| O3E2 |

| O3E2 |

| O3E2 |

| O3E2 |

| O3E2 |

| O3E2 |

| O3E2 |

| O3E2 |

| O3E2 |

図17 コントローラからの次のフレーム出力

図14 フレーム1の奇数ピクセル

図15 フレーム2の偶数ピクセル

# AD9884A

図18 シングル・チャンネル・モード

図19 シングル・チャンネル・モード、交互ピクセル・サンプリング（偶数ピクセル）

図20 シングル・チャンネル・モード、交互ピクセル・サンプリング（奇数ピクセル）

図21 デュアル・チャンネル・モード、インターリーブ出力

図22 デュアル・チャンネル・モード、パラレル出力

図23 デュアル・チャンネル・モード、インターリーブ出力、交互ピクセル・サンプリング（偶数ピクセル）

図24 デュアル・チャンネル・モード、インターリーブ出力、交互ピクセル・サンプリング（奇数ピクセル）

図25 デュアル・チャンネル・モード、パラレル出力、交互ピクセル・サンプリング（偶数ピクセル）

# AD9884A

図26 デュアル・チャンネル・モード、パラレル出力、交互ピクセル・サンプリング（奇数ピクセル）

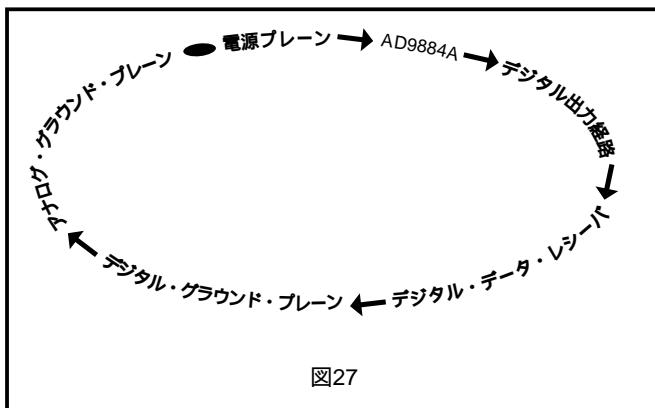

## PCB推奨レイアウト

AD9884Aは、高精度の高速アナログ・デバイスです。従って、デバイスの性能を最大限に発揮するためには、ボード・レイアウトを慎重に行う必要があります。

### 入力

グラフィック信号の入力については、以下の手法によるレイアウトが極めて重要です。

グラフィック入力までの経路の距離を最小限にします。AD9884Aを入力コネクタのできる限り近くに配置することにより、最短の経路が可能です。入力経路が長くなると、ボードや他の外部デバイスからのノイズを拾いやすくなるので、望ましくありません。

75 の終端抵抗を、AD9884Aのなるべく近くに設置します。AD9884Aの入力と終端抵抗の間の経路が長くなると、反射波が大きくなつてグラフィック信号の品質が低下します。

75 のインピーダンス整合のとれた経路を使用します。経路のインピーダンスが75 に達しない場合にも反射波が大きくなつます。

AD9884Aは、非常に高い入力帯域幅( 500MHz )を備えています。これは、エッジの変化が速い高解像度のPCグラフィックの収集に必要ですが、同時に高周波のノイズも拾いやすくなります。このため、入力にカップリングされるノイズのを減らすことが重要です。アナログ入力の近くには、デジタル経路を設置しないでください。