# AD9840A

## 特長

40MSPS相關ダブル・サンプラー (CDS)

6ビット分解能の4dB ± 6dB可変CDSゲイン

2 ~ 36dBの10ビット可変ゲイン・アンプ (VGA)

ローノイズ・クランプ回路

アナログ・プリプランキング機能

10ビット40MSPS A/Dコンバータ

VGAおよび入力クランプを備えた補助入力

3線式シリアル・デジタル・インターフェース

+ 3V単電源動作

低消費電力：3.0V電源において155mW

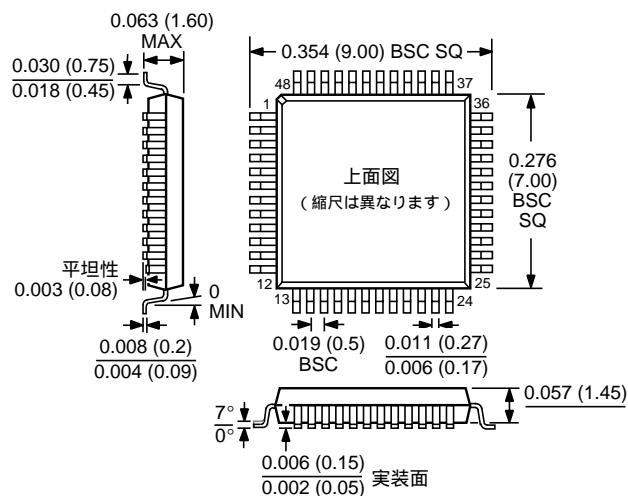

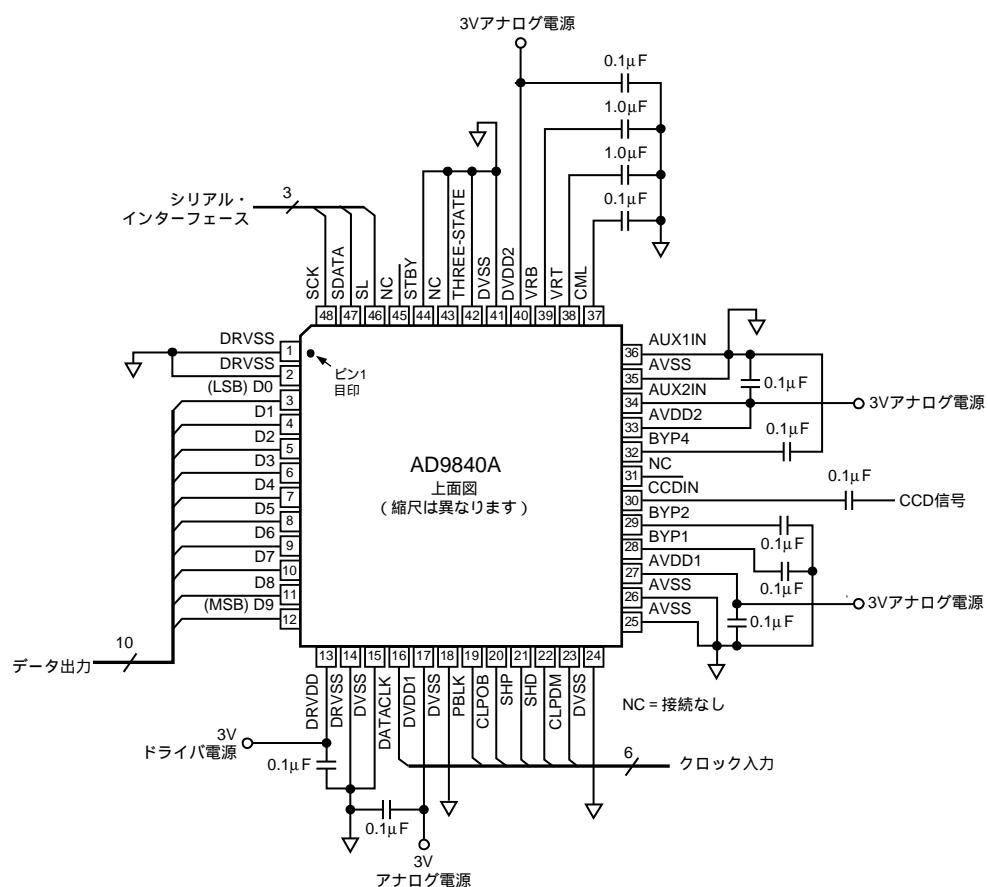

48ピンLQFPパッケージ

## アプリケーション

デジタル・ビデオ・カメラ

デジタル・スチル・カメラ

工業用画像処理

## 概要

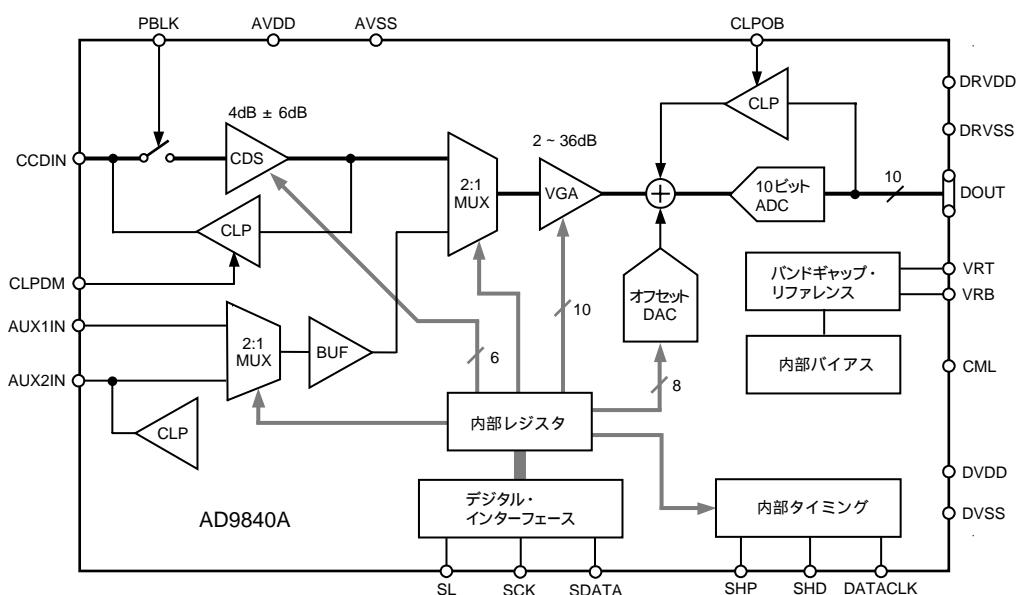

AD9840Aは、CCDアプリケーション用の完全なアナログ信号プロセッサです。インターレースおよびプログレッシブのスキャン領域CCDアレイの出力のサンプルと整形用に設計された、40MHzのシングル・チャンネル・アーキテクチャを備えています。AD9840Aのシグナル・チェーンは、入力クランプ、相關ダブル・サンプラー (Correlated Double Sampler, CDS)、デジタル制御の可変ゲイン・アンプ (Variable Gain Amplifier, VGA)、黒レベル・クランプ、10ビットA/Dコンバータによって構成されています。アナログのビデオ信号を処理するため、追加の入力モードを提供します。

AD9840Aの内部レジスタは、3線式のデジタル・インターフェースを介してプログラムされます。ゲイン調整、黒レベル調整、入力設定、パワーダウン・モードなど、プログラマブルな機能があります。

AD9840Aは、+ 3V単電源から動作し、標準的な消費電力は155mWです。48ピンLQFPパッケージで供給されます。

機能ブロック図

# AD9840A 仕様

## 一般的仕様

(特に指定のない限り、 $T_{MIN} \sim T_{MAX}$ 、 $AVDD = DVDD = 3.0V$ 、 $f_{DATACLK} = 40MHz$  )

| パラメータ                                                                     | Min  | Typ               | Max        | 単位                     |

|---------------------------------------------------------------------------|------|-------------------|------------|------------------------|

| 温度範囲                                                                      |      |                   |            |                        |

| 動作時                                                                       | - 20 |                   | + 85       |                        |

| 保管時                                                                       | - 65 |                   | + 150      |                        |

| 電源電圧<br>アナログ、デジタル、デジタル・ドライバ                                               | 2.7  |                   | 3.6        | V                      |

| 消費電力<br>通常動作<br>パワーダウン・モード<br>高速リカバリ・モード<br>スタンバイ<br>全パワーダウン              |      | (各動作モードについて仕様を規定) |            |                        |

|                                                                           |      | 90                |            | mW                     |

|                                                                           |      | 5                 |            | mW                     |

|                                                                           |      | 1                 |            | mW                     |

| 最大クロック・レート                                                                | 40   |                   |            | MHz                    |

| A/Dコンバータ<br>分解能<br>微分非直線性 (DNL)<br>ノー・ミス・コード<br>フルスケール入力電圧<br>データ出力コーディング | 10   | $\pm 0.5$         | $\pm 1.0$  | ビット<br>LSB<br>保証済みビット数 |

|                                                                           | 10   | 2.0               | ストレート・バイナリ | V                      |

| 電圧リファレンス<br>リファレンス最高電圧 (VRT)<br>リファレンス最低電圧 (VRB)                          |      | 2.0               |            | V                      |

|                                                                           |      | 1.0               |            | V                      |

仕様は予告なく変更されることがあります。

## デジタル仕様

(特に指定のない限り、 $DRVDD = 2.7V$ 、 $C_L = 20pF$  )

| パラメータ                                                                       | 記号                                                       | Min | Typ | Max | 単位                                   |

|-----------------------------------------------------------------------------|----------------------------------------------------------|-----|-----|-----|--------------------------------------|

| ロジック入力<br>ハイ・レベル入力電圧<br>ロー・レベル入力電圧<br>ハイ・レベル入力電流<br>ロー・レベル入力電流<br>入力キャパシタンス | $V_{IH}$<br>$V_{IL}$<br>$I_{IH}$<br>$I_{IL}$<br>$C_{IN}$ | 2.1 |     | 0.6 | V<br>V<br>$\mu A$<br>$\mu A$<br>$pF$ |

| ロジック出力<br>ハイ・レベル出力電圧、 $I_{OH} = 2mA$<br>ロー・レベル出力電圧、 $I_{OL} = 2mA$          | $V_{OH}$<br>$V_{OL}$                                     | 2.2 |     | 0.5 | V<br>V                               |

仕様は予告なく変更されることがあります。

## CCDモード仕様

(特に指定のない限り、 $T_{MIN} = T_{MAX}$ 、 $AVDD = DVDD = 3.0V$ 、 $f_{DATACLK} = f_{SHP} = f_{SHD} = 40MHz$  )

| パラメータ                        | Min   | Typ   | Max   | 単位      | 備考                              |

|------------------------------|-------|-------|-------|---------|---------------------------------|

| 消費電力                         |       | 155   |       | mW      |                                 |

| 最大クロック・レート                   | 20    |       |       | MHz     |                                 |

| CDS                          |       |       |       |         |                                 |

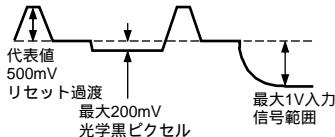

| 許容CCDリセット過渡 <sup>1</sup>     |       | 500   |       | mV      | 注1の入力波形を参照                      |

| 最大CCD黒ピクセル振幅 <sup>1</sup>    |       | 200   |       | mV      |                                 |

| 飽和前の最大入力範囲 <sup>1</sup>      | 1.0   |       |       | Vp-p    | 4dBのCDSゲイン                      |

| 飽和前の最大入力範囲                   |       | 1.5   |       | Vp-p    | - 2dBのCDSゲイン                    |

| 飽和前の最大入力範囲                   |       | 0.5   |       | Vp-p    | 10dBのCDSゲイン                     |

| 最大出力範囲                       | 1.6   |       |       | Vp-p    | すべてのCDSゲイン設定                    |

| ゲイン分解能                       |       | 64    |       | ステップ    |                                 |

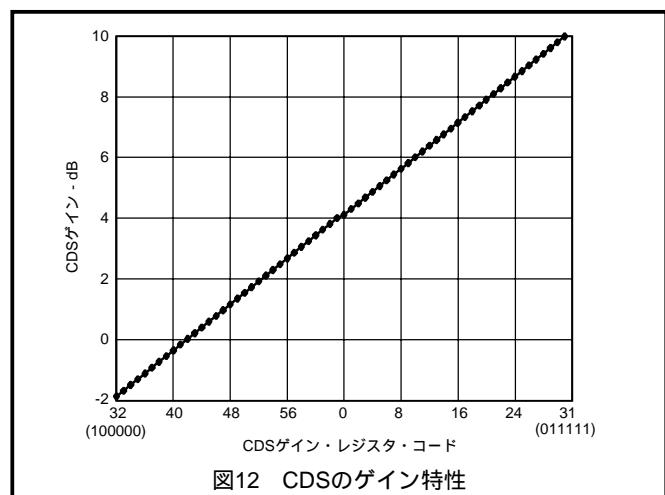

| ゲイン範囲(2の補数によるコーディング)         |       |       |       |         | CDSの特性曲線について図15を参照              |

| 最小ゲイン( CDSのゲイン・レジスタのコードは32 ) |       | - 2   |       | dB      |                                 |

| 中間ゲイン( CDSのゲイン・コードは63 )      |       | 4     |       | dB      | CDSのゲインがディスエーブルにされた場合のデフォルトは4dB |

| 最大ゲイン( CDSのゲイン・コードは31 )      |       | 10    |       | dB      |                                 |

| 可変ゲイン・アンプ( VGA )             |       |       |       |         |                                 |

| 最大入力範囲                       | 1.6   |       |       | Vp-p    |                                 |

| 最大出力範囲                       | 2.0   |       |       | Vp-p    |                                 |

| ゲイン制御分解能                     |       | 1024  |       | ステップ    |                                 |

| ゲイン単調性                       |       | 保証済み  |       |         |                                 |

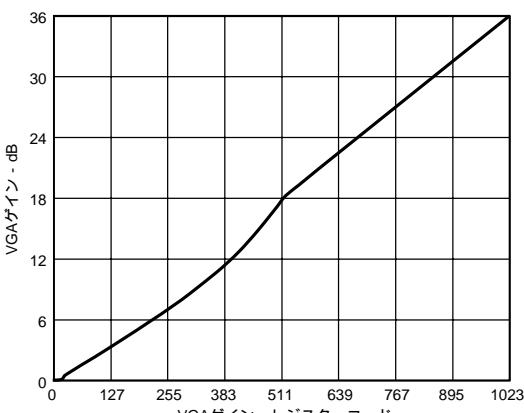

| ゲイン範囲                        |       |       |       |         | VGAの特性曲線について図13を参照              |

| 最小ゲイン( VGAレジスタのコードは91 )      |       | 2     |       | dB      | ゲインの計算式について12ページを参照             |

| 最大ゲイン( VGAのコードは1023 )        |       | 36    |       | dB      |                                 |

| 黒レベル・クランプ                    |       |       |       |         |                                 |

| クランプ・レベル分解能                  |       | 256   |       | ステップ    |                                 |

| クランプ・レベル                     |       |       |       |         | ADCの出力において測定                    |

| 最小クランプ・レベル                   |       | 0     |       | LSB     |                                 |

| 最大クランプ・レベル                   |       | 63.75 |       | LSB     |                                 |

| システム特性                       |       |       |       |         |                                 |

| ゲイン精度、VGAのコードは91～1023        | - 1.0 |       | + 1.0 | dB      | 仕様にはシグナル・チェーンの全体を含む             |

| ピーク非直線性、入力信号：500mV           |       | 0.4   |       | %       | ゲインの算出には12ページの式を使用              |

| 総合出力ノイズ                      |       | 0.25  |       | LSB rms | 12dBのゲインを適用( CDSのゲインは4dB )      |

| 電源除去( PSR )                  |       | 40    |       | dB      | ACをグラウンドとする入力、6dBのゲインを適用        |

| 電源をステップ的に変化させて測定             |       |       |       |         |                                 |

| パワーアップ・リカバリ時間                |       |       |       |         | 仕様にはシグナル・チェーンの全体を含む             |

| 高速リカバリ・モードから                 |       | 0.1   |       | ms      | ゲインの算出には12ページの式を使用              |

| リファレンス・スタンバイ・モードから           |       | 1     |       | ms      | 12dBのゲインを適用( CDSのゲインは4dB )      |

| 全シャットダウン・モードから               |       | 3     |       | ms      | ACをグラウンドとする入力、6dBのゲインを適用        |

| パワーオフ状態から                    |       | 15    |       | ms      | 電源をステップ的に変化させて測定                |

## 注

1. 入力信号の特性は4dBのCDSゲインについて次のように定義されます。

仕様は予告なく変更されることがあります。

# AD9840A 仕様

## AUX1モードの仕様

(特に指定のない限り、 $T_{MIN} \sim T_{MAX}$ 、AVDD = DVDD = 3.0V、 $f_{DATACLK} = 40MHz$  )

| パラメータ                                                                 | Min | Typ  | Max | 単位           |

|-----------------------------------------------------------------------|-----|------|-----|--------------|

| 消費電力                                                                  |     | 105  |     | mW           |

| 最大クロック・レート                                                            | 40  |      |     | MHz          |

| 入力バッファ<br>ゲイン<br>最大入力範囲                                               |     | 0    |     | dB<br>Vp-p   |

| 1.0                                                                   |     |      |     |              |

| VGA<br>最大出力範囲<br>ゲイン制御分解能<br>ゲイン (VGAゲイン・レジスタにより選択)<br>最小ゲイン<br>最大ゲイン | 2.0 | 1023 |     | Vp-p<br>ステップ |

|                                                                       |     | 0    |     | dB           |

|                                                                       |     | 36   |     | dB           |

仕様は予告なく変更されることがあります。

## AUX2モードの仕様

(特に指定のない限り、 $T_{MIN} \sim T_{MAX}$ 、AVDD = DVDD = 3.0V、 $f_{DATACLK} = 40MHz$  )

| パラメータ                                                                              | Min | Typ            | Max | 単位           |

|------------------------------------------------------------------------------------|-----|----------------|-----|--------------|

| 消費電力                                                                               |     | 105            |     | mW           |

| 最大クロック・レート                                                                         | 40  |                |     | MHz          |

| 入力バッファ                                                                             |     | ( AUX1モードと同様 ) |     |              |

| VGA<br>最大出力範囲<br>ゲイン制御分解能<br>ゲイン ( VGAゲイン・レジスタにより選択)<br>最小ゲイン<br>最大ゲイン             | 2.0 | 512            |     | Vp-p<br>ステップ |

|                                                                                    |     | 0              |     | dB           |

|                                                                                    |     | 18             |     | dB           |

| アクティブ・クランプ<br>クランプ・レベル分解能<br>クランプ・レベル ( ADCの出力において測定 )<br>最小クランプ・レベル<br>最大クランプ・レベル |     | 256            |     | ステップ         |

|                                                                                    |     | 0              |     | LSB          |

|                                                                                    |     | 63.75          |     | LSB          |

仕様は予告なく変更されることがあります。

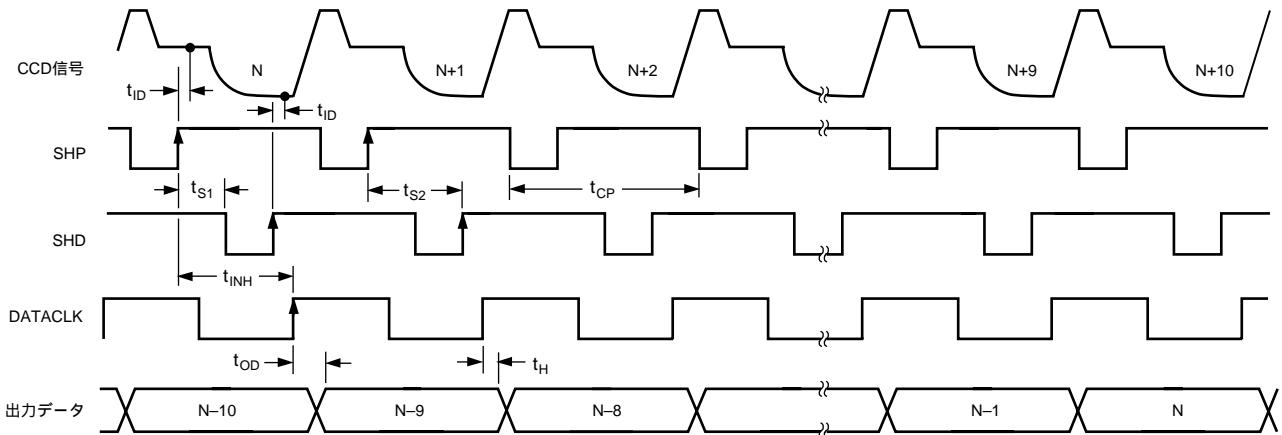

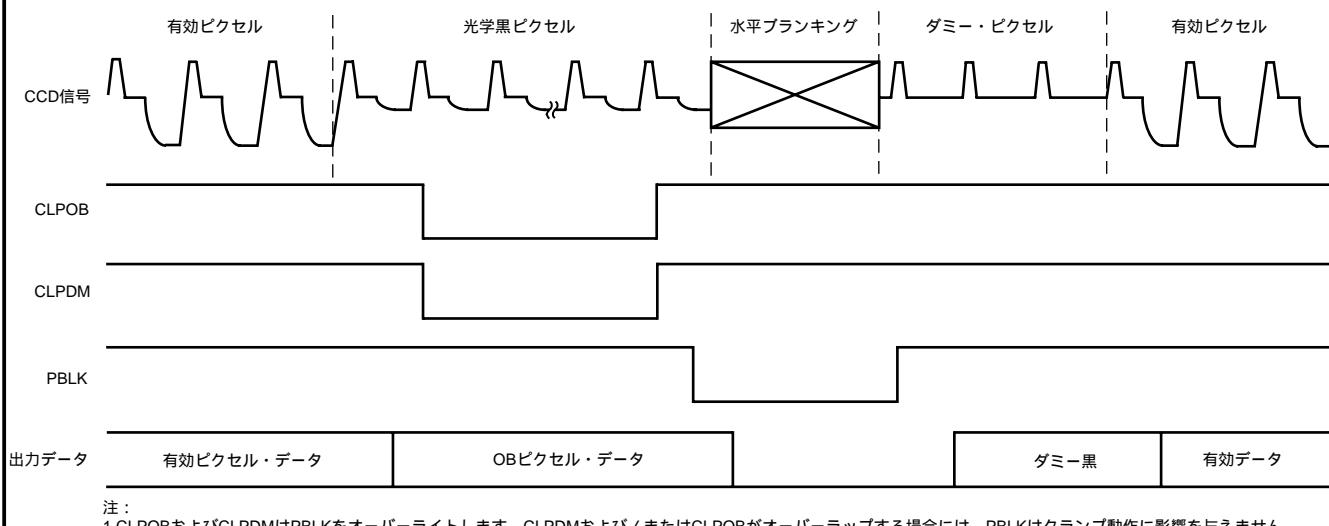

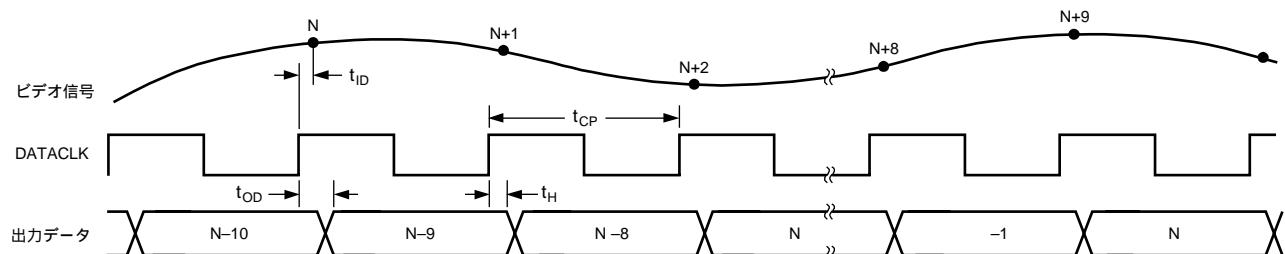

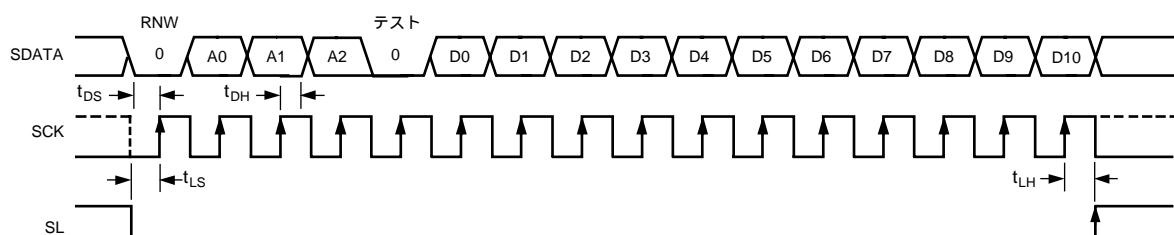

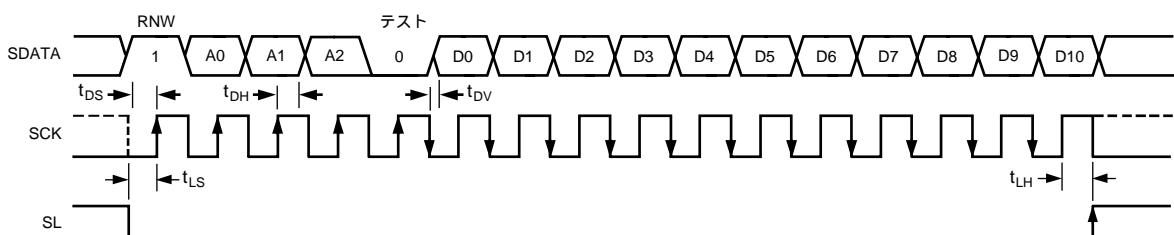

## タイミング特性

(  $C_L = 20\text{pF}$ ,  $f_{\text{SAMP}} = 40\text{MHz}$ , CCDモード・タイミングは図5および6、AUXモード・タイミングは図7を参照。シリアル・タイミングは図8~10を参照 )

| パラメータ                        | 記号         | Min | Typ  | Max | 単位   |

|------------------------------|------------|-----|------|-----|------|

| サンプル・クロック                    |            |     |      |     |      |

| DATACLK,SHDクロック期間            | $t_{CP}$   | 25  |      |     | ns   |

| DATACLKハイ / ロー・パルス幅          | $t_{ADC}$  | 10  | 12.5 |     | ns   |

| SHDパルス幅                      | $t_{SHD}$  | 5   | 6    |     | ns   |

| SHDパルス幅                      | $t_{SHD}$  | 5   | 6    |     | ns   |

| CLPDMパルス幅                    | $t_{CDM}$  | 4   | 10   |     | ピクセル |

| CLPOBパルス幅1                   | $t_{COB}$  | 2   | 20   |     | ピクセル |

| SHD立ち上がりエッジからSHDの立ち下りエッジまで   | $t_{S1}$   | 0   | 6    |     | ns   |

| SHD立ち上がりエッジからSHDの立ち上がりエッジまで  | $t_{S2}$   | 10  | 12.5 |     | ns   |

| 内部クロック遅延                     | $t_{ID}$   |     | 3.0  |     | ns   |

| クロック禁止期間                     | $t_{INH}$  | 10  |      |     | ns   |

| データ出力                        |            |     |      |     |      |

| 出力遅延                         | $t_{OD}$   |     | 14.5 | 16  | ns   |

| 出力ホールド時間                     | $t_H$      | 7.0 | 7.6  |     | ns   |

| パイプライン遅延                     |            |     | 9    |     | サイクル |

| シリアル・インターフェース                |            |     |      |     |      |

| 最大SCK周波数                     | $f_{SCLK}$ | 10  |      |     | MHz  |

| SLからSCKへのセットアップ時間            | $t_{LS}$   | 10  |      |     | ns   |

| SCKからSLへのホールド時間              | $t_{LH}$   | 10  |      |     | ns   |

| SDATA有効からSCK立ち上がりエッジへのセットアップ | $t_{DS}$   | 10  |      |     | ns   |

| SCK立ち下りエッジからSDATA有効へのホールド    | $t_{DH}$   | 10  |      |     | ns   |

| SCK立ち下りエッジからSDATAの有効な読み出し    | $t_{DV}$   | 10  |      |     | ns   |

### 注

- 最小のCLPOBパルス幅は、機能の動作のみに対するものです。ローノイズのクランプ動作のためには、より広いパルスを標準とすることが推奨されます。

- 仕様は予告なく変更される場合があります。

## 絶対最大定格

| パラメータ            | 基準    | Min   | Max          | 単位 |

|------------------|-------|-------|--------------|----|

| AVDD1,AVDD2      | AVSS  | - 0.3 | + 3.9        | V  |

| DVDD1,DVDD2      | DVSS  | - 0.3 | + 3.9        | V  |

| DRVDD            | DRVSS | - 0.3 | + 3.9        | V  |

| デジタル出力           | DRVSS | - 0.3 | DRVDD + 0.3V | V  |

| SHD,DATACLK      | DVSS  | - 0.3 | DVDD + 0.3V  | V  |

| CLPOB,CLPDM,PBLK | DVSS  | - 0.3 | DVDD + 0.3V  | V  |

| SCK,SL,SDATA     | DVSS  | - 0.3 | DVDD + 0.3V  | V  |

| VRT,VRB,CMLEVEL  | AVSS  | - 0.3 | AVDD + 0.3V  | V  |

| BYP1 ~ 4,CCDIN   | AVSS  | - 0.3 | AVDD + 0.3V  | V  |

| 接合温度             |       | 150   |              |    |

| ピン温度 ( 10秒 )     |       | 300   |              |    |

## オーダー・ガイド

| モデル        | 温度範囲        | パッケージ                          | パッケージ・オプション |

|------------|-------------|--------------------------------|-------------|

| AD9840AJST | - 20 ~ + 85 | 薄型プラスチック・ケワード・フラットパック ( LQFP ) | ST-48       |

### 熱特性

### 熱抵抗

48ピンLQFPパッケージ

$J_A = 92$

### 注意

ESD ( 静電放電 ) の影響を受けやすいデバイスです。4000Vもの高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることがあります。本製品には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や機能喪失を回避するために、適切なESD予防措置をとるようお奨めします。

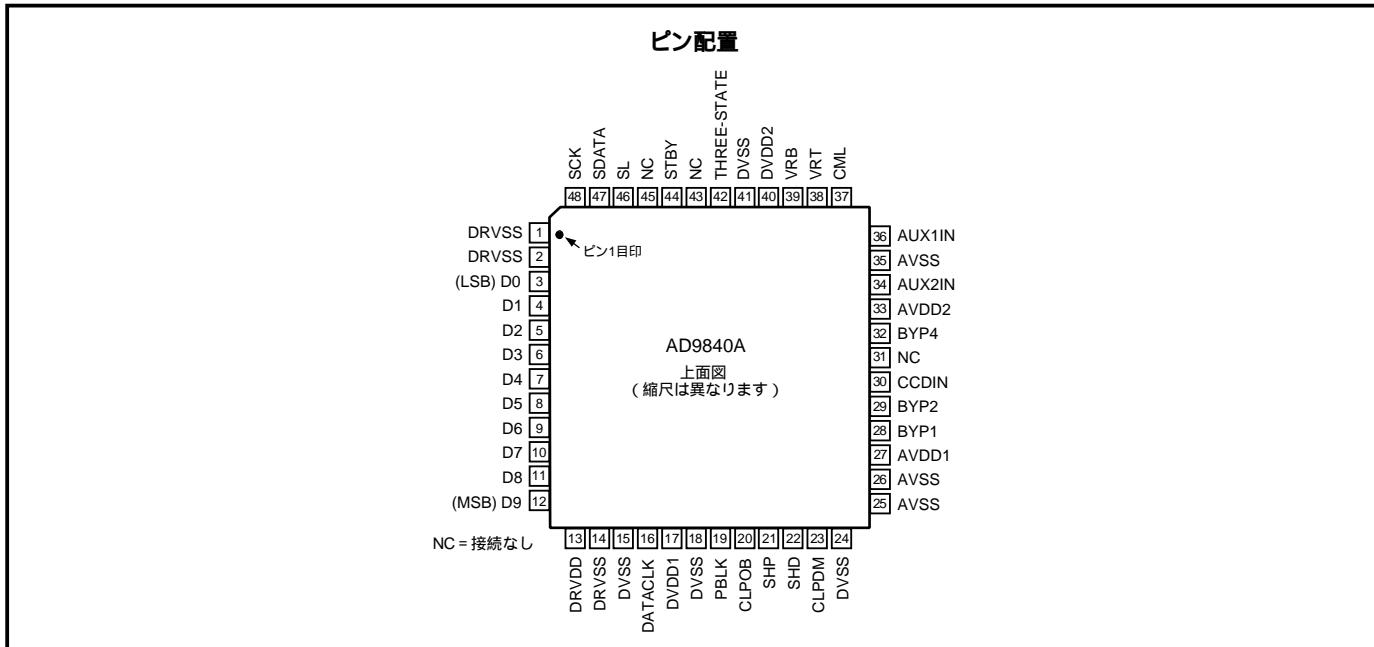

# AD9840A

## ピン機能の説明

| ピン番号        | 名称          | タイプ | 説明                                            |

|-------------|-------------|-----|-----------------------------------------------|

| 1,2         | DRVSS       | P   | デジタル・ドライバ・グラウンド                               |

| 3 ~ 12      | D0 ~ D9     | DO  | デジタル・データ出力                                    |

| 13          | DRVDD       | P   | デジタル出力ドライバ電源                                  |

| 14          | DRVSS       | P   | デジタル出力ドライバ・グラウンド                              |

| 15,18,24,41 | DVSS        | P   | デジタル・グラウンド                                    |

| 16          | DATACLK     | DI  | デジタル・データ出力ラッチ・クロック                            |

| 17          | DVDD1       | P   | デジタル電源                                        |

| 19          | PBLK        | DI  | ブリブランкиング・クロック入力                              |

| 20          | CLPOB       | DI  | 黒レベル・クランプ・クロック入力                              |

| 21          | SHP         | DI  | CCDのリファレンス・レベルへのCDSサンプリング・クロック                |

| 22          | SHD         | DI  | CCDのデータ・レベルへのCDSサンプリング・クロック                   |

| 23          | CLPDM       | DI  | 入力クランプ・クロック入力                                 |

| 25,26,35    | AVSS        | P   | アナログ・グラウンド                                    |

| 27          | AVDD1       | P   | アナログ電源                                        |

| 28          | BYP1        | AO  | 内部バイアス・レベル・デカップリング                            |

| 29          | BYP2        | AO  | 内部バイアス・レベル・デカップリング                            |

| 30          | CCDIN       | AI  | CCD信号のアナログ入力                                  |

| 31          | NC          | NC  | フローティングにするか、グラウンドに0.1 μFでデカップリングします。          |

| 32          | BYP4        | AO  | 内部バイアス・レベル・デカップリング                            |

| 33          | AVDD2       | P   | アナログ電源                                        |

| 34          | AUX2IN      | AI  | アナログ入力                                        |

| 36          | AUX1IN      | AI  | アナログ入力                                        |

| 37          | CML         | AO  | 内部バイアス・レベル・デカップリング                            |

| 38          | VRT         | AO  | A/Dコンバータの最高リファレンス電圧のデカップリング                   |

| 39          | VRB         | AO  | A/Dコンバータの最低リファレンス電圧のデカップリング                   |

| 40          | DVDD2       | P   | デジタル電源                                        |

| 42          | THREE-STATE | DI  | デジタル出力ディスエーブル。アクティブ・ハイ                        |

| 43          | NC          | NC  | ハイまたはローに接続可能。フローティングにすることは不可                  |

| 44          | STBY        | DI  | スタンバイ・モード、アクティブ・ハイ。シリアル・インターフェース・スタンバイ・モードと同様 |

| 45          | NC          | NC  | 内部的に無接続。ハイまたはローに接続できます。                       |

| 46          | SL          | DI  | シリアル・デジタル・インターフェース・ロード・パルス                    |

| 47          | SDATA       | DI  | シリアル・デジタル・インターフェース・データ                        |

| 48          | SCK         | DI  | シリアル・デジタル・インターフェース・クロック                       |

タイプ : AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力、P = 電源。

**仕様の定義****微分非直線性(DNL)**

理想的なA/Dコンバータのコード遷移は、正確に1 LSB間隔になります。DNLとは、この理想的な値からの偏差を言います。このように、それぞれのコードの幅は有限である必要があります。10ビットの分解能に対して「ノーミス・コード」が保証されているということは、すべての動作範囲にわたって、それに対応する1024個のコードが存在することを意味します。

**ピーク非直線性**

ピーク非直線性は、全シグナル・チェーンの仕様であり、完全な直線からのAD9840Aの出力のピーク偏差を意味します。「ゼロ・スケール」として使用される点は、最初のコードの遷移から1/2 LSBだけ前に発生します。「正極性のフルスケール」は、最後のコードの遷移を1/2 LSBだけ超えたレベル1と定義されます。この偏差は、特定の出力のそれぞれの中間から完全な直線までを測定して求められます。次に、2VのA/Dコンバータのフルスケール信号に対する%値として表されます。入力信号は、常に、A/Dコンバータのフルスケール範囲を利用できるように、適当なゲインで増幅されます。

**総合出力ノイズ**

出力ノイズのrms値は、ヒストグラムの手法によって測定されま

す。A/Dコンバータの出力コードの標準偏差は、LSB単位で算出され、特定のゲイン設定における総合シグナル・チェーンのノイズ・レベルのrms値を表します。出力ノイズは、A/Dコンバータの分解能をNビットとしたときの $1\text{ LSB} = (\text{ADCのフルスケール}/2^N\text{コード})$ の等式を用いて、これと等価な電圧に変換できます。AD9840Aでは、1 LSBは2mVとなります。

**電源除去(PSR)**

PSRは、電源ピンにステップ状の変化を与えた状態で測定されます。これは、AD9840Aの電源に極めて高周波数の妨害が与えられた場合の状態を示します。PSRの仕様は、電源電圧に任意のステップ状の変化を与えた場合のデータ出力の変化から算出されます。

**SHP/SHDの内部遅延**

内部遅延(アパーチャ遅延とも呼ばれる)は、サンプリング・エッジがAD9840Aに与えられてから入力信号のサンプルが実際に保持されるまでの時間を測定したものです。SHPとSHDの双方は、ローからハイへの遷移の間で入力信号をサンプルするため、内部遅延は、各クロックの立ち上がりエッジから内部サンプルが実際に得られるまでの時間を測定して得られます。

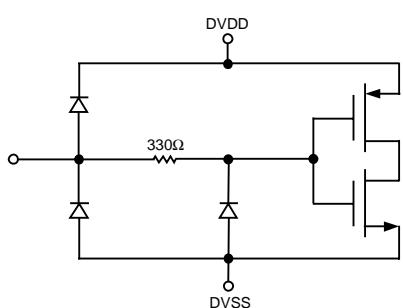

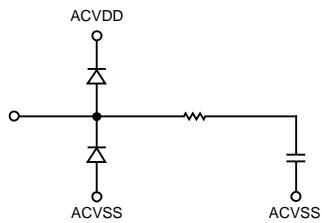

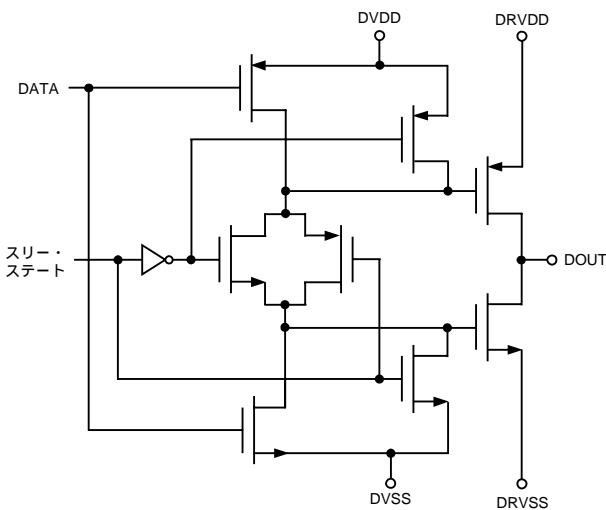

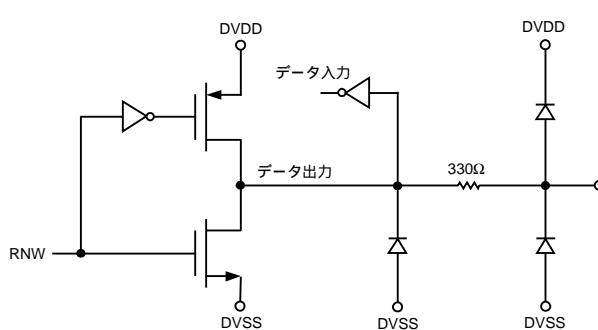

図1 デジタル入力 - SHP, SHD, DATACLK, CLPOB, CLPDM, HD, VD, PBLK, SCK, SL

図3 CCDIN (30pin)

図2 データ出力

図4 SDATA (47pin)

# AD9840A

CCDモードおよびAUXモードのタイミング

注：

1 DATACLKの立ち上がりエッジの位置は、SHDの立ち上がりエッジと次のSHPの立ち下りエッジとの間にすることを推奨します。

2 CCD信号は、SHPおよびSHDの立ち上がりエッジでサンプルされます。

図5 CCDモードのタイミング

図6 標準的なCCDモードのライン・クランプ・タイミング

図7 AUXモードのタイミング

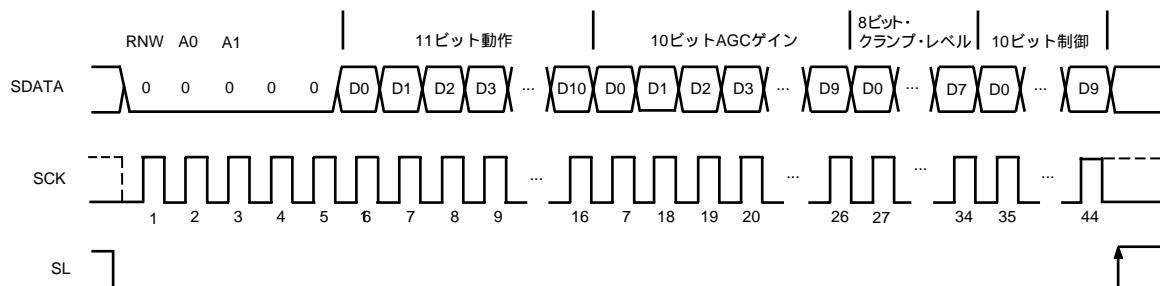

## シリアル・インターフェース・タイミングおよび内部レジスタの説明

表1 内部レジスタのマップ

| レジスタの名称  | アドレス |     |     | データ・ビット            |                |                 |                  |                               |     |     |             |     |     |      |  |

|----------|------|-----|-----|--------------------|----------------|-----------------|------------------|-------------------------------|-----|-----|-------------|-----|-----|------|--|

|          | A 0  | A 1 | A 2 | D 0                | D 1            | D 2             | D 3              | D 4                           | D 5 | D 6 | D 7         | D 8 | D 9 | D 10 |  |

| 動作       | 0    | 0   | 0   | チャンネル選択<br>CCD/AUX | パワーダウン・<br>モード | ソフトウェア・<br>リセット | OBクランプ<br>ON/OFF | 0*                            | 1** | 0*  | 0*          | 0*  | 0*  |      |  |

| VGAゲイン   | 1    | 0   | 0   | LSB                |                |                 |                  |                               |     |     |             |     | MSB | X    |  |

| クランプ・レベル | 0    | 1   | 0   | LSB                |                |                 |                  |                               |     |     |             | MSB | X   | X    |  |

| 制御       | 1    | 1   | 0   | 0*                 | 0*             | 0*              | CDSゲイン<br>ON/OFF | SHP/SHD/CLP/DATAのクロック<br>極性選択 | 0*  | 0*  | スリー<br>ステート |     | X   |      |  |

| CDSゲイン   | 0    | 0   | 1   | LSB                |                |                 |                  |                               | MSB | X   | X           | X   | X   | X    |  |

\*内部のみで使用。0にセット。

\*\*1にセット。

- 注：

- 1 SDATAのビットは、SCKの立ち上がりエッジで内部的にラッチされます。

- 2 RNW = READ-NOT WRITE。書き込み動作ではローに設定します。

- 3 テスト・ビットは内部使用のみです。ローに設定する必要があります。

- 4 ロードされたレジスタのシステム更新は、SLの立ち上がりエッジで発生します。

図8 シリアル書き込み動作

- 1 RNW = READ-NOT WRITE。読み出し動作ではハイに設定します。

2 テスト・ビットは内部使用のみです。ローに設定する必要があります。

3 選択されたレジスタからのシリアル・データは、SCKの5番目の立ち下りエッジから有効であり、SCKの立ち下りエッジで更新されます。

図9 シリアル読み戻し動作（シリアル・リードバック動作）

- 注：

- 1 任意の数の隣接するレジスタをシーケンシャルにロードでき、一番低位のアドレスから始まってアドレスが一度に1つずつインクリメントされます。

- 2 複数のレジスタをシーケンシャルにロードするときには、各レジスタについてレジスタの正確な長さ（上記）を使用する必要があります。3 ロードされたすべてのレジスタは、SLの立ち上がりエッジで同時に更新されます。

図10 複数のレジスタへの連続シリアル書き込み動作

# AD9840A

表 II 動作レジスタの内容（デフォルト値：x000）

| 光学黒クランプ |    |    |     |    | リセット                               | パワーダウン・モード                        |                                                    | チャンネル選択                                               |    |    |

|---------|----|----|-----|----|------------------------------------|-----------------------------------|----------------------------------------------------|-------------------------------------------------------|----|----|

| D10     | D9 | D8 | D7  | D6 | D5                                 | D4                                | D3                                                 | D2                                                    | D1 | D0 |

| 0*      | 0* | 0* | 1** | 0* | 0 クランピング・イネーブル<br>1 クランピング・ディスエーブル | 0 通常<br>1 すべてのレジスタを<br>デフォルトにリセット | 0 0 通常電力<br>0 1 高速リカバリ<br>1 0 スタンバイ<br>1 1 全パワー・ダウ | 0 0 CCDモード<br>0 1 AUX1モード<br>1 0 AUX2モード<br>1 1 テストのみ |    |    |

\*0に設定する必要があります。 \*\*11に設定する必要があります。

表 III VGAゲイン・レジスタの内容（デフォルト値：x096）

表 IV クランプ・レジスタの内容（デフォルト値：x080）

表 V 制御レジスタの内容（デフォルト値：x000）

| D 10 | データ出力<br>D 9          | D 8 D 7 | DATACLK<br>D 6                     | CLP/PBLK<br>D 5          | SHP/SHD<br>D 4           | CDS ゲイン<br>D 3         | D 2 D 1 D 0 |

|------|-----------------------|---------|------------------------------------|--------------------------|--------------------------|------------------------|-------------|

| X    | 0 イネーブル<br>1 スリー・ステート | 0* 0*   | 0 立ち上がりエッジ・トリガー<br>1 立ち下がりエッジ・トリガー | 0 アクティブ・ロー<br>1 アクティブ・ハイ | 0 アクティブ・ロー<br>1 アクティブ・ハイ | 0 ディスエーブル**<br>1 イネーブル | 0* 0* 0*    |

\*0に設定する必要があります

\*D3=0 (GDSゲイン・ディジタルエーブル) のときには、GDSゲイン・レジスタは4dB (コードは63 (10進数)) に固定されます。

表 VI CDSゲイン・レジスタの内容（デフォルト値：x000）

\*CDSゲイン・レジスタを使用するためには、制御レジスタのピットD3をハイに設定する必要があります。

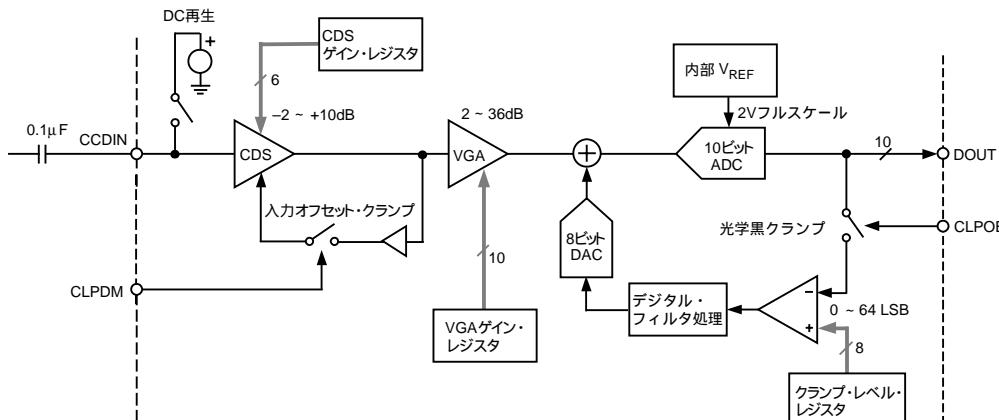

図11 CCDモードのブロック図

### 回路の説明および動作

図11にAD9840Aのシグナル・プロセス・チェーンを示します。各処理ステップは、CCDピクセルの生データから高品質な画像を得るために不可欠なものです。

#### DC再生

CCD出力信号の大きなDCオフセットを低減するために、DC再生回路が外部の $0.1\mu F$ の直列カッピング・コンデンサとともに用いられています。これにより、CCD信号のDCレベルは約1.5Vまで再生され、AD9840Aの3V単電源とコラボレートとなります。

#### 相關ダブル・サンプラー

CDS回路は各CCDピクセルを2回サンプリして、ビデオ情報を抽出し、低周波ノイズを阻止します。図5に示すタイミングは、CDSの2つのクロックであるSHPおよびSHDを用いて、それぞれ、CCD信号のリフレンス・レベルおよびデータ・レベルをサンプリする様子を示したもので。CCD信号は、SHPおよびSHDの立ち上がりエッジでサンプリされます。これらの2つのクロック信号の位置は、CCDの性能を最大限に発揮させるために重要です。SHP/SHDの内部の遅延( $t_{ID}$ )は3nsであり、これは、内部の伝播遅延によって発生します。

CDS段は、デフォルトで4dBのゲインを持っていますが、ユニークなアーキテクチャにより、CDSのゲインを変更することができます。CDSゲイン・レジスタを使用することにより、ゲインは、2の補数のコードを用いて、-2 ~ +10dBの範囲で64ステップで変化させられます。図12にCDSのゲイン特性を示します。CDSゲイン・レジスタを用いてCDSのゲインを変更するためには、制御レジスタのビットD3をハイ(CDSゲイン・イネーブル)に設定する必要があります。制御レジスタのビットD3がロー(CDSゲイン・ディスエーブル)のときのデフォルトのゲイン設定は4dBです。詳細は表VおよびVIを参照してください。

CDSのゲインを4dBとすると、ある程度のフロント・エンド信号に対するゲインが得られ、全体的なS/N比が向上します。このゲイン設定は、大部分のアプリケーションにおいて非常に有効であり、CCDモードの仕様は、このデフォルトのゲイン設定におけるものです。しかしながら、特定のアプリケーションにおいては、AD9840Aの動作を最適化するためにCDSのゲインを変更することができます。CDSゲインを大きくすることは出力レベルの低いICCDにおいて有用であり、CDSゲインを小さくすることはAD9840Aによる1Vp-pを超える振幅を持ったCCD信号の受け入れが可能になります。表VIIIに、異なる最大信号振幅に対するいくつかのCDSゲイン設定の例を示します。CDSのゲイン・レジスタは、出力レベルを「直ちに」+6dB増幅または-6dB減衰に設定できます。CDSの出力レベルを1.5 ~ 1.6V超えないようにすることが最善です。

表 VII CDSゲイン設定の例

| 最大入力信号   | 推奨ゲイン範囲  | レジスタのコード範囲 |

|----------|----------|------------|

| 250mVp-p | 8 ~ 10dB | 21 ~ 31    |

| 500mVp-p | 6 ~ 8dB  | 10 ~ 21    |

| 800mVp-p | 4 ~ 6dB  | 63 ~ 10    |

| 1Vp-p    | 2 ~ 4dB  | 53 ~ 63    |

| 1.25Vp-p | 0 ~ 2dB  | 42 ~ 53    |

| 1.5Vp-p  | -2 ~ 0dB | 32 ~ 42    |

図12 CDSのゲイン特性

入力クランプ

CCDの光学黒オフセットを除去するために、ラインレート入力クランピング回路が用いられています。このオフセットは、CCDのシールドされた黒リフレンス・ピクセルに存在します。一部のAFEのアーキテクチャと異なり、AD9840Aは、このオフセットを入力段で除去することにより、通常「ゲイン・ステップ」と呼ばれるシステムの黒レベルにおけるゲインの変化による影響を最小化しています。入力段でこのオフセットを除去することによる他の利点としては、システムのヘッドルームを最大化することができます。一部の領域CCDは大きな黒レベル・オフセット電圧を持っており、これが入力段で修正されない場合には、VGAゲインが高く設定されたときに、内部回路で利用可能なヘッドルームを著しく減少させます。

図6に、水平タイミングを示します。CCDのダーク・ピクセルが有効な間は、CLPDMパルスの使用が推奨されます。

CLPDMパルスは、光学黒ピクセルの間、CLPOBと共にまたはCLPOBと独立して使用することができます。

# AD9840A

## 可変ゲイン・アンプ

VGA段では2~36dBのゲイン範囲が与えられ、シリアル・デジタル・インターフェースを介して10ビットの分解能でプログラムすることができます。CDS段の標準的な4dBのゲインとの組合せにより、AD9840Aの全体としてのゲインの範囲は6~40dBとなります。6dBのゲインにより、1Vの入力信号はフルスケールが2VのA/Dコンバータに整合します。フルスケールが1Vのシステム(例えばADIのAD9803)と比較すると、等価なゲイン範囲は0~34dBとなります。

VGAゲインの特性は、2つの領域に分割されます。VGAゲイン・レジスタのコードが0~511の間では、特性曲線が、 $\alpha(1+x)/(1-x)$ の形となり、これは「dBにおいて直線」の特性に類似します。コードが512~1023の間では、特性曲線は「dBにおいて直線」となります。任意のゲイン・レジスタの値についてのVGAゲインは、次の2つの式により算出できます。

コード範囲 ゲインの式(CDSのゲインは含まれていません)

$$0 \sim 511 \quad \text{Gain} = 20\log_{10}( [658 + \text{code}] / [658 - \text{code}] ) - 0.35$$

$$512 \sim 1023 \quad \text{Gain} = (0.0354 \times \text{code}) - 0.35$$

これらの2つの式を用いてAD9840Aの実際のゲインを±0.5dBの精度で求められます。CCDモードの仕様に示したように、VGAゲインは2~36dBまでの仕様しか規定されていません。これは、VGAのコード範囲の91~1023に対応します。ゲイン精度についての仕様には4dBのCDSゲインも含まれており、全体としてのゲイン範囲は6~40dBとなります。

図13 VGAゲインの特性曲線

## 光学黒クランプ

光学黒クランプ・ループは、シグナル・チェーンに残留するオフセットを除去し、CCDの黒レベルの低周波変動に追随するために使用されます。各走査線の光学黒(シールドされているピクセル・インターバルの間、A/Dコンバータの出力は、ユーザがクランプ・レベル・レジスタにより選択した一定の黒レベル・リファレンスと比較されます。0~64LSBの間の任意の値を8ビットの分解能でプログラムできます。これにより得られた誤差信号はノイズを低減するためにフィルタ処理され、修正値がD/Aコンバータを介してA/Dコンバータの入力に与えられます。通常は、光学黒クランプ・ループは走査線1本ごとに動作しますが、特定のアプリケーションでは、このループをより遅く更新することもできます。後処理の間に外部デジタル・クランプ処理が使用される場合には、

AD9840Aの光学黒クランプは、動作レジスタのビットD5(「シリアル・インターフェース・タイミングおよび内部レジスタの説明」の項参照)によりディスエーブルできます。ループがディスエーブルにされたときでも、クランプ・レベル・レジスタによってプログラマブルなオフセット調整が可能です。

図6に水平タイミングを示します。CLPOBパルスは、CCDの光学黒ピクセルの間に発生させる必要があります。クランプ・ノイズを最小化するためには、CLPOBパルスの期間を最低でも20ピクセルの幅にすることを推奨します。より狭いパルス幅にもできますが、クランプ・ノイズが増加し、ループの黒レベルの低周波における変化に追随する性能が低下するおそれがあります。

## A/Dコンバータ

AD9840Aは高性能のA/Dコンバータのアーキテクチャを採用しており、高速および低消費電力に最適化されています。微分非直線性(DNL)の特性は、標準的には0.5LSBより良好です。アナログ・デバイセズのAD9801およびAD9803のような従来の製品に採用されていた1Vのフルスケール・レンジの替わりに、AD9840AのA/Dコンバータは、2Vの入力レンジを採用しています。A/Dコンバータのフルスケール・レンジを拡張することにより、ノイズ特性が向上しています。

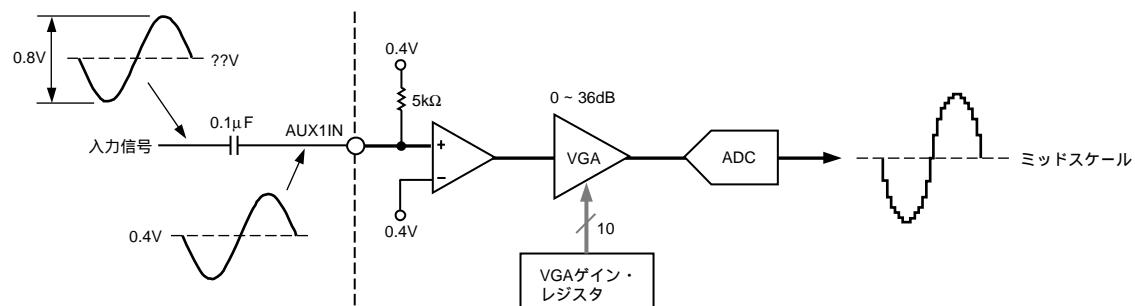

## AUX1モード

CDSを必要としないアプリケーションのために、AD9840AはACカップリングされた波形をサンプルするように設定できます。図14に、AUX1チャンネル入力(36ピン)を用いた回路設定を示します。入力信号ドライバとAUX1INピンの間に0.1μFのACカップリング・コンデンサを1つ設置する必要があります。オンチップのDCバイアス回路が、入力信号の平均値を約0.4Vに設定し、A/Dコンバータのミッドスケール・コードへのリファレンスを与えます。VGAゲイン・レジスタは、この動作モードVGAゲインの特性曲線(図13を参照)で0~36dBまでのゲイン範囲を与えます。VGAは、0.4Vのバイアス・レベルに対して、信号レベルにゲインを与えます。バイアス・レベルより高い信号レベルは、さらに増加してより高いADCのコードとなり、バイアス・レベルより低い信号レベルは、さらに減少してより低いADCのコードとなります。

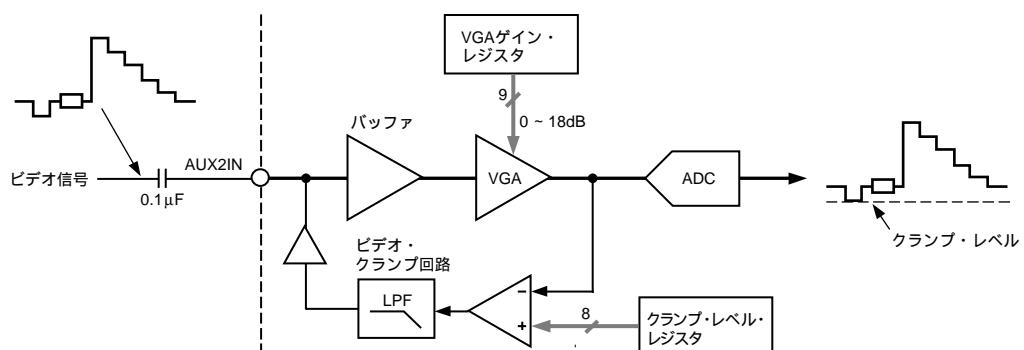

## AUX2モード

NTSCやPALの信号のようなビデオ領域の波形をサンプルするために、AUX2チャンネルは黒レベルのクランプ処理、ゲイン調整、A/D変換を行います。図15に、AUX2チャンネル入力(34ピン)を使用した回路設定を示します。オンチップのビデオ・クランプ回路には外付けの0.1μFのプロッキング・コンデンサを付加して、入力信号を、目的のリファレンス・レベルにレベル・シフトします。クランプ回路は、入力信号の負極性側の最も振幅の大きな部分を自動的に検知し、入力コンデンサの両端にかかる電圧を調整します。これにより、入力信号の黒レベルを強制的にクランプ・レベル・レジスタシリアル・インターフェース・レジスタの説明を参照)にプログラムされた値に等しくします。VGAは、0~18dBの間でゲイン調整を行います。同様なVGAゲイン・レジスタも使用されますが、ゲイン・レジスタの9個のMSB側ビットのみが使用されます。(表III参照)

図14 AUX1回路設定

図15 AUX2回路設定

表 VIII AUX2モードで使用されるVGAゲイン・レジスタ

| D10 | MSB |    |    |    |    |    |    |    |    |    |     | LSB<br>D0 | ゲイン(dB) |

|-----|-----|----|----|----|----|----|----|----|----|----|-----|-----------|---------|

|     | D9  | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |     |           |         |

| X   | 0   | X  | X  | X  | X  | X  | X  | X  | X  | X  | 0.0 | 0.0       | .       |

|     | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0.0 | 0.0       | .       |

|     |     |    |    |    |    |    |    |    |    |    |     | .         | .       |

|     |     |    |    |    |    |    |    |    |    |    |     | .         | .       |

|     |     |    |    |    |    |    |    |    |    |    |     |           | 18.0    |

|     | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |     |           |         |

# AD9840A

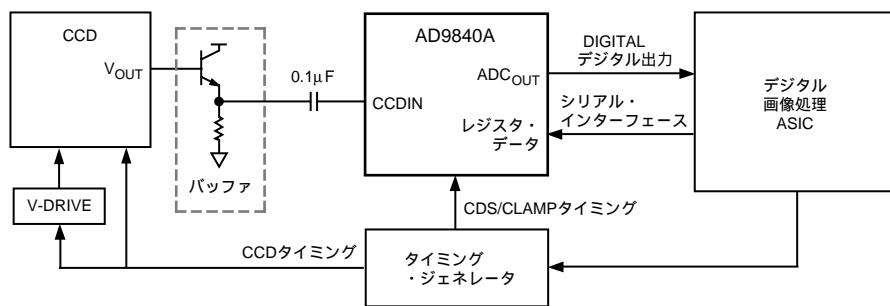

図33 CCDモードの推奨回路構成

## アプリケーション情報

AD9840Aは、デジタル・スチル・カメラやビデオ・カメラのアプリケーション用の完全なアナログ・フロント・エンド (Analog Front End, AFE) 製品です。図16に示すように、CCDの画像（ピクセル）データは、バッファされ、直列の入力コンデンサを通過してAD9840Aのアナログ入力に送られます。AD9840Aは、DC再生、CDS、ゲイン調整、黒レベル修正、A/D変換を実行します。次に、AD9840Aのデジタル出力・データは画像処理ASICにより処理されます。AD9840Aの内部レジスタ（ゲイン、オフセット・レベル、他の機能の制御に用いられる）は、3線式のシリアル・データ・インターフェースを介してASICまたはマイクロプロセッサによってプログラマれます。システムのタイミング・ジェネレータは、CCDおよびAFEの双方にクロック信号を供給します。

## 内部パワーオン・リセット回路

AD9840Aは、パワーオンの後で、自動的にすべての内部レジスタをリセットし、内部のキャリブレーションのプロシージャを実行します。これらの処理が完了するまでの時間は約0.1msです。この間、通常のクロック信号およびシリアル書き込み動作が発生することがあります。しかしながら、内部リセット動作が完了するまでは、シリアル・レジスタへの書き込みは無視されます。ピン43（従来のAD9843でAの添え字がないものではRSTB）は、AD9840Aではリセット動作のために使用しません。AD9840Aでは、43ピンをトグル操作しても、動作に影響を与えません。

グラウンド処理およびデカップリングについての推奨事項図17に示すように、AD9840Aについては単一のグラウンド・プレーンが推奨されます。このグラウンド・プレーンは、特にピン25から39の周辺では、できる限り連続したものとします。これにより、すべてのアナログ・デカップリング・コンデンサによって、電源とバイパスピンおよび対応するグラウンド・ピンの間でインピーダンスを最小限とした経路を構成することができます。すべてのデカップリング・コンデンサは、パッケージ・ピンのなるべく近くに設置します。AD9840Aについては、単一のノイズの少ないクリーンな電源が推奨されますが、DRVDD (13pin) については、別個のデジタル・ドライバ電源を使用することもできます。DRVDDは、常に、DRVSS (14pin) に対してデカップリングしておく必要があります、これをアナログ・グラウンドのプレーンに接続する必要があります。

別個のデジタル・ドライバ電源を用いることにより、低い電圧 (2.7V) での2.7VのASICに適合、デジタルの消費電力の低減、ノイズのカッピングの可能性の低減などの利点を得ることができます。デジタル出力（ピン3～12）が、20pFを超える負荷をドライブする必要がある場合には、デジタル・コードの遷移によるノイズを低減するために、バッファ処理を行うことが推奨されます。これに代わり、デジタル出力ピンの近くに直列抵抗を設置することによってノイズを低減できる場合もあります。

図17 CCDモードにおける推奨回路設定

# AD9840A

## 外形寸法

サイズはインチと (mm) で示します。

14 ピン LQFP

(ST-48)