## 特長

シングル・レーン: 2:1 Mux/1:2 Demux

データレート: 3.2Gbps~DC

次のいずれかの機能により、3.2Gbpsで40インチを超える

FR4バックプレーンを補償:

2つの入力レベル・イコライゼーション

4つのレベルの出力プリエンファシス

ACまたはDC結合の差動入出力動作

低い確定ジッタ: 16ps p-p (typ)

低いランダム・ジッタ: 500fs RMS (typ)

オンチップ終端

1:2デマルチプレクサ機能でユニキャスト/バイキャストに対応

全ポート上のループバック機能

3.3Vコア電源

フレキシブルな入出力電源

低消費電力: 基本構成で200mW (typ)<sup>1</sup>

32ビンLFCSPパッケージ

動作温度範囲: -40~+85°C

## アプリケーション

低価格の冗長スイッチ

SONET OC48/SDH16および低データレート

バックプレーン上を伝送するギガビット イーサネット

バックプレーン上を伝送する1.06Gbps/2.12Gbps

ファイバ・チャンネル

シリアル高速IO

PCI Express Gen1

バックプレーンのInfiniBand

## 概要

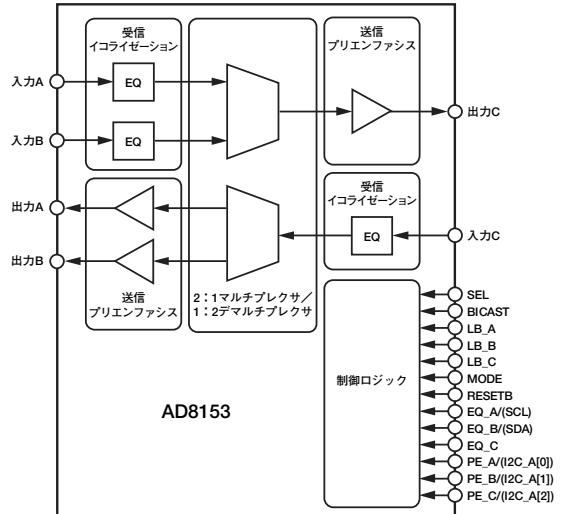

AD8153は、3個の差動CML入力と3個の差動CML出力を備えたプロトコル不問の非同期シングル・レーン2:1スイッチです。Xstream 製品ラインに属するもう一つのAD8159は、複数のレーンを必要とする同種のアプリケーションに適しています。

AD8153は、NRZ信号処理（ポート当たりの最大データレート 3.2Gbps）用に動作が最適化されています。各ポートは、2つのレベルの入力イコライゼーションと4つのレベルの出力プリエンファシスが設定できます。

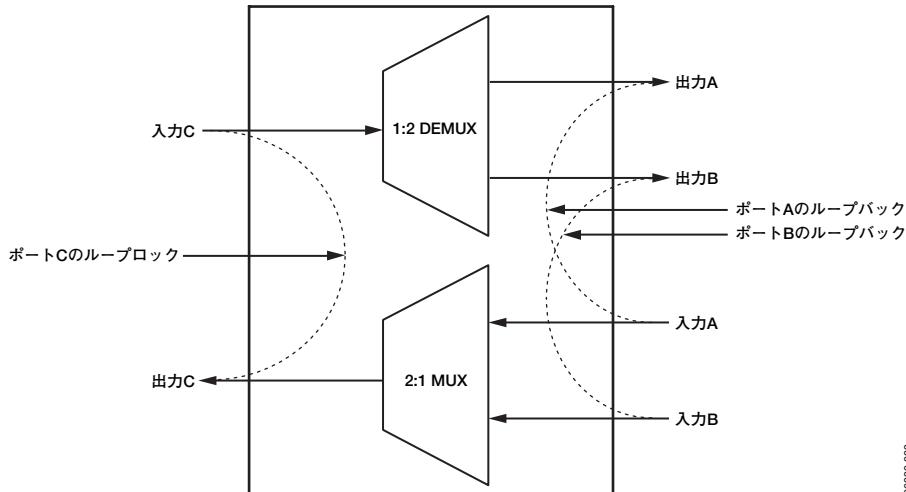

AD8153は、2:1マルチプレクサ（MUX）と1:2デマルチプレクサ（DEMUX）で構成されています。このデバイスには、ピン・モード、シリアル・モード、ミックスド・モードという3つの動作モードがあります。ピン・モードでは、外部ピンを使ってレーンの切替え、イコライゼーション、プリエンファシスの制御のみを行います。シリアル・モードでは、I<sup>2</sup>C イン

## 機能ブロック図

図1

ターフェースを使ってデバイスの制御を行います。このモードでは、追加のプリエンファシス設定、出力ディスエーブルなどのアドバンスト機能にアクセスできます。ミックスド・モードではI<sup>2</sup>C機能を使ってアドバンスト機能にアクセスできますが、外部ピンを使ってレーンの切替えを制御することもできます。

AD8153は、主にシリアル・リンクのライン・インターフェース側とバックプレーン側の両方で冗長性を可能にするために使用します。ユニキャスト/バイキャスト機能を備えているため、1+1または1:1の冗長性に対応できます。

バイキャスト・モードとループバック・モードを組み合せて使用し、受信データを複製してそれを目的のポートと試験装置に同時に送信すれば、高速シリアル・リンクをテストすることもできます。

<sup>1</sup> プリエンファシスなしで2ポートがアクティブ

## 目次

|                         |    |                                |    |

|-------------------------|----|--------------------------------|----|

| 特長                      | 1  | 送信ブリエンファシス                     | 14 |

| アプリケーション                | 1  | I <sup>2</sup> Cシリアル制御インターフェース | 15 |

| 機能ブロック図                 | 1  | レジスタ設定                         | 15 |

| 概要                      | 1  | 一般的な機能                         | 15 |

| 改訂履歴                    | 2  | I <sup>2</sup> Cデータ書き込み        | 16 |

| 仕様                      | 3  | I <sup>2</sup> Cデータ読み出し        | 17 |

| I <sup>2</sup> Cタイミング仕様 | 4  | アプリケーション情報                     | 18 |

| 絶対最大定格                  | 5  | PCB設計のガイドライン                   | 19 |

| ESDに関する注意               | 5  | AD8153とのインターフェース               | 20 |

| ピン配置と機能の説明              | 6  | 端子の構造                          | 20 |

| 代表的な性能特性                | 7  | 入力信号の守るべき条件                    | 20 |

| 動作原理                    | 13 | 出力信号の守るべき条件                    | 21 |

| スイッチ設定                  | 13 | 外形寸法                           | 22 |

| 受信イコライゼーション             | 14 | オーダー・ガイド                       | 22 |

## 改訂履歴

4/07—Revision 0: Initial Version

## 仕様

特に指定のない限り、 $V_{CC}=V_{TTI}=V_{TTO}=3.3V$ 、 $V_{EE}=0V$ 、 $R_L=50\Omega$ 、2出力アクティブ、プリエンファシスなし、データレート＝3.2Gbps、AC結合、PRBS7テスト・パターン、 $V_{ID}=800mVp-p$ 、 $T_A=25^\circ C$ 。<sup>1</sup>

表1

| パラメータ                    | 条件                                               | Min          | Typ          | Max          | 単位                        |

|--------------------------|--------------------------------------------------|--------------|--------------|--------------|---------------------------|

| <b>動的性能</b>              |                                                  |              |              |              |                           |

| データレート／チャンネル (NRZ)       |                                                  | DC           |              | 3.2          | Gbps                      |

| データレート=3.2Gbps、ハイレベルEQ   |                                                  |              | 16           |              | ps p-p                    |

| ディターミニスティック・ジッタ          |                                                  |              | 500          |              | fs                        |

| ランダム・ジッタ                 |                                                  |              | 640          |              | ps                        |

| 伝播遅延                     | 入力から出力まで                                         |              | 55           |              | ps                        |

| レーン間スキュー                 |                                                  |              | 5            |              | ns                        |

| スイッチ切替え時間                |                                                  |              | 85           |              | ps                        |

| 出力立上がり／立下がり時間            | 20~80%                                           |              |              |              |                           |

| <b>入力特性</b>              |                                                  |              |              |              |                           |

| 入力電圧振幅                   | 差動                                               | 200          | 2000         |              | mV p-p                    |

| 入力電圧範囲                   | 同相電圧、 $V_{ID}=800mVp-p$                          | $V_{EE}+1.0$ | $V_{CC}+0.3$ |              | V                         |

| 入力容量                     |                                                  | 2            |              |              | pF                        |

| <b>出力特性</b>              |                                                  |              |              |              |                           |

| 出力電圧振幅                   | 差動、@DC                                           | 700          | 800          | 900          | mV p-p                    |

| 出力電圧範囲                   | シングルエンド絶対電圧レベル                                   | $V_{CC}-1.6$ |              | $V_{CC}+0.6$ | V                         |

| 出力電流                     | プリエンファシスなし                                       |              | 16           |              | mA                        |

| 出力電流                     | 最大プリエンファシス、全ポート                                  |              | 28           |              | mA                        |

| 出力容量                     |                                                  |              | 2            |              | pF                        |

| <b>終端特性</b>              |                                                  |              |              |              |                           |

| 抵抗                       | 差動                                               |              | 100          |              | $\Omega$                  |

| 温度係数                     |                                                  |              | 0.1          |              | $\Omega/\text{ }^\circ C$ |

| <b>電源</b>                |                                                  |              |              |              |                           |

| 動作範囲                     |                                                  |              |              |              |                           |

| $V_{CC}$                 | $V_{EE}=0V$                                      | 3.0          | 3.3          | 3.6          | V                         |

| $V_{TTI}$                | $V_{EE}=0V$                                      |              | $V_{CC}$     |              | V                         |

| $V_{TTO}$                | $V_{EE}=0V$                                      |              | $V_{CC}$     |              | V                         |

| 電源電流                     | 2出力アクティブ、プリエンファシスなし、<br>400mV I/O振幅 (800mVp-p差動) | 27           | 31           | 35           | mA                        |

| $I_{CC}$                 |                                                  | 26           | 32           | 39           | mA                        |

| $I_{IO}=I_{TTO}+I_{TTI}$ |                                                  |              |              |              |                           |

| 電源電流                     | 3出力アクティブ、最大プリエンファシス、<br>400mV I/O振幅 (800mVp-p差動) | 53           | 58           | 63           | mA                        |

| $I_{CC}$                 |                                                  | 74           | 84           | 95           | mA                        |

| $I_{IO}=I_{TTO}+I_{TTI}$ |                                                  |              |              |              |                           |

| <b>熱特性</b>               |                                                  |              |              |              |                           |

| 動作温度範囲                   |                                                  | -40          |              | +85          | $^\circ C$                |

| $\theta_{JA}$            | 自然空冷                                             |              | 30.0         |              | $^\circ C/W$              |

| <b>ロジック入力特性</b>          |                                                  |              |              |              |                           |

| ハイレベル入力電圧 ( $V_{IH}$ )   |                                                  | 2.4          |              | $V_{CC}$     | V                         |

| ローレベル入力電圧 ( $V_{IL}$ )   |                                                  | $V_{EE}$     |              | 0.8          | V                         |

<sup>1</sup>  $V_{ID}$ ：入力差動電圧振幅

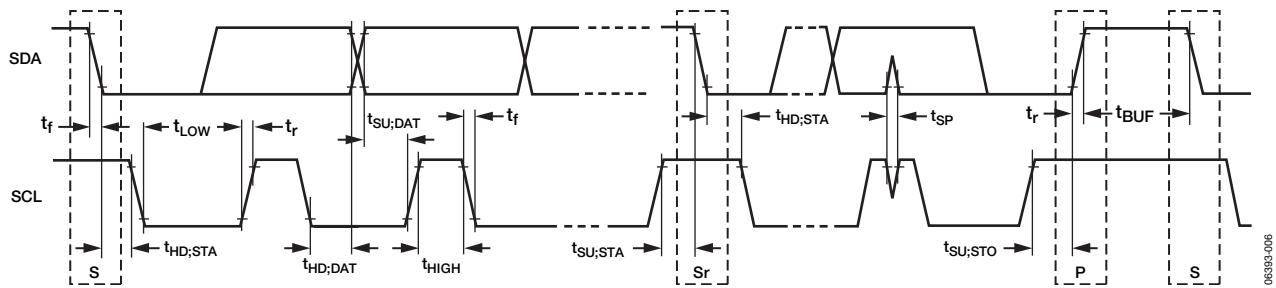

I<sup>2</sup>Cタイミング仕様図2. I<sup>2</sup>Cタイミング仕様

表2

| パラメータ                    | 記号           | Min | Max  | 単位  |

|--------------------------|--------------|-----|------|-----|

| SCLクロック周波数               | $f_{SCL}$    | 0   | 400+ | kHz |

| スタート条件のホールド時間            | $t_{HD:STA}$ | 0.6 | —    | μs  |

| 反復スタート条件のセットアップ時間        | $t_{SU:STA}$ | 0.6 | —    | μs  |

| SCLクロックのローレベル期間          | $t_{LOW}$    | 1.3 | —    | μs  |

| SCLクロックのハイレベル期間          | $t_{HIGH}$   | 0.6 | —    | μs  |

| データ・ホールド時間               | $t_{HD:DAT}$ | 0   | —    | μs  |

| データ・セットアップ時間             | $t_{SU:DAT}$ | 10  | —    | ns  |

| SDAとSCLの立上がり時間           | $t_r$        | 1   | 300  | ns  |

| SDAとSCLの立下がり時間           | $t_f$        | 1   | 300  | ns  |

| ストップ条件のセットアップ時間          | $t_{SU:STO}$ | 0.6 | —    | μs  |

| ストップ条件とスタート条件の間のバス・フリー時間 | $t_{BUF}$    | 1   | —    | ns  |

| 各I/Oピンの容量                | $C_i$        | 5   | 7    | pF  |

## 絶対最大定格

表3

| パラメータ                | 定格値                                      |

|----------------------|------------------------------------------|

| $V_{CC} \sim V_{EE}$ | 3.7V                                     |

| $V_{TTI}$            | $V_{CC} + 0.6V$                          |

| $V_{TTO}$            | $V_{CC} + 0.6V$                          |

| 内部電力消費               | 4.1W                                     |

| 差動入力電圧               | 2.0V                                     |

| ロジック入力電圧             | $V_{EE} - 0.3V < V_{IN} < V_{CC} + 0.6V$ |

| 保存温度範囲               | -65 ~ +125°C                             |

| ピン温度                 | 300°C                                    |

| ジャンクション温度            | 150°C                                    |

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### ESDに関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

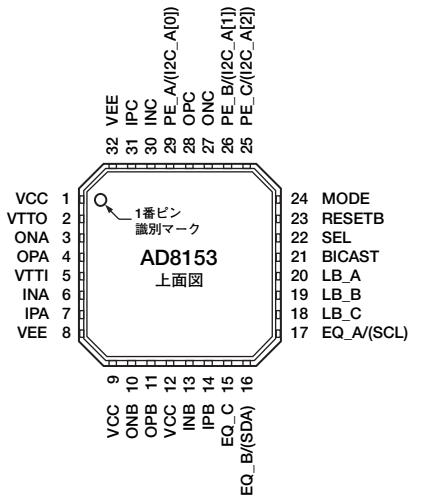

## ピン配置と機能の説明

注

EPADはVEEに電気的に接続する必要があります。

06393-02

図3. ピン配置

表4. ピン機能の説明

| ピン番号      | 記号              | タイプ | 説明                                                        |

|-----------|-----------------|-----|-----------------------------------------------------------|

| 1、9、12    | VCC             | 電源  | 正側電源                                                      |

| 2         | VTTO            | 電源  | 出力終端電源                                                    |

| 3         | ONA             | I/O | 高速反転出力                                                    |

| 4         | OPA             | I/O | 高速出力                                                      |

| 5         | VTTI            | 電源  | 入力終端電源                                                    |

| 6         | INA             | I/O | 高速反転入力                                                    |

| 7         | IPA             | I/O | 高速入力                                                      |

| 8、32、EPAD | VEE             | 電源  | 負側電源                                                      |

| 10        | ONB             | I/O | 高速反転出力                                                    |

| 11        | OPB             | I/O | 高速出力                                                      |

| 13        | INB             | I/O | 高速反転入力                                                    |

| 14        | IPB             | I/O | 高速入力                                                      |

| 15        | EQ_C            | 制御  | ポートCの入力イコライゼーション制御                                        |

| 16        | EQ_B/(SDA)      | 制御  | ポートBの入力イコライゼーション制御／(MODE=1のときのI <sup>C</sup> データ)         |

| 17        | EQ_A/(SCL)      | 制御  | ポートAの入力イコライゼーション制御／(MODE=1のときのI <sup>C</sup> クロック)        |

| 18        | LB_C            | 制御  | ポートCのループバックをイネーブル                                         |

| 19        | LB_B            | 制御  | ポートBのループバックをイネーブル                                         |

| 20        | LB_A            | 制御  | ポートAのループバックをイネーブル                                         |

| 21        | BICAST          | 制御  | バイキャストをイネーブル                                              |

| 22        | SEL             | 制御  | A/Bの選択                                                    |

| 23        | RESETB          | 制御  | 設定レジスタのリセット                                               |

| 24        | MODE            | 制御  | 設定モード。シリアル／ミックスド・モード：1、ピン・モード：0                           |

| 25        | PE_C/(I2C_A[2]) | 制御  | ポートCのプリエンファシス制御／(MODE=1のときのI <sup>C</sup> スレーブ・アドレス・ビット2) |

| 26        | PE_B/(I2C_A[1]) | 制御  | ポートBのプリエンファシス制御／(MODE=1のときのI <sup>C</sup> スレーブ・アドレス・ビット1) |

| 27        | ONC             | I/O | 高速反転出力                                                    |

| 28        | OPC             | I/O | 高速出力                                                      |

| 29        | PE_A/(I2C_A[0]) | 制御  | ポートAのプリエンファシス制御／(MODE=1のときのI <sup>C</sup> スレーブ・アドレス・ビット0) |

| 30        | INC             | I/O | 高速反転入力                                                    |

| 31        | IPC             | I/O | 高速入力                                                      |

## 代表的な性能特性

特に指定のない限り、 $V_{CC} = V_{TTO} = V_{TTO} = 3.3V$ 、 $V_{EE} = 0V$ 、 $R_L = 50\Omega$ 、2出力アクティブ、プリエンファシスなし、ハイレベルEQ、データレート = 3.2Gbps、AC結合、PRBS7テスト・パターン、 $V_{ID} = 800mVp-p$ 、 $T_A = 25^\circ C$ 。<sup>1</sup>

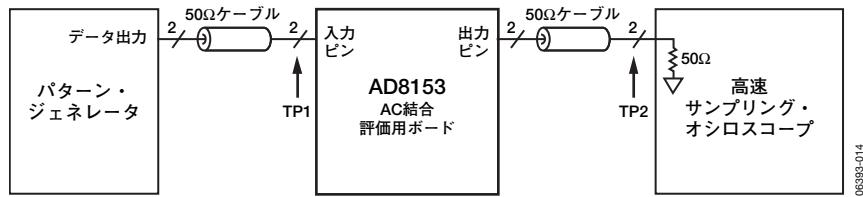

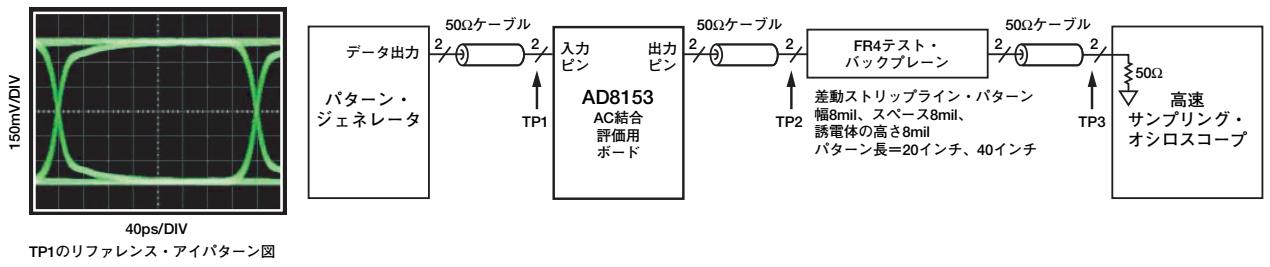

図4. 標準テスト回路（チャンネルなし）

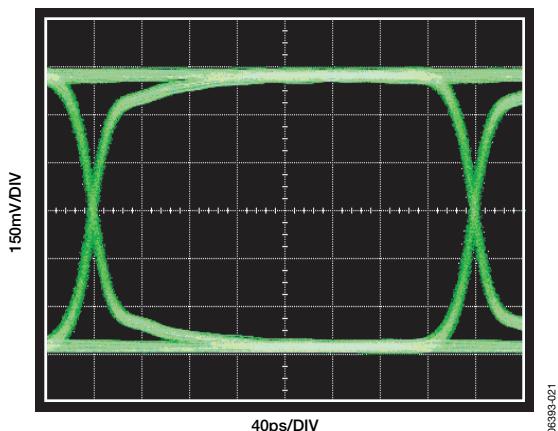

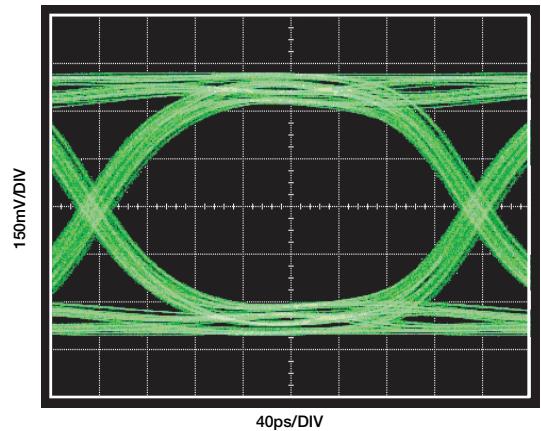

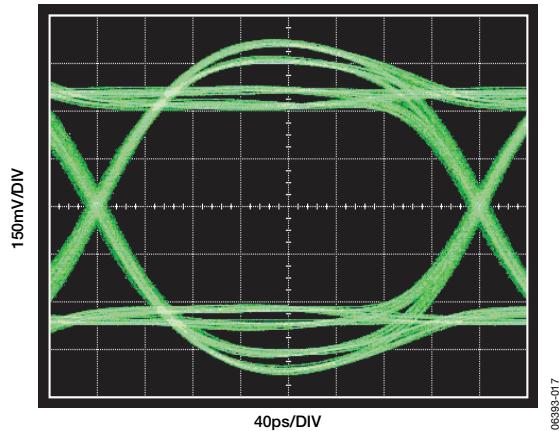

図5. 3.2Gbps入力アイパターン（図4のTP1）

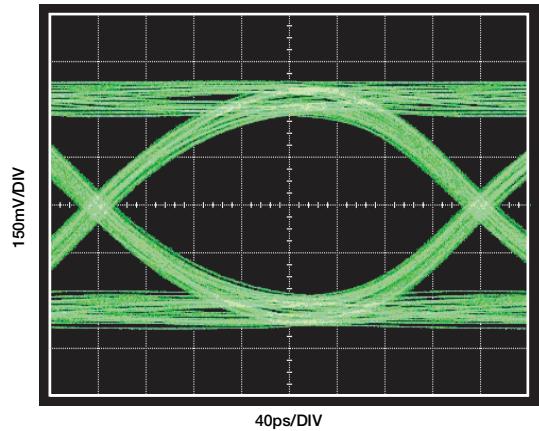

図6. 3.2Gbps出力アイパターン、チャンネルなし

(図4のTP2)

# AD8153

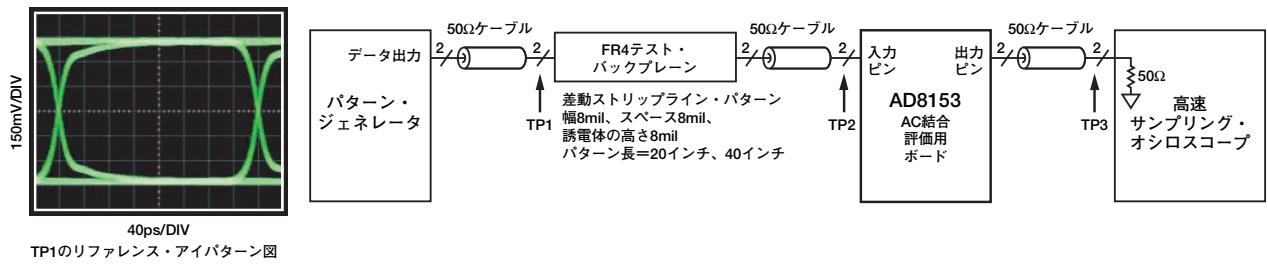

図7. 入力イコライゼーション・テスト回路

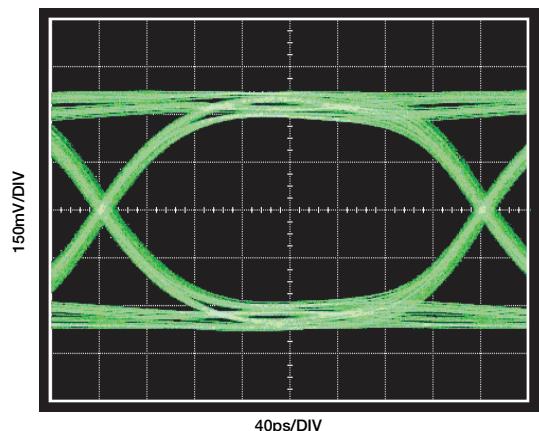

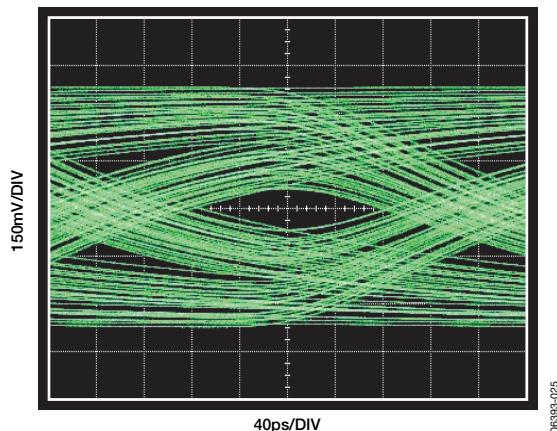

図8. 3.2Gbps入力アイバターン、20インチFR4入力

チャンネル（図7のTP2）

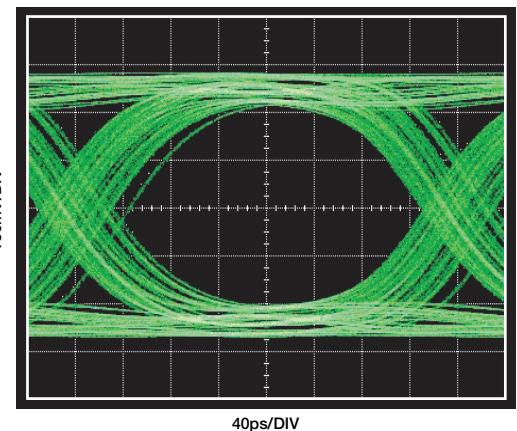

図10. 3.2Gbps出力アイバターン、20インチFR4入力

チャンネル、ハイレベルEQ（図7のTP3）

図9. 3.2Gbps入力アイバターン、40インチFR4入力

チャンネル（図7のTP2）

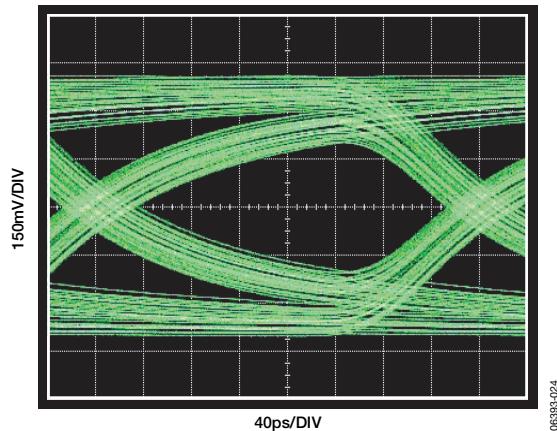

図11. 3.2Gbps出力アイバターン、40インチFR4入力

チャンネル、ハイレベルEQ（図7のTP3）

図12. 出力プリエンファシス・テスト回路

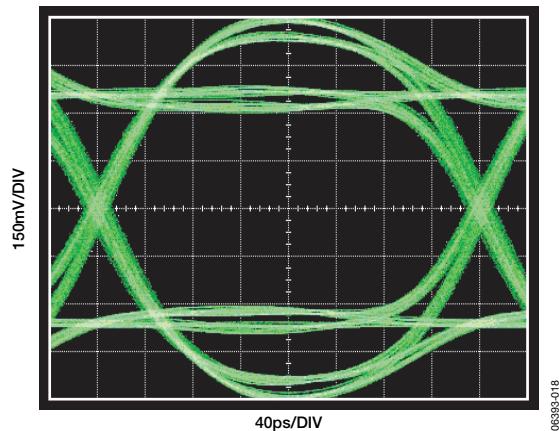

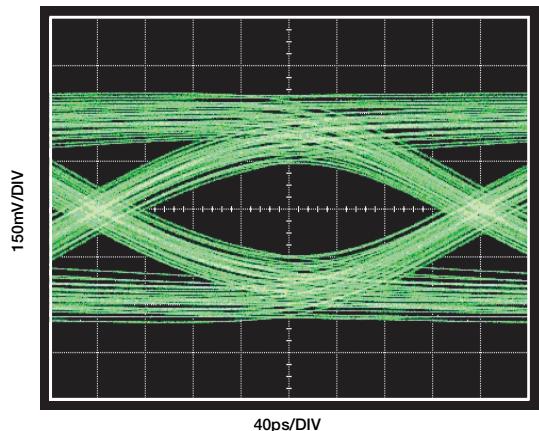

図13. 3.2Gbps出力アイパターン、プリチャンネル、PE=2

(図12のTP2)図15. 3.2Gbps出力アイパターン、20インチFR4出力

チャンネル、PE=2 (図12のTP3)図14. 3.2Gbps出力アイパターン、プリチャンネル、PE=3

(図12のTP2)図16. 3.2Gbps出力アイパターン、40インチFR4出力

チャンネル、PE=3 (図12のTP3)

# AD8153

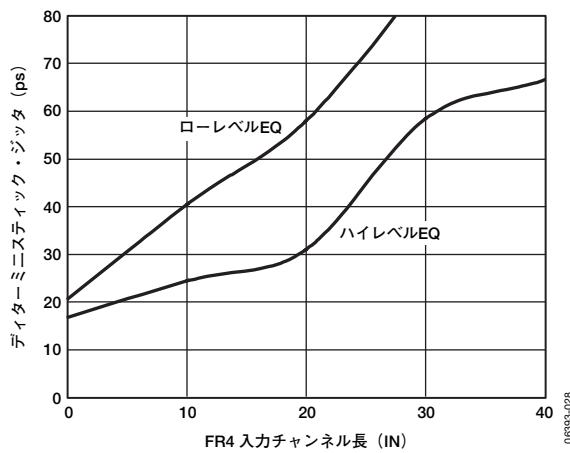

図17. FR4入力チャンネル長 対

ディターミニスティック・ジッタ

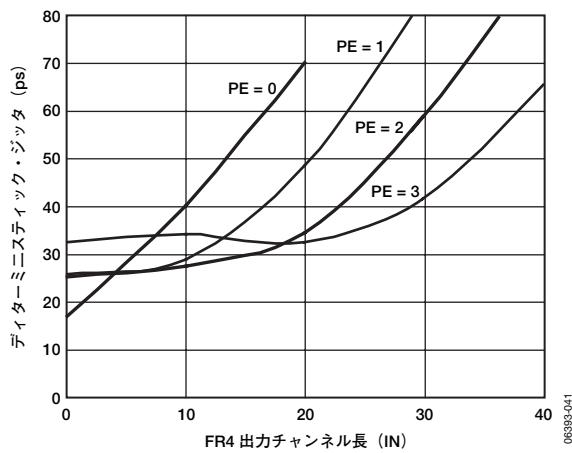

図20. FR4出力チャンネル長 対

ディターミニスティック・ジッタ

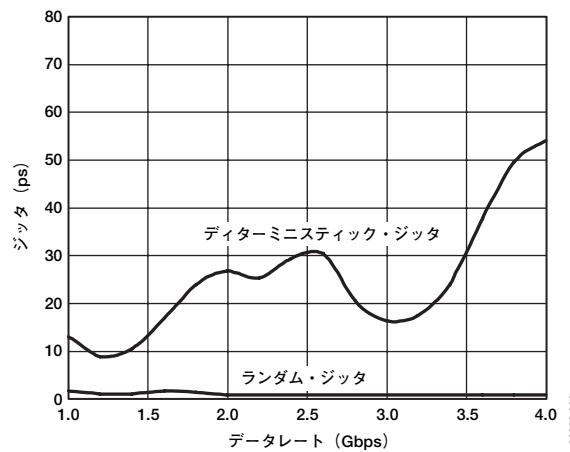

図18. データレート 対 ジッタ

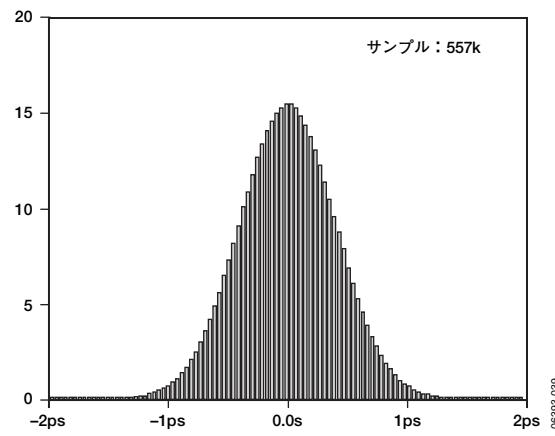

図21. ランダム・ジッタ・ヒストグラム

(3.2Gbps)

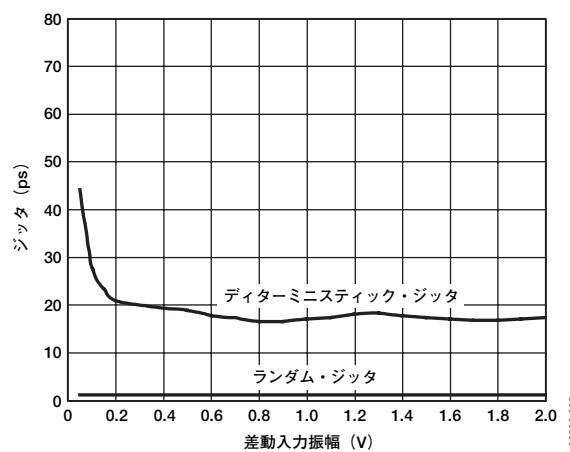

図19. 差動入力振幅 対 ジッタ

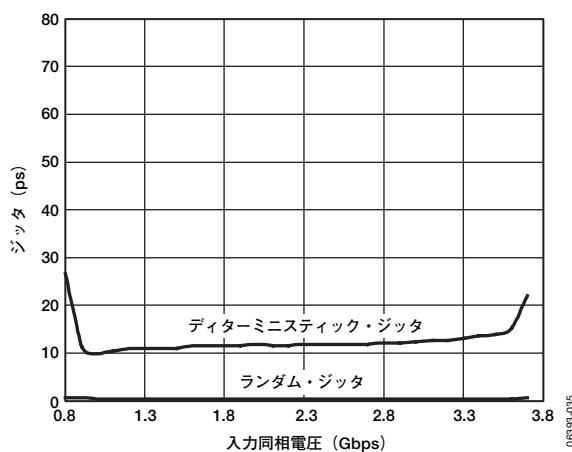

図22. 入力同相電圧 対 ジッタ

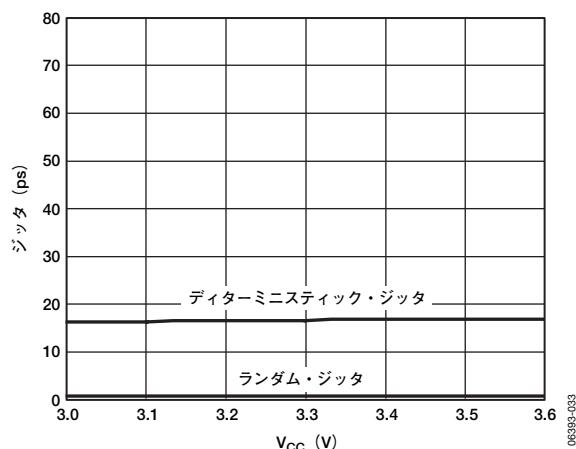

図23. コア電源電圧 対 ジッタ

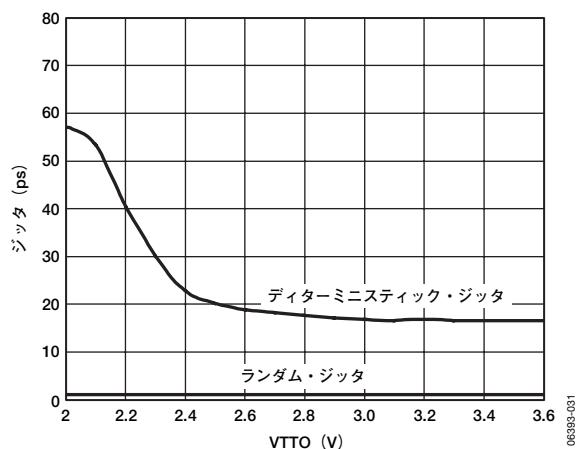

図26. 出力終端電圧 対 ジッタ

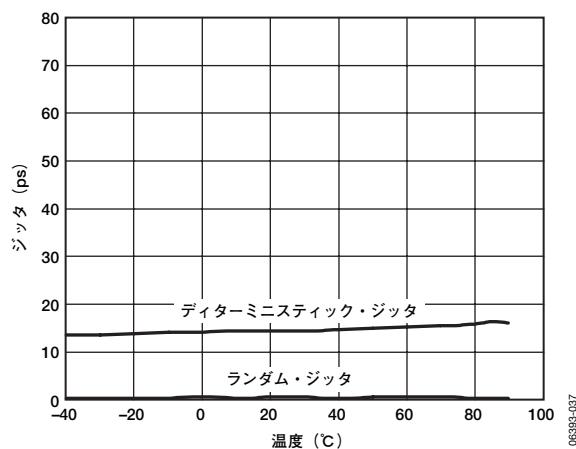

図24. ジッタの温度特性

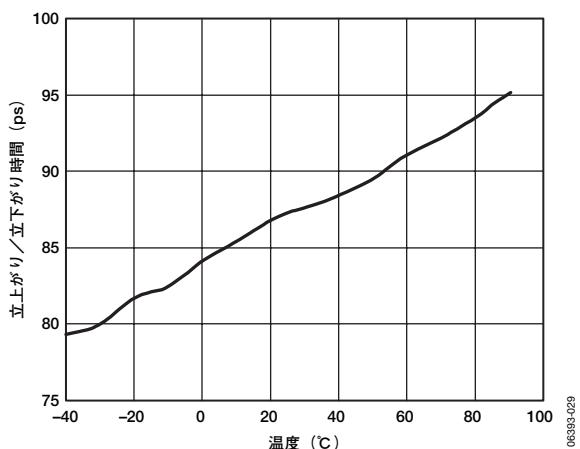

図27. 立上がり／立下がり時間の温度特性

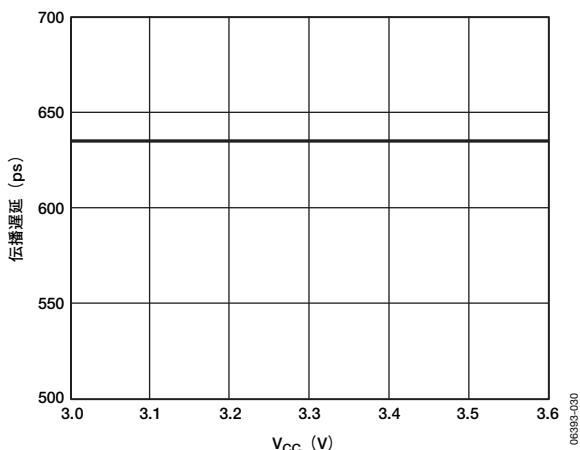

図25. コア電源電圧 対 伝播遅延

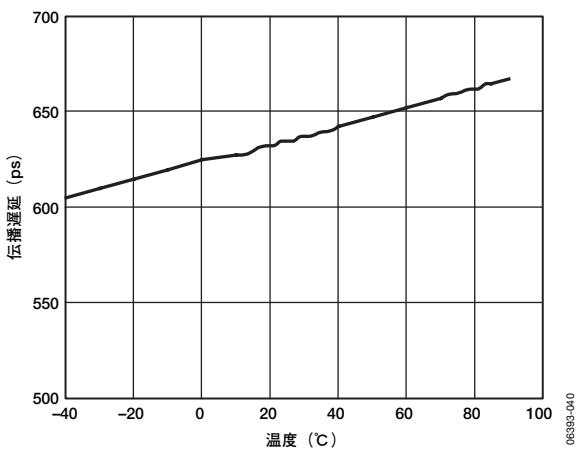

図28. 伝播遅延の温度特性

## AD8153

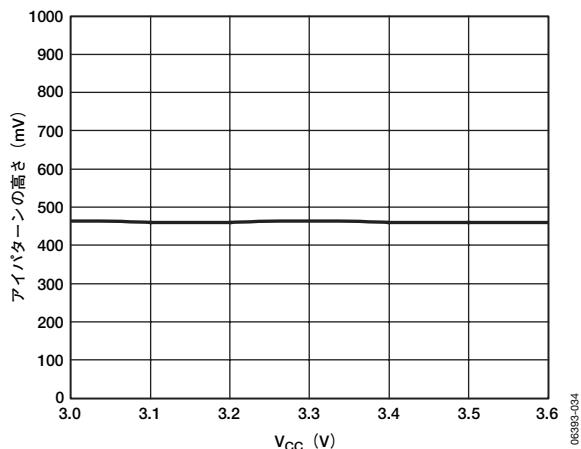

図29. コア電源電圧 対 アイパターーンの高さ

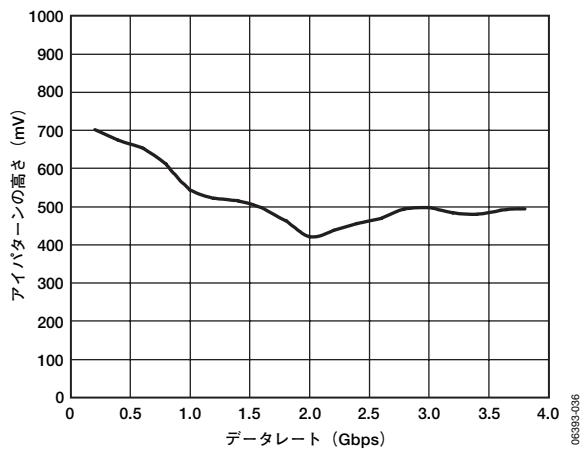

図30. データレート 対 アイパターーンの高さ

## 動作原理

AD8153は、2:1マルチプレクサと1:2デマルチプレクサで構成されています。このデバイスには、ピン・モード、シリアル・モード、ミックスド・モードという3つの動作モードがあります。ピン・モードでは、外部ピンを使ってレーンの切替え、イコライゼーション、プリエンファシスの制御を行います。シリアル・モードでは、I<sup>2</sup>Cインターフェースを使ってデバイスの制御を行います。このモードでは、追加のプリエンファシス設定、出力ディスエーブルなどのアドバンスト機能にアクセスできます。ミックスド・モードでは、I<sup>2</sup>C機能を使ってアドバンスト機能にアクセスできますが、外部ピンを使ってレーンの切替えを制御することもできます。

### スイッチ設定

AD8153のデマルチプレクサ側では、BICASTビットとSELビットの状態に応じて、入力ポートCで受信したデータを出力ポートAとBの一方または両方に送信します。マルチプレクサ側では、SELビットの状態に応じて、入力ポートAまたはBで受信したデータを出力ポートCに送信します。

バイキャスト・モードがオフのときは、ポートAまたはBのどちらかの出力がアイドル状態となります。アイドル状態では、出力のテール電流が0に設定され、レーンのP側とN側が内蔵の終端抵抗を介して出力終端電圧にプルアップされます。

AD8153は、図31に示す全ポートのループバックをサポートしています。任意のポートでループバックをイネーブルにすると、制御ビットのBICASTとSELによる設定があってもループバックされます。表5は、実行可能なスイッチ設定を要約したものです。

AD8153の出力ディスエーブル機能を使って、出力をアイドル（パワーダウン）状態にできます。この機能には、シリアル制御インターフェースを介してのみアクセスできます。

図31. ループバック構成

表5. スイッチ構成

| LB_A | LB_B | LB_C | SEL | BICAST | Output A | Output B | Output C |

|------|------|------|-----|--------|----------|----------|----------|

| 0    | 0    | 0    | 0   | 0      | Input C  | アイドル     | Input A  |

| 0    | 0    | 0    | 0   | 1      | Input C  | Input C  | Input A  |

| 0    | 0    | 0    | 1   | 0      | アイドル     | Input C  | Input B  |

| 0    | 0    | 0    | 1   | 1      | Input C  | Input C  | Input B  |

| 0    | 0    | 1    | 0   | 0      | Input C  | アイドル     | Input C  |

| 0    | 0    | 1    | X   | 1      | Input C  | Input C  | Input C  |

| 0    | 0    | 1    | 1   | 0      | アイドル     | Input C  | Input C  |

| 0    | 1    | 0    | 0   | X      | Input C  | Input B  | Input A  |

| 0    | 1    | 0    | 1   | 0      | アイドル     | Input B  | Input B  |

| 0    | 1    | 0    | 1   | 1      | Input C  | Input B  | Input B  |

| 0    | 1    | 1    | 0   | X      | Input C  | Input B  | Input C  |

| 0    | 1    | 1    | 1   | 0      | アイドル     | Input B  | Input C  |

| 0    | 1    | 1    | X   | 1      | Input C  | Input B  | Input C  |

| 1    | 0    | 0    | 0   | 0      | Input A  | アイドル     | Input A  |

| 1    | 0    | 0    | 0   | 1      | Input A  | Input C  | Input A  |

# AD8153

| LB_A | LB_B | LB_C | SEL | BICAST | 出力A | 出力B  | 出力C |

|------|------|------|-----|--------|-----|------|-----|

| 1    | 0    | 0    | 1   | X      | 入力A | 入力C  | 入力B |

| 1    | 0    | 1    | 0   | 0      | 入力A | アイドル | 入力C |

| 1    | 0    | 1    | X   | 1      | 入力A | 入力C  | 入力C |

| 1    | 0    | 1    | 1   | X      | 入力A | 入力C  | 入力C |

| 1    | 1    | 0    | 0   | X      | 入力A | 入力B  | 入力A |

| 1    | 1    | 0    | 1   | X      | 入力A | 入力B  | 入力B |

| 1    | 1    | 1    | X   | X      | 入力A | 入力B  | 入力C |

## 受信イコライゼーション

バックプレーン・アプリケーションの場合、AD8153は長いパターンによって生じる信号劣化を補償する必要があります。このデバイスは、ポート単位で設定でき2つのレベルの入力イコライゼーションをサポートしています。表6は、各設定と高周波の漸近ゲイン・ブーストを要約したものです。

表6. 受信イコライゼーション設定

| EQ_A/B/C | EQブースト |

|----------|--------|

| 0        | 6dB    |

| 1        | 12dB   |

## 送信プリエンファシス

送信のプリエンファシスのレベルは、I<sup>2</sup>Cインターフェースの使用時にピン制御または制御レジスタによって設定できます。ピン制御では2通りのプリエンファシス設定、制御レジスタではさらに2通りの追加設定を行うことができます。

表7. プリエンファシス設定

| シリアル・モード<br>PE_A/B/C設定 | ピン・モード<br>PE_A/B/C | PEブースト (%) | PEブースト (dB) |

|------------------------|--------------------|------------|-------------|

| 0                      | 0                  | 0          | 0           |

| 1                      | N/A                | 25         | 1.9         |

| 2                      | 1                  | 50         | 3.5         |

| 3                      | N/A                | 75         | 4.9         |

# I<sup>2</sup>Cシリアル制御インター フェース

## レジスタ設定

AD8153は、ピン・モード、シリアル・モード、ミックスド・モードのいずれか1つで制御できます。ピン・モードではパッケージ・ピンからAD8153を制御し、シリアル・モードでは内部レジスタ・セットで制御します。ミックスド・モードでは、外部ピンでスイッチングを制御し、内部レジスタでイコライゼーションとプリエンファシスを制御します。AD8153に対するデータの書き込み／読み出し方法については、「I<sup>2</sup>Cデータ書き込み」セクションと「I<sup>2</sup>Cデータ読み出し」セクションで説明します。

モードはMODEピンで制御します。デバイスをピン・モードに設定するには、MODEをローレベル（VEE）にします。MODEをハイレベル（VCC）にすると、デバイスはシリアル・モードまたはミックスド・モードに設定されます。

ピン・モードでは、すべての制御を外部ピンで行います。シリアル・モードでは、表8に示すように、各チャンネルのイコライゼーションとプリエンファシスをレジスタでのみ制御します。また、シリアル・モードにはこれ以外の機能もあり、出力イネーブル制御ビットで各チャンネルの出力をイネーブルまたはディスエーブルにすることもできます。ピン・モードには、この機能がありません。以下で説明するように、AD8153のスイッチングをシリアル・モードに変更するには、マスク・ビット（レジスタ0x00）を1に設定します。すなわち、このレジスタに値0x1Fを書き込みます。マスク・ビットをすべて1に設定した場合は、レジスタ・セットのLB\_A、LB\_B、LB\_C、SEL、BICASTの各ビットでスイッチングを制御します。

ミックスド・モードでは、レジスタを使って各チャンネルのイコライゼーションとプリエンファシスを制御します。ただし、スイッチングは外部ピンまたは内部レジスタ・セットを使って

制御できます。このどちらを使うかは、マスク・ビット（レジスタ0x00）を使って選択します。マスク・ビットを0に設定すると外部ピンが制御源として機能し、マスク・ビットを1に設定すると該当する内部レジスタが制御源として機能します。たとえば、レジスタ0x00の値が0x0Cに設定されている場合は、内部レジスタ・セット（レジスタ0x04のビット0とレジスタ0x03のビット3）でSELおよびLB\_C制御を行い、外部ピンでBICAST、LB\_A、LB\_B制御を行います。

## 一般的な機能

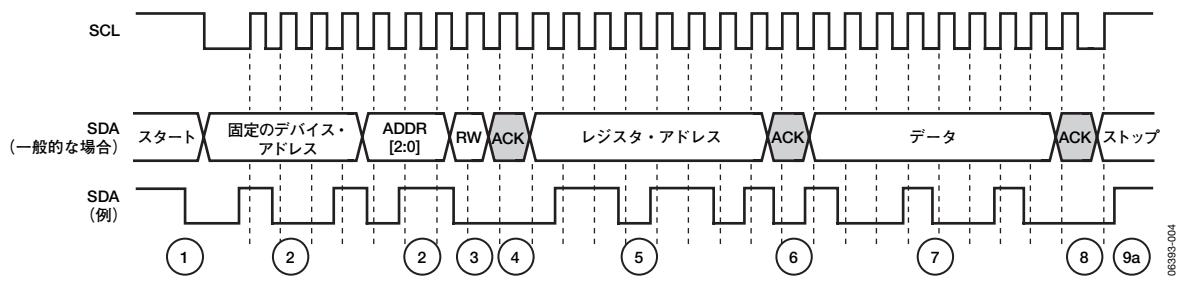

AD8153のレジスタ・セットは、2線式のI<sup>2</sup>Cインターフェースを使って制御します。AD8153は、I<sup>2</sup>Cスレーブ・デバイスとしてのみ動作します。したがって、システム内のI<sup>2</sup>Cバスには、AD8153を設定するためのI<sup>2</sup>Cマスターが必要になり、そのバスに他のI<sup>2</sup>Cデバイスが接続されているかもしれません。MODEピンがロジック1に設定されている場合は、2つのI<sup>2</sup>Cワイヤ、すなわち入力クロック・ピン（SCL）と双方向データ・ピン（SDA）を使ってデータ転送を制御します。

AD8153のI<sup>2</sup>Cインターフェースは、標準（100kHz）モードまたは高速モード（400kHz）で実行できます。SDAラインは、2つの例外を除き、SCLピンがローレベルのときだけ値が変化します。転送の開始または継続を示すには、SCLピンがハイレベルのときにSDAピンをローレベルに駆動します。また、転送の終了を示すには、SCLラインがハイレベルのときにSDAピンをハイレベルに駆動します。スタート・コンディション、リピート・スタート・コンディション、およびストップ・コンディションを示す場合でない限り、SDAラインが安定しているときにのみSCLクロックがトグルするよう制御することが重要です。

表8. レジスタ・マップ

| アドレス               | ビット7 | ビット6 | ビット5 | ビット4       | ビット3     | ビット2      | ビット1      | ビット0      | デフォルト              |

|--------------------|------|------|------|------------|----------|-----------|-----------|-----------|--------------------|

| 00000000<br>(0x00) |      |      |      | バイキャスト・マスク | SEL MASK | LB_C MASK | LB_B MASK | LB_A MASK | 00000000<br>(0x00) |

| 00000001<br>(0x01) |      |      |      | 出力ディスエーブルA | LB_A     | EQ_A      | PE_A[1]   | PE_A[0]   | 00000000<br>(0x00) |

| 00000010<br>(0x02) |      |      |      | 出力ディスエーブルB | LB_B     | EQ_B      | PE_B[1]   | PE_B[0]   | 00000000<br>(0x00) |

| 00000011<br>(0x03) |      |      |      | 出力ディスエーブルC | LB_C     | EQ_C      | PE_C[1]   | PE_C[0]   | 00000000<br>(0x00) |

| 00000100<br>(0x04) |      |      |      |            |          |           | バイキャスト    | SEL       | 00000000<br>(0x00) |

## I<sup>2</sup>Cデータ書き込み

AD8153のレジスタ・セットにデータを書き込むには、マイクロコントローラ、その他のI<sup>2</sup>Cマスターは、AD8153のスレーブ・デバイスに制御信号を送信する必要があります。以下に必要な手順を示します。この場合は、特に規定がない限り、信号はI<sup>2</sup>Cマスターで制御します。図32は、この書き込み手順を示します。

1. スタート・コンディションを送信します (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)。

2. AD8153デバイスのアドレス (7ビット) を送信します。このアドレスの上位4ビットは特定の値 (b1001) であり、下位3ビットは入力ピンI2C\_A[2:0]で制御されます。このデータ転送はMSBファーストです。

3. 書込みを示すビット (0) を送信します。

4. AD8153が要求にアクノレッヂ応答するのを待ちます。

5. データの書き込み先のレジスタ・アドレス (8ビット) を送信します。このデータ転送はMSBファーストです。

6. AD8153が要求にアクノレッヂ応答するのを待ちます。

7. ステップ5でアドレスを設定したレジスタに書き込むデータ (8ビット) を送信します。このデータ転送はMSBファーストです。

8. AD8153が要求にアクノレッヂ応答するのを待ちます。

9. ストップ・コンディションを送信して (SCLラインをハイレベルに維持して、SDAラインをハイレベルにプルアップ)、バスの制御を解除します。

10. リピートド・スタート・コンディションを送信し (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)、この手順のステップ2を引き続き実行して別の書き込みを行います。

11. リピートド・スタート・コンディションを送信し (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)、読み出し手順 (【I<sup>2</sup>C読み出しデータ】を参照) のステップ2を引き続き実行して別のアドレスからの読み出しを行います。

12. リピートド・スタート・コンディションを送信し (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)、読み出し手順 (【I<sup>2</sup>C読み出しデータ】を参照) のステップ8を引き続き実行して、ステップ5で設定したアドレスからの読み出しを行います。

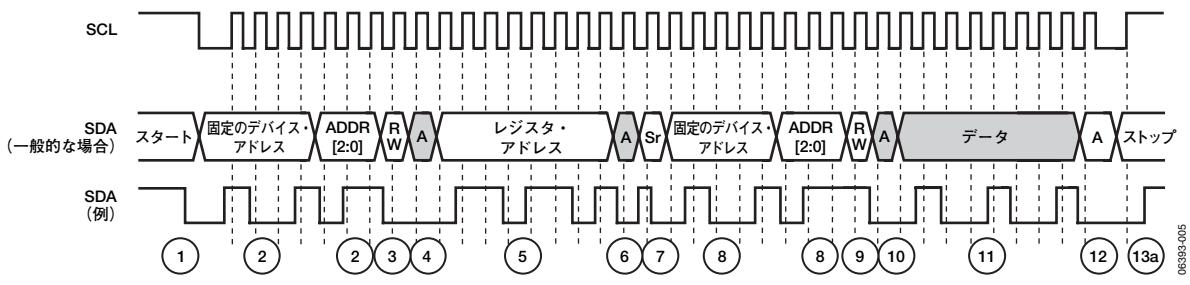

図32にAD8153の書き込みプロセスを示します。ここには、SCL信号、一般的な書き込み動作、および特定の例を示します。この例では、デバイス・アドレス0x4Bを持つAD8153デバイスのアドレス0x6Dにデータ0x92を書き込みます。デバイスのアドレスは7ビット幅で、AD8153の特定の値である上位4ビット (b1001) とピン・プログラマブルな下位3ビット (I2C\_ADDR[2:0]) から構成されています。この例では、I2C\_ADDRビットをb011に設定します。図32では波形の下側に、ステップに対応する丸印の番号を示します。SCLラインはI<sup>2</sup>Cマスターによって駆動しますが、AD8153スレーブからは駆動しません。SDAラインについては、影を付けた領域のデータはAD8153によって駆動し、影の付いていない領域のデータはI<sup>2</sup>Cマスターによって駆動します。図の9aは終了状態の例を示します。

ここでは次の点が重要です。すなわち、スタート・コンディション、ストップ・コンディション、またはリピートド・スタート・コンディションを送信する場合 (このケースではステップ1とステップ9) を除き、SCLラインがローレベルのときだけSDAラインは変化します。

図32. I<sup>2</sup>C書き込み図

## I<sup>2</sup>Cデータ読出し

AD8153のレジスタ・セットからデータを読み出すには、マイクロコントローラ、その他のI<sup>2</sup>Cマスターが、AD8153のスレーブ・デバイスに制御信号を送信する必要があります。以下に必要な手順を示します。この場合は、特に規定がない限り、信号はI<sup>2</sup>Cマスターで制御します。図33は、この書き込み手順を示します。

1. スタート・コンディションを送信します (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)。

2. AD8153デバイスのアドレス (7ビット) を送信します。このアドレスの上位4ビットは特定な値 (b1001) であり、下位3ビットは入力ビンI2C\_ADDR[2:0]で制御されます。このデータ転送はMSBファーストです。

3. 書込みを示すビット (0) を送信します。

4. AD8153が要求にアクノレッヂ応答するのを待ちます。

5. データの読み出し先のレジスタ・アドレス (8ビット) を送信します。このデータ転送はMSBファーストです。レジスタ・アドレスは、デバイスがリセットされるかレジスタ・アドレスが同じ手順 (ステップ1~6) で上書きされるまで、AD8153のメモリ内に保持されます。

6. AD8153が要求にアクノレッヂ応答するのを待ちます。

7. リピーテッド・スタート・コンディションを送信します (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)。

8. AD8153デバイスのアドレス (7ビット) を送信します。このアドレスの上位4ビットは特定な値 (b1001) であり、下位3ビットは入力ビンI2C\_ADDR[1:0]で制御されます。このデータ転送はMSBファーストです。

9. 読出しを示すビット (1) を送信します。

10. AD8153が要求にアクノレッヂ応答するのを待ちます。

11. AD8153は、ステップ5でアドレス・セットにより示したレジスタ内のデータ (8ビット) をシリアルに転送します。

12. データをアクノレッヂ応答します。

13. ストップ・コンディションを送信して (SCLラインをハイレベルに維持して、SDAラインをハイレベルにプルアップ)、バスの制御を解除します。

14. リピーテッド・スタート・コンディションを送信します (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)。書き込みの手順 ([I<sup>2</sup>Cデータ書き込み] を参照) のステップ2を引き続き実行して書き込みを行います。

15. リピーテッド・スタート・コンディションを送信し (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)、この手順のステップ2を引き続き実行して別のアドレスから読み出しを行います。

16. リピーテッド・スタート・コンディションを送信し (SCLラインをハイレベルに維持して、SDAラインをローレベルにプルダウン)、この手順のステップ8を引き続き実行して同じアドレスからの読み出しを行います。

図33に、AD8153の読み出しプロセスを示します。ここには、SCL信号、一般的な読み出し動作、および特定の例を示します。この例では、デバイス・アドレス0x4Bを持つAD8153デバイスのアドレス0x6Dからデータ0x49を読み出しています。デバイスのアドレスは7ビット幅で、AD8153の特定な値である上位4ビット (b1001) とビン・プログラマブルな下位3ビット (I2C\_ADDR[2:0]) から構成されています。この例では、I2C\_ADDRビットをb011に設定します。図33では波形の下側に、ステップに対応する丸印の番号を示します。SCLラインはI<sup>2</sup>Cマスターによって駆動しますが、AD8153スレーブからは駆動しません。SDAラインについては、影を付けた領域のデータがAD8153によって駆動し、影の付いていない領域のデータはI<sup>2</sup>Cマスターによって駆動します。図の13aは終了状態の例を示します。

ここでは次の点が重要です。すなわち、スタート・コンディション、ストップ・コンディション、またはリピーテッド・スタート・コンディション (このケースではステップ1、ステップ7、ステップ13) を送信する場合を除き、SCLラインがローレベルのときだけSDAラインは変化します。図33のAは、図32のACK同じです。リピーテッド・スタート・コンディションSrでは、SCLが立ち上がる前にSDAラインがハイレベルになります。この後、SCLはハイレベルのうちにSDAはローに落ちます。

図33. I<sup>2</sup>C読み出し図

## AD8153

### アプリケーション情報

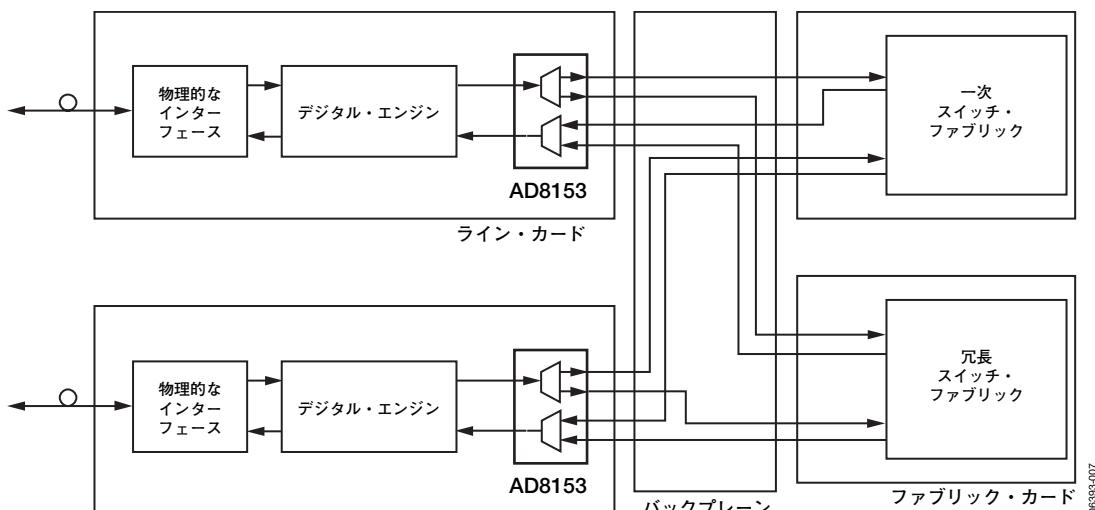

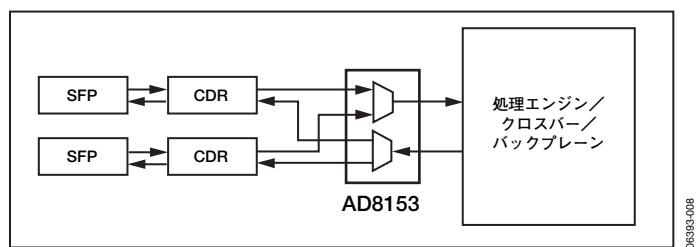

AD8153の主なアプリケーションでは、主にバックプレーン側とシリアル・リンクのライン・インターフェース側で冗長性を持たせることです。図34は、代表的なバックプレーン・システムの冗長構成を示します。各ライン・カードは2つのスイッチ・ファブリック（一次側と冗長側）に接続されています。また、1+1または1:1の構成も可能です。

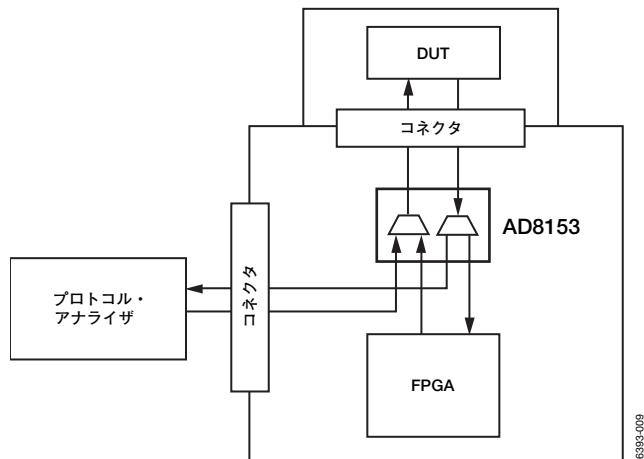

AD8153は、高速シリアル・リンクを評価する試験装置にも適用できます。図36は、AD8153を適用した単純なリンク・テストを示します。

図34. 冗長スイッチ・アプリケーション

図35. 冗長ライン・インターフェース・アプリケーション

図36. 試験装置アプリケーション

# PCB設計のガイドライン

最適性能を得るには、正しいRF PCB設計技術の使用が必要です。

## 電源接続とグラウンド・プレーン

低インピーダンスのグラウンド・プレーンを1つ使用することをお薦めします。VEEピンはグラウンド・プレーンに直接ハンダ付けして、直列インダクタンスを減らす必要があります。グラウンド・プレーンが内部プレーンで、かつビアを使ってグラウンド・プレーンへの接続を行う場合は、複数のビアを並列に使用して直列インダクタンスを減らす必要があります。リフロー中にハンダがビアを通して漏れるのを防ぐために、エクスポート・パッドはプラグ型ビアを使ってVEEプレーンに接続してください。

3.3V電源をPCBに投入する箇所には、VCCとVEEの間に $10\mu\text{F}$ の電解コンデンサを接続するとよいでしょう。 $0.1\mu\text{F}$ と $1\text{nF}$ のセラミック・チップ・コンデンサは、高周波電源デカップリングを良好に行うために、各電源ピンで並列に接続することを推奨します。 $0.1\mu\text{F}$ と $1\text{nF}$ のセラミック・チップ・コンデンサを使用するときは、これらをIC電源ピン（VCC、VTTI、VTTO）とVEE間に間のできる限り電源ピンの近くに接続する必要があります。

隣接する電源とGNDプレーンを使用し、プレーン間の間隔を狭くすれば、優れた高周波デカップリングが可能です。この容量は次式で表すことができます。

$$C_{\text{PLANE}} = 0.88\epsilon_r A/d \text{ (pF)}$$

ここで、

$\epsilon_r$ は、PCB材料の誘電率です。

$A$ は、電源プレーンとGNDプレーンの重なり合う領域 ( $\text{cm}^2$ ) です。

$d$ は、プレーン間のセパレーション (mm) です。

FR4の場合、 $\epsilon_r = 4.4$ 、間隔は $0.25\text{mm}$ 、 $C$ は約 $15\text{pF/cm}^2$ です。

## 伝送ライン

反射を最小限に抑えるために、すべての高周波入力および出力信号には $50\Omega$ の伝送ラインを使用する必要があります。差動バターン間のスキューを避けるために、差動入力バターンの高速ペアや差動出力バターンの高速ペアは長さが一致するようにします。

## チップ・スケール・パッケージのハンダ付けのガイドライン

32ピンLFCSPのランドは長方形です。これに対して、PCBのパッドはパッケージのランド長より $0.1\text{mm}$ 長く、パッケージのランド幅より $0.05\text{mm}$ 広くし、ランドの中心はパッドの中心とします。これは、ハンダ接続部のサイズを最大にすることになります。チップ・スケール・パッケージの底部には、中央にエクスポート・パッドがあります。PCB上のパッドは、このエクスポート・パッドと同じかそれ以上の大さが必要があります。このエクスポート・パッドは、リフロー中にハンダがビアを通して漏れるのを防ぐためにプラグ型ビアを使ってVEEに接続します。これによって、エクスポート・パッドとVEE間は切れ目なく接続されます。

## AD8153とのインターフェース

### 端子の構造

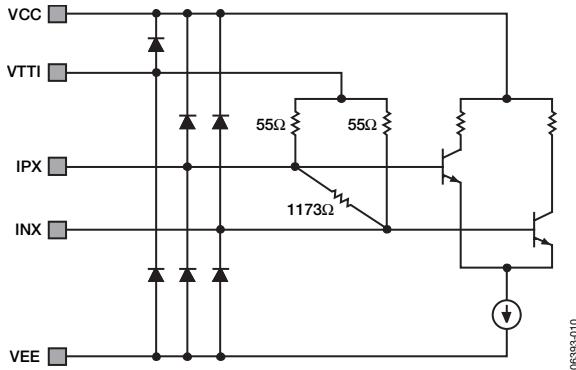

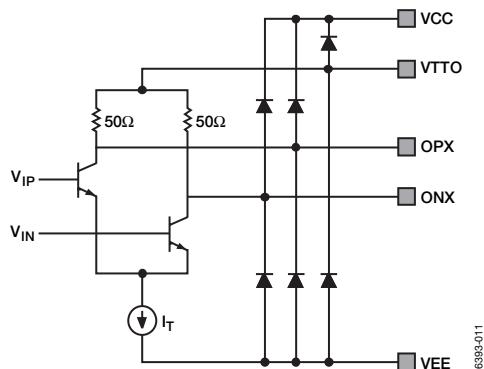

AD8153の高速ピンへの最適な接続方法を決めるには、まず、内蔵端子の構造をユーザにご理解いただく必要があります。この端子構造には、入力ポートと出力ポートの2タイプがあります（図37と図38を参照）。

図37. 簡略化したレシーバの回路図

図38. 簡略化したトランスマッタの回路図

入力ポートの端子構造は、端子電源に接続された2個の55Ω抵抗と差動入力にまたがって接続された1173Ωの抵抗からなり、後者はイコライザの有限な差動入力インピーダンスによって決まります。

出力ポートの端子構造では、2個の50Ω抵抗が端子電源に接続されています。両構造の差動入力抵抗は同じ100Ωとなります。

### 入力信号の守るべき条件

許容入力電圧範囲は、アクティブ入力回路の基本的な制限によって決まります。この信号範囲は、一般に電源電圧、信号の振幅、および入力信号の同相電圧レベルによって決まります。ある任意の入力信号振幅については、高電圧と低電圧の可動域として許容制限内にあるべきという同相電圧範囲があります。また、任意の同相入力電圧については、最大許容入力信号振幅が存在します。さらに、アクティブな入力回路で適正に処理できる最小信号振幅も存在します。仕様については、表1を参照してください。

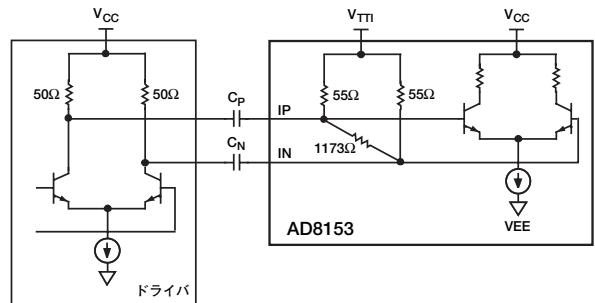

### AC結合

入力回路を簡素化して、さまざまな駆動デバイスとの互換性を持たせるために、AC結合を利用できます。これには、AD8153入力回路とドライバのDC同相レベルをアイソレートする効果があります。AC結合では、図39に示すようにコンデンサを各シングルエンド入力信号と直列に接続し、PCBの高速信号品質を損なわないような方法で行う必要があります。

図39. AD8153のACカップリング入力信号

AC結合を使用するとき、デバイスへの入力の同相電圧レベルはV<sub>TTI</sub>と同じになります。シングルエンド入力信号は、V<sub>TTI</sub>の上下に等しくスイングします。表1の仕様を参照して、AD8153の入力範囲を満たす入力信号の振幅レベルを決めることができます。

DC結合が必要な場合は、入力同相電圧レベルを決めるのはそれほど簡単ではありません。ドライバの設定も考慮する必要があるからです。ほとんどの場合は、AD8153のV<sub>TTI</sub>をドライバの出力終端電圧と同じレベルに設定します。これによって、連続直流電流が2つの電源ネット間に流れるのを防ぎます。実際には、両デバイスを同じ物理電源ネットに終端させることができます。

次の例を考えてみましょう。AD8153の入力にはドライバがDC結合されているものとします。AD8153の入力終端電圧（V<sub>TTI</sub>）とドライバ出力終端電圧は（V<sub>TTOD</sub>）は両方とも同じレベルに設定されています。すなわち、V<sub>TTI</sub>=V<sub>TTOD</sub>=3.3Vとなります。800mVの差動p-p電圧が必要な場合、ドライバの全出力電流は16mAとなります。平衡な状態で、出力電流は差動信号経路の両側で均等（それぞれ8mA）に分割されます。この8mAの電流は、並列に接続されたAD8153側の55Ω入力終端抵抗とドライバ側の50Ω出力終端抵抗を流れるため、以下の同相電圧レベルが得られます。

$$V_{TTI} - 8mA \times (50\Omega \parallel 55\Omega) = V_{TTI} - 209mV$$

ここで、800mVp-pの差動振幅に基づいて入力コンプライアンス範囲を満たすV<sub>TTI</sub>の許容範囲値を決めることができます。

## 出力信号の守るべき条件

図40は、AD8153の出力のシングルエンド波形を示します。同相電圧レベル ( $V_{OCM}$ ) とこの波形の振幅 ( $V_{OSE}$ ) は、出力テール電流 ( $I_T$ )、出力終端電源電圧 ( $V_{TTO}$ )、遠端レシーバのトポロジ、AC結合/DC結合の使用によって決まります。ここでは、出力テール電流がプリエンファシス・レベルに応じて変化するという点を留意する必要があります。出力の高電圧 ( $V_H$ ) と低電圧 ( $V_L$ ) の可動域としてシングルエンドの絶対電圧範囲内(表1に規定)を越えないようにしてください。AC結合/DC結合の選択や出力信号レベルを正しく理解していないと、トランジスタ飽和や伝送性能の低下を招く恐れがあります。

表9は出力レベルの代表的な計算例を示します。この場合、 $V_{CC}=V_{TTO}=3.3V$ で、 $50\Omega$ の遠端終端が3.3V電源に接続されています。

図40. シングルエンド出力波形

表9. 出力電圧レベル

| PE設定 | $I_T$ (mA) | $V_{OSE-DC}$ (mV p-p) | $V_{OSE-BOOST}$ (mV p-p) | DC結合          |           |           | AC結合          |           |           |

|------|------------|-----------------------|--------------------------|---------------|-----------|-----------|---------------|-----------|-----------|

|      |            |                       |                          | $V_{OCM}$ (V) | $V_H$ (V) | $V_L$ (V) | $V_{OCM}$ (V) | $V_H$ (V) | $V_L$ (V) |

| 0    | 16         | 400                   | 400                      | 3.1           | 3.3       | 2.9       | 2.9           | 3.1       | 2.7       |

| 1    | 20         | 400                   | 500                      | 3.05          | 3.3       | 2.8       | 2.8           | 3.05      | 2.55      |

| 2    | 24         | 400                   | 600                      | 3             | 3.3       | 2.7       | 2.7           | 3         | 2.4       |

| 3    | 28         | 400                   | 700                      | 2.95          | 3.3       | 2.6       | 2.6           | 2.95      | 2.25      |

表10. 記号の定義

| 記号               | 式                                         | 定義                   |

|------------------|-------------------------------------------|----------------------|

| $V_{OSE-DC}$     | $I_T _{PE=0} \times 25\Omega$             | セトリング後のシングルエンド出力電圧振幅 |

| $V_{OSE-BOOST}$  | $I_T \times 25\Omega$                     | 上昇したシングルエンド出力電圧振幅    |

| $V_{OCM}$ (DC結合) | $V_{TTO} - \frac{I_T}{2} \times 25\Omega$ | 出力がDC結合されている場合の同相電圧  |

| $V_{OCM}$ (AC結合) | $V_{TTO} - \frac{I_T}{2} \times 50\Omega$ | 出力がAC結合されている場合の同相電圧  |

| $V_H$            | $V_{OCM} + V_{OSE-BOOST}/2$               | 大きなシングルエンド出力電圧振幅     |

| $V_L$            | $V_{OCM} - V_{OSE-BOOST}/2$               | 小さなシングルエンド出力電圧振幅     |

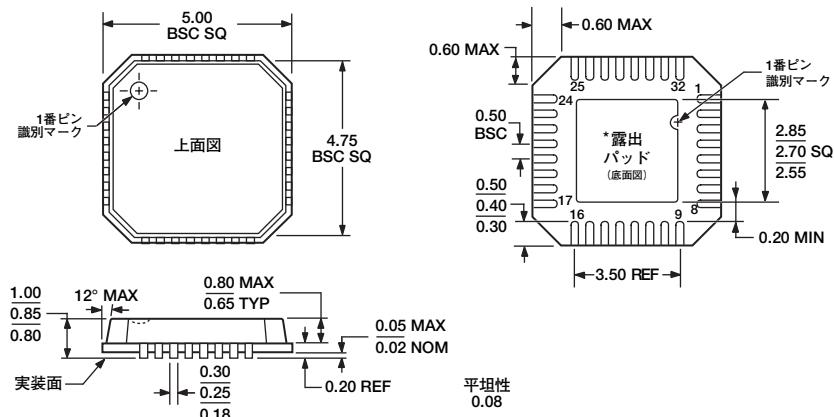

## 外形寸法

JEDEC規格MO-220-VHHD-2に準拠

\*AD8153は熱放散を助ける伝導性放熱板を使用して、工業用温度範囲の全域でデバイスの高信頼動作を保証しています。

この放熱板はパッケージの底面に露出しており、電気的にV<sub>EE</sub>に接続されています。

伝導性放熱板に接触するパッケージの下にはPCBパターンまたはビアを配置しないことを推奨します。

022807-A

図41. 32ピン・リード・フレーム・チップ・スケール・パッケージ [LFCSP\_VQ]

5mm×5mmボディ、極薄クワッド

(CP-32-8)

寸法単位：mm

## オーダー・ガイド

| モデル                         | 温度範囲      | パッケージ                                      | パッケージ・オプション |

|-----------------------------|-----------|--------------------------------------------|-------------|

| AD8153ACPZ <sup>1</sup>     | -40~+85°C | 32ピン・リード・フレーム・チップ・スケール・パッケージ<br>[LFCSP_VQ] | CP-32-8     |

| AD8153ACPZ-RL7 <sup>1</sup> | -40~+85°C | 32ピン・リード・フレーム・チップ・スケール・パッケージ<br>[LFCSP_VQ] | CP-32-8     |

| AD8153-EVALZ <sup>1</sup>   |           | 評価用ボード                                     |             |

<sup>1</sup> Z=RoHS準拠製品