## 特長

16×5高速、非ブロッキング・スイッチ・アレイ

AD8106: G=1, AD8107: G=2

AD8110/AD8111 (16×8スイッチ・アレイ) とピン互換

16×16アレイについては、AD8114/AD8115を参照

16×8アレイについては、AD8110/AD8111を参照

全機能を内蔵

バッファ付き入力

5個の出力アンプ

150Ω負荷の駆動能力

優れたビデオ性能

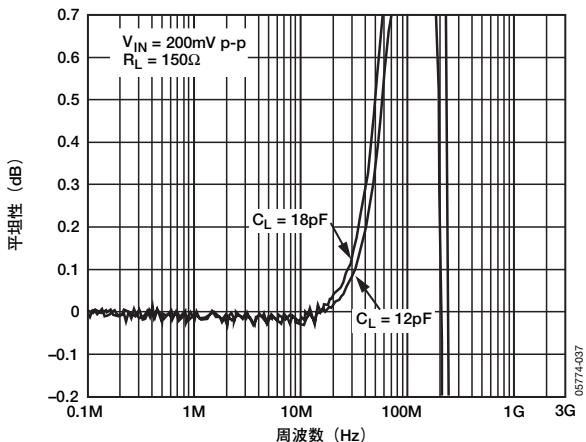

60MHz、0.1dBのゲイン平坦性

0.02%の微分ゲイン誤差 ( $R_L=150\Omega$ )

0.02度の微分位相誤差 ( $R_L=150\Omega$ )

優れたAC性能

−3dB帯域幅: >260MHz

スルーレート: 500V/μs

低消費電力: 50mA

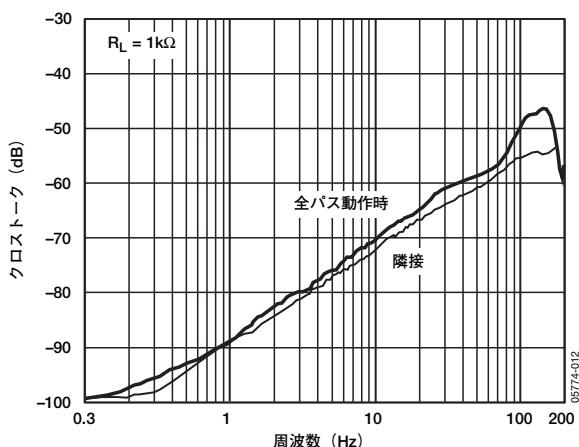

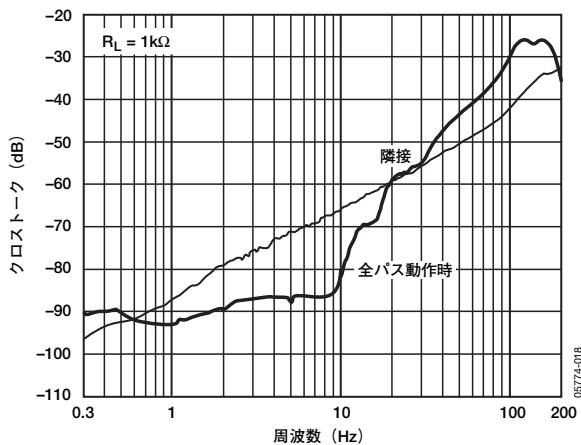

全パス動作時の低いクロストーク: −78dB (@5MHz)

出力ディスエーブル機能で複数のデバイス出力の接続が可能

リセット・ピンですべての出力のディスエーブルが可能

優れたESD定格: >4000V (人体モデル)

80ピンLQFP (12mm×12mm)

## アプリケーション

以下の高速信号のルーティング:

コンポジット・ビデオ (NTSC、PAL、S、SECAM)

コンポーネント・ビデオ (YUV、RGB)

圧縮ビデオ (MPEG、Wavelet)

3レベル・デジタル・ビデオ (HDB3)

## 概要

AD8106とAD8107は、高速16×5ビデオ・クロスポイント・スイッチ・マトリックスです。−3dB信号帯域幅は260MHzを超え、チャンネル・スイッチ時間は1%のセトリングで25ns未満です。−78dBのクロストークと−97dBのアイソレーション(@5MHz)のAD8106/AD8107は、多くの高速アプリケーションに利用できます。微分ゲイン誤差は0.02%未満、微分位相誤差も0.02度未満で、60MHzまで0.1dBの平坦性であるため、ビデオ信号のスイッチングに最適です。

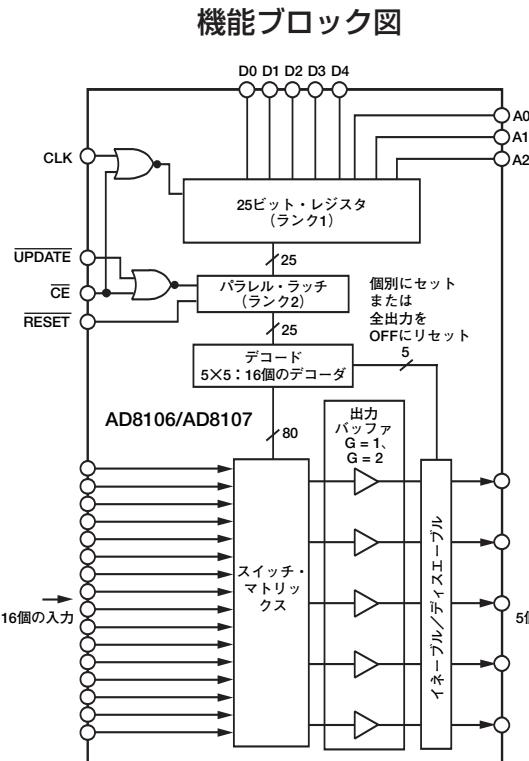

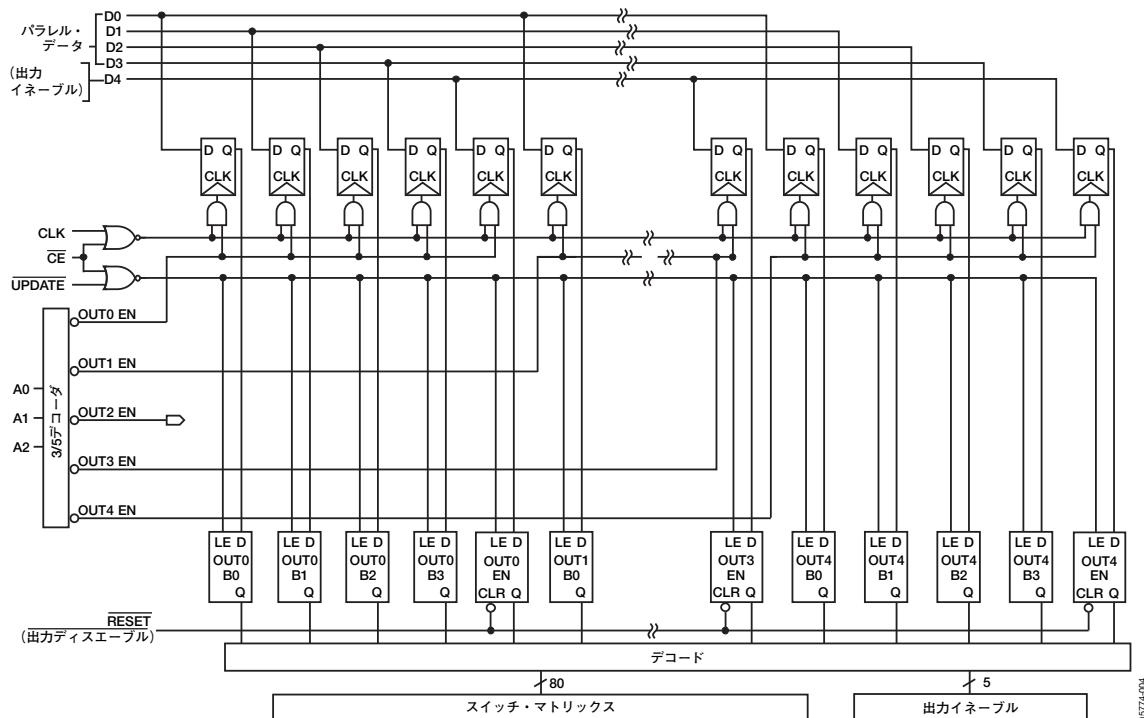

図1

05774-001

AD8106とAD8107には5個の独立した出力バッファが備わっており、複数のクロスポイントの出力をパラレル接続した場合、出力バッファーを高インピーダンス状態に設定すれば、オフ状態のチャンネルに出力バスの負担がかかりません。ゲインはAD8106が1、AD8107は2です。いずれも±5Vの電源電圧で動作し、アイドル電流はわずか30mAです。パラレル制御によってチャンネル・スイッチングを行うため、アレイ全体を設定し直すことなく個々に出力を更新できます。

AD8106/AD8107は、80ピンLQFPを採用しており、−40~+85°Cの拡張工業用温度範囲で使用できます。

# AD8106/AD8107

## 目次

|            |    |                           |    |

|------------|----|---------------------------|----|

| 特長         | 1  | 動作原理                      | 16 |

| アプリケーション   | 1  | パワーオン・リセット                | 16 |

| 機能ブロック図    | 1  | 初期化                       | 16 |

| 概要         | 1  | ゲインの選択                    | 16 |

| 改訂履歴       | 2  | 大きなクロスポイント・アレイの作成         | 16 |

| 仕様         | 3  | クロストーク                    | 18 |

| タイミング特性    | 5  | PCBのレイアウト                 | 19 |

| 絶対最大定格     | 6  | 評価用ボード                    | 21 |

| 最大消費電力     | 6  | 評価用ボードのPCからの制御            | 25 |

| ESDに関する注意  | 6  | プリンタ・ポートのデータライン上のオーバーシュート | 25 |

| ピン配置と機能の説明 | 8  | 外形寸法                      | 27 |

| I/O回路図     | 9  | オーダー・ガイド                  | 27 |

| 代表的な性能特性   | 10 |                           |    |

## 改訂履歴

3/06—Revision 0: Initial Version

## 仕様

特に指定のない限り、 $V_s = \pm 5V$ 、 $T_A = 25^\circ C$ 、 $R_L = 1k\Omega$ 。

表1

| パラメータ                | 条件                                                                                                                                           | Min        | Typ      | Max      | 単位     | 参考      |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|----------|--------|---------|

| 動的性能                 |                                                                                                                                              |            |          |          |        |         |

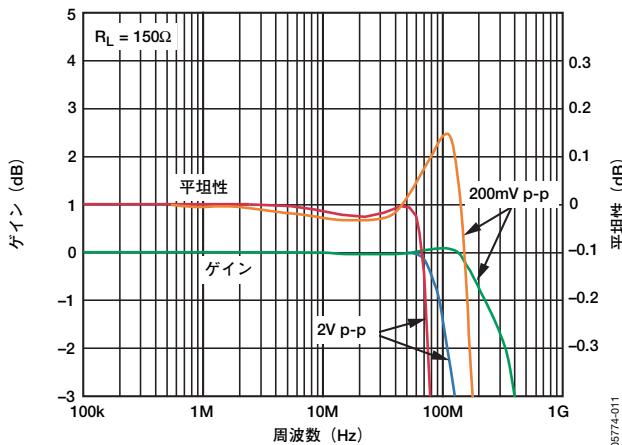

| −3dB帯域幅              | 200mVp-p、 $R_L = 150\Omega$<br>2Vp-p、 $R_L = 150\Omega$                                                                                      | 300/190    | 390/260  |          | MHz    | 図10、図16 |

| 伝搬遅延                 | 2Vp-p、 $R_L = 150\Omega$                                                                                                                     |            | 150      |          | MHz    | 図10、図16 |

| スルーレート               | 2Vステップ、 $R_L = 150\Omega$                                                                                                                    |            | 5        |          | ns     |         |

| セトリング時間              | 0.1%、2Vステップ、 $R_L = 150\Omega$                                                                                                               |            | 500      |          | V/μs   |         |

| ゲイン平坦性               | 0.05dB、200mVp-p、 $R_L = 150\Omega$<br>0.05dB、2Vp-p、 $R_L = 150\Omega$<br>0.1dB、200mVp-p、 $R_L = 150\Omega$<br>0.1dB、2Vp-p、 $R_L = 150\Omega$ | 40         | 60/40    | 80/57    | MHz    | 図10、図16 |

|                      |                                                                                                                                              |            | 65/40    |          | MHz    | 図10、図16 |

|                      |                                                                                                                                              |            | 70/57    |          | MHz    | 図10、図16 |

| ノイズ/歪み性能             |                                                                                                                                              |            |          |          |        |         |

| 微分ゲイン誤差              | NTSCまたはPAL、 $R_L = 1k\Omega$<br>NTSCまたはPAL、 $R_L = 150\Omega$                                                                                | 0.01       |          |          | %      |         |

| 微分位相誤差               | NTSCまたはPAL、 $R_L = 1k\Omega$<br>NTSCまたはPAL、 $R_L = 150\Omega$                                                                                | 0.02       |          |          | %      |         |

| クロストーク<br>(全パス動作時)   | $f = 5MHz$<br>$f = 10MHz$                                                                                                                    | 0.01       | 78/85    | 0.02     | 度      | 図11、図17 |

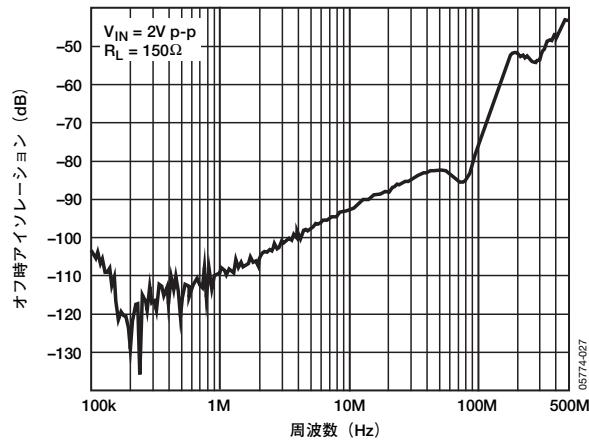

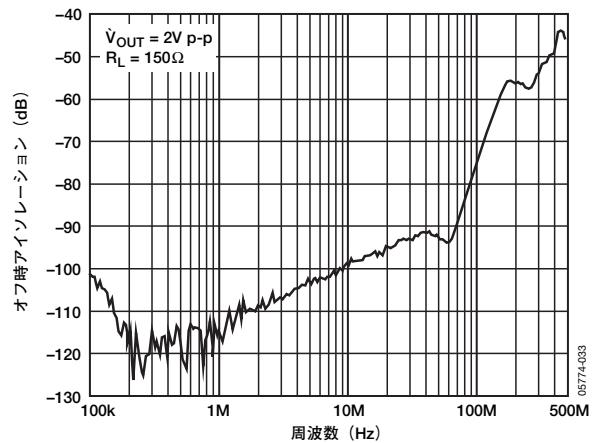

| オフ時アイソレーション<br>(入出力) | $f = 10MHz$ 、 $R_L = 150\Omega$ 、1チャンネル                                                                                                      | 0.02       | 70/80    | 93/99    | dB     | 図26、図32 |

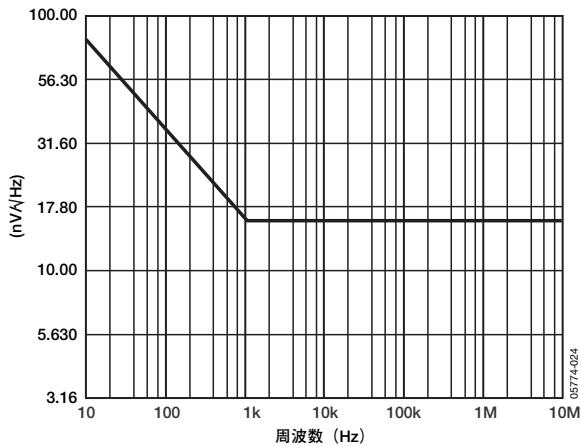

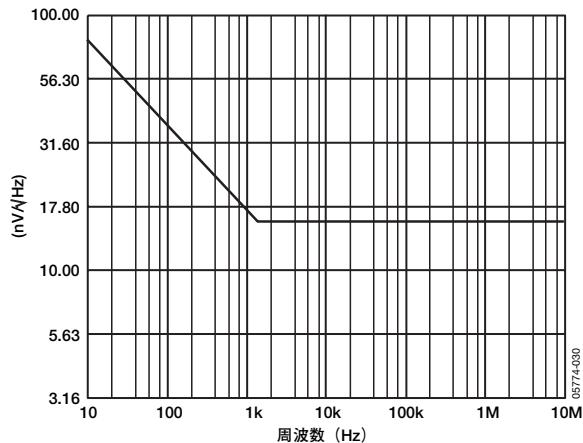

| 入力電圧ノイズ              | 0.01～50MHz                                                                                                                                   | 15         |          |          | nV/√Hz | 図23、図29 |

| DC性能                 |                                                                                                                                              |            |          |          |        |         |

| ゲイン誤差                | $R_L = 1k\Omega$<br>$R_L = 150\Omega$                                                                                                        | 0.04/0.1   | 0.07/0.5 |          | %      |         |

| ゲイン・マッチング            | 無負荷、チャンネル間<br>$R_L = 1k\Omega$ 、チャンネル間                                                                                                       | 0.15/0.25  | 0.02/1.0 | 0.09/1.0 | %      |         |

| ゲイン温度係数              |                                                                                                                                              |            | 0.5/8    |          | ppm/°C |         |

| 出力特性                 |                                                                                                                                              |            |          |          |        |         |

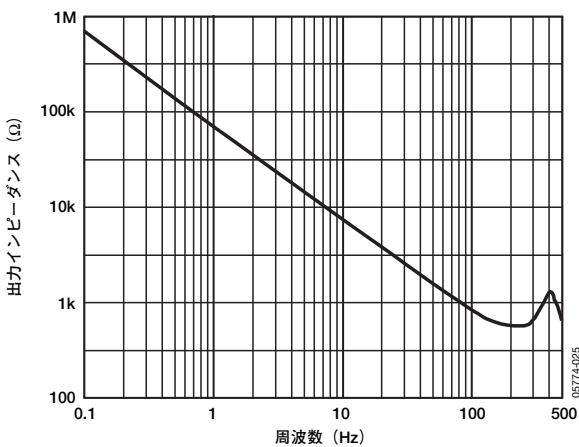

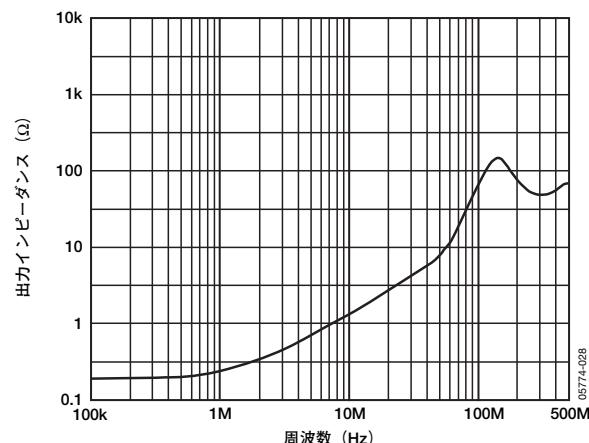

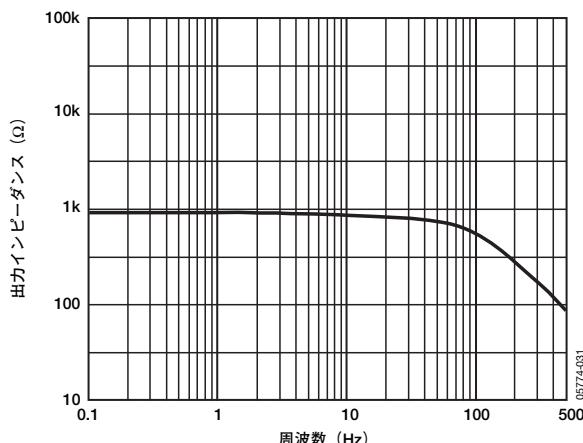

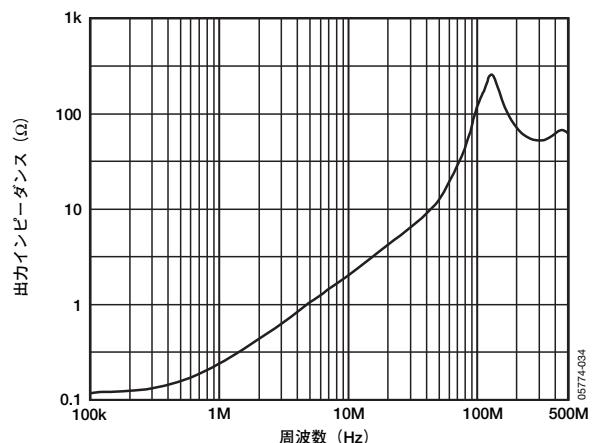

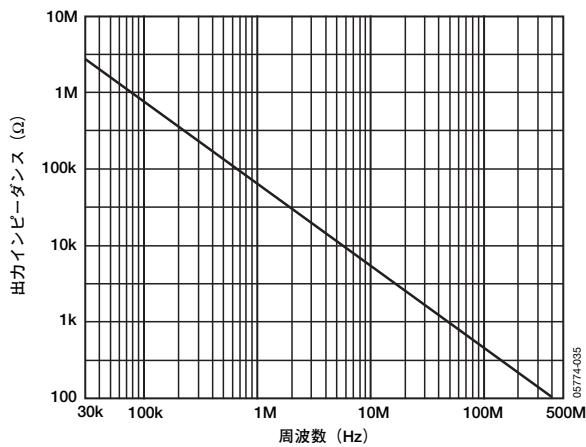

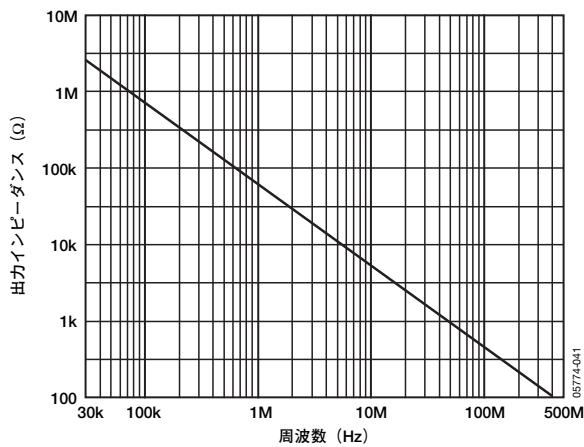

| 出力インピーダンス            | DC、イネーブル<br>ディスエーブル                                                                                                                          | 0.2        |          |          | Ω      | 図27、図33 |

| 出力ディスエーブル容量          | ディスエーブル                                                                                                                                      | 10/0.001   |          |          | MΩ     | 図24、図30 |

| 出力漏れ電流               | ディスエーブル (AD8106のみ)                                                                                                                           | 2          |          |          | pF     |         |

| 出力電圧範囲               | 無負荷                                                                                                                                          | 1/NA       |          |          | μA     |         |

| 出力電流                 |                                                                                                                                              | ±2.5       | ±3       |          | V      |         |

| 短絡電流                 |                                                                                                                                              | 20         | 40       |          | mA     |         |

|                      |                                                                                                                                              |            | 65       |          | mA     |         |

| 入力特性                 |                                                                                                                                              |            |          |          |        |         |

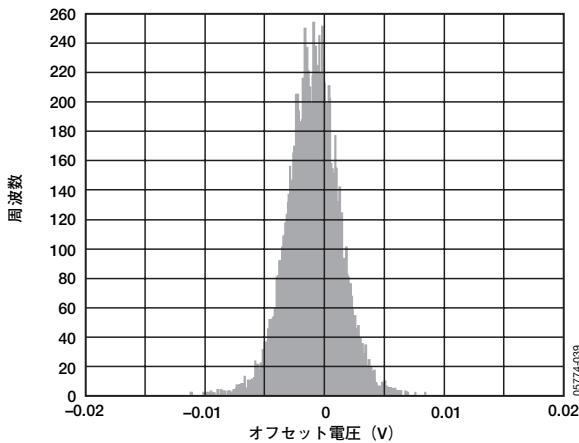

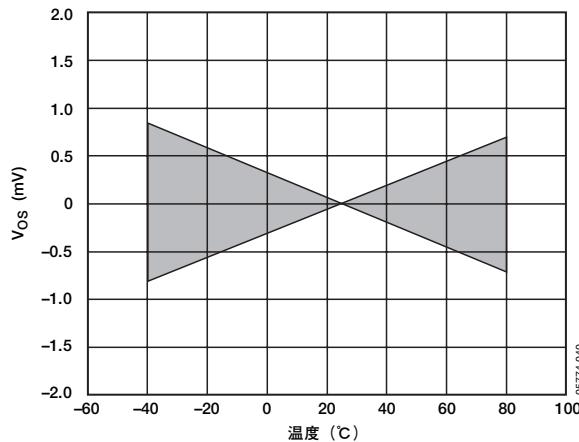

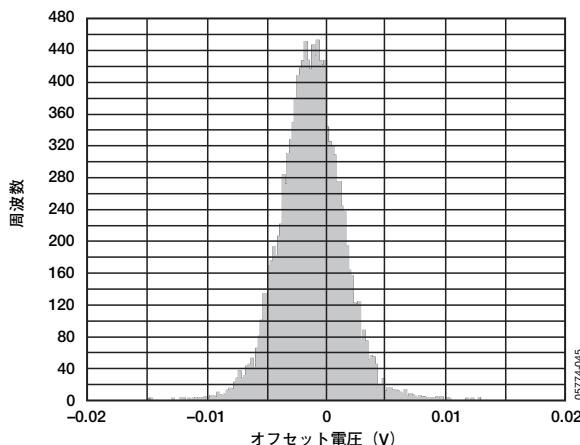

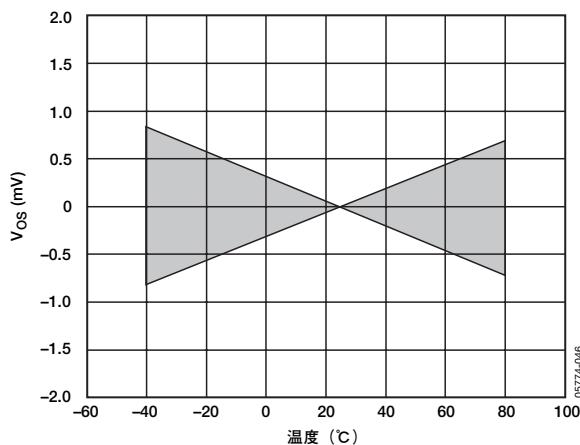

| 入力オフセット電圧            | ワースト・ケース (全設定)                                                                                                                               | 5          | 20       |          | mV     | 図38、図44 |

| 入力電圧範囲               | 温度係数                                                                                                                                         | 12         |          |          | μV/°C  | 図39、図45 |

| 入力容量                 |                                                                                                                                              | ±2.5/±1.25 | ±3/±1.5  |          | V      |         |

| 入力抵抗                 | 任意のスイッチ設定                                                                                                                                    | 2.5        |          |          | pF     |         |

| 入力バイアス電流             | 選択した出力当たり                                                                                                                                    | 1          | 10       | 5        | MΩ     |         |

|                      |                                                                                                                                              |            | 2        |          | μA     |         |

## AD8106/AD8107

| パラメータ                | 条件                        | Min       | Typ | Max   | 単位 | 参考      |

|----------------------|---------------------------|-----------|-----|-------|----|---------|

| スイッチング特性             |                           |           |     |       |    |         |

| イネーブルのオン時間           |                           | 60        |     | ns    |    |         |

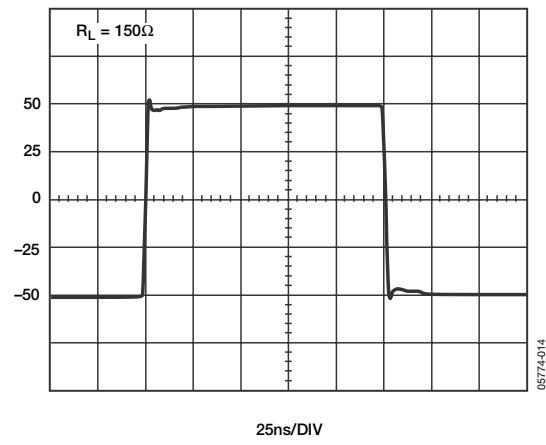

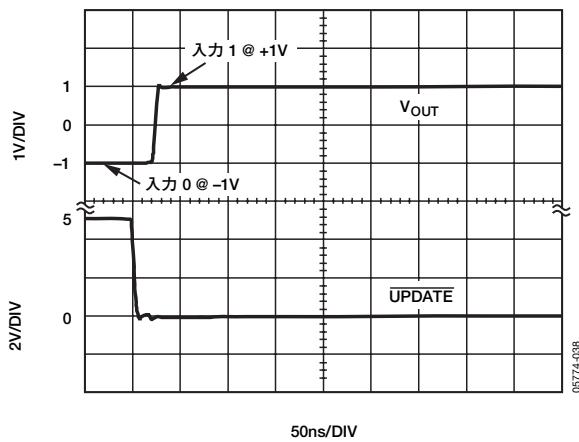

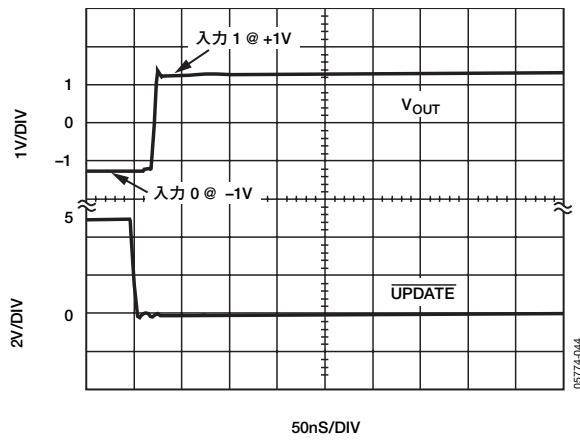

| スイッチング時間<br>(2Vステップ) | UPDATEの50%から1%セトリング<br>まで | 25        |     | ns    |    |         |

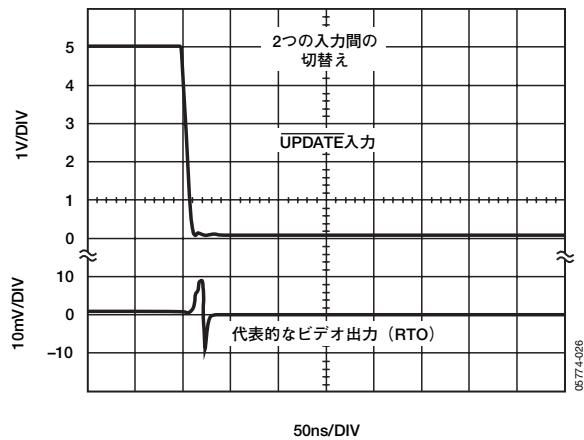

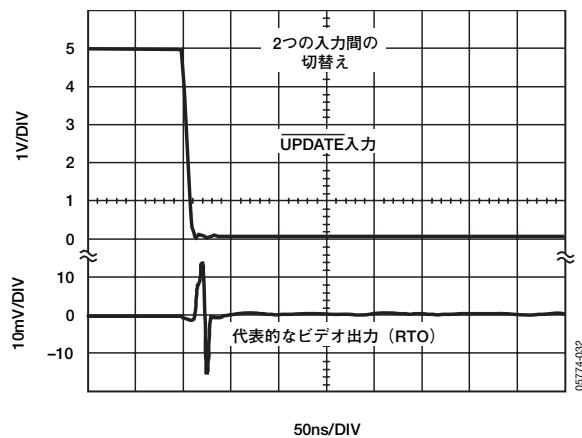

| スイッチング過渡電圧<br>(グリッヂ) | 出力で測定                     | 20/30     |     | mVp-p |    | 図25、図31 |

| 電源                   |                           |           |     |       |    |         |

| 電源電流                 | AVCC、出力イネーブル、無負荷          | 30        |     | mA    |    |         |

|                      | AVCC、出力ディスエーブル            | 15        |     | mA    |    |         |

|                      | AVEE、出力イネーブル、無負荷          | 30        |     | mA    |    |         |

|                      | AVEE、出力ディスエーブル            | 15        |     | mA    |    |         |

|                      | DVCC                      | 11        |     | mA    |    |         |

| 電源電圧範囲               |                           | ±4.5~±5.5 |     | V     |    |         |

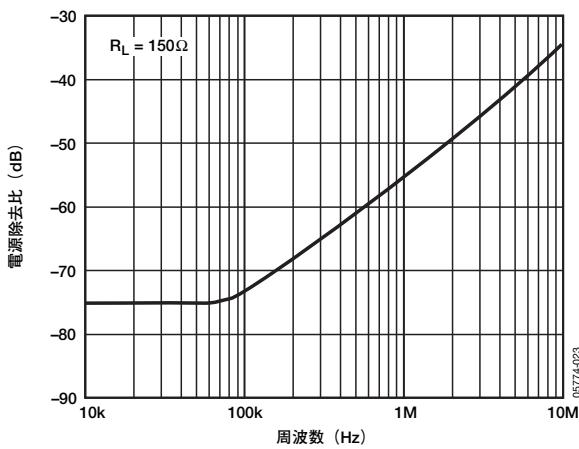

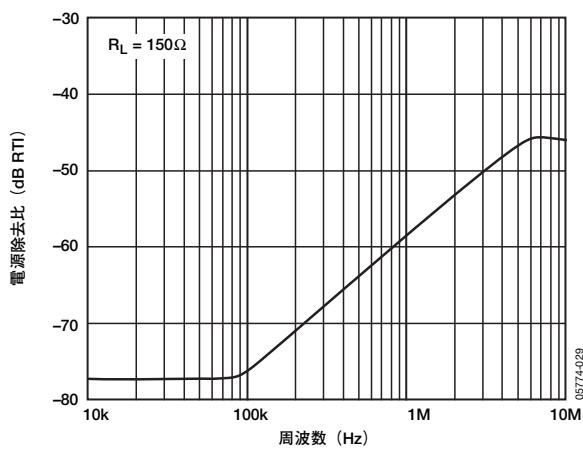

| PSRR                 | f=100kHz                  | 75/78     |     | dB    |    | 図22、図28 |

|                      | f=1MHz                    | −55/−58   |     | dB    |    |         |

| 動作温度                 |                           |           |     |       |    |         |

| 温度範囲                 | 動作時（自然空冷）                 | −40~+85   |     | ℃     |    |         |

| $\theta_{JA}$        | 動作時（自然空冷）                 | 48        |     | ℃/W   |    |         |

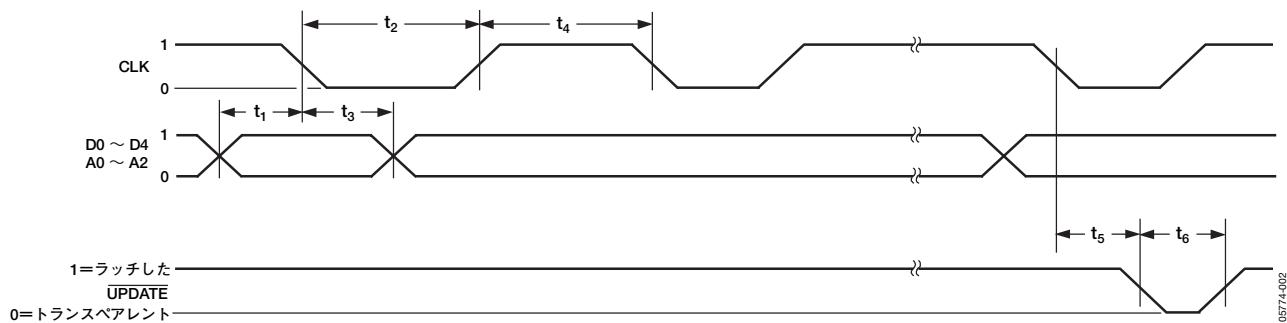

## タイミング特性

表2

| パラメータ | $T_{MIN}$ 、 $T_{MAX}$ の値 | 単位       | 説明                                       |

|-------|--------------------------|----------|------------------------------------------|

| $t_1$ | 20                       | ns (min) | データ・セットアップ時間                             |

| $t_2$ | 100                      | ns (min) | CLKパルス幅                                  |

| $t_3$ | 20                       | ns (min) | データ・ホールド時間                               |

| $t_4$ | 100                      | ns (min) | CLKパルス・セパレーション                           |

| $t_5$ | 0                        | ns (min) | CLKから $\overline{UPDATE}$ までの遅延          |

| $t_6$ | 50                       | ns (min) | $\overline{UPDATE}$ パルス幅                 |

| —     | 8                        | ns (max) | 伝搬遅延、 $\overline{UPDATE}$ からスイッチ・オン／オフまで |

| —     | 100                      | ns (max) | CLK、 $\overline{UPDATE}$ の立上がり時間と立下がり時間  |

| —     | 200                      | ns (min) | RESET時間                                  |

図2. タイミング図

表3. ロジック・レベル

| $V_{IH}$                                                                               | $V_{IL}$                                                                               | $I_{IH}$                                                                               | $I_{IL}$                                                                               |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| $\overline{RESET}$ 、CLK、D0、D1、D2、D3、D4、A0、A1、A2、 $\overline{CE}$ 、 $\overline{UPDATE}$ |

| 2.0V (min)                                                                             | 0.8V (max)                                                                             | 20 $\mu$ A (max)                                                                       | -400 $\mu$ A (min)                                                                     |

## 絶対最大定格

表4

| パラメータ                               | 定格値               |

|-------------------------------------|-------------------|

| 電源電圧                                | 12.0V             |

| 内部消費電力                              |                   |

| AD8106/AD8107 80ピンLQFP<br>(ST-80-1) | 2.6W              |

| 入力電圧                                | $\pm V_s$         |

| 出力短絡時間                              | 消費電力ディレーティング曲線を参照 |

| $\theta_{JA}$                       | 48°C/W            |

| 動作温度範囲                              | -40~85°C          |

| 保存温度範囲                              | -65~+125°C        |

| ピン温度 (ハンダ処理10秒)                     | 300°C             |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

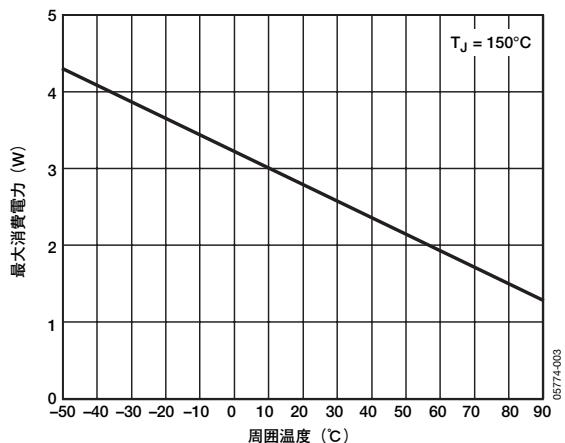

### 最大消費電力

AD8106/AD8107が安全に消費できる最大電力には、ジャンクション温度の上昇による限界があります。プラスチック・パッケージのデバイスの場合、安全な最大ジャンクション温度は、プラスチックのガラス遷移温度に基づき約150°Cです。この規定値を一時的にでも超えると、パッケージがチップに与える応力の変化によりパラメータ性能が変化することがあります。

長時間にわたり175°Cのジャンクション温度を超えると、デバイスが故障することがあります。

AD8106/AD8107には内部短絡保護がありますが、あらゆる条件下で最大ジャンクション温度（150°C）を超えないようにするには十分ではありません。確実に正しい動作を実現するには、図3の最大消費電力ディレーティング曲線を参照する必要があります。

図3. 最大消費電力の温度特性

### 注意

ESD（静電放電）の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

表5. 動作真理値表

| <u>CE</u> | <u>UPDATE</u> | CLK | DATA IN            | DATA OUT         | <u>RESET</u> | 動作／コメント                                                           |

|-----------|---------------|-----|--------------------|------------------|--------------|-------------------------------------------------------------------|

| 1         | X             | X   | X                  | X                | X            | ロジック内の変化なし。                                                       |

| 0         | 1             | $f$ | D0 … D4<br>A0 … A2 | パラレル・モード<br>ではなし | 1            | パラレル・データ・ラインD0～D4上のデータを、A0～A2が指定する40ビットのシリアル・シフト・レジスタにロードします。     |

| 0         | 0             | X   | X                  | X                | 1            | 40ビットのシフト・レジスタ内のデータを、スイッチ・アレイを制御するパラレル・ラッチに転送します。ラッチはトランスペアメントです。 |

| X         | X             | X   | X                  | X                | 0            | 非同期動作。全出力がディスエーブル状態です。ロジックの他の部分は不变です。                             |

図4. ロジック回路図

# AD8106/AD8107

## ピン配置と機能の説明

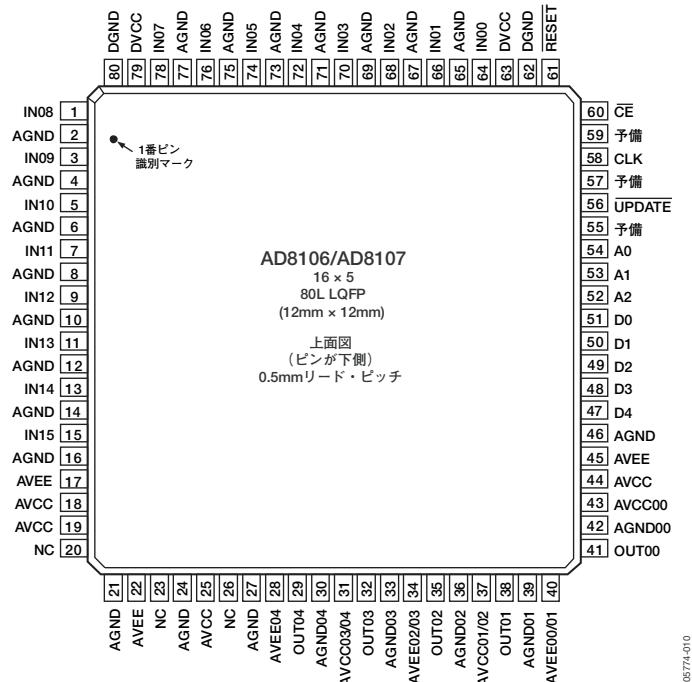

図5. 80ピン・プラスチックLQFP

表6. ピン機能の説明

| ピン番号                                                 | 記号        | 説明                                                            |

|------------------------------------------------------|-----------|---------------------------------------------------------------|

| 64、66、68、70、72、74、76、78、1、3、5、7、9、11、13、15           | INxx      | アナログ入力。xx=チャンネル番号00~15。                                       |

| 58                                                   | CLK       | クロック。TTL互換。立下がりエッジでトリガれます。                                    |

| 56                                                   | UPDATE    | イネーブル（トランスペアレント）ロー。シリアル・レジスタをスイッチ・マトリックスに直接接続できます。ハイでデータをラッチ。 |

| 61                                                   | RESET     | 出力をディスエーブルにします。アクティブ・ロー。                                      |

| 60                                                   | CE        | チップ・イネーブル。イネーブル・ローです。データを入力してラッチするには、ローにする必要があります。            |

| 41、38、35、32、29                                       | OUTyy     | アナログ出力。yy=チャンネル番号00~04。                                       |

| 2、4、6、8、10、12、14、16、21、24、27、46、65、67、69、71、73、75、77 | AGND      | 入力とスイッチ・マトリックス用のアナログ・グラウンド。                                   |

| 63、79                                                | DVCC      | デジタル回路用の5V。                                                   |

| 62、80                                                | DGND      | デジタル回路用のグラウンド。                                                |

| 17、22、45                                             | AVEE      | 入力とスイッチ・マトリックス用の-5V。                                          |

| 18、19、25、44                                          | AVCC      | 入力とスイッチ・マトリックス用の+5V。                                          |

| 42、39、36、33、30                                       | AGNDxx    | 出力アンプ用のグラウンド。xx=出力チャンネル番号00~07。接続する必要があります。                   |

| 43、37、31、22                                          | AVCCxx/yy | 出力アンプ用の+5V。チャンネル番号xxとyyで共有。接続する必要があります。                       |

| 40、34、28                                             | AVEExx/yy | 出力アンプ用の-5V。チャンネル番号xxとyyで共有。接続する必要があります。                       |

| 54                                                   | A0        | パラレル・データ入力。TTL互換（出力セレクトLSB）。                                  |

| 53                                                   | A1        | パラレル・データ入力。TTL互換（出力セレクト）。                                     |

| 52                                                   | A2        | パラレル・データ入力。TTL互換（出力セレクトMSB）                                   |

| 51                                                   | D0        | パラレル・データ入力。TTL互換（入力セレクトLSB）。                                  |

| 50                                                   | D1        | パラレル・データ入力。TTL互換（入力セレクト）。                                     |

| 49                                                   | D2        | パラレル・データ入力。TTL互換（入力セレクト）。                                     |

| 48                                                   | D3        | パラレル・データ入力。TTL互換（入力セレクトMSB）。                                  |

| 47                                                   | D4        | パラレル・データ入力。TTL互換（出力イネーブル）。                                    |

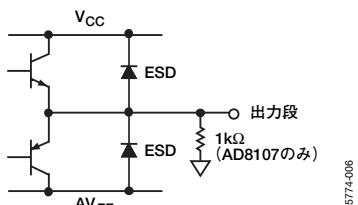

## I/O回路図

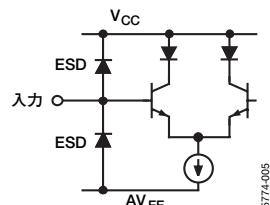

図6. アナログ入力段

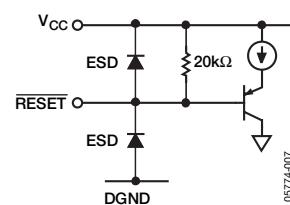

図8.  $\overline{RESET}$ 入力

図7. アナログ出力

図9. ロジック入力

## AD8106/AD8107

### 代表的な性能特性

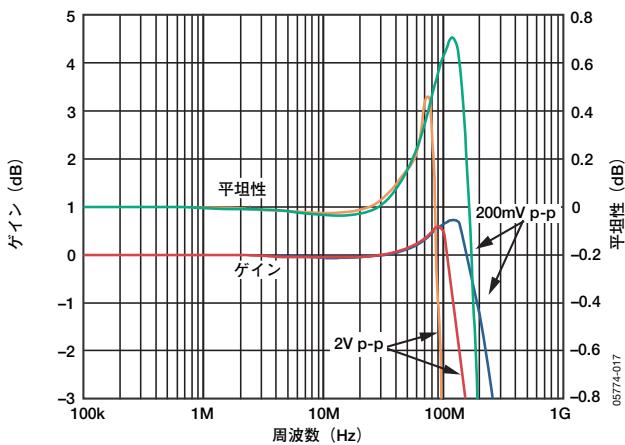

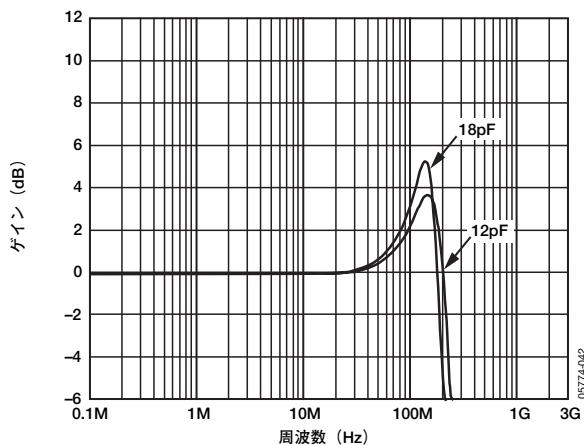

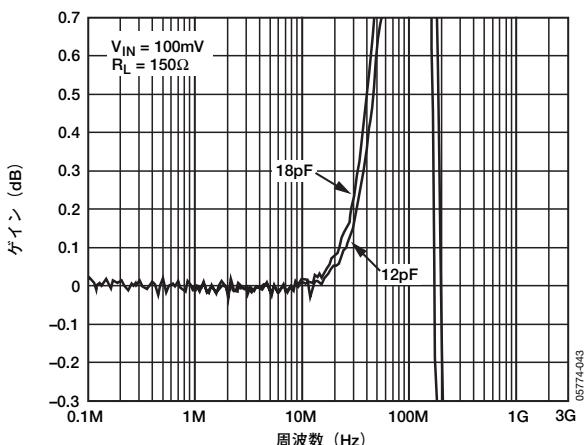

図10. AD8106、周波数応答

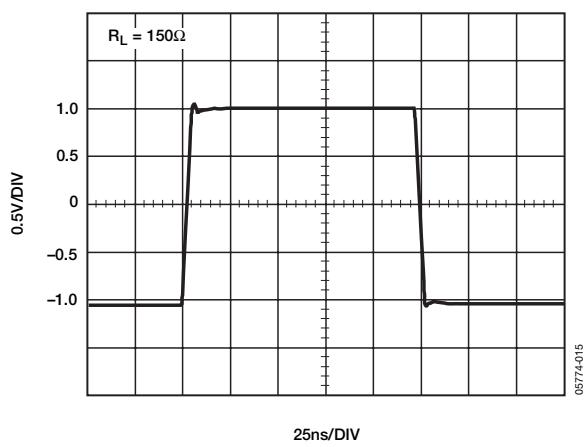

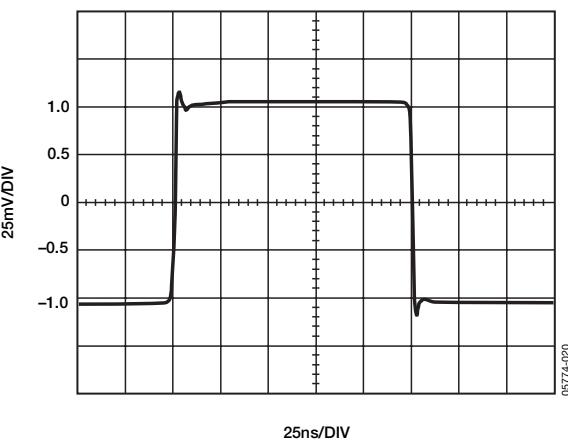

図13. AD8106、ステップ応答

(100mVステップ)

図11. AD8106、クロストークの周波数特性

図14. AD8106、ステップ応答 (2Vステップ)

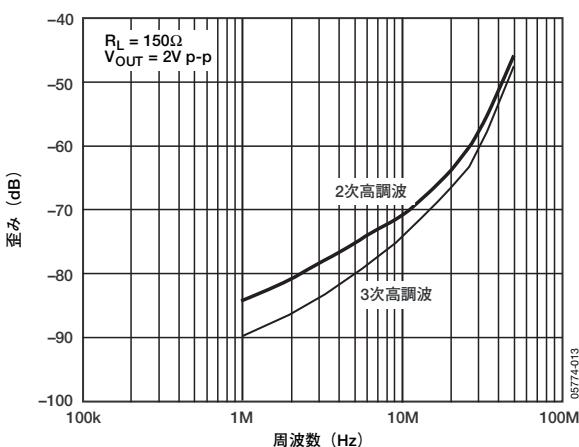

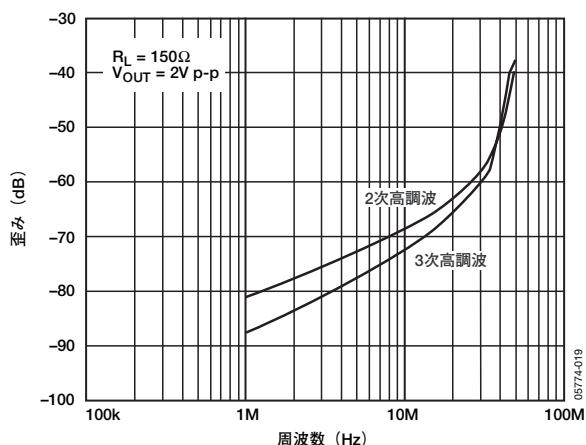

図12. AD8106、歪みの周波数特性

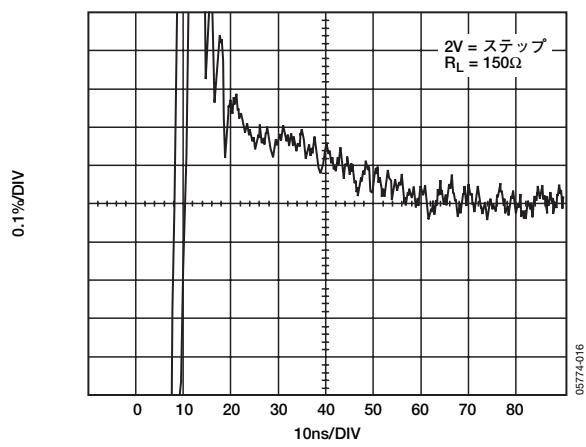

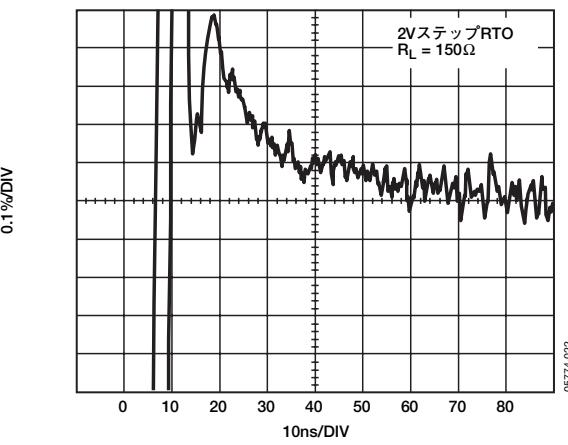

図15. AD8106、セトリング時間

図16. AD8107、周波数応答

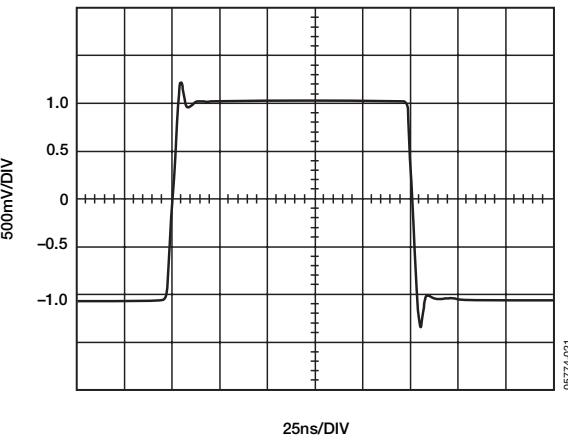

図19. AD8107、ステップ応答

(100mVステップ)

図17. AD8107、クロストークの周波数特性

図20. AD8107、ステップ応答 (2Vステップ)

図18. AD8107、歪みの周波数特性

図21. AD8107、セトリング時間

## AD8106/AD8107

図22. AD8106、PSRRの周波数特性

図25. AD8106、スイッチング過渡電圧

(グリッチ)

図23. AD8106、電圧ノイズの周波数特性

図26. AD8106、オフ時アイソレーション

(入出力)

図24. AD8106、出力インピーダンス

(ディスエーブル)

図27. AD8106、出力インピーダンス

(イネーブル)

図28. AD8107、PSRRの周波数特性

図31. AD8107、スイッチング過渡電圧

(グリッチ)

図29. AD8107、電圧ノイズの周波数特性

図32. AD8107、オフ時アイソレーション

(入出力)

図30. AD8107、出力インピーダンス

(ディスエーブル)

図33. AD8107、出力インピーダンス

(イネーブル)

## AD8106/AD8107

図34. AD8106、入力インピーダンスの周波数特性

図37. AD8106、スイッチング時間

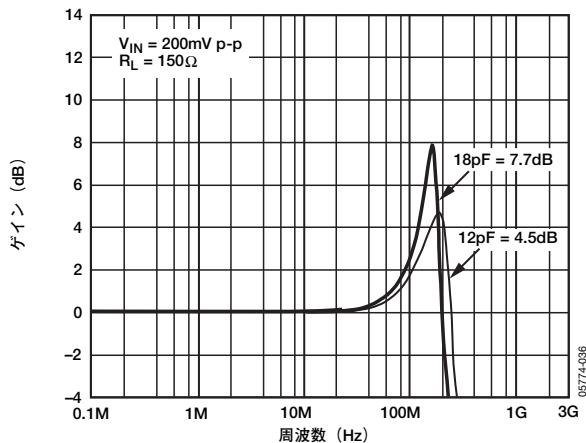

図35. AD8106、容量性負荷対周波数応答

図38. AD8106、オフセット電圧分布

図36. AD8106、容量負荷対平坦性

図39. AD8106、オフセット電圧の温度特性

(25°Cで正規化)

図40. AD8107、入力インピーダンスの周波数特性

図43. AD8107、スイッチング時間

図41. AD8107、容量性負荷対周波数応答

図44. AD8107、オフセット電圧分布 (RTI)

図42. AD8107、容量性負荷対平坦性

図45. AD8107、オフセット電圧ドリフトの温度特性 (25°Cで正規化)

### 動作原理

AD8106 (G=1) とAD8107 (G=2) の共通のコア・アーキテクチャは、5個の16:1マルチプレクサと16ラインの共通アナログ入力バス1つで構成された80個のトランスコンダクタンス(gm) 入力段アレイです。各マルチプレクサは、基本的に16個の入力段を持つ折り返しカスコード型高速電圧帰還アンプです。入力段はNPN差動ペアで、その差動電流出力は出力段で結合されます。出力段には、高インピーダンス・ノード、補償回路、相補型エミッタ・フォロア出力バッファがあります。AD8106は、各マルチプレクサの出力を16個のgm段の反転入力に直接戻します。AD8107の帰還ネットワークは、2本の同値の抵抗で構成される分圧器になっています。

このスイッチドgmアーキテクチャによって、低消費電力のクロスポイント・スイッチが得られます。スイッチはバック終端ビデオ負荷(150Ω)を低歪み(微分ゲイン誤差0.02%未満、微分位相誤差0.02度未満)で直接駆動します。この設計は、高い入力抵抗と低い入力容量を実現しながら、入力バッファの追加に伴う電力消費や信号劣化を招くことはありません。ただし、いずれの入力においても、その入力に設定された出力の数に比例してわずかな入力バイアス電流の増加があります。

クロスポイントの出力ディスエーブル機能を利用することで、複数の16×5 ICの出力を組み合わせ、大きなスイッチ・マトリックスを作成できます。ただし、AD8106のディスエーブルした出力インピーダンスが非常に高くなる(10MΩ)のに対して、AD8107の出力インピーダンスは抵抗帰還ネットワークの制限を受けるため、公称合計抵抗は1kΩで、ディスエーブルした出力と並行して出現します。複数のAD8107の出力が別々のバック終端抵抗によって接続されている場合は、有限な出力インピーダンスのために、ローディングによってマトリックス全体の実効バック終端インピーダンスが低下します。この問題は、複数のAD8107の出力を直接接続し、マトリックス全体の出力ごとに1個のバック終端抵抗を共有することで解消します。この設定では、イネーブルにしたAD8107の出力上のディスエーブルにしたAD8107の容量性負荷が増加します。

### パワーオン・リセット

AD8106/AD8107をパワーアップするには、一般に出力をディスエーブルにする必要があります。RESETピンをローレベルにすると、すべての出力がディスエーブルになります。

RESETピンにはDVDDに接続された20kΩプルアップ抵抗があり、簡単なパワーアップ・リセット回路を作成できます。RESETとグラウンドの間にコンデンサを接続すると、デバイスが安定するまでRESETはローレベルに保持されます。このローレベルにより、すべての出力がディスエーブルになります。その後、コンデンサがプルアップ抵抗からハイレベルに充電されると、デバイスのすべてのプログラム機能が使用可能になります。

### 初期化

AD8106/AD8107のパワーアップ後に初期化し、電源電流とバイアス電流を制御して、予期しないプログラムの状態が発生していないか確認してください。初期化を実行するには、00~07(バイナリ: 000~111)のすべてのアドレス位置に00000のデータ・ワードを書き込みます。

### ゲインの選択

16×5クロスポイントには、アナログ回路パスのゲインによって2つのバージョンがあります。AD8106デバイスはユニティ・ゲインであり、アナログ・ロジックのスイッチングや、ユニティ・ゲインにしたいその他のアプリケーションに使用できます。AD8106は、一般に出力信号の終端を使用しない、大きなクロスポイント・アレイの入力部や内部に使用できます。AD8106の出力をディスエーブルにすると、インピーダンスが非常に高くなります。

AD8107は、出力で終端したケーブルを駆動するデバイスに使用できます。このデバイスはゲインが2であるため、ビデオ・ラインを駆動するときにゲイン2のバッファは不要です。帰還ネットワークがあるため、ディスエーブルにした出力インピーダンスは約1kΩです。

### 大きなクロスポイント・アレイの作成

AD8106/AD8107は、16×5より大きいサイズのクロスポイント・アレイができる高集積ビルディング・ブロックです。出力ディスエーブル、チップ・イネーブル、ゲイン1とゲイン2のオプションなどのさまざまな機能が、大きなアレイを作成する場合に役に立ちます。非常に大きいアレイの場合は、AD8106/AD8107をAD8114/AD8115(16×16ビデオ・クロスポイント・デバイス)やAD8110/AD8111(16×8ビデオ・クロスポイント・デバイス)とともに使用します。クロスポイント・アレイのサイズのカスタマイズが必要な場合は、8×8ビデオ・クロスポイント・スイッチのペア(ユニティ・ゲインとゲイン2)、AD8108とAD8109とともに使用します。

大きなクロスポイントを構成するときに最初に考慮すべきことは、必要なデバイスの最小数を決めることがあります。AD8106/AD8107の16×5アーキテクチャには、80ポイントがあります。非ブロッキング・クロスポイントの場合、必要なポイント数は入力数と出力数の積になります。非ブロッキングの場合は、ある入力を1つまたは複数の出力に設定していても、他の出力にもその入力を接続できなければなりません。

非ブロッキング・クロスポイントのアーキテクチャによっては、上述の計算による最小値よりも多くのデバイスが必要になることがあります。また、この最小値よりも少ないデバイスで構成できるブロッキング・アーキテクチャも存在します。これらのシステムは、システム全体を設計するときに決めた統計的なベースに基づき、接続性を提供します。

大きいクロスポイント・アレイを構成するときの基本的な考え方は、水平方向に入力を並列に接続し、垂直方向に出力をワイヤードOR接続することです。

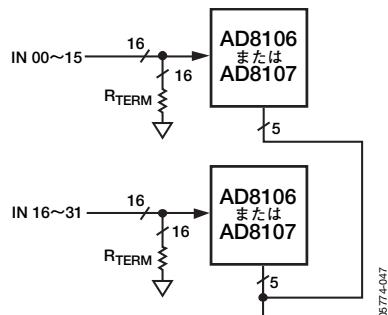

図46に、この考え方を32×5クロスポイント・アレイで示します。

図46. 2個のAD8106または2個のAD8107を使用する32×5クロスポイント・アレイ

入力は、2個のデバイスの32本の各入力に一意に割り当て、適切に終端します。出力はペアにして、ワイヤードOR接続します。ワイヤードOR接続されたペアの両方の出力を同時にイネーブルにすることはできません。デバイスをプログラムするソフトウェアを作成するときに、片方だけがイネーブルになるようにする必要があります。

ワイヤードOR接続された出力の数が増えすぎて、システム性能が維持できなくなるポイントがあります。このタイミングは、どのシステム仕様が最も重要であるかによって異なります。また、マトリックスの構成にAD8106を使用するか、AD8107を使用するかによっても異なります。

出力ディスエーブルのときのAD8106のインピーダンスは、AD8107の場合に比べてかなり高くなります。したがって、ディスエーブルにされた寄生容量が、イネーブルになっている出力1つに与える影響が小さくなります。たとえば、8個のAD8106/AD8107を使って、128×5クロスポイントを作成できます。この設計では、128個の別々の入力に対し、8つのグループにワイヤードOR接続された各デバイスの対応する出力があります。

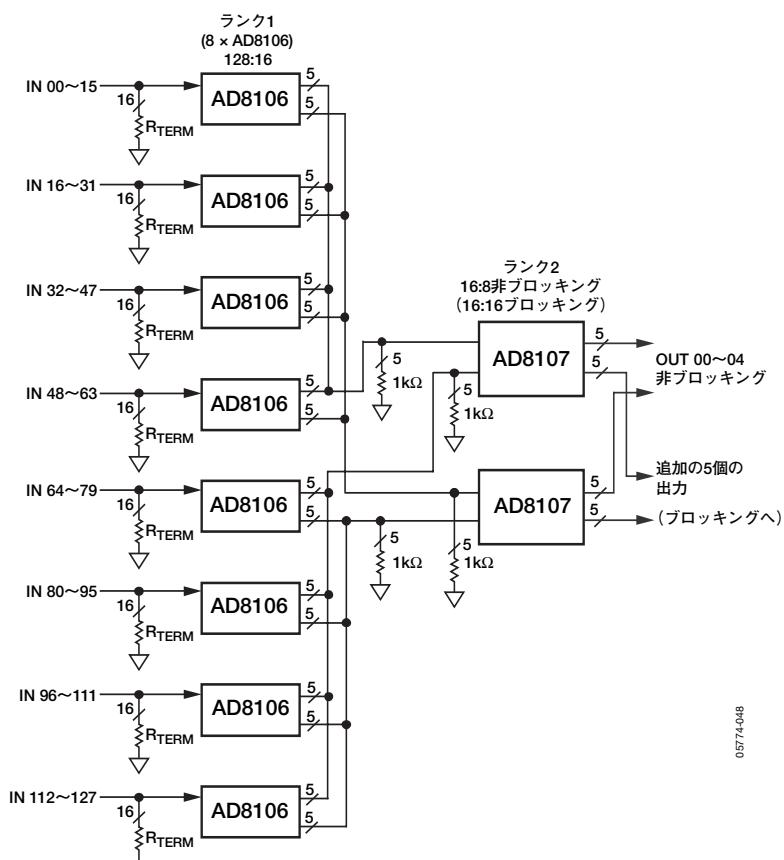

この設計にクロスポイント・デバイスをさらに追加すると、ワイヤードOR接続する出力数を少なくすることができます。図47に、8個のAD8106と2個のAD8107を使用し、ゲイン2、非ブロッキングの128×5クロスポイントを作成し、出力でのワイヤードOR接続を4個の出力に絞ったシステムのブロック図を示します。

さらに、ランク2の2個のAD8107の各々から下位4個の出力を使って、ブロッキングの128×10クロスポイント・アレイを作成できます。ただし、この方法には欠点があります。カスケード接続されたさまざまなデバイスのオフセット電圧が累積され、デバイスの帯域幅が制限されてしまいます。その上、デバイスを追加することによって消費電流が増え、ボード・スペースも増加してしまいます。この場合もやはり、システム全体の設計の仕様に基づいてトレードオフを決める必要があります。

図47. ゲイン2の128×5非ブロッキング・クロスポイント・アレイ (128×10ブロッキング)

# AD8106/AD8107

## クロストーク

放送ビデオなど多くのシステムでは、さまざまな信号がシステム内の他の信号に絶対に干渉しないように多数のアナログ信号チャンネルを扱わなければなりません。クロストークとは、近接のチャンネル間で別のチャンネルの信号が混入する状態をいいます。

AD8106/AD8107を使用するシステムも明らかにそうですが、システム内で多くの信号が近接して存在する場合、クロストークの問題はかなり複雑になります。1つまたは複数のAD8106/AD8107を使用するシステムの仕様を決めるには、クロストークの性質と関連する用語を理解する必要があります。

### クロストークの種類

クロストークは3つの方法で伝搬します。電界、磁界、共通インピーダンスの共有という3種類に分類できます。ここでは、これらの影響について説明します。

どの導体も、電界の放射器と受信器のいずれにもなります。電界クロストーク・メカニズムが発生するのは、送信器が生成した電界が浮遊容量（自由空間など）を伝搬し、受信器に結合して電圧を誘導するときです。この電圧を受信したチャンネル内では、これが不要なクロストーク信号になります。

導体に流入する電流は、その電流の周囲に磁界を生成します。これらの磁界は、電流が流入した導体に接続されている他の導体に電圧を発生させます。これらのチャンネル内の不要な誘導電圧が、クロストーク信号になります。クロストークが発生したチャンネルには、1つのチャンネルから別のチャンネルに信号を結合する相互インダクタンスが存在するということになります。

多チャンネル・システムでは電源、グラウンド、その他の信号のリターン・バスが、一般に多くのチャンネルによって共有されます。電流が1つのチャンネルからこれらのバスの1つに流入すると、インピーダンスの両端に電圧が発生して、共通インピーダンスを共有する他のチャンネルに対して入力クロストーク信号になります。

これらすべてのクロストーク源はベクトル量であるため、単純にこれらの振幅を加算しても全クロストークを得ることはできません。場合によっては、同じ構成で並列の追加回路を駆動すると、クロストークが減少することもあります。

### クロストークの領域

実用的なAD8106/AD8107回路は、電源と計測装置に接続するためにある種の回路ボードに実装する必要があります。デバイスに固有のわずかなクロストーク以外は生じないようにキャラクタライゼーション・ボード（評価用ボードとしても使用可能）の作成が特に念に行われてきました。ただし、このために、システムのクロストークがデバイスに固有のクロストークとデバイスを実装した回路ボードを合わせたものになるという問題が生じます。クロストークの影響を小さくするには、2つのクロストーク領域を分離することが重要です。

さらに、クロストークは、クロスポイントに対する入力間でもクロスポイントの出力間でも発生します。また、入力から出力に対しても発生します。クロストークを生じさせているシステムの箇所を診断するには、「入力でのクロストークと出力でのクロストーク」を参照してください。

## クロストークの測定

クロストークを測定するには、1つまたは複数のチャンネルに信号を入力し、選択したチャンネル上でその信号の相対強度を測定します。測定値は、一般にテスト信号の振幅からの減衰をdBで表したものになります。クロストークは次式で表すことができます。

$$|XT| = 20 \log_{10}(A_{sel}(s)/A_{test}(s)) \quad (1)$$

ここで、

$s=j\omega$ は、ラプラス変換変数です。

$A_{sel}(s)$ は、選択したチャンネルにおける誘導されたクロストーク信号の振幅です。

$A_{test}(s)$ は、テスト信号の振幅です。

クロストークは周波数の関数ですが、テスト信号の振幅の関数にはならないことがわかります（一次近似）。また、クロストーク信号には、対応するテスト信号を基準にする位相があります。

一般にネットワーク・アナライザを使用して、対象となる周波数範囲のクロストークを測定します。この装置からクロストーク信号の振幅と位相の情報が得られます。

クロスポイント・システムやデバイスの規模が大きくなると、理論的なクロストークの組み合わせと順列の数が極端に大きくなります。たとえば、AD8106/AD8107の16×5マトリックスについて、1つのチャンネル（IN00入力など）に対して考えられるクロストークの項数を調べてみましょう。AD8106/AD8107の出力の1つに接続するようにIN00を設定し、この出力で測定します。

まず、他の15本の入力の各々に1つずつテスト信号を入力したときの対応するクロストーク項を測定します。次いで、他の全15本の入力に1回に2本ずつ、全組み合わせについて並列テスト信号を入力したときの対応するクロストーク項を測定します。その次には、1回に3本ずつ入力して測定し、このようにしてテスト信号を他の全15本の入力に入力する方法が1つだけになるまで続けます。

各ケースは理論上それぞれ異なっており、計測システムの分解能に応じて固有の値が出ます。ただ、すべての項を測定してからそれぞれを特定するような方法は、実用的ではありません。さらに、これでは、1つの入力チャンネルについてのクロストーク・マトリックスが解明できるだけです。他のすべての入力に対しても同様のクロストーク・マトリックスが考えられます。また、入力を他の出力（測定に使用していない出力）に接続する組み合わせと順列を考慮すると、数値はすぐに天文学的になってしまいます。複数のAD8106/AD8107による大きなクロスポイント・アレイを作成する場合は、この数値はさらに大きくなります。

明らかに、これらのケースの一部を選択してクロストーク測定の目安にすることが実用的な方法です。一般的なやり方としては、全パス動作時のクロストークを測定する方法があります。この場合、選択したチャンネルのクロストークを測定するときに、他のすべてのシステム・チャンネルを並列に駆動します。一般に、この測定ではワースト・ケースのクロストーク値が得られます。クロストーク信号はペクトル量であるため常にワースト・ケースになるわけではありません。

他の方法として、いずれかの端点で1つの隣接チャンネルまたは2つの隣接チャンネルにおいて測定したクロストーク値を使用できます。これらのクロストーク測定値は、一般に離れたチャンネル間の測定値より大きい値になるため、他の1チャンネル・クロストーク測定値または2チャンネル・クロストーク測定値のワースト・ケースとして利用することができます。

### 入力でのクロストークと出力でのクロストーク

AD8106/AD8107のフレキシブルなプログラミング機能を使って、入力側または出力側のいずれでクロストークがより大きく発生しているかを診断できます。たとえば、中央にあるIN07などの入力チャンネルは、OUT01を駆動するように設定できます。IN07に対する入力はグラウンドに終端されており (50Ωまたは75Ωを経由)、信号の入力はありません。

他の全入力は同じテスト信号で並列に駆動し (実際には分配アンプを使用)、OUT01以外の他の全出力をディスエーブルにします。グラウンドに接続するIN07はOUT01を駆動する設定になっているため、IN07には信号を入力しません。他の出力は駆動されていないため (すべてディスエーブル)、何らかの信号が存在すれば、他の15本のパス動作時の入力信号に起因することになります。このようにして、この方法で全パス動作時の入力がIN07のクロストークに及ぼす影響を測定できます。この方法は、他の入力チャンネルやパス動作時入力の組み合わせにも使用できます。

出力クロストーク測定では、1つの入力チャンネル (たとえばIN00) を駆動し、任意の1つの出力を除き、他の全出力をIN00に接続するように設定します。OUT01は、IN00から遠く離れているIN15に接続する設定にし、グラウンドに終端します。その結果、無信号の入力に対応しているためOUT01には信号が出力されません。OUT01で測定されたあらゆる信号は、他の7本のパス動作時出力の出力クロストークに起因することになります。この方法も、他のチャンネルや他のクロスポイント・マトリックスの組み合わせを測定できるように変更できます。

### クロストークに対するインピーダンスの影響

入力側クロストークは、入力を駆動する信号源の出力インピーダンスの影響を受けます。駆動信号源のインピーダンスが小さいほど、クロストークの振幅は小さくなります。入力側での支配的なクロストーク・メカニズムは、容量性結合です。高インピーダンス入力では大きな電流は発生せず、磁界による誘導クロストークは発生しません。ただし、大きな電流が入力終端抵抗とそれらを駆動するループを流れことがあります。このため、入力側のPCボードが磁界結合のクロストークの原因になることがあります。

回路の観点から見ると、入力クロストーク・メカニズムは抵抗性負荷を結合するコンデンサに似ています。低い周波数では、クロストークの振幅を次式で表すことができます。

$$|XT| = 20 \log_{10} [(R_s C_M) \times s] \quad (2)$$

ここで、

$R_s$ は、信号源抵抗です。

$C_M$ は、テスト信号回路と選択された回路の間の相互容量です。

$s$ は、ラプラス変換変数です。

式2から、このクロストーク・メカニズムがハイパス特性を持っていることがわかります。入力回路の結合容量を小さくし、ドライバの出力インピーダンスを小さくすることによって、クロストークを小さくすることも可能です。75Ω終端のケーブルで入力を駆動する場合は、この信号を低出力インピーダンス・バッファでバッファリングすることによって入力クロストークを小さくできます。

出力側では、軽い負荷を駆動することによってクロストークを小さくできます。AD8106/AD8107では、標準の150Ωビデオ負荷を駆動するときに微分ゲインと微分位相が優れた値になりますが、大きな出力電流のために、実現可能な最小値より大きいクロストークになってしまいます。大きな出力電流は、出力ピンとAD8106/AD8107のボンディング・ワイヤの相互インダクタンスによってクロストークを誘発します。

回路の観点から見ると、この出力クロストーク・メカニズムは、負荷抵抗を駆動する巻線間に相互インダクタンスがあるトランズに似ています。低い周波数では、クロストークの振幅を次式で表すことができます。

$$|XT| = 20 \log_{10} (M_{xy} \times s / R_L) \quad (3)$$

ここで、

$M_{xy}$ は、出力xと出力yの間の相互インダクタンスです。

$R_L$ は、測定した出力上の負荷抵抗です。

このクロストーク・メカニズムを最小化するには、相互インダクタンスを小さくし、 $R_L$ を大きくします。相互インダクタンスを小さく抑えるには、導体間の間隔を大きくし、並列部分の長さを短くします。

### PCBのレイアウト

システム回路ボードから生じる余分なクロストークが最小になるように、最大の注意を払う必要があります。特に注意しなければならない領域は、グラウンドディング、シールディング、信号ルーティング、電源のバイパスです。

AD8106/AD8107のパッケージは、クロストークを最小にするように設計されています。各入力は、アナログ・グラウンド・ピンにより他の入力から分離されています。すべてのAGNDは、回路ボードのグラウンド・プレーンに直接接続する必要があります。グラウンド・ピンにより、シールディング、低インピーダンスのリターン・バス、入力に対する物理的な分離が得られます。これらのすべてがクロストークの低減に効果的です。

## AD8106/AD8107

各出力は、いずれかの極性のアナログ電源ピンとアナログ・グラウンド・ピンによって2本の隣接出力から分離されています。各アナログ電源ピンは、2本の隣接出力についてのみ出力段に電源を供給します。電源ピンとアナログ・グラウンドによって、出力のシールディング、物理的分離、低インピーダンスの電源が得られます。0.01 $\mu$ Fのチップ・コンデンサを直接グラウンド・プレーンに接続し、電源ピンを個々にバイパスさせることで、共通インピーダンスを共有するメカニズムから生じる高周波出力クロストークを最小にします。

各出力には、近くのアナログ・グラウンド・ピンAGND00～AGND03にそれぞれ接続するオンチップ補償コンデンサがあります。この方法により、これらのパスに流入する電流がIC上やパッケージ・ピン内の共通インピーダンスを共有できなくなるため、クロストークが低減します。AGNDxx信号は、すべて直接グラウンド・プレーンに接続します。

入力信号と出力信号が上下のレイヤでグラウンド・プレーンに挟まれていて、間にあるグラウンドによって相互に分離されている場合に、クロストークは最小になります。入力と出力を内部レイヤに送るには、ビアをICのできるだけ近くに配置します。入力信号と出力信号が出現する場所は、入力終端抵抗と出力直列逆側終端抵抗だけに限定します。これらの信号も、ICパッケージから出てきたらただちに可能な限り相互に分離します。

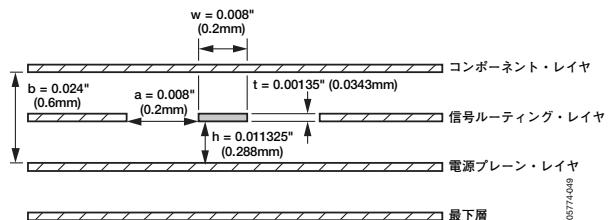

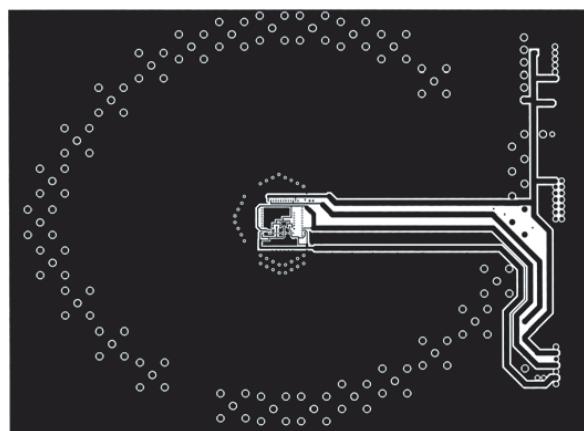

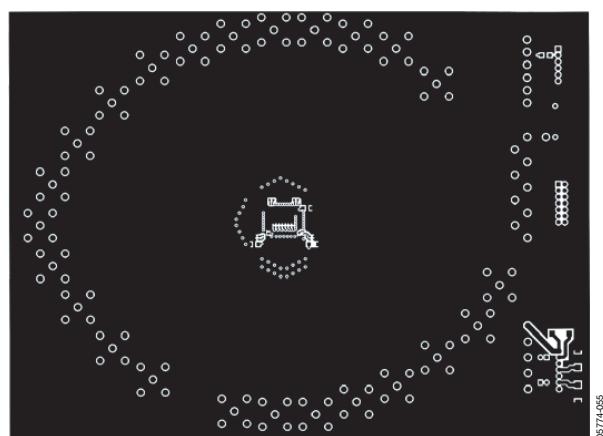

## 評価用ボード

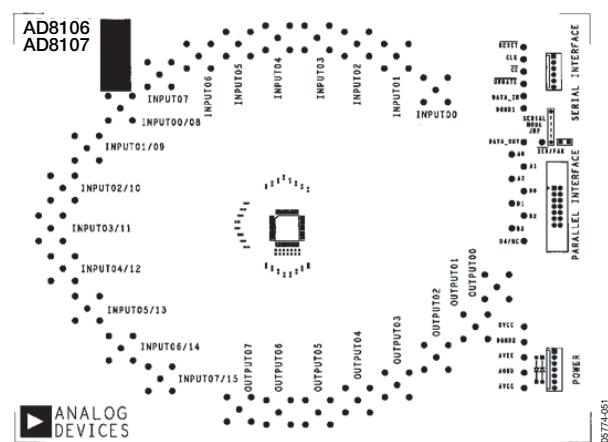

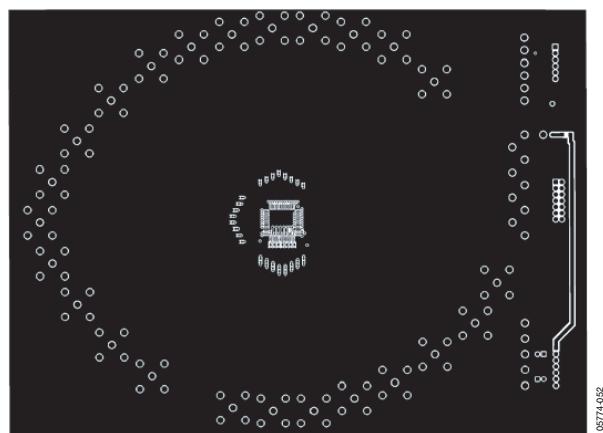

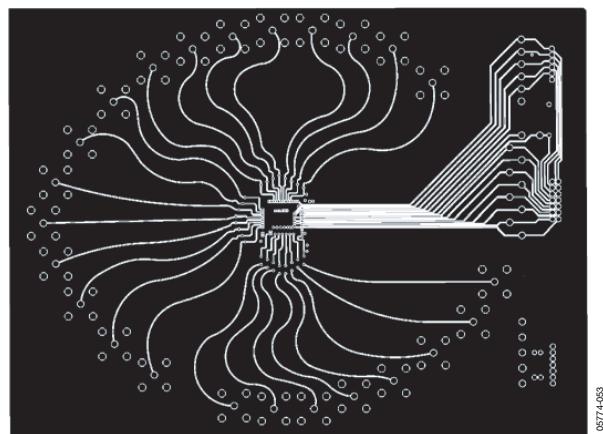

AD8106/AD8107の評価用ボードは4層のボードとなっています。いずれのデバイスも同じボードと外付け部品を使用します。唯一の違いはデバイスそのもので、アナログ・チャンネルによってゲイン1またはゲイン2を選択します。デバイスの仕様規定による高速性能を実現できるように、評価用ボードは入念に設計とテストが行われています。図49に、評価用ボードの回路図を示します。図50には、部品面のシルクスクリーンを示します。評価用ボードの4つのレイヤは、以下のようなレイアウトになっています。

- ・ コンポーネント・レイヤ (図51を参照)

- ・ 信号ルーティング・レイヤ (図52を参照)

- ・ 電源レイヤ (図53を参照)

- ・ 最下層 (図54を参照)

評価用ボード・パッケージには、以下が含まれています。

- ・ 完全実装基板 (BNCタイプ・コネクタ付き)

- ・ プリンタ・ポートを介してPCからボードを制御するためのWindows®ベースのソフトウェア

- ・ 評価用ボードとPCを接続するカスタム・ケーブル

- ・ ボード・レイアウトのガーバーファイルが入っているディスク

ビデオ・アプリケーション用に最適化されているため、全信号入力と全信号出力が $75\Omega$ 抵抗で終端されています。ストリップライン技術により、信号入力ラインと信号出力ラインの特性インピーダンスは $75\Omega$ に維持されています。図48に、入力パターンまたは出力パターンの1つの断面図とPCBレイヤの配置を示します。4つのレイヤの未使用領域はグラウンド・プレーンで埋めています。その結果、インピーダンスを制御できるだけでなく、入力パターンと出力パターンを十分にシールドできます。

図48. 入力パターンと出力パターンの断面図

このボードには、24個のBNCタイプ・コネクタがあります (入力用16個と出力用8個)。コネクタはデバイスを取り囲んで三日月状に配置されています。図53に示すように、これによって16本の入力信号パターンすべてと8本の信号出力パターンすべてが同じ長さになります。このようにすると、位相関係と信号間の遅延を入出力間で維持しなければならない全バス動作時のクロストークなどのテストに便利です。

3つの電源ピン (AVCC、DVCC、AVEE) は、高品質で低ノイズの $\pm 5V$ 電源に接続する必要があります。アナログもデジタルも同じ $\pm 5V$ 電源を使用しますが、評価用ボードのアナログ電源ピンとデジタル電源ピンには別々のケーブルを接続する必要があります。

一般的なルールとして、各電源ピン (または隣接する電源ピンのグループ) は、 $0.01\mu F$ のコンデンサを使ってローカルにデカップリングします。スペースの制約がある場合は、アナログ電源ピンをデカップリングした後にデジタル電源ピンをデカップリングします。多くの電源ピンをデカップリングするには、ピンのできるだけ近くに $0.1\mu F$ のコンデンサを配置します。最後は、 $10\mu F$ のコンデンサを使って、ボードに接続するところで電源ラインをデカップリングします。

# AD8106/AD8107

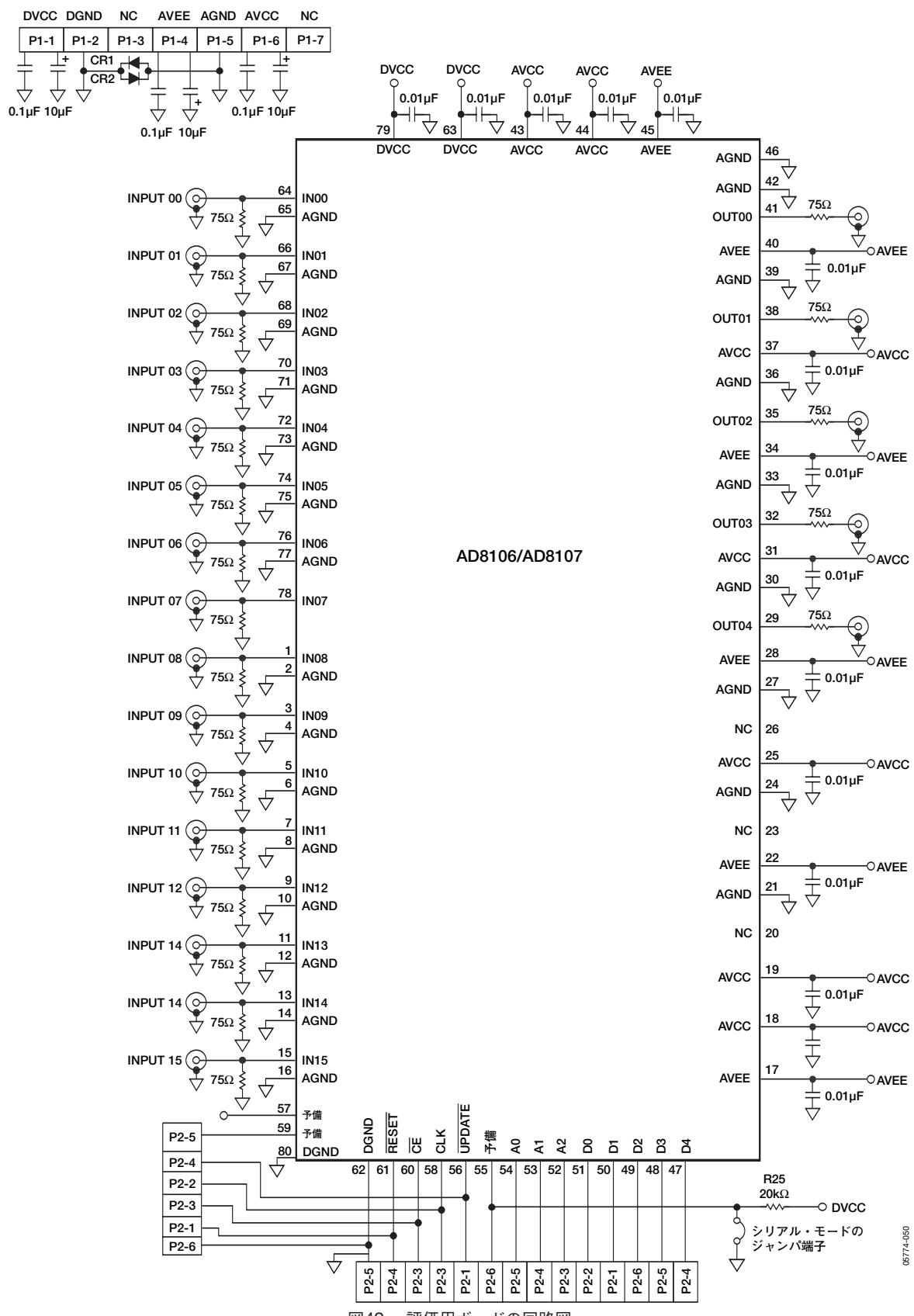

図49. 評価用ボードの回路図

## AD8106/AD8107

図50. 部品面のシルクスクリーン

図51. ボード・レイアウト (部品面)

図52. ボード・レイアウト (信号ルーティング・レイヤ)

## AD8106/AD8107

図53. ボード・レイアウト (電源プレーン・レイヤ)

図54. ボード・レイアウト (最下層)

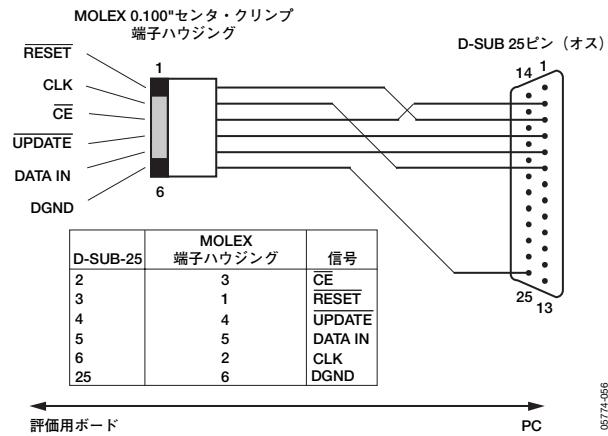

## 評価用ボードのPCからの制御

評価用ボードには、Windowsベースの制御ソフトウェアと、ボードのデジタル・インターフェースとPCのプリンタ・ポートを接続するカスタム・ケーブルが同梱されています。図55に、カスタム・ケーブルの接続を示します。ソフトウェアは、Windows 3.1以降で動作します。ソフトウェアをインストールする前に、実行中のWindowsアプリケーションを終了させてください。ソフトウェアをインストールするには、「Disk #1 of 2」のラベルがあるディスクをPCに挿入し、setup.exeファイルを実行します。画面に表示される指示に従って、インストールを行ってください。

図55. 評価用ボードのPC接続ケーブル

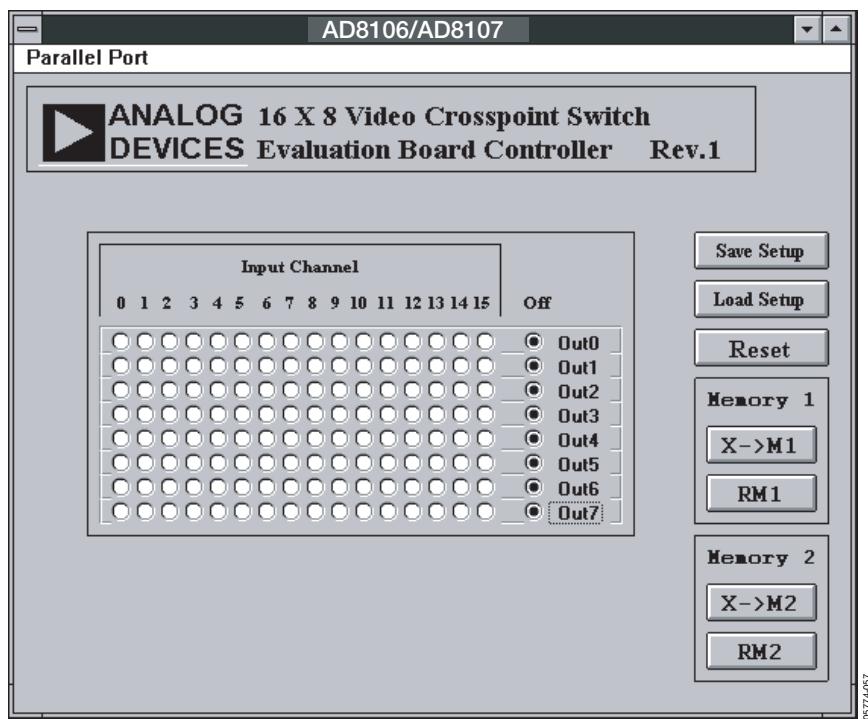

クロスポイント制御ソフトウェアを起動すると、使用するプリンタ・ポートを選択するように指示されます。大部分のPCにはLPT1と呼ばれるプリンタ・ポートが1つしかありませんが、PRNポートを使うラップトップ・コンピュータもあります。

図56に、初期リセット状態（全出力オフ）の制御ソフトウェアのメイン画面を示します。画面に表示された16×8アレイ内の該当するボタンをマウスでクリックするだけで、任意の入力を1つまたは複数の出力に接続できます。ボタンをクリックするごとに、必要な40ビットのデータ・ストリームが自動的に送信され、評価用ボードにラッピングされます。出力をオフにするには、off列内の該当するボタンをクリックします。全出力をオンにするには、RESETをクリックします。

ソフトウェアには、揮発性および不揮発性の設定保存用メモリがあります。揮発性メモリは2つまで設定を保存することができ、メモリ1バッファとメモリ2バッファを使って読み出することができます。これらは、電卓のメモリと同じように機能します。不揮発性メモリに設定を保存する場合は、Save Setup機能とLoad Setup機能を使うことができます。これによって、ディスク上のデータ・ファイルに設定が保存されます。

## プリンタ・ポートのデータライン上のオーバーシュート

プリンタ・ポートによっては、データライン上で大きなオーバーシュートを発生するものもあります。シリアル・クロック（D-Sub-25コネクタのpin 6）に使用しているpinでオーバーシュートが発生すると、通信の故障が生じことがあります。オーバーシュートをなくすには、評価用ボードのCLKラインとグラウンドの間にコンデンサを接続します。コンデンサを所定の位置にハンダ付けできるように、評価用ボードのハンダ面にパッドがあります。プリンタ・ポートからのオーバーシュートに応じて、コンデンサの大きさは0.01μF程度にする必要があります。

## AD8106/AD8107

図56. 評価用ボードのコントロール・パネル

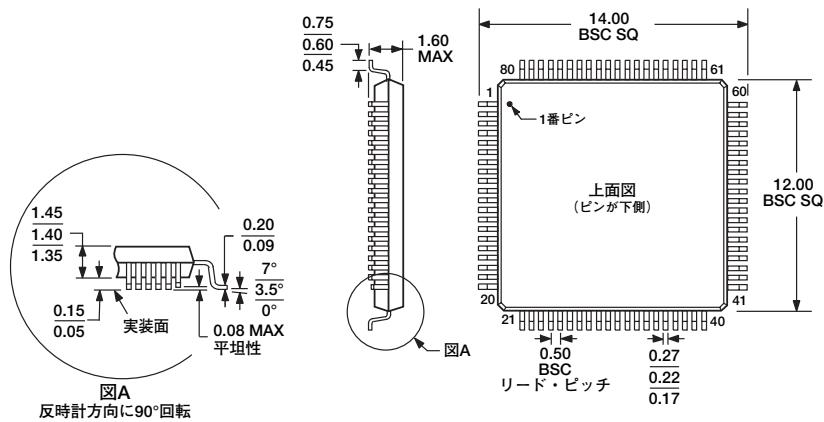

## 外形寸法

JEDEC規格MS-026-BDDに準拠

図57. 80ピン薄型クワッド・フラット・パッケージ [LQFP]

(ST-80-1)

寸法単位: mm

## オーダー・ガイド

| モデル                     | 温度範囲        | パッケージ                        | パッケージ・オプション |

|-------------------------|-------------|------------------------------|-------------|

| AD8106ASTZ <sup>1</sup> | -40 ~ +85°C | 80ピン薄型クワッド・フラット・パッケージ [LQFP] | ST-80-1     |

| AD8107ASTZ <sup>1</sup> | -40 ~ +85°C | 80ピン薄型クワッド・フラット・パッケージ [LQFP] | ST-80-1     |

| AD8106-EB               |             | 評価用ボード                       |             |

| AD8107-EB               |             | 評価用ボード                       |             |

<sup>1</sup> Z=鉛フリー製品