# MSOP/LFCSP、100 kSPS/500 kSPS、18-ビット PulSAR ADC

## データシート

## AD7989-1/AD7989-5

### 特長

#### 低消費電力

##### AD7989-1

100 kSPS で 400  $\mu$ W (VDD のみ)

100 kSPS で 700  $\mu$ W (全体)

##### AD7989-5

500 kSPS で 2 mW (VDD のみ)

500 kSPS で 3.5 mW (全体)

#### ノーミッシング・コードの 18 ビット分解能

#### スループット・レート

: 100 kSPS (AD7989-1) / 500 kSPS (AD7989-5)

INL :  $\pm 1$ LSB (typ) , 2LSB (max)

SNR : 98 dB (@1 kHz,  $V_{REF} = 5$  V)

SINAD : 97 dB (@1 kHz)

THD : -120 dB (@1 0kHz)

ダイナミック・レンジ : 99 dB ( $V_{REF} = 5$  V)

真の差動アナログ入力範囲 :  $\pm V_{REF}$

0 V ~  $V_{REF}$ ,  $V_{REF}$  は 2.4 V から 5.1 までの間

パイプライン遅延なし

2.5V 単電源で動作、1.8 V/2.5 V/3 V/5 V のロジック・インターフェース電源

SPI/QSPI™-/MICROWIRE™-/DSP-互換<sup>1</sup> のシリアル・インターフェース

複数の ADC のデジーチェーン接続

10 ピン・パッケージ : MSOP、3 mm×3 mm の LFCSP

### アプリケーション

バッテリ駆動の装置

データ・アクイジション・システム

医療用計測

地震データ・アクイジション・システム

<sup>1</sup> 米国特許 No. 6,703,961 により保護されています。

### 概要

AD7989-1/AD7989-5 は、単電源(VDD)で動作する 18 ビットの逐次比較型 A/D コンバータ (ADC) です。低消費電力の高速 18 ビット・サンプリング ADC、融通性に優れたシリアル・インターフェース・ポートを備えています。AD7989-1/AD7989-5 は、CNV の立ち上がりエッジで、IN+ピンと IN-ピンとの電位差をサンプルします。これらのピン上の電圧は通常、0 V と VREF 間で、逆位相で振幅します。リファレンス電圧 REF は外部から供給し、電源電圧 VDD、とは別に設定することができます。消費電力は、スループットと直線的に比例して変化します。

AD7989-1/AD7989-5 の、SPI 互換のシリアル・インターフェースでは、SDI 入力を使用し、単一の 3 線式バス上で複数の ADC をデジーチェーン接続することができます。この 3 線式バスは、別の VIO 電源を使うことで、1.8V、2.5V、3V、及び 5V ロジックと互換となります。

AD7989-1/AD7989-5 は、10 ピン MSOP または 10 ピン LFCSP パッケージで提供しており、-40~+85°C の温度範囲で仕様が規定されています。

表 1. MSOP、LFCSP 14-/16-/18-ビット PulSAR® ADC

| Bits            | 100 kSPS              | 250 kSPS                      | 400 kSPS to 500 kSPS                                                | $\geq 1000$ kSPS                           |

|-----------------|-----------------------|-------------------------------|---------------------------------------------------------------------|--------------------------------------------|

| 18 <sup>1</sup> | AD7989-1 <sup>2</sup> | AD7691 <sup>2</sup>           | AD7690 <sup>2</sup>                                                 | AD7982 <sup>2</sup>                        |

| 16 <sup>1</sup> | AD7684                | AD7687 <sup>2</sup>           | AD7989-5 <sup>2</sup><br>AD7688 <sup>2</sup><br>AD7693 <sup>2</sup> | AD7984 <sup>2</sup>                        |

| 16 <sup>3</sup> | AD7680<br>AD7683      | AD7685 <sup>2</sup><br>AD7694 | AD7686 <sup>2</sup><br>AD7988-5 <sup>2</sup>                        | AD7980 <sup>2</sup><br>AD7983 <sup>2</sup> |

| 14 <sup>3</sup> | AD7940                | AD7942 <sup>2</sup>           | AD7946 <sup>2</sup>                                                 |                                            |

<sup>1</sup> 真の差動 <sup>2</sup> ピン互換 <sup>3</sup> 擬似差動

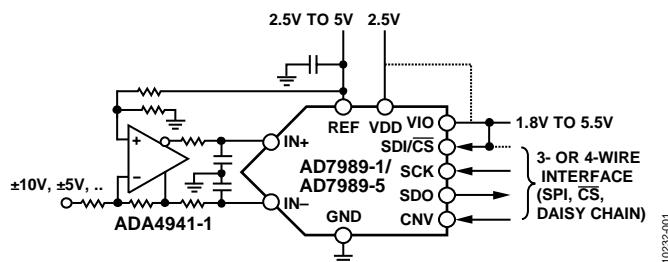

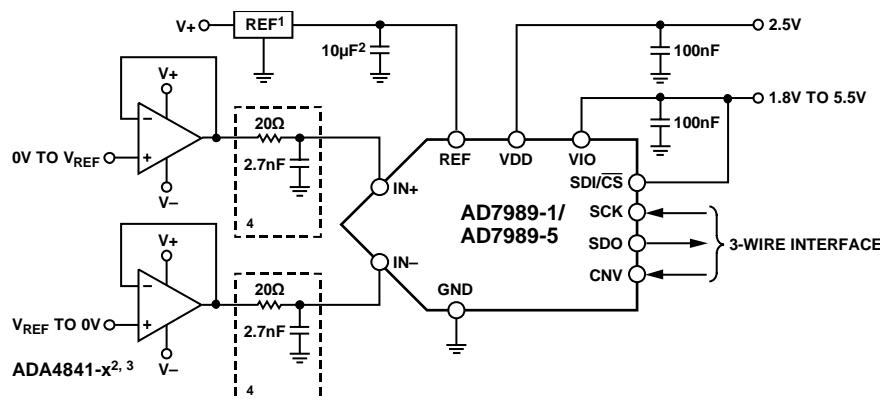

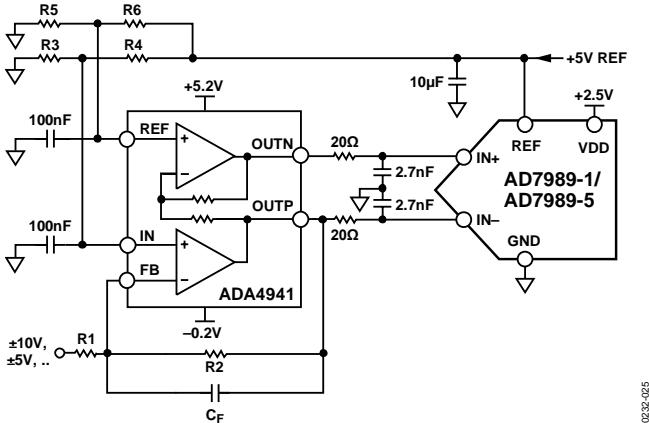

### アプリケーション回路図

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するもは、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合については、英語版をご参照ください。

## 目次

|                    |    |                               |    |

|--------------------|----|-------------------------------|----|

| 特長 .....           | 1  | ドライバ・アンプの選択 .....             | 15 |

| アプリケーション .....     | 1  | 単相・差動変換ドライバ .....             | 16 |

| 概要 .....           | 1  | 基準電圧入力 .....                  | 16 |

| アプリケーション回路図 .....  | 1  | 電源 .....                      | 16 |

| 改訂履歴 .....         | 2  | デジタル・インターフェース .....           | 16 |

| 仕様 .....           | 3  | <u>CS</u> モード、3線 .....        | 17 |

| タイミング仕様 .....      | 5  | <u>CS</u> モード、4線 .....        | 18 |

| 絶対最大定格 .....       | 7  | チェーン・モード .....                | 19 |

| ESDに関する注意 .....    | 7  | アプリケーション情報 .....              | 20 |

| ピン配置および機能の説明 ..... | 8  | Blackfin® DSPとのインターフェース ..... | 20 |

| 代表的な性能特性 .....     | 9  | レイアウト .....                   | 20 |

| 用語 .....           | 12 | AD7989-1/AD7989-5の性能評価 .....  | 21 |

| 動作原理 .....         | 13 | 外形寸法 .....                    | 22 |

| 回路説明 .....         | 13 | オーダー・ガイド .....                | 23 |

| コンバータの動作 .....     | 13 |                               |    |

| 代表的な接続図 .....      | 14 |                               |    |

| アナログ入力 .....       | 15 |                               |    |

## 改訂履歴

### 7/14—Rev. 0 to Rev. A

|                  |    |

|------------------|----|

| 機能セクションを変更 ..... | 1  |

| 表 1 を変更 .....    | 1  |

| 表 8 を変更 .....    | 15 |

### 1/14—Revision 0: Initial Version

## 仕様

特に指定のない限り、VDD = 2.5 V、VIO = 2.3 V~5.5 V、V<sub>REF</sub> = 5 V、T<sub>A</sub> = -40°C~+85°C

表 2.

| Parameter                                                     | Test Conditions/Comments                                                 | Min                      | Typ                    | Max                      | Unit             |

|---------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------|------------------------|--------------------------|------------------|

| RESOLUTION                                                    |                                                                          | 18                       |                        |                          | Bits             |

| ANALOG INPUT                                                  |                                                                          |                          |                        |                          |                  |

| Voltage Range                                                 | IN+ - IN-                                                                | -V <sub>REF</sub>        | +V <sub>REF</sub>      |                          | V                |

| Absolute Input Voltage                                        | IN+, IN-                                                                 | -0.1                     | V <sub>REF</sub> + 0.1 |                          | V                |

| Common-Mode Input Range                                       | IN+, IN-                                                                 | V <sub>REF</sub> × 0.475 | V <sub>REF</sub> × 0.5 | V <sub>REF</sub> × 0.525 | V                |

| Analog Input CMRR                                             | f <sub>IN</sub> = 450 kHz                                                |                          | 67                     |                          | dB               |

| Leakage Current at 25°C                                       | Acquisition phase                                                        |                          | 200                    |                          | nA               |

| Input Impedance                                               |                                                                          | アナログ入力の項目をご覧ください         |                        |                          |                  |

| ACCURACY                                                      |                                                                          |                          |                        |                          |                  |

| No Missing Codes                                              |                                                                          | 18                       |                        |                          | Bits             |

| Differential Nonlinearity Error                               |                                                                          | -0.85                    | ±0.5                   | +1.5                     | LSB              |

| Integral Nonlinearity Error                                   |                                                                          | -2                       | ±1                     | +2                       | LSB              |

| Transition Noise                                              | V <sub>REF</sub> = 5 V                                                   |                          | 1.05                   |                          | LSB <sup>1</sup> |

| Gain Error, T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> |                                                                          | -0.023                   | +0.004                 | +0.023                   | % of FS          |

| Gain Error Temperature Drift                                  |                                                                          |                          | ±1                     |                          | ppm/°C           |

| Zero Error, T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> |                                                                          |                          | ±100                   | +700                     | μV               |

| Zero Temperature Drift                                        |                                                                          |                          | 0.5                    |                          | ppm/°C           |

| Power Supply Rejection Ratio                                  | VDD = 2.5 V ± 5%                                                         |                          | 90                     |                          | dB               |

| THROUGHPUT                                                    |                                                                          |                          |                        |                          |                  |

| AD7989-1 Conversion Rate                                      |                                                                          | 0                        | 100                    |                          | kSPS             |

| AD7989-5 Conversion Rate                                      |                                                                          | 0                        | 500                    |                          | kSPS             |

| Transient Response                                            | Full-scale step                                                          |                          | 400                    |                          | ns               |

| AC ACCURACY                                                   |                                                                          |                          |                        |                          |                  |

| Dynamic Range                                                 | V <sub>REF</sub> = 5 V                                                   | 97                       | 99                     |                          | dB <sup>3</sup>  |

| Oversampled Dynamic Range <sup>4</sup>                        | V <sub>REF</sub> = 2.5 V                                                 |                          | 93                     |                          | dB <sup>3</sup>  |

| Signal-to-Noise Ratio                                         | f <sub>0</sub> = 1 kSPS                                                  |                          | 126                    |                          | dB <sup>3</sup>  |

| Spurious-Free Dynamic Range                                   | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 5 V, T <sub>A</sub> = 25°C   | 95.5                     | 98                     |                          | dB <sup>3</sup>  |

| Total Harmonic Distortion <sup>5</sup>                        | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 2.5 V, T <sub>A</sub> = 25°C |                          | 92.5                   |                          | dB <sup>3</sup>  |

| Signal-to-Noise-and-Distortion Ratio                          | f <sub>IN</sub> = 10 kHz                                                 |                          | -115                   |                          | dB <sup>3</sup>  |

|                                                               | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 5 V, T <sub>A</sub> = 25°C   |                          | -120                   |                          | dB <sup>3</sup>  |

|                                                               |                                                                          |                          | 97                     |                          | dB <sup>3</sup>  |

<sup>1</sup> LSB は最下位ビットを意味します。入力範囲が±5 V の場合、1LSB = 38.15 μV。

<sup>2</sup> 用語のセクションを参照してください。これらの仕様にはすべての温度範囲の変動が含まれますが、外付けリファレンス電圧の変動による影響は含まれません。

<sup>3</sup> デシベルで表示されているすべての仕様はフルスケール入力 FSR を基準とし、特に指定のない限り、フルスケールより 0.5 dB 小さい入力信号でテストされています。

<sup>4</sup> ダイナミック・レンジは、ADC をオーバーサンプリングしてスループット f<sub>S</sub>=500kSPS で動作させ、さらに f<sub>0</sub> のポストデジタル・フィルタ処理をして出力ワードレートを取得して測定。

<sup>5</sup> 製造時に f<sub>IN</sub> = 1 kHz でテスト。

特に指定のない限り、VDD = 2.3 V、VIO=2.3 V～5.5 V; V<sub>REF</sub>= 5 V; T<sub>A</sub>=-40°C～+85°C。

表 3.

| Parameter                                                                                                  | Test Conditions/Comments                                                                                                      | Min                                                                                                        | Typ                                                | Max       | Unit                       |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------|----------------------------|

| REFERENCE<br>Voltage Range<br>Load Current                                                                 | V <sub>REF</sub> = 5 V                                                                                                        | 2.4                                                                                                        | 250                                                | 5.1       | V<br>μA                    |

| SAMPLING DYNAMICS<br>-3 dB Input Bandwidth<br>Aperture Delay                                               | VDD = 2.5 V                                                                                                                   |                                                                                                            | 10                                                 | 2         | MHz<br>ns                  |

| DIGITAL INPUTS<br>Logic Levels<br>V <sub>IL</sub><br>V <sub>IH</sub>                                       | VIO > 3 V<br>VIO ≤ 3 V<br>VIO > 3 V<br>VIO ≤ 3 V                                                                              | -0.3<br>-0.3<br>0.7 × VIO<br>0.9 × VIO                                                                     | +0.3 × VIO<br>+0.1 × VIO<br>VIO + 0.3<br>VIO + 0.3 |           | V                          |

| I <sub>IL</sub><br>I <sub>IH</sub>                                                                         |                                                                                                                               | -1<br>-1                                                                                                   | +1<br>+1                                           |           | μA                         |

| DIGITAL OUTPUTS<br>Data Format<br>Pipeline Delay                                                           |                                                                                                                               | Serial, 18 bits, twos complement<br>Conversion results available immediately<br>after completed conversion |                                                    |           |                            |

| V <sub>OL</sub><br>V <sub>OH</sub>                                                                         | I <sub>SINK</sub> = +500 μA<br>I <sub>SOURCE</sub> = -500 μA                                                                  | VIO - 0.3                                                                                                  | 0.4                                                |           | V<br>V                     |

| POWER SUPPLIES<br>VDD<br>VIO<br>VIO Range<br>Standby Current <sup>1, 2</sup><br>AD7989-1 Power Dissipation | Specified performance<br>Functional range<br>VDD and VIO = 2.5 V, 25°C<br>VDD = 2.625 V, V <sub>REF</sub> = 5 V, VIO<br>= 3 V | 2.375<br>2.3<br>1.8                                                                                        | 2.5<br>5.5<br>5.5                                  | 2.625     | V<br>V<br>V<br>μA          |

| Total<br>VDD Only<br>REF Only<br>VIO Only                                                                  | 10 kSPS throughput<br>100 kSPS throughput                                                                                     |                                                                                                            | 70<br>700<br>400<br>170<br>130                     | 86<br>860 | μW<br>μW<br>μW<br>μW<br>μW |

| AD7989-5 Power Dissipation                                                                                 | VDD = 2.625 V, V <sub>REF</sub> = 5 V, VIO<br>= 3 V                                                                           |                                                                                                            |                                                    |           |                            |

| Total<br>VDD Only<br>REF Only<br>VIO Only                                                                  | 500 kSPS throughput                                                                                                           |                                                                                                            | 3.5<br>2<br>0.85<br>0.65                           | 4.3       | mW<br>mW<br>mW<br>mW       |

| Energy per Conversion                                                                                      |                                                                                                                               |                                                                                                            | 7.0                                                |           | nJ/sample                  |

| TEMPERATURE RANGE<br>Specified Performance                                                                 | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                          | -40                                                                                                        |                                                    | +85       | °C                         |

<sup>1</sup>すべてのデジタル入力を必要に応じて VIO またはグラウンドに接続。

<sup>2</sup> アクイジョン時。

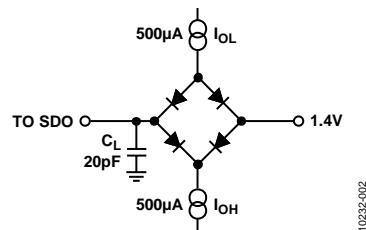

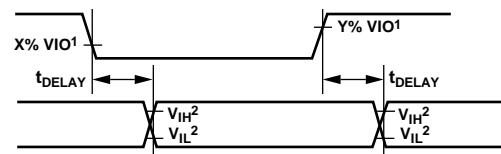

## タイミング仕様

特に指定のない限り、 $T_A = -40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ 、 $V_{DD} = 2.37 \text{ V} \sim 2.63 \text{ V}$ 、 $V_{IO} = 2.3 \text{ V} \sim 5.5 \text{ V}$ 。負荷条件については図2と図3を参照してください。

表4.

| Parameter                                                                              | Symbol        | Min  | Typ | Max  | Unit          |

|----------------------------------------------------------------------------------------|---------------|------|-----|------|---------------|

| AD7989-1                                                                               |               |      |     |      |               |

| Throughput Rate                                                                        |               |      |     | 100  | kSPS          |

| Conversion Time: CNV Rising Edge to Data Available                                     | $t_{CONV}$    |      |     | 9500 | ns            |

| Acquisition Time                                                                       | $t_{ACQ}$     | 500  |     |      | ns            |

| Time Between Conversions                                                               | $t_{CYC}$     | 10   |     |      | $\mu\text{s}$ |

| AD7989-5                                                                               |               |      |     |      |               |

| Throughput Rate                                                                        |               |      |     | 500  | kSPS          |

| Conversion Time: CNV Rising Edge to Data Available                                     | $t_{CONV}$    |      |     | 1600 | ns            |

| Acquisition Time                                                                       | $t_{ACQ}$     | 400  |     |      | ns            |

| Time Between Conversions                                                               | $t_{CYC}$     | 2    |     |      | $\mu\text{s}$ |

| CNV Pulse Width ( $\overline{CS}$ Mode)                                                | $t_{CNVH}$    | 500  |     |      | ns            |

| SCK Period ( $\overline{CS}$ Mode)                                                     | $t_{SCK}$     |      |     |      |               |

| VIO Above 4.5 V                                                                        |               | 10.5 |     |      | ns            |

| VIO Above 3 V                                                                          |               | 12   |     |      | ns            |

| VIO Above 2.7 V                                                                        |               | 13   |     |      | ns            |

| VIO Above 2.3 V                                                                        |               | 15   |     |      | ns            |

| SCK Period (Chain Mode)                                                                | $t_{SCK}$     |      |     |      |               |

| VIO Above 4.5 V                                                                        |               | 11.5 |     |      | ns            |

| VIO Above 3 V                                                                          |               | 13   |     |      | ns            |

| VIO Above 2.7 V                                                                        |               | 14   |     |      | ns            |

| VIO Above 2.3 V                                                                        |               | 16   |     |      | ns            |

| SCK Low Time                                                                           | $t_{SCKL}$    | 4.5  |     |      | ns            |

| SCK High Time                                                                          | $t_{SCKH}$    | 4.5  |     |      | ns            |

| SCK Falling Edge to Data Remains Valid                                                 | $t_{HSDO}$    | 3    |     |      | ns            |

| SCK Falling Edge to Data Valid Delay                                                   | $t_{DSDO}$    |      |     |      |               |

| VIO Above 4.5 V                                                                        |               |      | 9.5 |      | ns            |

| VIO Above 3 V                                                                          |               |      | 11  |      | ns            |

| VIO Above 2.7 V                                                                        |               |      | 12  |      | ns            |

| VIO Above 2.3 V                                                                        |               |      | 14  |      | ns            |

| CNV or SDI Low to SDO D15 MSB Valid ( $\overline{CS}$ Mode)                            | $t_{EN}$      |      |     |      |               |

| VIO Above 3 V                                                                          |               |      | 10  |      | ns            |

| VIO Above 2.3 V                                                                        |               |      | 15  |      | ns            |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance ( $\overline{CS}$ Mode) | $t_{DIS}$     |      |     | 20   | ns            |

| SDI Valid Setup Time from CNV Rising Edge ( $\overline{CS}$ Mode)                      | $t_{SSDICNV}$ | 5    |     |      | ns            |

| SDI Valid Hold Time from CNV Rising Edge ( $\overline{CS}$ Mode)                       | $t_{HSDICNV}$ | 2    |     |      | ns            |

| SCK Valid Setup Time from CNV Rising Edge (Chain Mode)                                 | $t_{SSCKCNV}$ | 5    |     |      | ns            |

| SCK Valid Hold Time from CNV Rising Edge (Chain Mode)                                  | $t_{HSCKCNV}$ | 5    |     |      | ns            |

| SDI Valid Setup Time from SCK Falling Edge (Chain Mode)                                | $t_{SSDISCK}$ | 2    |     |      | ns            |

| SDI Valid Hold Time from SCK Falling Edge (Chain Mode)                                 | $t_{HSDISCK}$ | 3    |     |      | ns            |

図 2. デジタル・インターフェース・タイミングの負荷回路

<sup>1</sup>FOR VIO  $\leq$  3.0V, X = 90 AND Y = 10; FOR VIO > 3.0V, X = 70 AND Y = 30.

<sup>2</sup>MINIMUM V<sub>IH</sub> AND MAXIMUM V<sub>IL</sub> USED. SEE DIGITAL INPUTS SPECIFICATIONS IN TABLE 3.

10232-403

図 3. タイミング測定の電圧レベル

## 絶対最大定格

表 5.

| Parameter                                       | Rating                                      |

|-------------------------------------------------|---------------------------------------------|

| Analog Inputs<br>IN+, IN- to GND <sup>1</sup>   | -0.3 V to $V_{REF} + 0.3$ V or $\pm 130$ mA |

| Supply Voltage<br>REF, VIO to GND               | -0.3 V to +6.0 V                            |

| VDD to GND                                      | -0.3 V to +3.0 V                            |

| VDD to VIO                                      | +3 V to -6 V                                |

| Digital Inputs to GND                           | -0.3 V to VIO + 0.3 V                       |

| Digital Output to GND                           | -0.3 V to VIO + 0.3 V                       |

| Storage Temperature Range                       | -65°C to +150°C                             |

| Junction Temperature                            | 150°C                                       |

| $\theta_{JA}$ Thermal Impedance<br>10-Lead MSOP | 200°C/W                                     |

| 10-Lead LFCSP_WD                                | 48.7°C/W                                    |

| $\theta_{JC}$ Thermal Impedance<br>10-Lead MSOP | 44°C/W                                      |

| 10-Lead LFCSP_WD                                | 2.96°C/W                                    |

| Reflow Soldering                                | JEDEC Standard (J-STD-020)                  |

<sup>1</sup> IN+ および IN-についてはアナログ入力セクションの説明を参照してください。

上記の絶対最大定格またはそれ以上のストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の範囲に記載する規定値以上での製品の動作を定めたものではありません。製品を長時間最大動作条件以上で動作させると製品の信頼性に影響を与えます。

### ESDに関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

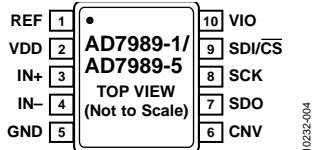

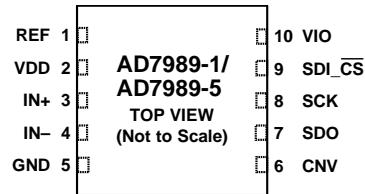

## ピン配置およびピン機能説明

図 4.10 ピン MSOP のピン配置

NOTES:

1. THE EXPOSED PAD CAN BE CONNECTED TO GND.

図 5.10 ピン LFCSP のピン配置

表 6. ピン機能の説明

| ピン番号 | 記号     | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                                                                                                                                                       |

|------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | REF    | AI               | リファレンス電圧入力。REFの範囲は2.4 V～5.1 Vです。このピンの電圧はGNDピンに対する電圧であり、ピンの近くで10 μFのコンデンサでGNDにデカッピングする必要があります。                                                                                                                                                                                                                                            |

| 2    | VDD    | P                | 電源                                                                                                                                                                                                                                                                                                                                       |

| 3    | IN+    | AI               | 正側差動アナログ入力。                                                                                                                                                                                                                                                                                                                              |

| 4    | IN-    | AI               | 負側差動アナログ入力。                                                                                                                                                                                                                                                                                                                              |

| 5    | GND    | P                | 電源グラウンド                                                                                                                                                                                                                                                                                                                                  |

| 6    | CNV    | DI               | 変換入力。この入力は複数の機能を持っています。入力信号の立ち上がりエッジで、変換が開始され、デバイスのインターフェース・モード(チェーン・モードまたはチップセレクト(CS)モード)が選択されます。CSモードでは、CNVがロー・レベルのときにSDOピンがイネーブルされます。チェーン・モードでは、CNVがハイ・レベルのときにデータを読み出します。                                                                                                                                                             |

| 7    | SDO    | DO               | シリアル・データ出力。変換結果はこのピンに出力されます。SCKに同期します。                                                                                                                                                                                                                                                                                                   |

| 8    | SCK    | DI               | シリアル・データ・クロック入力。デバイスが選択されると、変換結果がこのクロックでシフト出力されます。                                                                                                                                                                                                                                                                                       |

| 9    | SDI/CS | DI               | シリアル・データ入力/チップセレクト。この入力は複数の機能を持っています。この入力は、ADCのインターフェース・モードを次のように選択します。<br>CNVの立ち上がりエッジで、このピンがロー・レベルであれば、チェーン・モードが選択されます。このモードでは、SDIはデータ入力として使用され、複数のADCの変換結果を1本のSDO線にディジーチェーン接続します。SDI/CSのデジタル・データ・レベルはSCKの16サイクル分の遅延でSDOに出力されます。<br>CNVの立ち上がりエッジで、SDI/CSがハイ・レベルであれば、CSモードが選択されます。このモードでは、SDI/CSまたはCNVのいずれかがロー・レベルのときにシリアル出力信号が有効になります。 |

| 10   | VIO    | P                | 入出力インターフェースのデジタル電源。このピンには通常、ホスト・インターフェースと同じ電源電圧(1.8 V、2.5 V、3 V、または5 V)が加えられます。                                                                                                                                                                                                                                                          |

|      | EP     |                  | 露出パッド。リードフレーム・チップスケール・パッケージ(LFCSP)の場合、露出パッドはGNDに接続することができます。この接続は、電気的性能を満たすためのものではありません。                                                                                                                                                                                                                                                 |

<sup>1</sup>AI = アナログ入力、DI = デジタル入力、DO = デジタル出力、P = 電源

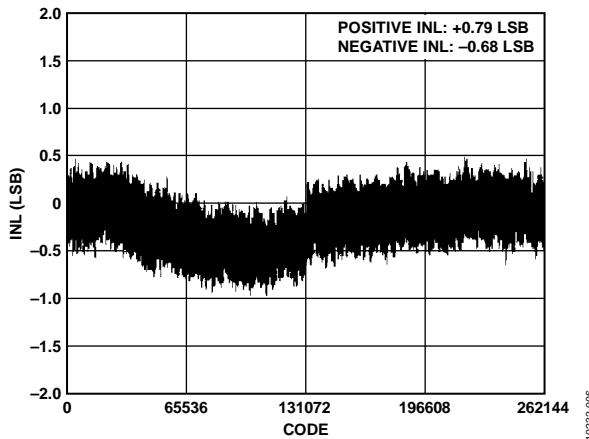

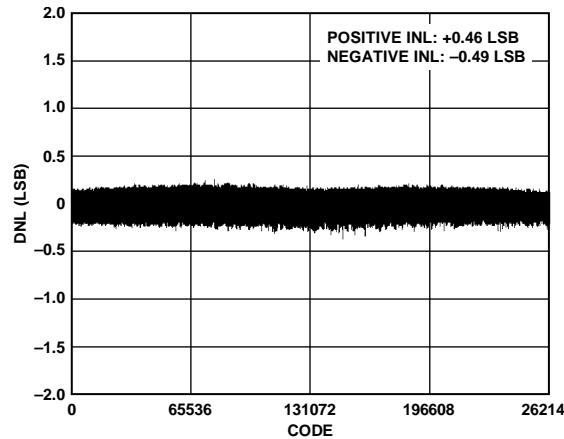

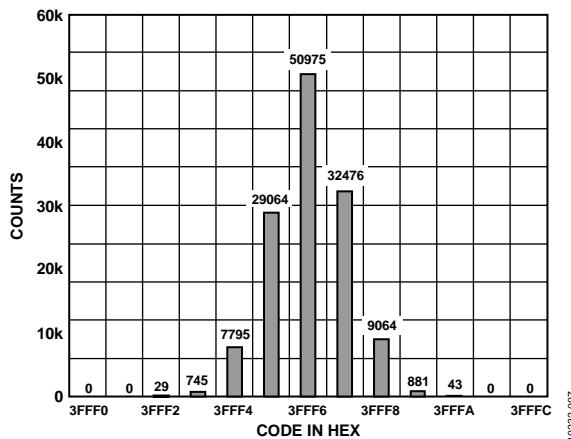

## 代表的な性能特性

VDD = 2.5 V, V<sub>REF</sub> = 5.0 V, VIO = 3.3 V.

図 6. 積分非直線性対コード

図 9. 差動非直線性対コード

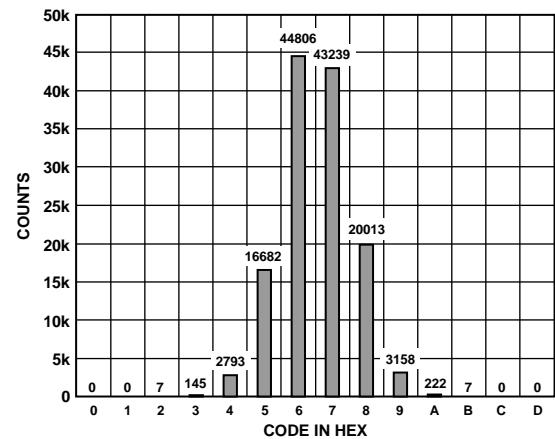

図 7. コード中央での DC 入力のヒストグラム

図 10. コード変化での DC 入力のヒストグラム

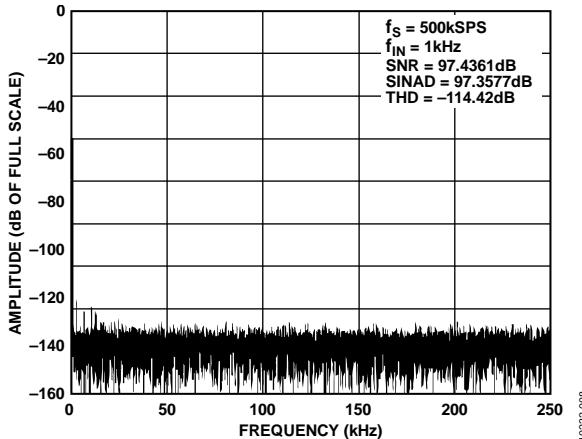

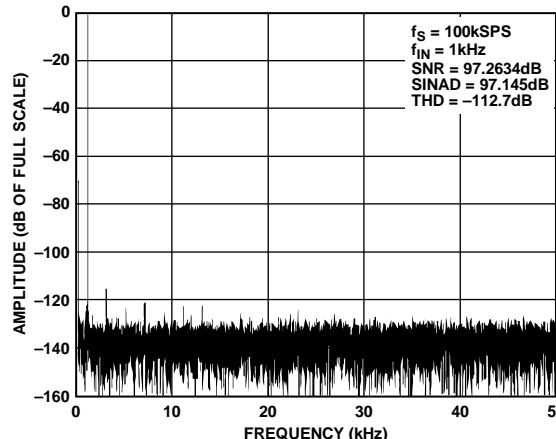

図 8. AD7989-5 FFT プロット

図 11. AD7989-1 FFT プロット

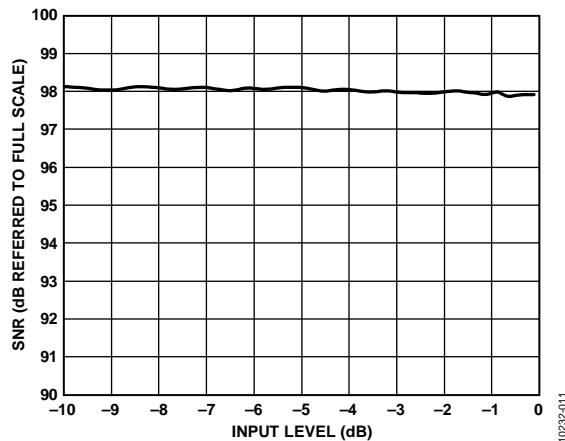

図 12.SNR 対入力レベル

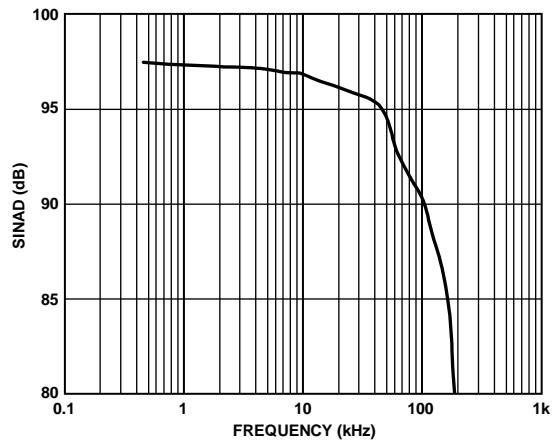

図 15.SINAD 対周波数

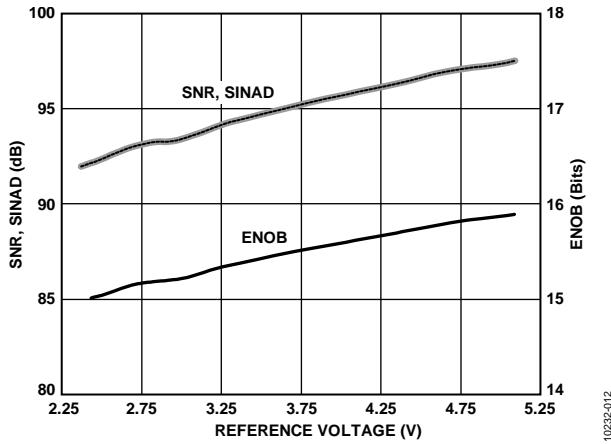

図 13. SNR、SINAD、ENOB 対リファレンス電圧

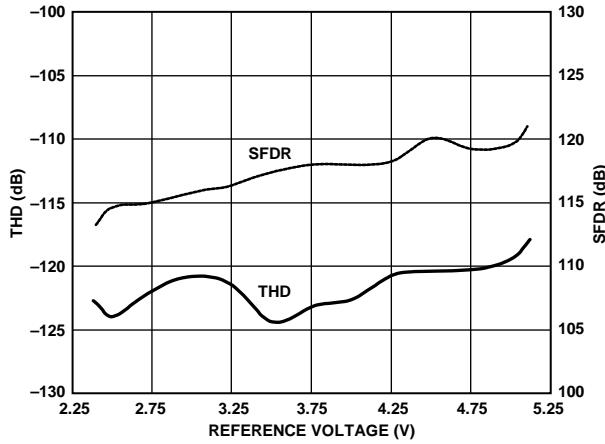

図 16. THD, SFDR 対リファレンス電圧

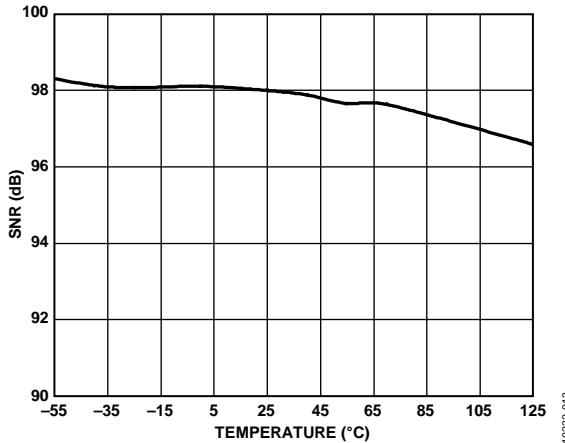

図 14.SNR 対温度

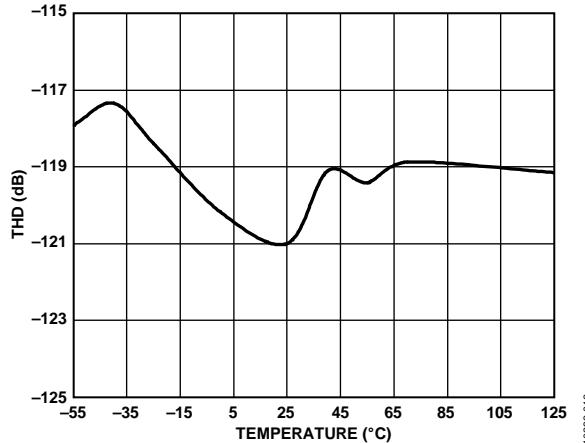

図 17.THD 対温度

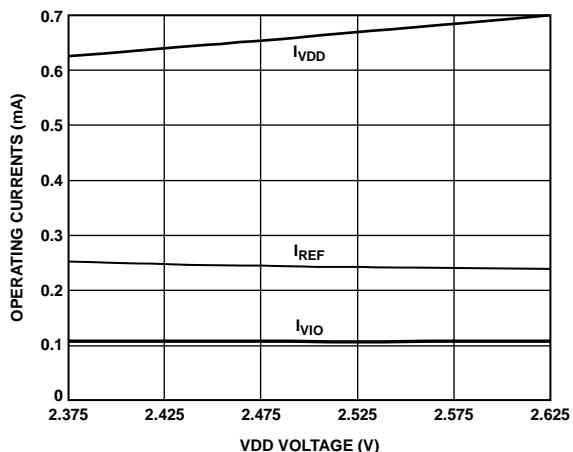

図 18.動作電流対 VDD 電圧 (AD7989-5)

10232-118

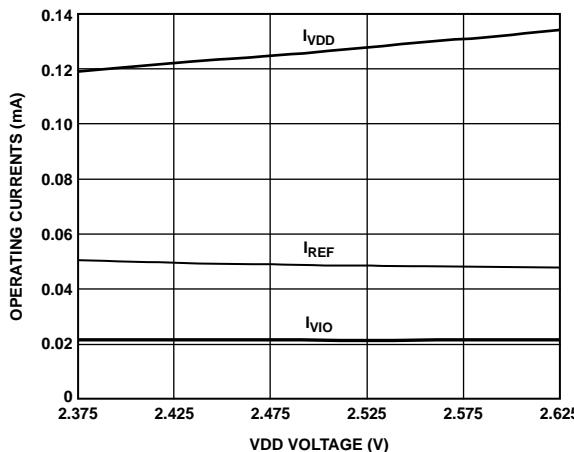

図 21.動作電流対 VDD 電圧 (AD7989-1)

10232-11A

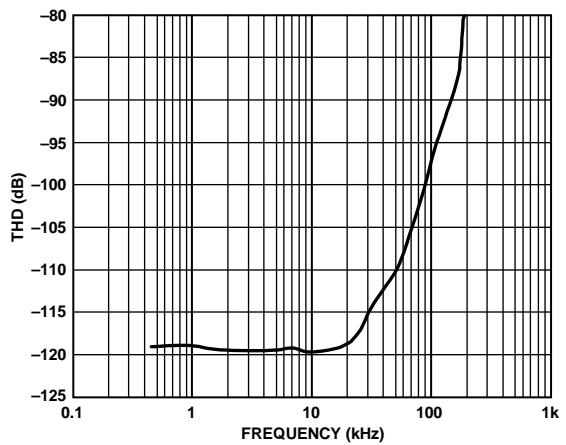

図 19. THD 対周波数

10232-017

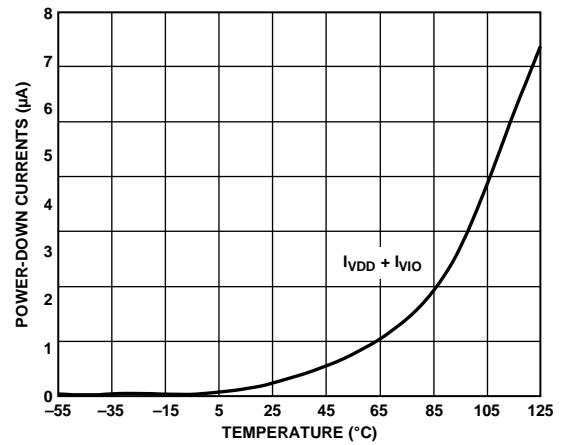

図 22.パワーダウン電流対温度

10232-018

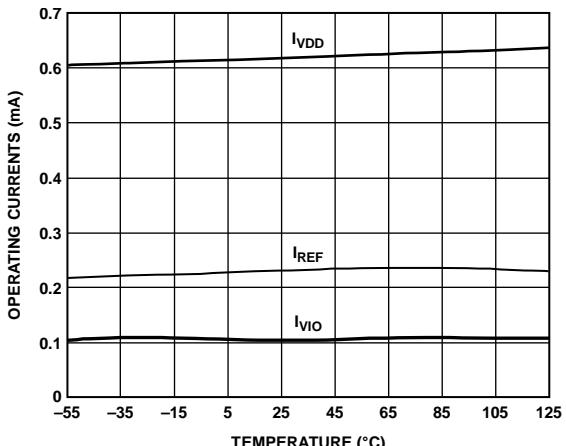

図 20.動作電流対温度 (AD7989-5)

10232-120

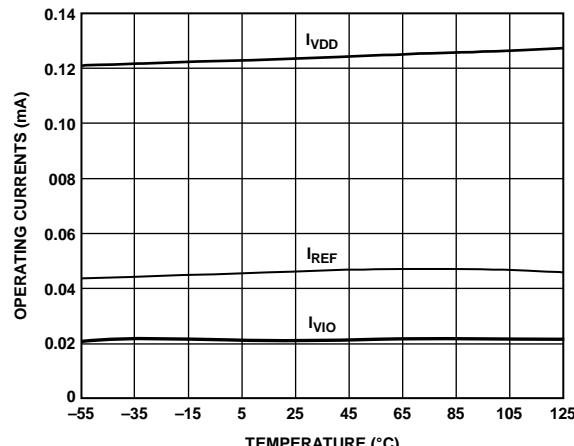

図 23.動作電流対温度 (AD7989-1)

10232-123

## 用語

### Integral Nonlinearity Error (INL : 積分非直線性誤差)

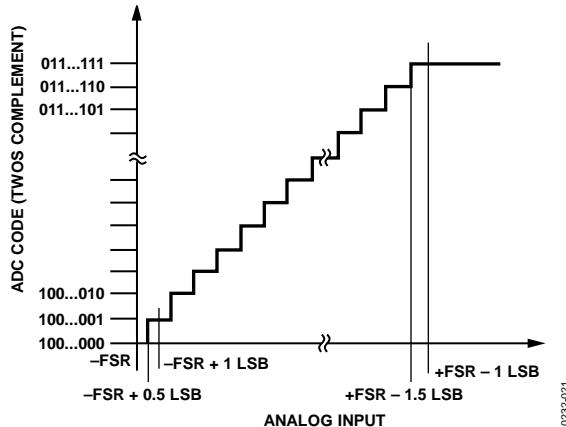

INLは、負側のフルスケールと正側のフルスケールを結ぶ直線と実際のコード出力との誤差として定義されます。負側フルスケールとして使用されるポイントは、最初のコード遷移より 1/2 LSB だけ下に存在します。正側フルスケールは、最後のコード遷移より 1/2 LSB だけ上のレベルと定義されます。偏差は各コードの中央と直線との間の距離として測定されます(図 25)。

### Differential Nonlinearity Error (DNL : 微分非直線性誤差)

理想的な ADC では、各コード遷移は 1 LSB だけ離れた位置で発生します。DNL は、この理論値からの最大偏差を意味します。微分非直線性は、ノーミス・コードが保証される分解能として規定されることがあります。

### Zero Error (ゼロ誤差)

ゼロ誤差は、理想的なミッドスケール値入力電圧(0 V)とミッドスケール出力コード(0LSB)を発生する実際の電圧との差を意味します。

### Gain Error (ゲイン誤差)

最初の変化(100...00 から 100...01 へ) は負の公称フルスケール ( $\pm 5$  V の範囲で -4.999981 V) の 1/2 LSB 上のレベルで発生しなければなりません。最後の変化(011...011 から 011...11 へ) は公称フルスケール ( $\pm 5$  V の範囲で +4.999943 V) の 1/2 LSB 下のアナログ電圧に対して発生します。ゲイン誤差は、最後の変化の実際のレベルと最初の変化の実際のレベルとの差と、対応する理論値レベル間の差との偏差を表します。

### Spurious-Free Dynamic Range (SFDR : スピリアス・フリー・ダイナミック・レンジ)

SFDR は入力信号の rms 振幅値とピーク・スピリアス信号との差を意味し、dB 値で表します。

### Effective Number of Bits ENOB : 実効ビット数

ENOB は、正弦波を入力したときの分解能を表します。ENOB と SINAD の関係は次の式で表されます：

$$ENOB = (SINAD_{dB} - 1.76)/6.02$$

ビット数で表されます。

### Noise-Free Code Resolution (NFCR : ノイズ・フリー・コード分解能)

ノイズ・フリー・コード分解能は、それを超えると個々のコードが区別できなくなるビット数。NFCR は次式を使って計算します：

$$Noise-Free Code Resolution = \log_2(2^N/Peak-to-Peak Noise)$$

ビット数で表されます。

### Effective Resolution (有効分解能)

有効分解能は次式を使って計算します：

$$Effective Resolution = \log_2(2^N/RMS Input Noise)$$

ビット数で表されます。

### Total Harmonic Distortion (THD : 総合高調波歪み)

THD とは、基本波から 5 次高調波成分までの rms 値の総和の、フルスケール入力信号の rms 値に対する比を意味し、デシベル値で表します。

### Dynamic Range (ダイナミック・レンジ)

ダイナミック・レンジは、入力を短絡して測定した合計 rms ノイズに対するフルスケールの rms 値の比を表します。ダイナミック・レンジの値は dB で表されます。ダイナミック・レンジは、すべての雑音源と DNL アーティファクトが含まれるように -60dB の信号レベルで測定されます。

### Signal-to-Noise Ratio (SNR : 信号対ノイズ比)

SNR は、実際の入力信号 rms 値の、ナイキスト周波数より下の全スペクトル成分の rms 値総和から高調波成分と DC 成分を除いた値に対する比です。SNR の値は dB で表されます。

### Signal-to-Noise-and-Distortion Ratio (SINAD : 信号対ノイズおよび歪み比)

SINAD は、測定した入力信号 rms 値の、ナイキスト周波数より下の全スペクトル成分の rms 値総和 (DC 以外の高調波を含む)に対する比です。SINAD の値は dB で表されます。

### Aperture Delay (アペーチャ遅延)

アペーチャ遅延はアクイージション性能を表し、CNV 入力の立ち上がりエッジから入力信号が変換用にホールドされるまでの時間として測定されます。

### Transient Response (過渡応答)

過渡応答はフルスケールのステップ関数が与えられてから ADC が正常に入力を取得するまでに要する時間を表します。

## 動作原理

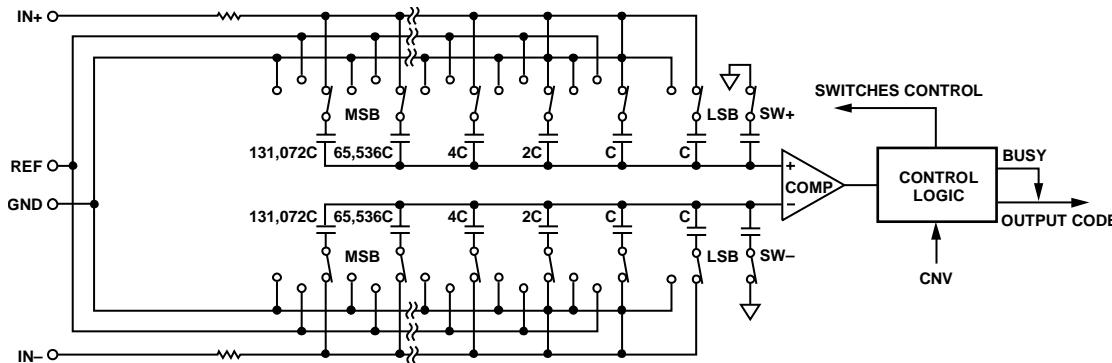

図 24. ADC の簡略化した回路図

## 回路説明

AD7989-1/AD7989-5 は单電源動作の逐次比較型アーキテクチャを採用した高速、高精度、低消費電力の 18 ビット A/D コンバータ(ADC)です。

AD7989-5 は毎秒 500,000 サンプルの AD 変換 (500 kSPS) が、AD7989-1 は毎秒 100,000 サンプルの AD 変換 (100 kSPS) が可能であり、変換動作の合間はパワーダウンします。AD7989-1 が 100 kSPS で動作する場合、その典型的な消費電力は僅か  $700 \mu\text{W}$  であり、バッテリ駆動のアプリケーションに最適です。

AD7989-1/AD7989-5 はトラック&ホールドを内蔵し、パイプライン遅延やレイテンシがないため、マルチプレクスされた複数チャンネルのアプリケーションに最適です。

AD7989-1/AD7989-5 は、1.8 V～5 V のデジタル・ロジック・ファミリとインタフェースすることができます。どちらも省スペースと柔軟な構成が可能な、10 ピン MSOP または 10 ピン LFCSP パッケージを採用しています。

## コンバータの動作

AD7989-1/AD7989-5 は、電荷再分配型 DAC をベースとする逐次比較型 A/D コンバータです。図 24 に、ADC の簡単化した回路図を示します。この容量性 DAC は、2 進数の重みを持った 18 個のコンデンサから成る 2 列の同じアレイで構成されており、各アレイはコンパレータの 2 つの入力に接続されています。

アクイジョン・フェーズでは、コンパレータの入力に接続されたアレイの端子は、SW+ と SW- を経由して GND に接続されます。すべての独立したスイッチはアナログ入力に接続されます。したがって、コンデンサ・アレイはサンプリング・コンデンサとして使用され、IN+ 入力と IN- 入力でアナログ信号が取り込まれます。アクイジョン・フェーズが終わると、CNV 入力がハイ・レベルになり、変換フェーズが開始されます。変換フェーズが開始されると、先ず SW+ と SW- が開きます。次に、2 つのコンデンサ・アレイは入力から切り離されて、GND 入力に接続されます。そうすると、アクイジョン・フェーズの終わりに取り込まれた、IN+ と IN- 間の差動電圧がコンパレータ入力に接続されて、コンパレータは平衡しなくなります。コンデンサ・アレイの各エレメントを GND と REF の間でスイッチングすることにより、コンパレータ入力は 2 進数重みの電圧ステップ (VREF/2, VREF/4, ..., VREF/262,144) で変化します。コントロール・ロジックがこれらのスイッチをトグルして (MSB から開始)、コンパレータが再度平衡するようにします。この処理が終了すると、デバイスはアクイジョン・フェーズに戻り、コントロール・ロジックが ADC 出力コードを発生します。

AD7989-1/AD7989-5 は変換クロックを内蔵しているため、変換プロセスの際にシリアル・クロック (SCK) は不要です。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するもは、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合については、英語版をご参照ください。

## 伝達関数

AD7989-1/AD7989-5 の理論伝達特性を図 25 と表 7 に示します。

図 25. ADC の理想的な伝達関数

表 7. 出力コードと入力電圧の理論値

| 説明               | アナログ入力<br>$V_{REF} = 5\text{ V}$ | デジタル出力コード(Hex)       |

|------------------|----------------------------------|----------------------|

| +FSR - 1 LSB     | +4.999962 V                      | 0x1FFFF <sup>1</sup> |

| Midscale + 1 LSB | +38.15 $\mu\text{V}$             | 0x00001              |

| Midscale         | 0 V                              | 0x00000              |

| Midscale - 1 LSB | -38.15 $\mu\text{V}$             | 0x3FFF               |

| -FSR + 1 LSB     | -4.999962 V                      | 0x20001              |

| -FSR             | -5 V                             | 0x20000 <sup>2</sup> |

<sup>1</sup> アナログ入力範囲より上のコードでもあります( $V_{REF} \sim VGND$  より上の  $VIN+ \sim VIN-$ )。

<sup>2</sup> アナログ入力範囲より下のコードでもあります( $VGND$  より下の  $VIN+ \sim VIN-$ )。

## 代表的な接続図

図 26 に、複数の電源を使用した場合の AD7989-1/AD7989-5 の推奨接続図の例を示します。

<sup>1</sup> SEE THE VOLTAGE REFERENCE INPUT SECTION FOR REFERENCE SELECTION.

<sup>2</sup>  $C_{REF}$  IS USUALLY A  $10\mu\text{F}$  CERAMIC CAPACITOR (X5R).

SEE THE RECOMMENDED LAYOUT IN FIGURE 39 AND FIGURE 40.

<sup>3</sup> SEE THE DRIVER AMPLIFIER CHOICE SECTION.

<sup>4</sup> OPTIONAL FILTER. SEE THE ANALOG INPUTS SECTION.

10232-022

図 26. 複数の電源を使用する代表的なアプリケーション図

## アナログ入力

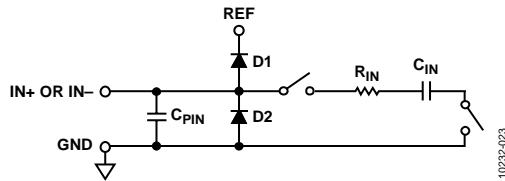

図 27 に、AD7989-1/AD7989-5 の入力構造の等価回路を示します。

ダイオード D1 と D2 は、アナログ入力 IN+ と IN- に対する ESD 保護用です。アナログ入力信号は基準入力電圧(REF)より 0.3 V 以上高くならないよう注意する必要があります。アナログ入力がこのレベルを超えると、ダイオードが順バイアスとなって電流を通し始めます。これらのダイオードは、最大 130 mA の順方向バイアス電流を処理することができます。しかし、入力バッファの電源（例：図 26 の ADA4841-x の電源）が REF の電源と異なる場合、アナログ入力信号が電源レールを 0.3 V 以上超過することがあります。このような場合、たとえば短絡電流制限機能を持つ入力バッファを使ってデバイスを保護することができます。

図 27. アナログ入力等価回路

このアナログ入力構造を使うと、IN+ と IN- の間の差動信号のサンプリングが可能になります。この差動入力の採用により、両入力に共通する小さい信号を除去することができます。

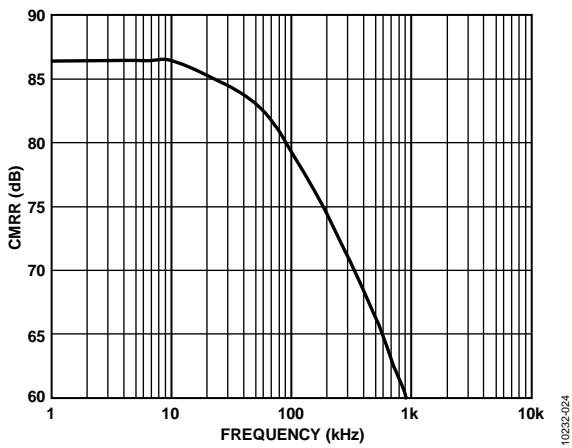

図 28. アナログ入力 CMRR の周波数特性

アクイジション・フェーズでは、アナログ入力(IN+ または IN-) のインピーダンスは、コンデンサ C<sub>PIN</sub> と、R<sub>IN</sub> および C<sub>IN</sub> の直列接続の回路との並列組み合わせとしてモデル化することができます。C<sub>PIN</sub> は主にピン容量です。R<sub>IN</sub> は 400 kΩ (typ) であり、直列抵抗とスイッチのオン抵抗から構成される集中定数です。C<sub>IN</sub> は 30 pF(typ) であり、主に ADC サンプリング・コンデンサから構成されています。

スイッチが閉じているサンプリング・フェーズでは、入力インピーダンスは C<sub>PIN</sub> に制限されます。R<sub>IN</sub> と C<sub>IN</sub> により、1 次ローパス・フィルタが構成されるため、不要な折り返し効果が削減され、ノイズが制限されます。

駆動回路のソース・インピーダンスが小さい場合は、AD7989-1/AD7989-5 を直接駆動することができます。ソース・インピーダンスが大きい場合には、AC 性能、特に THD が大きい影響を受けます。DC 性能は、入力インピーダンスからあまり影響を受けません。最大ソース・インピーダンスは、許容可能な THD

の大きさに依存します。THD の値は、ソース・インピーダンスと最大入力周波数の関数として性能低下します。

## ドライバ・アンプの選択

AD7989-1/AD7989-5 の駆動は簡単ですが、ドライバ・アンプは次の条件を満たす必要があります。

- AD7989-1/AD7989-5 の SNR 性能と遷移ノイズ性能を維持するためには、ドライバ・アンプが保証するノイズをできるだけ低く抑える必要があります。ドライバから発生するノイズは、AD7989-1/AD7989-5 アナログ入力回路の R<sub>IN</sub> と C<sub>IN</sub> から構成される 1 次ローパス・フィルタまたは外付けフィルタ(使用した場合)により除去されます。AD7989-1/AD7989-5 のノイズは 40 μV rms(typ) であるため、アンプに起因する SNR の性能低下は次式で与えられます。

$$SNR_{LOSS} = 20 \log \left( \frac{40}{\sqrt{40^2 + \frac{\pi}{2} f_{-3dB} (N_{eN})^2}} \right)$$

- ここで、f<sub>-3dB</sub> は AD7989-1/AD7989-5 (10 MHz) の入力帯域幅 (MHz)、または入力フィルタのカットオフ周波数 (使用した場合)。N はアンプのノイズ・ゲイン (たとえば、バッファ構成では 1)。

e<sub>N</sub> は、オペアンプの等価入力ノイズ電圧(nV/√Hz)。

- AC アプリケーションの場合、ドライバは AD7989-1/AD7989-5 と釣り合う THD 性能を持つ必要があります。

- 多チャンネルをマルチプレクスするアプリケーションの場合、ドライバ・アンプと AD7989-1/AD7989-5 アナログ入力回路は、コンデンサ・アレイへのフル・スケール・ステップに対して 18 ビット・レベル(0.0004%、4 ppm)でセトリングする必要があります。アンプのデータシートでは、一般に 0.1~0.01%でのセトリングが規定されています。このセトリングは、18 ビット・レベルでのセトリング・タイムとは大幅に異なることがあるため、ドライバを選択する前に確認する必要があります。

表 8. 推奨されるドライバ・アンプ<sup>1</sup>

| アンプ                     | 代表的アプリケーション           |

|-------------------------|-----------------------|

| ADA4941-1               | 超低雑音、低消費電力、単相から差動への変換 |

| ADA4841-1/<br>ADA4841-2 | 超低雑音、小型、低消費電力         |

| AD8021                  | 超低雑音、高周波              |

| AD8022                  | 低雑音、高周波               |

| OP184                   | 低消費電力、低雑音、低周波         |

| AD8655                  | 5 V 単一電源、低雑音          |

| AD8605,<br>AD8615       | 5 V 単一電源、低消費電力        |

<sup>1</sup> 最新の推奨ドライバについては、製品 Web ページの推奨製品リストを参照してください。

## 単相・差動変換ドライバ

シングルエンド・アナログ信号(バイポーラまたはユニポーラ)を使うアプリケーションの場合、ADA4941-1 シングルエンド/差動変換ドライバを使うと、差動入力をデバイスに入力することができます。図 29 にこの回路図を示します。

入力信号のレンジと AD コンバータの入力レンジ ( $V_{REF}$ ) 間の減衰比に応じて  $R1$  と  $R2$  を設定します。 $R1$ 、 $R2$ 、 $C_F$  は、望ましい入力インピーダンス、信号帯域幅、アンチエリアシング、およびノイズ量に依存して選択されます。たとえば、入力インピーダンスが  $4\text{ k}\Omega$  で電圧範囲が  $\pm 10\text{ V}$  の場合は、 $R2 = 1\text{ k}\Omega$ 、 $R1 = 4\text{ k}\Omega$  となります。

$R3$  と  $R4$  は、AD コンバータの IN-入力のコモンモード電圧を設定し、 $R5$  と  $R6$  は IN+入力のコモンモード電圧を設定します。コモンモード電圧が  $V_{REF}/2$  に近いことを確認してください。たとえば、 $\pm 10\text{ V}$  の範囲で、单電源動作の場合は、 $R3 = 8.45\text{ k}\Omega$ 、 $R4 = 11.8\text{ k}\Omega$ 、 $R5 = 10.5\text{ k}\Omega$ 、and  $R6 = 9.76\text{ k}\Omega$  となります。

図 29. シングルエンド/差動変換ドライバ

## リファレンス電圧入力

AD7989-1/AD7989-5 のリファレンス電圧入力 REF は動的入力インピーダンスを持っています。このため、REF 入力と GND 入力との間を効果的にデカップリングした低インピーダンス源から駆動する必要があります(レイアウトの節参照)。

REF を非常に小さいインピーダンス源で駆動する場合(たとえば、AD8031 または AD8605 を使用するリファレンス・バッファ)は、 $10\text{ }\mu\text{F}$  のセラミック・チップ・コンデンサ(X5R、0805 サイズ)でデカップリングを行えば最適な性能を得ることができます。

バッファなしでリファレンス電圧を使う場合は、デカップリング値は使用するリファレンスに依存します。たとえば低温度ドリフト ADR43x リファレンスを使用する場合は、 $22\text{ }\mu\text{F}$  のセラミック・チップ・コンデンサ(X5R、1206 サイズ)を使って最適な性能を得ることができます。

必要に応じて、 $2.2\text{ }\mu\text{F}$ までの小型なリファレンス・デカップリング・コンデンサ値を使うことができ、性能、特に DNL への影響は最小限に抑えることができます。

REF ピンと GND ピンの間に小さい値のセラミック・デカップリング・コンデンサ(100 nF など)を追加する必要はありません。

## 電源

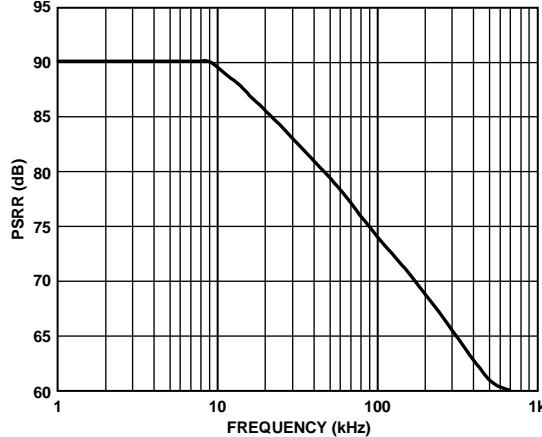

AD7989-1/AD7989-5 は、コア電源(VDD)とデジタル入力/出力インターフェース電源(VIO)の 2 種類の電源ピンを使っています。VIO は  $1.8\text{ V} \sim 5.5\text{ V}$  で動作するロジックとの直接インターフェースを可能にします。所要電源数を減らすため、VIO と VDD はひとつにまとめることができます。AD7989-1/AD7989-5 は VIO と VDD の間の電源シーケンスに依存しません。さらに、図 30 に示されるように広い周波数範囲で電源変動に対して安定です。

図 30. PSRR 対周波数

10232-026

AD7989-1/AD7989-5 は、各変換フェーズが終る度に自動的にパワーダウンします。

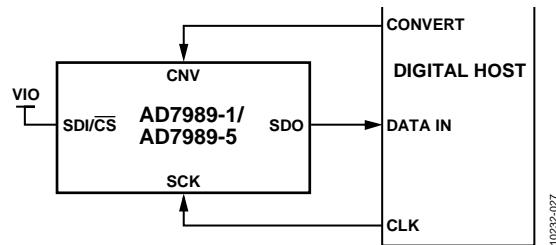

## デジタル・インターフェース

AD7989-1/AD7989-5 のピン数は少ないですが、シリアル・インターフェース・モードが柔軟性を提供します。

CS モードの場合、AD7989-1/AD7989-5 は SPI、QSPI、デジタル・ホスト、及び DSP と互換性があります。CNV 信号、SCK 信号、SDO 信号を使う 3 線式インターフェースは、配線数が少ないので、たとえば、絶縁アプリケーションに適しています。SDI/CS 信号、CNV 信号、SCK 信号、SDO 信号を使う 4 線式インターフェースを使用すると、変換を開始する CNV を読み出しタイミング(SDI)と無関係に使用できます。この機能は、低ジッタ・サンプリング・アプリケーションや同時サンプリング・アプリケーションに有用です。

AD7989-1/AD7989-5 をチェーン・モードで使うと、SDI 入力を使って、シフト・レジスタに似た 1 本のデータ・ライン上で複数の ADC をカスケード接続することができます。

デバイスがどのモードで動作するかは、CNV の立ち上がりエッジでの SDI/CS のレベルで決定されます。SDI/CS がハイ・レベルなら CS モードが選択され、SDI/CS がロー・レベルなら チェーン・モードが選択されます。SDI と CNV を接続して SDI のホールド時間を決めるときには、チェーン・モードが選択されます。ユーザーは、読み出し前に最大変換時間の経過を待たなければなりません。

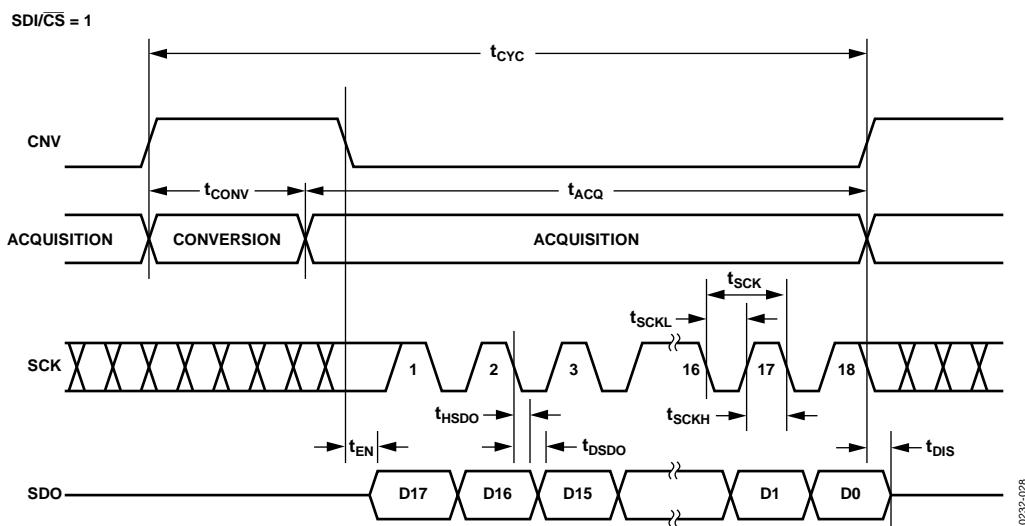

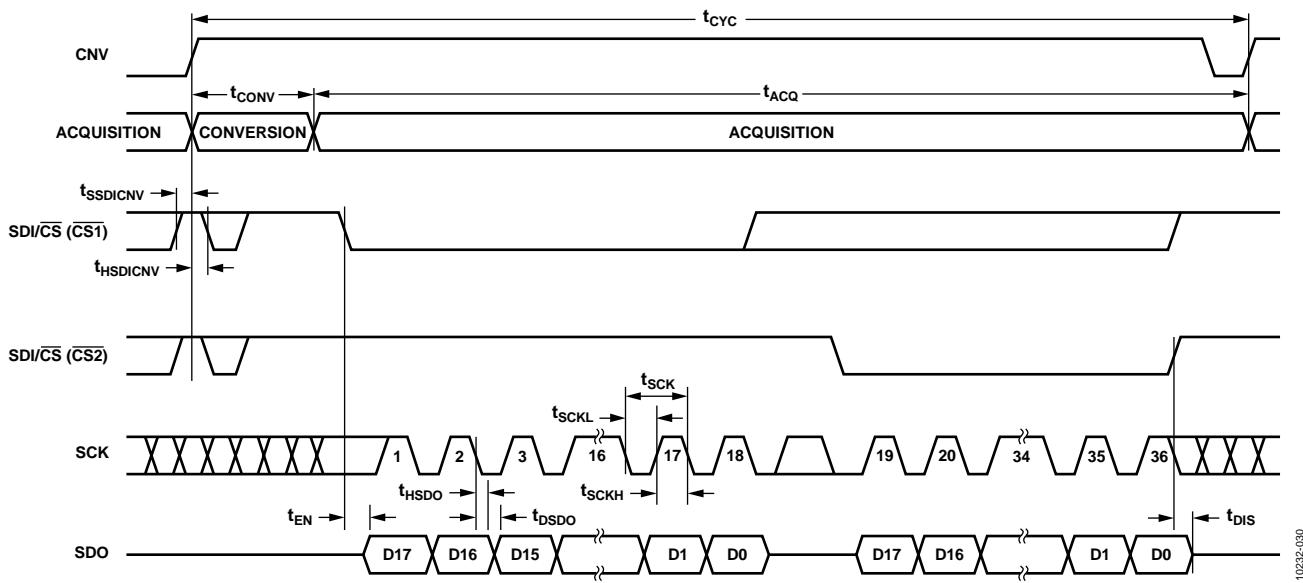

## CSモード、3線

このモードは、1個の AD7989-1/AD7989-5 を SPI 互換のデジタル・ホストに接続する際に使用されます。図 31 に接続図を、図 32 に対応するタイミングを、それぞれ示します。

VIO ヘプルアップされた SDI/CS では、CNV の立ち上がりエッジで変換が開始され、CSモードが選択され、SDO は高インピーダンスになります。変換が終了すると AD7989-1/AD7989-5 はアクイジション・フェーズになります。CNV

がロー・レベルになると、変換結果が MSB から SDO に出力されます。残りのデータ・ビットは、後に続く SCK の立ち下がりエッジで出力されます。SDO のデータは、SCK の両エッジで有効です。SCK の立ち上がりエッジを使ってデータを取込むことができますが、SCK の立ち下がりエッジを使うデジタル・ホストを使うと、ホールド・タイムが許容できる限り、高速な読み出しレートが可能になります。18番目の SCK 立ち下がりエッジの後、または CNV がハイ・レベルになったときのいずれか早い方で、SDO は高インピーダンスに戻ります。

図 31. CSモード、3線インターフェースの接続図 (SDH がハイ・レベル)

図 32. CS モード、3 線シリアル・インターフェースのタイミング図 (SDI がハイ・レベル)

**CSモード、4線**

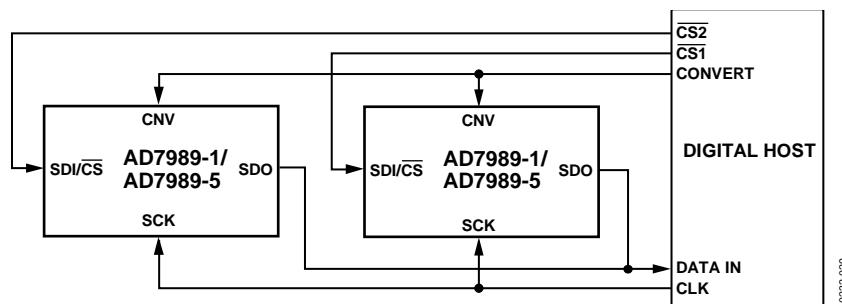

このモードは、複数の AD7989-1/AD7989-5 デバイスを SPI 互換のデジタル・ホストに接続する際に使用されます。

2つの AD7989-1/AD7989-5 を用いた場合の接続図を図 33 に、対応するタイミング図を図 34 に示します。

SDI がハイ・レベルの状態で、CNV の立ち上がりエッジで変換が開始され、SDI/CS モードが選択され、SDO は高インピーダンスになります。このモードでは、変換フェーズとそれに続くデータ読み出しの間、CNV がハイ・レベルに維持される必要があります。（SDI/CS と CNV をロー・レベルにすると、SDO がロー・レベルに駆動されます。最小変換時間の前に、SDI/CS を使ってアナログ・マルチプレクサのような他の SPI デバイスを選択することができますが、最小変換時間が経過する前に SDI/CS がハイ・レベルに戻り、可能な最大変換時間の間ハイ・レベル

を維持する必要があります。変換が完了すると、AD7989-1/AD7989-5 はアクイジョン・フェーズに入り、パワーダウン状態になります。SDI/CS 入力にロー・レベルを入力すると、各 ADC の変換結果を読み出すことができ、MSB が SDO へ出力されます。残りのデータ・ビットは、後続の SCK の立ち下がりエッジで出力されます。データは、SCK の両エッジで有効です。立ち上がりエッジを使ってデータを取込むことができますが、SCK の立ち下がりエッジを使うデジタル・ホストを使うと、ホールド・タイムが許容できる限り、高速な読み出しレートが可能になります。18 番目の SCK 立ち下がりエッジの後、または SDI/CS がハイ・レベルになったときのいずれか早い方で、SDO は高インピーダンスに戻り、もう一方の AD7989-1/AD7989-5 を読み出すことができるようになります。

図 33. CS モード、4 線インターフェースの接続図

図 34. CS モード、4 線シリアル・インターフェースのタイミング図

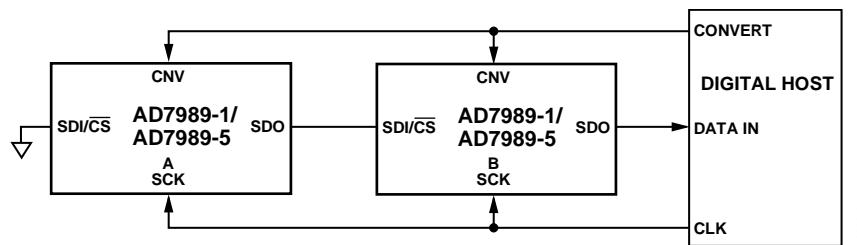

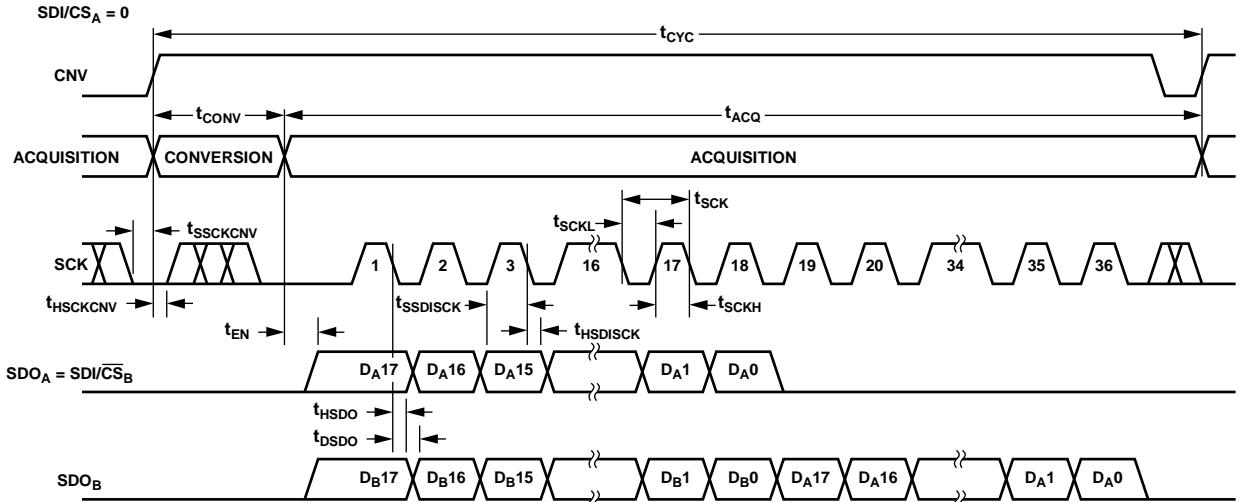

## チェーン・モード

このモードは、3線シリアル・1インターフェースに複数のAD7989-1/AD7989-5をディジチーチェーン接続するために使用されます。この機能は部品数と接続配線数の削減に役立ちます。たとえば、孤立した複数のコンバータを使用するアプリケーションまたはインターフェース能力が制限されているシステムではこの接続が使用されます。データのリードバックは、シフトレジスタをクロック駆動するのに似ています。

2つのAD7989-1/AD7989-5を用いた場合の接続図を図35に、対応するタイミング図を図36に示します。

SDI/CSとCNVをロー・レベルにすると、SDOがロー・レベルに駆動されます。SCKがロー・レベルのとき、CNVの立ち上がりエッジで変換が開始され、チェーン・モードが選択されます。このモードでは、変換フェーズとそれに続くデータ・リードバックの間、CNVがハイ・レベルに維持される必要があります。

変換が完了すると、SDOにMSBが出力され、AD7989-1/AD7989-5はアクイジョン・フェーズに入り、パワーダウン状態になります。内部シフトレジスタに保存されている残りのデータ・ビットは、後続のSCKの立ち下がりエッジで出力されます。各ADCで、SDIが内部シフトレジスタの入力に接続され、SCKの立ち下がりエッジでクロック駆動されます。チェーン内の各ADCはデータのMSBを先頭に出力し、N番目のADCをリードバックするためには $18 \times N$ 個のクロックが必要です。データは、SCKの両エッジで有効です。立ち上がりエッジを使ってデータを取り込むことができますが、SCKの立ち下がりエッジを使うデジタル・ホストを使うと、ホールド・タイムが許容できる限り、高速な読み出しレートが可能になり、かつチェーン内のAD7989-1/AD7989-5の数を増やすことができます。最大変換レートは、合計リードバック時間により低下することがあります。

図35. チェーン・モードの接続図

図36. チェーン・モード、シリアル・インターフェースのタイミング図

## アプリケーション情報

### BLACKFIN® DSP とのインターフェース

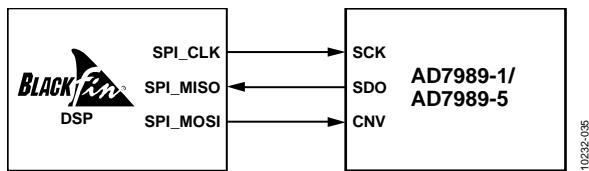

AD7989-1/AD7989-5 は、DSP の SPI、または SPORT と簡単に接続することができます。図 37 に示すように、SPI は標準の SPI インタフェースを用いて簡単に構成することができます。

図 37. 代表的な Blackfin SPI インタフェース接続

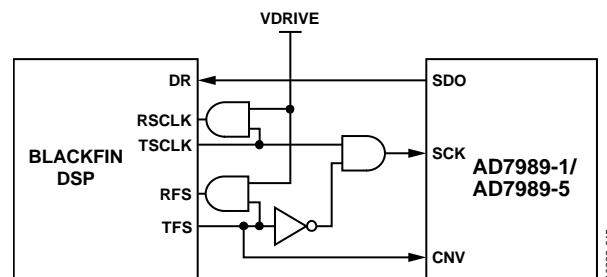

同様に、この ADC との接続に DSP の SPORT インタフェースを使用することもできます。SPORT インタフェースでは、ダイレクト・メモリ・アクセス (DMA) が使用でき、ハードウェア・カウンタが生成する低ジッタの CNV 信号を使用できるという利点があります。

SPORT と D7989-1/AD7989-5 を接続する際には、追加で外付けロジックが必要となることがあります。AD7989-1/AD7989-5 の評価ボードは、SDP ボードに実装されている Blackfin DSP

(ADSP-BF527) の SPORT インタフェースに直接接続することができます。SPORT インタフェースとの接続のために用いられる配線では、図 38 に示すようないくつかの外付けロジックを必要とします。ADC への SCK 入力は、CNV がハイ・レベルの場合はゲート・オフされ、データ変換を行いながら SCK ラインを静止状態に維持します。これによって変換結果の完全性が保証されます。この方法では、SCK 信号線に AND ゲートと NOT ゲートが 1 個ずつ用いられます。RSCLK 及び RFS 信号線上で用いられている他のロジック・ゲートは遅延を整合させることを目的としており、信号線の配線長が短いのであれば不要の場合もあります。

この回路は、この ADC と DSP の SPORT インタフェースとを接続するための一例であり、他の回路構成もあり得ます。

図 38. 評価ボードと Blackfin SPORT インタフェースの接続

### レイアウト

AD7989-1/AD7989-5 を実装するプリント回路ボードは、アナログ部とデジタル部を分離して、ボード内でそれぞれをまとめて配置するようにデザインする必要があります。AD7989-1/AD7989-5 では、アナログ信号を左側に、デジタル信号を右側に配置しているため、この作業が容易になります。

AD7989-1/AD7989-5 の下のグラウンド・プレーンがシールドして使われてない限り、ノイズがチップに混入するので、デバイスの真下をデジタル・ラインが通らないようにしてください。CNV やクロックのような高速なスイッチング信号は、アナログ信号パスの近くを通らないように配置してください。デジタル信号とアナログ信号の交差は回避する必要があります。

グラウンド・プレーンを少なくとも 1 層以上使用することが推奨されます。グラウンド・プレーンは、デジタル部とアナログ部に共通または分けて使うことができます。後者の場合、AD7989-1/AD7989-5 デバイスの下部に敷かれるグラウンド面を結合してください。

AD7989-1/AD7989-5 のリファレンス電圧入力 REF はダイナミックな入力インピーダンスを持っています。REF ピンと GND ピンの近くに、理想的には直接に、リファレンス電圧デカップリング・セラミック・コンデンサを、太い低インピーダンスのパターンを用いた最小寄生インダクタンスの配線で接続することによって REF をデカップリングしてください。

最後に、AD7989-1/AD7989-5 の電源 VDD と VIO は AD7989-1/AD7989-5 の近くに配置したセラミック・コンデンサ(一般に 100 nF)でデカップリングし、低インピーダンス・バスを提供する短く太いパターンで接続して、電源ライン上のグリッチの影響を軽減します。

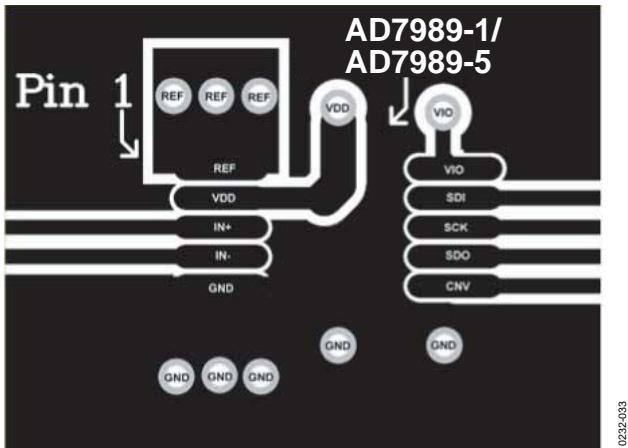

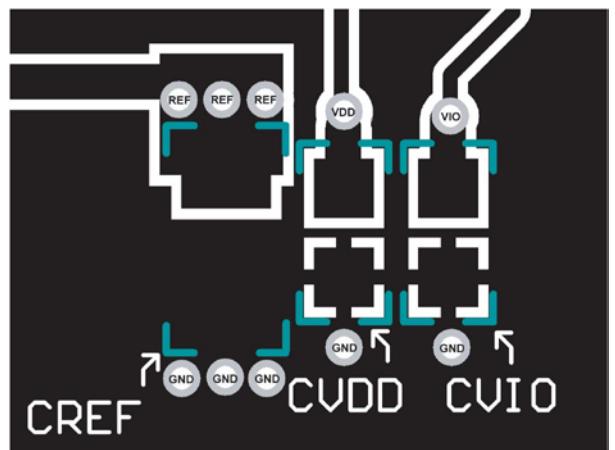

これらのルールに従ったレイアウトの例を図 39 と図 40 に示します。

### AD7989-1/AD7989-5 の性能評価

AD7989-1/AD7989-5 のその他の推奨レイアウトは、AD7989-1/AD7989-5 (EVAL-AD7689-5SDZ)用評価ボードのドキュメントにも記載してあります。評価ボードの梱包には、組み立て済みでテスト済みの評価ボード、ユーザーガイド、及び EVAL-SDP-CB1Z を介して PC からボードを制御するソフトウェアが添付されています。

図 39. AD7989-1/AD7989-5 の推奨レイアウト (表面レイヤー)

図 40. AD7989-1/AD7989-5 の推奨レイアウト (裏面レイヤー)

10232-034

## 外形寸法

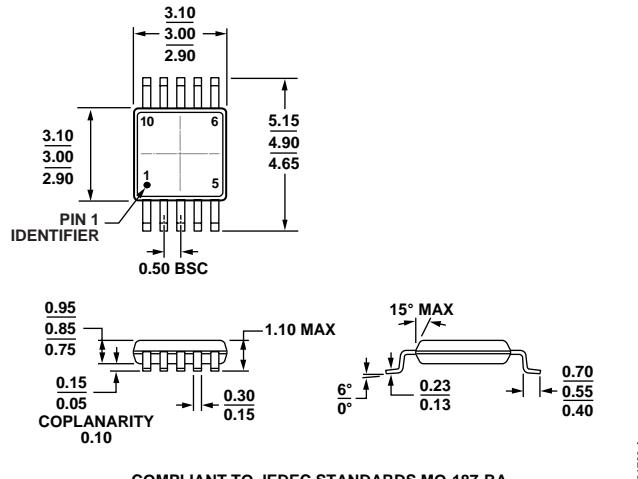

COMPLIANT TO JEDEC STANDARDS MO-187-BA

091709-A

図 41. 10 ピン・ミニ・スマール・アウトライン・パッケージ[MSOP]

(RM-10)

寸法表示 : mm

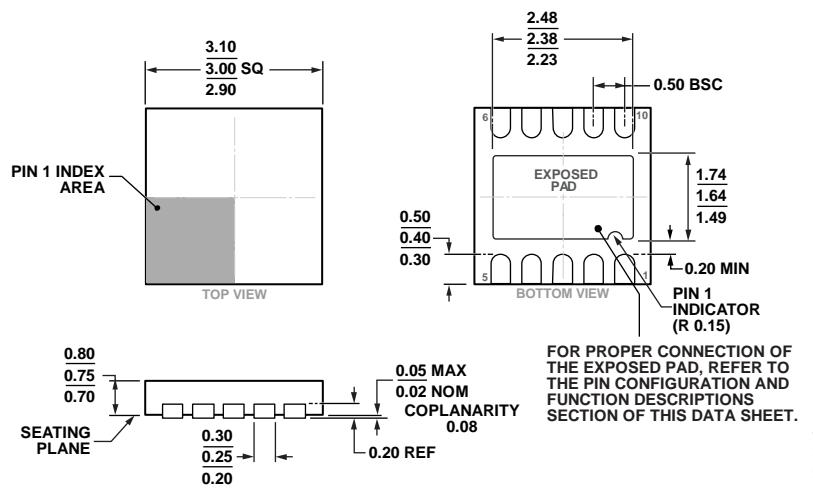

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

0245-2013-C

図 42. 10 ピン・リードフレーム・チップ・スケール・パッケージ[LFCSP\_WD]

3 mm×3 mm ボディ、超薄型デュアル・ピン(CP-10-9)

寸法表示 : mm

## オーダー・ガイド

| Model <sup>1, 2, 3</sup> | Temperature Range | Package Description                                                                                    | Package Option | Ordering Quantity | Branding |

|--------------------------|-------------------|--------------------------------------------------------------------------------------------------------|----------------|-------------------|----------|

| AD7989-1BRMZ             | -40°C to +85°C    | 10-Lead MSOP, Tube                                                                                     | RM-10          | 50                | C76      |

| AD7989-1BRMZ-RL7         | -40°C to +85°C    | 10-Lead MSOP, 7" Tape and Reel                                                                         | RM-10          | 1,000             | C76      |

| AD7989-1BCPZ-RL7         | -40°C to +85°C    | 10-Lead LFCSP_WD, 7" Tape and Reel                                                                     | CP-10-9        | 1,500             | C80      |

| AD7989-1BCPZ-R2          | -40°C to +85°C    | 10-Lead LFCSP_WD                                                                                       | CP-10-9        | 250               | C80      |

| AD7989-5BRMZ             | -40°C to +85°C    | 10-Lead MSOP, Tube                                                                                     | RM-10          | 50                | C7N      |

| AD7989-5BRMZ-RL7         | -40°C to +85°C    | 10-Lead MSOP, 7" Tape and Reel                                                                         | RM-10          | 1,000             | C7N      |

| AD7989-5BCPZ-RL7         | -40°C to +85°C    | 10-Lead LFCSP_WD, 7" Tape and Reel                                                                     | CP-10-9        | 1,500             | C7Y      |

| AD7989-5BCPZ-R2          | -40°C to +85°C    | 10-Lead LFCSP_WD                                                                                       | CP-10-9        | 250               | C7Y      |

| EVAL-AD7989-5SDZ         |                   | Evaluation Board with AD7989-5<br>Populated; Use for Evaluation of Both<br>AD7989-1 and AD7989-5       |                |                   |          |

| EVAL-SDP-CB1Z            |                   | System Demonstration Board, Used as a<br>Controller Board for Data Transfer via USB<br>Interface to PC |                |                   |          |

<sup>1</sup> Z = RoHS 準拠製品<sup>2</sup> EVAL-AD7989-5SDZ ボードは単独の評価ボードとして、または評価/デモ目的の EVAL-SDP-CB1Z と組み合わせて、使用することができます。<sup>3</sup> EVAL-SDP-CB1Z ボードを使うと、PC からの制御と SD サフィックスが付くすべてのアナログ・デバイセズ社評価ボードとの通信が可能です。

メモ