### 特長

4つの80MSPS広帯域入力 (14リニア・ビット+3 RSSI)

4つの実数入力ポート/2つの複素数入力ポート

4つの広帯域チャンネル (UMTSまたはcdma2000×1) または8つのGSM/EDGE、IS136チャンネルを処理

8個の独立したデジタル・レシーバをシングル・パッケージに内蔵

4つの16ビット・パラレル出力ポートと、4つの8ビット・リンク・ポート

4つのレンジ96dBでプログラマブルなデジタルAGCループ

非整数のデシメーション・レート用のデジタル・リサンプリング

プログラマブルなデシメーションFIRフィルタ

4つのインターポレーション・ハーフバンド・フィルタ

マルチキャリアおよびフェーズド・アレイの柔軟な制御

レベル・インジケータによる外部ゲイン・レンジングおよびクリップ防止用のプログラマブルな減衰器制御

I/O: 3.3V、CMOSコア: 2.5V

ユーザー設定可能な内蔵セルフ・テスト (BIST) 機能

### アプリケーション

マルチキャリア、マルチモード・デジタル・レシーバ

GSM、IS136、EDGE、PHS、IS95、UMTS、cdma2000

マイクロ/ピコ・セル・システム、ソフトウェア無線

ワイヤレス・ローカル・ループ

スマート・アンテナ・システム

屋内無線電話

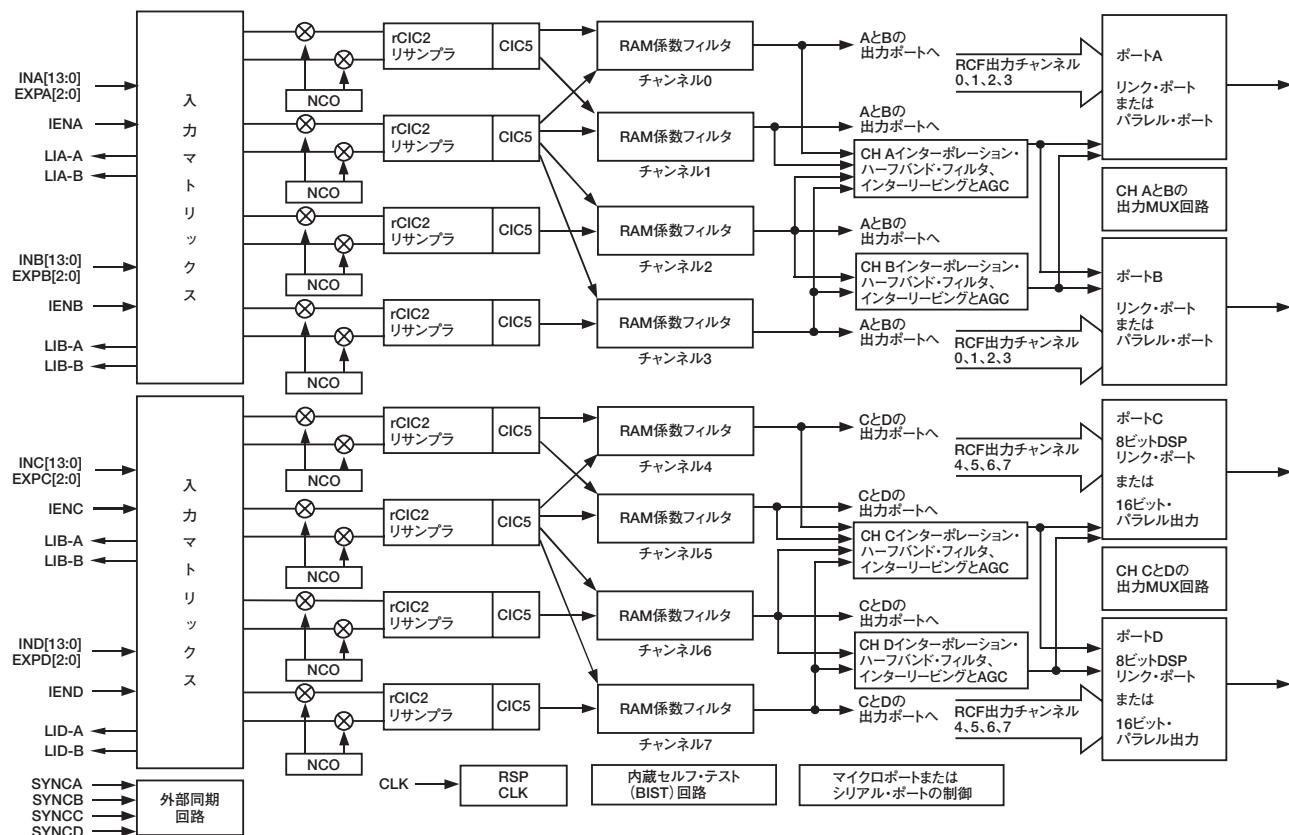

### 機能ブロック図

# AD6635

## 概要

AD6635は、4つまでのWCDMAチャンネルを処理できるマルチモード、8チャンネルのデジタル受信信号プロセッサ (RSP) です。各チャンネルは、周波数変換器、2つのCICデシメーション・フィルタ、プログラマブルな係数デシメーション・フィルタの4つの信号処理エレメントをカスケード接続することによって構成されています。各入力ポートには、広いダイナミックレンジに対応したり、ゲイン・レンジング・コンバータを使用する場合に備えて、入力レベルのスレッショールド検出回路があります。クワッド16ビット・パラレル出力ポートは、高データ・レートのWBCDMAアプリケーションに使用できます。内蔵のインターポレーション・ハーフバンド・フィルタを使用すれば、出力レートをさらに高くすることもできます。さらに、狭いビット幅を使用する広いダイナミックレンジに対応するために、各出力ポートにはデジタルAGCがあります。AGCは、そのモードに応じて、信号レベルまたはクリッピング・レベルを維持できます。リンク・ポート出力を利用すれば、アナログ・デバイセズのTigerSHARC DSPコアへのグリースレスなインターフェースが可能です。

AD6635は、アナログ・デバイセズSoftCellマルチキャリア・トランシーバのチップセットを構成するものであり、当社の高速サンプル・レート、IFサンプリングADCファミリー (AD9238/AD6645 12/14ビット) と互換性をもつように設計されています。SoftCellレシーバには、キャリアの全スペクトルをデジタル化し、同調およびチャンネル選択の対象となるキャリアをデジタル的に抽出する機能を備えたデジタル・レシーバが含まれています。このアーキテクチャにより、ワイヤレス基

地局アプリケーションにおいて、不要な無線通信を低減することができます。

ダイナミックレンジの広いデシメーション・フィルタにより、広範囲のデシメーション・レートが得られます。RAMベースのアーキテクチャであることから、マルチモードのアプリケーション用に簡単に設定を変更することができます。

デシメーション・フィルタは、対象チャンネルの不要な信号やノイズを取り除きます。対象チャンネルの使用する帯域幅が入力信号より狭い場合、このような帯域外ノイズの除去は「ゲイン処理」と呼ばれます。大きなデシメーション係数を使用すると、このゲイン処理によって、ADCのSNRを30dB以上向上することができます。さらに、プログラマブルなRAM係数フィルタにより、コスト効果の高い単一フィルタで、アンチエイリアス処理、整合フィルタ処理、スタティック等化の機能をまとめて実現することができます。特にWCDMAやcdma2000など、さまざまなアプリケーションで出力にインターポレーション・ハーフバンド・フィルタを使用することにより、出力レートがチップ・レートの2~4倍まで向上します。また、AD6635には、独立した自動ゲイン制御 (AGC) ループが4つ装備され、RAKEレシーバへの直接インターフェースとなります。

AD6635は、AD664x、AD923x、AD943x、AD922xファミリーのデータ・コンバータなど、標準的なADCコンバータに対して互換性があります。AD6600ダイバーシティADCとの互換性もあるので、AD6600 ADCを使用する既存システムの設計に取り入れることも可能です。

## 目次

|                               |    |

|-------------------------------|----|

| 特長                            | 1  |

| アプリケーション                      | 1  |

| 概要                            | 2  |

| アーキテクチャ                       | 5  |

| 推奨動作条件                        | 7  |

| 電気的特性                         | 7  |

| 一般的なタイミング特性                   | 8  |

| マイクロプロセッサ・ポートのタイミング特性         | 10 |

| 絶対最大定格                        | 11 |

| オーダー・ガイド                      | 11 |

| ピン配置                          | 12 |

| ピン配置（ピンアウト）                   | 13 |

| ピン機能の説明                       | 14 |

| タイミング図                        | 16 |

| 入力データ・ポート                     | 23 |

| 入力データ・フォーマット                  | 23 |

| 入力タイミング                       | 23 |

| 入力イネーブル制御                     | 23 |

| ゲイン・スイッチング                    | 23 |

| 入力データのスケーリング                  | 24 |

| 固定小数点ADCによるスケーリング             | 24 |

| 浮動小数点またはゲイン・レンジングADCによるスケーリング | 25 |

| 数値制御発振器                       | 26 |

| 周波数変換                         | 26 |

| NCO周波数ホールドオフ・レジスタ             | 26 |

| 位相オフセット                       | 26 |

| NCOコントロール・レジスタ                | 26 |

| バイパス                          | 26 |

| 位相ディザ                         | 26 |

| 振幅ディザ                         | 26 |

| ホップ時の位相アキュムレータのクリア            | 26 |

| 入力イネーブル制御                     | 27 |

| モード00：IENのローレベルでデータをブランク      | 27 |

| モード01：IENのハイレベルでクロック入力        | 27 |

| モード10：IENの立ち上がり変化でクロック入力      | 27 |

| モード11：IENの立ち下がり変化でクロック入力      | 27 |

| WB入力セレクト                      | 27 |

| 同期セレクト                        | 27 |

| 2次rCICフィルタ                    | 27 |

| rCIC2除去比                      | 28 |

| 例計算                           | 28 |

| デシメーション・レジスタとインターポレーション・レジスタ  | 29 |

| rCIC2スケール                     | 29 |

| 5次CICフィルタ                     | 29 |

| CIC5除去比                       | 29 |

| RAM係数フィルタ                     | 30 |

| RCFデシメーション・レジスタ               | 30 |

| RCFデシメーション位相                  | 30 |

| RCFフィルタ長                      | 30 |

| RCF出力スケール係数とコントロール・レジスタ       | 30 |

| インターポレーション・ハーフバンド・フィルタ        | 31 |

| 自動ゲイン制御                       | 32 |

| AGCループ                        | 32 |

| 目標信号レベル・モード                   | 32 |

| 目標クリップ・レベル・モード                | 34 |

| 同期                            | 34 |

|                                          |    |

|------------------------------------------|----|

| ユーザー設定可能な内蔵セルフ・テスト（BIST）                 | 35 |

| RAM BIST                                 | 35 |

| チャンネルBIST                                | 35 |

| チップの同期化                                  | 35 |

| スタート                                     | 36 |

| 非同期スタート                                  | 36 |

| ソフト同期によるスタート                             | 36 |

| SYNCピンによるスタート                            | 36 |

| ホップ                                      | 36 |

| ホップなしで周波数を設定                             | 36 |

| ソフト同期によるホップ                              | 37 |

| SYNCピンによるホップ                             | 37 |

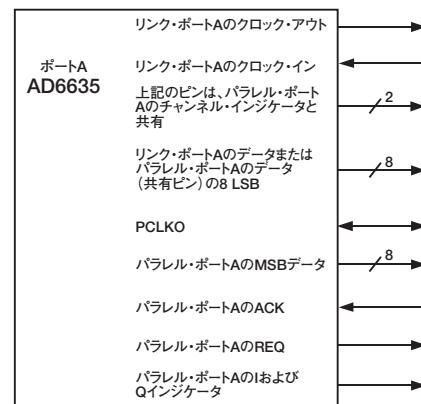

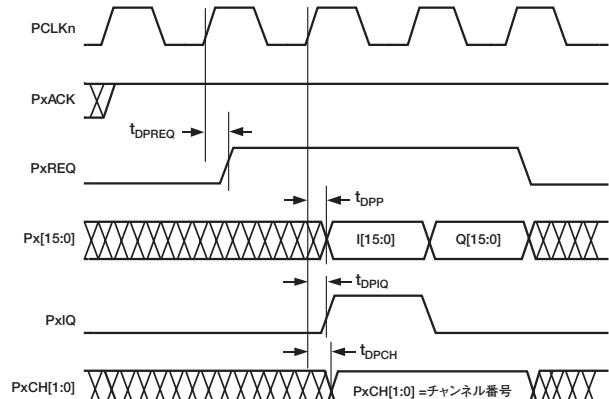

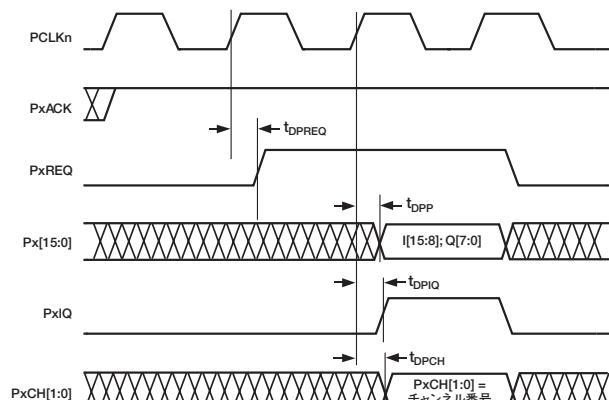

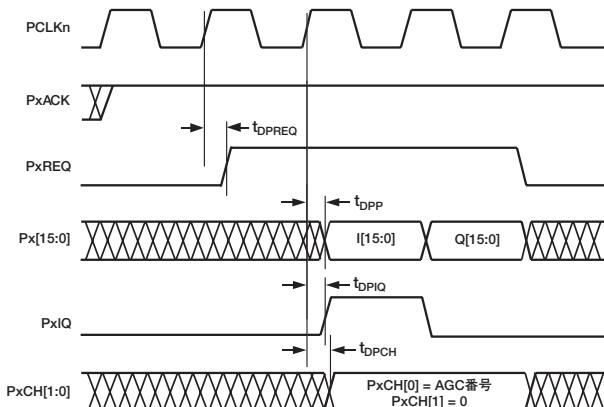

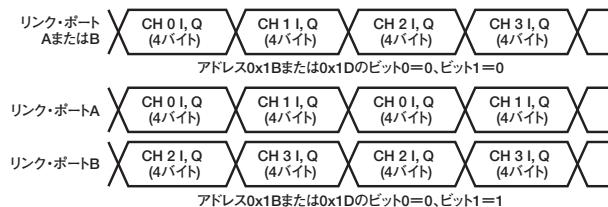

| パラレル出力ポート                                | 37 |

| チャンネル・モード                                | 37 |

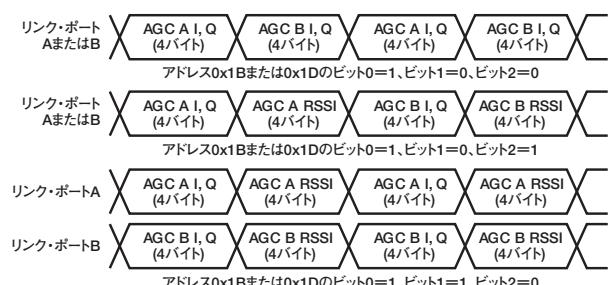

| AGCモード                                   | 38 |

| マスター／スレーブPCLKnモード                        | 39 |

| パラレル・ポートのピン機能                            | 39 |

| リンク・ポート                                  | 39 |

| リンク・ポートのデータ・フォーマット                       | 40 |

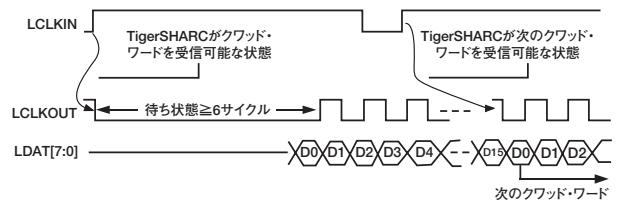

| リンク・ポートのタイミング                            | 40 |

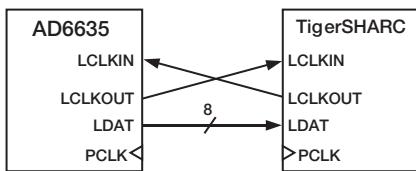

| TigerSHARCの設定                            | 41 |

| チャンネル・メモリ・マップ                            | 41 |

| 0x00～0x7F：係数メモリ（CMEM）                    | 42 |

| 0x80：チャンネル・スリープ・レジスタ                     | 42 |

| 0x81：Soft_SYNCレジスタ                       | 42 |

| 0x82：Pin_SYNCレジスタ                        | 42 |

| 0x83：スタート・ホールドオフ・カウンタ                    | 42 |

| 0x84：NCO周波数ホールドオフ・カウンタ                   | 42 |

| 0x85：NCO周波数レジスタ0                         | 42 |

| 0x86：NCO周波数レジスタ1                         | 42 |

| 0x87：NCO位相オフセット・レジスタ                     | 42 |

| 0x88：NCOコントロール・レジスタ                      | 42 |

| 0x90：rCIC2デシメーション-1 ( $M_{rCIC2}-1$ )    | 44 |

| 0x91：rCIC2インターポレーション-1 ( $L_{rCIC2}-1$ ) | 44 |

| 0x92：rCIC2スケール                           | 44 |

| 0x93：                                    | 44 |

| 0x94：CIC5デシメーション-1 ( $M_{CIC5}-1$ )      | 44 |

| 0x95：CIC5スケール                            | 44 |

| 0x96：                                    | 44 |

| 0xA0：RCFデシメーション-1 ( $M_{RCF}-1$ )        | 44 |

| 0xA1：RCFデシメーション位相 ( $P_{RCF}$ )          | 44 |

| 0xA2：RCFタップ数-1 ( $N_{TAPS}-1$ )          | 44 |

| 0xA3：RCF係数オフセット ( $CO_{RCF}$ )           | 44 |

| 0xA4：RCFコントロール・レジスタ                      | 45 |

| 0xA5：I用BISTレジスタ                          | 45 |

| 0xA6：Q用BISTレジスタ                          | 45 |

| 0xA7：BISTコントロール・レジスタ                     | 45 |

| 0xA8：RAM BISTコントロール・レジスタ                 | 45 |

| 0xA9：出力コントロール・レジスタ                       | 45 |

| 入力ポートコントロール・レジスタのメモリ・マップ                 | 46 |

| 入力ポート・コントロール・レジスタ                        | 46 |

| 0x00：下限レッシュホールドA                         | 46 |

| 0x01：上限レッシュホールドA                         | 46 |

| 0x02：ドウェル・タイムA                           | 46 |

| 0x03：ゲイン・レンジAコントロール・レジスタ                 | 46 |

| 0x04：下限レッシュホールドB                         | 47 |

| 0x05：上限レッシュホールドB                         | 47 |

| 0x06：ドウェル・タイムB                           | 47 |

| 0x07：ゲイン・レンジBコントロール・レジスタ                 | 47 |

# AD6635

## 目次（続き）

---

|                           |    |                          |    |

|---------------------------|----|--------------------------|----|

| 出力ポート・コントロール・レジスタのメモリ・マップ | 47 | マイクロポートの制御               | 53 |

| 0x08：ポートAコントロール・レジスタ      | 50 | 外部メモリ・マップ                | 53 |

| 0x09：ポートBコントロール・レジスタ      | 50 | アクセス・コントロール・レジスタ (ACR)   | 54 |

| 0x0A：AGC Aコントロール・レジスタ     | 50 | チャネル・アドレス・レジスタ (CAR)     | 54 |

| 0x0B：AGC Aホールドオフ・カウンタ     | 50 | SOFT_SYNCコントロール・レジスタ     | 55 |

| 0x0C：AGC A目標レベル           | 50 | PIN_SYNCコントロール・レジスタ      | 55 |

| 0x0D：AGC A信号ゲイン           | 51 | スリープ・コントロール・レジスタ         | 55 |

| 0x0E：AGC Aループ・ゲイン         | 51 | データ・アドレス・レジスタ            | 55 |

| 0x0F：AGC Aポール位置           | 51 | 書き込みシーケンス                | 55 |

| 0x10：AGC A平均サンプル          | 51 | 読み出しシーケンス                | 56 |

| 0x11：AGC A更新デシメーション       | 51 | 読み出し／書き込みチェーン            | 56 |

| 0x12：AGC Bコントロール・レジスタ     | 51 | インテル非マルチプレックス・モード (INM)  | 56 |

| 0x13：AGC Bホールドオフ・カウンタ     | 51 | モトローラ非マルチプレックス・モード (MNM) | 56 |

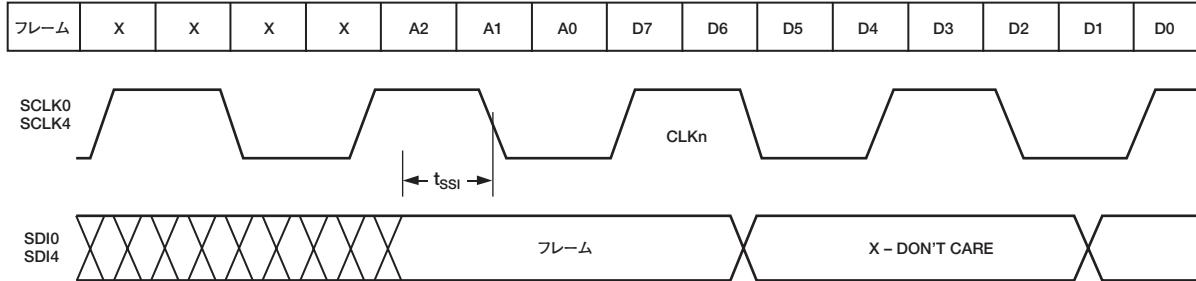

| 0x14：AGC B目標レベル           | 51 | シリアル・ポートの制御              | 56 |

| 0x15：AGC B信号ゲイン           | 51 | シリアル・ポートのタイミング仕様         | 56 |

| 0x16：AGC Bループ・ゲイン         | 51 | SDI0、SDI4                | 56 |

| 0x17：AGC Bポール位置           | 52 | SCLK0、SCLK4              | 57 |

| 0x18：AGC B平均サンプル          | 52 | 内部書き込みアクセス               | 58 |

| 0x19：AGC B更新デシメーション       | 52 | 書き込み擬似コード                | 58 |

| 0x1A：パラレル・ポート制御A          | 52 | 内部読み出しアクセス               | 58 |

| 0x1B：リンク・ポート制御A           | 52 | 読み出し擬似コード                | 58 |

| 0x1C：パラレル・ポート制御B          | 52 | 外形寸法                     | 59 |

| 0x1D：リンク・ポート制御B           | 53 |                          |    |

| 0x1E：ポート・クロック制御           | 53 |                          |    |

## アーキテクチャ

AD6635には、4つの信号処理段があります。すなわち、周波数変換器、リサンプリング・カスケード積分型2次樹形FIRフィルタ (rCIC2)、カスケード積分型5次樹形FIRフィルタ (CIC5)、RAM係数FIRフィルタ (RCF) です。チップへの入／出力データをクロックさせるための複数のモードがサポートされており、さまざまなデジタル化機器に幅広く接続できる柔軟性があります。プログラミングと制御は、シリアル・インターフェースやマイクロプロセッサのインターフェースを介して実行されます。

周波数変換は、32ビットの複素数値制御発振器 (NCO) を用いて行われます。この段に入ってくる実数データは、同相成分 (I) と直交成分 (Q) に分けられます。ここでは、入力信号をデジタル中間周波数 (IF) からデジタル・ベースバンドに変換します。位相および振幅のディザをチップ上で有効にすると、NCOのスブリアス性能が向上します。また位相オフセット・ワードを利用すれば、複数のAD6635間またはチャンネル間で既知の位相関係を確立することができます。

周波数変換の後には、固定係数による高速リサンプリング・カスケード積分型2次樹形 (rCIC2) フィルタが続きます。このフィルタは、デシメーション・レジスタとインターポレーション・レジスタ間の比率に基づいてサンプル・レートを低減します。

次の段は、カスケード積分型5次樹形 (CIC5) フィルタで、その応答はデシメーション・レートによって決定されます。このフィルタの目的は、最終フィルタ段 (RCF) へのデータ・レートを低減して、同じRCF帯域幅に対して計算できるタップ数を増やすことです。CIC5フィルタは、rCIC2よりも優れたアンチエイリアシング (フィルタリング) 機能を備えています。この点から、このフィルタを使用するのは、リサンプリングが必要な場合、またはCIC5単独では必要なデシメーションに対処できない場合だけにすることをお勧めします。

最終段は、プログラマブルな20ビット係数と、1～256（実用的には1～32）のプログラマブルなデシメーション・レートを備えた、積和FIRフィルタです。RAM係数FIRフィルタ（機能ブロック図のRCF）は、最大160タップを処理できます。

RCFから出力されたデータは、出力ポートまたはインターリーバに送信できます。このセクションでは、複数のチャンネルからのデータをインターリーブできます。複数のチャンネルを使用して1つのキャリアの処理ができ、データをインターリーブして出力セクションに戻します。このように、1つのキャリアに対して複数のチャンネルの処理パワーが使用できます。

インターリーブされたデータは、固定係数のインターポレーション・ハーフバンド・フィルタに送信され、ここで係数2でインターポレーションされます。ハーフバンド・フィルタの後に続くデジタルAGCには、96.3dBのゲイン範囲があります。このAGCセクションは、その応答に関して完全にプログラマブルです。機能ブロック図に示すように、AD6635には4つのハーフバンド・フィルタとAGCがあります。ハーフバンド・フィルタとAGCの各セクションは、個別にバイパスできます。

AD6635の全体的なフィルタ応答は、すべてのデシメーション段とインターポレーション段を合成したものになります。後に続く各フィルタ段は、より狭い遷移帯域幅で応答することができるですが、出力を計算するために、より多くのCLKサイクルが必要となります。最初のフィルタ段で多数のデシメーションを実行すれば、全体の電力消費を最大限低減することができます。独立したそれぞれのフィルタ段は、独特な方法でバイパスできます。チップからのデータは、高速パラレル・ポートまたはTigerSHARC互換のリンク・ポートを介して、DSPに接続します。各出力でパラレル・ポートまたはリンク・ポートを使用するように個別に設定できます。

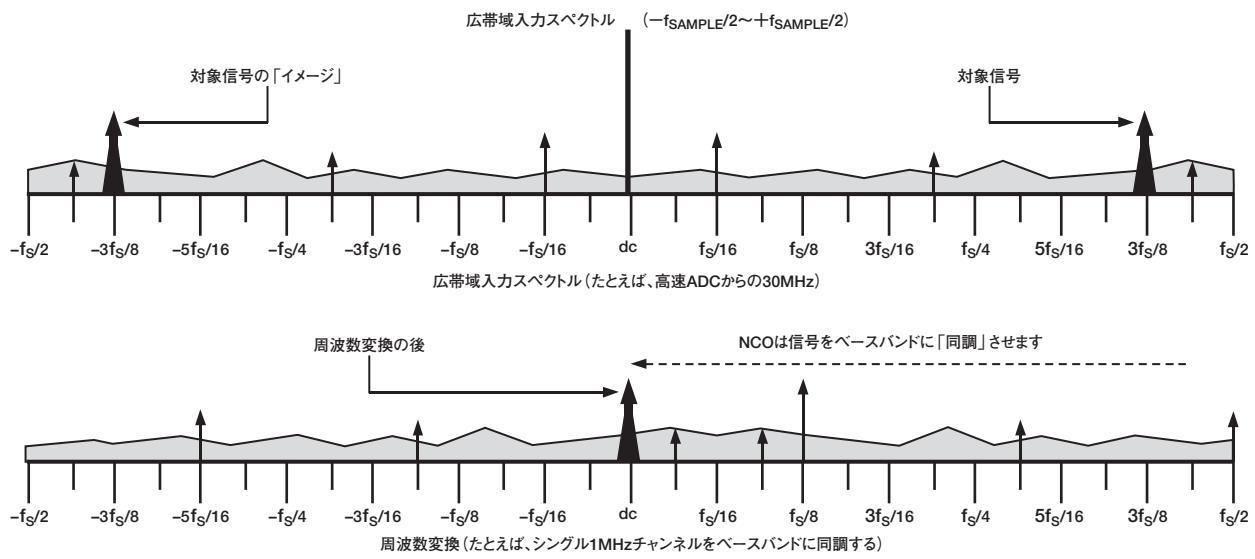

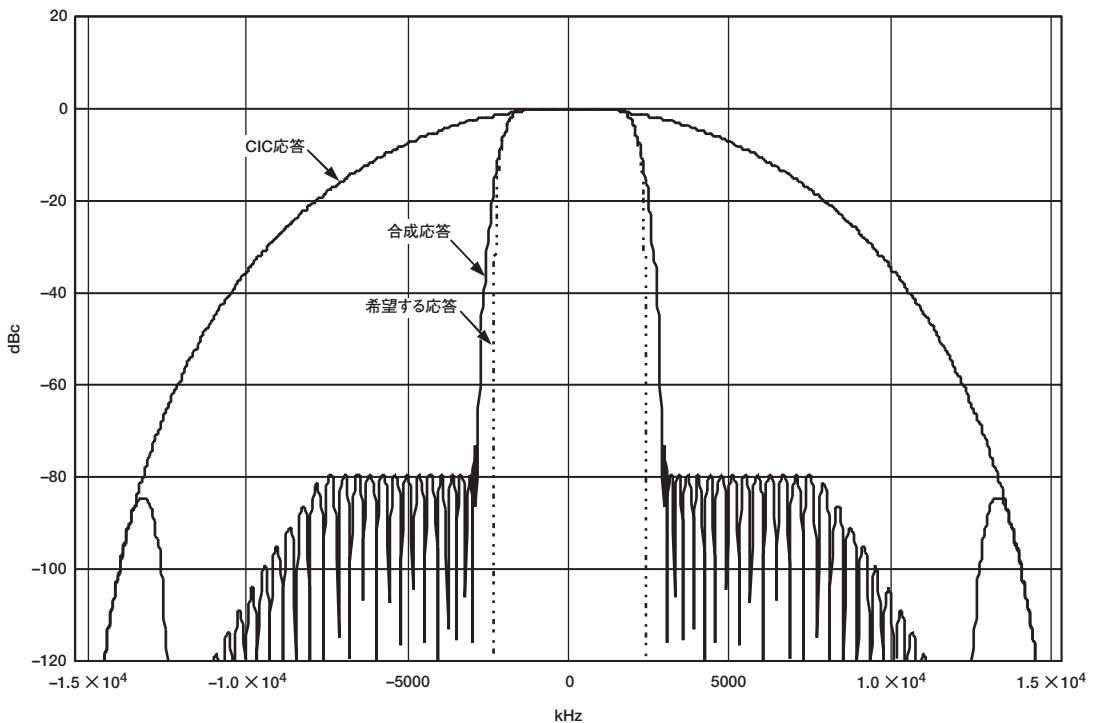

図1には、広い入力スペクトルから1つのチャンネルを選択してフィルタするためのAD6635 NCOの同調機能を示します。周波数変換器で、希望するキャリアをベースバンドに「同調」させます。図2に、サンプル・フィルタ設定に対するrCIC2、CIC5、RCFフィルタの合成フィルタ応答を示します。

# AD6635

図1. 広帯域入力スペクトルのAD6635周波数変換

図2. サンプル・フィルタ設定に対するrCIC2、CIC5、RCFの合成フィルタ応答

# 仕様

## 推奨動作条件

| パラメータ                | 温度 | テスト・レベル | AD6635BB |     |      | 単位 |

|----------------------|----|---------|----------|-----|------|----|

|                      |    |         | Min      | Typ | Max  |    |

| VDD                  |    | IV      | 2.25     | 2.5 | 2.75 | V  |

| VDDIO                |    | IV      | 3.0      | 3.3 | 3.6  | V  |

| T <sub>AMBIENT</sub> |    | IV      | -40      | +25 | +85  | ℃  |

## 電気的特性

| パラメータ (条件)                                        | 温度   | テスト・レベル | Min  | Typ       | Max  | 単位 |

|---------------------------------------------------|------|---------|------|-----------|------|----|

| ロジック入力 (5V対応)                                     |      |         |      |           |      |    |

| ロジック互換性                                           | 全範囲  | IV      |      | 3.3V CMOS |      |    |

| ロジック “1” 電圧                                       | 全範囲  | IV      | 2.0  |           | 5.0  | V  |

| ロジック “0” 電圧                                       | 全範囲  | IV      | -0.3 |           | +0.8 | V  |

| ロジック “1” 電流                                       | 全範囲  | IV      |      | 1         | 10   | μA |

| ロジック “0” 電流                                       | 全範囲  | IV      |      | 1         | 10   | μA |

| ロジック “1” 電流 (プルダウン付き入力)                           | 全範囲  | IV      |      |           |      |    |

| ロジック “0” 電流 (プルアップ付き入力)                           | 全範囲  | IV      |      |           |      |    |

| 入力容量                                              | 25°C | V       |      | 4         |      | pF |

| ロジック出力                                            |      |         |      |           |      |    |

| ロジック互換性                                           | 全範囲  | IV      |      |           |      |    |

| ロジック “1” 電圧 (I <sub>OH</sub> =0.25mA)             | 全範囲  | IV      | 2.4  | VDD-0.2   |      | V  |

| ロジック “0” 電圧 (I <sub>OL</sub> =0.25mA)             | 全範囲  | IV      | 0.2  |           | 0.4  | V  |

| IDD電源電流                                           |      |         |      |           |      |    |

| CLK=80MHz (VDD=2.75V、VDDIO=3.6V)                  | 全範囲  | IV      |      |           |      |    |

| I <sub>VDD</sub>                                  |      |         |      |           | 880  | mA |

| I <sub>VDDIO</sub>                                |      |         |      |           | 150  | mA |

| CLK=GSMの例 (65MSPS、VDD=2.5V、VDDIO=3.3V、4チャンネル)     | 25°C | V       |      |           |      |    |

| I <sub>VDD</sub>                                  |      |         |      |           | 485  | mA |

| I <sub>VDDIO</sub>                                |      |         |      |           | 60   | mA |

| CLK=WCDMAの例 (76.8MSPS、VDD=2.5V、VDDIO=3.3V、2チャンネル) | 25°C | V       |      |           |      |    |

| I <sub>VDD</sub>                                  |      |         |      |           | 830  | mA |

| I <sub>VDDIO</sub>                                |      |         |      |           | 120  | mA |

| 消費電力                                              |      |         |      |           |      |    |

| CLK=80MHz                                         | 全範囲  | IV      |      |           | 2.8  | W  |

| CLK=65MHz GSM/EDGEの例                              |      | V       |      | 1.4       |      | mW |

| CLK=76.8MHz WCDMAの例                               |      | V       |      | 2.5       |      | W  |

| CLK=78.64MHz cdma2000の例                           |      | V       |      | 2.3       |      | W  |

| すべてのチャンネルがスリープ・モード                                | 全範囲  | IV      |      | 570       |      | μW |

仕様は予告なく変更されることがあります。

# AD6635

## 仕様 (続き)

### 一般的なタイミング特性<sup>1, 2</sup>

| パラメータ (条件)                                                              | 温度  | テスト・レベル | AD6635BB |                        |      |    |

|-------------------------------------------------------------------------|-----|---------|----------|------------------------|------|----|

|                                                                         |     |         | Min      | Typ                    | Max  | 単位 |

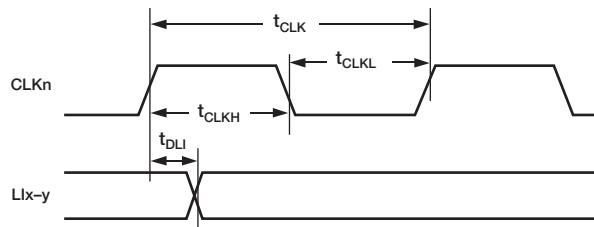

| <b>CLKnのタイミング条件</b>                                                     |     |         |          |                        |      |    |

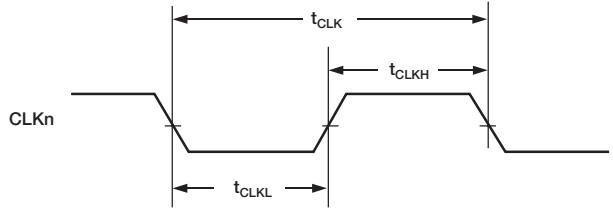

| $t_{CLK}$ CLKnの周期                                                       | 全範囲 | I       | 12.5     |                        |      | ns |

| $t_{CLKL}$ CLKnのローレベル幅                                                  | 全範囲 | IV      | 5.6      | $0.5 \times t_{CLK}$   |      | ns |

| $t_{CLKH}$ CLKnのハイレベル幅                                                  | 全範囲 | IV      | 5.6      | $0.5 \times t_{CLK}$   |      | ns |

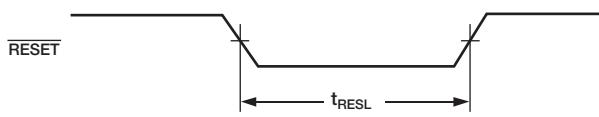

| <b>RESETのタイミング条件</b>                                                    |     |         |          |                        |      |    |

| $t_{RESL}$ RESETローレベル幅                                                  | 全範囲 | I       | 30.0     |                        |      | ns |

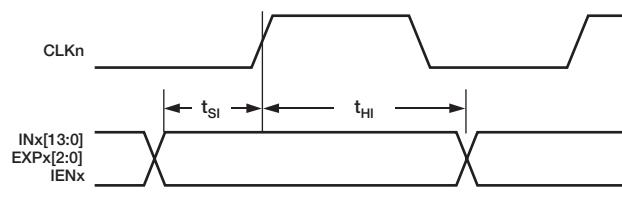

| <b>入力広帯域データのタイミング条件</b>                                                 |     |         |          |                        |      |    |

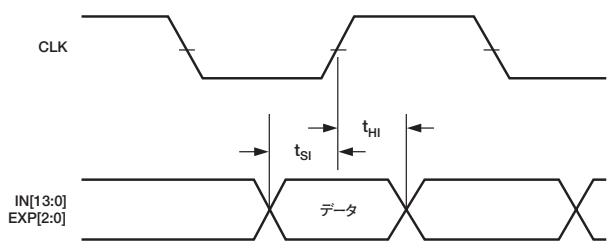

| $t_{SI}$ 入力から $\uparrow$ CLKnまでのセットアップ・タイム                              | 全範囲 | IV      | 2.0      |                        |      | ns |

| $t_{HI}$ 入力から $\uparrow$ CLKnまでのホールド・タイム                                | 全範囲 | IV      | 1.0      |                        |      | ns |

| <b>レベル・インジケータの出力スイッチング特性</b>                                            |     |         |          |                        |      |    |

| $t_{DLI}$ $\uparrow$ CLKnから LIx-yまでの出力遅延時間                              | 全範囲 | IV      | 3.3      |                        | 10.0 | ns |

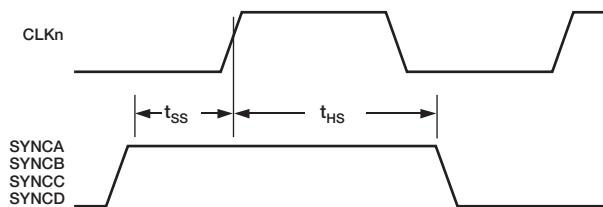

| <b>SYNCのタイミング条件</b>                                                     |     |         |          |                        |      |    |

| $t_{SS}$ SYNC (A, B, C, D) から $\uparrow$ CLKnまでのセットアップ・タイム              | 全範囲 | IV      | 2.0      |                        |      | ns |

| $t_{HS}$ SYNC (A, B, C, D) から $\uparrow$ CLKnまでのホールド・タイム                | 全範囲 | IV      | 1.0      |                        |      | ns |

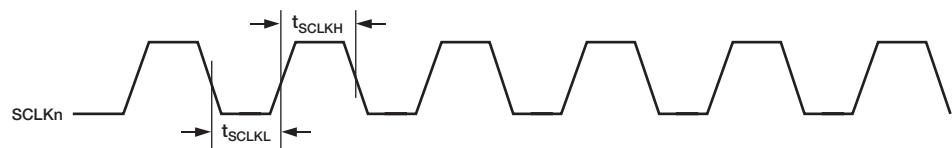

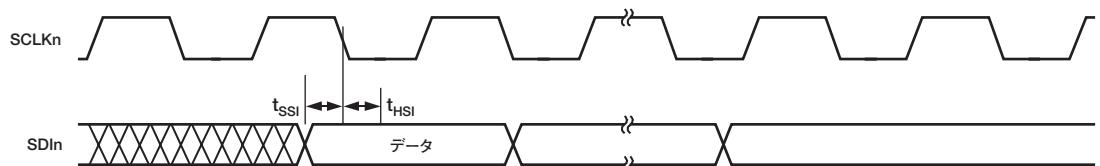

| <b>シリアル・ポート制御のタイミング条件</b>                                               |     |         |          |                        |      |    |

| <b>スイッチング特性<sup>2</sup></b>                                             |     |         |          |                        |      |    |

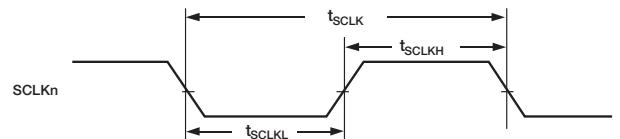

| $t_{SCLK}$ SCLKn (n=0, 4) 周期                                            | 全範囲 | IV      | 16       |                        |      | ns |

| $t_{SCLKL}$ SCLKnローレベル時間                                                | 全範囲 | IV      | 3.0      |                        |      | ns |

| $t_{SCLKH}$ SCLKnハイレベル時間                                                | 全範囲 | IV      | 3.0      |                        |      | ns |

| <b>入力特性</b>                                                             |     |         |          |                        |      |    |

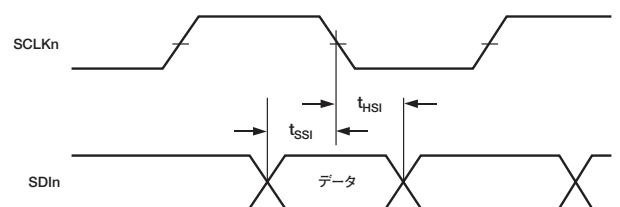

| $t_{SSI}$ SDInから $\downarrow$ SCLKnまでのセットアップ・タイム                        | 全範囲 | IV      | 1.0      |                        |      | ns |

| $t_{HSI}$ SDInから $\downarrow$ SCLKnまでのホールド・タイム                          | 全範囲 | IV      | 1.0      |                        |      | ns |

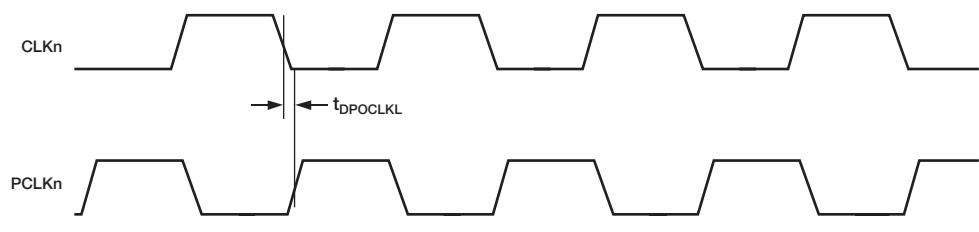

| <b>パラレル・ポートのタイミング条件</b>                                                 |     |         |          |                        |      |    |

| <b>(マスター・モード) スイッチング特性<sup>3</sup></b>                                  |     |         |          |                        |      |    |

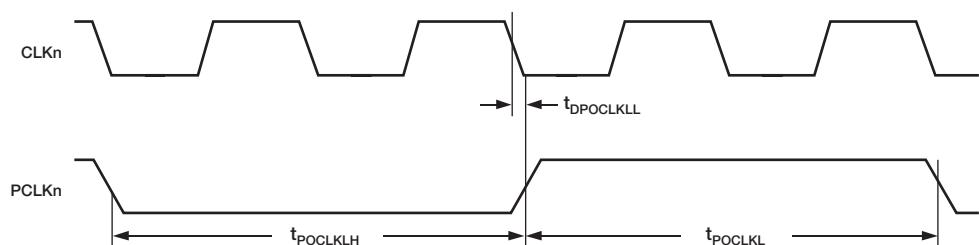

| $t_{DPOCLKL}$ $\downarrow$ CLKnから $\uparrow$ PCLKnまでの遅延 (1分周)           | 全範囲 | IV      | 6.5      |                        | 10.5 | ns |

| $t_{DPOCLKLL}$ $\downarrow$ CLKnから $\uparrow$ PCLKnまでの遅延 (2, 4, または8分周) | 全範囲 | IV      | 8.3      |                        | 14.6 | ns |

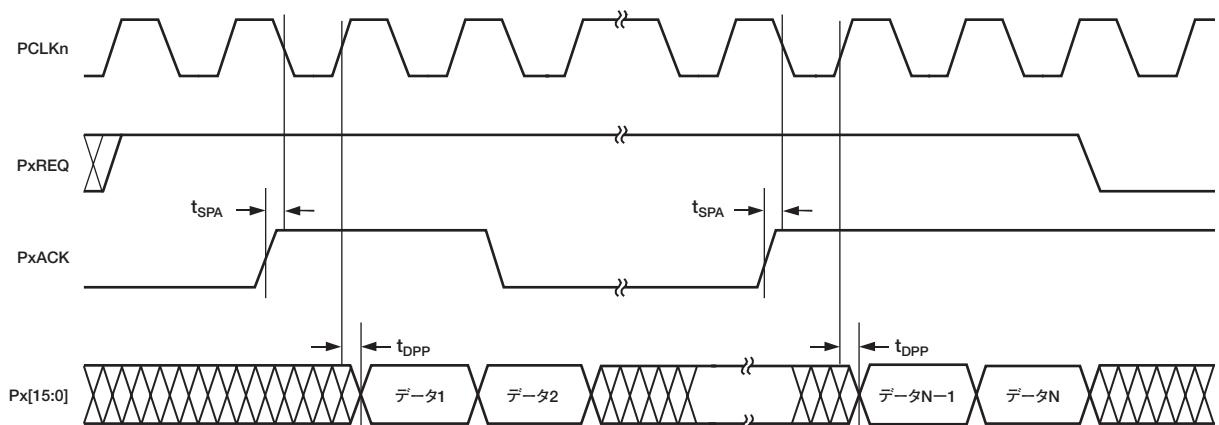

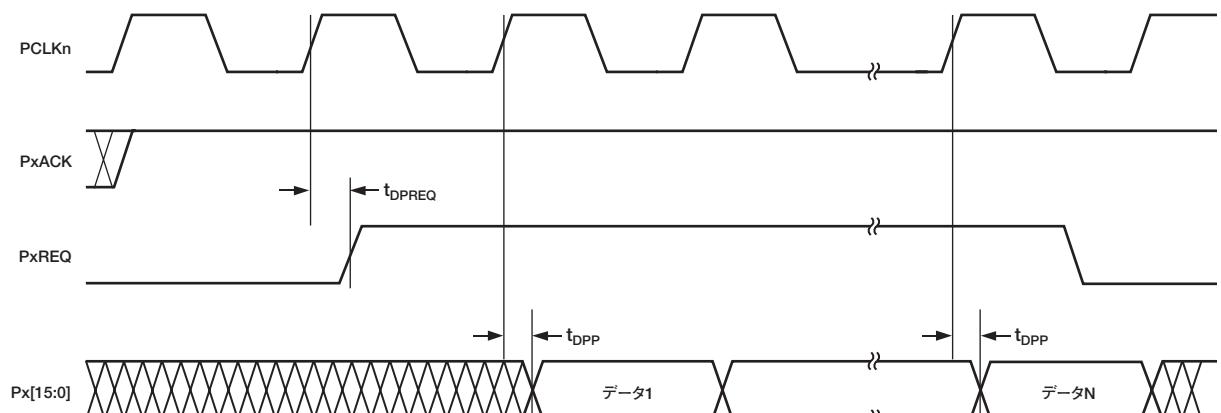

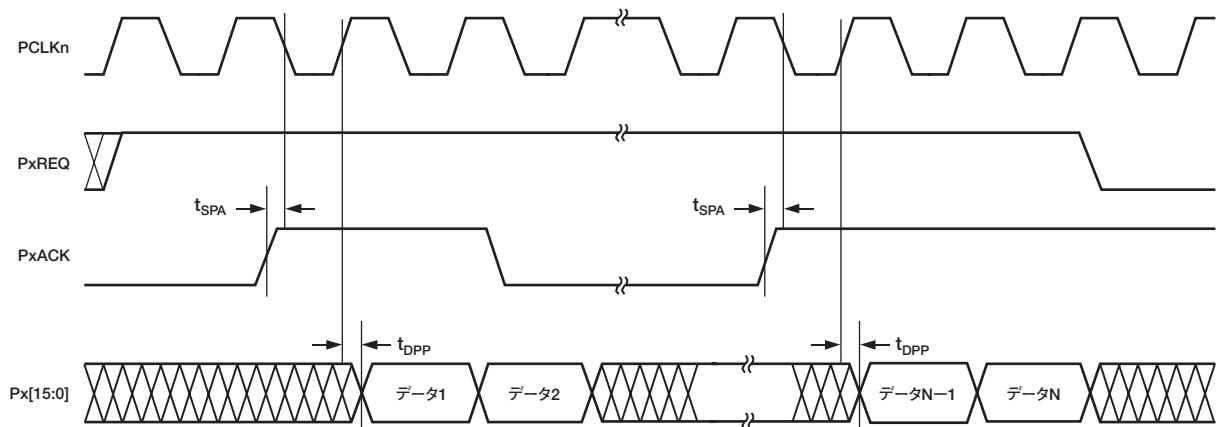

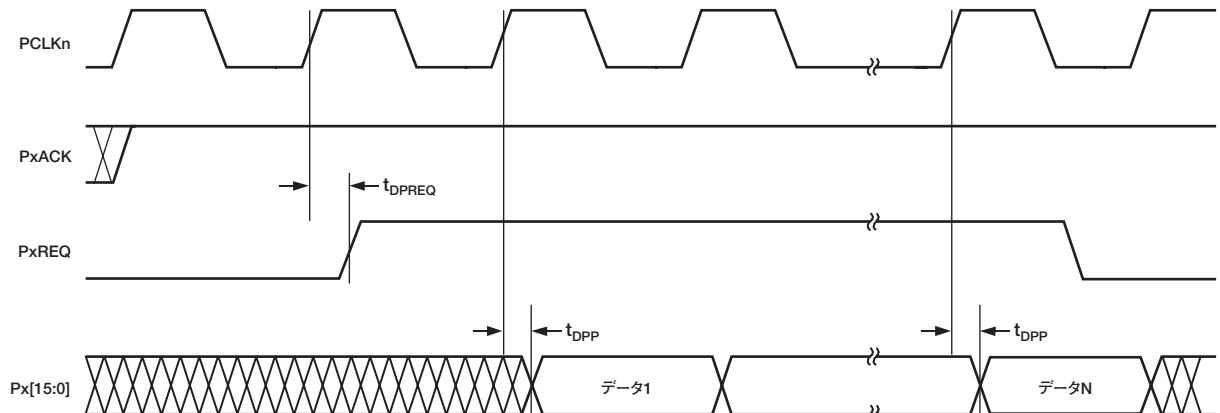

| $t_{DPREQ}$ $\uparrow$ CLKnから $\uparrow$ PxREQまでの遅延                     |     |         |          |                        | 1.0  | ns |

| $t_{DPP}$ $\uparrow$ CLKnから Px[15:0]までの遅延                               |     |         |          |                        | 0.0  | ns |

| <b>入力特性</b>                                                             |     |         |          |                        |      |    |

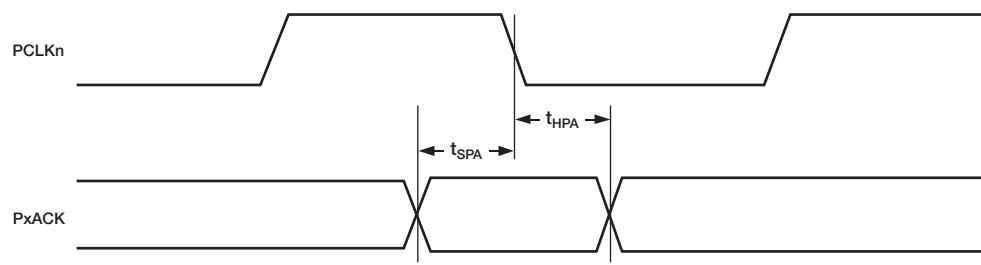

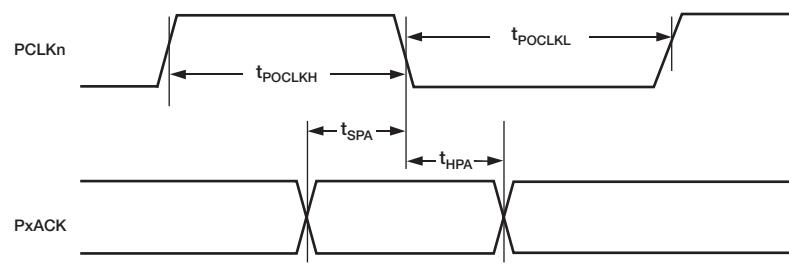

| $t_{SPA}$ PxACKから $\downarrow$ PCLKnまでのセットアップ・タイム                       |     |         | 7.0      |                        |      | ns |

| $t_{HPA}$ PxACKから $\downarrow$ PCLKnまでのホールド・タイム                         |     |         | -3.0     |                        |      | ns |

| <b>パラレル・ポートのタイミング条件</b>                                                 |     |         |          |                        |      |    |

| <b>(スレーブ・モード) スイッチング特性<sup>3</sup></b>                                  |     |         |          |                        |      |    |

| $t_{POCLK}$ PCLKn周期                                                     | 全範囲 | I       | 12.5     |                        |      | ns |

| $t_{POCLKL}$ PCLKnローレベル周期 (PCLK分周比=1のとき)                                | 全範囲 | IV      | 2.0      | $0.5 \times t_{POCLK}$ |      | ns |

| $t_{POCLKH}$ PCLKnハイレベル周期 (PCLK分周比=1のとき)                                | 全範囲 | IV      | 2.0      | $0.5 \times t_{POCLK}$ |      | ns |

| $t_{DPREQ}$ $\uparrow$ CLKnから $\uparrow$ PxREQまでの遅延                     |     |         |          |                        | 10.0 | ns |

| $t_{DPP}$ $\uparrow$ CLKnから Px[15:0]までの遅延                               |     |         |          |                        | 11.0 | ns |

## 一般的なタイミング特性<sup>1, 2</sup>

| パラメータ (条件)                  | 温度                                              | テスト・レベル | AD6635BB |     |     | 単位 |

|-----------------------------|-------------------------------------------------|---------|----------|-----|-----|----|

|                             |                                                 |         | Min      | Typ | Max |    |

| <b>入力特性</b>                 |                                                 |         |          |     |     |    |

| $t_{SPA}$                   | PxACKから $\downarrow$ PCLKnまでのセットアップ・タイム         |         |          | 1.0 |     | ns |

| $t_{HPA}$                   | PxACKから $\downarrow$ PCLKnまでのホールド・タイム           |         |          | 1.0 |     | ns |

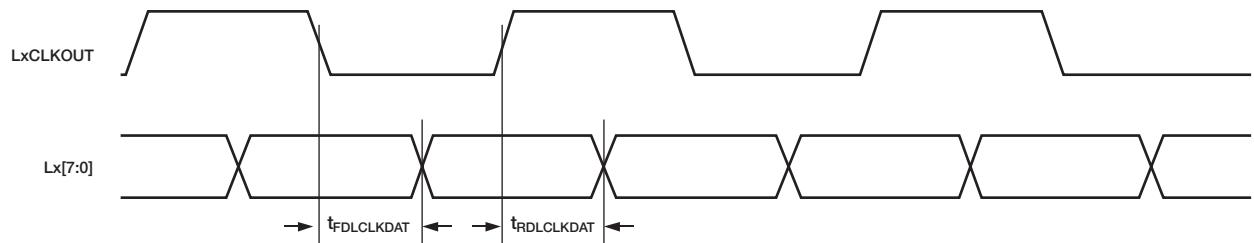

| <b>リンク・ポートのタイミング条件</b>      |                                                 |         |          |     |     |    |

| <b>スイッチング特性<sup>3</sup></b> |                                                 |         |          |     |     |    |

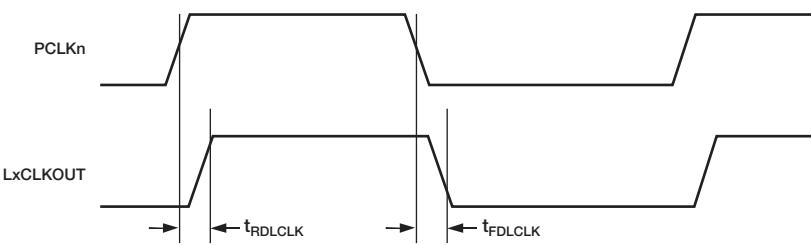

| $t_{RDCLK}$                 | $\uparrow$ PCLKnから $\uparrow$ LxCLKOUTまでの遅延     | 全範囲     | IV       |     | 2.5 | ns |

| $t_{FDLCLK}$                | $\downarrow$ PCLKnから $\downarrow$ LxCLKOUTまでの遅延 | 全範囲     | IV       |     | 0   | ns |

| $t_{RLCLKDAT}$              | $\uparrow$ LxCLKOUTからLx[7:0]までの遅延               | 全範囲     | IV       | 0   | 2.9 | ns |

| $t_{FLCLKDAT}$              | $\downarrow$ LxCLKOUTからLx[7:0]までの遅延             | 全範囲     | IV       | 0   | 2.2 | ns |

## 注

<sup>1</sup> すべてのタイミング仕様は、2.25~2.75VのVDD範囲と3.0~3.6VのVDDIO範囲で有効です。

<sup>2</sup> 特に指定がない限り、すべての出力で $C_{LOAD}=40\text{pF}$ 。

<sup>3</sup> Px[15:0]、PxREQ、PxACK、LxCLKOUT、Lx[7:0]のタイミング・パラメータは、出力ポートA、B、C、Dに適用されます（xはA、B、C、またはDを表します）。

仕様は予告なく変更されることがあります。

# AD6635

## マイクロプロセッサ・ポートのタイミング特性<sup>1, 2</sup>

| パラメータ (条件)                           | 温度  | テスト・レベル | AD6635BB           |                     |                     | 単位 |

|--------------------------------------|-----|---------|--------------------|---------------------|---------------------|----|

|                                      |     |         | Min                | Typ                 | Max                 |    |

| <b>マイクロプロセッサ・ポート、モードMNM (MODE=0)</b> |     |         |                    |                     |                     |    |

| モードINMの書き込みタイミング                     |     |         |                    |                     |                     |    |

| $t_{SC}$                             | 全範囲 | IV      | 2.0                |                     |                     | ns |

| $t_{HC}$                             | 全範囲 | IV      | 2.5                |                     |                     | ns |

| $t_{HWR}$                            | 全範囲 | IV      | 7.0                |                     |                     | ns |

| $t_{SAM}$                            | 全範囲 | IV      | 3.0                |                     |                     | ns |

| $t_{HAM}$                            | 全範囲 | IV      | 5.0                |                     |                     | ns |

| $t_{DRDY}$                           | 全範囲 | IV      | 8.0                |                     |                     | ns |

| $t_{ACC}$                            | 全範囲 | IV      | $4 \times t_{CLK}$ | $5 \times t_{CLK}$  | $9 \times t_{CLK}$  | ns |

| モードINMの読み出しタイミング                     |     |         |                    |                     |                     |    |

| $t_{SC}$                             | 全範囲 | IV      | 5.0                |                     |                     | ns |

| $t_{HC}$                             | 全範囲 | IV      | 2.0                |                     |                     | ns |

| $t_{SAM}$                            | 全範囲 | IV      | 0.0                |                     |                     | ns |

| $t_{HAM}$                            | 全範囲 | IV      | 5.0                |                     |                     | ns |

| $t_{DRDY}$                           | 全範囲 | IV      | 8.0                |                     |                     | ns |

| $t_{ACC}$                            | 全範囲 | IV      | $8 \times t_{CLK}$ | $10 \times t_{CLK}$ | $13 \times t_{CLK}$ | ns |

| <b>マイクロプロセッサ・ポート、モードMNM (MODE=1)</b> |     |         |                    |                     |                     |    |

| モードMNMの書き込みタイミング                     |     |         |                    |                     |                     |    |

| $t_{SC}$                             | 全範囲 | IV      | 2.0                |                     |                     | ns |

| $t_{HC}$                             | 全範囲 | IV      | 2.5                |                     |                     | ns |

| $t_{HDS}$                            | 全範囲 | IV      | 8.0                |                     |                     | ns |

| $t_{HRW}$                            | 全範囲 | IV      | 7.0                |                     |                     | ns |

| $t_{SAM}$                            | 全範囲 | IV      | 3.0                |                     |                     | ns |

| $t_{HAM}$                            | 全範囲 | IV      | 5.0                |                     |                     | ns |

| $t_{DDTACK}$                         | 全範囲 | IV      | 8.0                |                     |                     | ns |

| $t_{ACC}$                            | 全範囲 | IV      | $4 \times t_{CLK}$ | $5 \times t_{CLK}$  | $9 \times t_{CLK}$  | ns |

| モードMNMの読み出しタイミング                     |     |         |                    |                     |                     |    |

| $t_{SC}$                             | 全範囲 | IV      | 5.0                |                     |                     | ns |

| $t_{HC}$                             | 全範囲 | IV      | 2.0                |                     |                     | ns |

| $t_{HDS}$                            | 全範囲 | IV      | 8.0                |                     |                     | ns |

| $t_{SAM}$                            | 全範囲 | IV      | 0.0                |                     |                     | ns |

| $t_{HAM}$                            | 全範囲 | IV      | 5.0                |                     |                     | ns |

| $t_{DDTACK}$                         | 全範囲 | IV      | 8.0                |                     |                     | ns |

| $t_{ACC}$                            | 全範囲 | IV      | $8 \times t_{CLK}$ | $10 \times t_{CLK}$ | $13 \times t_{CLK}$ | ns |

注

<sup>1</sup> すべてのタイミング仕様は、2.25~2.75VのVDD範囲と3.0~3.6VのVDDIO範囲で有効です。

<sup>2</sup> 特に指定がない限り、すべての出力で  $C_{LOAD}=40\text{pF}$ 。

<sup>3</sup> 仕様は次の制御信号のものです：R/W、(WR)、(DS)、(RD)、CS0、CS1

仕様は予告なく変更されることがあります。

**絶対最大定格\***

|            |                   |

|------------|-------------------|

| 電源電圧       | 3.6V              |

| 入力電圧       | -0.3~+5.3V (5V対応) |

| 出力電圧振幅     | -0.3V~VDDIO+0.3V  |

| 負荷容量       | 200pF             |

| バイアス時の接合温度 | 150°C             |

| 保管温度範囲     | -65~+150°C        |

| ピン温度 (5秒)  | 280°C             |

\* 上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態にすると、デバイスの信頼性に影響を与えることがあります。

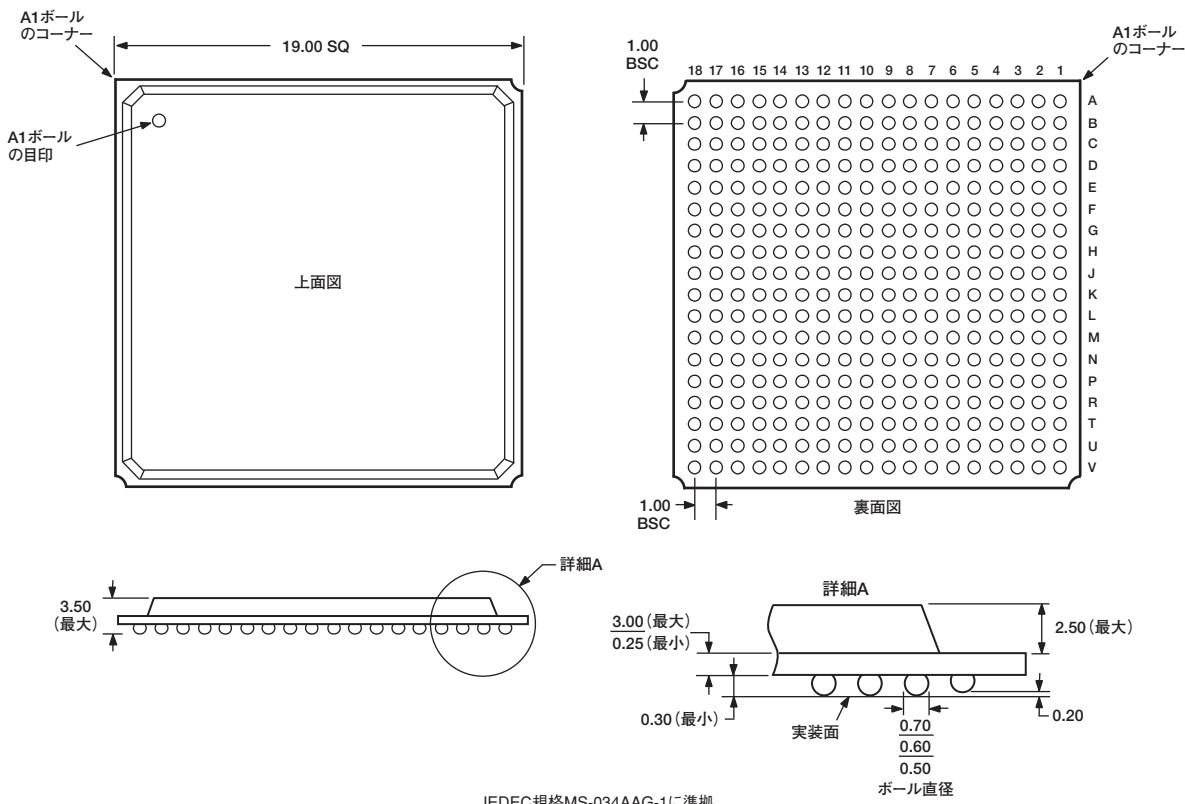

**熱特性**

324ピンBGA :

$\theta_{JA} = 16.87^{\circ}\text{C}/\text{W}$ 、自然空冷

温度は4層ボード上の水平位置で測定。

**テスト・レベルの説明**

- I 100%の出荷テストを実施。

- II 25°Cでの100%の出荷テストおよび指定温度でのサンプル・テストを実施。

- III サンプル・テストだけを実施。

- IV パラメータは設計と解析により保証。

- V パラメータは代表値のみ。

- VI 25°Cでの100%の出荷テストおよび限界温度でのサンプル・テストを実施。

**オーダー・ガイド**

| 製品モデル        | 温度範囲      | パッケージ                    | パッケージ・オプション |

|--------------|-----------|--------------------------|-------------|

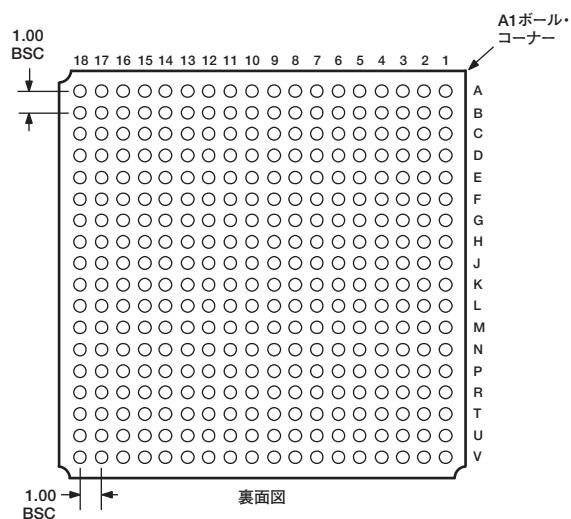

| AD6635BB     | -40~+85°C | 324ピンPBGA (ボール・グリッド・アレイ) | B-324       |

| AD6635BB/PCB |           | 評価ボード (AD6635とソフトウェア付き)  |             |

**注意**

ESD (静電放電) の影響を受けやすいデバイスです。人体や試験機器には4,000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されます。AD6635は当社独自のESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

# AD6635

## ピン配置

19mm×19mm — 18<sup>2</sup>ポールZAPHODパッケージ

## ピン配置 (ピンアウト)

|   | 1               | 2               | 3               | 4     | 5     | 6     | 7     | 8     | 9       | 10      | 11      | 12    | 13    | 14              | 15        | 16              | 17             | 18              |   |   |

|---|-----------------|-----------------|-----------------|-------|-------|-------|-------|-------|---------|---------|---------|-------|-------|-----------------|-----------|-----------------|----------------|-----------------|---|---|

| A |                 | IENC            | INC0            | INC7  | INC12 | IND2  | IND3  | IND7  | IND8    | IND11   | EXPDI   | PDREQ | PD14  | PD10            | PD8       | PD5_LD5         | PDCH1_LDCLK_IN |                 | A |   |

| B | CLK0            | VDDIO<br>(予約済み) | INC1            | INC8  | INC11 | IND1  | IND4  | IND6  | IND9    | IND12   | EXPDI2  | PDAck | PD12  | PD11            | PD4_LD4   | PD3_LD3         | PD7_LD7        | PDCH0_LDCLK_OUT |   | B |

| C | CLK1            | VDDIO<br>(予約済み) | PAREQ           | INC2  | INC9  | LID-B | IND0  | IND5  | IND10   | IND13   | EXPDI0  | PD15  | PD9   | PD1_LD1         | PD2_LD2   | PD0_LD0         | SDI4           | PDIQ            |   | C |

| D | PAAACK          | CHIP0_ID0       |                 | LID-A | INC3  | INC10 | INC13 | IEND  | EXPDI0  | VDD     | VDD     | VDD   | PD13  | PCACK           | CHIP1_ID1 | PCIQ            | PD6_LD6        | PCLK1           |   | D |

| E | CHIP0_ID1       | CHIP0_ID2       |                 |       | INC4  | INC5  | INC6  | EXPC2 | EXPC1   | VDD     | VDD     | VDD   |       | VDDIO<br>(予約済み) | DNC       | CHIP1_ID0       | CHIP1_ID2      | SCLK4           |   | E |

| F | SCLK0           | PAIQ            |                 | VDD   | VDD   | VDD   | VDDIO | VDDIO | VDDIO   | GND     | GND     | GND   | VDDIO | VDDIO           | VDDIO     | PCREQ           | PC14           | PC15            |   | F |

| G | PCLK0           | SDI0            | PB6_LB6         | VDD   | VDD   | VDD   | VDDIO | VDDIO | VDDIO   | GND     | GND     | GND   | VDDIO | VDDIO           | VDDIO     | PC11            | PC13           | PC12            |   | G |

| H | PBCH0_LBCLK_OUT | PBIQ            | PB7_LB7         | GND   | GND   | GND   | GND   | GND   | GND     | GND     | GND     | GND   | GND   | GND             | GND       | PC10            | PC9            | DNC             |   | H |

| J | PBCH1_LBCLK_IN  | PB0_LB0         | PB3_LB3         | GND   | GND   | GND   | GND   | GND   | GND     | GND     | GND     | GND   | GND   | GND             | GND       | PC8             | PC0_LC0        | GND<br>(予約済み)   |   | J |

| K | PB2_LB2         | PB4_LB4         | PB5_LB5         | GND   | GND   | GND   | GND   | GND   | GND     | GND     | GND     | GND   | GND   | GND             | GND       | PC1_LC1         | PC3_LC3        | PC2_LC2         |   | K |

| L | PB11            | PB1_LB1         | PB8             | GND   | GND   | GND   | GND   | GND   | GND     | GND     | GND     | GND   | GND   | GND             | GND       | A1              | PC5_LC5        | PC4_LC4         |   | L |

| M | PB13            | PB9             | PB10            | VDDIO | VDDIO | VDDIO | VDD   | VDD   | VDD     | VDDIO   | VDDIO   | VDDIO | VDD   | VDD             | VDD       | PC6_LC6         | PC7_L_C7       | PCCH1_LCCLK_IN  |   | M |

| N | PB12            | PB14            | VDDIO<br>(予約済み) | VDDIO | VDDIO | VDDIO | VDD   | VDD   | VDD     | VDDIO   | VDDIO   | VDDIO | VDD   | VDD             | VDD       | A0              | A2             | PCCH0_LCCLK_OUT |   | N |

| P | PBREQ           | PB15            | PBACK           | PA15  | PA14  | PA13  | PA10  | PA12  | PA11    | PA3_LA3 | LIC-A   | DNC   | DNC   | DNC             | D7        | D0              | D1             | DS              |   | P |

| R | EXPB0           | INB10           | INB11           | INB12 | INB13 | EXPB0 | EXPB2 | PA9   | PA8     | LIC-B   | PA5_LA5 | CS0   | DNC   | D4              | D3        | CS1             | R/W            | VDDIO<br>(予約済み) |   | R |

| T | EXPB1           | INB9            | INB4            | INB3  | INB0  | EXPB1 | INA9  | INA8  | PA0_LA0 | PA2_LA2 | PA1_LA1 | SYNCD | DTACK | RESET           | PA7_LA7   | DNC             | D5             | D2              |   | T |

| U | EXPB2           | INB8            | INB5            | INB2  | LIC-B | INA13 | INA10 | INA7  | INA5    | INA3    | INA1    | LIA-A | SYNCA | SYNCC           | PA6_LA6   | PA4_LA4         | MODE           | D6              |   | U |

| V |                 | INB7            | INB6            | INB1  | IENB  | INA12 | INA11 | INA6  | INA4    | INA2    | INA0    | IENA  | LIC-A | LIA-B           | SYNCB     | PACH0_LACLK_OUT | PACH1_LACLK_IN |                 |   | V |

|   | 1               | 2               | 3               | 4     | 5     | 6     | 7     | 8     | 9       | 10      | 11      | 12    | 13    | 14              | 15        | 16              | 17             | 18              |   |   |

# AD6635

## ピン機能の説明

| 名前                         | タイプ | 機能                                   |

|----------------------------|-----|--------------------------------------|

| 電源                         |     |                                      |

| VDD                        | P   | 2.5Vコア電源 (DVCOREとも呼ばれます)             |

| VDDIO                      | P   | 3.3V IO電源 (DVRINGとも呼ばれます)            |

| GND                        | G   | グラウンド                                |

| 入力                         |     |                                      |

| INA[13:0] <sup>1</sup>     | I   | A入力データ (仮数部)                         |

| EXPA[2:0] <sup>1</sup>     | I   | A入力データ (指数部)                         |

| IENA <sup>2</sup>          | I   | 入力イネーブルー 入力A                         |

| INB[13:0] <sup>1</sup>     | I   | B入力データ (仮数部)                         |

| EXPB[2:0] <sup>1</sup>     | I   | B入力データ (指数部)                         |

| IENB <sup>2</sup>          | I   | 入力イネーブルー 入力B                         |

| INC[13:0] <sup>1</sup>     | I   | C入力データ (仮数部)                         |

| EXPC[2:0] <sup>1</sup>     | I   | C入力データ (指数部)                         |

| IENC <sup>2</sup>          | I   | 入力イネーブルー 入力C                         |

| IND[13:0] <sup>1</sup>     | I   | D入力データ (仮数部)                         |

| EXPD[2:0] <sup>1</sup>     | I   | D入力データ (指数部)                         |

| IEND <sup>2</sup>          | I   | 入力イネーブルー 入力D                         |

| RESET                      | I   | アクティブ・ロー・リセット・ピン                     |

| CLK0                       | I   | 入力クロック0 (チャンネル0~3とポートA、B用のマスター・クロック) |

| CLK1                       | I   | 入力クロック1 (チャンネル4~7とポートC、D用のマスター・クロック) |

| PCLK0                      | I/O | 出力ポートAとB用のリンク/パラレル・ポート・クロック          |

| PCLK1                      | I/O | 出力ポートCとD用のリンク/パラレル・ポート・クロック          |

| LACLKIN                    | I   | リンク・ポートAデータ・レディ                      |

| LBCLKIN                    | I   | リンク・ポートBデータ・レディ                      |

| LCCLKIN                    | I   | リンク・ポートCデータ・レディ                      |

| LDCLKIN                    | I   | リンク・ポートDデータ・レディ                      |

| SYNCA <sup>1</sup>         | I   | すべてのSyncピンを8チャンネルすべてに接続              |

| SYNCB <sup>1</sup>         | I   | すべてのSyncピンを8チャンネルすべてに接続              |

| SYNCC <sup>1</sup>         | I   | すべてのSyncピンを8チャンネルすべてに接続              |

| SYNCD <sup>1</sup>         | I   | すべてのSyncピンを8チャンネルすべてに接続              |

| CHIP0_ID[2:0] <sup>1</sup> | I   | チャンネル0~3とポートA、B用のチップIDセレクタ           |

| CHIP1_ID[2:0] <sup>1</sup> | I   | チャンネル4~7とポートC、D用のチップIDセレクタ           |

| 制御                         |     |                                      |

| PAACK                      | I   | パラレル・ポートAアクノレッジ                      |

| PAREQ                      | O   | パラレル・ポートAリクエスト                       |

| PBACK                      | I   | パラレル・ポートBアクノレッジ                      |

| PBREQ                      | O   | パラレル・ポートBリクエスト                       |

| PCACK                      | I   | パラレル・ポートCアクノレッジ                      |

| PCREQ                      | O   | パラレル・ポートCリクエスト                       |

| PDACK                      | I   | パラレル・ポートDアクノレッジ                      |

| PDREQ                      | O   | パラレル・ポートDリクエスト                       |

ピン・タイプ:I=入力、O=出力、P=電源、G=グラウンド、T=スリーステート。

## ピン機能の説明（続き）

| 名前                       | タイプ   | 機能                                     |

|--------------------------|-------|----------------------------------------|

| マイクロポート制御                |       |                                        |

| D[7:0]                   | I/O/T | 両方向マイクロポート・データ                         |

| A[2:0]                   | I     | マイクロポート・アドレス・バス                        |

| DS (RD)                  | I     | アクティブ・ロー・データ・ストローブ（アクティブ・ロー読み出し）       |

| DTACK (RDY) <sup>2</sup> | O/T   | アクティブ・ロー・データ・アクノレッジ（マイクロポート・ステータス・ビット） |

| R/W (WR)                 | I     | 読み書き（アクティブ・ロー書き込み）                     |

| MODE                     | I     | インテルまたはモトローラのモード・セレクト                  |

| CS0 <sup>1</sup>         | I     | チャンネル0～3とポートA、B用のチップ・セレクト              |

| CS1 <sup>1</sup>         | I     | チャンネル4～7とポートC、D用のチップ・セレクト              |

| シリアル・ポート制御               |       |                                        |

| SDIO <sup>1</sup>        | I     | チャンネル0～3とポートA、B用のシリアル・ポート制御データ入力       |

| SCLK0 <sup>1</sup>       | I     | チャンネル0～3とポートA、B用のシリアル・ポート制御クロック        |

| SDI4 <sup>1</sup>        | I     | チャンネル4～7とポートC、D用のシリアル・ポート制御データ入力       |

| SCLK4 <sup>1</sup>       | I     | チャンネル4～7とポートC、D用のシリアル・ポート制御クロック        |

| 出力                       |       |                                        |

| LIA-A                    | O     | レベル・インジケーター入力A、インターリープされたデータA          |

| LIA-B                    | O     | レベル・インジケーター入力A、インターリープされたデータB          |

| LIB-A                    | O     | レベル・インジケーター入力B、インターリープされたデータA          |

| LIB-B                    | O     | レベル・インジケーター入力B、インターリープされたデータB          |

| LIC-A                    | O     | レベル・インジケーター入力C、インターリープされたデータA          |

| LIC-B                    | O     | レベル・インジケーター入力C、インターリープされたデータB          |

| LID-A                    | O     | レベル・インジケーター入力D、インターリープされたデータA          |

| LID-B                    | O     | レベル・インジケーター入力D、インターリープされたデータB          |

| LACLKOUT                 | O     | リンク・ポートAクロック出力                         |

| LBCLKOUT                 | O     | リンク・ポートBクロック出力                         |

| LCCLKOUT                 | O     | リンク・ポートCクロック出力                         |

| LDCLKOUT                 | O     | リンク・ポートDクロック出力                         |

| LA[7:0]                  | O     | リンク・ポートA出力データ                          |

| LB[7:0]                  | O     | リンク・ポートB出力データ                          |

| LC[7:0]                  | O     | リンク・ポートC出力データ                          |

| LD[7:0]                  | O     | リンク・ポートD出力データ                          |

| PA[15:0]                 | O     | パラレル出力データ・ポートA                         |

| PB[15:0]                 | O     | パラレル出力データ・ポートB                         |

| PC[15:0]                 | O     | パラレル出力データ・ポートC                         |

| PD[15:0]                 | O     | パラレル出力データ・ポートD                         |

| PACH[1:0]                | O     | パラレル出力ポートAのチャンネル・インジケータ                |

| PBCH[1:0]                | O     | パラレル出力ポートBのチャンネル・インジケータ                |

| PCCH[1:0]                | O     | パラレル出力ポートCのチャンネル・インジケータ                |

| PDCH[1:0]                | O     | パラレル出力ポートDのチャンネル・インジケータ                |

| PAIQ                     | O     | パラレル・ポートAのI/Qデータ・インジケータ                |

| PBIQ                     | O     | パラレル・ポートBのI/Qデータ・インジケータ                |

| PCIQ                     | O     | パラレル・ポートCのI/Qデータ・インジケータ                |

| PDIQ                     | O     | パラレル・ポートDのI/Qデータ・インジケータ                |

ピン・タイプ：I=入力、O=出力、P=電源、G=グラウンド、T=スリーステート。

注

<sup>1</sup> ノミナル70kΩのプルダウン抵抗付きのピン<sup>2</sup> ノミナル70kΩのプルアップ抵抗付きのピン

# AD6635

## タイミング図

図3. レベル・インジケータの出力スイッチング特性 ( $x=A, B, C, D$ 、および  $y=A, B$ )

( $x=A$ および  $B$ 、 $n=0$ の場合、および  $x=C$ または  $D$ 、 $n=1$ の場合)

図4.  $\overline{RESET}$ のタイミング条件

図5. SCLKスイッチング特性 ( $n=0, 4$ )

図6. シリアル・ポートの入力タイミング特性 ( $n=0, 4$ )

図7. AチャンネルとBチャンネルの入力タイミング

図8. SYNCタイミング入力

図9. PCLKn/CLKnのスイッチング特性（1分周）

図10. PCLKn/CLKnのスイッチング特性（2、4、または8分周）

# AD6635

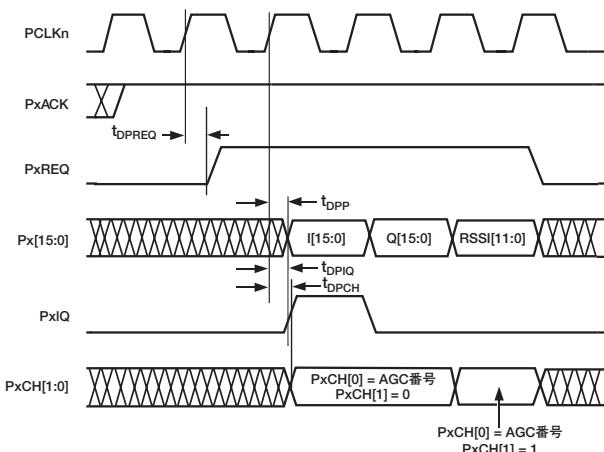

図11. マスター・モードでのPxACK/PCLKnのセットアップおよびホールド特性

(n=0、x=A、B、またはn=1、x=C、D)

図12. マスター・モードでのPxACK/PCLKnのスイッチング特性

(n=0、x=A、B、またはn=1、x=C、D)

図13. マスター・モードでのPxREQ/PCLKnのスイッチング特性

(n=0、x=A、B、またはn=1、x=C、D)

図14. スレーブ・モードでのPxACK/PCLKnのセットアップおよびホールド特性

(n=0、x=A、B、またはn=1、x=C、D)

図15. スレーブ・モードでのPxACK/PCLKnのスイッチング特性

(n=0、x=A、B、またはn=1、x=C、D)

図16. スレーブ・モードでのPxREQ/PCLKnのスイッチング特性

(n=0、x=A、B、またはn=1、x=C、D)

# AD6635

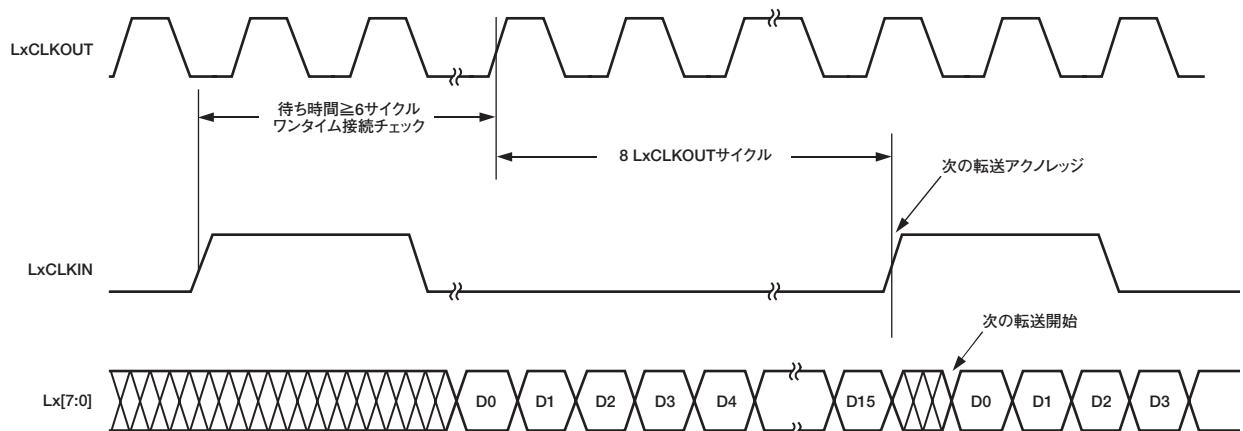

図17. LxCLKOUT/PCLKn ( $n=0$ 、 $x=A$ 、 $B$ 、または $n=1$ 、 $x=C$ 、 $D$ ) のスイッチング特性

図18. LxCLKIN/LxCLKOUTのデータ・スイッチング特性

図19. LxCLKOUT/Lx[7:0]のデータ・スイッチング特性

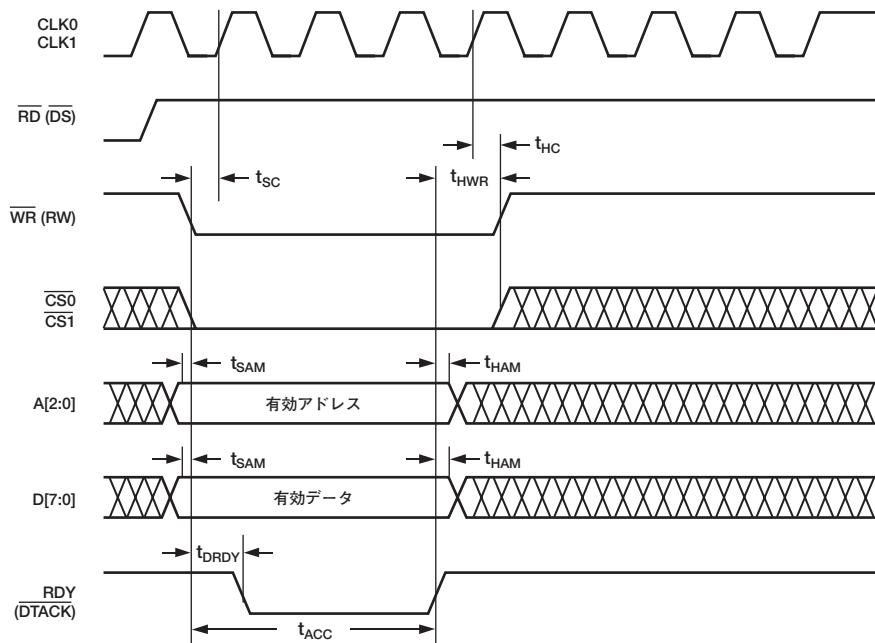

## タイミング図 — INMマイクロポート・モード (MODE=0)

注

- $t_{ACC}$ のアクセス時間は、アクセスするアドレスに依存します。アクセス時間は、WRのFEからRDYのREまでを測定。

- $t_{ACC}$ には、最大で9 CLK周期が必要です。

図20. INMマイクロポート書き込みのタイミング条件

CLK0はCS0、CLK1はCS1に対応。CS0とCS1が同時にアクティブ（ロー）になる場合、書き込みエラーが発生。

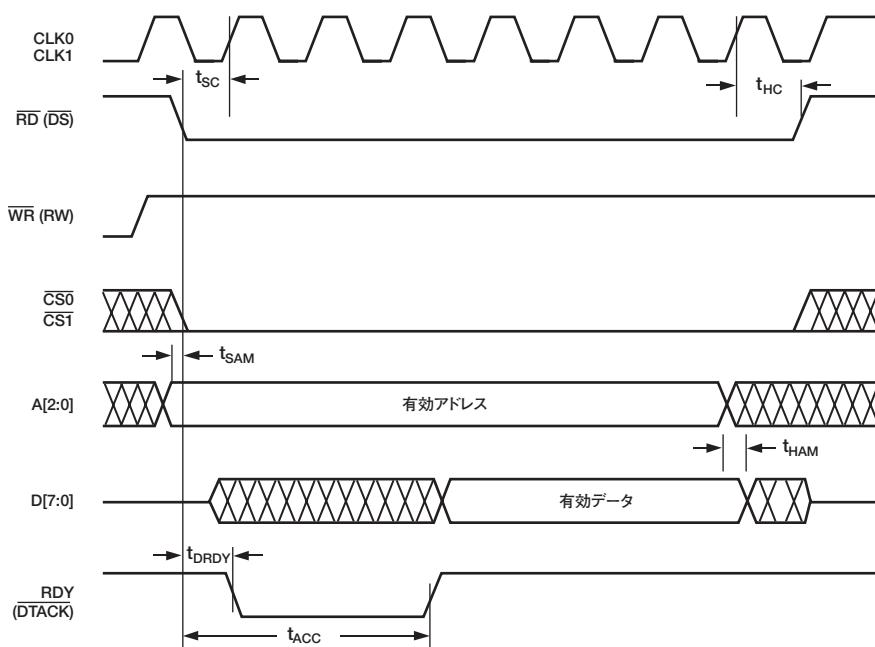

注

- $t_{ACC}$ アクセス時間は、アクセスするアドレスに依存します。アクセス時間は、WRのFEからRDYのREまでを測定。

- $t_{ACC}$ には、最大で13 CLK周期が必要で、A[2:0]=7、6、5、3、2、1に適用されます。

図21. INMマイクロポート読み出しのタイミング条件

CLK0はCS0、CLK1はCS1に対応。CS0とCS1が同時にアクティブ（ロー）になる場合、データ・バスの競合が発生。

# AD6635

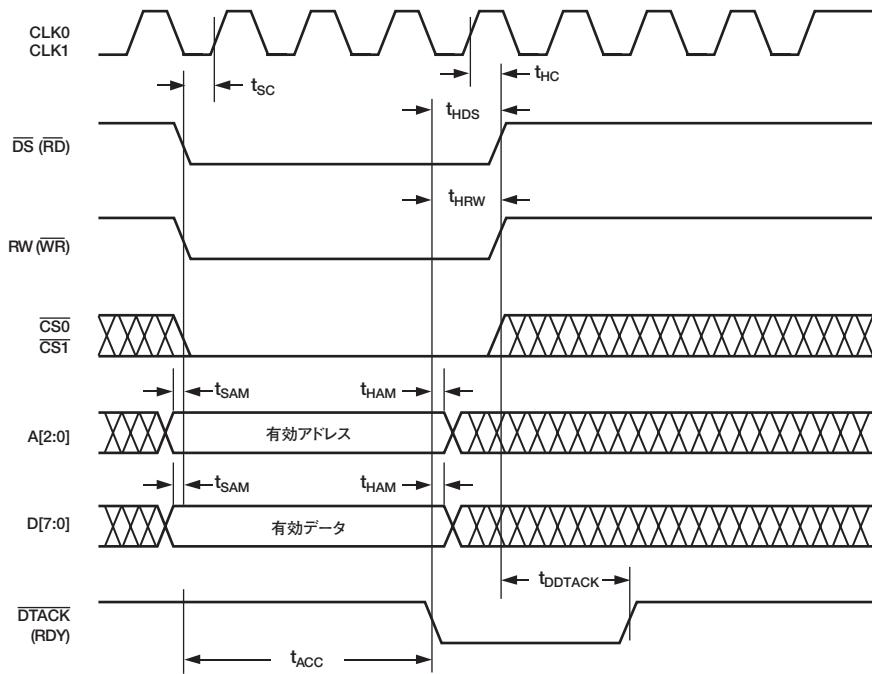

タイミング図 — MNMマイクロポート・モード (MODE=1)

注

1.  $t_{ACC}$ アクセス時間は、アクセスするアドレスに依存します。アクセス時間は、 $\overline{DS}$ のFEから $\overline{DTACK}$ のFEまでを測定。

2.  $t_{ACC}$ には、最大で9 CLK周期が必要です。

図22. MNMマイクロポート書き込みのタイミング条件

CLK0は $\overline{CS0}$ 、CLK1は $\overline{CS1}$ に対応。 $\overline{CS0}$ と $\overline{CS1}$ が同時にアクティブ（ロー）になる場合、書き込みエラーが発生。

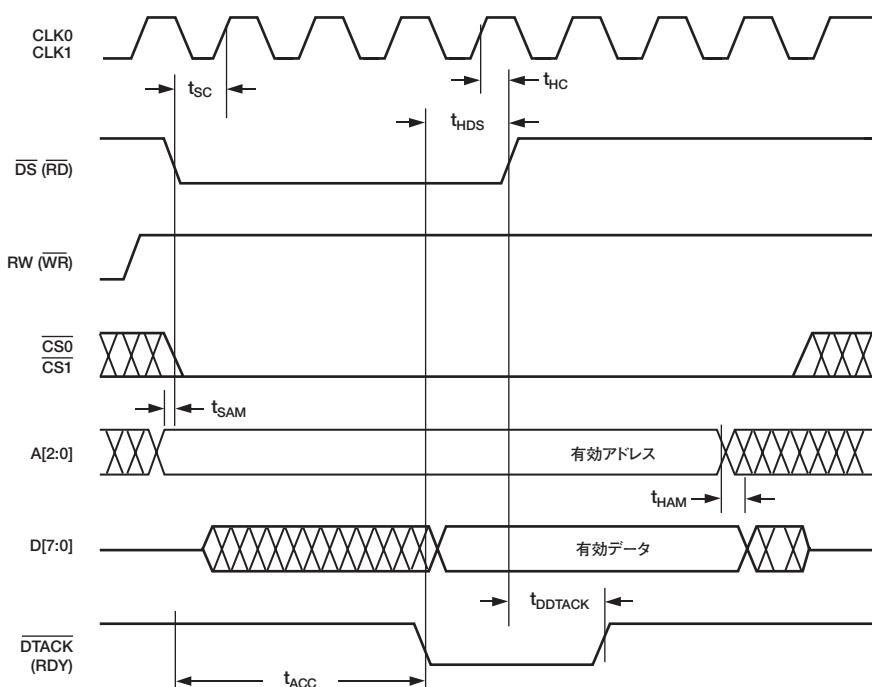

注

1.  $t_{ACC}$ アクセス時間は、アクセスするアドレスに依存します。アクセス時間は、 $\overline{DS}$ のFEから $\overline{DTACK}$ のFEまでを測定。

2.  $t_{ACC}$ には、最大で13 CLK周期が必要です。

図23. MNMマイクロポート読み出しのタイミング条件

CLK0は $\overline{CS0}$ 、CLK1は $\overline{CS1}$ に対応。 $\overline{CS0}$ と $\overline{CS1}$ が同時にアクティブ（ロー）になる場合、データ・バスの競合が発生。

## 入力データ・ポート

AD6635は、A、B、C、Dという4つの高速なADC入力ポートを備えています。これらの入力ポートにより、単一のチューナ・チップで最大の柔軟性を発揮します。入力には、ダイバーシティ入力、または個別アンテナ・セグメントのようなまったく独立した入力を使用できます。チャンネル0~3は、入力ポートAまたはBのどちらからでも独立してデータを取得できます。同様に、チャンネル4~7は、入力ポートCまたはDのどちらからでも独立してデータを取得できます。さらに高い柔軟性をもたらす特長として、AD6600やマルチプレクサ出力を備えたその他のADCのように、各入力ポートでマルチプレクサ入力が可能です。このように強化された柔軟性によって、AD6635は8つの内部チャンネルによって、8つまでの異なるアナログ・ソースを同時に処理できます。

また、AD6635のフロント・エンドは、高速信号レベルの検出と制御が可能な回路を内蔵しています。この回路は、最大4つのアナログ信号バスを最小限のレイテンシと最大限の柔軟性で制御できる独自の高速レベルの検出回路を備えています。AD6635の入力から出力までの信号バス全体のレイテンシは、高速クロック・サイクル数で表すことができます。次の式を使用して、レイテンシを計算することができます。

$$T_{LATENCY} = M_{rCIC2}(M_{CIC5} + 7) + N_{TAPS} + 26$$

$M_{rCIC2}$ と $M_{CIC5}$ は、それぞれrCIC2フィルタとCIC5フィルタのデシメーション値です。 $N_{TAPS}$ は、選択されているRCFタップの数です。

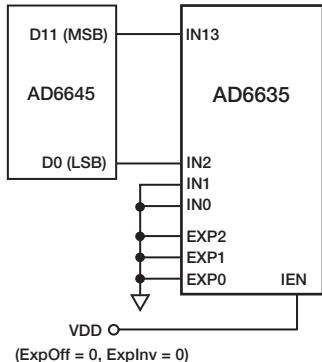

## 入力データ・フォーマット

各入力ポートは、14ビットの仮数部と3ビットの指数部で構成されます。標準ADCにインターフェースをとる場合には、指数部ビットをグラウンドに接続できます。AD6600などの浮動小数点ADCに接続する場合には、そのADC製品からの指数部ビットは、AD6635の入力指数部ビットに接続できます。仮数部のデータ・フォーマットは2の補数で、指数部は符号なし2進数です。

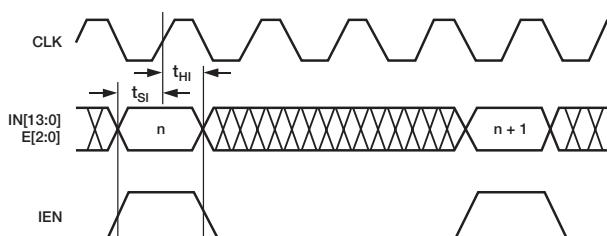

## 入力タイミング

各高速入力ポートからのデータは、CLKの立ち上がりエッジでラッチされます。このクロック信号は、入力ポートをサンプリングし、選択されたチャンネルで次に続く同期信号処理段をクロック駆動するために使用されます。

図24. 入力データのタイミング条件

クロック信号は、最大80MHzで動作することができ、50%のデューティ・サイクルです。高速ADCを使用するアプリケーションでは、AD6635のクロック駆動にADCのサンプル・クロックやデータ有効ストローブを使用するのが一般的です。

図25. CLKnのタイミング条件 (n=0, 1)

## 入力イネーブル制御

個々の入力ポートA~Dに対応して、4つの入力イネーブル・ピンIEN<sub>x</sub> (<sub>x</sub>=A、B、C、またはD) があります。各IENピンを使用するときには、4つの動作モードが可能です。これらのモードを使用すると、通常ダイバーシティ動作に付随するデュアル・チャンネル・モードを提供するAD6620などの他のRSPの動作をエミュレートできます。4つのモードは、「IENの立ち下がり変化」、「IENの立ち上がり変化」、「IENハイレベル」、および「ブランク・オンIENロー」です。

「IENハイレベル」モードでは、入力イネーブルがハイレベルのときに、入力や通常動作が行われます。「IENの立ち下がり変化」モードでは、IENの立ち下がり変化後のクロックの最初の立ち上がりエッジで、通常動作が行われます。同様に、「IENの立ち上がり変化」モードでは、IENの立ち上がり変化後のクロックの立ち上がりエッジで、動作が行われます。入力イネーブル・モードの設定の詳細については、「数値制御発振器」のセクションを参照してください。「ブランク・オンIENロー」モードでは、IENがローレベルのときに、入力データはゼロと解釈されます。

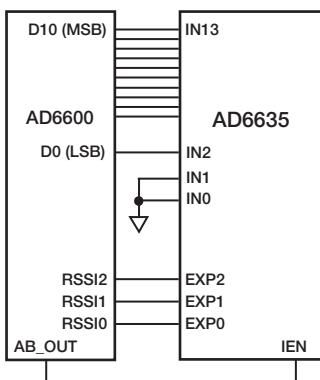

入力モードの代表的なアプリケーションでは、AD6600ダイバーシティADCからAD6635の入力の1つにデータを取り込みます。そのチップからのA/B\_OUTは、対応する入力ポートのIENに接続されます。次に、「IENの立ち下がり変化」が有効になるように、AD6635内の1つのチャンネルが設定されます。さらに、「IENの立ち上がり変化」が有効になるように、もう1つのチャンネルも設定されます。これによって、AD6620をダイバーシティ・モードでエミュレートし、インターリープされた入力データを受信するようにAD6635の2チャンネルを設定できます。NCO周波数やその他のチャンネル特性も同様に設定する必要がありますが、この機能によって、AD6635は、AD6600の場合のようにインターリープされたデータ・ストリームを処理できるようになります。

「IENの立ち上がり変化」と「IENハイレベル」との違いが明らかになるのは、コンバータのデータ・レートより高いシステム・クロックが供給されたときです。データ・レートより高速なクロックを供給すれば、計算できるフィルタ・タップの数を増やすことができます。これによって、優れたフィルタリング効果が得られます。回路の他の部分が高速なクロックを簡単かつ適切に認識できるように、「IENの立ち下がり変化」や「IENの立ち上がり変化」を使用してください。このモードでは、セットアップ・タイムとホールド・タイムを満足する最初のクロック・エッジだけが入力データのラッチと処理に使用されます。フロントエンド処理では、他のすべてのクロック・パルスが無視されます。ただし、各クロック・サイクルで、引き続き新しいフィルタ計算ペアが生成されます。

## ゲイン・スイッチング

AD6635には、ダイナミックレンジが広いアプリケーションや、ゲイン・レンジング・コンバータを使用するアプリケーションに便利な回路が内蔵されています。この回路では、上限と下限のスレッショールドをプログラムできるように、デジタル・スレッショールドを設定できます。

# AD6635

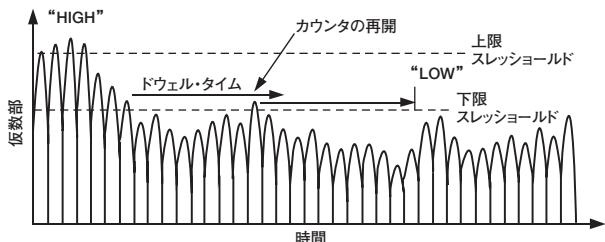

この機能の用途の1つは、特定の入力条件で、ADCがいつフルスケールに到達しようとしているかを検出することです。その結果として提供されるフラグを使用すれば、ADCのオーバーホーリーを防止する減衰器をすばやく挿入できます。18dB（または他の任意の値）の減衰を与えた場合には、システムの信号ダイナミックレンジは18dBだけ増えます。このプロセスは、設定された上限スレッショールドに入力信号が到達したときに開始されます。代表的なアプリケーションでは、これはフルスケールより1dB（ユーザー定義可能）下に設定されます。この入力条件を満足すると、対応する入力ポート（A～D）に関連する適切なLI信号（LIA-A、LIB-A、LIC-A、またはLID-A）がアクティブになります。これを使用して、外部回路のゲインや減衰量を切り替えることができます。LIラインは、入力条件が設定された下限スレッショールドを下回るまで、アクティブのままであります。ヒステリシスを与えるときは、ドウェル・タイム・レジスタ（入力コントロール・レジスタのメモリ・マップを参照）を使用して、あらかじめ決められたクロック数だけ、制御ラインの切り替えを阻止することができます。入力条件が下限スレッショールドを下回ると、プログラマブル・カウンタが高速クロックのカウントを開始します。設定された高速クロック・サイクル数の間、入力信号が下限スレッショールドを下回る限り、減衰器はターミナル・カウントで除去されます。しかし、カウンタの動作中に入力条件が下限スレッショールドを上回った場合には、カウンタがリセットされ、プロセスを開始するには、入力が下限スレッショールドを再び下回る必要があります。これによって、不必要的状態切り替えを防止できます。

これを図26に示します。入力信号が上限スレッショールドを上回ると、適切なLI信号がアクティブになります。信号が下限スレッショールドを下回ると、カウンタがカウントを開始します。入力条件が下限スレッショールドを上回った場合には、カウンタがリセットされ、図に示すように動作を再開します。カウンタが0まで達すると、LIラインは非アクティブになります。

図26. LIのスレッショールド設定

LIラインはさまざまな機能に使用できます。たとえば、減衰器DVGAの制御設定に使用したり、アナログVGAと組み合わせて使用することも可能です。この機能を簡単に使用するため、AD6635には2つの独立したゲイン設定が組み込まれています。その1つは、このLIラインが非アクティブ（0x92レジスタのビット9:5に格納されたrCIC2\_QUIET[4:0]）のときに動作し、もう1つはアクティブ（0x92レジスタのビット4:0に格納されたrCIC2\_LOUD[4:0]）のときに動作します。これによって、外部変化に合わせてデジタル・ゲインを調整できます。ゲイン設定と組み合わせて、ADCのパイプライン遅延とゲイン制御エレメントのスイッチング時間を補償するために、可変ホールドオフ機能が内蔵されています。これらの2つの機能を組み合わせて、スムーズなゲイン・スイッチングが可能になります。

このピンのもう1つの用途は、ゲイン・レンジングADCの内部で、ゲイン・レンジのホールドオフを可能にすることです。ゲイン・レンジングを使用してトータルな信号ダイナミックレンジを拡張するコンバータでは、場合によっては、内部ゲイン・

レンジングの実行を禁止する方がよいことがあります。このようなコンバータでは、LI（AまたはB）ラインを使用して、この機能を阻止することができます。このアプリケーションでは、上限スレッショールドを類似の基準で設定します。しかし、下限スレッショールドには、特定のコンバータのゲイン・レンジと整合するレベルを設定します。これによって、減衰プロファイル、信号のピーク対平均比、または不必要的ゲイン変化を招くその他の時間ベースの特性など、多くの要因に合わせてホールドオフ遅延を適切に設定できます。

AD6635には、すべてのチャンネルをサポートするために、合計で8つのゲイン制御回路があります。したがって、すべての入力ポートにインターリープされたデータがある場合にも使用できます。データが特定の入力ポートでインターリープされる場合、ゲイン・レンジ・コントロール・レジスタで適切なビットをセットしてください。こうすれば、インターリープされた両方のチャンネル・データを監視することができ、対応する入力ポートA～Dに関連付けられたLIA-B、LIB-B、LIC-B、LID-Bピンがインターリープされたチャンネルの出力インジケータとして機能します。このモードでは、LIX-AピンがIEN<sub>X</sub>ローレベルに対応する入力データのインジケータとして機能し、LIX-BはIEN<sub>X</sub>ハイレベルに対応する入力データのインジケータとして機能します。インターリープされたチャンネルを使用しない場合、LIX-Bピンは、LIX-Aピンを補足して、反対の極性を持つインジケータとして機能します。なお、ゲイン制御回路は広帯域であり、ループ遅延を最小限に抑えるために、フィルタ・エレメントに先立って実装されます。

このチップは、LI信号に関連付けられた減衰に基づいて、内部データの適切なスケーリング機能も提供します。このように、DSPへのデータは、プロセスの全体にわたって正しいスケール値を維持するので、完全に独立したデータとなります。通常、外部のゲイン・スイッチング部品には固有の有限遅延が存在しますが、AD6635に内蔵されている可変パイプライン遅延を使用すれば、外部パイプライン遅延や、ゲイン/減衰器デバイスに伴う総セトリング時間を補償することができます。この遅延は、最大7つの高速クロックに対して設定できます。これらの機能によって、ゲイン設定間でのスムーズなスイッチングが可能になります。

## 入力データのスケーリング

AD6635には4つのデータ入力ポートがあります。各データ入力ポートは、14ビットの仮数部（2の補数整数）IN[13:0]、3ビットの指数部（符号なし整数）EXP[2:0]、入力イネーブル（IEN）を受け付けます。入力ポートAとBはCLK0によってクロック駆動され、入力ポートCとDはCLK1によってクロック駆動されます。これらのピンを使用すれば、AD6600などのゲイン・レンジングADCだけでなく、AD9238やAD6645などの標準の固定小数点ADCにも直接にインターフェースをとることができます。14ビット未満のADCによる通常動作では、アクティブ・ビットをMSB側に寄せて、未使用のLSBをローレベルに接続してください。

3ビットの指数部EXP[2:0]は、符号なし整数と解釈されます。その後、この指数部は、LIラインがアクティブかどうかに応じて、rCIC2\_LOUD[4:0]またはrCIC2\_QUIET[4:0]によって修飾されます。この5ビットのスケール値は、rCIC2スケール・レジスタ（0x92）に格納され、データがrCIC2リサンプリング・フィルタに入る前にスケーリングが適用されます。この5ビット・レジスタには、rCIC2ゲイン、外部減衰器（使用される場合）、指数部オフセット（ExpOff）を補償するためのスケール値が含まれています。外部減衰器を使用しない場合には、rCIC2\_QUIETレジスタとrCIC2\_LOUDレジスタには同じ値が入ります。詳細な説明と、減衰スケール・レジスタを設定する

数式については、「浮動小数点ADCによるスケーリング」のセクションを参照してください。

#### 固定小数点ADCによるスケーリング

固定小数点ADCでは一般にAD6635の指数部入力EXP[2:0]を使用しない場合、ローに接続してください。ADC出力を、MSB側に寄せて、AD6635の入力に直接接続します。0x92のExpOffビットは、0に設定してください。同様に、指数部反転ビットも0にしてください。固定小数点ADCでは一般に指数部はスタティックであり、AD6635で入力スケーリングを使用しません。

図27. AD6645固定小数点ADCとAD6635との代表的な接続例

浮動小数点またはゲイン・レンジングADCによるスケーリング指數部制御機能の1つの例として、AD6600とAD6635を組み合わせるものがあります。AD6600は、3ビットのゲイン・レンジングがある11ビットのADCです。実際に、11ビットのADCが仮数部を提供するほか、指數部に3ビットの相対信号強度インジケータ (RSSI) を提供します。AD6600で使用するのは、使用可能な8つの段のうち5つだけです。詳細については、AD6600のデータシートを参照してください。

AD6600などのゲイン・レンジングADCでは、次の式が成立します。

$$scaled\_input = in \times 2^{-mod(7-Exp+rCIC2, 32)}$$

ExpInv=1、ExpWeight=0

ここで、INはIN[13:0]の値、ExpはEXP[2:0]の値、rCIC2はrCICスケール・レジスタ値 (0x92のビット9~5と4~0) です。modは剰余関数です。たとえば、mod(1, 32)=1、mod(2, 32)=2、mod(34, 32)=2となります。

AD6600のRSSI出力は、アナログ入力の信号強度の増加につれて増加します（大信号ではRSSI=5、小信号ではRSSI=0）。指數部反転ビット (ExpInv) がゼロに設定されると、AD6635では、IN[13:0]での最小信号を最大値と見なします。そしてEXPワードが増大するにつれて、データを内部的にシフト・ダウンします（EXP=5では、14ビット・ワードを右側に内部5ビットだけシフトしてから、データをrCIC2に渡します）。この例で、ExpInv=0の場合、AD6635は、RSSI[2:0]=5をAD6600での最小信号、RSSI[2:0]=0を最大信号と見なします。したがって、指數部反転ビットを使用すれば、AD6635の指數部をAD6600のRSSIと一致させることができます。ExpInv=1に設定すると、AD6635では、EXPの増大に対してデータを（シフト・ダウントではなく）シフト・アップ（左シフト）します。AD6600で使用するためには、指數部反転ビットを常にハイレベルに設定してください。

指數部オフセットは、データをシフト・アップするために使用されます。たとえば、表Iに示すように、rCIC2スケーリングがない場合、ADC入力が最大レベルのときに12dBのレンジが失われます。そうすると、量子化ノイズ・フロアに比べて対象となる信号が小さくなり、システムのS/N比とダイナミックレンジが低下するので、これは望ましいことではありません。

表I. AD6600の伝達関数

(AD6635のExpInv=1でExpOffなしの場合)

| ADC入力<br>レベル | AD6600<br>RSSI[2:0] | AD6635<br>データ | 信号の損失<br>(dB) |

|--------------|---------------------|---------------|---------------|

| 最大           | 101 (5)             | /4 (>>2)      | -12           |

|              | 100 (4)             | /8 (>>3)      | -18           |

|              | 011 (3)             | /16 (>>4)     | -24           |

|              | 010 (2)             | /32 (>>5)     | -30           |

|              | 001 (1)             | /64 (>>6)     | -36           |

|              | 000 (0)             | /128 (>>7)    | -42           |

(ExpInv=1、rCIC2スケール=0)

フルスケールADC信号のこのような自動減衰を回避するため、ExpOffを使用して、最大信号 (RSSI=5) をダウンシフトがないポイントまで移動させます。つまり、指數部反転ビットが設定されたら、 $mod(7-5+ExpOff, 32)=0$ になるように、指數部オフセットを調整します。 $mod(32, 32)=0$ であるため、これは、指數部オフセットが30に設定された場合に該当します。表IIには、AD6600 ADCを使用する場合のExpInvとExpOffの使い方を示します。

表II. AD6600の伝達関数

(AD6620のExpInv=1でExpOff=30の場合)

| ADC入力<br>レベル | AD6600<br>RSSI[2:0] | AD6635<br>データ | 信号の損失<br>(dB) |

|--------------|---------------------|---------------|---------------|

| 最大           | 101 (5)             | /1(>>0)       | 0             |

|              | 100 (4)             | /2(>>1)       | -6            |

|              | 011 (3)             | /4 (>>2)      | -12           |

|              | 010 (2)             | /8 (>>3)      | -18           |

|              | 001 (1)             | /16 (>>4)     | -24           |

|              | 000 (0)             | /32 (>>5)     | -30           |

(ExpInv=1、ExpOff=30、Exp Weight=0)

指數部をこのように柔軟に処理できるため、AD6635は、AD6600以外のゲイン・レンジングADCともインターフェースをとることができます。指數部オフセットの調整によって、最大7つのRSSI (EXP) レンジを使用できます (AD6600では5つ)。また、AD6600を使用するシステムでAD6635を調整することもできますが、その信号レンジのすべてを利用するわけではありません。たとえば、最初の4つのRSSIレンジだけが必要な場合には、ExpOffを29に調整し、RSSI=4をAD6635の0dBポイントに対応させることができます。

なお、rCIC2レジスタで設定された上記のスケール係数は、必要なExpOffだけを考慮したものです。このレジスタでは、補償rCIC2フィルタ・ゲインも考慮する必要があります。このために必要な値については、CIC2フィルタのセクションを参照してください。したがって、rCIC2レジスタで設定される最終値は、必要なExpOffとrCIC2スケールの合計となります。

# AD6635

図28. AD6600ゲイン・レンジングADCとAD6635の代表的な接続例

## 数値制御発振器

### 周波数変換

この処理段は、2つの乗算器と32ビットの複素数NCOを含むデジタル・チューナで構成されます。AD6635の各チャンネルには独立したNCOがあります。このNCOは、複素数モードで、 $CLK/2^{32}$ の分解能で $-CLK/2 \sim +CLK/2$ の範囲のNCO周波数を生成できる直交ローカル発振器として機能します。最悪の場合でもNCOからのスプリアス信号は、すべての出力周波数で $-100dBc$ よりも小さくなります。

レジスタ0x85と0x86のNCO周波数値は、32ビットの符号なし整数と解釈されます。NCO周波数は、次式を使用して計算します。

$$NCO\_FREQ = 2^{32} \times \text{mod} \left( \frac{f_{CHANNEL}}{CLKn}, 1 \right)$$

ここで、 $NCO\_FREQ$ は、目標周波数 $f_{CHANNEL}$ に合わせるためにユーザーが設定しなければならない32ビット整数です（レジスタ0x85と0x86）。 $CLKn$ は、使用する入力イネーブル・モードに応じて、AD6635のマスター・クロック・レートまたは入力データ・レートになります。どの場合に $CLK$ または入力データ・レートになるかについては、「入力イネーブル制御」のセクションを参照してください。チャンネル0~3には $CLK0$ を使用し、チャンネル4~7には $CLK1$ を使用します。

$\text{mod}$ は剩余関数に似ています。たとえば、 $f_{CHANNEL}=220MHz$ で $CLK=80MHz$ の場合には、 $\text{mod}(220/80, 1)=\text{mod}(2.75, 1)=0.75$ になります。

しかし、たとえば、負の周波数の場合には、以下のようになります。

$$\text{mod}(-220/80, 1)=\text{mod}(-1.75, 1)=0.25$$

この定義は、 $NCO\_FREQ$ レジスタが符号付き数値として扱われる場合に有効です。

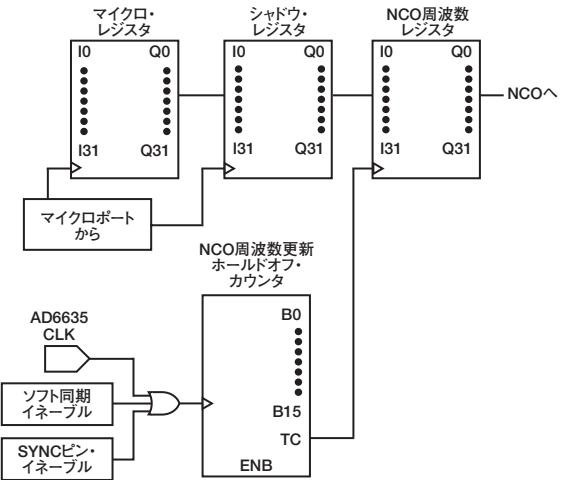

### NCO周波数ホールドオフ・レジスタ

NCO周波数レジスタが書き込まれると、データは実際にはシャドウ・レジスタに渡されます。データがメイン・レジスタに移動するのは、チャンネルがスリープ・モードから出たとき、またはSYNCホップが発生したときです。いずれの場合も、カウンタにはNCO周波数ホールドオフ・レジスタの値をロードできます。マスター・クロックからクロック駆動される16ビットの符号なし整数カウンタ（0x84）がカウント・ダウンを開始し、ゼロに達すると、シャドウ・レジスタ内の新しい周波数値がNCO周波数レジスタに書き込まれます。NCOは、すぐにSYNCに設定することもできます。その場合、周波数ホールド

オフ・カウンタがバイパス（値1を書き込む）され、新しい周波数値が直ちに更新されます。ゼロが書き込まれた場合には、SYNCは発生しません。

### 位相オフセット

位相オフセット・レジスタ（0x87）は、NCOの位相アキュムレータにオフセットを加算します。START SYNCの場合、このレジスタの値でNCO位相アキュムレータが開始します。これは16ビット・レジスタであり、16ビットの符号なし整数と解釈されます。このレジスタの0x0000は0ラジアンのオフセットに対応し、0xFFFFは $2\pi \times (1-1/(2^{16}))$ ラジアンのオフセットに対応します。このレジスタを使用すれば、複数のNCOを同期させて、既知の安定した位相差を持つ正弦波を生成できます。

### NCOコントロール・レジスタ

0x88に置かれているNCOコントロール・レジスタは、NCOの機能設定に使用します。NCOの機能は、以下に示すようにチャンネルごとに制御されます。

### バイパス

AD6635のフロントエンドにあるNCOはバイパスできます。バイパス・モードをイネーブルにするには、0x88のビット0をハイレベルに設定します。NCOがバイパスされると、ダウン変換が実行されず、複素数データに対してAD6635のチャンネルが単に実数フィルタとして機能します。これは、A入力をフィルタ内のI信号バスに接続し、B入力をチャンネル0~3のQ信号バスに接続するベースバンド・サンプリング・アプリケーションの場合に便利です。同様に、入力CをI信号バスに接続し、入力Dをチャンネル4~7のQ信号バスに接続します。以前のアナログ段で、もしくは他のデジタル前処理によって、デジタル化された信号がすでにベースバンドに変換されている場合には、この機能を使用するとよいでしょう。

### 位相ディザ

AD6635は、NCOのスプリアス性能を向上させるために、位相ディザ・オプションを提供します。位相ディザをイネーブルにするには、NCOコントロール・レジスタのビット1を設定します。このビットをハイレベルに設定して位相ディザがイネーブルになると、NCOでの位相切り捨てによるスプリアスがランダム化されます。このようなスプリアスからのエネルギーはノイズ・フロアに拡散され、S/N比がごくわずかに減少するものの、スプリアスフリーのダイナミックレンジが増大します。システムで位相ディザを使用するかどうかは、最終的にはシステムの目標に依存します。ノイズ・フロアを若干犠牲にしても低いスプリアスが望ましい場合には、位相ディザを使用してください。低いノイズ・フロアが必要であり、高いスプリアスを許容できる場合や後続の段でフィルタリングできる場合には、位相ディザは必要ありません。

### 振幅ディザ

NCOのスプリアス性能を向上させるため、振幅ディザも使用できます。振幅ディザをイネーブルにするには、ビット2を設定します。振幅ディザは、NCOの角度からカーテシアンへの変換において振幅量子化誤差をランダム化することによって、性能を向上させます。このオプションでは、ノイズ・フロアを若干犠牲にしてスプリアスを減らすことができます。振幅ディザと位相ディザは、一緒に使用したり、個別に使用したり、まったく使用しないこともできます。

### ホップ時の位相アキュムレータのクリア

ビット3を設定すると、周波数ホップの前に、NCO位相アキュムレータがクリアされます。これによって、各ホップでのNCOの位相の整合性が保証されます。NCO位相オフセットは、この設定に影響されず、依然として有効です。位相の連続ホッピングが必要な場合には、このビットをクリアしてください。NCO

位相レジスタの最後の位相が新しい周波数の開始点となります。

#### 入力イネーブル制御

入力イネーブルには、4つの異なる動作モードがあります。各高速入力ポートには、IENラインがあります。4つのフィルタ・チャンネル0~3のどれでも、2つの入力ポートAまたはBからデータを受け取るよう設定できます（「WB入力セレクト」のセクションを参照）。同様に、4つのフィルタ・チャンネル4~7のどれでも、2つの入力ポートCまたはDからデータを受け取るよう設定できます。データに加えて、IENx信号もあります。各フィルタ・チャンネルは、4つのモードのいずれかでIEN信号を処理するよう設定できます。モードのうちの3つは、時分割多重化データ・ストリームに基づいてデータを処理するタイミングに関係します。4番目のモードは、レーダー、ソナー、超音波、TDDに関連する通信など、時分割二重を採用するアプリケーションで使用します。

#### モード00：IENのローレベルでデータをブランク

このモードでは、IENラインがローレベルの間、データがブランク（無効）になります。IENラインがハイレベルの間は、入力クロックの各立ち上がりエッジで新しいデータがストローブされます。IENラインがローレベルになると、入力データがゼロ値に置き換えられます。この間NCOは動作を続け、IENラインが再びハイレベルになったときに、NCO値がIENラインがローレベルにならなかった場合の値になります。このモードには、IENラインがローレベルになったとき、デジタル入力を無効にする効果があります。IENラインがハイレベルの間、バックエンド処理（rCIC2、CIC5、RCF）が継続します。このモードは、時分割多重のアプリケーションに向いています。

#### モード01：IENのハイレベルでクロック入力

このモードでは、IENラインがハイレベルの間、データがクロックに同期してチップに入力されます。IENラインがハイレベルの間は、入力クロックの各立ち上がりエッジで新しいデータがストローブされます。IENラインがローレベルになると、入力データがチャンネルにラッチされなくなり、さらにNCOの進行も停止します。ただし、この間もバックエンド処理（rCIC2、CIC5、RCF）は継続します。このモードの主な用途は、入力サンプル・データ・レートより高速のクロックを用いて、より多くのフィルタ・タップ数を計算できるようにすることです。図29では、入力データはIENがハイレベルの間だけストローブされますが、CLKはデータより4倍速いレートで動作し続けます。

図29. モード01での小数レートの入力タイミング (4×CLK)

#### モード10：IENの立ち上がり変化でクロック入力

このモードでは、IENラインの立ち上がり変化後の最初のクロック・エッジでのみ、データがチップにクロック入力されます。データは最初の有効なクロック・エッジでのみラッチされますが、モード01と同様、バックエンド処理（rCIC2、CIC5、RCF）は与えられた使用可能な各クロックで継続します。NCO位相アキュムレータは、入力クロックごとではなく、新しい入力データ・サンプルごとに1回だけインクリメントされます。

#### モード11：IENの立ち下がり変化でクロック入力

このモードでは、IENラインの立ち下がり変化後の最初のクロック・エッジでのみ、データがチップにクロック入力されます。データは最初の有効なクロック・エッジでのみラッチされますが、モード01と同様、バックエンド処理（rCIC2、CIC5、RCF）は与えられた使用可能な各クロックで継続します。NCO位相アキュムレータは、入力クロックごとではなく、新しい入力データ・サンプルごとに1回だけインクリメントされます。

#### WB入力セレクト

このレジスタのビット6では、信号処理用にどの入力ポートを選択するかを制御します。チャンネル0~3では、このビットをハイレベルにセットすると、入力ポートB（INB、EXPB、IENB）が、選択したAD6635チャンネルに接続されます。このビットをクリアすると、入力ポートA（INA、EXPB、IENA）が、選択したフィルタ・チャンネルに接続されます。同様にチャンネル4~7では、ビット6がセットされると入力ポートDが選択され、このビットがクリアされると入力ポートCが選択されます。

#### 同期セレクト

このレジスタのビット7と8で、選択したチャンネルに対応する外部同期ピンを決めます。AD6635には、SYNCA、SYNCB、SYNCC、SYNCDの4本の同期ピンがあります。任意の同期ピンを、AD6635の8つのレシーバ・チャンネルのいずれにも対応させることができます。さらに、システムが1本の同期信号しか必要としない場合でも、8つのレシーバ・チャンネルのすべてで同じ同期ピンを基準にすることができます。ビット値00でSYNCA、01でSYNCB、10でSYNCC、11でSYNCDをそれぞれ選択します。

#### 2次rCICフィルタ

rCIC2フィルタは、リサンプリング・カスケード積分型2次樹形フィルタです。リサンプラーは、高速クロックを必要としない独自の技術を使って実装されているので、設計が簡素化され消費電力の節約ができます。リサンプラーにより、マスター・クロックと出力データ・レートの間を非整数の関係にできるので、マルチモードのシステムや、あるいは使用するデータ・レートの整数倍でないマスター・クロックを必要とするシステムを簡単に実装できます。

rCIC2では、512までのインターポレーションと4096までのデシメーションが可能です。rCIC2（L）のリサンプリング係数は9ビットの整数です。12ビットのデシメーション係数Mと組み合わせると、総合レート変化は、次式で表される小数値になります。

$$R_{rCIC2} = \frac{L}{M}$$

$$R_{rCIC2} \leq 1$$

唯一の制約は、 $L/M$ が1以下でなければならないことです。これは、rCIC2が1以上のデシメーションを行うことを意味します。

リサンプリングは、入力サンプル・レートをL倍して見かけ上大きくすることで行われ、新しいデータ・サンプルにはゼロ・スタッフィングを使用します。リサンプラーの後に、カスケード積分型2次樹形フィルタが接続されます。フィルタ特性は、小数レート変化（ $L/M$ ）によってのみ決まります。

フィルタは、入力ポートの最大レートである80MHzで信号を処理できます。この段の出力レートは、次式で得られます。

$$f_{SAMP\ 2} = \frac{L_{rCIC\ 2} f_{SAMP}}{M_{rCIC\ 2}}$$

# AD6635

$M_{rCIC2}$ と $L_{rCIC2}$ は、どちらも符号なし整数です。インターポレーション・レート ( $L_{rCIC2}$ ) は1~512、デシメーション ( $M_{rCIC2}$ ) は1~4096の値をとります。この段をバイパスするには、デシメーション/インターポレーションに1/1を設定します。

rCIC2フィルタの周波数応答は、次式で得られます。

$$H(z) = \frac{1}{2^{S_{rCIC2}} \times L_{rCIC2}} \times \left( \frac{1 - \frac{M_{rCIC2}}{L_{rCIC2}} z^{-1}}{1 - z^{-1}} \right)^2$$

$$H(f) = \frac{1}{2^{S_{rCIC2}} \times L_{rCIC2}} \times \left( \frac{\sin \left[ \pi \frac{M_{rCIC2} \times f}{L_{rCIC2} \times f_{SAMP}} \right]}{\sin \left[ \pi \frac{f}{f_{SAMP}} \right]} \right)^2$$

スケール係数 $S_{rCIC2}$ は、プログラマブルな符号なし5ビット値(0~31)で、 $rCIC2$ のゲインを6dB単位で削減できる減衰器として機能します。最適なダイナミックレンジを得るため、 $S_{rCIC2}$ には、オーバーフロー状態を発生させない、できるだけ小さい値(最小の減衰量)を設定してください。これは、次の式を使用すれば、十分に達成できます。ここで、*input\_level*は、AD6635への入力として許容されるフル・スケールの最大値です(通常は1)。 $rCIC2$ スケール係数は、 $rCIC2$ をバイパスするかどうかにかかわらず、常に使用されます。

$$S_{rCIC2} = \text{ceil} \left[ \log_2 \left( \left\lceil \frac{M_{rCIC2} + \text{floor} \left( \frac{M_{rCIC2}}{L_{rCIC2}} \right) \times 2 \times M_{rCIC2} - L_{rCIC2} \times \text{floor} \left( \frac{M_{rCIC2}}{L_{rCIC2}} + 1 \right) } \right\rceil \right) \right]$$

$$OL_{rCIC2} = \frac{(M_{rCIC2})^2}{L_{rCIC2} \times 2^{S_{rCIC2}}} \times \text{input\_level}$$

上式の`ceil`関数は次の整数を表し、`floor`関数は前の整数を表します。たとえば、`ceil(4.5)`は5ですが、`floor(4.5)`は4になります。

(0x92の`rCIC2_LOUD[4:0]`ビット4~0)と(0x92の`rCIC2 QUIET[4:0]`ビット9~5)という2つのスケール・レジスタがあり、 $S_{rCIC2}$ スケール係数を実現するために使用されます。これらのプログラマブルなレジスタに書き込まれる値は、 $S_{rCIC2}$ 、浮動小数点ADCに必要な`ExpOff`('入力ポート'のセクションで説明)、および`LI`(レベル・インジケータ)ピンを使用してアクティブにできる外部減衰量に対する補償の総合計となります。3番目の成分は、`LI`ピンがアクティブかどうかによって異なる値になるため、2つのレジスタ(`rCIC2_LOUD`と`rCIC2 QUIET`)を使用します。これらの成分の総合計は、`rCIC2_LOUD`レジスタと`rCIC2 QUIET`レジスタとして、AD6635に供給されます。レジスタが格納できる最大数は31です。なお、これらのレジスタによって指定されるスケーリングは、AD6635チャンネルの1つの場所だけ(`rCIC2`フィルタの前)で適用されます。

`rCIC2`のゲインと通過帯域ドループは、前述のフィルタ伝達式だけではなく、上の式も使用して計算してください。過剰な通過帯域ドループは、ロールオフの反転によって通過帯域をピギングすることにより、RCF段で補償することができます。

$$\text{scaled\_input} = IN \times 2^{-\text{mod}(Exp + rCIC2, 32)}, \text{ExpInv} = 0$$

$$\text{scaled\_input} = IN \times 2^{-\text{mod}(7 - Exp + rCIC2, 32)}, \text{ExpInv} = 1$$

ここで、`IN`は`INx[13:0]`の値(`x=A, B, C, D`)、`Exp`は`EXPx[2:0]`の値で、`rCIC2`は0x92スケール・レジスタの値です(`LI`ピンに応じて、`rCIC2 QUIET[4:0]`または`rCIC2 LOUD[4:0]`)。

## rCIC2除去比

表IIIに、`rCIC2`段に入力される帯域幅をデータ・レートのパーセント値で示します。この表のデータは、80MHzまでの任意の許容サンプル・レートにスケーリングできます。`rCIC2`、`CIC5`、`RCF`の間でデシメーションをどう分散させるかを決めるツールとして、この表を利用できます。

表III. SSB `rCIC2`のエイリアス除去比 ( $f_{SAMP}=1$ )

帯域幅は $f_{SAMP}$ のパーセント値として表示(入力レート)。

| $M_{rCIC2}/L_{rCIC2}$ | -50dB | -60dB | -70dB | -80dB | -90dB | -100dB |

|-----------------------|-------|-------|-------|-------|-------|--------|

| 2                     | 1.790 | 1.007 | 0.566 | 0.318 | 0.179 | 0.101  |

| 3                     | 1.508 | 0.858 | 0.486 | 0.274 | 0.155 | 0.087  |

| 4                     | 1.217 | 0.696 | 0.395 | 0.223 | 0.126 | 0.071  |

| 5                     | 1.006 | 0.577 | 0.328 | 0.186 | 0.105 | 0.059  |

| 6                     | 0.853 | 0.490 | 0.279 | 0.158 | 0.089 | 0.050  |

| 7                     | 0.739 | 0.425 | 0.242 | 0.137 | 0.077 | 0.044  |

| 8                     | 0.651 | 0.374 | 0.213 | 0.121 | 0.068 | 0.038  |

| 9                     | 0.581 | 0.334 | 0.190 | 0.108 | 0.061 | 0.034  |

| 10                    | 0.525 | 0.302 | 0.172 | 0.097 | 0.055 | 0.031  |

| 11                    | 0.478 | 0.275 | 0.157 | 0.089 | 0.050 | 0.028  |

| 12                    | 0.439 | 0.253 | 0.144 | 0.082 | 0.046 | 0.026  |

| 13                    | 0.406 | 0.234 | 0.133 | 0.075 | 0.043 | 0.024  |

| 14                    | 0.378 | 0.217 | 0.124 | 0.070 | 0.040 | 0.022  |

| 15                    | 0.353 | 0.203 | 0.116 | 0.066 | 0.037 | 0.021  |

| 16                    | 0.331 | 0.190 | 0.109 | 0.061 | 0.035 | 0.020  |

## 例計算

目的: 入力サンプル・レートが10MHzで、 $\pm 7\text{kHz}$ の通過帯域に100dBのエイリアス除去比を必要とするフィルタを実装します。

ソリューション: まず、通過帯域で表されるサンプル・レートのパーセント値を求めます。

$$BW_{FRACTION} = 100 \times \frac{7\text{kHz}}{10\text{MHz}} = 0.07$$

表の右端にある-100dBの列から、クロック・レートの通過帯域パーセント値以上の値を探します。そこから左端の列に進み、対応するレート変化係数( $M_{rCIC2}/L_{rCIC2}$ )を見つけます。表によると、 $M_{rCIC2}/L_{rCIC2}$ が4の場合に、-100dBのエイリアス除去比を持つ周波数は0.071%であり、これは計算値の0.07%より少し大きな値です。したがって、この例では、`rCIC2`レート変化の上限値は4になります。大きな $M_{rCIC2}/L_{rCIC2}$ の値を選択するほど、エイリアス除去比は必要とされる100dBより小さくなります。

4より小さい $M_{rCIC2}/L_{rCIC2}$ を選ぶと、必要な除去比が得られます。ただし、この`rCIC2`段で可能な限り多くデシメーションを行えば、消費電力を最小限に抑えることができます。`rCIC2`でのデシメーションによりデータ・レートが低下するため、後続段での消費電力が減少します。なお、4のデシメーションを決める方法は1つだけではありません。デシメーションが4であることから、L/M比は0.25になります。したがって、L/Mが0.25となる任意の整数の組み合わせ(1/4、2/8、4/16)が有効です。ただし、最適なダイナミックレンジを得るには、最も簡単な比を使う必要があります。たとえば、1/4の方が4/16よりも優れた性能が得られます。

デシメーション・レジスタとインターポレーション・レジスタrCIC2のデシメーション値は、レジスタ0x90に格納されます。これは12ビット・レジスタであり、1より小さいデシメーション部分を格納します。インターポレーション部分は、レジスタ0x91に格納されます。この9ビット値で、1より小さいインターポレーションを保持します。

#### rCIC2スケール

レジスタ0x92は、回路のrCIC2セクションに関するスケーリング情報を格納します。主な機能は、これまでに計算したスケール値を格納することです。

このレジスタのビット4~0 (rCIC2\_LOUD[4:0]) は、信号が強いときのrCIC2のスケーリング係数を格納するために使用します。これらの5ビットは、先に計算したrCIC2スケーラと、減衰器による任意の外部信号スケーリングを表します。

このレジスタのビット9~5 (rCIC2 QUIET[4:0]) は、信号が弱いときのrCIC2のスケーリング係数を格納するために使用します。このレジスタでは外部減衰器を使わないと、外部減衰器は含まれていません。これらのビットには、rCIC2補償に関して先に計算した値だけが格納されます。

このレジスタのビット10は、外部指数部の値を示すために使用します。このビットをローレベルに設定した場合、外部指数部は、AD6600の場合と同様、6dB/段を表します。このビットをハイレベルに設定した場合、各指数部は12dB/段を表します。

このレジスタのビット11は、内部計算の前に外部指数部を反転するために使用します。指数部を増加させて信号レベルの増大を表すゲイン・レンジングADCの場合は、このビットをハイレベルに設定します。指数部を減少させて信号レベルの増大を表すゲイン・レンジングADCの場合は、このビットをローレベルに設定してください。

rCIC2の機能が不要なアプリケーションでは、L/M比を1/1に設定して、バイパスすることができます。この設定により、rCIC2のすべての回路がバイパスされますが、有効なスケーリングはそのままです。

#### 5次CICフィルタ

3番目の信号処理段のCIC5では、rCIC2よりもシャープな固定係数のデシメーション・フィルタを実装します。このフィルタへの入力レートは $f_{SAMP2}$ です。フィルタへの最大入力レートは、AD6635への入力レートと等しくなります。したがって、rCIC2フィルタをバイパスすることができます。

デシメーション比 $M_{CIC5}$ には、2~32 (すべて整数値) の値を設定できます。フィルタの周波数応答は、次式で得られます。これらの式を用いて、CIC5のゲインと通過帯域ドロープを計算する必要があります。どちらのパラメータもRCF段で補償することができます。

$$H(z) = \frac{1}{2^{S_{rCIC5+5}}} \times \left( \frac{1 - z^{-M_{CIC5}}}{1 - z^{-1}} \right)^5$$

$$H(f) = \frac{1}{2^{S_{rCIC5+5}}} \times \left( \frac{\sin\left(\pi \frac{M_{CIC5} \times f}{f_{SAMP2}}\right)}{\sin\left(\pi \frac{f}{f_{SAMP2}}\right)} \right)$$

スケール係数 $S_{CIC5}$ は、プログラマブルな符号なし整数 (0~20) で、データの減衰量を制御して6dB単位でCIC5段に渡す役割があります。最適なダイナミックレンジを得るため、 $S_{CIC5}$ には、オーバーフロー条件を発生させない、できるだけ小さい値 (最

小の減衰量) を設定してください。以下の式を使用すれば、十分にこの値を設定できます。ここで、 $OL_{rCIC2}$ は、このフィルタ段への入力で可能なフル・スケールの最大値です。この値は、rCIC2段から出力され、CIC5にパイプライン入力されます。

$$S_{CIC5} = \text{ceil}(\log_2(M_{CIC5} \times OL_{rCIC2})) - 5$$

$$OL_{CIC5} = \frac{(M_{CIC5})^5}{2^{S_{rCIC5+5}}} \times OL_{rCIC2}$$

この段の出力レートは、以下の式で得られます。

$$f_{SAMP5} = \frac{f_{SAMP2}}{M_{CIC5}}$$

#### CIC5除去比

表IVに、さまざまなデシメーション・レートとエイリアス除去比を指定して保護できる帯域幅をクロック・レート (入力レート) のパーセント値で示します。rCIC2が1のデシメーションを行うとき、CIC5への最大入力レートは80MHzです。前の表と同様に、これがCIC5の1/2帯域幅特性になります。CIC5段では、rCIC2段に比べて、与えられたどの除去レベルについても、はあるかに広い帯域を保護できます。この表は、目標のフィルタ特性が与えられた場合に、デシメーション $M_{CIC5}$ の上限値を計算するのに役立ちます。

表IV. SSB CIC5のエイリアス除去比 ( $f_{SAMP2}=1$ )

帯域幅は $f_{SAMP2}$ のパーセント値として表示。

| $M_{CIC5}$ | -50dB  | -60dB | -70dB | -80dB | -90dB | -100dB |

|------------|--------|-------|-------|-------|-------|--------|

| 2          | 10.227 | 8.078 | 6.393 | 5.066 | 4.008 | 3.183  |

| 3          | 7.924  | 6.367 | 5.110 | 4.107 | 3.297 | 2.642  |

| 4          | 6.213  | 5.022 | 4.057 | 3.271 | 2.636 | 2.121  |

| 5          | 5.068  | 4.107 | 3.326 | 2.687 | 2.170 | 1.748  |

| 6          | 4.267  | 3.463 | 2.808 | 2.270 | 1.836 | 1.480  |

| 7          | 3.680  | 2.989 | 2.425 | 1.962 | 1.588 | 1.281  |

| 8          | 3.233  | 2.627 | 2.133 | 1.726 | 1.397 | 1.128  |

| 9          | 2.881  | 2.342 | 1.902 | 1.540 | 1.247 | 1.007  |

| 10         | 2.598  | 2.113 | 1.716 | 1.390 | 1.125 | 0.909  |

| 11         | 2.365  | 1.924 | 1.563 | 1.266 | 1.025 | 0.828  |

| 12         | 2.170  | 1.765 | 1.435 | 1.162 | 0.941 | 0.760  |

| 13         | 2.005  | 1.631 | 1.326 | 1.074 | 0.870 | 0.703  |

| 14         | 1.863  | 1.516 | 1.232 | 0.998 | 0.809 | 0.653  |

| 15         | 1.740  | 1.416 | 1.151 | 0.932 | 0.755 | 0.610  |

| 16         | 1.632  | 1.328 | 1.079 | 0.874 | 0.708 | 0.572  |

| 17         | 1.536  | 1.250 | 1.016 | 0.823 | 0.667 | 0.539  |

| 18         | 1.451  | 1.181 | 0.960 | 0.778 | 0.630 | 0.509  |

| 19         | 1.375  | 1.119 | 0.910 | 0.737 | 0.597 | 0.483  |

| 20         | 1.307  | 1.064 | 0.865 | 0.701 | 0.568 | 0.459  |

| 21         | 1.245  | 1.013 | 0.824 | 0.667 | 0.541 | 0.437  |

| 22         | 1.188  | 0.967 | 0.786 | 0.637 | 0.516 | 0.417  |

| 23         | 1.137  | 0.925 | 0.752 | 0.610 | 0.494 | 0.399  |

| 24         | 1.090  | 0.887 | 0.721 | 0.584 | 0.474 | 0.383  |

| 25         | 1.046  | 0.852 | 0.692 | 0.561 | 0.455 | 0.367  |

| 26         | 1.006  | 0.819 | 0.666 | 0.540 | 0.437 | 0.353  |

| 27         | 0.969  | 0.789 | 0.641 | 0.520 | 0.421 | 0.340  |

| 28         | 0.934  | 0.761 | 0.618 | 0.501 | 0.406 | 0.328  |

| 29         | 0.902  | 0.734 | 0.597 | 0.484 | 0.392 | 0.317  |

| 30         | 0.872  | 0.710 | 0.577 | 0.468 | 0.379 | 0.306  |

| 31         | 0.844  | 0.687 | 0.559 | 0.453 | 0.367 | 0.297  |

| 32         | 0.818  | 0.666 | 0.541 | 0.439 | 0.355 | 0.287  |

# AD6635

## RAM係数フィルタ

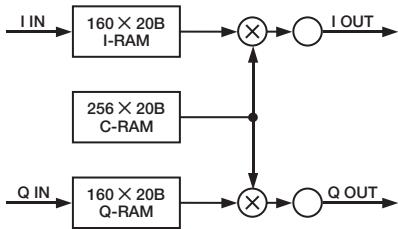

個々のチャンネルの最後の信号処理段は、プログラマブルな係数を持つ積和デシメーション・フィルタです。簡略化したブロック図を次に示します。データ・メモリI-RAMとQ-RAMは、前のフィルタ段から入力される最新の160個の複素数サンプルを20ビット分解能で格納します。係数メモリCMEMは、最大256個の係数を20ビット分解能で格納します。各CLKサイクルで、Iに1タップ、Qに1タップを同じ係数を使って計算します。RCF出力は、24ビットのデータで構成されています。

## RCFデシメーション・レジスタ

各RCFチャンネルを使用して、データ・レートをデシメーションできます。デシメーション・レジスタは、8ビット・レジスタで、1~256のデシメーションが可能です。RCFデシメーションは、 $M_{RCF}-1$ の形で0xA0に格納されます。RCFへの入力レートは $f_{SAMP5}$ です。

## RCFデシメーション位相

RCFデシメーション位相を使用して、チップ内の複数のフィルタを同期化することができます。これは、AD6635内の複数のチャンネルを使用して多相フィルタを実装する場合に有効で、複数のRCFフィルタのリソースを並列に接続できます。このようなアプリケーションでは、2つのRCFフィルタがCIC5からの同一データを処理することになります。ただし、各フィルタはデシメーション・レートの1/2だけ遅延されるため、2つの間に180°の位相差が生じます。

AD6635フィルタ・チャンネルでは、このレジスタに格納されている値を使用して、RCFカウンタをプリロードします。したがって、カウンタは0(係数0)からスタートするのではなく、次の値がロードされます。

$$\text{カウンタ} = \frac{\text{デシメーション位相} \times \text{使用するチャンネル数} \times f_{CLK}}{\text{各チャンネルでのRCFデシメーション} \times f_{RCF}}$$

このようにして、必要な処理遅延に等しいオフセットが処理の中で得られます。上の式では、1つのキャリアの処理に使用されるチャンネルまたはRCFの数が使用されます。 $f_{CLK}$ はAD6635への入力クロック・レート、 $f_{RCF}$ はCIC5段からRCFへの入力サンプル・レートです。このデータは、8ビット値として0xA1に格納されます。RCFデシメーション位相を使用できるのは、RCFデシメーションと使用するRCFの数との比率が整数であるときだけです。

## RCFフィルタ長

このフィルタが計算できる最大タップ数 $N_{TAPS}$ は、次式で得られます。AD6635のアドレス0xA2にあるチャンネル・レジスタには、値 $N_{TAPS}-1$ が書き込まれます。

$$N_{TAPS} \leq \min \left( \frac{f_{CLK} \times M_{RCF}}{f_{SAMP5}}, 160 \right)$$

上で使用する関数minは、かっこ内のすべての式の最小値を意味します。

RCF係数は、アドレス0x00~0x7Fに配置され、20ビットの2の補数値として解釈されます。係数RAMを書き込むと、下位アドレスにはCIC5からの相対的に古いデータが乗算され、係数の上位アドレスにはCIC5からの相対的に新しいデータが乗算されます。係数は対称である必要はなく、係数長 $N_{TAPS}$ は偶数または奇数のいずれでも可能です。係数が対称の場合は、インパルス応答の両側を係数RAMに書き込む必要があります。

係数用のベース・メモリは128ワード長しかありませんが、実際の長さは256ワード長になります。2つのページがあり、それぞれが128ワード長です。ページは0xA4のビット8で選択します。

このデータは複数ページに書き込む必要がありますが、内部コアでは128タップ長を超えるフィルタを処理します。したがって、データRAMの全長をフィルタ長(160タップ)として使用できます。RCFでは160タップのフィルタしか計算できませんが、フィルタ係数メモリは256ワード長であるため、このメモリに複数のフィルタ設定を格納することができ、係数オフセット0xA3レジスタを使用して選択できます。

RCFは、CIC5からのデータを160×40のRAMに格納します。Iデータに160×20、Qデータに160×20が割り当てられます。RCFは、循環バッファとしてRAMを使用するため、特定のデータ・エレメントが格納されているアドレスを知ることは困難です。データRAM値が未定義であるために生じるスタートアップ時の過渡出力を回避するため、初期化時にデータRAMをクリアしてください。

RCFでフィルタ出力の計算が開始されると、まず最初に、データRAM内の最も古い値に、RCF係数オフセット・レジスタ(0xA3)で示される最初の係数が乗算されます。この値に、これより新しいデータ・ワードに係数RAM内の後続する位置の値を乗算した積が累計されます。この操作は、係数アドレスが $RCF_{OFF} + N_{TAPS} - 1$ に達するまで繰り返されます。

## 表V. 3タップ・フィルタ

| 係数アドレス               | インパルス応答 | データ       |

|----------------------|---------|-----------|

| 0                    | h(0)    | N(0)最も古い  |

| 1                    | h(1)    | N(1)      |

| $2 = (N_{TAPS} - 1)$ | h(2)    | N(2)最も新しい |

RCF係数オフセット・レジスタは、2つの目的で使用できます。このレジスタの主な目的は、複数のフィルタをメモリにロードしておき、オフセットをポインタとして変更するだけでフィルタを選択し、フィルタ変更が迅速にできるようにすることです。このレジスタのもう1つの目的は、シンボル・タイミング調整の一部を実行することです。目標フィルタ長の両端にゼロが埋められている場合、高速クロックを基準にしてフィルタを計算するときに、スタート・ポイントを調整してわずかな遅延を発生させることができます。この方法で、シンボル・タイミングの微調整が可能になります。粗調整は、RCFデシメーション位相で行うことができます。

このフィルタの出力レートは、CIC5段の出力レートと $M_{RCF}$ によって求めます。

$$f_{SAMP5} = \frac{f_{SAMP5}}{M_{RCF}}$$

## RCF出力スケール係数とコントロール・レジスタ

レジスタ0xA4は、RCFレジスタのさまざまな項目の設定に使用する複合レジスタです。ビット3~0は、固定小数点出力モードのスケール設定に使用します。このスケール値は、このレジ

スタのビット6と組み合わせて、浮動小数点出力の設定にも使用できます。

ビット4と5では、出力モードを決定します。モード00は、チップを固定小数点モードに設定します。ビット数は、パラレル・ポートまたはリンク・ポートの設定によって決まります。

モード01では、浮動小数点モード8+4を選択します。このモードでは、8ビットの仮数部の後ろに4ビットの指数部が続きます。モード1x (xは任意) では、モードは12+4、つまり12ビットの仮数部と4ビットの指数部になります。

表VI. 出力モード・フォーマット

|           |    |

|-----------|----|

| 浮動小数点12+4 | 1x |

| 浮動小数点8+4  | 01 |

| 固定小数点     | 00 |

通常、AD6635は数値の精度を最適化する指数部の値を決定します。ただし、このコントロール・レジスタのビット6がセットされると、ビット3~0に格納されている値によって、出力がスケーリングされます。これにより、予測可能な出力レンジを保証できる条件では、整合性のあるスケーリングと精度が得られます。ビット3~0がRCFスケールによって表される場合、スケーリング係数 (dB単位) は次式で得られます。

$$\text{スケーリング係数} = (\text{RCFスケール} - 3) \times 20 \log_{10}(2) \text{ dB}$$

RCFスケールが0の場合、スケーリング係数は-18.06dBになります、RCFスケールが最大の15の場合、スケーリング係数は72.25dBになります。

このレジスタのビット7がセットされると、同一の指数部が実数と虚数 (IとQ) の両出力に使用されます。使用される指数部の値は数値的にオーバーフローを防止するものですが、小信号の精度は落ちます。ただし、小さな数値は、使用する指数部とは関係なく0を表すため、これが問題になることはほとんどありません。

このレジスタのビット8は、レジスタの設定に使用するRCFバンク・セレクト・ビットです。このビットが0のときには、最下位の128ブロックが選択されます (タップ0~127)。このビットがハイレベルのときには、最上位のブロックが選択されます (タップ128~255)。チップがフィルタを計算している間は、タップ127がタップ128に隣接しているため、ページング問題が発生することはあります。

このレジスタのビット9は、各RCFへ入力するデータの提供元を選択します。ビット9がクリアされている場合、RCF入力は、通常そのRCFに対応しているCIC5から与えられます。チャンネル0~3では、このビットがセットされている場合、CIC5のチャンネル1から入力が与えられます。チャンネル1だけは例外で、CIC5のチャンネル0の出力を代替として使用します。この機能を使用すると、各RCFは、各自のチャンネルのNCO+rCIC2+CIC5のデータで動作したり、チャンネル1のRCFとペアにしたりできます。チャンネル1のRCFは、チャンネル0とペアにすることもできます。この制御ビットは、多相分散型フィルタリングで使用されます。

同様に、チャンネル4~7では、このビットがセットされている場合、CIC5のチャンネル5から入力が与えられます。唯一の例外はチャンネル5であり、CIC5のチャンネル4の出力を代替ソースとして使用します。

ビット10がクリアされている場合、AD6635のチャンネルはノーマル・モードで動作します。しかし、ビット10がセットされている場合、チャンネルBISTを実行するためにRCFはバイパスされます。詳細については、「チャンネルBIST (内蔵セルフ・テスト)」のセクションを参照してください。

なお、RCFの出力は、ポート・コントロール・レジスタの適切な設定を使用して、出力ポート (パラレルまたはリンク) に直接送信できます (出力ポート・コントロール・レジスタのメモリ・マップを参照)。あるいは、複数のチャンネルからのデータを、インターポレーション・ハーフバンド・フィルタとAGCにインターリープできます (たとえハーフバンド・フィルタとAGCがバイパスされても、インターリープ機能は行われます)。この機能によりAD6635の内部でデータをインターリープすれば、複数のチャンネルを使用して单一キャリアを処理できます。

### インターポレーション・ハーフバンド・フィルタ

AD6635には、RCFチャンネル出力と4つのデジタルAGCとの間に、4つのインターポレーション・ハーフバンドFIRフィルタがあります。各インターポレーション・ハーフバンド・フィルタは、先行のRCFからIデータとQデータを受け取り、IデータとQデータをAGCに出力します。ハーフバンド・フィルタとAGCは、互いに独立して動作するため、AGCをバイパスすることができます。その場合、ハーフバンド・フィルタの出力は、出力データ・ポートに直接に送信されます。これらのハーフバンド・フィルタも互いに独立して動作するので、ハーフバンド・コントロール・レジスタを使用して、どれでもイネーブル/ディスエーブルにできます。

ハーフバンド・フィルタでは、インターポレーションが実際に機能する前に、さまざまなRCFチャンネル出力からのデータをインターリープする機能も実行します。データのインターリープ機能は、ハーフバンド・フィルタの実際の機能がバイパスされている場合も利用できます。この機能により、AD6635上で複数のチャンネル (多相フィルタを実装) を使用して、单一キャリアを処理できます。チャンネルの位相を正しく調整するには、RCF位相デシメーションを使用したり、チャンネルのスタート・ホールドオフ・カウンタを使用します。たとえば、cdma2000の1つのキャリアを処理するために、AD6635の2つのチャンネルが使用される場合、両チャンネルのRCFフィルタの位相を180°ずらしてください。それには、RCF位相デシメーションまたは適切なスタート・ホールドオフ・カウンタに統いて、適切なNCO位相オフセットを使用してください。

ハーフバンド・フィルタAは、チャンネル0~3、チャンネル0と1、またはチャンネル0だけを待ち受けることができます。ハーフバンド・フィルタBは、チャンネル2と3、またはチャンネル2だけを待ち受けることができます。各ハーフバンド・フィルタは、コントロール・レジスタで指定されたチャンネルをインターリープします。インターリープされたデータは前述のように組み合わせられ、2で補間されます。インターリープ機能は、インターポレーション機能とは独立に使用できます。その場合、ハーフバンド・フィルタは、ハーフバンド・コントロール・レジスタを使用してバイパスされます。ハーフバンド・フィルタがバイパスされても、インターリープ機能はまだ実行されます。チップ・レートの2倍のレートで動作するチャンネルの場合、ハーフバンド・フィルタを使用すれば、チップ・レート×4でチャンネル・データを出力できます。

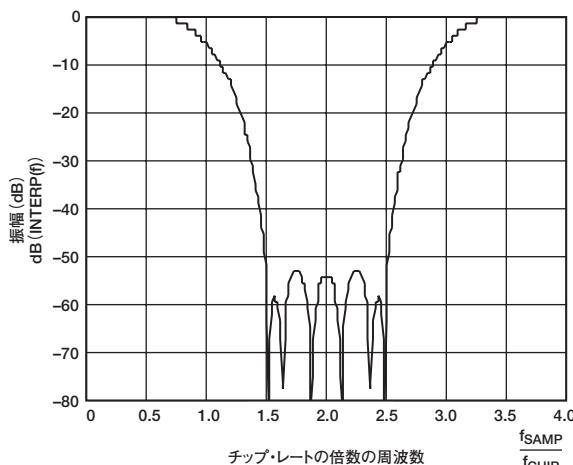

図31には、チップ・レートを基準とするインターポレーション・ハーフバンドFIRフィルタの周波数応答を示します。

# AD6635

図31. インターポレーション・ハーフバンド・フィルタの周波数応答

インターポレーション・ハーフバンド・フィルタのS/N比は、約149.6dBです。固定小数点演算による最大スプリアス誤差は、約-172.9dBです。表VIIに、13タップのインターポレーション・ハーフバンドFIRフィルタの係数を示します。

表VII. ハーフバンド係数

|     |

|-----|

| 0   |

| 14  |

| 0   |

| -66 |

| 0   |

| 309 |

| 512 |

| 309 |

| 0   |

| -66 |

| 0   |

| 14  |

| 0   |

## 自動ゲイン制御

AD6635には、RAKEレシーバに直接インターフェースがとれるように、4つの独立した自動ゲイン制御（AGC）ループがあります。各AGC回路は96dBのレンジを許容します。各AGCループが対象のキャリアでのみ動作し、周波数の異なるキャリアによってループのレンジングが影響されないようにするために、AGCの手前でAD6635のデシメーション・フィルタによって不要な信号を除去することが大切です。

AGCは、インターポレーション・ハーフバンド・フィルタからの23ビットの複素数出力を、4~8、10、12、または16ビットのプログラマブルなワード・サイズに圧縮します。ゲインを加えることで、下位ビットからの小信号が上位ビットに押し上げられるので、下位ビットのクリッピングが対象信号のS/N比を損うことはありません。AGCによって、対象信号のレベルに関係なく、出力上で一定の平均電力が維持されるため、信号のダイナミックレンジが出力分解能のダイナミックレンジを超える環境でも動作できます。

AGCとインターポレーション・フィルタは、互いに拘束されていません。1つのフィルタを他方のフィルタとは別に利用することも、両方のフィルタを利用することもできます。AGCセクションは、AGC制御ワードのビット0をセットすることにより、必要に応じてバイパスできます。バイパスした場合、I/Qデータは、16ビットI/Qデータへのクリッピングの後で、出力ポートに渡されます。

AGC機能によって生じる誤差には、アンダーフロー、オーバーフロー、変調の3つの原因があります。アンダーフローは、出力レンジを下回るビットの切り捨てが原因です。オーバーフローは、出力信号が出力レンジを上回る場合のクリッピング誤差が原因です。変調誤差は、データの受信中に出力ゲインが変動する場合に発生します。

目標信号レベルは、アンダーフローとオーバーフローによる誤差のバランスがとれるように、信号の確率密度関数に基づいて設定してください。ループ・フィルタのゲインと減衰の値は、AGCが過剰なアンダーフロー やオーバーフローを引き起こす信号の長期的な振幅変化を追跡できる程度に高速で、しかも信号の変調によって生じる振幅情報の過剰な損失が生じない程度に低速であるように設定してください。

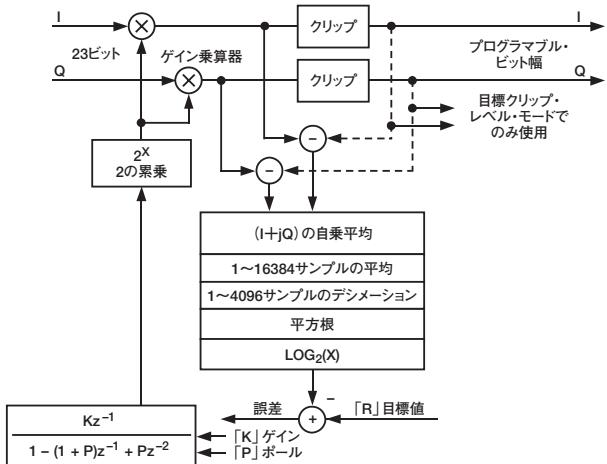

## AGCループ

AGCループは、ログリニア・アーキテクチャを使用して実現されます。これには、累乗計算、誤差計算、ループ・フィルタリング、ゲイン乗算の4つの基本動作があります。

AGCは、AGC制御ワード（0x0A、0x12）のビット4をセットすることで、「目標信号レベル」モードまたは「目標クリップ・レベル」モードのいずれかで動作するよう設定できます。AGCは、選択した動作モードに応じて、所定の目標信号レベルまたは目標クリップ・レベルからの差に基づいて、着信データのゲインを調整します。AGCループへのデータ・パスは2つあります。図32に示すように、クリップ回路の前と後に1つずつです。目標信号レベル・モードでは、クリップ回路の前のI/Qパスだけが使用されます。目標クリップ・レベル・モードでは、クリップ回路の前後のI/Q信号の差分が使用されます。

## 目標信号レベル・モード

この動作モードでは、AGCは、プログラマブルな設定レベルで出力信号を維持するように動作します。この動作モードを選択するには、AGC制御ワード（0x0A、0x12）のビット4に値ゼロを書き込みます。最初に、ループは、IとQをそれぞれ2乗したものを加算することで、複素数の着信データ信号の2乗（つまり累乗）を求めます。この動作は、 $2^x$ （2の累乗）を使用して指数部領域で実行されます。

AGCループには、平均/デシメーション・ブロックがあります。この平均/デシメーション演算は、平方根演算の前に累乗サンプルに対して行われます。このブロックをプログラムして1~16384の累乗サンプルの平均を計算し、デシメーション・セクションをプログラムして1~4096のサンプルごとに1回AGCを更新することができます。平均演算には、平均する累乗サンプルの数をデシメーション値の倍数（1、2、3、4倍）にするという制限があります。

平均とデシメーションの演算は、AGCが実質的に1~16384の出力サンプルの累乗平均に対して動作できることを意味します。1~4096のサンプルごとに1回AGCを更新し、平均累乗の処理を選択すれば、AGC誤差がゆっくり収束してゲイン調整があまり行われない遅い時定数のループ・フィルタを実装できるようになります。また、データのフレーム（またはシンボルのストリーム）全体にわたってゲイン・スケーリングを一定に保ちたい場合にも役立ちます。

図32. AGCのブロック図

平均サンプルの数をデシメーション値の倍数にするという制限により、プログラム可能な倍数は1、2、3、または4だけになります。この数値は、0x10および0x18レジスタのビット1、0で設定します。次にこれらの平均サンプルに、プログラムブルな1~4096のデシメーション率でデシメーションを行います。デシメーション率は、12ビットのレジスタ0x11と0x19で設定します。

平均とデシメーションの演算は組み合わせになっていて、1次CICフィルタといくつかのFIFOレジスタを使用して実行されます。CICフィルタにはゲインとビットの増大が伴いますが、これらはデシメーション率に依存します。演算に伴うゲインを補償するために、CICフィルタの前に減衰スケーリングが設けられています。

スケーリング演算が行われるのは、平均演算に伴う除算、およびCICフィルタにおける一般的なビット増大があるためです。これはビットのシフト演算によって行われるため、粗いスケーリングしかできません。細かいスケーリングは、後で説明するリクエスト・レベルのオフセットで実現できます。減衰スケーリング( $S_{CIC}$ )は、 $0x10$ および $0x18$ レジスタの4つのビットを使用し、 $0\sim14$ の範囲で設定でき、次の式で得られます。