## 特長

52 ピン LQFP パッケージまたは 56 ピン LFCSP パッケージを採用した 8 チャンネル DAC

16/14 ビットの単調性を保証

公称出力電圧範囲: -10 V ~ +10 V

複数の出力電圧振幅が使用可能

サーマル・シャットダウン機能

チャンネル・モニタリング・マルチブレクサ

GPIO 機能

システム・キャリブレーション機能によりオフセットとゲインをユーザー設定可能

チャンネルのグルーピング機能とアドレッシング機能

データ・エラー・チェック機能

SPI 互換シリアル・インターフェース

2.5 V ~ 5.5 V のデジタル・インターフェース

デジタル・リセット(RESET)

ユーザー定義の SIGGNDx に対するクリア機能

DAC 出力の同時更新

## アプリケーション

計測機器

工業用制御システム

自動テスト装置(ATE)のレベル設定

可変光減衰器(VOA)

光ライン・カード

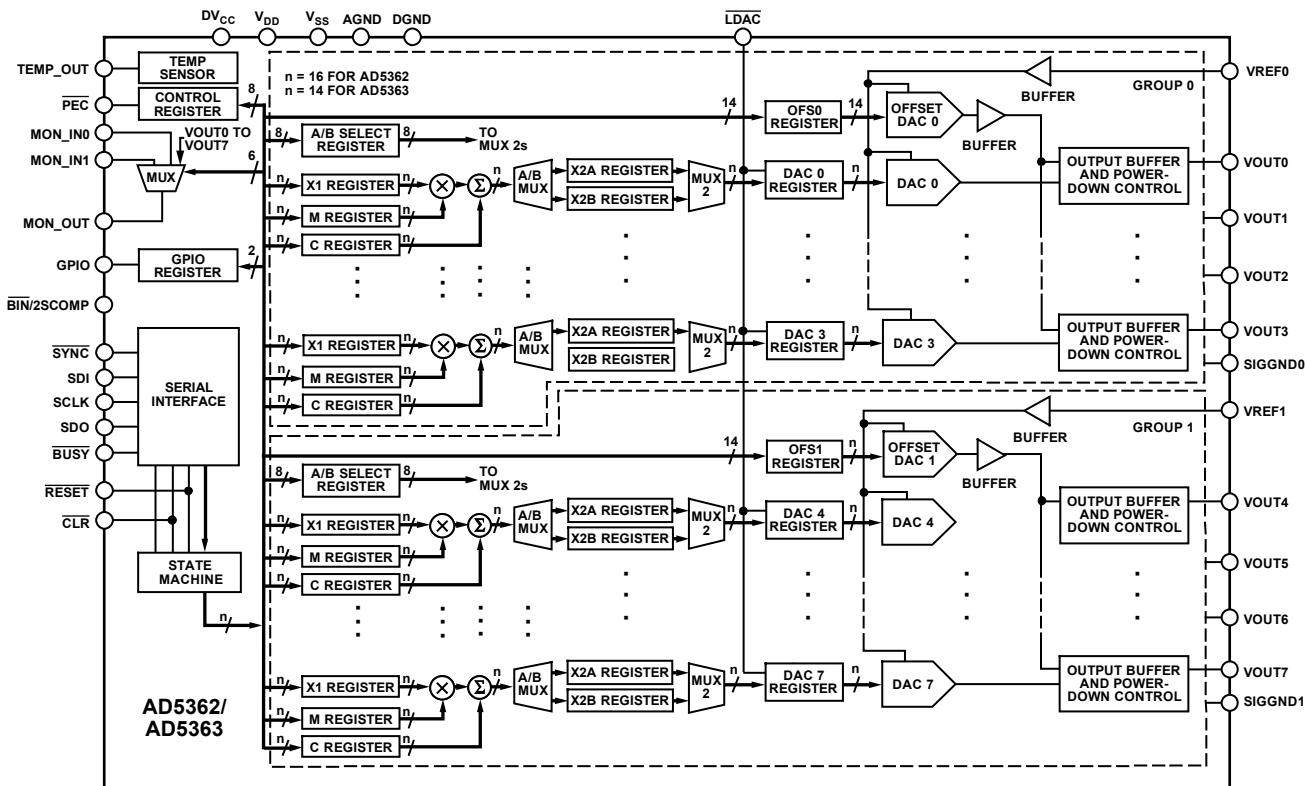

## 機能ブロック図

図 1

05762.001

03

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                       |    |

|-----------------------|----|

| 特長                    | 1  |

| アプリケーション              | 1  |

| 機能ブロック図               | 1  |

| 改訂履歴                  | 2  |

| 概要                    | 3  |

| 仕様                    | 4  |

| AC 特性                 | 6  |

| タイミング特性               | 7  |

| 絶対最大定格                | 10 |

| ESD に関する注意            | 10 |

| ピン配置およびピン機能説明         | 11 |

| 代表的な性能特性              | 13 |

| 用語                    | 15 |

| 動作原理                  | 16 |

| DAC アーキテクチャ           | 16 |

| チャンネル・グループ            | 16 |

| A/B レジスタとゲイン/オフセットの調整 | 17 |

| オフセット DAC             | 17 |

| 出力アンプ                 | 17 |

| 伝達関数                  | 18 |

| リファランスの選択             | 18 |

| キャリブレーション             | 19 |

| その他のキャリブレーション         | 19 |

| リセット機能                | 20 |

## 改訂履歴

### 3/08—Rev. 0 to Rev. A

|                                                             |           |

|-------------------------------------------------------------|-----------|

| Added 56-Lead LFCSP_VQ.                                     | Universal |

| Changes to Table 2                                          | 4         |

| Added $t_{23}$ Parameter                                    | 7         |

| Changes to 図 4                                              | 8         |

| Changes to Table 6                                          | 11        |

| Changes to A/B Registers and Gain/Offset Adjustment Section | 17        |

|                         |    |

|-------------------------|----|

| クリア機能                   | 20 |

| BUSY 機能と LDAC 機能        | 20 |

| BIN/2SCOMP ピン           | 20 |

| 温度センサー                  | 20 |

| モニター機能                  | 21 |

| GPIO ピン                 | 21 |

| パワーダウン・モード              | 21 |

| サーマル・シャットダウン機能          | 21 |

| トグル・モード                 | 21 |

| シリアル・インターフェース           | 22 |

| SPI 書き込みモード             | 22 |

| SPI リードバック・モード          | 22 |

| レジスタ更新レート               | 22 |

| パケット・エラーのチェック           | 23 |

| チャンネル・アドレッシングとスペシャル・モード | 23 |

| スペシャル・ファンクション・モード       | 24 |

| アプリケーション情報              | 26 |

| 電源デカッピング                | 26 |

| 電源シーケンシング               | 26 |

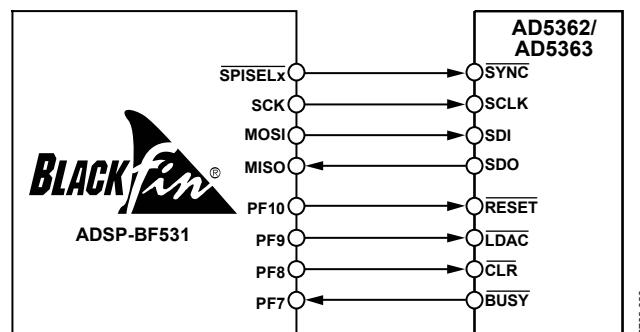

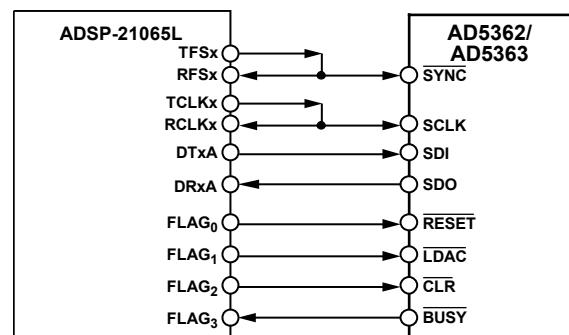

| インターフェース例               | 26 |

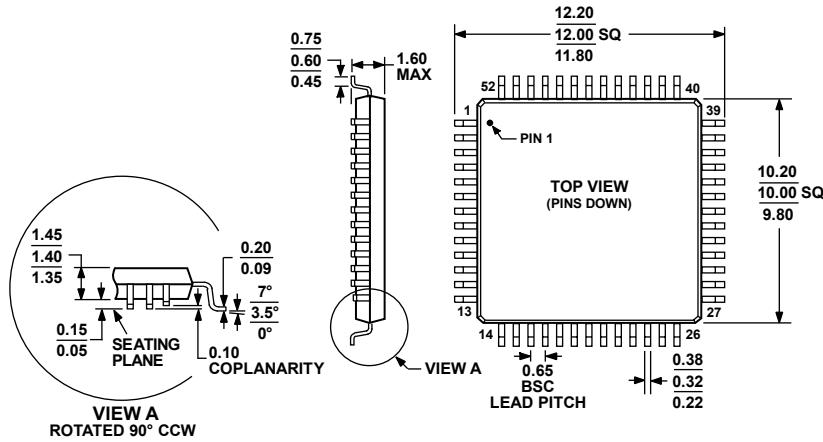

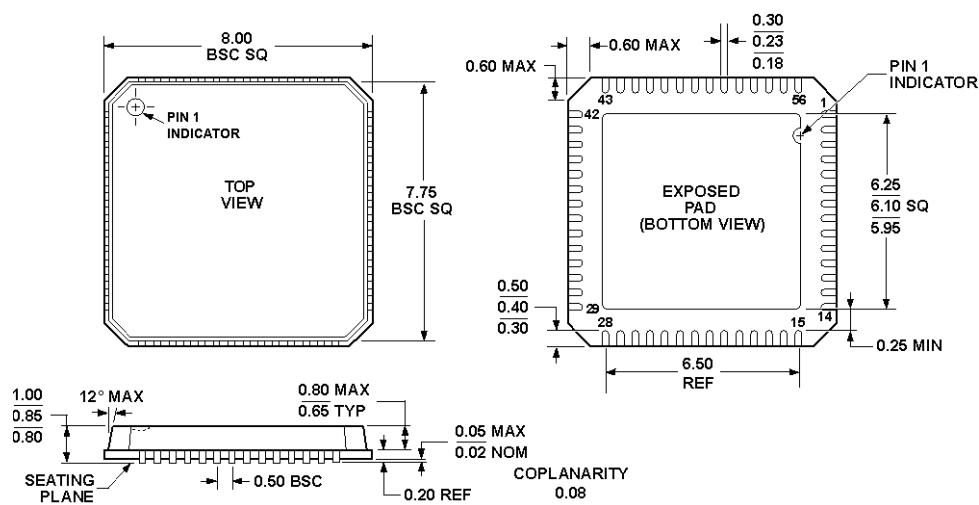

| 外形寸法                    | 27 |

| オーダー・ガイド                | 28 |

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| Changes to Calibration Section                                        | 19 |

| Changes to Reset Function Section and BUSY and LDAC Functions Section | 20 |

| Changes to Channel Addressing and Special Modes Section               | 23 |

| Updated Outline Dimensions                                            | 27 |

| Changes to Ordering Guide                                             | 28 |

### 1/08—Revision 0: Initial Version

## 概要

AD5362/AD5363 は、1 個の 52 ピン LQFP パッケージまたは 56 ピン LFCSP パッケージに 16/14 ビット DAC を 8 個内蔵しています。このデバイスは、リファレンス電圧の 4 倍の振幅を持つバッファ付き電圧出力を提供します。各 DAC のゲインとオフセットを、独立に調節して誤差を除去することができます。柔軟性を高めるため、デバイスを 4 個の DAC からなる 2 つのグループに分割して、各グループの出力範囲をオフセット DAC を使って独立に調整することができます。

AD5362/AD5363 の動作は、 $V_{SS} = -16.5 \text{ V} \sim -4.5 \text{ V}$  と  $V_{DD} = +9 \text{ V} \sim +16.5 \text{ V}$  の広い電源範囲で保証されています。出力アンプ・ヘッドルーム条件は、負荷電流 1 mA で 1.4 V 動作です。

Table 1. チャンネル数の多いバイポーラ DAC

| Model                  | Resolution (Bits) | Nominal Output Span               | Output Channels | Linearity Error (LSB) |

|------------------------|-------------------|-----------------------------------|-----------------|-----------------------|

| <a href="#">AD5360</a> | 16                | $4 \times V_{REF} (20 \text{ V})$ | 16              | $\pm 4$               |

| <a href="#">AD5361</a> | 14                | $4 \times V_{REF} (20 \text{ V})$ | 16              | $\pm 1$               |

| AD5362                 | 16                | $4 \times V_{REF} (20 \text{ V})$ | 8               | $\pm 4$               |

| AD5363                 | 14                | $4 \times V_{REF} (20 \text{ V})$ | 8               | $\pm 1$               |

| <a href="#">AD5370</a> | 16                | $4 \times V_{REF} (12 \text{ V})$ | 40              | $\pm 4$               |

| <a href="#">AD5371</a> | 14                | $4 \times V_{REF} (12 \text{ V})$ | 40              | $\pm 1$               |

| <a href="#">AD5372</a> | 16                | $4 \times V_{REF} (12 \text{ V})$ | 32              | $\pm 4$               |

| <a href="#">AD5373</a> | 14                | $4 \times V_{REF} (12 \text{ V})$ | 32              | $\pm 1$               |

| <a href="#">AD5378</a> | 14                | $\pm 8.75 \text{ V}$              | 32              | $\pm 3$               |

| <a href="#">AD5379</a> | 14                | $\pm 8.75 \text{ V}$              | 40              | $\pm 3$               |

AD5362/AD5363 は、SPI、QSPI™、MICROWIRE™、DSP の各インターフェース規格と互換性を持つ高速 4 線式シリアル・インターフェースを内蔵し、最大 50 MHz のクロック速度で動作することができます。すべての出力は、LDAC 入力をロー・レベルにすることにより、同時に更新することができます。各チャンネルには、プログラマブル・ゲインおよびオフセット調整レジスタがあります。

各 DAC 出力は、内部で SIGGNDx 外部入力を基準とするゲインが決定され、バッファされています。また、DAC 出力は CLR ピンを使って SIGGNDx に接続することもできます。

## 仕様

特に指定のない限り、 $DV_{CC} = 2.5\text{ V} \sim 5.5\text{ V}$ ;  $V_{DD} = 9\text{ V} \sim 16.5\text{ V}$ ;  $V_{SS} = -16.5\text{ V} \sim -4.5\text{ V}$ ;  $V_{REF} = 5\text{ V}$ ; AGND = DGND = SIGGND0 = SIGGND1 = 0 V;  $R_L$  = オープン; ゲイン(M)、オフセット(C)、DAC オフセットの各レジスタはデフォルト値; すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

表 2.

| Parameter                                  | B Version <sup>1</sup>           | Unit                                             | Test Conditions/Comments                                                                               |

|--------------------------------------------|----------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| ACCURACY                                   |                                  |                                                  |                                                                                                        |

| Resolution                                 | 16<br>14                         | Bits<br>Bits                                     | AD5362<br>AD5363                                                                                       |

| Integral Nonlinearity (INL)                | $\pm 4$<br>$\pm 1$               | LSB max<br>LSB max                               | AD5362<br>AD5363                                                                                       |

| Differential Nonlinearity (DNL)            | $\pm 1$                          | LSB max                                          | Guaranteed monotonic by design over temperature                                                        |

| Zero-Scale Error                           | $\pm 15$                         | mV max                                           | Before calibration                                                                                     |

| Full-Scale Error                           | $\pm 20$                         | mV max                                           | Before calibration                                                                                     |

| Gain Error                                 | 0.1                              | % FSR                                            | Before calibration                                                                                     |

| Zero-Scale Error <sup>2</sup>              | 1                                | LSB typ                                          | After calibration                                                                                      |

| Full-Scale Error                           | 1                                | LSB typ                                          | After calibration                                                                                      |

| Span Error of Offset DAC                   | $\pm 75$                         | mV max                                           | See the Offset DACs section for details                                                                |

| VOUTx <sup>3</sup> Temperature Coefficient | 5                                | ppm FSR/ $^{\circ}\text{C}$ typ                  | Includes linearity, offset, and gain drift                                                             |

| DC Crosstalk                               | 180                              | $\mu\text{V}$ max                                | Typically 20 $\mu\text{V}$ ; measured channel at midscale, full-scale change on any other channel      |

| REFERENCE INPUTS (VREF0, VREF1)            |                                  |                                                  |                                                                                                        |

| VREFx Input Current                        | $\pm 10$                         | $\mu\text{A}$ max                                | Per input; typically $\pm 30\text{ nA}$                                                                |

| VREFx Range                                | 2/5                              | V min/V max                                      | $\pm 2\%$ for specified operation                                                                      |

| SIGGND0 AND SIGGND1 INPUTS                 |                                  |                                                  |                                                                                                        |

| DC Input Impedance                         | 50                               | k $\Omega$ min                                   | Typically 55 k $\Omega$                                                                                |

| Input Range                                | $\pm 0.5$                        | V min/V max                                      |                                                                                                        |

| SIGGNDx Gain                               | 0.995/1.005                      | min/max                                          |                                                                                                        |

| OUTPUT CHARACTERISTICS                     |                                  |                                                  |                                                                                                        |

| Output Voltage Range                       | $V_{SS} + 1.4$<br>$V_{DD} - 1.4$ | V min<br>V max                                   | $I_{LOAD} = 1\text{ mA}$<br>$I_{LOAD} = 1\text{ mA}$                                                   |

| Nominal Output Voltage Range               | -10 to +10                       | V                                                |                                                                                                        |

| Short-Circuit Current                      | 15                               | mA max                                           | VOUTx to DV <sub>CC</sub> , V <sub>DD</sub> , or V <sub>SS</sub>                                       |

| Load Current                               | $\pm 1$                          | mA max                                           |                                                                                                        |

| Capacitive Load                            | 2200                             | pF max                                           |                                                                                                        |

| DC Output Impedance                        | 0.5                              | $\Omega$ max                                     |                                                                                                        |

| MONITOR PIN (MON_OUT)                      |                                  |                                                  |                                                                                                        |

| Output Impedance                           |                                  |                                                  |                                                                                                        |

| DAC Output at Positive Full Scale          | 1000                             | $\Omega$ typ                                     |                                                                                                        |

| DAC Output at Negative Full Scale          | 500                              | $\Omega$ typ                                     |                                                                                                        |

| Three-State Leakage Current                | 100                              | nA typ                                           |                                                                                                        |

| Continuous Current Limit                   | 2                                | mA max                                           |                                                                                                        |

| DIGITAL INPUTS                             |                                  |                                                  |                                                                                                        |

| Input High Voltage                         | 1.7<br>2.0                       | V min<br>V min                                   | $DV_{CC} = 2.5\text{ V} \text{ to } 3.6\text{ V}$<br>$DV_{CC} = 3.6\text{ V} \text{ to } 5.5\text{ V}$ |

| Input Low Voltage                          | 0.8                              | V max                                            | $DV_{CC} = 2.5\text{ V} \text{ to } 5.5\text{ V}$                                                      |

| Input Current                              | $\pm 1$<br>$\pm 20$              | $\mu\text{A}$ max<br>$\mu\text{A}$ max           | RESET, SYNC, SDI, and SCLK pins<br>CLR, BIN/2SCOMP, and GPIO pins                                      |

| Input Capacitance                          | 10                               | pF max                                           |                                                                                                        |

| DIGITAL OUTPUTS (SDO, BUSY, GPIO, PEC)     |                                  |                                                  |                                                                                                        |

| Output Low Voltage                         | 0.5                              | V max                                            | Sinking 200 $\mu\text{A}$                                                                              |

| Output High Voltage (SDO)                  | $DV_{CC} - 0.5$                  | V min                                            | Sourcing 200 $\mu\text{A}$                                                                             |

| High Impedance Leakage Current             | $\pm 5$                          | $\mu\text{A}$ max                                | SDO only                                                                                               |

| High Impedance Output Capacitance          | 10                               | pF typ                                           |                                                                                                        |

| TEMPERATURE SENSOR (TEMP_OUT)              |                                  |                                                  |                                                                                                        |

| Accuracy                                   | $\pm 1$<br>$\pm 5$               | $^{\circ}\text{C}$ typ<br>$^{\circ}\text{C}$ typ | @ 25 $^{\circ}\text{C}$<br>-40 $^{\circ}\text{C} < T < +85^{\circ}\text{C}$                            |

| Output Voltage at 25 $^{\circ}\text{C}$    | 1.46                             | V typ                                            |                                                                                                        |

| Parameter                         | B Version <sup>1</sup> | Unit        | Test Conditions/Comments                                                             |

|-----------------------------------|------------------------|-------------|--------------------------------------------------------------------------------------|

| Output Voltage Scale Factor       | 4.4                    | mV/°C typ   |                                                                                      |

| Output Load Current               | 200                    | μA max      | Current source only                                                                  |

| Power-On Time                     | 10                     | ms typ      | To within ±5°C                                                                       |

| POWER REQUIREMENTS                |                        |             |                                                                                      |

| DV <sub>CC</sub>                  | 2.5/5.5                | V min/V max |                                                                                      |

| V <sub>DD</sub>                   | 8/16.5                 | V min/V max |                                                                                      |

| V <sub>SS</sub>                   | -16.5/-4.5             | V min/V max |                                                                                      |

| Power Supply Sensitivity          |                        |             |                                                                                      |

| ΔFull Scale/ΔV <sub>DD</sub>      | -75                    | dB typ      |                                                                                      |

| ΔFull Scale/ΔV <sub>SS</sub>      | -75                    | dB typ      |                                                                                      |

| ΔFull Scale/ΔDV <sub>CC</sub>     | -90                    | dB typ      |                                                                                      |

| DI <sub>CC</sub>                  | 2                      | mA max      | DV <sub>CC</sub> = 5.5 V, V <sub>IH</sub> = DV <sub>CC</sub> , V <sub>IL</sub> = GND |

| I <sub>DD</sub>                   | 8.5                    | mA max      | Outputs = 0 V and unloaded                                                           |

| I <sub>SS</sub>                   | 8.5                    | mA max      | Outputs = 0 V and unloaded                                                           |

| Power-Down Mode                   |                        |             | Bit 0 in the control register is 1                                                   |

| DI <sub>CC</sub>                  | 5                      | μA typ      |                                                                                      |

| I <sub>DD</sub>                   | 35                     | μA typ      |                                                                                      |

| I <sub>SS</sub>                   | -35                    | μA typ      |                                                                                      |

| Power Dissipation                 |                        |             |                                                                                      |

| Power Dissipation Unloaded (P)    | 209                    | mW max      | V <sub>SS</sub> = -12 V, V <sub>DD</sub> = 12 V, DV <sub>CC</sub> = 2.5 V            |

| Junction Temperature <sup>4</sup> | 130                    | °C max      | T <sub>J</sub> = T <sub>A</sub> + P <sub>TOTAL</sub> × θ <sub>JA</sub>               |

<sup>1</sup> B バージョンの温度範囲は -40 ~ +85°C。Typ 値仕様は 25°C の値。<sup>2</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。<sup>3</sup> VOUTx は VOUT0 ~ VOUT7 を表します。<sup>4</sup> θ<sub>JA</sub> はパッケージの熱抵抗を表します。

## AC 特性

特に指定のない限り、 $DV_{CC} = 2.5\text{ V}$ ;  $V_{DD} = 15\text{ V}$ ;  $V_{SS} = -15\text{ V}$ ;  $V_{REF} = 5\text{ V}$ ;  $AGND = DGND = SIGGND0 = SIGGND1 = 0\text{ V}$ ;  $C_L = 200\text{ pF}$ ;  $R_L = 10\text{ k}\Omega$ ; ゲイン(M)、オフセット(C)、DAC オフセットの各レジスタはデフォルト値;すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

表 3.

| Parameter                              | B Version <sup>1</sup> | Unit                                   | Test Conditions/Comments                                                          |

|----------------------------------------|------------------------|----------------------------------------|-----------------------------------------------------------------------------------|

| <b>DYNAMIC PERFORMANCE<sup>1</sup></b> |                        |                                        |                                                                                   |

| Output Voltage Settling Time           | 20<br>30               | $\mu\text{s typ}$<br>$\mu\text{s max}$ | Full-scale change<br>DAC latch contents alternately loaded with all 0s and all 1s |

| Slew Rate                              | 1                      | $\text{V}/\mu\text{s typ}$             |                                                                                   |

| Digital-to-Analog Glitch Energy        | 5                      | $\text{nV}\cdot\text{s typ}$           |                                                                                   |

| Glitch Impulse Peak Amplitude          | 10                     | $\text{mV max}$                        |                                                                                   |

| Channel-to-Channel Isolation           | 100                    | $\text{dB typ}$                        | $V_{REF0}, V_{REF1} = 2\text{ V p-p, } 1\text{ kHz}$                              |

| DAC-to-DAC Crosstalk                   | 10                     | $\text{nV}\cdot\text{s typ}$           |                                                                                   |

| Digital Crosstalk                      | 0.2                    | $\text{nV}\cdot\text{s typ}$           |                                                                                   |

| Digital Feedthrough                    | 0.02                   | $\text{nV}\cdot\text{s typ}$           | Effect of input bus activity on DAC output under test                             |

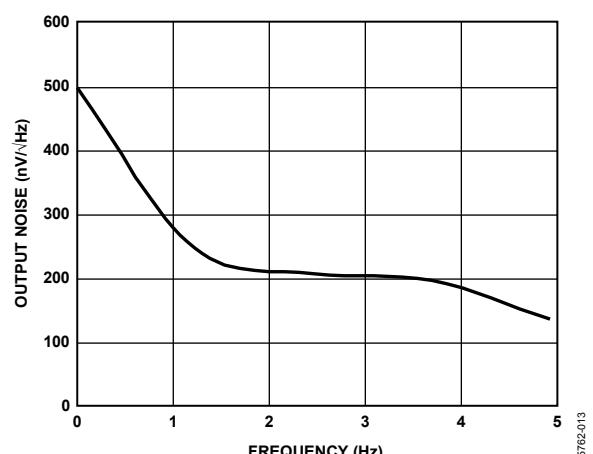

| Output Noise Spectral Density @ 10 kHz | 250                    | $\text{nV}/\sqrt{\text{Hz typ}}$       | $V_{REF0} = V_{REF1} = 0\text{ V}$                                                |

<sup>1</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

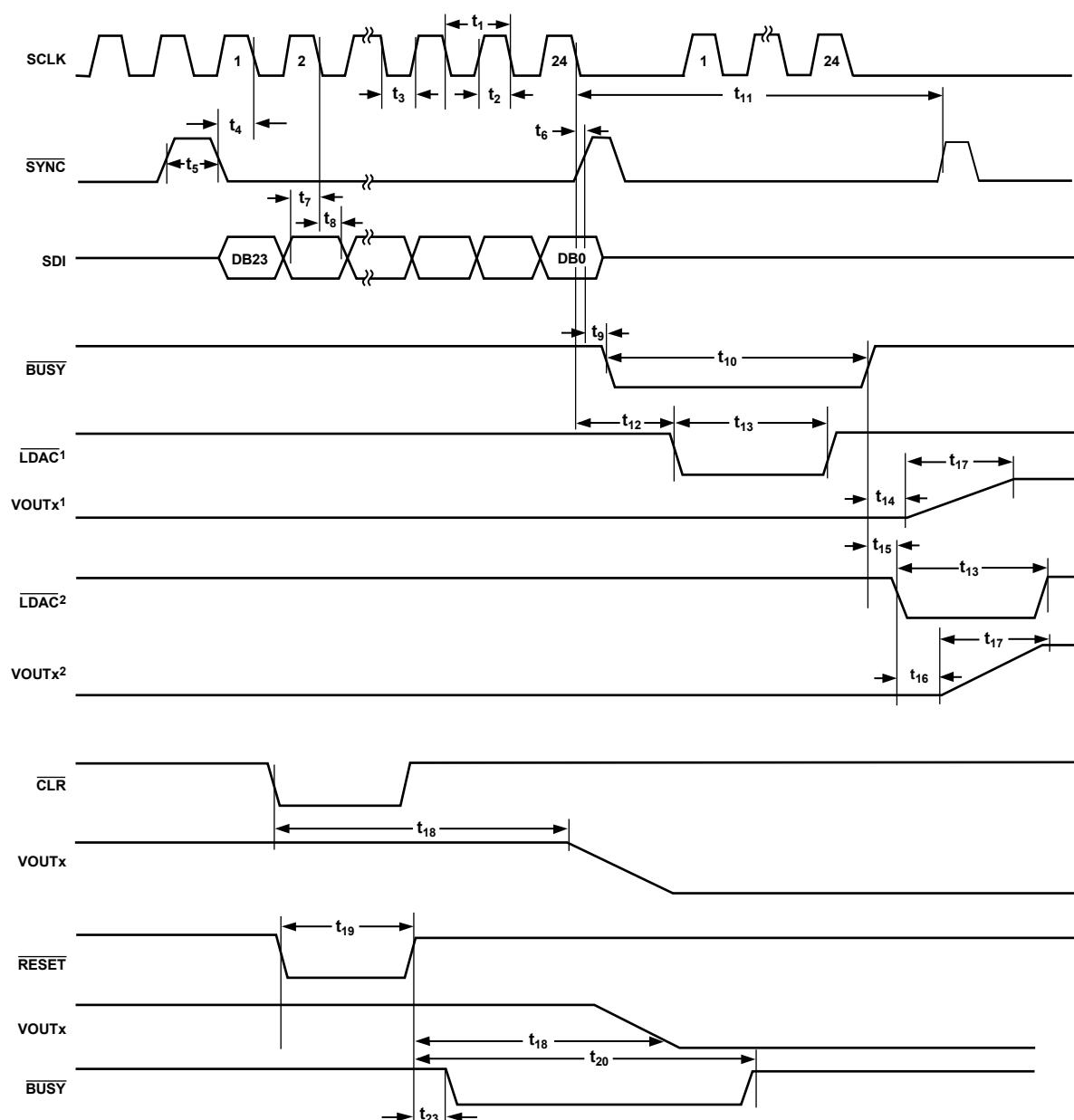

## タイミング特性

特に指定のない限り、 $DV_{CC} = 2.5\text{ V} \sim 5.5\text{ V}$ ;  $V_{DD} = 9\text{ V} \sim 16.5\text{ V}$ ;  $V_{SS} = -16.5\text{ V} \sim -8\text{ V}$ ;  $V_{REF} = 5\text{ V}$ ;  $AGND = DGND = SIGGND = 0\text{ V}$ ;  $C_L = GND \sim 200\text{ pF}$ ;  $R_L = \text{オープン}$ ; ゲイン(M)、オフセット(C)、DAC オフセットの各レジスタはデフォルト値;すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

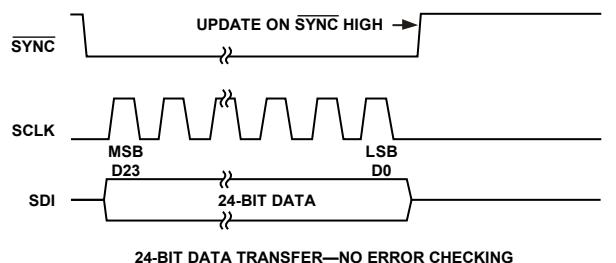

表 4.SPI インターフェース

| Parameter <sup>1, 2, 3</sup> | Limit at $T_{MIN}, T_{MAX}$ | Unit                              | Description                                                                   |

|------------------------------|-----------------------------|-----------------------------------|-------------------------------------------------------------------------------|

| $t_1$                        | 20                          | ns min                            | SCLK cycle time                                                               |

| $t_2$                        | 8                           | ns min                            | SCLK high time                                                                |

| $t_3$                        | 8                           | ns min                            | SCLK low time                                                                 |

| $t_4$                        | 11                          | ns min                            | SYNC falling edge to SCLK falling edge setup time                             |

| $t_5$                        | 20                          | ns min                            | Minimum $\overline{\text{SYNC}}$ high time                                    |

| $t_6$                        | 10                          | ns min                            | 24 <sup>th</sup> SCLK falling edge to $\overline{\text{SYNC}}$ rising edge    |

| $t_7$                        | 5                           | ns min                            | Data setup time                                                               |

| $t_8$                        | 5                           | ns min                            | Data hold time                                                                |

| $t_9^4$                      | 42                          | ns max                            | $\overline{\text{SYNC}}$ rising edge to $\overline{\text{BUSY}}$ falling edge |

| $t_{10}$                     | 1/1.5                       | $\mu\text{s typ}/\mu\text{s max}$ | BUSY pulse width low (single-channel update); see Table 9                     |

| $t_{11}$                     | 600                         | ns max                            | Single-channel update cycle time                                              |

| $t_{12}$                     | 20                          | ns min                            | $\overline{\text{SYNC}}$ rising edge to $\overline{\text{LDAC}}$ falling edge |

| $t_{13}$                     | 10                          | ns min                            | LDAC pulse width low                                                          |

| $t_{14}$                     | 3                           | $\mu\text{s max}$                 | BUSY rising edge to DAC output response time                                  |

| $t_{15}$                     | 0                           | ns min                            | BUSY rising edge to LDAC falling edge                                         |

| $t_{16}$                     | 3                           | $\mu\text{s max}$                 | LDAC falling edge to DAC output response time                                 |

| $t_{17}$                     | 20/30                       | $\mu\text{s typ}/\mu\text{s max}$ | DAC output settling time                                                      |

| $t_{18}$                     | 140                         | ns max                            | CLR/RESET pulse activation time                                               |

| $t_{19}$                     | 30                          | ns min                            | RESET pulse width low                                                         |

| $t_{20}$                     | 400                         | $\mu\text{s max}$                 | RESET time indicated by BUSY low                                              |

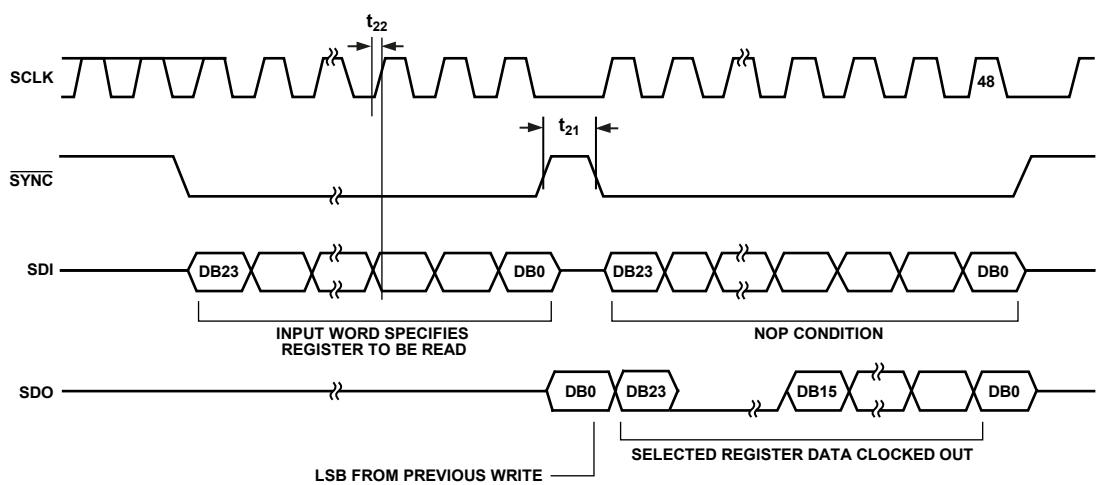

| $t_{21}$                     | 270                         | ns min                            | Minimum $\overline{\text{SYNC}}$ high time in readback mode                   |

| $t_{22}^5$                   | 25                          | ns max                            | SCLK rising edge to SDO valid                                                 |

| $t_{23}$                     | 80                          | ns max                            | RESET rising edge to $\overline{\text{BUSY}}$ falling edge                    |

<sup>1</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

<sup>2</sup> すべての入力信号は  $t_R = t_f = 2\text{ ns}$  ( $DV_{CC}$  の 10%から 90%)で規定し、1.2 V の電圧レベルからの時間とします。

<sup>3</sup> 図 4 と図 5 を参照。

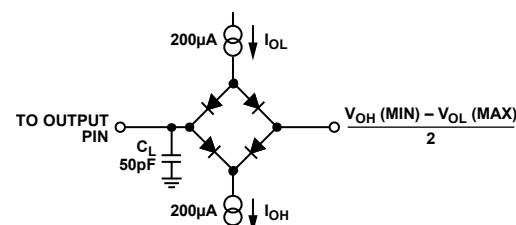

<sup>4</sup>  $t_9$  は、図 3.SDO タイミング図の負荷回路の負荷回路で測定。

<sup>5</sup>  $t_{22}$  は、図 3.SDO タイミング図の負荷回路の負荷回路で測定。

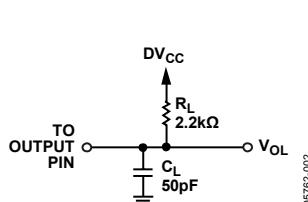

図 2. BUSY タイミング図の負荷回路

05762-003

図 3. SDO タイミング図の負荷回路

05762-004

図 4. SPI 書き込みタイミング

図 5.SPI 読み出しタイミング

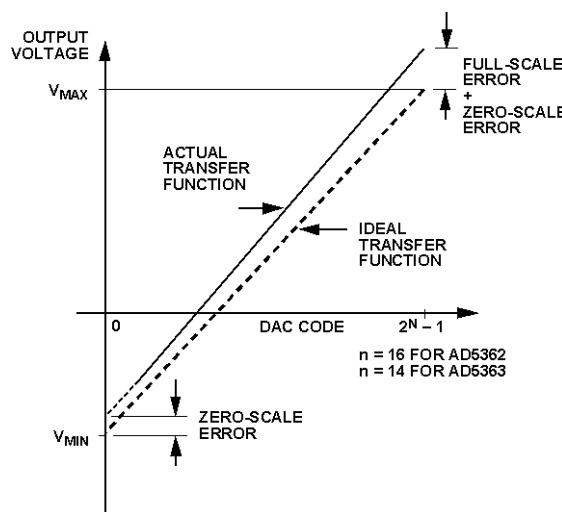

図 6.DAC の伝達関数

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。最大 60 mA までの過渡電流では SCR ラッチ・アップは生じません。

表 5.

| Parameter                                  | Rating                               |

|--------------------------------------------|--------------------------------------|

| $V_{DD}$ to AGND                           | -0.3 V to +17 V                      |

| $V_{SS}$ to AGND                           | -17 V to +0.3 V                      |

| $DV_{CC}$ to DGND                          | -0.3 V to +7 V                       |

| Digital Inputs to DGND                     | -0.3 V to $DV_{CC} + 0.3$ V          |

| Digital Outputs to DGND                    | -0.3 V to $DV_{CC} + 0.3$ V          |

| $V_{REF0}, V_{REF1}$ to AGND               | -0.3 V to +5.5 V                     |

| $V_{OUT0}$ through $V_{OUT7}$ to AGND      | $V_{SS} - 0.3$ V to $V_{DD} + 0.3$ V |

| SIGGND0, SIGGND1 to AGND                   | -1 V to +1 V                         |

| AGND to DGND                               | -0.3 V to +0.3 V                     |

| MON_IN0, MON_IN1, MON_OUT to AGND          | $V_{SS} - 0.3$ V to $V_{DD} + 0.3$ V |

| Operating Temperature Range ( $T_A$ )      |                                      |

| Industrial (J Version)                     | -40°C to +85°C                       |

| Storage Temperature Range                  | -65°C to +150°C                      |

| Operating Junction Temperature( $T_j$ max) | 130°C                                |

| $\theta_{JA}$ Thermal Impedance            |                                      |

| 52-Lead LQFP                               | 38°C/W                               |

| 56-Lead LFCSP                              | 25°C/W                               |

| Reflow Soldering                           |                                      |

| Peak Temperature                           | 230°C                                |

| Time at Peak Temperature                   | 10 sec to 40 sec                     |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の節に記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

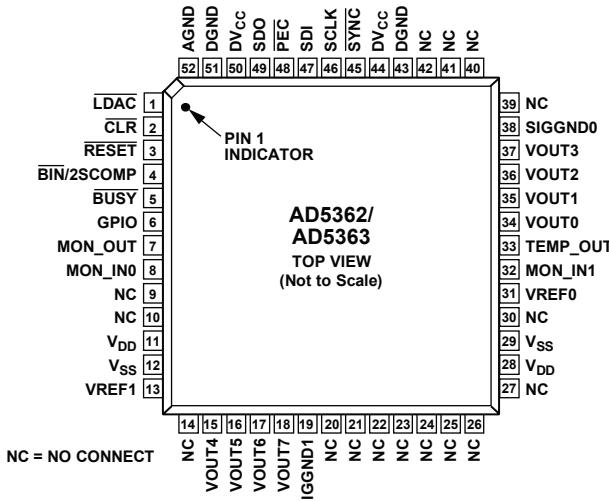

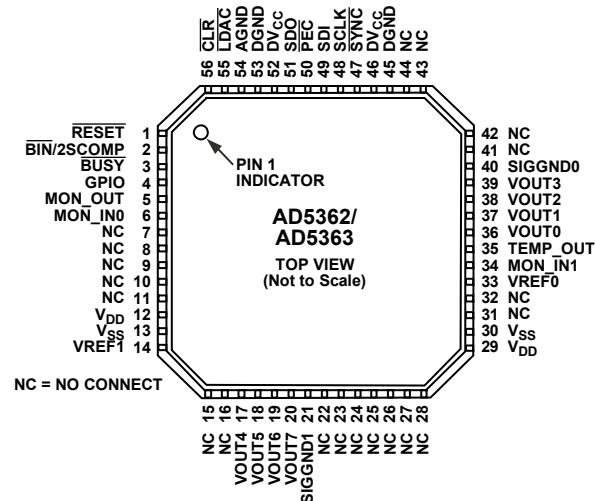

## ピン配置およびピン機能説明

図 7.52 ピン LQFP のピン配置

図 8.56 ピン LFCSP のピン配置

表 6. ピン機能の説明

| ピン番号                            |                                               | 記号                  | 説明                                                                                                                             |

|---------------------------------|-----------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|

| LQFP                            | LFCSP                                         |                     |                                                                                                                                |

| 1                               | 55                                            | LDAC                | ロード DAC ロジック入力(アクティブ・ロー・レベル)。詳細については、 <u>BUSY</u> とLDACの機能のセクション参照。                                                            |

| 2                               | 56                                            | CLR                 | 非同期クリア入力(レベル検出、アクティブ・ロー)。詳細については、クリア機能のセクション参照。                                                                                |

| 3                               | 1                                             | RESET               | デジタル・リセット入力。                                                                                                                   |

| 4                               | 2                                             | <u>BIN/2SCOMP</u>   | データ・フォーマット・デジタル入力。このピンを DGND に接続すると、オフセット・バイナリが選択されます。このピンを 1 に設定すると、2 の補数が選択されます。この入力には弱いプルダウンが付いています。                        |

| 5                               | 3                                             | <u>BUSY</u>         | デジタル入力/オープン・ドレイン出力。 <u>BUSY</u> は出力時オープン・ドレインになります。詳細については、 <u>BUSY</u> とLDACの機能のセクション参照。                                      |

| 6                               | 4                                             | GPIO                | デジタル I/O ピン。このピンは入力または出力に設定でき、シリアル・インターフェースを介してリードバックするか、またはハイ/ロー・レベルに設定することができます。入力に設定すると、このピンは弱いプルダウンを持ちます。                  |

| 7                               | 5                                             | MON_OUT             | アナログ・マルチプレクサ出力。すべての DAC 出力、MON_IN0 入力、または MON_IN1 入力をこの出力に取り出して、モニターすることができます。                                                 |

| 8、32                            | 6、34                                          | MON_IN0、<br>MON_IN1 | アナログ・マルチプレクサ入力。MON_OUT に取り出すことができます。                                                                                           |

| 9、10、14、20 to<br>27、30、39 to 42 | 7 to 11、15、16、<br>22 to 28、31、<br>32、41 to 44 | NC                  | 未接続。                                                                                                                           |

| 11、28                           | 12、29                                         | VDD                 | 正のアナログ電源;仕様性能に対して 9 V~16.5 V。これらのピンは、0.1 $\mu$ F のセラミック・コンデンサと 10 $\mu$ F のコンデンサでデカッピングする必要があります。                              |

| 12、29                           | 13、30                                         | VSS                 | 負のアナログ電源;仕様性能に対して -16.5 V~-8 V。これらのピンは、0.1 $\mu$ F のセラミック・コンデンサと 10 $\mu$ F のコンデンサでデカッピングする必要があります。                            |

| 13                              | 14                                            | VREF1               | DAC 4~DAC 7 のリファレンス電圧入力。このリファレンス電圧は AGND を基準とします。                                                                              |

| 34 to 37、15 to 18               | 36 to 39、17 to 20                             | VOUT0 to VOUT7      | DAC 出力。8 個の各 DAC チャンネルのバッファ付きアナログ出力。各アナログ出力は、グラウンドへ接続した 10 k $\Omega$ の出力負荷を駆動することができます。これらのアンプの出力インピーダンスは 0.5 $\Omega$ (typ)。 |

| 19                              | 21                                            | SIGGND1             | DAC 4~DAC 7 のリファレンス電圧グラウンド。VOUT4~VOUT7 はこの電圧を基準とします。                                                                           |

| 31                              | 33                                            | VREF0               | DAC 0~DAC 3 のリファレンス電圧入力。このリファレンス電圧は AGND を基準                                                                                   |

| ピン番号  |       | 記号       | 説明                                                                                                    |

|-------|-------|----------|-------------------------------------------------------------------------------------------------------|

| LQFP  | LFCSP |          |                                                                                                       |

| 33    | 35    | TEMP_OUT | チップ温度に比例する電圧を出力します。25°Cで 1.46 V (typ)、出力は 4.4 mV/°Cで変化します。                                            |

| 38    | 40    | SIGGND0  | DAC 0～DAC 3 のリファレンス電圧グラウンド。VOUT0～VOUT3 はこの電圧を基準とします。                                                  |

| 43、51 | 45、53 | DGND     | すべてのデジタル回路のグラウンド。両 DGND ピンは DGND プレーンに接続する必要があります。                                                    |

| 44、50 | 46、52 | DVCC     | ロジック電源; 2.5 V～5.5 V。これらのピンは、0.1 $\mu$ F のセラミック・コンデンサと 10 $\mu$ F のコンデンサでデカップリングする必要があります。             |

| 45    | 47    | SYNC     | SPI インターフェースのアクティブ・ロー SYNC 入力。これは、SPI シリアル・インターフェースのフレーム同期信号です。詳細については、図 4、図 5、シリアル・インターフェースのセクション参照。 |

| 46    | 48    | SCLK     | SPI インターフェースのシリアル・クロック入力。詳細については、図 4、図 5、シリアル・インターフェースのセクション参照。                                       |

| 47    | 49    | SDI      | SPI インターフェースのシリアル・データ入力。詳細については、図 4、図 5、シリアル・インターフェースのセクション参照。                                        |

| 48    | 50    | PEC      | パケット・エラー・チェック出力。50 k $\Omega$ ブルアップを持つオープン・ドライン出力で、パケット・エラー・チェックが発生すると、ロー・レベルになります。                   |

| 49    | 51    | SDO      | SPI インターフェースのシリアル・データ出力。詳細については、図 4、図 5、シリアル・インターフェースのセクション参照。                                        |

| 52    | 54    | AGND     | すべてのアナログ回路のグラウンド。AGND ピンは AGND プレーンに接続する必要があります。                                                      |

| 露出パドル |       | EP       | 露出パドル。V <sub>SS</sub> へ接続します。                                                                         |

## 代表的な性能特性

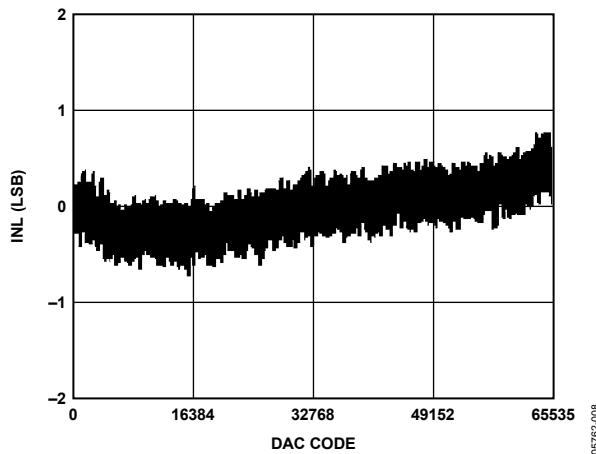

図 9.AD5362 の INL (Typ) のプロット

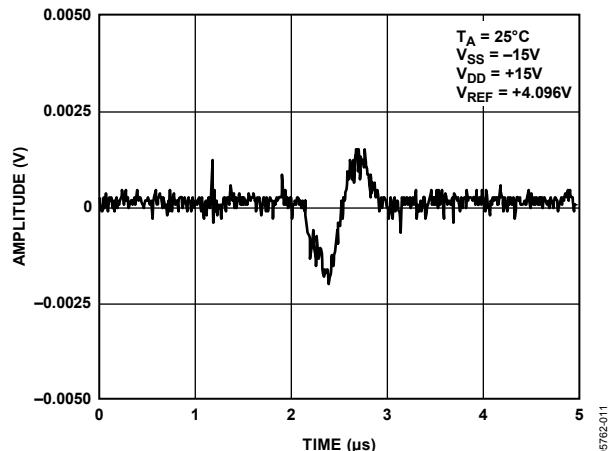

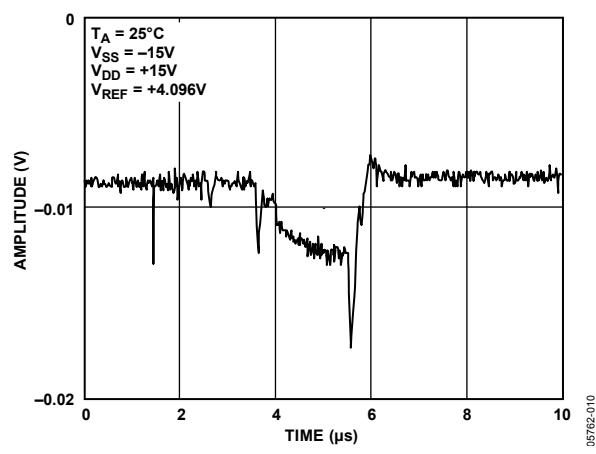

図 12. デジタル・クロストーク

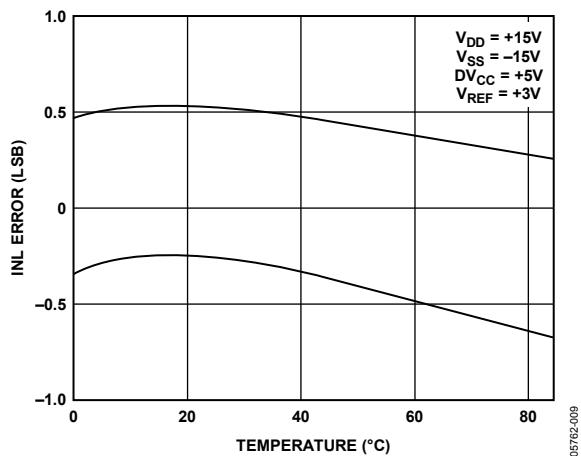

図 10. INL 誤差(Typ)の温度特性

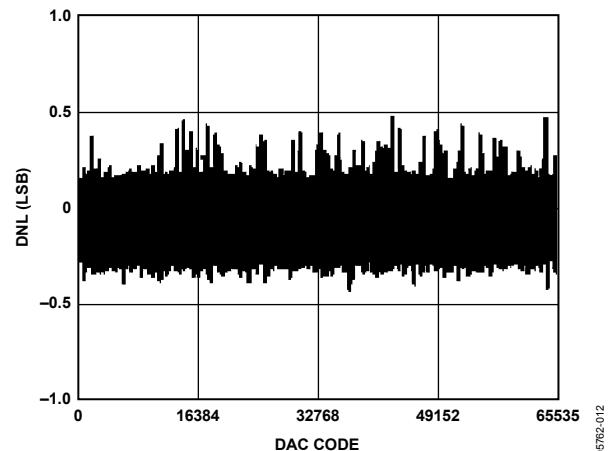

図 13. AD5362 の DNL(Typ) のプロット

図 11.  $\overline{\text{LDAC}}$ に起因するアナログ・クロストーク

図 14. 出力ノイズ・スペクトル密度

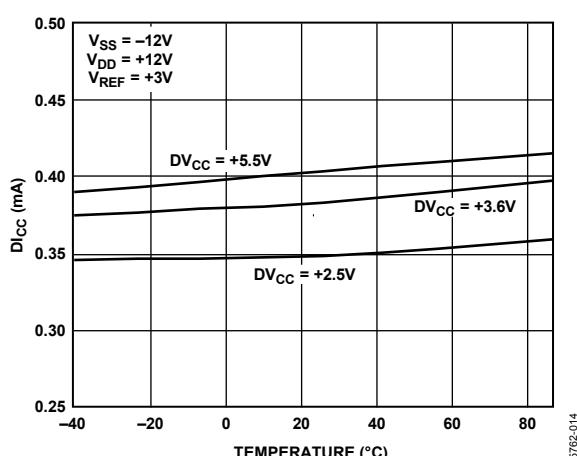

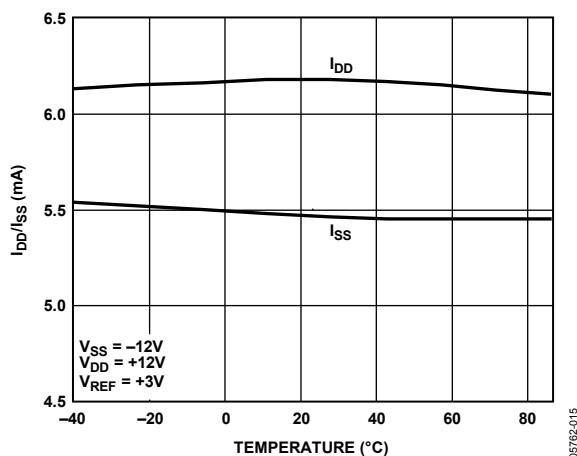

図 15.DICC の温度特性

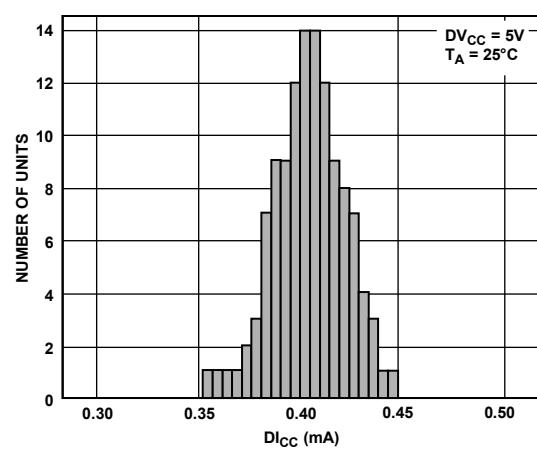

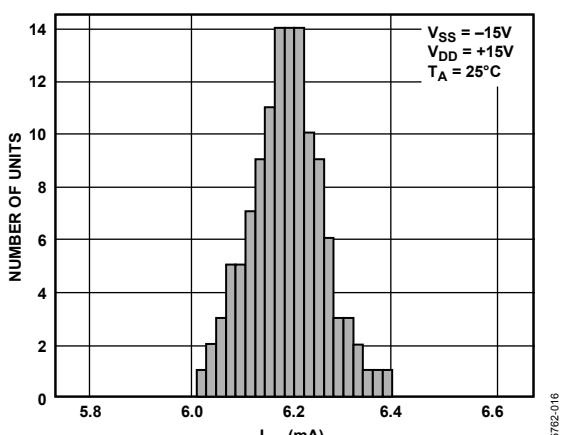

図 18.DICC (Typ)の分布

図 16.IDD/ISS の温度特性

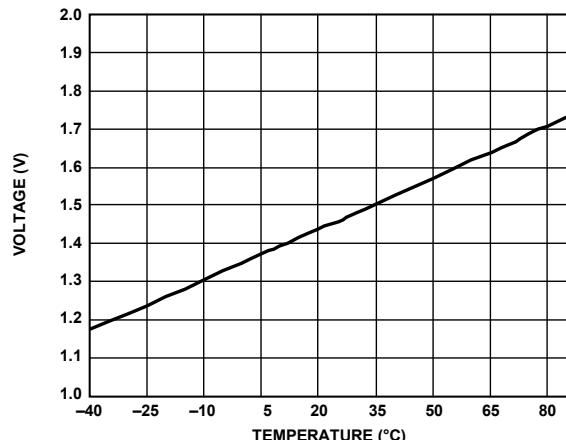

図 19.TEMP\_OUT 電圧の温度特性

図 17.IDD (Typ)の分布

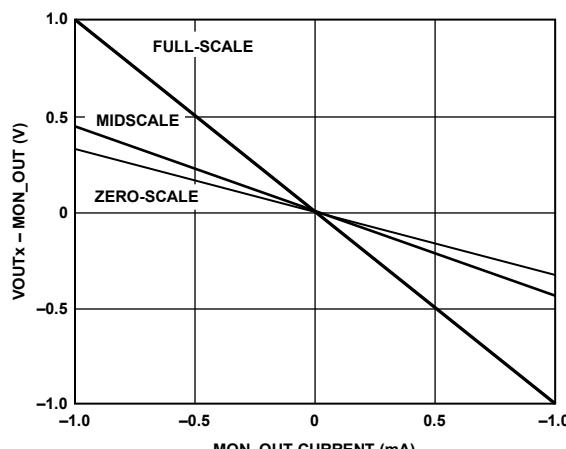

図 20.VOUTx MON\_OUT 誤差対 MON\_OUT 電流

## 用語

### 積分非直線性(INL)

積分非直線性または端点直線性とは、DAC伝達関数の両端を結ぶ直線からの最大偏差値を表します。ゼロ・スケール誤差とフル・スケール誤差を調節した後に測定して、 LSB数で表します。

### 微分非直線性(DNL)

微分非直線性(DNL)は、隣接する2つのコードの間における測定された変化と理論的な1 LSB変化との差をいいます。最大1 LSBの微分非直線性の仕様は、単調性を保証するものです。

### ゼロ・スケール誤差

ゼロ・スケール誤差は、全ビット0をDACレジスタにロードしたときのDAC出力電圧の誤差です。オフセット誤差は、チャンネルが最小値にある場合のVOUT(実測値)とVOUT(理論)の差を表し、mVで表示されます。ゼロ・スケール誤差は、主に出力アンプのオフセットから発生します。

### フル・スケール誤差

フル・スケール誤差は、全ビット1をDACレジスタにロードしたときのDAC出力電圧の誤差です。フルスケール誤差は、チャンネルが最大値にある場合のVOUT(実測値)とVOUT(理論)の差を表し、mVで表示されます。フル・スケール誤差はゼロ・スケール誤差を含みません。

### ゲイン誤差

ゲイン誤差は、フル・スケール誤差とゼロ・スケール誤差の差を表します。フルスケール・レンジ(FSR)のパーセント値で表示します。

$$\text{ゲイン誤差} = \text{フル・スケール誤差} - \text{ゼロ・スケール誤差}$$

### VOUT 温度係数

VOUT温度係数には、直線性、オフセット、ゲイン・ドリフトの出力誤差成分が含まれます。

### DC 出力インピーダンス

DC出力インピーダンスは実効出力ソース抵抗です。パッケージのピン抵抗により支配されます。

### DC クロストーク

各DAC出力は、V<sub>DD</sub>とV<sub>SS</sub>電源を共通にする各オペアンプによりバッファされています。1つのチャンネルでDC負荷電流が変化すると(更新による)、この変化が複数のチャンネル出力でさらにDC変化を生じさせます。負荷電流が大きいとこの影響が大きくなり、負荷電流が小さいと影響が小さくなります。高インピーダンス負荷では、影響を無視することができます。DCクロストークを小さくするために、複数のV<sub>DD</sub>ピンとV<sub>SS</sub>ピンを設けてあります。

### 出力電圧セトリング・タイム

フル・スケール入力変化に対して、出力が規定のレベルまでに安定するために要する時間を表します。

### デジタル/アナログ・グリッチ・エネルギー

これは、大きなコード変化があったときにアナログ出力に混入するエネルギーの大きさを表します。グリッチの面積として規定されnV-sで表示されます。0x7FFFと0x8000(AD5362)との間、または0x1FFFと0x2000(AD5363)との間でDACレジスタ・データをトグルさせて測定します。

### チャンネル間アイソレーション

チャンネル間アイソレーションは、1つのDACリファレンス入力から現れる入力信号の一部を意味します。この一部の信号は、別のリファレンス電圧で動作している別のDAC出力から混入したもので、ミッドスケールで測定し、デシベルで表します。

### DAC から DAC へのクロストーク

DACからDACへのクロストークは、デジタル変化とそれに続く別のコンバータでのアナログ出力変化の両方に起因して、別のコンバータ出力に発生するグリッチ・インパルスで表されます。nV-sで表わします。

### デジタル・クロストーク

コンバータの出力変化に起因して、別のコンバータ出力に混入するグリッチ・インパルス。nV-sで表わします。

### デジタル・フィードスルー

デバイスが選択されていないときに、デバイスのデジタル入力での高周波ロジック動作がデバイスを超えて、およびデバイスを通過して容量結合して、VOUTピンにノイズとして現れることを意味します。電源ラインとグラウンド・ラインを経由して結合することもあります。このノイズがデジタル・フィードスルーです。

### 出力ノイズ・スペクトル密度

これは、内部で発生されたランダム・ノイズの大きさを表します。ランダム・ノイズは、スペクトル密度( $\sqrt{\text{Hz}}$ あたりの電圧)で表されます。全DACにミッド・スケールを入力し、出力のノイズを測定します。nV/ $\sqrt{\text{Hz}}$ で表します。

## 動作原理

### DAC アーキテクチャ

AD5362/AD5363 は、8 個の DAC チャンネルと 8 個の出力アンプを 1 個のパッケージに内蔵しています。DAC の 1 チャンネルは、16 ビット(AD5362)または 14 ビット(AD5363)の抵抗ストリング DAC とそれに続く出力バッファ・アンプから構成されています。抵抗ストリング・セクションは、VREF0 または VREF1 から AGND までの等しい値の抵抗の単純なストリングです。このタイプのアーキテクチャでは、DAC の単調性が保証されています。DAC レジスタにロードされる 16 ビット(AD5362)または 14 ビット(AD5363)のバイナリ・デジタル・コードが、電圧を取り出すストリング上のノードを決め、取り出されたこの電圧が出力アンプに入力されます。

表 7.AD5362/AD5363 のレジスタ

| Register Name         | Word Length in Bits | Description                                                                                                                                                                        |

|-----------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1A (Group) (Channel) | 16 (14)             | Input Data Register A, one for each DAC channel.                                                                                                                                   |

| X1B (Group) (Channel) | 16 (14)             | Input Data Register B, one for each DAC channel.                                                                                                                                   |

| M (Group) (Channel)   | 16 (14)             | Gain trim registers, one for each DAC channel.                                                                                                                                     |

| C (Group) (Channel)   | 16 (14)             | Offset trim registers, one for each DAC channel.                                                                                                                                   |

| X2A (Group) (Channel) | 16 (14)             | Output Data Register A, one for each DAC channel. These registers store the final, calibrated DAC data after gain and offset trimming. They are not readable or directly writable. |

| X2B (Group) (Channel) | 16 (14)             | Output Data Register B, one for each DAC channel. These registers store the final, calibrated DAC data after gain and offset trimming. They are not readable or directly writable. |

| DAC (Group) (Channel) |                     | Data registers from which the DACs take their final input data. The DAC registers are updated from the X2A or X2B registers. They are not readable or directly writable.           |

| OFS0                  | 14                  | Offset DAC 0 data register: sets offset for Group 0.                                                                                                                               |

| OFS1                  | 14                  | Offset DAC 1 data register: sets offset for Group 1.                                                                                                                               |

| Control               | 5                   | Bit 4 = overtemperature indicator.<br>Bit 3 = PEC error flag.<br>Bit 2 = A/B select.<br>Bit 1 = thermal shutdown.<br>Bit 0 = software power-down.                                  |

| Monitor               | 6                   | Bit 5 = monitor enable.<br>Bit 4 = monitor DACs or monitor MON_INx pin.<br>Bit 3 to Bit 0 = monitor selection control.                                                             |

| GPIO                  | 2                   | Bit 1 = GPIO configuration.<br>Bit 0 = GPIO data.                                                                                                                                  |

| A/B Select 0          | 8                   | Bits [3:0] in this register determine whether a DAC in Group 0 takes its data from Register X2A or Register X2B (0 = X2A, 1 = X2B).                                                |

| A/B Select 1          | 8                   | Bits [3:0] in this register determine whether a DAC in Group 1 takes its data from Register X2A or Register X2B (0 = X2A, 1 = X2B).                                                |

表 8.AD5362/AD5363 入力レジスタのデフォルト値

| Register Name                 | AD5362 Default Value | AD5363 Default Value |

|-------------------------------|----------------------|----------------------|

| X1A, X1B                      | 0x8000               | 0x2000               |

| M                             | 0xFFFF               | 0x3FFF               |

| C                             | 0x8000               | 0x2000               |

| OFS0, OFS1                    | 0x2000               | 0x2000               |

| Control                       | 0x00                 | 0x00                 |

| A/B Select 0 and A/B Select 1 | 0x00                 | 0x00                 |

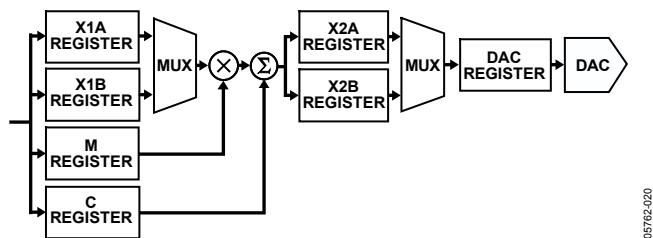

## A/B レジスタとゲイン/オフセットの調整

各 DAC チャンネルには 7 個のデータ・レジスタがあります。実際の DAC データ・ワードは、コントロール・レジスタ内の A/B ビットの設定に応じて、X1A または X1B 入力レジスタに書き込むことができます。A/B ビットが 0 の場合、データは X1A レジスタに書き込まれます。A/B ビットが 1 の場合、データは X1B レジスタに書き込まれます。この 1 ビットはグローバル制御であるため、デバイス内の各 DAC チャンネルを制御することに注意してください。ある書き込みは X1A レジスタへ、別の書き込みは X1B レジスタへというように、チャンネルごとにデバイスを設定することはできません。

図 21. 各 DAC チャンネルに対応するデータ・レジスタ

各 DAC チャンネルにはゲイン(M)レジスタとオフセット(C)レジスタがあるため、これらを使ってシグナル・チェイン全体のゲイン誤差とオフセット誤差を調整することができます。X1A レジスタからのデータは、M レジスタと C レジスタの値で制御されるデジタル乗算器と加算器で演算されます。キャリブレーションされた DAC データは X2A レジスタに保存されます。同様に、X1B レジスタからのデータは、デジタル乗算器と加算器で演算され、X2B レジスタに保存されます。

各チャンネルの乗算器と加算器のシンボルを図 21 に示していますが、デバイス内には乗算器と加算器は各 1 個だけ存在し、すべてのチャンネル間で共用されます。これは、レジスタ更新レートのセクションで説明するように、複数のチャンネルを 1 回で更新する際に更新速度に影響を与えます。

X1A レジスタへデータを書き込むごとに、あるいは A/B コントロール・ビット = 0 で M レジスタまたは C レジスタへデータを書き込むごとに、X2A データが再計算され、X2A レジスタが自動的に更新されます。同様に、データを X1B へ、あるいは A/B = 1 で M または C へ、それぞれ書き込むごとに、X2B が更新されます。X2A レジスタと X2B レジスタを読み出すことはできず、ユーザーが直接書き込むこともできません。

X2A レジスタと X2B レジスタからのデータ出力は、マルチプレクサを介して最終 DAC レジスタに渡されます。4 個の DAC の各グループに対応している 4 ビットの A/B セレクト・レジスタは、各 DAC が X2A レジスタまたは X2B レジスタのいずれからデータを受け取るかを制御します。このレジスタのビットが 0 の場合、DAC はデータを X2A レジスタから受け取ります。1 の場合、DAC はデータを X2B レジスタから受け取ります。

2 つのレジスタに 8 ビットあるため、チャンネルごとに、各 DAC が X2A レジスタまたは X2B レジスタのいずれからデータを受け取るかを指定できることに注意してください。A/B セレクト・レジスタ内のすべてのビットを 0 または 1 に設定するグローバル・コマンドも用意しております。

各 DAC レジスタが A/B セレクト・レジスタの設定に応じて X2A レジスタまたは X2B レジスタから更新される際に、LDAC をロー・レベルにすることにより、AD5362/AD5363 内のすべての DAC を同時に更新することができます。DAC レジスタはユーザーが読み出すことはできず、直接書き込むこともできません。LDAC をロー・レベルに固定して、該当する DAC レジスタに新しいデータが入力されるごとに DAC 出力を更新することができます。

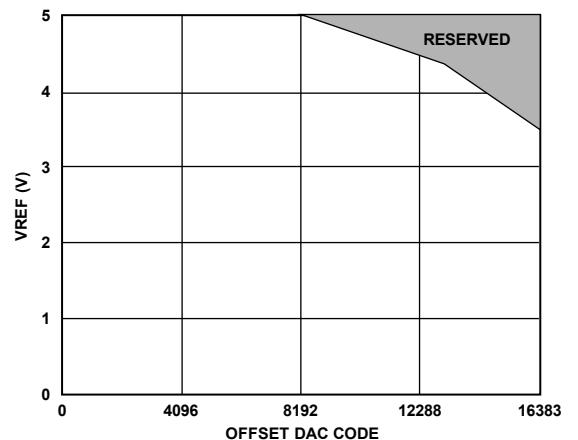

## オフセット DAC

各 DAC のゲインとオフセットの調整の他に、14 ビットのオフセット DAC がグループ 0 とグループ 1 に 1 個ずつ合計 2 個あります。これらを使うと、これらに接続されているすべての DAC の出力範囲に、所定の範囲内でオフセットを与えることができます。ヘッドルームの制限に従い、グループ 0 またはグループ 1 の出力範囲を正のユニポーラ、負のユニポーラ、または 0 V を中心とする対称または非対称のバイポーラに設定することができます。AD5362/AD5363 内の DAC は、出荷時にオフセット DAC にデフォルト値を設定した状態で設定されています。この設定は、デフォルトの出力範囲と振幅に対して最適なオフセット性能とゲイン性能を与えます。

オフセット DAC の値を変えて出力範囲を調整する際に、オフセット DAC のゲイン誤差のために余分なオフセットが導入されます。オフセット量は、リファレンス電圧の大きさと、デフォルト値からオフセット DAC が移動した大きさに依存します。このオフセットについては、仕様のセクションを参照してください。ワーストケース・オフセットは、オフセット DAC が正または負のフルスケールのときに発生します。この値は、そのチャンネルのオフセット全体を表示するために、メイン DAC チャンネルに存在するオフセットに加算することができます。多くの場合、チャンネルの C レジスタに適切な値を設定することにより、オフセットを除去することができます。オフセット DAC により発生した余分なオフセットは、オフセット DAC がデフォルト値から変更された場合にのみ考慮する必要があります。図 22 に、使用するリファレンス値に応じて、オフセット DAC にロードできる許容コード範囲を示します。5 V リファレンスの場合、オフセット DAC に 8192 (0x2000) より大きい値を設定することはできません。

図 22. オフセット DAC のコード範囲

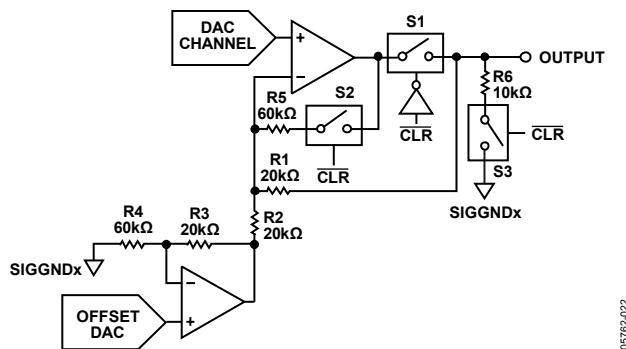

## 出力アンプ

出力アンプは、正電源の下側 1.4 V まで、および負電源の上側 1.4 V まで振れることができるため、これが与えられたリファレンス電圧に対して出力をオフセットできる限界を定めます。た

とえば、最大電源電圧が $\pm 16.5$  V の場合、20 V のユニポーラ出力範囲を持つことはできません。

図 23. 出力アンプとオフセット DAC

図 23 に、DAC 出力アンプとオフセット DAC への接続を示します。パワーアップ時、S1 はオープンになり、アンプを出力から切り離します。S3 は閉じて、出力が SIGGNDx にプルダウンされます(R1 と R2 は R6 より大)。S2 も閉じて、出力アンプがオープン・ループになるのを防止します。パワーアップ時に CLR がロー・レベルになると、CLR がハイ・レベルになるまで、出力はこの状態に留まります。DAC レジスタを設定することができるため、CLR がハイ・レベルになったとき、出力は設定された値になります。パワーアップ時に CLR をハイ・レベルにしても、 $V_{DD} > 6$  Vかつ  $V_{SS} < -4$  V で、さらに初期化シーケンスが完了するまで、出力はこの状態を維持します。その後、出力はパワー・オン・デフォルト値になります。

## 伝達関数

AD5362/AD5363 内の DAC の出力電圧は、入力レジスタの値、M レジスタと C レジスタの値、オフセット DAC の値に依存します。

### AD5362 の伝達関数

入力コードは DAC に入力される X1A レジスタまたは X1B レジスタの値です(X1A、X1B のデフォルト・コード=32,768)。

$$DAC\_CODE = INPUT\_CODE \times (M + 1)/2^{16} + C - 2^{15}$$

ここで、 $M$ =ゲイン・レジスタ内のコード-デフォルト・コード= $2^{16} - 1$ 。 $C$ =オフセット・レジスタ内のコード-デフォルト・コード= $2^{15}$ 。

DAC 出力電圧は次のように計算されます。

$$VOUT = 4 \times VREF \times (DAC\_CODE - (OFFSET\_CODE \times 4))/2^{16} + V_{SIGGND}$$

ここで、 $DAC\_CODE$  は 0~65,535 の範囲である必要があります。12 V 振幅の場合、 $VREF = 3.0$  V。20 V 振幅の場合、 $VREF = 5.0$  V。 $OFFSET\_CODE$  は、オフセット DAC にロードされるコード。この DAC は 14 ビット・デバイスであるため、伝達関数内で 4 倍されます。パワーアップ時に、オフセット DAC にロードされるデフォルト・コードは 8192 (0x2000)です。5 V リファレンスの場合、-10 V~+10 V の振幅になります。

### AD5363 の伝達関数

入力コードは DAC に入力される X1A レジスタまたは X1B レジスタの値です(X1A、X1B のデフォルト・コード=8192)。

$$DAC\_CODE = INPUT\_CODE \times (M + 1)/2^{14} + C - 2^{13}$$

ここで、 $M$ =ゲイン・レジスタ内のコード-デフォルト・コード= $2^{14} - 1$ 。 $C$ =オフセット・レジスタ内のコード-デフォルト・コード= $2^{13}$ 。

DAC 出力電圧は次のように計算されます。

$$VOUT = 4 \times VREF \times (DAC\_CODE - OFFSET\_CODE)/2^{14} + V_{SIGGND}$$

ここで、 $DAC\_CODE$  は 0~16,383 の範囲である必要があります。12 V 振幅の場合、 $VREF = 3.0$  V。20 V 振幅の場合、 $VREF = 5.0$  V。 $OFFSET\_CODE$  は、オフセット DAC にロードされるコード。パワー・アップ時に、オフセット DAC にロードされるデフォルト・コードは 8192 (0x2000)です。5 V リファレンスの場合、-10 V~+10 V の振幅になります。

## リファレンスの選択

AD5362/AD5363 には、リファレンス入力ピンが 2 本あります。リファレンス・ピンに加えられる電圧によって、VOUT0~VOUT7 の出力電圧振幅が決定されます。VREF0 が VOUT0~VOUT3 (グループ 0) の電圧振幅を、VREF1 が VOUT4~VOUT7 (グループ 1) の電圧振幅を、それぞれ決定します。各 VREF ピンに加えるリファレンス電圧は、必要に応じて異なることができるので、4 チャンネルの各グループが異なる電圧振幅を持つことができます。各チャネルのオフセット・レジスタとゲイン・レジスタ、およびオフセット DAC を設定することにより、出力電圧の範囲と振幅をさらに調整することができます。オフセット機能とゲイン機能を使わない(すなわち M レジスタと C レジスタをデフォルト値のままに維持する)場合、所要リファレンス・レベルは次のように計算されます。

$$VREF = (VOUT_{MAX} - VOUT_{MIN})/4$$

AD5362/AD5363 のオフセット機能とゲイン機能を使う場合、所要出力範囲は少し異なります。選択する出力範囲ではシステムのオフセット誤差とゲイン誤差を考慮する必要があります。これらを調整して除去する必要があります。したがって、選択する出力範囲は実際に必要とする範囲より広い必要があります。

所要リファレンス・レベルは次のように計算されます。

1. VOUT の公称出力範囲を決めます。

2. フル出力信号範囲に必要とされる最大オフセット振幅と最大ゲインを決定します。

3. 予想される最大オフセット誤差とゲイン誤差を含む、VOUT の新しい最大出力範囲を計算します。

4. 新しい所要  $VOUT_{MAX}$  と  $VOUT_{MIN}$  を選択して、公称値を中心とする VOUT 限界値を維持します。 $V_{DD}$  と  $V_{SS}$  は十分なヘッドラムを確保する必要があることに注意してください。

5. VREF 値を  $VREF = (VOUT_{MAX} - VOUT_{MIN})/4$  から求めます。

## リファレンス電圧の選択例

次の条件の場合、

公称出力範囲=20 V (-10 V~+10 V)

オフセット誤差= $\pm 100$  mV

ゲイン誤差= $\pm 3\%$ 、さらに

$SIGGND = AGND = 0$  V

次が得られます。

ゲイン誤差= $\pm 3\%$

$\Rightarrow$  正の最大ゲイン誤差= $3\% \Rightarrow$  ゲイン誤差を含む出力範囲 =  $20 + 0.03(20) = 20.6$  V

オフセット誤差= $\pm 100$  mV

$\Rightarrow$  最大オフセット誤差振幅 =  $2(100 \text{ mV}) = 0.2 \text{ V} \Rightarrow$  ゲイン誤差とオフセット誤差を含む出力範囲 =  $20.6 \text{ V} + 0.2 \text{ V} = 20.8 \text{ V}$

VREF の計算

実際の出力範囲 = 20.6 V、すなわち -10.3 V ~ +10.3 V (中心);  $V_{REF} = (10.3 \text{ V} + 10.3 \text{ V})/4 = 5.15 \text{ V}$

このソリューションから不便なリファレンス・レベルが得られる場合、ユーザーは次のいずれかの方法を探ることができます。

- 抵抗デバイダを使って、便利で高いリファレンス・レベルを所要レベルへ分圧します。

- $V_{REF}$  以上の便利なリファレンス・レベルを選択し、ゲイン・レジスタとオフセット・レジスタを変更して、デジタル的にリファレンスを下げます。この方法では、ほぼすべての便利なリファレンス・レベルを使用できますが、伝達関数の縮めすぎで性能が低下することがあります。

- これらの 2 つの方法の組み合わせを使います。

## キャリブレーション

AD5362/ AD5363 上でシステム・キャリブレーションを行って、ゲイン誤差とオフセット誤差を 1 LSB 以下にすることができます。この誤差の除去は、M レジスタと C レジスタの新しい値を計算して再設定することにより行われます。

ゼロ・スケール誤差とフル・スケール誤差が計算されるまで、M レジスタと C レジスタを設定しないようにする必要があります。

### ゼロ・スケール誤差の除去

ゼロ・スケール誤差は、次のようにして除去できます。

1. 出力を最小値に設定します。

2. 実際の出力電圧と所要値を比較します。これにより、ゼロ・スケール誤差が得られます。

3. 誤差に相当する LSB 数を計算し、この値を C レジスタのデフォルト値に加算します。負のゼロ・スケール誤差のみが除去されることに注意してください。

### フル・スケール誤差の除去

フル・スケール誤差は、次のようにして除去できます。

1. ゼロ・スケール誤差を測定します。

2. 出力を最大値に設定します。

3. 実際の出力電圧と所要値を比較します。この誤差をゼロ・スケール誤差に加算します。これが振幅誤差で、フル・スケール誤差を含んでいます。

4. 振幅誤差に相当する LSB 数を計算し、M レジスタのデフォルト値からこの値を減算します。正のフル・スケール誤差のみが除去されることに注意してください。

### AD5362 のキャリブレーション例

この例では、-10 V ~ +10 V が所要出力と仮定します。DAC 出力を -10 V に設定しますが、-10.03 V と測定されています。したがって、ゼロ・スケール誤差は -30 mV です。

$$1 \text{ LSB} = 20 \text{ V}/65,536 = 305.176 \mu\text{V}$$

$$30 \text{ mV} = 98 \text{ LSB}$$

これで、フル・スケール誤差が計算できます。出力を 10 V に設定し、10.02 V と測定されます。これで、フル・スケール誤差は +20 mV、振幅誤差は +20 mV - (-30 mV) = +50 mV になります。

$$50 \text{ mV} = 164 \text{ LSB}$$

この誤差は次のようにして、除去できます。

1. 98 LSB を C レジスタのデフォルト値に加算します:  $(32,768 + 98) = 32,866$ 。

2. M レジスタのデフォルト値から 164 LSB を減算します:  $(65,535 - 164) = 65,371$ 。

3. M レジスタに 65,371 を、C レジスタに 32,866 を、それぞれ設定します。

### その他のキャリブレーション

前のセクションで説明した技術は、大部分のアプリケーションでゼロ・スケール誤差とフル・スケール誤差を除去する十分な方法ですが、誤差が十分に除去できないという制約があります。たとえば、オフセット(C)レジスタは負のゼロ・スケール誤差から発生するオフセットの削減にのみに使用できることです。正のオフセットは除去できません。同様に、最大電圧が理論値より小さい場合、すなわちフル・スケール誤差が負の場合、ゲイン(M)レジスタを使ってゲインを増やして、誤差を補償することはできません。

これらの制約は、リファレンス値を大きくすることにより克服することはできません。リファレンスが 2.5 V の場合、10 V の振幅が実現できます。AD5362 または AD5363 の理論電圧範囲は -5 V ~ +5 V です。+2.6 V のリファレンスを使うと、範囲を -5.2 V ~ +5.2 V に広げることができます。明らかに、この場合、オフセット誤差とゲイン誤差が小さいので、M レジスタと C レジスタを使って、負電圧を -5 V へ持ち上げて最大電圧を +5 V に下げるにより最も正確な値を得ることができます。

## リセット機能

リセット機能はRESETピンにより起動されます。RESETの立ち上がりエッジで、AD5362/AD5363 のステート・マシンがリセット・シーケンスを開始して、X、M、C の各レジスタをデフォルト値にリセットします。このシーケンスには 300 μs 要し、この期間中デバイスへの書き込みはできません。パワーアップ後、レジスタを正しく初期化するため、できるだけ速やかにRESETをハイ・レベルにすることが推奨されます。

リセット・シーケンスが完了すると( CLRがハイ・レベル)、DAC 出力はデフォルト・レジスタ設定が指定する電位(SIGGND<sub>x</sub>)になります。X、M、または C の各レジスタが更新されて、LDACがロー・レベルになるまで、DAC 出力は SIGGND<sub>x</sub> を維持します。少なくとも 30 ns 間RESETをロー・レベルにした後ハイ・レベルに戻すと、AD5362/AD5363 をデフォルト状態に戻すことができます。リセット機能は立ち上がりエッジで開始されるため、RESETをロー・レベルにするだけでは AD5362/AD5363 の動作に影響しないことに注意してください。

## クリア機能

CLR はアクティブ・ロー入力であり、通常動作ではハイ・レベルにしておく必要があります。CLRピンには 500 kΩ の内部プルダウン抵抗がついています。CLRをロー・レベルにすると、各 DAC 出力バッファステージ(VOUT0~VOUT7)への入力は、該当する SIGGND<sub>x</sub> ピンを使って外部から設定された電位に切り替えられます。CLRがロー・レベルの間、すべてのLDACパルスは無視されます。CLRがハイ・レベルに戻ると、DAC 出力は前の値に戻ります。入力レジスタの値と DAC レジスタ 0~DAC レジスタ 7 の値は、CLRがロー・レベルになつても影響を受けません。出力にグリッチが発生するのを防止するため、オフセット DACへ書き込みを行って出力振幅を調整するたびに、CLRをロー・レベルにする必要があります。

## BUSY 機能と LDAC 機能

新しいデータを対応する X1、C、M の各レジスタに書き込むたびに、X2 (A または B) レジスタの値が計算されます。X2 の計算中、BUSY出力はロー・レベルになります。BUSYがロー・レベルの間、X1、M、または C の各レジスタへの新しいデータの書き込みを続けることができますが、DAC 出力は更新できません(詳細については、レジスタ更新レートのセクション参照)。

BUSYピンは双方向ピンであり、50 kΩ の内部プルアップ抵抗がついています。複数の AD5362 デバイスまたは AD5363 デバイスを 1 つのシステムで使用する場合には、BUSYピンを相互に接続することができます。他のすべての DAC がレディになるまで、いずれのデバイス内の DAC も更新できないことが要請される場合には、この機能が便利です。各デバイスが X2 (A または B) レジスタの更新を完了すると、BUSYピンを解除します。あるデバイスが X2 レジスタの更新を完了していない場合には、そのデバイスがBUSYをロー・レベルにするため、LDACがロー・レベルになるのが遅延されます。

LDAC入力をロー・レベルにすると、DAC 出力は更新されます。BUSYがアクティブのときにLDACをロー・レベルにすると、LDACイベントが保存され、BUSYがハイ・レベルになると直ちに DAC レジスタが更新されます。LDAC入力をロー・レベルに固定することもできます。この場合、BUSYがハイ・レベルになると直ちに DAC 出力が更新されます。A/B セレクト・レジスタに書き込みが行われるごとに、BUSYも約 600 ns 間ロー・レベルになります。

AD5362/AD5363 は、1 つのチャンネル、グループ内のすべてのチャンネル、またはデバイス内の全チャンネルに対してデータの書き込みを可能にする柔軟なアドレッシング機能を持っています。これは、1 個、2 個、4 個、または 8 個の DAC レジスタ値を計算して更新することを意味しています。1 個の乗算器を 8 チャンネル間で共用しているため、この作業はシーケンシャルに実行する必要があります。したがって、BUSYパルスの継続時間は、更新するチャンネル数に応じて変わります。

表 9.BUSY パルス幅

| Action                                           | BUSY Pulse Width <sup>1</sup> |

|--------------------------------------------------|-------------------------------|

| Loading input, C, or M to 1 channel <sup>2</sup> | 1.5 μs maximum                |

| Loading input, C, or M to 2 channels             | 2.1 μs maximum                |

| Loading input, C, or M to 8 channels             | 5.7 μs maximum                |

<sup>1</sup> BUSY パルス幅 = ((チャンネル数 + 1) × 600 ns) + 300 ns。

<sup>2</sup> 1 チャンネルの更新には 1 μs(typ) を要します。

AD5362/AD5363 には追加機能があります。この機能を使うと、LDACがロー・レベルになった後に X2A または X2B レジスタに書き込みが済んでいない場合、これが済むまで DAC レジスタの更新を行わないことができます。通常、LDACロー・レベルになると、A/B セレクト・レジスタの設定に応じて、DAC レジスタには X2A または X2B レジスタ値がロードされます。ただし、X2A または X2B データが変更された場合にのみ、AD5362/AD5363 は DAC レジスタを更新するため、不要なデジタル・クロストークが発生しません。

## BIN/2SCOMP ピン

BIN/2SCOMP ピンは、出力データ・フォーマット(オフセット・バイナリまたは 2 の補数)を指定します。このピンをロー・レベルにすると、データはストレート・バイナリになります。ハイ・レベルにすると、データは 2 の補数になります。このピンは X レジスタ、C レジスタ、オフセット DAC レジスタに対してのみ有効で、M レジスタとコントロールおよびコマンド・データは、ストレート・バイナリとして解釈されます。

## 温度センサー

内蔵の温度センサーは TEMP\_OUT ピンに電圧を出力します。この電圧は摂氏温度に比例しています。温度センサーの精度(typ)は +25°C で +1°C、-40°C ~ +85°C の範囲で ±5°C です。公称出力電圧は 25°C で 1.46 V、4.4 mV/°C で変化します。出力インピーダンスが小さく、自己発熱が小さく、かつ出力がリニアであるため、温度制御回路や A/D コンバータへのインターフェースが簡素化されます。

## モニター機能

AD5362/AD5363 は、インターフェースを介してアドレス指定されるアナログ・マルチプレクサから構成されるチャンネル・モニタ機能を内蔵しているため、任意のチャンネル出力を MON\_OUT ピンに接続することができるので、外付け ADC を使ってモニタリングすることができます。さらに、2 つのモニター入力(MON\_IN0 と MON\_IN1)を持っており、これを MON\_OUT に接続することができます。モニター機能はモニター・レジスタから制御されます。この機能を使うと、モニター出力をイネーブルまたはディスエーブルすることができ、DAC チャンネルまたはモニター・ピンの 1 つを選択することができます。複数のモニター出力を並列に接続して、1 回に 1 つだけをイネーブルできるように、ディスエーブル時にモニター出力が高インピーダンスになります。表 10 に、モニター・レジスタの設定を示します。

表 10. モニター・レジスタの機能

| F5 | F4 | F3 | F2 | F1 | F0 | Function          |

|----|----|----|----|----|----|-------------------|

| 0  | X  | X  | X  | X  | X  | MON_OUT disabled  |

| 1  | X  | X  | X  | X  | X  | MON_OUT enabled   |

| 1  | 0  | 0  | 0  | 0  | 0  | MON_OUT = VOUT0   |

| 1  | 0  | 0  | 0  | 0  | 1  | MON_OUT = VOUT1   |

| 1  | 0  | 0  | 0  | 1  | 0  | MON_OUT = VOUT2   |

| 1  | 0  | 0  | 0  | 1  | 1  | MON_OUT = VOUT3   |

| 1  | 0  | 1  | 0  | 0  | 0  | MON_OUT = VOUT4   |

| 1  | 0  | 1  | 0  | 0  | 1  | MON_OUT = VOUT5   |

| 1  | 0  | 1  | 0  | 1  | 0  | MON_OUT = VOUT6   |

| 1  | 0  | 1  | 0  | 1  | 1  | MON_OUT = VOUT7   |

| 1  | 1  | 0  | 0  | 0  | 0  | MON_OUT = MON_IN0 |

| 1  | 1  | 0  | 0  | 0  | 1  | MON_OUT = MON_IN1 |

マルチプレクサは、アナログ・スイッチの直列接続として構成されています。このため、マルチプレクサの入力(VOUTx または MON\_INx)からマルチプレクサの出力(MON\_OUT)へ大きな電流が流れる可能性があるため、MON\_OUT ピンに接続するものはすべて高インピーダンスにして、連続電流制限仕様を超えないようにする必要があります。MON\_OUT ピンにはバッファが付いていないため、このピンから流れる電流によりスイッチに電圧降下が発生します。これがモニター対象の電圧に誤差を発生させます。精度が重要な場合には、MON\_OUT ピンにバッファを付けることが推奨されます。図 20 に、MON\_OUT 電流から発生する誤差(typ)を示します。

## GPIO ピン

AD5362/AD5363 は、汎用 I/O ピン(GPIO)を 1 本持っています。このピンは入力または出力に設定でき、シリアル・インターフェースを介してリードバックするか、またはハイ/ロー・レベルに設定することができます。このピンのアプリケーションとしては、ロジック信号やリミット・スイッチのステータスのモニター、または外付けマルチプレクサの制御などがあります。GPIO ピンは、スペシャル・ファンクション・コード 001101 を持つ GPIO レジスタ(表 15 と表 16 参照)に対する書き込みによって設定されます。

ビット F1 をセットすると、GPIO ピンは出力になり、ビット F0 で+ピンのハイ/ロー・レベルを指定します。0 をビット F1 とビット F0 に書き込むと、GPIO ピンを入力に設定することができます。表 17 内の該当するビットを使って読み出し動作を開始すると、GPIO ピンのステータスを読み出すことができます。このピンのステータスは、読み出したレジスタの LSB で表示されます。

## パワーダウン・モード

コントロール・レジスタのビット 0 を 1 に設定すると、AD5362/AD5363 はパワーダウンします。これにより DAC がタンオフされるため、消費電流を減らすことができます。DAC 出力は、該当する SIGGNDx 電位に接続されます。パワーダウン・モードでレジスタ値は変更されないため、パワーダウン・ビットが 0 にクリアされると、DAC は前の電圧に戻ります。

## サーマル・シャットダウン機能

チップ温度が 130°C を超えたとき、AD5362/AD5363 が DAC をシャットダウンするように設定することができます。コントロール・レジスタのビット 1 を 1 に設定すると、この機能がイネーブルされます(表 16 参照)。チップ温度が 130°C を超えると、AD5362/AD5363 サーマル・シャットダウン・モードになります。これは、コントロール・レジスタのパワーダウン・ビットをセットすることと同じです。AD5362/AD5363 がサーマル・シャットダウン・モードになったことを表示するため、コントロール・レジスタのビット 4 が 1 に設定されます。AD5362/AD5363 は、チップ温度が下がっても、コントロール・レジスタのビット 1 が 0 にクリアされるまで、サーマル・シャットダウン・モードに留まります。

## トグル・モード

AD5362/AD5363 はチャンネルごとに 2 個の X2 レジスタ(X2A と X2B)を持っています。これらのレジスタを使うと、DAC 出力を 2 つのレベル間で容易に切り替えることができます。この方法を使うと、マイクロプロセッサのオーバーヘッドを大幅に減らすことができます。この方法を使わないと、各チャンネルに個別に書き込みを行う必要があるためです。X1A、X1B、M、または C の各レジスタに書き込みを行うと、計算エンジンは、該当する X2A または X2B の値を計算するために所定の時間を必要とします。データ・ジェネレータのようなアプリケーションで、2 つのレベル間でのみ DAC 出力の切り替えが必要な場合、計算時間を削減するどのような方法でも利点があります。データ・ジェネレータの例の場合、X1A レジスタと X1B レジスタへ書き込みを行った後に、各チャンネルにハイ・レベルとロー・レベルを設定するだけで済みます。X2A と X2B の値が計算されて、該当するレジスタに保存されます。このため、計算遅延はセットアップのフェーズ、すなわち初期値の設定でのみ発生します。2 つのレベル間で DAC 出力をトグルするときは、関係する A/B セレクト・レジスタに書き込みを行って、MUX2 レジスタ・ビットを設定するだけで済みます。さらに、レジスタごとに 4 個の MUX2 コントロール・ビットがあるため、2 回の書き込みだけで 8 チャンネルを更新することができます。表 18 に、各 DAC 出力に対応するビットを示します。

## シリアル・インターフェース

AD5362/AD5363 は、最大 50 MHz (読み出し動作は 20 MHz) のクロック周波数で動作する高速 SPI を内蔵しています。デバイスに書き込みを行うときだけ、すなわち SYNC の立ち下がりエッジでのみ、インターフェースをパワーアップさせるため、デバイスの消費電力とチップ内のデジタル・ノイズを最小にすることができます。シリアル・インターフェースは、2.5 V ~ 3.6 V DV<sub>CC</sub> 電源で動作する場合、2.5 V の LVTTL と互換です。このインターフェースは、SYNC (フレーム同期化入力)、SDI (シリアル・データ入力ピン)、SCLK (デバイスに対するデータの入出力クロック)、SDO (データ・リードバック用のシリアル・データ出力ピン) の 4 本のピンで制御されます。

### SPI 書き込みモード

AD5362/AD5363 では、シリアル・インターフェースを使って、シリアル・インターフェースから直接アクセス可能な各レジスタすなわち X2A、X2B、DAC の各レジスタを除くすべてのレジスタに対してデータの書き込みが可能です。X2A レジスタと X2B レジスタは、X1A、X1B、M、C の各レジスタに書き込みを行ったときに更新され、DAC データ・レジスタは、LDAC により更新されます。シリアル・ワード(表 11 または表 12 参照)は 24 ビット長で、データ・ビットが 16 (AD5362) ビットまたは 14 (AD5363) ビット、アドレス・ビットが 6 ビット、モード・ビットが 2 ビット (データの処理を指定) です。AD5363 では、2 ビットは未使用です。

シリアル・インターフェースは連続およびバースト(ゲーティングされた)シリアル・クロックで動作します。SDI に入力されるシリアル・データは、SCLK に入力されるクロック・パルスにより AD5362/AD5363 に入力されます。SYNC の最初の立ち下がりエッジで書き込みサイクルが開始されます。24 ビットのデータを入力するためには、SYNC をハイ・レベルに戻す前に、少なくとも 24 個の立ち下がりクロック・エッジを SCLK に入力する必要があります。24 個目の立ち下がりクロック・エッジの前に SYNC をハイ・レベルにすると、書き込み動作はアボートされます。

連続クロックを使用する場合、25 個目の立ち下がりクロック・エッジの前に SYNC をハイ・レベルにする必要があります。これにより、AD5362/AD5363 内部でクロックが停止されます。SYNC がハイ・レベルに戻る前に、24 個より多くの立ち下がりクロック・エッジを入力すると、入力データは破壊されます。外部でゲーティングした 24 個のクロック・パルスを使う場合は、24 個目の立ち下がりクロック・エッジの前の任意のタイミングで SYNC をハイ・レベルにすることができます。

表 11. AD5362 シリアル・ワードのビット配置

| I23 | I22 | I21 | I20 | I19 | I18 | I17 | I16 | I15 | I14 | I13 | I12 | I11 | I10 | I9 | I8 | I7 | I6 | I5 | I4 | I3 | I2 | I1 | I0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| M1  | M0  | A5  | A4  | A3  | A2  | A1  | A0  | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

表 12. AD5363 シリアル・ワードのビット配置

| I23 | I22 | I21 | I20 | I19 | I18 | I17 | I16 | I15 | I14 | I13 | I12 | I11 | I10 | I9 | I8 | I7 | I6 | I5 | I4 | I3 | I2 | I1 <sup>1</sup> | I0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|-----------------|----|

| M1  | M0  | A5  | A4  | A3  | A2  | A1  | A0  | D13 | D12 | D11 | D10 | D9  | D8  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 0               | 0  |

<sup>1</sup> ビット 1 とビット I0 は将来用途に予約されています。シリアル・ワードを書き込む際は 0 を書き込んでください。読み出すと、0 が返されます。

アドレス指定された入力レジスタは、SYNC の立ち上がりエッジで更新されます。次のシリアル転送を行うときは、SYNC をロー・レベルに戻す必要があります。

### SPI リードバック・モード

AD5362/AD5363 では、シリアル・インターフェースを使って、シリアル・インターフェースから直接アクセス可能な各レジスタすなわち X2A、X2B、DAC データの各レジスタを除くすべてのレジスタからデータのリードバックが可能です。レジスタをリードバックするときは、最初に読み出し対象のレジスタを AD5362/AD5363 に知らせる必要があります。これは、先頭の 2 ビットがスペシャル・ファンクション・コード 00 であるワードをデバイスに書き込むことにより行われます。その後の残りのビットで、リードバック対象レジスタが指定されます。

リードバック・コマンドがスペシャル・ファンクション・レジスタに書き込まれると、選択したレジスタからデータが次の SPI 動作で SDO ピンへ出力されます。SDO ピンは通常スリー・ステートですが、読み出しコマンドが発行されると直ちに駆動状態になります。このピンは、レジスタ・データが出力されるまで駆動状態を維持します。読み出しタイミング図については、図 5 を参照してください。タイミング条件 t<sub>22</sub> (25 ns) があるため、読み出し動作時の SPI インターフェースの最大速度は 20 MHz を超えないことに注意してください。

### レジスタ更新率

新しいデータを対応する X1、C、M の各レジスタに書き込むたびに、X2A レジスタまたは X2B レジスタの値が計算されます。計算は 3 ステージのプロセスで実行されます。最初の 2 ステージはそれぞれ約 600 ns を要し、3 番目のステージは約 300 ns を要します。X1、C、または M の各レジスタへの書き込みが完了すると、計算プロセスが開始されます。1 個の DAC チャンネルを更新する書き込み動作では、最初のステージの計算が完了する前に、すなわち最初の書き込み動作完了から 600 ns までに書き込み動作が完了しない場合でも、別のレジスタへ自由に書き込みを行うことができます。1 回の書き込み動作でチャンネルのグループを更新する場合には、最初のステージの計算が各チャンネルごとに繰り返されるため、各チャンネルに 600 ns を要します。この場合、この時間が経過するまで次の書き込み動作を完了することはできません。

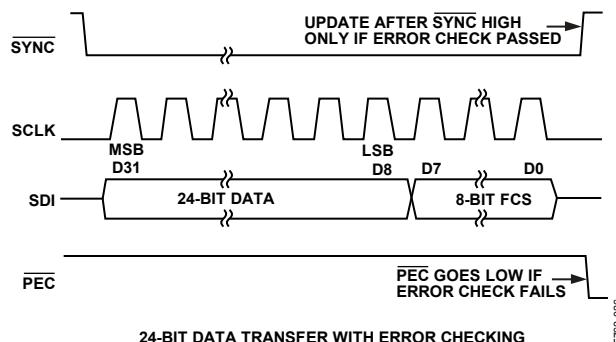

## パケット・エラーのチェック

ノイズの多い環境でデータが正しく受信されたことを確認するため、AD5362/AD5363 は 8 ビット(CRC-8)サイクリック冗長性チェックを採用したエラー・チェック機能のオプションを提供します。AD5362/AD5363 を制御するデバイスは、多項式  $C(x) = x^8 + x^2 + x^1 + 1$  を使って 8 ビット・チェックサムを生成する必要があります。このチェックサムはデータ・ワードの終わりに追加され、32 ビットのデータが SYNC がハイ・レベルになる前に AD5362/AD5363 へ送信されます。AD5362/AD5363 が 32 ビットのデータ・フレームを受け取ると、SYNC がハイ・レベルになったときにエラー・チェックを実行します。チェックサムが有効な場合は、データが選択されたレジスタへ書き込まれます。チェックサムが無効な場合は、パケット・エラー・チェック(PEC)出力がロー・レベルになり、コントロール・レジスタのビット 3 がセットされます。コントロール・レジスタを読み出すと、ビット 3 が自動的にクリアされて、PEC がハイ・レベルに戻ります。

図 24. エラー・チェックありとなしの場合の SPI 書き込み

## チャンネル・アドレッシングとスペシャル・モード

モード・ビットが 00 でない場合、データ・ワード D15~D0 (AD5362) または D13~D0 (AD5363) がデバイスへ書き込まれます。アドレス・ビット A4 ~ アドレス・ビット A0 によって書き込み対象チャンネルが、モード・ビットによってデータの書き込み対象レジスタ(X1A、X1B、C、または M)が、それぞれ指定されます(表 13 と表 14 参照)。データは、コントロール・レジスタの A/B ビットが 0 の場合には X1A レジスタへ、または A/B ビットが 1 の場合には X1B レジスタへ、それぞれ書き込まれます。

AD5362/AD5363 は、1 つのチャンネル、グループ内のすべてのチャンネル、またはデバイス内の全チャンネルに対してデータの書き込みを可能にする柔軟なアドレッシング機能を持っています。表 14 に、アドレス・ビット A4 ~ アドレス・ビット A0 の組み合わせによって指定されるグループとチャンネルを示します。

表 13. モード・ビット

| M1 | M0 | Action                                                                 |

|----|----|------------------------------------------------------------------------|

| 1  | 1  | Write to DAC data (X) register                                         |

| 1  | 0  | Write to DAC offset (C) register                                       |

| 0  | 1  | Write to DAC gain (M) register                                         |

| 0  | 0  | Special function, used in combination with other bits of the data-word |

表 14. グループとチャンネルのアドレッシング

| Address Bit A2<br>to Address Bit A0 | Address Bit A4 to Address Bit A3 |     |    |                          |

|-------------------------------------|----------------------------------|-----|----|--------------------------|

|                                     | 00                               | 01  | 10 | 11                       |

| 000                                 | All groups, all channels         | 000 |    | All groups, all channels |

| 001                                 | Group 0, all channels            | 001 |    | Group 0, all channels    |

| 010                                 | Group 1, all channels            | 010 |    | Group 1, all channels    |

| 011                                 | Unused                           | 011 |    | Unused                   |

| 100                                 | Unused                           | 100 |    | Unused                   |

| 101                                 | Unused                           | 101 |    | Unused                   |

| 110                                 | Unused                           | 110 |    | Unused                   |

| 111                                 | Unused                           | 111 |    | Unused                   |

## スペシャル・ファンクション・モード

モード・ビットが 00 の場合、スペシャル・ファンクション・モードが選択されます(表 15 参照)。シリアル・データ・ワードのビット I21 ~ ビット I16 によって、スペシャル・ファンクションが選択され、残りのビットは、スペシャル・ファンクションの実行に必要とされるデータであり、たとえば、データ・リードバックでのチャンネル・アドレスなどになります。スペシャル・ファンクションのコードを表 16 に示します。表 17 には、データ・リードバックのアドレスを示します。

表 15.スペシャル・ファンクション・モード

| I23 | I22 | I21 | I20 | I19 | I18 | I17 | I16 | I15 | I14 | I13 | I12 | I11 | I10 | I9 | I8 | I7 | I6 | I5 | I4 | I3 | I2 | I1 | I0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 0   | 0   | S5  | S4  | S3  | S2  | S1  | S0  | F15 | F14 | F13 | F12 | F11 | F10 | F9 | F8 | F7 | F6 | F5 | F4 | F3 | F2 | F1 | F0 |

表 16.スペシャル・ファンクション・コード

| Special Function Code |    |    |    |    |    | Data (F15 to F0)          | Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|----|----|----|----|----|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S5                    | S4 | S3 | S2 | S1 | S0 |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                     | 0  | 0  | 0  | 0  | 0  | 0000 0000 0000 0000       | NOP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0                     | 0  | 0  | 0  | 0  | 1  | XXXX XXXX XXXX X [F2:F0]  | Write control register.<br>F4 = 1: Temperature over 130°C.<br>F4 = 0: Temperature below 130°C.<br>Read-only bit. This bit should be 0 when writing to the control register.<br>F3 = 1: PEC error.<br>F3 = 0: No PEC error. Reserved.<br>Read-only bit. This bit should be 0 when writing to the control register.<br>F2 = 1: Select Register X1B for input.<br>F2 = 0: Select Register X1A for input.<br>F1 = 1: Enable thermal shutdown mode.<br>F1 = 0: Disable thermal shutdown mode.<br>F0 = 1: Software power-down.<br>F0 = 0: Software power-up. |

| 0                     | 0  | 0  | 0  | 1  | 0  | XX [F13:F0]               | Write data in F13 to F0 to OFS0 register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0                     | 0  | 0  | 0  | 1  | 1  | XX [F13:F0]               | Write data in F13 to F0 to OFS1 register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0                     | 0  | 0  | 1  | 0  | 0  | Reserved                  | Select register for readback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0                     | 0  | 0  | 1  | 0  | 1  | See Table 17              | Write data in F3 to F0 to A/B Select Register 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0                     | 0  | 0  | 1  | 1  | 0  | XXXX XXXX XXXX [F3:F0]    | Write data in F3 to F0 to A/B Select Register 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0                     | 0  | 1  | 0  | 0  | 0  | Reserved                  | Block write to A/B select registers.<br>F7 to F0 = 0: Write all 0s (all channels use X2A register).<br>F7 to F0 = 1: Write all 1s (all channels use X2B register).                                                                                                                                                                                                                                                                                                                                                                                     |

| 0                     | 0  | 1  | 0  | 0  | 1  | Reserved                  | F5 = 1: Monitor enable.<br>F5 = 0: Monitor disable.<br>F4 = 1: Monitor input pin selected by F0.<br>F4 = 0: Monitor DAC channel selected by F3:F0 (see Table 10).<br>F3 = not used if F4 = 1.<br>F2 = not used if F4 = 1.<br>F1 = not used if F4 = 1.<br>F0 = 0: MON_IN0 selected for monitoring (if F4 and F5 = 1).<br>F0 = 1: MON_IN1 selected for monitoring (if F4 and F5 = 1).                                                                                                                                                                    |

| 0                     | 0  | 1  | 1  | 0  | 0  | XXXX XXXX XX [F5:F0]      | GPIO configure and write.<br>F1 = 1: GPIO is an output. Data to output is written to F0.<br>F1 = 0: GPIO is an input. Data can be read from F0 on readback.                                                                                                                                                                                                                                                                                                                                                                                            |

| 0                     | 0  | 1  | 1  | 0  | 1  | XXXX XXXX XXXX XX [F1:F0] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

表 17. データ・リードバックのアドレス・コード1

| F15 | F14 | F13 | F12 | F11 | F10 | F9 | F8 | F7 | Register Read                       |

|-----|-----|-----|-----|-----|-----|----|----|----|-------------------------------------|

| 0   | 0   | 0   |     |     |     |    |    |    | X1A register                        |

| 0   | 0   | 1   |     |     |     |    |    |    | X1B register                        |

| 0   | 1   | 0   |     |     |     |    |    |    | C register                          |

| 0   | 1   | 1   |     |     |     |    |    |    | M register                          |

| 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 1  | Control register                    |

| 1   | 0   | 0   | 0   | 0   | 0   | 0  | 1  | 0  | OFS0 data register                  |

| 1   | 0   | 0   | 0   | 0   | 0   | 0  | 1  | 1  | OFS1 data register                  |

| 1   | 0   | 0   | 0   | 0   | 0   | 1  | 0  | 0  | Reserved                            |

| 1   | 0   | 0   | 0   | 0   | 0   | 1  | 1  | 0  | A/B Select Register 0               |

| 1   | 0   | 0   | 0   | 0   | 0   | 1  | 1  | 1  | A/B Select Register 1               |

| 1   | 0   | 0   | 0   | 0   | 1   | 0  | 0  | 0  | Reserved                            |

| 1   | 0   | 0   | 0   | 0   | 1   | 0  | 0  | 1  | Reserved                            |

| 1   | 0   | 0   | 0   | 0   | 1   | 0  | 1  | 0  | Reserved                            |

| 1   | 0   | 0   | 0   | 0   | 1   | 0  | 1  | 1  | GPIO read (data in F0) <sup>2</sup> |

<sup>1</sup> データ・リードバック機能に対してビット F6～ビット F0 は don't care。<sup>2</sup> GPIO 読み出しの場合、ビット F6～Bit F0 は 0。

表 18.A/B セレクト・レジスタで選択される DAC

| A/B Select<br>Register | Bits <sup>1</sup> |          |          |          |       |       |       |       |

|------------------------|-------------------|----------|----------|----------|-------|-------|-------|-------|

|                        | F7                | F6       | F5       | F4       | F3    | F2    | F1    | F0    |

| 0                      | Reserved          | Reserved | Reserved | Reserved | DAC 3 | DAC 2 | DAC 1 | DAC 0 |