## 特長

### AD5337

バッファ付き8ビットDAC、8ピンMSOP、2個

### AD5338

バッファ付き10ビットDAC、8ピンMSOP、2個

### AD5339

バッファ付き12ビットDAC、8ピンMSOP、2個

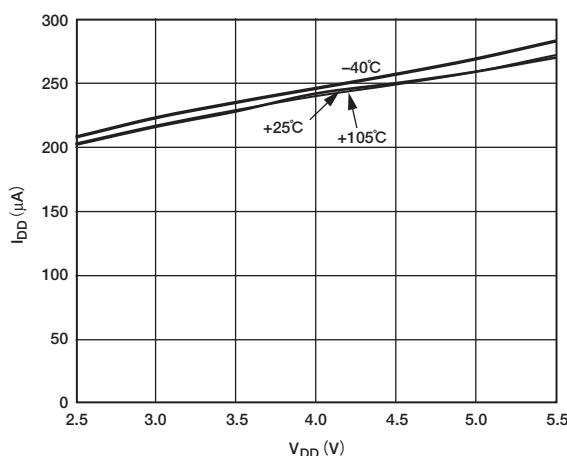

低消費電力動作：3Vで250 $\mu$ A、5Vで300 $\mu$ A

2線式（I<sup>2</sup>C互換）シリアル・インターフェース

電源：2.5~5.5V

全コードについて設計により単調性を保証

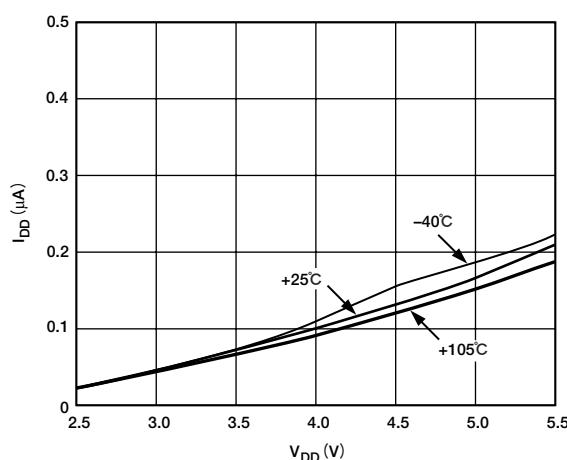

3Vで80nA、5Vで200nAにパワーダウン

3つのパワーダウン・モード

ダブル・バッファ入力ロジック

出力レンジ： $0V \sim V_{REF}$

0Vへのパワーオン・リセット

出力の同時更新（LDAC機能）

ソフトウェア・クリア機能

データ・リードバック機能

レールtoレール出力バッファ・アンプ内蔵

温度範囲：-40~+105°C

## アプリケーション

携帯型バッテリ駆動機器

ゲイン/オフセットのデジタル調整

プログラマブルな電圧/電流源

プログラマブル減衰器

工業プロセス制御

## 概要

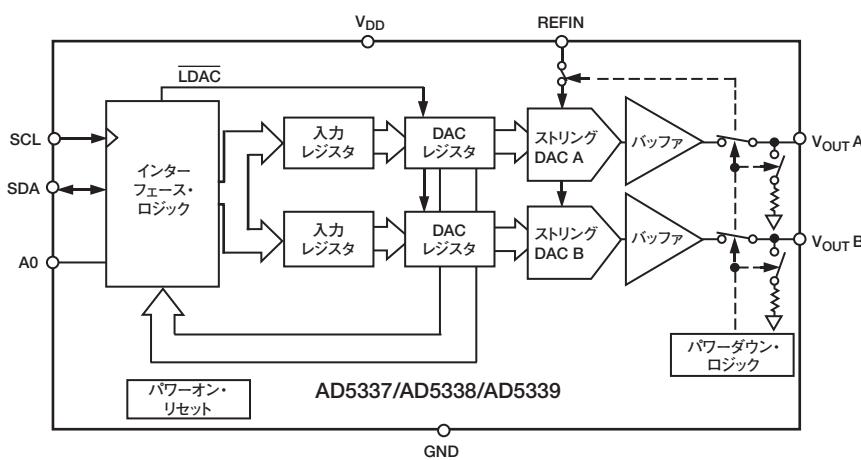

AD5337/AD5338/AD5339は、8、10、12ビットのデュアル・バッファ電圧出力DACです。8ピンMSOPパッケージを採用し、2.5~5.5Vの单電源で動作し、3Vで250 $\mu$ Aを消費します。内蔵の出力アンプにより、0.7V/ $\mu$ sのスルーレートでレールtoレールの出力振幅が得られます。最大400kHzのクロック・レートで動作する2線式シリアル・インターフェースは、 $V_{DD} < 3.6V$ でSMBus互換です。同じバスに複数のデバイスを割り当てることができます。

1本のリファレンス・ピンから2つのDACのリファレンスが得られます。すべてのDACの出力は、ソフトウェアLDAC機能を使用して同時に更新できます。内蔵のパワーオン・リセット回路によって、DAC出力はパワーアップ時に0Vになり、デバイスに有効な書き込みが行われるまで、その状態にとどまります。また、すべての入力レジスタとDACレジスタを0Vにリセットするソフトウェア・クリア機能も備えています。さらに、デバイスの消費電流を5Vで200nA（3Vで80nA）に低減するパワーダウン機能もあります。

これらのデバイスは、通常動作での消費電力が低いため、携帯型バッテリ駆動機器に最適です。消費電力は5Vで1.5mW、3Vで0.75mW（いずれもtyp値）ですが、パワーダウン・モードでは1 $\mu$ Wまで低下します。

この3つのデバイスはすべてピン互換であり、ユーザーは回路ボードのデザインを変更することなく、アプリケーションに適した分解能を選択することができます。

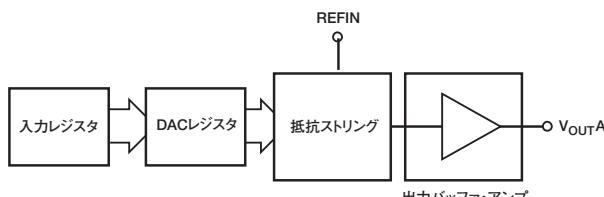

## 機能ブロック図

# AD5337/AD5338/AD5339

## AD5337/AD5338/AD5339—仕様

(特に指定のない限り、 $V_{DD}=2.5\sim 5.5V$ 、 $V_{REF}=2V$ 、 $R_L=GND$ に対し $2k\Omega$ 、 $C_L=GND$ に対し $200pF$ 、すべての仕様は $T_{MIN}\sim T_{MAX}$ で規定)

| パラメータ <sup>1</sup>            | グレードA<br>Min<br>Typ<br>Max | グレードB<br>Min<br>Typ<br>Max  | 単位                   | Bバージョン <sup>2</sup><br>条件／備考                                     |                                  |

|-------------------------------|----------------------------|-----------------------------|----------------------|------------------------------------------------------------------|----------------------------------|

| <b>DC性能<sup>3, 4</sup></b>    |                            |                             |                      |                                                                  |                                  |

| AD5337                        |                            |                             |                      |                                                                  |                                  |

| 分解能                           | 8                          | 8                           | ピット                  |                                                                  |                                  |

| 相対精度                          | $\pm 0.15$                 | $\pm 0.15$                  | LSB                  |                                                                  |                                  |

| 微分非直線性                        | $\pm 0.02$                 | $\pm 0.02$                  | LSB                  | 全コードについて設計によって<br>単調性を保証                                         |                                  |

| AD5338                        |                            |                             |                      |                                                                  |                                  |

| 分解能                           | 10                         | 10                          | ピット                  |                                                                  |                                  |

| 相対精度                          | $\pm 0.5$                  | $\pm 0.5$                   | LSB                  |                                                                  |                                  |

| 微分非直線性                        | $\pm 0.05$                 | $\pm 0.05$                  | LSB                  | 全コードについて設計によって<br>単調性を保証                                         |                                  |

| AD5339                        |                            |                             |                      |                                                                  |                                  |

| 分解能                           | 12                         | 12                          | ピット                  |                                                                  |                                  |

| 相対精度                          | $\pm 2$                    | $\pm 2$                     | LSB                  |                                                                  |                                  |

| 微分非直線性                        | $\pm 0.2$                  | $\pm 0.2$                   | LSB                  | 全コードについて設計によって<br>単調性を保証                                         |                                  |

| オフセット誤差                       | $\pm 0.4$                  | $\pm 0.4$                   | FSRの%                |                                                                  |                                  |

| ゲイン誤差                         | $\pm 0.15$                 | $\pm 0.15$                  | FSRの%                |                                                                  |                                  |

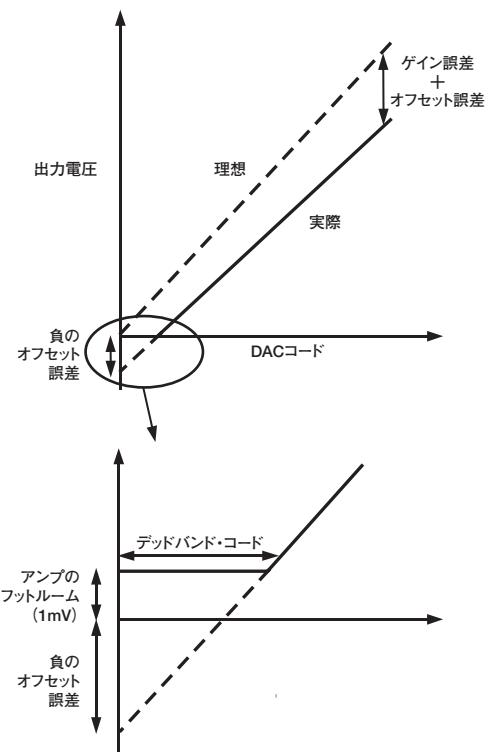

| 下側デッドバンド                      | 20                         | 60                          | mV                   | オフセット誤差が負のときのみ、<br>下側デッドバンドが存在                                   |                                  |

| オフセット誤差ドリフト <sup>5</sup>      | -12                        | -12                         | FSRのppm /°C          |                                                                  |                                  |

| ゲイン誤差ドリフト <sup>5</sup>        | -5                         | -5                          | FSRのppm /°C          |                                                                  |                                  |

| 電源除去比 <sup>5</sup>            | -60                        | -60                         | dB                   |                                                                  |                                  |

| DCクロストーク <sup>5</sup>         | 200                        | 200                         | μV                   | $\Delta V_{DD}=\pm 10\%$<br>$R_L=2k\Omega \sim GND$ または $V_{DD}$ |                                  |

| DACリファレンス入力 <sup>5</sup>      |                            |                             |                      |                                                                  |                                  |

| $V_{REF}$ 入力レンジ               | 0.25<br>37                 | $V_{DD}$                    | 0.25<br>37           | $V$                                                              |                                  |

| $V_{REF}$ 入力インピーダンス           | 45<br>$>10$                |                             | 45<br>$>10$          | $k\Omega$                                                        |                                  |

| リファレンス・フィードスルー                | $>90$                      |                             | $>90$                | $M\Omega$                                                        |                                  |

|                               |                            |                             |                      | 通常動作                                                             |                                  |

|                               |                            |                             |                      | パワーダウン・モード                                                       |                                  |

|                               |                            |                             |                      | 周波数=10kHz                                                        |                                  |

| 出力特性 <sup>5</sup>             |                            |                             |                      |                                                                  |                                  |

| 最小出力電圧 <sup>6</sup>           | 0.001                      | 0.001                       | V                    | これは出力アンプの<br>最小／最大駆動能力を示す値です。                                    |                                  |

| 最大出力電圧 <sup>6</sup>           | $V_{DD}-0.001$             | $V_{DD}-0.001$              | V                    |                                                                  |                                  |

| DC出力インピーダンス                   | 0.5                        | 0.5                         | $\Omega$             |                                                                  |                                  |

| 短絡電流                          | 25                         | 25                          | mA                   | $V_{DD}=5V$                                                      |                                  |

|                               | 16                         | 16                          | mA                   | $V_{DD}=3V$                                                      |                                  |

| パワーアップ時間                      | 2.5                        | 2.5                         | $\mu s$              | パワーダウン・モードからの復帰                                                  |                                  |

|                               | 5                          | 5                           | $\mu s$              | $V_{DD}=5V$                                                      |                                  |

|                               |                            |                             |                      | パワーダウン・モードからの復帰                                                  |                                  |

|                               |                            |                             |                      | $V_{DD}=3V$                                                      |                                  |

| ロジック入力 (AO) <sup>5</sup>      |                            |                             |                      |                                                                  |                                  |

| 入力電流                          | $\pm 1$                    | $\pm 1$                     | $\mu A$              |                                                                  |                                  |

| $V_{IL}$ 、ローレベル入力電圧           | 0.8<br>0.6<br>0.5          | 0.8<br>0.6<br>0.5           | V                    | $V_{DD}=5V \pm 10\%$                                             |                                  |

| $V_{IH}$ 、ハイレベル入力電圧           | 2.4<br>2.1<br>2.0          | 2.4<br>2.1<br>2.0           | V                    | $V_{DD}=3V \pm 10\%$                                             |                                  |

| ピン容量                          | 3                          | 3                           | pF                   | $V_{DD}=2.5V$                                                    |                                  |

|                               |                            |                             |                      | $V_{DD}=5V \pm 10\%$                                             |                                  |

|                               |                            |                             |                      | $V_{DD}=3V \pm 10\%$                                             |                                  |

|                               |                            |                             |                      | $V_{DD}=2.5V$                                                    |                                  |

| ロジック入力 (SCL、SDA) <sup>5</sup> |                            |                             |                      |                                                                  |                                  |

| $V_{IH}$ 、ハイレベル入力電圧           | 0.7 $V_{DD}$<br>-0.3       | $V_{DD}+0.3$<br>$0.3V_{DD}$ | 0.7 $V_{DD}$<br>-0.3 | V                                                                | $V_{DD}<3.6V$ でSMBus互換           |

| $V_{IL}$ 、ローレベル入力電圧           |                            | $\pm 1$                     | $0.3V_{DD}$          | V                                                                | $V_{DD}<3.6V$ でSMBus互換           |

| $I_{IN}$ 、入力リリーキ電流            | 0.05 $V_{DD}$              | 8                           | 0.05 $V_{DD}$        | $\mu A$                                                          |                                  |

| $V_{HYST}$ 、入力ヒステリシス          |                            | 50                          | 8                    | V                                                                |                                  |

| $C_{IN}$ 、入力容量                |                            |                             | 50                   | pF                                                               |                                  |

| グリッヂ除去                        |                            |                             |                      | ns                                                               | 入力のフィルタ処理で50ns未満の<br>ノイズ・スパイクを抑制 |

| ロジック出力 (SDA) <sup>5</sup>     |                            |                             |                      |                                                                  |                                  |

| $V_{OL}$ 、ローレベル出力電圧           | 0.4<br>0.6<br>$\pm 1$      | 0.4<br>0.6<br>$\pm 1$       | V                    | $I_{SINK}=3mA$                                                   |                                  |

| スリーステート・リーク電流                 | 8                          | 8                           | V                    | $I_{SINK}=6mA$                                                   |                                  |

| スリーステート出力容量                   |                            |                             | $\mu A$              |                                                                  |                                  |

|                               |                            |                             | pF                   |                                                                  |                                  |

| パラメータ <sup>1</sup>               | Min  | グレードA<br>Typ | Max | Min  | グレードB<br>Typ | Max | 単位      | Bバージョン <sup>2</sup><br>条件／備考               |

|----------------------------------|------|--------------|-----|------|--------------|-----|---------|--------------------------------------------|

| 電源要求                             |      |              |     |      |              |     |         |                                            |

| $V_{DD}$                         | 2.5  | 5.5          |     | 2.5  | 5.5          |     | V       |                                            |

| $I_{DD}$ (ノーマル・モード) <sup>7</sup> |      |              |     |      |              |     |         | $V_{IH} = V_{DD}$ および $V_{IL} = GND$       |

| $V_{DD} = 4.5 \sim 5.5V$         | 300  | 375          |     | 300  | 375          |     | $\mu A$ |                                            |

| $V_{DD} = 2.5 \sim 3.6V$         | 250  | 350          |     | 250  | 350          |     | $\mu A$ |                                            |

| $I_{DD}$ (パワーダウン・モード)            |      |              |     |      |              |     |         | $V_{IH} = V_{DD}$ および $V_{IL} = GND$       |

| $V_{DD} = 4.5 \sim 5.5V$         | 0.2  | 1            |     | 0.2  | 1            |     | $\mu A$ | SDAでのリードバックが0の間は $I_{DD} = 4\mu A$ (Max)   |

| $V_{DD} = 2.5 \sim 3.6V$         | 0.08 | 1            |     | 0.08 | 1            |     | $\mu A$ | SDAでのリードバックが0の間は $I_{DD} = 1.5\mu A$ (Max) |

注

<sup>1</sup> 用語集を参照してください。<sup>2</sup> 温度範囲 (A、Bバージョン) : -40 ~ +105°C。typ値は25°C。<sup>3</sup> DC仕様は出力無負荷でテスト。<sup>4</sup> 直線性はコード範囲を狭めてテスト: AD5337 (コード8~248)、AD5338 (コード28~995)、AD5339 (コード115~3981)<sup>5</sup> 設計と特性により保証しており、出荷テストは実施していません。<sup>6</sup> アンプ出力を最小電圧にするには、負のオフセット誤差が必要です。アンプ出力を最大電圧にするには、 $V_{REF} = V_{DD}$  で、オフセットとゲインの誤差の合計が正になる必要があります。<sup>7</sup>  $I_{DD}$ 仕様はすべてのDACコードで有効です。インターフェースは非アクティブ。すべてのDACはアクティブで、負荷電流は除きます。

仕様は予告なく変更されることがあります。

## AC特性<sup>1</sup>

(特に指定のない限り、 $V_{DD} = 2.5 \sim 5.5V$ 、 $R_L = GND$ に対し  $2k\Omega$ 、 $C_L = GND$ に対し  $200pF$ 、すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定)

| パラメータ <sup>2</sup>   | Min | グレードBバージョン <sup>3</sup><br>Typ | Max | 単位           | 条件／備考                                                           |

|----------------------|-----|--------------------------------|-----|--------------|-----------------------------------------------------------------|

| 出力電圧セトリング・タイム        |     |                                |     |              |                                                                 |

| AD5337               | 6   | 8                              |     | $\mu s$      | $V_{REF} = V_{DD} = 5V$<br>1/4スケールから3/4スケールへの変化<br>(0x40から0xC0) |

| AD5338               | 7   | 9                              |     | $\mu s$      | 1/4スケールから3/4スケールへの変化<br>(0x100から0x300)                          |

| AD5339               | 8   | 10                             |     | $\mu s$      | 1/4スケールから3/4スケールへの変化<br>(0x400から0xC00)                          |

| スルーレート               | 0.7 |                                |     | $V/\mu s$    |                                                                 |

| メジャー・コード遷移グリッチ・エネルギー | 12  |                                |     | $nV \cdot s$ | メジャー・キャリーを中心にして1LSBの変化                                          |

| デジタル・フィードスルー         | 1   |                                |     | $nV \cdot s$ |                                                                 |

| デジタル・クロストーク          | 1   |                                |     | $nV \cdot s$ |                                                                 |

| DAC間クロストーク           | 3   |                                |     | $nV \cdot s$ |                                                                 |

| 乗算帯域幅                | 200 |                                |     | $kHz$        | $V_{REF} = 2V \pm 0.1V$ p-p                                     |

| 全高調波歪み               | -70 |                                |     | $dB$         | $V_{REF} = 2.5V \pm 0.1V$ p-p、周波数 = 10kHz                       |

注

<sup>1</sup> 設計と特性により保証しており、出荷テストは実施していません。<sup>2</sup> 用語集を参照してください。<sup>3</sup> 温度範囲 (Bバージョン) : -40 ~ +105°C。typ値は25°C。

仕様は予告なく変更されることがあります。

# AD5337/AD5338/AD5339

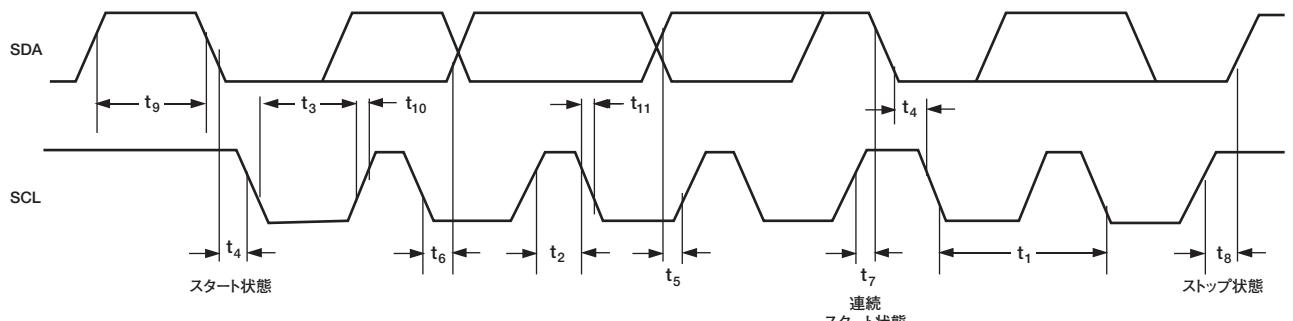

## タイミング特性<sup>1, 2</sup>

(特に指定のない限り、 $V_{DD}=2.5\sim5.5V$ 。すべての仕様は $T_{MIN}\sim T_{MAX}$ で規定)

| パラメータ     | $T_{MIN}, T_{MAX}$ における限界<br>(Bバージョン) | 単位        | 条件／備考                                |

|-----------|---------------------------------------|-----------|--------------------------------------|

| $f_{SCL}$ | 400                                   | kHz (max) | SCLクロック周波数                           |

| $t_1$     | 2.5                                   | μs (min)  | SCLサイクル時間                            |

| $t_2$     | 0.6                                   | μs (min)  | $t_{HIGH}$ 、SCLハイ時間                  |

| $t_3$     | 1.3                                   | μs (min)  | $t_{LOW}$ 、SCLロー時間                   |

| $t_4$     | 0.6                                   | μs (min)  | $t_{HD,STA}$ 、スタート／連続スタート状態のホールド・タイム |

| $t_5$     | 100                                   | ns (min)  | $t_{SU,DAT}$ 、データ・セットアップ・タイム         |

| $t_6^3$   | 0.9                                   | μs (max)  | $t_{HD,DAT}$ 、データ・ホールド・タイム           |

|           | 0                                     | μs (min)  | $t_{HD,DAT}$ 、データ・ホールド・タイム           |

| $t_7$     | 0.6                                   | μs (min)  | $t_{SU,STA}$ 、連続スタートでのセットアップ・タイム     |

| $t_8$     | 0.6                                   | μs (min)  | $t_{SU,STO}$ 、ストップ状態のセットアップ・タイム      |

| $t_9$     | 1.3                                   | μs (min)  | $t_{BUF}$ 、ストップ／スタート状態間のバス・フリー・タイム   |

| $t_{10}$  | 300                                   | ns (max)  | $t_R$ 、受信時のSCLとSDAの立ち上がり時間           |

|           | 0                                     | ns (min)  | $t_R$ 、受信時のSCLとSDAの立ち上がり時間(CMOS互換)   |

| $t_{11}$  | 250                                   | ns (max)  | $t_F$ 、送信時のSDAの立ち下がり時間               |

|           | 0                                     | ns (min)  | $t_F$ 、受信時のSDAの立ち下がり時間(CMOS互換)       |

|           | 300                                   | ns (max)  | $t_F$ 、受信時のSCLとSDAの立ち下がり時間           |

|           | $20+0.1C_B^4$                         | ns (min)  | $t_F$ 、送信時のSCLとSDAの立ち下がり時間           |

| $C_B$     | 400                                   | pF (max)  | 各バス・ラインの容量性負荷                        |

### 注

<sup>1</sup> 図1を参照。

<sup>2</sup> 設計と特性により保証しており、出荷テストは実施していません。

<sup>3</sup> SCLの立ち下がりエッジの不定領域をブリッジするために、マスター・デバイスが少なくとも300nsのホールド・タイムをSDA信号(SCL信号の $V_{HLD\ min}$ )に与える必要があります。

<sup>4</sup>  $C_B$ は1本のバス・ラインの全容量をpFで表したものです。 $t_R$ と $t_F$ は、 $0.3V_{DD}$ と $0.7V_{DD}$ の間で測定しています。

仕様は予告なく変更されることがあります。

図1. 2線式シリアル・インターフェースのタイミング図

**絶対最大定格<sup>1, 2</sup>**(特に指定のない限り、T<sub>A</sub>=25°C)GNDに対するV<sub>DD</sub> ..... -0.3~+7VGNDに対するSCL、SDA ..... -0.3~V<sub>DD</sub>+0.3VGNDに対するA0 ..... -0.3~V<sub>DD</sub>+0.3VGNDに対するリファレンス入力電圧 ..... -0.3~V<sub>DD</sub>+0.3VGNDに対するV<sub>OUTA-B</sub> ..... -0.3~V<sub>DD</sub>+0.3V

動作温度範囲

工業用（Bバージョン） ..... -40~+105°C

保存温度範囲 ..... -65~+150°C

ジャンクション温度 (T<sub>j</sub> max) ..... 150°C

MSOPパッケージ

消費電力 ..... (T<sub>j</sub> max-T<sub>A</sub>) /θ<sub>JA</sub>θ<sub>JA</sub>熱抵抗 ..... 206°C/Wθ<sub>JC</sub>熱抵抗 ..... 44°C/W

リフロー、ハンド処理

ピーク温度 ..... 220+5/-0°C

ピーク温度での時間 ..... 10~40秒

**注**

<sup>1</sup> 上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作に関するセクションに記載されている規定値以上でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

<sup>2</sup> 100mAまでの過渡電流では、SCRラッチアップは発生しません。

**オーダー・ガイド**

| モデル             | 温度範囲       | パッケージ   | パッケージ・オプション | ブランド |

|-----------------|------------|---------|-------------|------|

| AD5337ARM       | -40~+105°C | 8ピンMSOP | RM-8        | D23  |

| AD5337ARM-REEL7 | -40~+105°C | 8ピンMSOP | RM-8        | D23  |

| AD5337BRM       | -40~+105°C | 8ピンMSOP | RM-8        | D20  |

| AD5337BRM-REEL  | -40~+105°C | 8ピンMSOP | RM-8        | D20  |

| AD5337BRM-REEL7 | -40~+105°C | 8ピンMSOP | RM-8        | D20  |

| AD5338ARM       | -40~+105°C | 8ピンMSOP | RM-8        | D24  |

| AD5338ARM-REEL7 | -40~+105°C | 8ピンMSOP | RM-8        | D24  |

| AD5338BRM       | -40~+105°C | 8ピンMSOP | RM-8        | D21  |

| AD5338BRM-REEL  | -40~+105°C | 8ピンMSOP | RM-8        | D21  |

| AD5338BRM-REEL7 | -40~+105°C | 8ピンMSOP | RM-8        | D21  |

| AD5339ARM       | -40~+105°C | 8ピンMSOP | RM-8        | D25  |

| AD5339ARM-REEL7 | -40~+105°C | 8ピンMSOP | RM-8        | D25  |

| AD5339BRM       | -40~+105°C | 8ピンMSOP | RM-8        | D22  |

| AD5339BRM-REEL  | -40~+105°C | 8ピンMSOP | RM-8        | D22  |

| AD5339BRM-REEL7 | -40~+105°C | 8ピンMSOP | RM-8        | D22  |

**注意**

ESD（静電放電）の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

# AD5337/AD5338/AD5339

## ピン配置

## ピン機能の説明

| ピン番号 | 記号                | 機能                                                                                                                |

|------|-------------------|-------------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>DD</sub>   | 電源入力。デバイスは2.5~5.5Vで動作しますが、GNDに対して電源をデカップリングする必要があります。                                                             |

| 2    | V <sub>OUTA</sub> | DAC Aからのバッファ・アナログ出力電圧。出力アンプはレールtoレールで動作します。                                                                       |

| 3    | V <sub>OUTB</sub> | DAC Bからのバッファ・アナログ出力電圧。出力アンプはレールtoレールで動作します。                                                                       |

| 4    | REFIN             | 2つのDACのリファレンス入力ピン。入力レンジは0.25V~V <sub>DD</sub> です。                                                                 |

| 5    | GND               | デバイス上の全回路のグラウンド・リファレンス・ポイント                                                                                       |

| 6    | SDA               | シリアル・データ・ライン。SCLラインとともに使用し、16ビット入力シフト・レジスタとの間でデータをクロック入／出力します。これは双方向のオープンドレインのデータ・ラインで、外付けブルアップ抵抗で電源に接続する必要があります。 |

| 7    | SCL               | シリアル・クロック・ライン。SDAラインとともに使用し、16ビット入力シフト・レジスタとの間でデータをクロック入／出力します。2線式インターフェースでは最高400kbpsのクロック・レートに対応できます。            |

| 8    | A0                | アドレス入力。7ビット・スレーブ・アドレスの最下位ビットを設定します。                                                                               |

## 用語集

### 相対精度

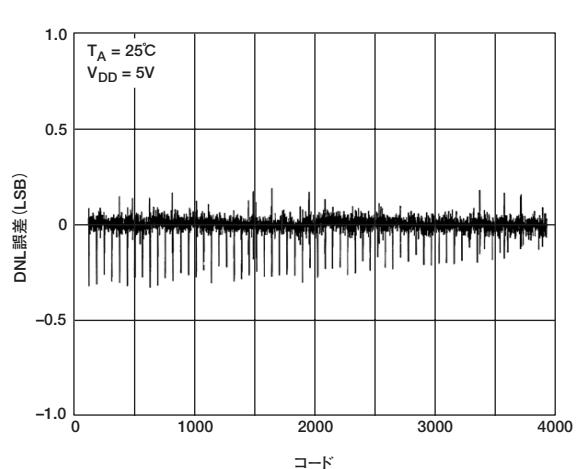

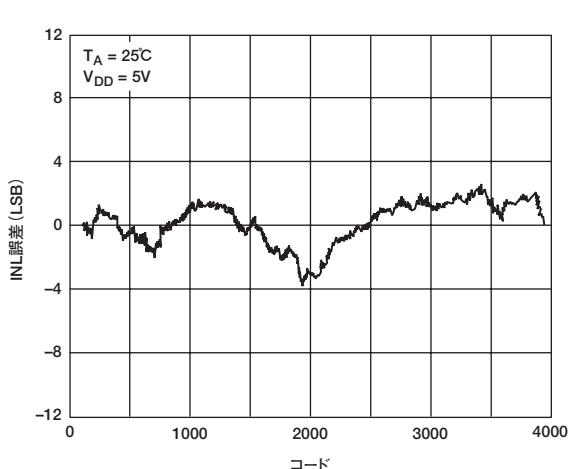

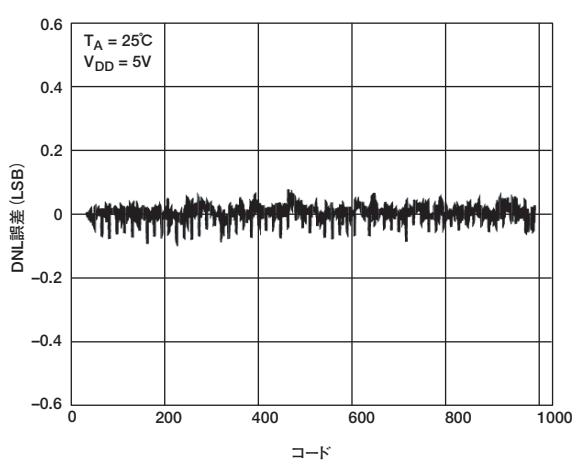

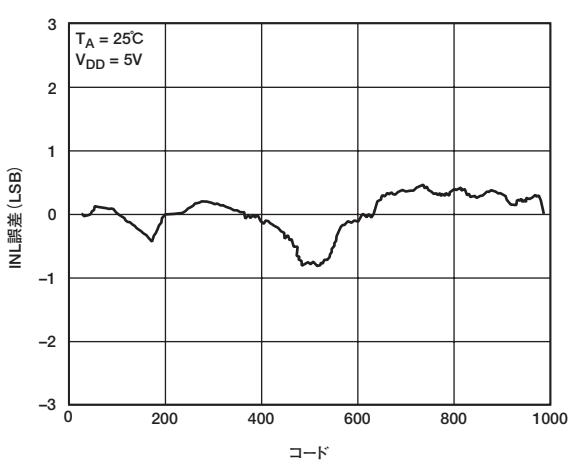

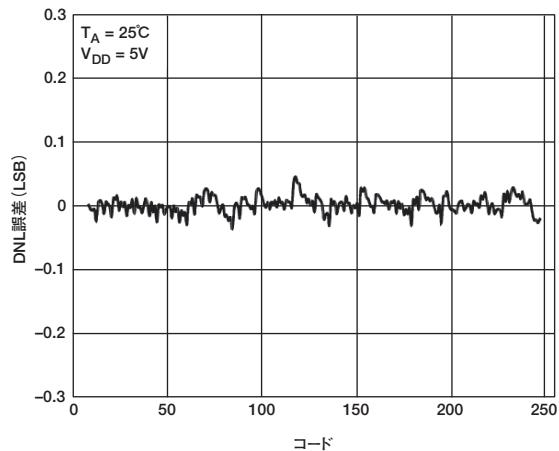

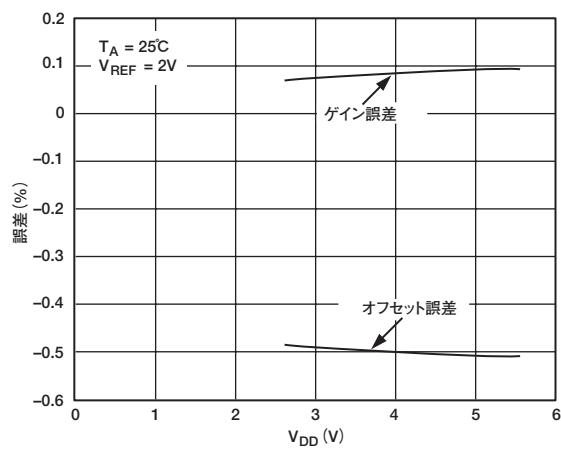

DACでは、相対精度または積分非直線性（INL）とは、DAC伝達関数のエンドポイントを結ぶ直線からの最大偏差を示す値で、単位はLSBです。TPC 1、2、3に、代表的なINLとコードの関係を示します。

### 微分非直線性

微分非直線性（DNL）とは、任意の2つの隣接するコード間での測定した変化と理想的な1 LSB変化との差異です。最大±1 LSBという仕様規定の微分非直線性によって、単調性を保証します。このDACは、設計によって単調性が保証されています。TPC 4、5、6に、代表的なDNLとコードの関係を示します。

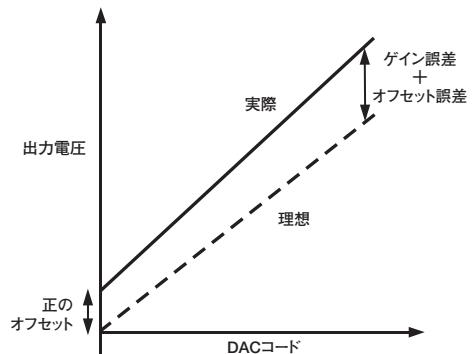

### オフセット誤差

DACと出力アンプのオフセット誤差を示す値で、フルスケール範囲のパーセンテージで表します。

### ゲイン誤差

DACのスパン誤差を示す値です。これは、DAC伝達特性の理想値と実際値の傾きの偏差であり、フルスケール範囲のパーセンテージで表します。

### オフセット誤差ドリフト

温度変化に伴うオフセット誤差の変化を示す値で、(フルスケール範囲に対するppm値) /°Cで表します。

### ゲイン誤差ドリフト

温度変化に伴うゲイン誤差の変化を示す値で、(フルスケール範囲に対するppm値) /°Cで表します。

### 電源除去比 (PSRR)

電源電圧の変化がDACの出力に与える影響を示す値です。PSRRはDACのフルスケール出力に対するV<sub>OUT</sub>の変化とV<sub>DD</sub>の変化の比率であり、単位はdBです。V<sub>REF</sub>は2Vに保持され、V<sub>DD</sub>は±10%で変動します。

### DCクロストーク

ミッドスケールでの1つのDACの出力レベルにおいて、他のDACのフルスケール・コード変化（オール0からオール1、およびその逆）と出力変化に応じて発生するDC変動で、単位はμVです。

### リファレンス・フィードスルー

DAC出力が更新されていないときの、DAC出力での信号の振幅とリファレンス入力との比率で、単位はdBです。

### メジャー・コード遷移グリッチ・エネルギー

DACレジスタ内のコードが状態を変化させるときに、アナログ出力に注入されるインパルスのエネルギーです。通常、nV-s単位でのグリッチの領域として仕様規定され、メジャー・キャリー遷移（011...11から100...00または100...00から011...11）においてデジタル・コードが1LSBだけ変化するときに測定します。

### デジタル・フィードスルー

DAC出力が更新されていないときに、デバイスのデジタル入力ピンからDACのアナログ出力に注入されるインパルスを示す値です。単位nV-sで仕様規定され、デジタル入力ピンでの最悪時の変化（つまりオール0からオール1、およびその逆）で測定します。

### デジタル・クロストーク

ミッドスケールでの1つのDACの出力に対して、他のDACの入力レジスタでのフルスケール・コード変化（オール0からオール1、およびその逆）に応じて転送されるグリッチ・インパルスであり、単位nV-sで表します。

### DAC間クロストーク

1つのDACの出力に対して、他のDACのデジタル・コード変化とそれ以降の出力変化によって転送されるグリッチ・インパルスです。これには、デジタルとアナログの両方のクロストークが含まれます。DAC間クロストークを測定するには、LDACピンをローレベルに設定して、DACの1つにフルスケール・コード変化（オール0からオール1、およびその逆）をロードして、他のDACの出力を監視します。グリッチのエネルギーは単位nV-sで表します。

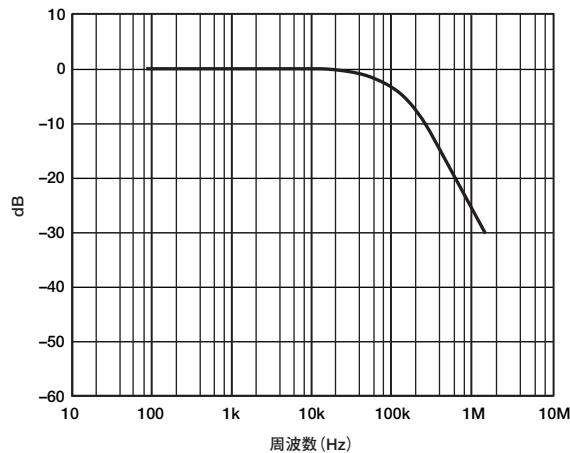

### 乗算帯域幅

DAC内のアンプには有限の帯域幅があります。乗算帯域幅はその値です。リファレンスの正弦波は、DACにフルスケール・コードをロードした状態で出力に現われます。乗算帯域幅は、出力振幅が入力より3dB低下する周波数です。

### 全高調波歪み

理想的な正弦波と、DACの使用で減衰した正弦波との差異です。正弦波はDACのリファレンスとして使用するもので、全高調波歪みはDAC出力に存在する高調波を示しています。単位はdBです。

図2. オフセットが負の伝達関数

図3. オフセットが正の伝達関数

# AD5337/AD5338/AD5339

## 代表的な性能特性

# AD5337/AD5338/AD5339

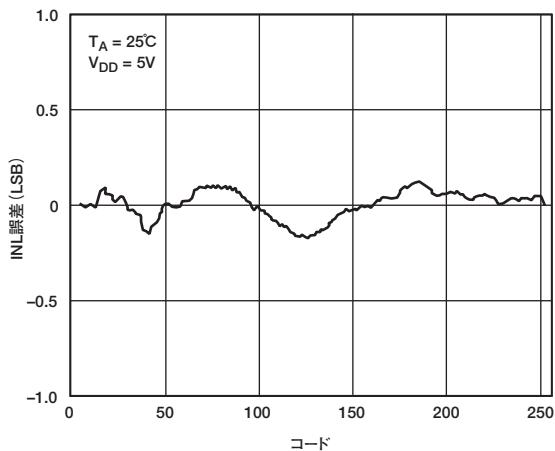

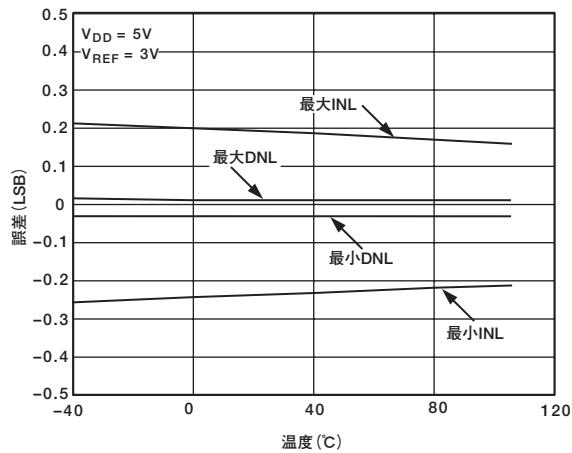

TPC 7. AD5337の $V_{REF}$ 対 INLおよびDNL誤差

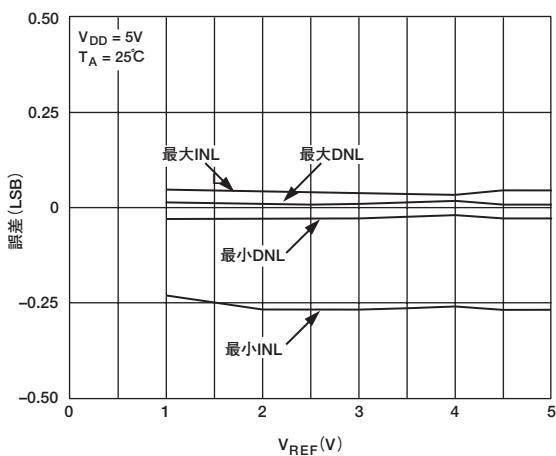

TPC 10.  $V_{DD}$ 対オフセット誤差およびゲイン誤差

TPC 8. AD5337の温度対 INLおよびDNL誤差

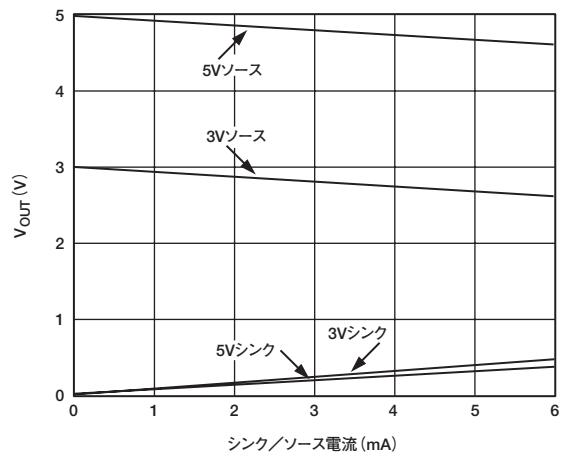

TPC 11.  $V_{OUT}$ のソース／シンク電流特性

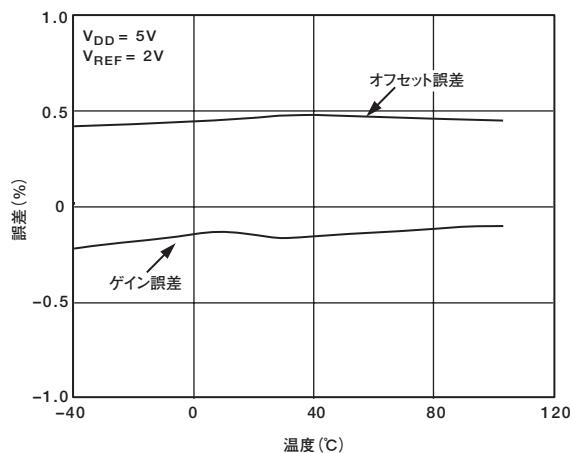

TPC 9. AD5337の温度対オフセット誤差

およびゲイン誤差

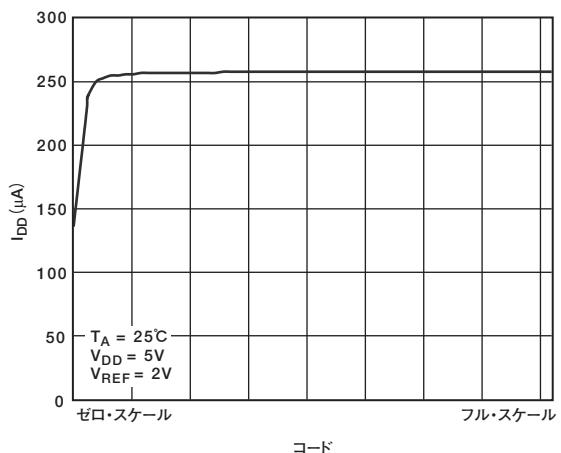

TPC 12. DACコード対電源電流

# AD5337/AD5338/AD5339

TPC 13. 電源電圧 対 電源電流

TPC 14. 電源電圧 対 パワーダウン電流

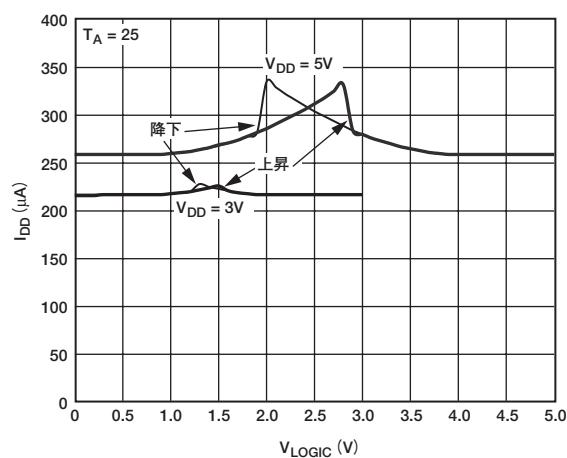

TPC 15. SDAとSCLの電圧上昇／降下時のロジック入力電圧 対 電源電流

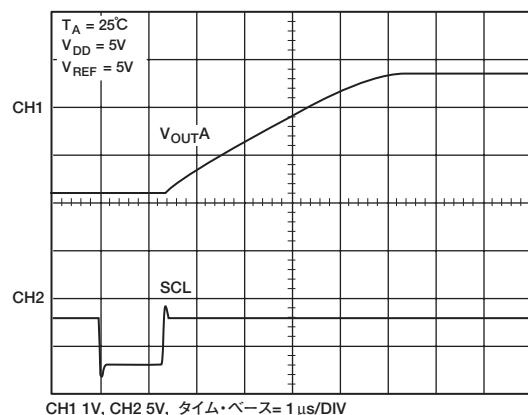

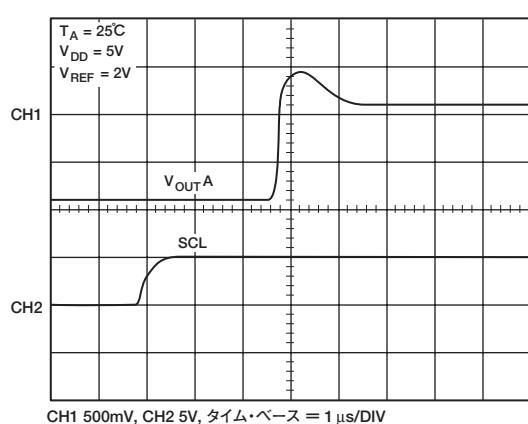

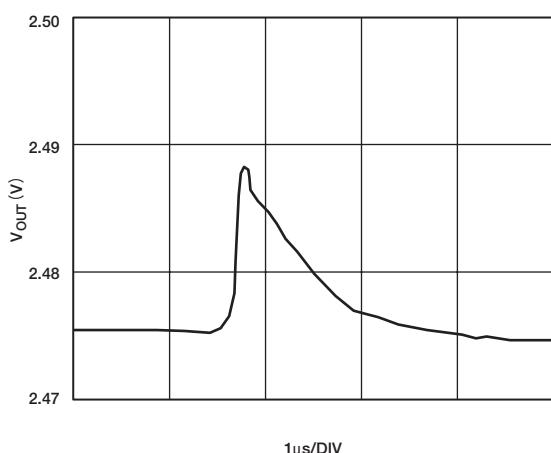

TPC 16. ハーフスケール・セトリング

(1/4から3/4スケールへのコード変化)

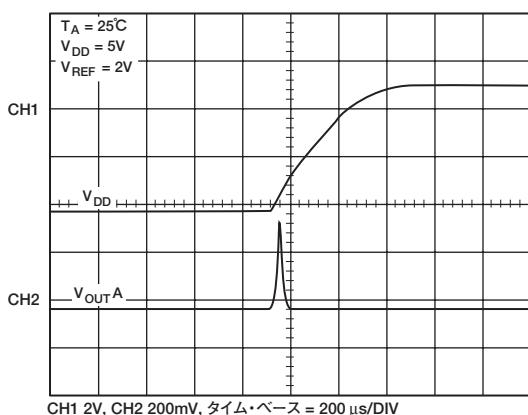

TPC 17. 0Vへのパワーオン・リセット

TPC 18. パワーダウンからミッドスケールへの復帰

## AD5337/AD5338/AD5339

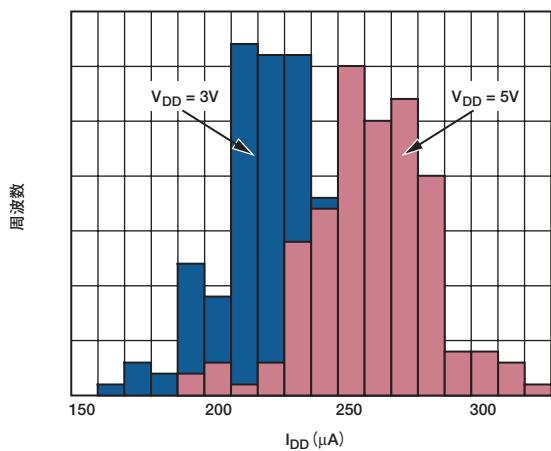

TPC 19.  $V_{DD} = 3V$  および  $V_{DD} = 5V$  における  $I_{DD}$  のヒストグラム

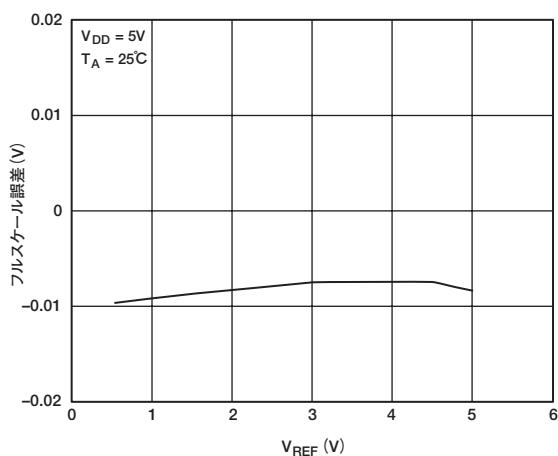

TPC 22.  $V_{REF}$  対 フルスケール誤差

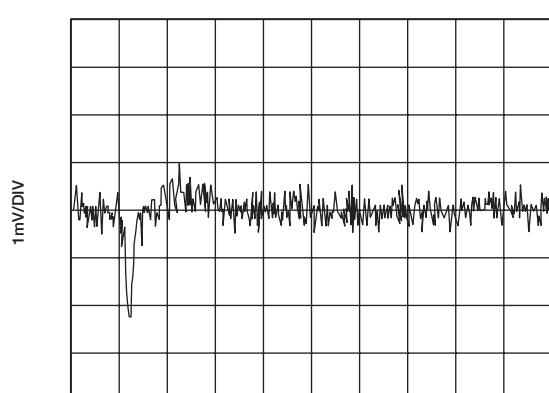

TPC 20. AD5339のメジャー・コード遷移グリッチ・エネルギー

TPC 23. DAC間クロストーク

TPC 21. 乗算帯域幅（小信号周波数応答）

# AD5337/AD5338/AD5339

## 機能の説明

AD5337/AD5338/AD5339は、CMOSプロセスで製造されたデュアル抵抗ストリングDACで、それぞれ8、10、12ビットの分解能があります。いずれも2つの出力バッファ・アンプを内蔵し、2線式シリアル・インターフェースから書き込みを行います。2.5~5.5Vの单電源で動作し、出力バッファ・アンプにより0.7V/ $\mu$ sのスルーレートでレールtoレールの出力振幅が得られます。2つのDACで1本のリファレンス入力ピンを共有しています。AD5337/AD5338/AD5339にはプログラマブルな3つのパワーダウン・モードがあり、高インピーダンス出力すべてのDACを完全にオフにしたり、内蔵抵抗により出力をローにすることができます。

## デジタル／アナログ変換部

1つのDACチャンネルのアーキテクチャは、抵抗ストリングDAC1つと、これに続く出力バッファ・アンプ1つで構成されています。REFINピンの電圧がDACへのリファレンス電圧を供給します。図4に、DACアーキテクチャのブロック図を示します。DACに対する入力コーディングはストレート・バイナリであるため、次の式で理想的な出力電圧を求めることができます。

$$V_{OUT} = \frac{V_{REF} \times D}{2^N}$$

ここで、

Dは2進コードと等価な10進値で、これをDACレジスタにロードします。

AD5337 (8ビット) では0~255

AD5338 (10ビット) では0~1023

AD5339 (12ビット) では0~4095です。

NはDACの分解能です。

図4. DACチャンネルのアーキテクチャ

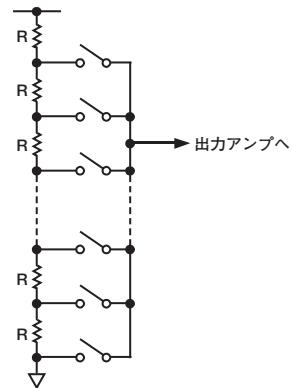

## 抵抗ストリング

抵抗ストリング部を図5に示します。これは、それぞれ値Rを持つ抵抗を並べただけの列（ストリング）です。ストリング上のどのノードで電圧を取り出して出力アンプに供給するかは、DACレジスタにロードされるデジタル・コードによって決まります。ストリングをアンプに接続しているスイッチの1つを閉じて、電圧を取ります。抵抗で構成されたストリングであるため、単調性を保証します。

図5. 抵抗ストリング

## DACリファレンス入力

2つのDACに対して、リファレンス入力ピンは1本です。リファレンス入力にはバッファがありません。リファレンス・アンプのヘッドルームとフットルームによる制約がないため、0.25V~V<sub>DD</sub>のリファレンス電圧が得られます。

外付け回路ではバッファ・リファレンスの使用を推奨します（たとえば、REF192）。入力インピーダンスは45kΩです（typ値）。

## 出力アンプ

出力バッファ・アンプは出力でレールtoレール電圧を生成でき、リファレンス=V<sub>DD</sub>の場合、出力範囲は0V~V<sub>DD</sub>になります。GNDまたはV<sub>DD</sub>に対する500pFに並列して、GNDまたはV<sub>DD</sub>に2kΩの負荷を駆動できます。出力アンプのソース／シンク特性をTPC 11に示します。

スルーレートは0.7V/ $\mu$ sで、±0.5LSB (8ビットで)までのハーフスケール・セトリング・タイムは6 $\mu$ sです。

## パワーオン・リセット

AD5337/AD5338/AD5339にはパワーオン・リセット機能があり、定義された状態でパワーアップします。パワーオン状態は次のとおりです。

- 通常動作

- 出力電圧を0Vに設定

入力レジスタとDACレジスタはいずれもゼロで埋められ、デバイスに対し有効な書き込みシーケンスが実行されるまでその状態にとどまります。デバイスがパワーアップするときのDAC出力の状態を把握していなければならないアプリケーションでは、特にこの機能が役に立ちます。

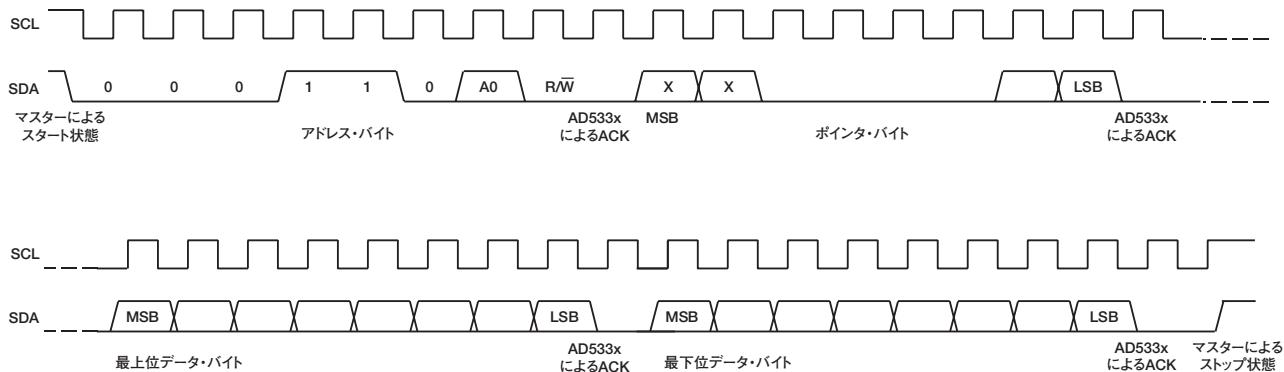

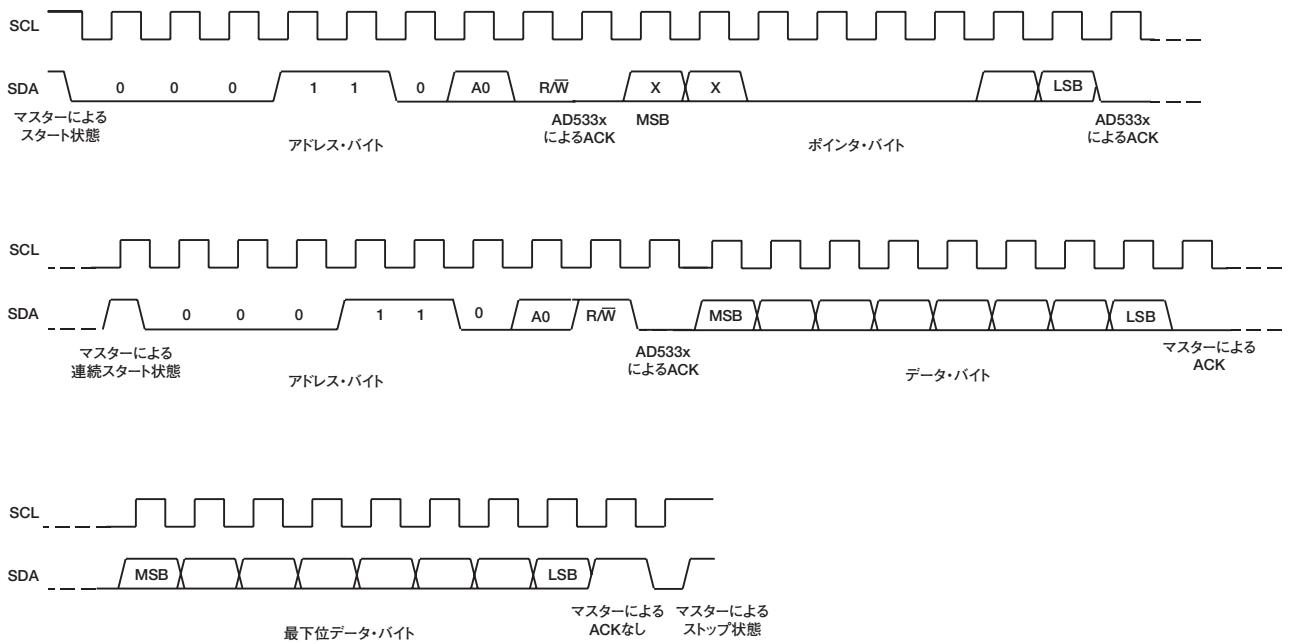

## シリアル・インターフェース

AD5337/AD5338/AD5339は、I<sup>2</sup>C互換のシリアル・バスから制御します。DACをスレーブ・デバイスとしてこのバスに接続します（つまり、AD5337/AD5338/AD5339のDACはクロックを生成しません）。このインターフェースは、V<sub>DD</sub><3.6VでSMBus互換です。

AD5337/AD5338/AD5339には7ビットのスレーブ・アドレスがあります。6つのMSBは000110で、A0ピンの状態によって LSBが決まります。A0への配線接続を変更できるため、ユーザーは1本のバスでこれらのデバイスを2つまで使用できます。

2線式シリアル・バス・プロトコルは以下のように動作します。

1. SCLがハイのときにSDAラインでハイからローへの遷移が発生すると、マスターがスタート状態を確立して、データ転送を開始します。後続のバイトはアドレス・バイトで、7ビットのスレーブ・アドレスとそれに続くR/Wビット（スレーブ・デバイスへの読み出し／書き込みを決定するビット）で構成されます。

2. 送信されたアドレスに対応するアドレスを持つスレーブが、9番目のクロック・パルス（アクノレッジ・ビット）中にSDAをローにして応答します。この段階で、バス上の他のデバイスはすべてアイドル状態となり、選択されたデバイスがそのシフト・レジスタにデータの読み出し／書き込みが行われるのを待ちます。

3. 9つのクロック・パルス（8つのデータ・ビットとそれに続くアクノレッジ・ビット）の連続でシリアル・バスを使ってデータを送信します。SDAライン上の遷移はSCLがローになっている期間中に生じ、SCLがハイの間は安定している必要があります。

4. すべてのデータ・ビットの読み出し／書き込みが終わると、ストップ状態が確立されます。書き込みモードでは、マスターが10番目のクロック・パルス中にSDAラインをハイレベルにプルしてストップ状態を確立します。読み出しモードでは、マスターが9番目のクロック・パルスに対してノー・アクノレッジを発行します（つまり、SDAラインはハイレベルのままであります）。続いてマスターは、10番目のクロック・パルスの前にSDAラインをローレベルにし、10番目のクロック・パルス中にハイレベルにしてストップ状態を確立します。

### 読み出し／書き込みシーケンス

AD5337/AD5338/AD5339では、すべての書き込みアクセス・シーケンスと大部分の読み出しシーケンスがデバイス・アドレス（R/W=0）で始まり、その後にポインタ・バイトが続きます。このポインタ・バイトがデータ・フォーマットを規定し、次の読み出し／書き込み動作でアクセスが行われるDACを決定します（図6を参照）。書き込み動作では、すぐにデータが続きます。読み出し動作では、R/W=1でアドレスが再送されてから、データの読み出しが行われます。R/W=1でアドレスだけを送信して読み出し動作を実行することもできます。この場合、以前にロードしたポインタ設定を読み出し動作に使用します。インターフェースについては、図7を参照してください。

| MSB |   |   |            |   |   |      |      |  | LSB |

|-----|---|---|------------|---|---|------|------|--|-----|

| X   | X | 0 | DOUBLE = 0 | 0 | 0 | DACB | DACA |  |     |

図6. ポインタ・バイト

### ポインタ・バイト・ビット

ポインタ・バイトを構成する各ビットを説明します。

|        |                                                                                               |

|--------|-----------------------------------------------------------------------------------------------|

| X      | ドント・ケア・ビット                                                                                    |

| DOUBLE | 0:ゼロに設定されるビット<br>0:データの書き込みと読み出しが2バイトの書き込み／読み出しシーケンスで実行されます<br>0:ゼロに設定されるビット<br>0:ゼロに設定されるビット |

| DACB   | 1:以下のデータ・バイトはDAC B用                                                                           |

| DACA   | 1:以下のデータ・バイトはDAC A用                                                                           |

### 入力シフト・レジスタ

入力シフト・レジスタは16ビット幅です。データは、シリアル・クロック入力SCLの制御によって、シリアル・データ・ラインSDA上の2つのデータ・バイトとしてデバイスにロードされます。図1に、この動作のタイミング図を示します。2つのデータ・バイトは、4つの制御ビットと、これに続く8/10/12ビット（デバイス・タイプによって異なります）のDACデータで構成されます。最初にロードされる2つのビットは、デバイスの動作モードを制御するPD1ビットとPD0ビットです。詳細についてはパワーダウン・モードのセクションを参照してください。ビット13はCLR、ビット12はLDACで、残りのビットは左揃えのDACデータ・ビットで、MSBから始まります。図7を参照してください。

|      |                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------|

| CLR  | 0:書き込みシーケンスの完了時に、すべてのDACレジスタと入力レジスタをゼロで埋めます。<br>1:通常動作                                                          |

| LDAC | 0:2つのDACレジスタを書き込みシーケンスの完了時に同時に更新します。これによって、すべてのDAC出力が同時に更新されます。<br>1:アドレス指定された入力レジスタのみを更新します。DACレジスタの内容は変更しません。 |

### デフォルトのリードバック条件

全ポインタ・バイト・ビットがパワーアップで0になります。このため、ユーザーが最初にポインタ・バイトに書き込みせずにリードバックを開始すると、DACチャンネルが1つも指定されません。この場合、1になるCLRビットを除き、デフォルトのリードバック・ビットがすべて0になります。

### 複数DACでの書き込みシーケンス

ポインタ・バイトには各DACごとに別のビットがあるため、該当するビットを1に設定すれば、同じデータ・ビットと制御ビットを2つのDACに同時に書き込むことができます。

### 複数DACでのリードバック・シーケンス

ユーザーが複数のDACからデータの読み出しを一度に行おうとすると、デバイスは、デフォルトのパワーオン・リセット状態、つまり1になるCLRを除きオール0を読み出します。

| 最上位データ・バイト<br>8ビットAD5337 |     |     |      |      |    |    |    |    | LSB |

|--------------------------|-----|-----|------|------|----|----|----|----|-----|

| MSB                      | PD1 | PD0 | CLR  | LDAC | D7 | D6 | D5 | D4 | LSB |

| MSB                      |     |     |      |      |    |    |    |    | LSB |

| PD1                      | PD0 | CLR | LDAC | D9   | D8 | D7 | D6 |    |     |

| 最下位データ・バイト<br>8ビットAD5337 |     |     |      |      |    |    |    |    | LSB |

| MSB                      | D3  | D2  | D1   | D0   | X  | X  | X  | X  | LSB |

| 最上位データ・バイト<br>10ビットAD5338 |     |     |      |     |     |    |    |   | LSB |

|---------------------------|-----|-----|------|-----|-----|----|----|---|-----|

| MSB                       | D5  | D4  | D3   | D2  | D1  | D0 | X  | X | LSB |

| MSB                       |     |     |      |     |     |    |    |   | LSB |

| PD1                       | PD0 | CLR | LDAC | D11 | D10 | D9 | D8 |   |     |

| 最上位データ・バイト<br>12ビットAD5339 |     |     |      |     |     |    |    |    | LSB |

|---------------------------|-----|-----|------|-----|-----|----|----|----|-----|

| MSB                       | D7  | D6  | D5   | D4  | D3  | D2 | D1 | D0 | LSB |

| MSB                       |     |     |      |     |     |    |    |    | LSB |

| PD1                       | PD0 | CLR | LDAC | D11 | D10 | D9 | D8 |    |     |

図7. 書き込みと読み出しのデータ・フォーマット

# AD5337/AD5338/AD5339

## 書き込み動作

AD5337/AD5338/AD5339 DACに書き込みを行うときには、必ずアドレス・バイト ( $R/W=0$ ) から開始します。これに続いて、DACがSDAをローにしてデータの受信準備ができたことをアクノレッジします。このアドレス・バイトの後にポイン

タ・バイトが続き、これもDACがアクノレッジします。続いて、図8に示すように、2バイトのデータがDACに書き込まれます。その後ストップ状態になります。

図8. 書き込みシーケンス

## 読み出し動作

AD5337/AD5338/AD5339のDACからデータを読み出すときは、アドレス・バイト ( $R/W=0$ ) から始めます。この後、DACがSDAをローにしてデータの受信準備ができたことをアクノレッジします。通常、このアドレス・バイトの後にポインタ・バイトが続き、これもDACがアクノレッジします。続いてマスターによる連続スタート状態となり、 $R/W=1$ でアドレスを再送します。DACがこれをアクノレッジし、データの送信準備ができたことを示します。次に、図9に示すように、DACから2バイトのデータが読み出されます。その後ストップ状態になります。

これに対し、マスターがACKを送信し、SCLのクロック駆動を続ける（ストップを送信しない）場合は、DACはSDAの同じ2バイトのデータを再送信します。これにより、選択したDACレジスタからのデータの連続読み出しが可能になります。

別の方法として、ユーザーがスタートを送り、続いてR/ $\sqrt{W}$ =1によるアドレスを送信することも可能です。この場合は、以前にロードしたポインタ設定を使用し、データの読み出しを直ちに開始できます。

図9. リードバック・シーケンス\*

\* データ・バイトは書き込みシーケンスの場合と同じですが、ドント・ケアだけは0で読み出されます。

# AD5337/AD5338/AD5339

## ダブル・バッファ・インターフェース

AD5337/AD5338/AD5339のDACにはすべて、入力レジスタとDACレジスタの2つのレジスタで構成されるダブル・バッファ・インターフェースがあります。入力レジスタは直接入力シフト・レジスタに接続され、有効な書き込みシーケンスが完了すると、該当する入力レジスタにデジタル・コードが転送されます。DACレジスタには、抵抗ストリングで使用するデジタル・コードが格納されています。

DACレジスタへのアクセスは、LDACピンで制御します。LDACがハイレベルのとき、DACレジスタはラッチされ、DACレジスタの内容を変えずに入力レジスタの状態を変更できます。LDACがローレベルになると、DACレジスタは透過になり、入力レジスタの内容が転送されます。

この機能が役に立つのは、ユーザーがすべてのDAC出力の同時更新を必要とする場合です。ユーザーは入力レジスタの3つに個別に書き込みを行ってから、残りのDAC入力レジスタに書き込むときにLDACをローに設定することで、全出力を同時に更新できます。

デバイスには、この他にもう1つの機能があります。これによって、LDACが最後にローであった時点以降入力レジスタが更新されなければ、DACレジスタが更新されることはありません。通常、LDACがローのときには、DACレジスタには入力レジスタの内容が入っています。AD5337/AD5338/AD5339の場合、DACレジスタが更新されるのはDACレジスタが最後に更新された後に入力レジスタが変更されている場合のみです。このため、余計なデジタル・クロストークがなくなります。

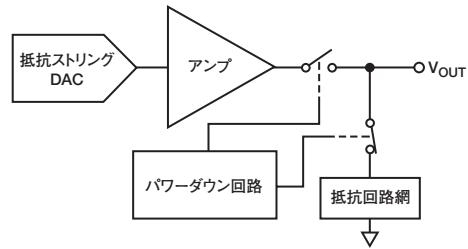

## パワーダウン・モード

AD5337/AD5338/AD5339は消費電力が非常に低く、3V電源で0.75mW、5V電源で1.5mWの電力を消費します（いずれもtyp値）。DACを使用していないときに消費電力をさらに低減するには、3つのパワーダウン・モードのいずれかに設定します。モードの選択は、データ・バイトのビット15と14 (PD1とPD0)で行います。表1に、ビットの状態に対応するDACの動作モードを示します。

表1. PD1/PD0の動作モード

| PD1 | PD0 | 動作モード                  |

|-----|-----|------------------------|

| 0   | 0   | 通常動作                   |

| 0   | 1   | パワーダウン (GNDに対し1kΩ負荷)   |

| 1   | 0   | パワーダウン (GNDに対し100kΩ負荷) |

| 1   | 1   | パワーダウン (スリーステート出力)     |

両方のビットを0に設定すると、DACは5Vで300μAという通常の消費電力で動作します。これに対し3つのパワーダウン・モードでは、電源電流は5Vで200nA (3Vで80nA) に低下します。電源電流が低下するだけでなく、出力段もアンプ出力から既知の値を持つ抵抗回路網に内部的に切り替えられます。こうすれば、パワーダウン・モード時の出力インピーダンスを知ることができ、DACアンプの出力に何が接続されているても決まった入力条件が得られるので便利です。3つのオプションから選択できます。出力は、1kΩ抵抗か100kΩ抵抗を介して内部的にGNDに接続したり、オープン・サーキット (スリーステート)にしておくことができます。抵抗許容量は±20%です。図10に出力段を示します。

図10. パワーダウン時の出力段

パワーダウン・モードになると、バイアス・ジェネレータ、出力アンプ、抵抗ストリング、その他の関連するリニア回路がすべてシャットダウンされます。パワーダウン中にDACレジスタの内容が変更されることはありません。パワーダウンから出るための時間は、 $V_{DD}=5V$ で $2.5\mu s$ 、 $V_{DD}=3V$ で $5\mu s$ です（いずれもtyp値）。これは、8番目のSCLパルスの立ち上がりエッジから、出力電圧がパワーダウン電圧から変化するまでの時間です。TPC 18の図を参照してください。

## アプリケーション

### 代表的なアプリケーション回路

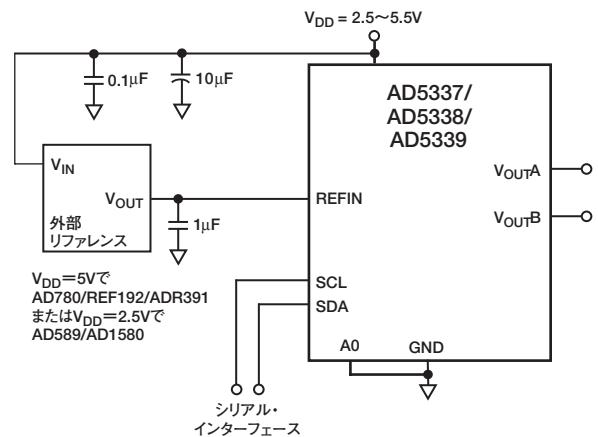

AD5337/AD5338/AD5339は広範なリファレンス電圧で使用でき、デバイスは0V～ $V_{DD}$ のリファレンス範囲で1象限の完全な乗算機能を提供します。一般的には、固定の高精度リファレンス電圧と組み合わせて使用します。5V動作に適したリファレンスは、AD780、REF192、ADR391 (2.5Vリファレンス) です。2.5V動作に適した外部リファレンスには、1.23Vのバンド・ギャップ・リファレンスであるAD589かAD1580があります。図11に、外部リファレンスを用いる場合のAD5337/AD5338/AD5339の代表的な構成を示します。なお、A0はハイまたはローにすることができます。

図11. AD5337/AD5338/AD5339に外部リファレンスを使用する場合

## AD5337/AD5338/AD5339

0V~V<sub>DD</sub>の出力レンジが必要な場合、最も簡単な方法はリファレンス入力をV<sub>DD</sub>に接続することです。この電源は精度が低くノイズが多い場合もあるため、たとえばREF195などの5Vリファレンスを使用して、AD5337/AD5338/AD5339にリファレンスから電源を供給することもできます。REF195は、AD5337/AD5338/AD5339に安定した電源電圧を供給します。REF195から取る必要な電流のtyp値は、DAC出力に負荷が存在しない場合、600μAの電源電流とリファレンス入力への約112μAです。DAC出力に負荷が存在する場合は、REF195は負荷にも電流を供給する必要があります。必要な合計電流（各出力に10kΩの負荷がある場合）は、以下のとおりです。

$$712 \mu\text{A} + 2(5\text{V}/10 \text{k}\Omega = 1.7 \text{mA})$$

REF195の負荷レギュレーションは2ppm/mA (typ) であるため、1.7mAの電流出力で誤差は3.4ppm (17μV) になります。これは8ビットで0.0009LSB、12ビットで0.014LSBの誤差に相当します。

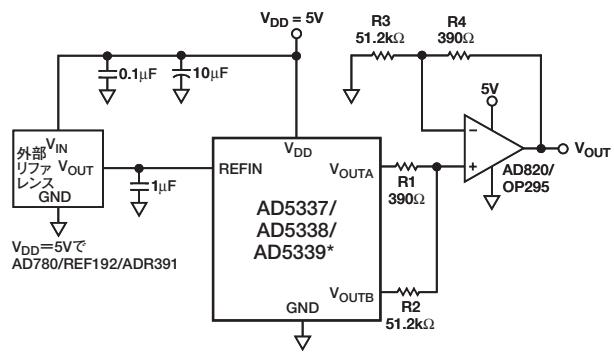

**AD5337/AD5338/AD5339を使用するバイポーラ動作**

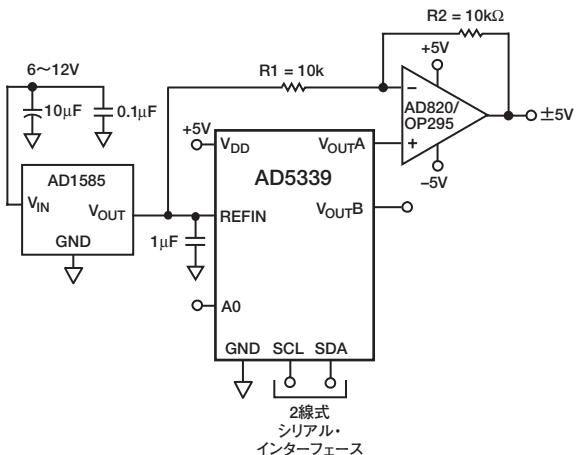

AD5337/AD5338/AD5339は単電源動作用に設計されていますが、図12に示す回路を使用すれば、バイポーラ出力レンジも可能になります。この回路の出力電圧レンジは±5Vです。出力アンプにAD820またはOP295を使用すれば、アンプ出力でのレールtoレール動作が得られます。

図12. AD5339によるバイポーラ動作

任意の入力コードに対する出力電圧は、次式で計算できます。

$$V_{OUT} = [(REFIN \times (D/2^N) \times (R1 + R2) / R1) - REFIN \times (R2 / R1)]$$

ここで、

Dは、DACにロードされるコードと等価な10進値です。

NはDACの分解能です。

REFINはリファレンス電圧入力です。

REFIN=5V、R1=R2=10kΩの場合、次のようにになります。

$$V_{OUT} = (10 \times D/2^N) - 5V$$

### 1つのバスに複数のデバイス

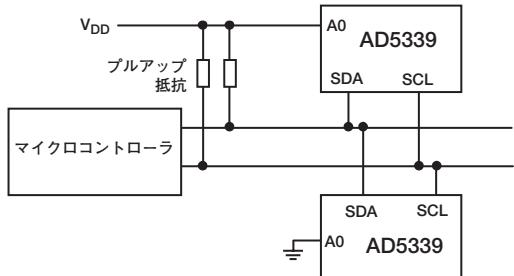

図13に、同じシリアル・バス上の2つのAD5339デバイスを示します。A0pinの状態が異なるため、それぞれのスレーブ・アドレスも異なります。これによって、4つのDACに別々に書き込み／読み出しができます。

図13. 1つのバスに接続した複数のAD5339デバイス

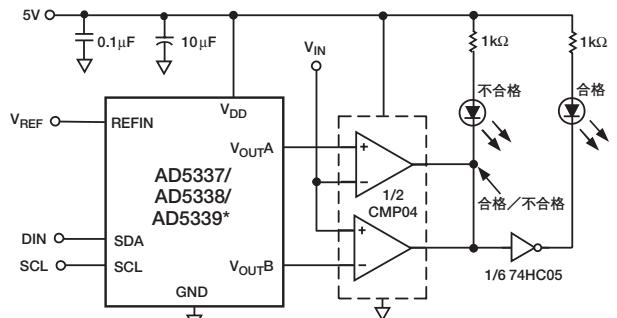

### デジタル設定可能なウインドウ検出器としてのAD5337/AD5338/AD5339

図14に、AD5337/AD5338/AD5339内の2個のDACを使用したデジタル設定可能な上／下限検出器を示します。テスト用の上限値と下限値をDAC AおよびDAC Bにロードし、これによってCMP04の限界値を設定します。V<sub>IN</sub>入力の信号が設定したウインドウの範囲から出ると、LEDが点灯して不合格状態を示します。

\*わかりやすくするために他のピンは省略しています。

図14. ウィンドウ検出

# AD5337/AD5338/AD5339

## AD5337/AD5338/AD5339を使用する粗調整と微調整

図15に示すように、AD5337/AD5338/AD5339内の2個のDACをペアにして、粗調整と微調整の機能を実現できます。DAC Aは粗調整に使用し、DAC Bは微調整に使用します。R1とR2の比率を変更すると、粗調整と微調整の相対的效果が変わります。図に示す抵抗値と外部リファレンスを使用すると、出力アンプにDAC A出力に対するユニティ・ゲインがあるため、出力レンジは0V～(2.5V-1LSB)になります。DAC Bではアンプのゲインが $7.6 \times 10^{-3}$ なので、DAC Bのレンジは19mVに等しくなります。

この回路は2.5Vリファレンスの場合ですが、最高 $V_{DD}$ までのリファレンス電圧を使用できます。ここに示すオペアンプで、レールtoレール出力振幅が可能になります。

\*わかりやすくするために他のピンは省略しています。

図15. 粗調整と微調整

## 電源のデカップリング

精度が大切な回路では、定格の性能を得るために電源とグラウンド・リターンのレイアウトを十分注意して行う必要があります。AD5337/AD5338/AD5339を実装するプリント回路ボードでは、アナログ部とデジタル部を分離して、ボードの一定の場所にまとめて配置するように設計してください。複数のデバイスがAGND～DGND接続を必要とするシステム内でAD5337/AD5338/AD5339を使用する場合は、その接続は1点だけで行ってください。可能な限りデバイスの近くに星形グラウンド・ポイントを配置してください。AD5337/AD5338/AD5339では、 $10\mu F$ と $0.1\mu F$ のコンデンサをできるだけパッケージの近く、理想的にはデバイスのすぐ隣で並列接続し、電源に対して十分なバイパスをとる必要があります。 $10\mu F$ のコンデンサは、タンタルのビード型を使います。 $0.1\mu F$ のコンデンサは、高周波でグラウンドに対する低インピーダンス・バスを提供する一般的なセラミック・タイプなど、低い有効直列抵抗(ESR)と有効直列インダクタンス(ESI)を備えたものを使用し、内部ロジックの切り替えによる過渡電流を処理します。

AD5337/AD5338/AD5339の電源ラインはできるだけ太いパターンにしてインピーダンスを下げ、電源ライン上のグリッチによる影響を小さくします。クロックなどの高速スイッチング信号はデジタル・グラウンドでシールドし、ボードの他の部分にノイズを拡散しないようにし、また絶対にリファレンス入力の近くを通さないようにしてください。SDAラインとSCLラインの間にグラウンド・ラインを配置すれば、この2つのラインの間のクロストークが低減します（多層ボードではグラウンド・プレーンが分離されているため不要ですが、ラインの分離は効果があります）。

デジタル信号とアナログ信号が交差しないようにしてください。ボードの反対側のパターンは互いに直角になるように配置し、これによってボードを通過するフィードスルーの影響を低減します。マイクロストリップ技術は最善の方法ですが、両面ボードでは常に使用できるわけではありません。この技術では、ボードの部品面をグラウンド・プレーン専用にし、信号パターンをハンダ面に配置します。

## AD5337/AD5338/AD5339

表2. 全AD53xxシリアル・デバイスの概要

| 部品番号        | 分解能 | DACの数 | DNL        | インターフェース | セトリング・タイム | パッケージ       | ピン  |

|-------------|-----|-------|------------|----------|-----------|-------------|-----|

| <b>シングル</b> |     |       |            |          |           |             |     |

| AD5300      | 8   | 1     | $\pm 0.25$ | SPI      | 4μs       | SOT-23、MSOP | 6、8 |

| AD5310      | 10  | 1     | $\pm 0.5$  | SPI      | 6μs       | SOT-23、MSOP | 6、8 |

| AD5320      | 12  | 1     | $\pm 1.0$  | SPI      | 8μs       | SOT-23、MSOP | 6、8 |

| AD5301      | 8   | 1     | $\pm 0.25$ | 2線式      | 6μs       | SOT-23、MSOP | 6、8 |

| AD5311      | 10  | 1     | $\pm 0.5$  | 2線式      | 7μs       | SOT-23、MSOP | 6、8 |

| AD5321      | 12  | 1     | $\pm 1.0$  | 2線式      | 8μs       | SOT-23、MSOP | 6、8 |

| <b>デュアル</b> |     |       |            |          |           |             |     |

| AD5302      | 8   | 2     | $\pm 0.25$ | SPI      | 6μs       | MSOP        | 8   |

| AD5312      | 10  | 2     | $\pm 0.5$  | SPI      | 7μs       | MSOP        | 8   |

| AD5322      | 12  | 2     | $\pm 1.0$  | SPI      | 8μs       | MSOP        | 8   |

| AD5303      | 8   | 2     | $\pm 0.25$ | SPI      | 6μs       | TSSOP       | 16  |

| AD5313      | 10  | 2     | $\pm 0.5$  | SPI      | 7μs       | TSSOP       | 16  |

| AD5323      | 12  | 2     | $\pm 1.0$  | SPI      | 8μs       | TSSOP       | 16  |

| AD5337      | 8   | 2     | $\pm 0.25$ | 2線式      | 6μs       | MSOP        | 8   |

| AD5338      | 10  | 2     | $\pm 0.5$  | 2線式      | 7μs       | MSOP        | 8   |

| AD5339      | 12  | 2     | $\pm 1.0$  | 2線式      | 8μs       | MSOP        | 8   |

| <b>クワッド</b> |     |       |            |          |           |             |     |

| AD5304      | 8   | 4     | $\pm 0.25$ | SPI      | 6μs       | MSOP        | 10  |

| AD5314      | 10  | 4     | $\pm 0.5$  | SPI      | 7μs       | MSOP        | 10  |

| AD5324      | 12  | 4     | $\pm 1.0$  | SPI      | 8μs       | MSOP        | 10  |

| AD5305      | 8   | 4     | $\pm 0.25$ | 2線式      | 6μs       | MSOP        | 10  |

| AD5315      | 10  | 4     | $\pm 0.5$  | 2線式      | 7μs       | MSOP        | 10  |

| AD5325      | 12  | 4     | $\pm 1.0$  | 2線式      | 8μs       | MSOP        | 10  |

| AD5306      | 8   | 4     | $\pm 0.25$ | 2線式      | 6μs       | TSSOP       | 16  |

| AD5316      | 10  | 4     | $\pm 0.5$  | 2線式      | 7μs       | TSSOP       | 16  |

| AD5326      | 12  | 4     | $\pm 1.0$  | 2線式      | 8μs       | TSSOP       | 16  |

| AD5307      | 8   | 4     | $\pm 0.25$ | SPI      | 6μs       | TSSOP       | 16  |

| AD5317      | 10  | 4     | $\pm 0.5$  | SPI      | 7μs       | TSSOP       | 16  |

| AD5327      | 12  | 4     | $\pm 1.0$  | SPI      | 8μs       | TSSOP       | 16  |

| <b>オクタル</b> |     |       |            |          |           |             |     |

| AD5308      | 8   | 8     | $\pm 0.25$ | SPI      | 6μs       | TSSOP       | 16  |

| AD5318      | 10  | 8     | $\pm 0.5$  | SPI      | 7μs       | TSSOP       | 16  |

| AD5328      | 12  | 8     | $\pm 1.0$  | SPI      | 8μs       | TSSOP       | 16  |

アナログ・デバイセズのWebサイトをご覧ください：[www.analog.com/support/standard\\_linear/selection\\_guides/AD53xx.html](http://www.analog.com/support/standard_linear/selection_guides/AD53xx.html)

# AD5337/AD5338/AD5339

表3. AD53xxパラレル・デバイスの概要

| 部品番号        | 分解能 | DNL   | V <sub>REF</sub> ピン | セトリング・タイム | 追加のピン機能 |      |      |     | パッケージ       | ピン    |

|-------------|-----|-------|---------------------|-----------|---------|------|------|-----|-------------|-------|

|             |     |       |                     |           | BUF     | GAIN | HBEN | CLR |             |       |

| <b>シングル</b> |     |       |                     |           |         |      |      |     |             |       |

| AD5330      | 8   | ±0.25 | 1                   | 6μs       | ✓       | ✓    |      | ✓   | TSSOP       | 20    |

| AD5331      | 10  | ±0.5  | 1                   | 7μs       |         | ✓    |      | ✓   | TSSOP       | 20    |

| AD5340      | 12  | ±1.0  | 1                   | 8μs       | ✓       | ✓    |      | ✓   | TSSOP       | 24    |

| AD5341      | 12  | ±1.0  | 1                   | 8μs       | ✓       | ✓    | ✓    | ✓   | TSSOP       | 20    |

| <b>デュアル</b> |     |       |                     |           |         |      |      |     |             |       |

| AD5332      | 8   | ±0.25 | 2                   | 6μs       |         |      |      | ✓   | TSSOP       | 20    |

| AD5333      | 10  | ±0.5  | 2                   | 7μs       | ✓       | ✓    |      | ✓   | TSSOP       | 24    |

| AD5342      | 12  | ±1.0  | 2                   | 8μs       | ✓       | ✓    |      | ✓   | TSSOP       | 28    |

| AD5343      | 12  | ±1.0  | 1                   | 8μs       |         |      | ✓    | ✓   | TSSOP       | 20    |

| <b>クワッド</b> |     |       |                     |           |         |      |      |     |             |       |

| AD5334      | 8   | ±0.25 | 2                   | 6μs       |         | ✓    |      | ✓   | TSSOP       | 24    |

| AD5335      | 10  | ±0.5  | 2                   | 7μs       |         |      | ✓    | ✓   | TSSOP       | 24    |

| AD5336      | 10  | ±0.5  | 4                   | 7μs       |         | ✓    |      | ✓   | TSSOP       | 28    |

| AD5344      | 12  | ±1.0  | 4                   | 8μs       |         |      |      |     | TSSOP       | 28    |

| <b>オクタル</b> |     |       |                     |           |         |      |      |     |             |       |

| AD5346      | 8   | ±0.25 | 4                   | 6μs       | ✓       | ✓    |      | ✓   | TSSOP、LFCSP | 38、40 |

| AD5347      | 10  | ±0.5  | 4                   | 7μs       | ✓       | ✓    |      | ✓   | TSSOP       | 38、40 |

| AD5348      | 12  | ±1.0  | 4                   | 8μs       | ✓       | ✓    |      | ✓   | TSSOP       | 38、40 |

C03756-0-11/03(0)-J

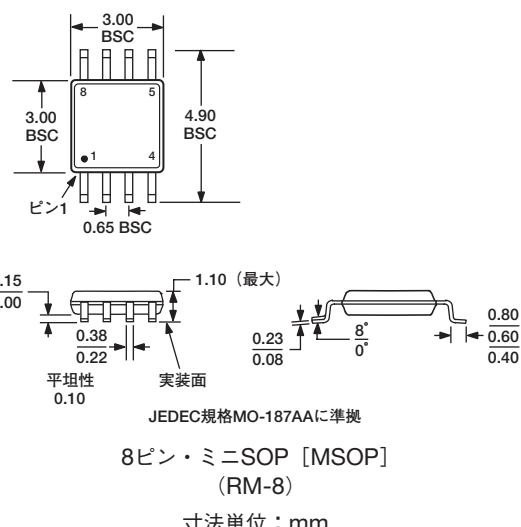

## 外形寸法

アナログ・デバイセズまたは同社の二次ライセンスを受けた関連会社からライセンスの対象となるI<sup>2</sup>Cコンポーネントを購入した場合、購入者にはこれらのコンポーネントをI<sup>2</sup>Cシステムで使用するフィリップス社のI<sup>2</sup>Cの特許権にもとづくライセンスが許諾されます。ただし、フィリップス社が規定するI<sup>2</sup>C標準仕様に準拠したシステムが必要です。