**AD5334/AD5335/AD5336/AD5344\***

**特長**

AD5334 : 24ピンTSSOPのクワッド8ビットDAC

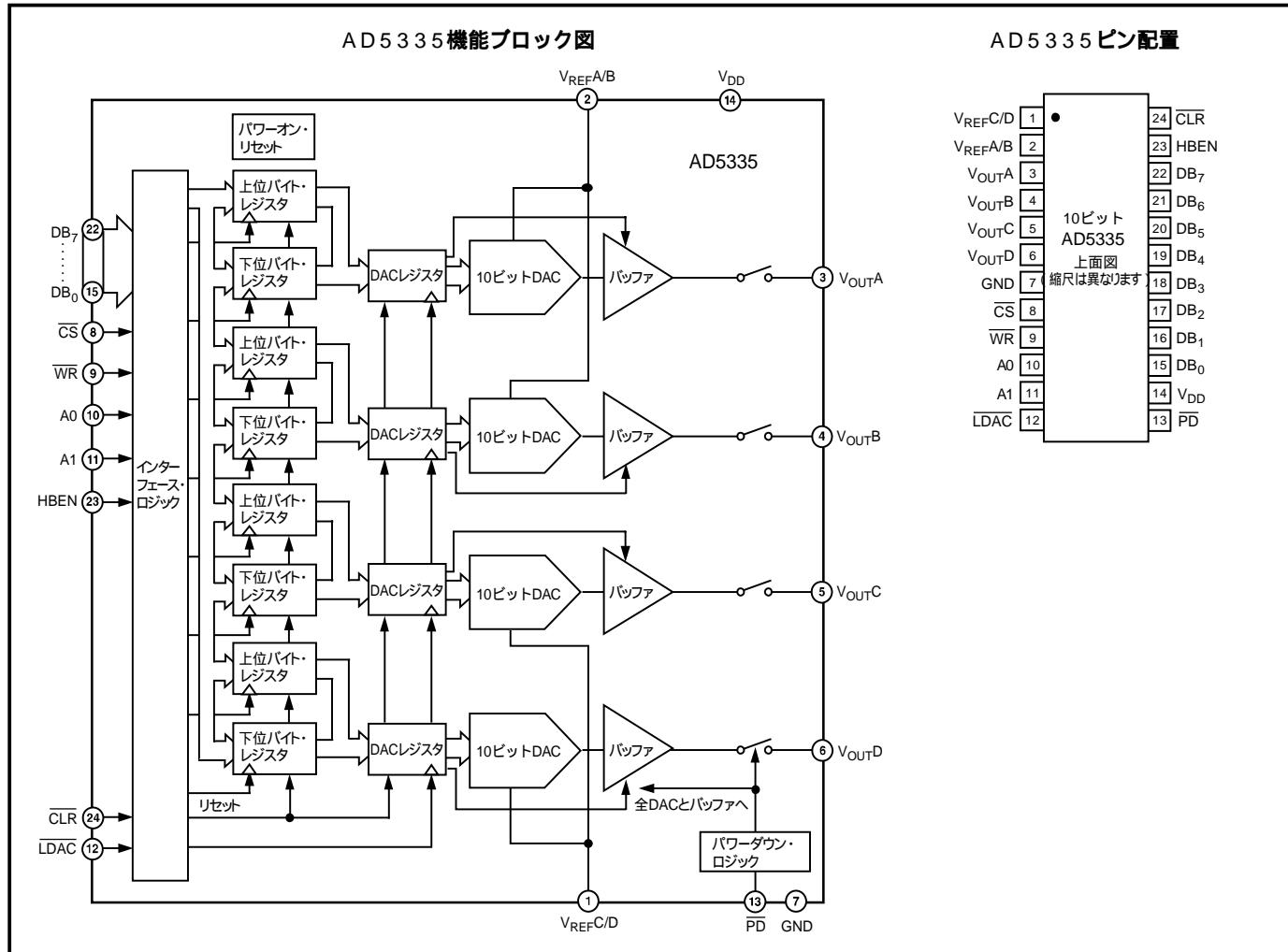

AD5335 : 24ピンTSSOPのクワッド10ビットDAC

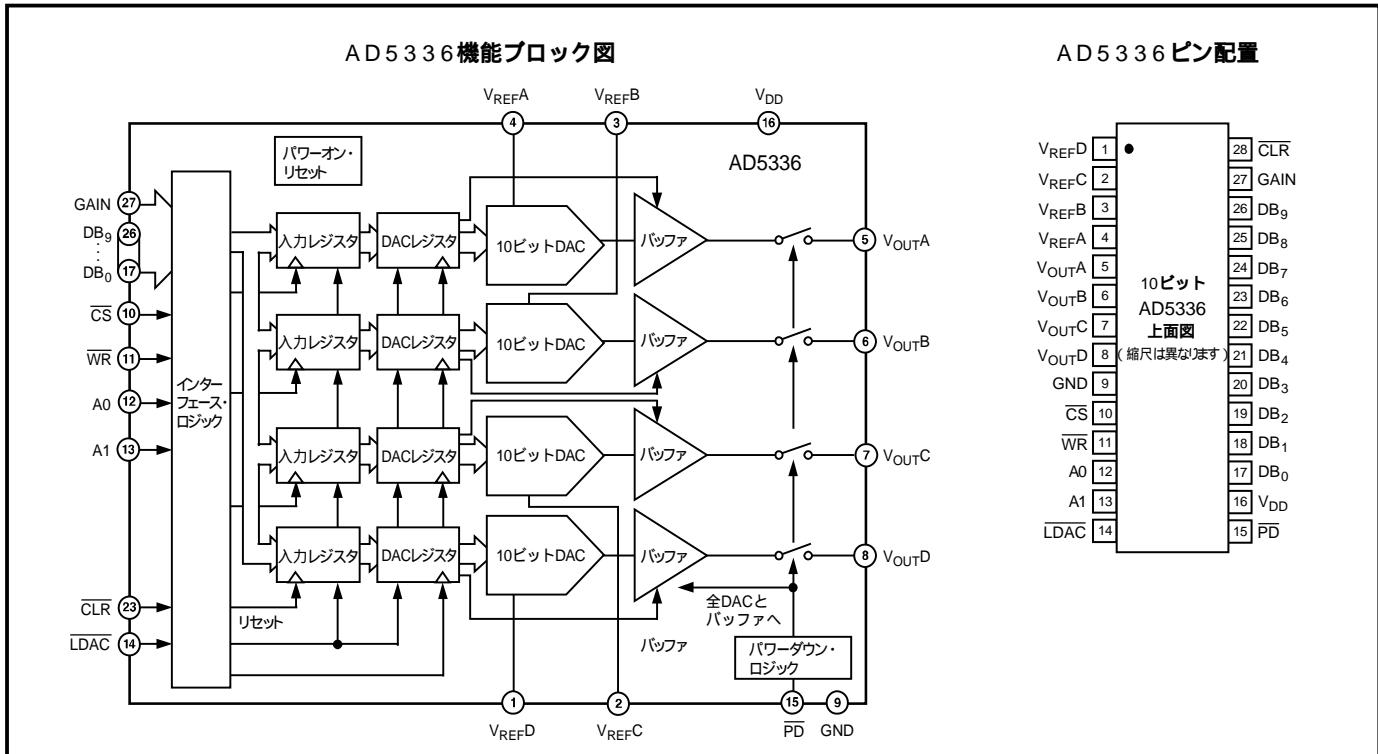

AD5336 : 28ピンTSSOPのクワッド10ビットDAC

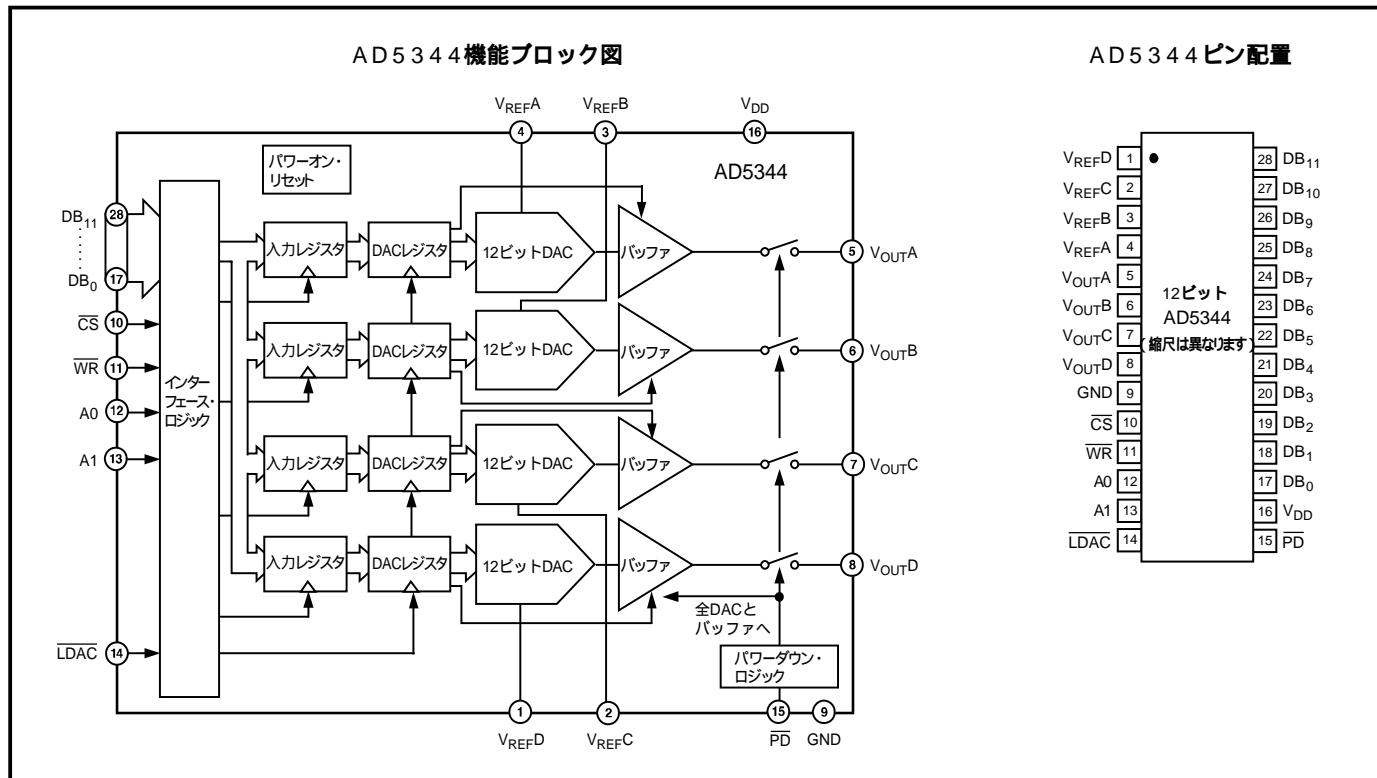

AD5344 : 28ピンTSSOPのクワッド12ビットDAC

**低消費電力動作** : 3Vで500 μA、5Vで600 μA

**パワーダウン** : PDピンを使い3Vで80nA、5Vで200nAまで

**電源** : 2.5~5.5V

**ダブルバッファ入力ロジック**

全コードに対する単調性を設計により保証

出力範囲 : 0 ~  $V_{REF}$  または 0 ~  $2 \times V_{REF}$

0Vへのパワーオン・リセット

LDACピンの非同期CLR機能を使うDAC出力の同時更新

低消費電力のパラレル・データ・インターフェース

レールtoレール出力のバッファ・アンプを内蔵

温度範囲 : -40 ~ +105

**アプリケーション**

バッテリ駆動のポータブル機器

ゲインとオフセットのデジタル調整

プログラマブルな電圧 / 電流源

プログラマブルな減衰器

工業用プロセス制御

**概要**

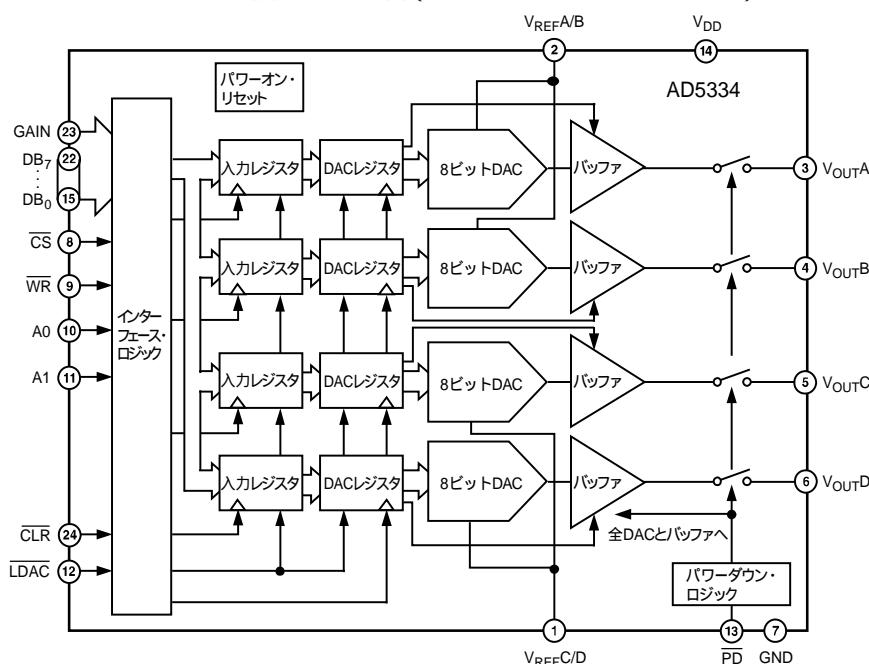

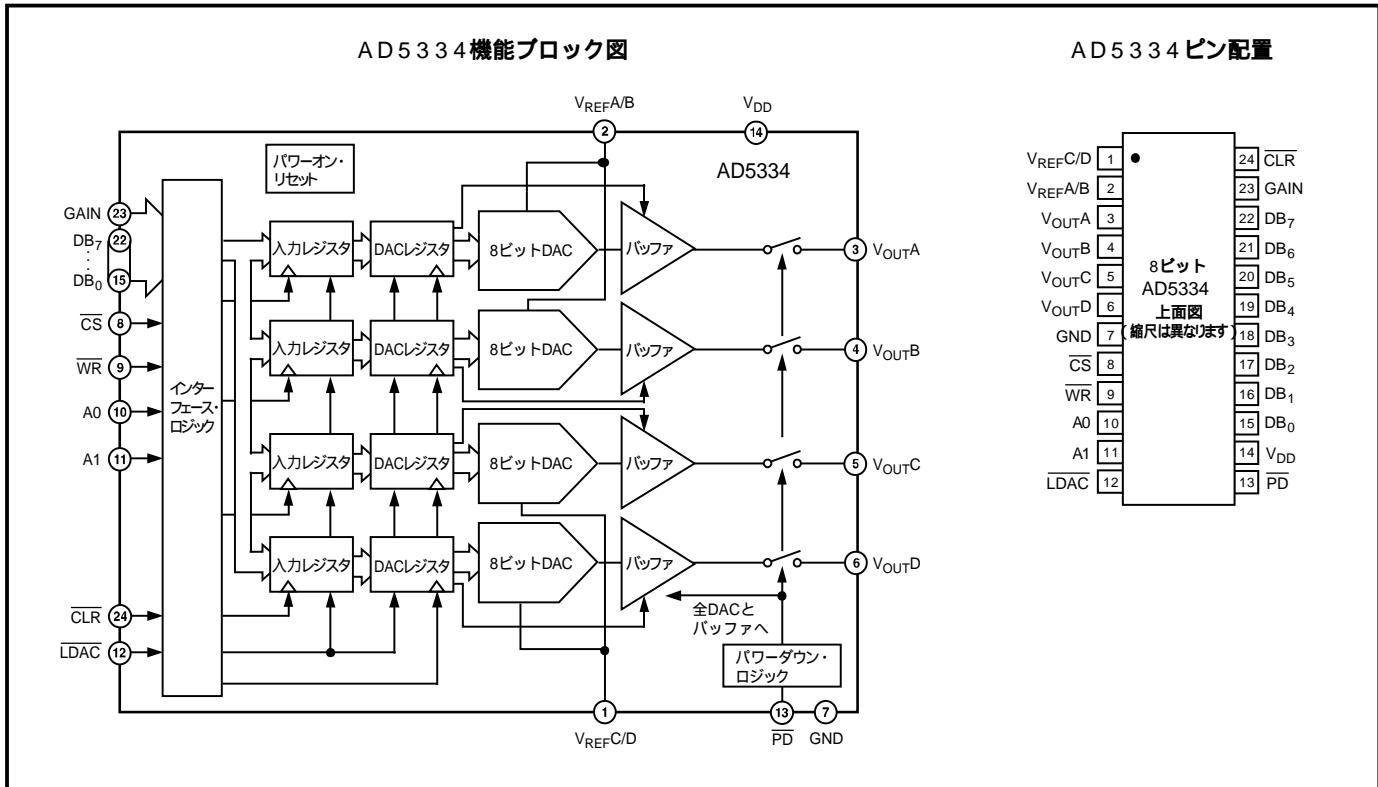

AD5334/AD5335/AD5336/AD5344は、それぞれ8/10/12ビットのクワッドDACです。これらのデバイスは、2.5~5.5V電源で動作し、3Vでの消費電力はわずか500 μA、さらに電流を80nAまで減少させるパワーダウン・モードを備えています。また、出力を両電源レールまで駆動できる出力バッファも内蔵しています。

AD5334/AD5335/AD5336/AD5344は、パラレル・インターフェースを内蔵しています。

CSはデバイスを選択し、データはWRの立ち上がりエッジで入力レジスタにロードされます。

AD5334/AD5336のGAINピンを使うと、出力範囲を0V ~  $V_{REF}$  または 0V ~  $2 \times V_{REF}$  に設定できます。

DACに対する入力データはダブルバッファされているため、LDACピンを使ってシステム内の複数のDACを同時に更新できます。

AD5334/AD5335/AD5336には、非同期のCLR入力も用意されており、入力レジスタとDACレジスタの値をゼロにリセットできます。

これらのデバイスは、パワーオン・リセット回路を内蔵しており、この回路により、パワーアップ時にDAC出力を0Vにし、デバイスに対する有効な書き込みが行われるまでこの0Vを維持できます。

AD5334/AD5335/AD5336/AD5344は、薄型シールド・スモール・アウトライン・パッケージ TSSOP を使用しています。

AD5334機能ブロック図 (他のブロック図は文中にあります)

\*米国特許No.5,969,657で保護されています。その他の特許は申請中です。

REV.0

アナログ・デバイセズ社が提供する情報は正確で信頼できるものと期していますが、その情報の利用または利用したことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものではありません。

# AD5334/AD5335/AD5336/AD5344 仕様

(特に指定のない限り、 $V_{DD} = 2.5 \sim 5.5V$ 、 $V_{REF} = 2V$ 、 $R_L = 2k$  ( GNDに接続 )、 $C_L = 200pF$  ( GNDに接続 )、 $T_{MIN} \sim T_{MAX}$  で全仕様を規定 )

| パラメータ <sup>1</sup>       | Min              | Bバージョン <sup>2</sup><br>Typ | Max | 単位       | 条件 / 備考                                                |

|--------------------------|------------------|----------------------------|-----|----------|--------------------------------------------------------|

| DC性能 <sup>3、4</sup>      |                  |                            |     |          |                                                        |

| AD5334                   |                  |                            |     |          |                                                        |

| 分解能                      | 8                |                            |     | ビット      |                                                        |

| 相対精度                     | $\pm 0.15$       | $\pm 1$                    |     | LSB      |                                                        |

| 微分非直線性                   | $\pm 0.02$       | $\pm 0.25$                 |     | LSB      | 全コードに対する単調性を設計により保証                                    |

| AD5335/AD5336            |                  |                            |     |          |                                                        |

| 分解能                      | 10               |                            |     | ビット      |                                                        |

| 相対精度                     | $\pm 0.5$        | $\pm 4$                    |     | LSB      |                                                        |

| 微分非直線性                   | $\pm 0.05$       | $\pm 0.5$                  |     | LSB      | 全コードに対する単調性を設計により保証                                    |

| AD5344                   |                  |                            |     |          |                                                        |

| 分解能                      | 12               |                            |     | ビット      |                                                        |

| 相対精度                     | $\pm 2$          | $\pm 16$                   |     | LSB      |                                                        |

| 微分非直線性                   | $\pm 0.2$        | $\pm 1$                    |     | LSB      | 全コードに対する単調性を設計により保証                                    |

| オフセット誤差                  | $\pm 0.4$        | $\pm 3$                    |     | FSRの%    |                                                        |

| ゲイン誤差                    | $\pm 0.1$        | $\pm 1$                    |     | FSRの%    |                                                        |

| 下側デッドバンド <sup>5</sup>    | 10               | 60                         |     | mV       |                                                        |

| 上側デッドバンド                 | 10               | 60                         |     | mV       |                                                        |

| オフセット誤差ドリフト <sup>6</sup> | - 12             |                            |     | FSR/ ppm |                                                        |

| ゲイン誤差ドリフト <sup>6</sup>   | - 5              |                            |     | FSR/ ppm |                                                        |

| DC電源変動除去比 <sup>6</sup>   | - 60             |                            |     | dB       |                                                        |

| DCクロストーク <sup>6</sup>    | 200              |                            |     | $\mu V$  |                                                        |

| DACリファレンス入力 <sup>6</sup> |                  |                            |     |          |                                                        |

| $V_{REF}$ 入力範囲           | 0.25             |                            |     |          |                                                        |

| $V_{REF}$ 入力インピーダンス      |                  | $V_{DD}$                   |     |          |                                                        |

| リファレンス・フィードスルー           |                  |                            |     |          | ゲイン = 1。入力インピーダンス = $R_{DAC}$ ( AD5336/AD5344 )        |

| チャンネル間アイソレーション           |                  |                            |     |          | ゲイン = 2。入力インピーダンス = $R_{DAC}$ ( AD5336 )               |

| 出力特性 <sup>6</sup>        |                  |                            |     |          | ゲイン = 1。入力インピーダンス = $R_{DAC}$ ( AD5334 / AD5335 )      |

| 最小出力電圧 <sup>4、7</sup>    | 0.001            |                            |     |          | ゲイン = 2。入力インピーダンス = $R_{DAC}$ ( AD5334 )               |

| 最大出力電圧 <sup>4、7</sup>    | $V_{DD} - 0.001$ |                            |     |          |                                                        |

| DC出力インピーダンス              | 0.5              |                            |     |          |                                                        |

| 短絡電流                     | 50               |                            |     | mA       |                                                        |

|                          | 20               |                            |     | mA       | $V_{DD} = 5V$                                          |

| パワーアップ時間                 | 2.5              |                            |     | $\mu s$  | $V_{DD} = 3V$                                          |

|                          | 5                |                            |     | $\mu s$  | パワーダウン・モードから。 $V_{DD} = 5V$                            |

|                          |                  |                            |     |          | パワーダウン・モードから。 $V_{DD} = 3V$                            |

| ロジック入力 <sup>6</sup>      |                  |                            |     |          |                                                        |

| 入力電流                     | $\pm 1$          |                            |     |          | レールtoレール動作                                             |

| $V_{IL}$ 、入力ロー電圧         |                  |                            |     |          |                                                        |

|                          |                  | 0.8                        |     | $\mu s$  |                                                        |

|                          |                  | 0.6                        |     | V        | $V_{DD} = 5V \pm 10\%$                                 |

|                          |                  | 0.5                        |     | V        | $V_{DD} = 3V \pm 10\%$                                 |

|                          |                  |                            |     | V        | $V_{DD} = 2.5V$                                        |

| $V_{IH}$ 、入力ハイ電圧         | 2.4              |                            |     | V        | $V_{DD} = 5V \pm 10\%$                                 |

|                          | 2.1              |                            |     | V        | $V_{DD} = 3V \pm 10\%$                                 |

|                          | 2.0              |                            |     | V        | $V_{DD} = 2.5V$                                        |

| ピン容量                     |                  | 3.5                        |     | $pF$     |                                                        |

| 電源条件                     |                  |                            |     |          |                                                        |

| $V_{DD}$                 | 2.5              |                            | 5.5 | V        |                                                        |

| $I_{DD}$ ( 通常モード )       |                  |                            |     |          | 全DACがアクティブ、負荷電流を除く。                                    |

| $V_{DD} = 4.5 \sim 5.5V$ | 600              | 900                        |     | $\mu A$  | $V_{IH} = V_{DD}$ 、 $V_{IL} = GND$                     |

| $V_{DD} = 2.5 \sim 3.6V$ | 500              | 700                        |     | $\mu A$  | $V_{REF} > V_{DD} - 100mV$ で、 $I_{DD}$ は50 $\mu A$ 増加。 |

| $I_{DD}$ ( パワーダウン・モード )  |                  |                            |     |          |                                                        |

| $V_{DD} = 4.5 \sim 5.5V$ | 0.2              | 1                          |     | $\mu A$  |                                                        |

| $V_{DD} = 2.5 \sim 3.6V$ | 0.08             | 1                          |     | $\mu A$  |                                                        |

## 注

- 用語集を参照。

- 温度範囲 : Bバージョン : - 40 ~ + 105 、 25 でのtyp値

- 直線性はコード範囲を縮小してテストしています。AD5334 : コード8 ~ 255、AD5335/AD5336 : コード28 ~ 1023、AD5344 : コード115 ~ 4095。

- 出力無負荷でテストしたDC仕様。

- これはxコードに対応します。x = デッドバンド電圧 / LSBサイズ。

- 設計と特性により保証しますが、出荷テストは行いません。

- アンプ出力が最小電圧に到達するためには、オフセット誤差は負である必要があります。アンプ出力が最大電圧に到達するためには、 $V_{REF} = V_{DD}$ かつ“オフセットとゲインの和”のオフセット誤差は正である必要があります。

仕様は予告なく変更されることがあります。

# AD5334/AD5335/AD5336/AD5344

## AC特性<sup>1</sup>

(特に指定のない限り、 $V_{DD} = 2.5 \sim 5.5V$ 、 $R_L = 2k$  ( GNDに接続 )  $C_L = 200pF$  ( GNDに接続 )  $T_{MIN} \sim T_{MAX}$ で全仕様を規定 )

| パラメータ <sup>2</sup> | Min | Bバージョン <sup>3</sup> | Max | 単位           | 条件 / 備考                                   |

|--------------------|-----|---------------------|-----|--------------|-------------------------------------------|

| 出力電圧セトリング・タイム      |     |                     |     |              | $V_{REF} = 2V$ 。図20参照                     |

| AD5334             | 6   | 8                   |     | $\mu s$      | 1/4スケールから3/4スケールに変化 ( 40Hex ~ C0Hex )     |

| AD5335             | 7   | 9                   |     | $\mu s$      | 1/4スケールから3/4スケールに変化 ( 100Hex ~ 300Hex )   |

| AD5336             | 7   | 9                   |     | $\mu s$      | 1/4スケールから3/4スケールに変化 ( 100Hex ~ 300Hex )   |

| AD5344             | 8   | 10                  |     | $\mu s$      | 1/4スケールから3/4スケールに変化 ( 400Hex ~ C00Hex )   |

| スルーレート             | 0.7 |                     |     | $V/\mu s$    |                                           |

| 主要コード変化時のグリッチ電力    | 8   |                     |     | $nV \cdot s$ | 主要キャリーの付近で1 LSB変化                         |

| デジタル・フィードスルー       | 0.5 |                     |     | $nV \cdot s$ |                                           |

| デジタル・クロストーク        | 3   |                     |     | $nV \cdot s$ |                                           |

| アナログ・クロストーク        | 0.5 |                     |     | $nV \cdot s$ |                                           |

| DAC間クロストーク         | 3.5 |                     |     | $nV \cdot s$ |                                           |

| マルチプル帯域幅           | 200 |                     |     | $kHz$        | $V_{REF} = 2V \pm 0.1Vp-p$ 。バッファなしモード     |

| 合計高調波歪み            | -70 |                     |     | $dB$         | $V_{REF} = 2.5V \pm 0.1Vp-p$ 。周波数 = 10kHz |

### 注

1. 設計と特性により保証しますが、出荷テストは行いません。

2. 用語集を参照。

3. 温度範囲: Bバージョン: -40 ~ +105 、25 でのtyp値

仕様は予告なく変更されることがあります。

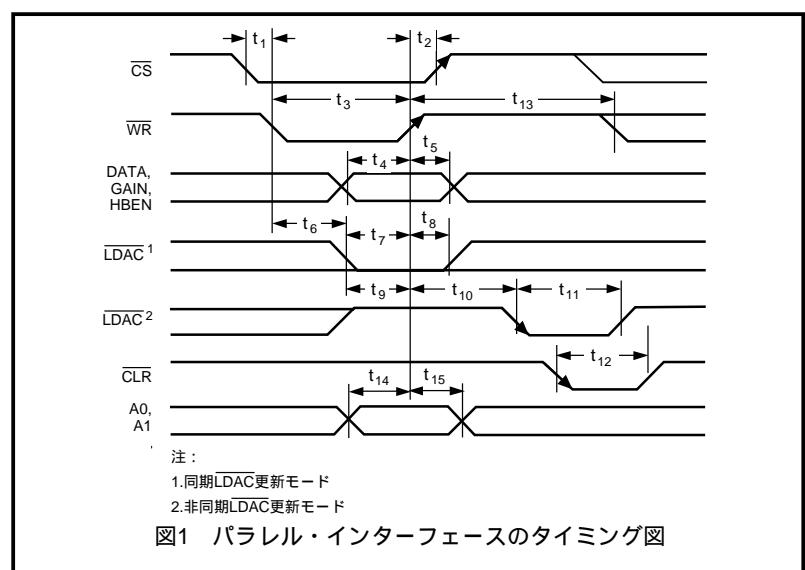

## タイミング特性<sup>1, 2, 3</sup>

(特に指定のない限り、 $V_{DD} = 2.5 \sim 5.5V$ 、 $T_{MIN} \sim T_{MAX}$ で全仕様を規定 )

| パラメータ    | $T_{MIN}, T_{MAX}$ での規定値 | 単位     | 条件 / 備考                        |

|----------|--------------------------|--------|--------------------------------|

| $t_1$    | 0                        | ns min | CSからWRまでのセットアップ・タイム            |

| $t_2$    | 0                        | ns min | CSからWRまでのホールド・タイム              |

| $t_3$    | 20                       | ns min | WRのパルス幅                        |

| $t_4$    | 5                        | ns min | データ、GAIN、HBENセットアップ・タイム        |

| $t_5$    | 4.5                      | ns min | データ、GAIN、HBENホールド・タイム          |

| $t_6$    | 5                        | ns min | 同期モード。WRの立ち下がりからLDACの立ち下がりまで。  |

| $t_7$    | 5                        | ns min | 同期モード。LDACの立ち下がりからWRの立ち上がりまで。  |

| $t_8$    | 4.5                      | ns min | 同期モード。WRの立ち上がりからLDACの立ち上がりまで。  |

| $t_9$    | 5                        | ns min | 非同期モード。LDACの立ち上がりからWRの立ち上がりまで。 |

| $t_{10}$ | 4.5                      | ns min | 非同期モード。WRの立ち上がりからLDACの立ち下がりまで。 |

| $t_{11}$ | 20                       | ns min | LDACのパルス幅                      |

| $t_{12}$ | 20                       | ns min | CLRのパルス幅                       |

| $t_{13}$ | 50                       | ns min | WRサイクル間の時間。                    |

| $t_{14}$ | 20                       | ns min | A0、A1のセットアップ・タイム               |

| $t_{15}$ | 0                        | ns min | A0、A1のホールド・タイム                 |

### 注

1. 設計と特性により保証しますが、出荷テストは行いません。

2. すべての入力信号は $t_r = t_f = 5ns$  ( $V_{DD}$ の10 ~ 90%) で規定し、 $(V_{IL} + V_{IH}) / 2$ の電圧レベルからの時間とします。

3. 図1を参照してください。

仕様は予告なく変更されることがあります。

# AD5334/AD5335/AD5336/AD5344

## 絶対最大定格 (特に指定のない限り、 $T_A = 25^\circ C$ )

|                     |                          |

|---------------------|--------------------------|

| $V_{DD} \sim GND$   | - 0.3 ~ + 7V             |

| デジタル入力電圧 $\sim GND$ | - 0.3V ~ $V_{DD} + 0.3V$ |

| デジタル出力電圧 $\sim GND$ | - 0.3V ~ $V_{DD} + 0.3V$ |

| 入力リファレンス $\sim GND$ | - 0.3V ~ $V_{DD} + 0.3V$ |

| $V_{OUT} \sim GND$  | - 0.3V ~ $V_{DD} + 0.3V$ |

## 動作温度範囲

|              |              |

|--------------|--------------|

| 工業用 (Bバージョン) | - 40 ~ + 105 |

| 保管温度範囲       | - 65 ~ + 150 |

| 接合温度         | 150          |

## TSSOPパッケージ

|                                  |                                    |

|----------------------------------|------------------------------------|

| ワット損                             | $(T_{J\max} - T_A) / \rho_{JA} mW$ |

| $\rho_{JA}$ 熱インピーダンス (24ピンTSSOP) | 128 /W                             |

| $\rho_{JA}$ 熱インピーダンス (28ピンTSSOP) | 97.9 /W                            |

| $\rho_{JC}$ 熱インピーダンス (24ピンTSSOP) | 42 /W                              |

| $\rho_{JC}$ 熱インピーダンス (28ピンTSSOP) | 14 /W                              |

## オーダー・ガイド

| モデル       | 温度範囲         | パッケージ                             | パッケージ・オプション* |

|-----------|--------------|-----------------------------------|--------------|

| AD5334BRU | - 40 ~ + 105 | TSSOP (薄型シュリンク・スマート・アウトライン・パッケージ) | RU-24        |

| AD5335BRU | - 40 ~ + 105 | TSSOP (薄型シュリンク・スマート・アウトライン・パッケージ) | RU-24        |

| AD5336BRU | - 40 ~ + 105 | TSSOP (薄型シュリンク・スマート・アウトライン・パッケージ) | RU-28        |

| AD5344BRU | - 40 ~ + 105 | TSSOP (薄型シュリンク・スマート・アウトライン・パッケージ) | RU-28        |

## 注意

ESD (静電放電) の影響を受けやすいデバイスです。4000Vもの高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることがあります。本製品には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や機能喪失を回避するために、適切なESD予防措置をとるようお奨めします。

# AD5334/AD5335/AD5336/AD5344

## AD5334 ピン機能説明

| ピン番号    | 記号                                | 機能                                                                                       |

|---------|-----------------------------------|------------------------------------------------------------------------------------------|

| 1       | V <sub>REFC/D</sub>               | DAC CとDAC Dのバッファなしのリファレンス入力。                                                             |

| 2       | V <sub>REFA/B</sub>               | DAC AとDAC Bのバッファなしのリファレンス入力。                                                             |

| 3       | V <sub>OUTA</sub>                 | DAC A出力。レールtoレール動作が可能なバッファ付き出力。                                                          |

| 4       | V <sub>OUTB</sub>                 | DAC B出力。レールtoレール動作が可能なバッファ付き出力。                                                          |

| 5       | V <sub>OUTC</sub>                 | DAC C出力。レールtoレール動作が可能なバッファ付き出力。                                                          |

| 6       | V <sub>OUTD</sub>                 | DAC D出力。レールtoレール動作が可能なバッファ付き出力。                                                          |

| 7       | GND                               | デバイス上の全回路に対するグラウンド・リファレンス・ポイント。                                                          |

| 8       | CS                                | アクティブ・ローのチップ・セレクト入力。WRと組み合わせて、パラレル・インターフェースへのデータの書き込みに使用します。                             |

| 9       | WR                                | アクティブ・ローの書き込み入力。CSと組み合わせて、パラレル・インターフェースへのデータの書き込みに使用します。                                 |

| 10      | A0                                | 書き込みを行うDACを選択するLSBアドレス・ピン。                                                               |

| 11      | A1                                | 書き込みを行うDACを選択するMSBアドレス・ピン。                                                               |

| 12      | LDAC                              | DACレジスタを入力レジスタ値で更新するアクティブ・ローのコントロール入力。この信号を使うと、全DAC出力を同時に更新できます。                         |

| 13      | PD                                | パワーダウン・ピン。このアクティブ・ローのコントロール・ピンにより、全DACをパワーダウン・モードにします。                                   |

| 14      | V <sub>DD</sub>                   | 電源ピン。これらのデバイスは2.5 ~ 5.5Vの電源で動作でき、電源は10 μFと0.1 μFのパラレル接続したコンデンサにより、GNDからデカップリングする必要があります。 |

| 15 ~ 22 | DB <sub>0</sub> ~ DB <sub>7</sub> | 8本のパラレル・データ入力。DB <sub>7</sub> がこれら8ビットのMSB。                                              |

| 23      | GAIN                              | ゲイン・コントロール・ピン。DAC出力範囲0 ~ V <sub>REF</sub> または0 ~ 2 × V <sub>REF</sub> を選択します。            |

| 24      | CLR                               | すべての入力レジスタとDACレジスタをゼロにクリアするアクティブ・ローの非同期コントロール入力。                                         |

# AD5334/AD5335/AD5336/AD5344

## AD5335 ピン機能説明

| ピン番号  | 記号                               | 機能                                                                                 |

|-------|----------------------------------|------------------------------------------------------------------------------------|

| 1     | V <sub>REFC/D</sub>              | DAC CとDAC Dのバッファなしのリファレンス入力。                                                       |

| 2     | V <sub>REFA/B</sub>              | DAC AとDAC Bのバッファなしのリファレンス入力。                                                       |

| 3     | V <sub>OUTA</sub>                | DAC A出力。レールtoレール動作が可能なバッファ付き出力。                                                    |

| 4     | V <sub>OUTB</sub>                | DAC B出力。レールtoレール動作が可能なバッファ付き出力。                                                    |

| 5     | V <sub>OUTC</sub>                | DAC C出力。レールtoレール動作が可能なバッファ付き出力。                                                    |

| 6     | V <sub>OUTD</sub>                | DAC D出力。レールtoレール動作が可能なバッファ付き出力。                                                    |

| 7     | GND                              | デバイス上の全回路に対するグラウンド・リファレンス・ポイント。                                                    |

| 8     | CS                               | アクティブ・ローのチップ・セレクト入力。WRと組み合わせて、パラレル・インターフェースへのデータの書き込みに使用します。                       |

| 9     | WR                               | アクティブ・ローの書き込み入力。CSと組み合わせて、パラレル・インターフェースへのデータの書き込みに使用します。                           |

| 10    | A0                               | 書き込みを行うDACを選択するLSBアドレス・ピン。                                                         |

| 11    | A1                               | 書き込みを行うDACを選択するMSBアドレス・ピン。                                                         |

| 12    | LDAC                             | DACレジスタを入力レジスタ値で更新するアクティブ・ローのコントロール入力。この信号を使うと、全DAC出力を同時に更新できます。                   |

| 13    | PD                               | パワーダウン・ピン。このアクティブ・ローのコントロール・ピンにより、全DACをパワーダウン・モードにします。                             |

| 14    | V <sub>DD</sub>                  | 電源ピン。これらのデバイスは2.5~5.5Vの電源で動作でき、電源はパラレル接続した10μFと0.1μFのコンデンサによりGNDからデカッピングする必要があります。 |

| 15~22 | DB <sub>0</sub> ~DB <sub>7</sub> | 8本のパラレル・データ入力。DB <sub>7</sub> がこれら8ビットのMSB。                                        |

| 23    | HBEN                             | デバイスに書き込みを行う際に、データを上位バイト・レジスタまたは下位バイト・レジスタのいずれに書き込むかを指定します。                        |

| 24    | CLR                              | すべての入力レジスタとDACレジスタをゼロにクリアするアクティブ・ローの非同期コントロール入力。                                   |

# AD5334/AD5335/AD5336/AD5344

## AD5336 ピン機能説明

| ピン番号    | 記号                                | 機能                                                                                     |

|---------|-----------------------------------|----------------------------------------------------------------------------------------|

| 1       | V <sub>REFD</sub>                 | DAC Dのバッファなしのリファレンス入力。                                                                 |

| 2       | V <sub>REFC</sub>                 | DAC Cのバッファなしのリファレンス入力。                                                                 |

| 3       | V <sub>REFB</sub>                 | DAC Bのバッファなしのリファレンス入力。                                                                 |

| 4       | V <sub>REFA</sub>                 | DAC Aのバッファなしのリファレンス入力。                                                                 |

| 5       | V <sub>OUTA</sub>                 | DAC A出力。レールtoレール動作が可能なバッファ付き出力。                                                        |

| 6       | V <sub>OUTB</sub>                 | DAC B出力。レールtoレール動作が可能なバッファ付き出力。                                                        |

| 7       | V <sub>OUTC</sub>                 | DAC C出力。レールtoレール動作が可能なバッファ付き出力。                                                        |

| 8       | V <sub>OUTD</sub>                 | DAC D出力。レールtoレール動作が可能なバッファ付き出力。                                                        |

| 9       | GND                               | デバイス上の全回路に対するグラウンド・リファレンス・ポイント。                                                        |

| 10      | CS                                | アクティブ・ローのチップ・セレクト入力。WRと組み合わせて、パラレル・インターフェースへのデータの書き込みに使用します。                           |

| 11      | WR                                | アクティブ・ローの書き込み入力。CSと組み合わせて、パラレル・インターフェースへのデータの書き込みに使用します。                               |

| 12      | A0                                | 書き込みを行うDACを選択するLSBアドレス・ピン。                                                             |

| 13      | A1                                | 書き込みを行うDACを選択するMSBアドレス・ピン。                                                             |

| 14      | LDAC                              | DACレジスタを入力レジスタ値で更新するアクティブ・ローのコントロール入力。<br>この信号を使うと、全DAC出力を同時に更新できます。                   |

| 15      | PD                                | パワーダウン・ピン。このアクティブ・ローのコントロール・ピンにより、全DACをパワーダウン・モードにします。                                 |

| 16      | V <sub>DD</sub>                   | 電源ピン。これらのデバイスは2.5 ~ 5.5Vの電源で動作でき、電源はパラレル接続した10 μFと0.1 μFのコンデンサによりGNDからデカッピングする必要があります。 |

| 17 ~ 26 | DB <sub>0</sub> ~ DB <sub>9</sub> | 10本のパラレル・データ入力。DB <sub>9</sub> がこれら10ビットのMSB。                                          |

| 27      | GAIN                              | ゲイン・コントロール・ピン。DAC出力範囲0 ~ V <sub>REF</sub> または0 ~ 2 × V <sub>REF</sub> を選択します。          |

| 28      | CLR                               | すべての入力レジスタとDACレジスタをゼロにクリアするアクティブ・ローの非同期コントロール入力。                                       |

# AD5334/AD5335/AD5336/AD5344

## AD5344 ピン機能説明

| ピン番号  | 記号                                | 機能                                                                                  |

|-------|-----------------------------------|-------------------------------------------------------------------------------------|

| 1     | V <sub>REFD</sub>                 | DAC Dのバッファなしのリファレンス入力。                                                              |

| 2     | V <sub>REFC</sub>                 | DAC Cのバッファなしのリファレンス入力。                                                              |

| 3     | V <sub>REFB</sub>                 | DAC Bのバッファなしのリファレンス入力。                                                              |

| 4     | V <sub>REFA</sub>                 | DAC Aのバッファなしのリファレンス入力。                                                              |

| 5     | V <sub>OUTA</sub>                 | DAC A出力。レールtoレール動作が可能なバッファ付き出力。                                                     |

| 6     | V <sub>OUTB</sub>                 | DAC B出力。レールtoレール動作が可能なバッファ付き出力。                                                     |

| 7     | V <sub>OUTC</sub>                 | DAC C出力。レールtoレール動作が可能なバッファ付き出力。                                                     |

| 8     | V <sub>OUTD</sub>                 | DAC D出力。レールtoレール動作が可能なバッファ付き出力。                                                     |

| 9     | GND                               | デバイス上の全回路に対するグラウンド・リファレンス・ポイント。                                                     |

| 10    | CS                                | アクティブ・ローのチップ・セレクト入力。WRと組み合わせて、パラレル・インターフェースへのデータの書き込みに使用します。                        |

| 11    | WR                                | アクティブ・ローの書き込み入力。CSと組み合わせて、パラレル・インターフェースへのデータの書き込みに使用します。                            |

| 12    | A0                                | 書き込みを行うDACを選択するLSBアドレス・ピン。                                                          |

| 13    | A1                                | 書き込みを行うDACを選択するMSBアドレス・ピン。                                                          |

| 14    | LDAC                              | DACレジスタを入力レジスタ値で更新するアクティブ・ローのコントロール入力。この信号を使うと、全DAC出力を同時に更新できます。                    |

| 15    | PD                                | パワーダウン・ピン。このアクティブ・ローのコントロール・ピンにより、全DACをパワーダウン・モードにします。                              |

| 16    | V <sub>DD</sub>                   | 電源ピン。これらのデバイスは2.5~5.5Vの電源で動作でき、電源はパラレル接続した10μFと0.1μFのコンデンサによりGNDからデカップリングする必要があります。 |

| 17~28 | DB <sub>0</sub> ~DB <sub>11</sub> | 12本のパラレル・データ入力。DB <sub>11</sub> がこれら12ビットのMSB。                                      |

## 用語集

### 相対精度

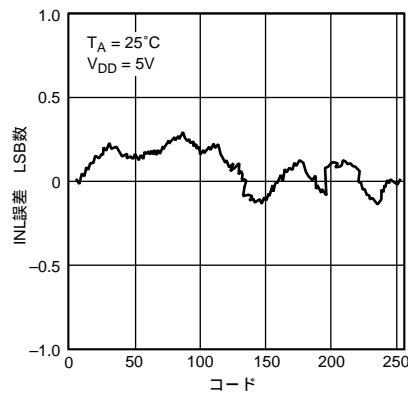

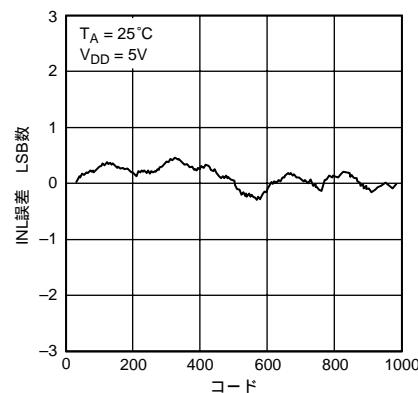

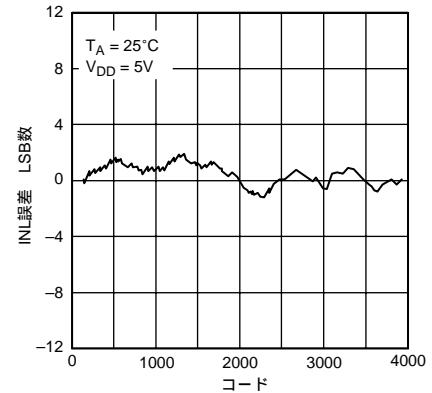

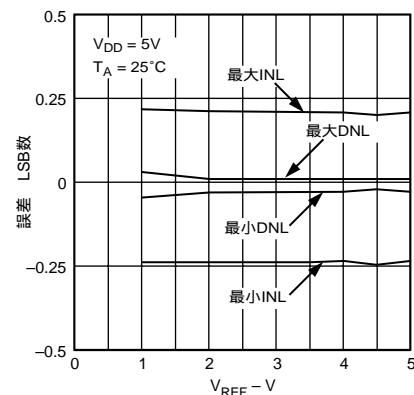

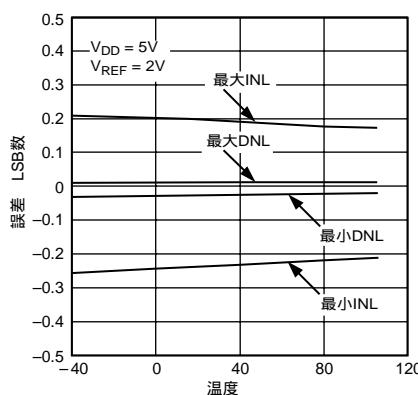

DACの場合、相対精度すなわち積分非直線性 (INL) は、DAC伝達関数の上下両端を結ぶ直線からの最大偏差 ( LSB 数で表示 ) を表します。図5~7は、代表的なINLとコードとの関係を表しています。

### 微分非直線性

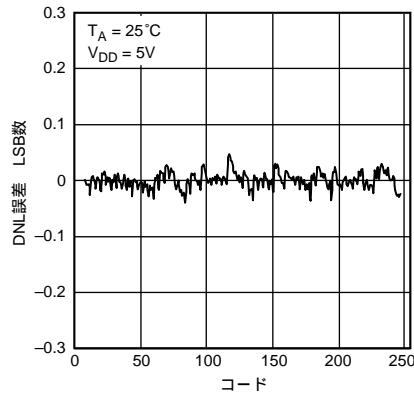

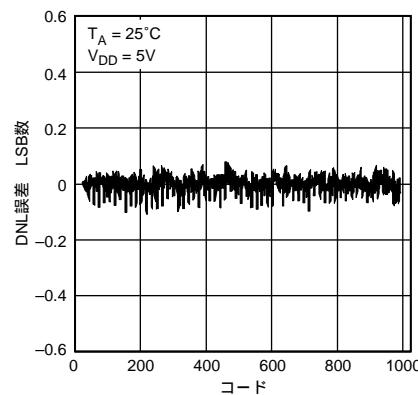

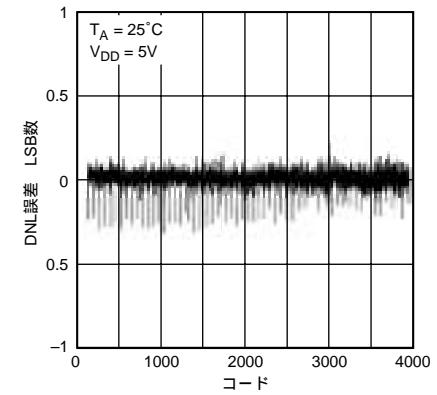

微分非直線性 (DNL) は、隣接する2つのコードの間における実測された変化と理論的な1 LSB変化との差をいいます。最大  $\pm 1$  LSBの微分非直線性の仕様は、単調性を保証するものです。このDACは設計により単調性を保証しています。図8~10は、代表的なDNLとコードとの関係を表しています。

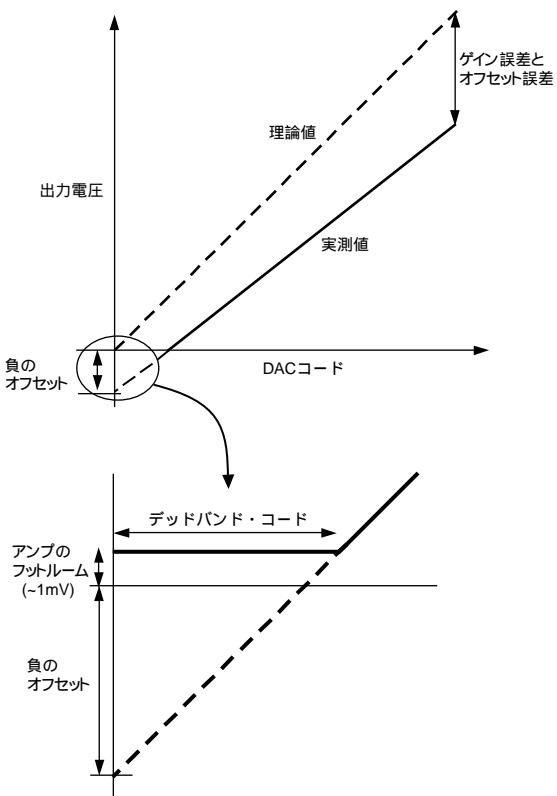

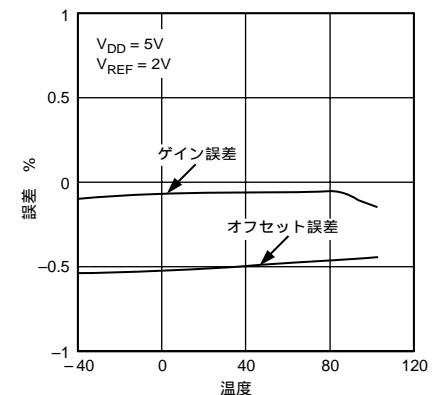

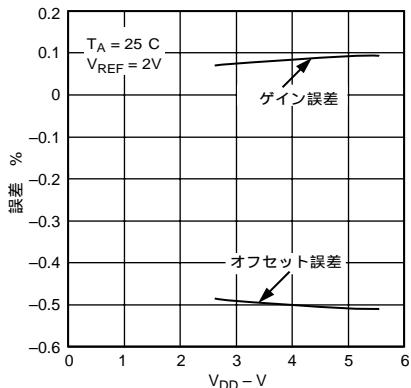

### オフセット誤差

DACと出力アンプのオフセット誤差を表します。フルスケール範囲のパーセント値で表示します。オフセット電圧が正の場合は、出力電圧もゼロ入力コードに対して正になります。図3にこの様子を示します。DACは单電源で動作するため、負のオフセットがバッファ・アンプ出力に現われることはありません。その代わり、アンプ出力が飽和するゼロ付近のコードが存在します (アンプのフットルーム)。このコードの下には、出力電圧が変化しないデッドバンドが存在します。この様子を図4に示します。

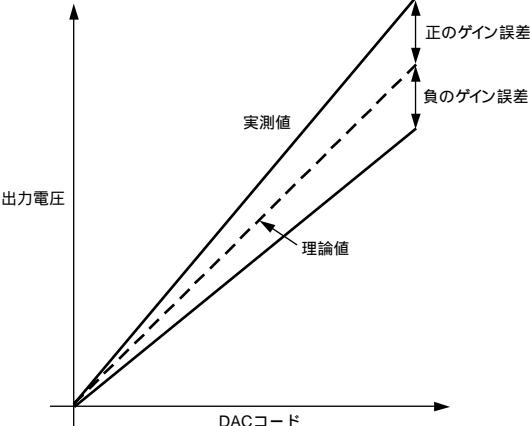

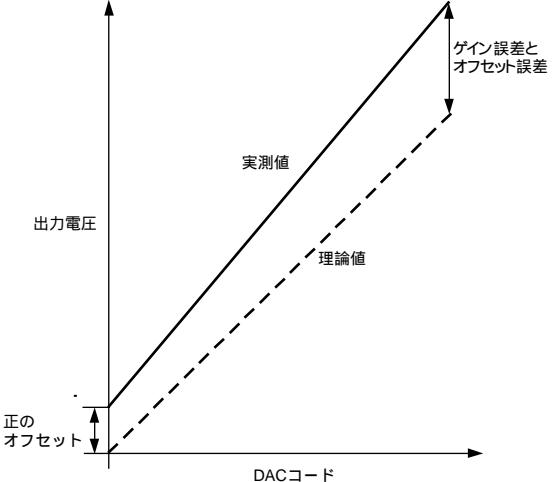

### ゲイン誤差

DACのスパン誤差を表します (バッファ・アンプのすべてのゲイン誤差を含みます)。理論値からの実際のDAC伝達特性の傾きの差をフルスケール範囲のパーセント値で表したものです。図2に説明図を示します。

図2 ゲイン誤差

図3 正のオフセット誤差とゲイン誤差

図4 負のオフセット誤差とゲイン誤差

# AD5334/AD5335/AD5336/AD5344

## オフセット誤差ドリフト

オフセット誤差の温度変化を表します。(フルスケール範囲のppm) / で表示します。

## ゲイン誤差ドリフト

ゲイン誤差の温度変化を表します。(フルスケール範囲のppm) / で表示します。

## DC電源変動除去比 (PSRR)

電源電圧変化のDAC出力に対する影響を表します。PSRRは、 $V_{OUT}$ 変化のDACフルスケール出力の $V_{DD}$ 変化に対する比です。dB値で表示します。 $V_{REF}$ を2Vに固定して、 $V_{DD}$ を±10%変化させます。

## DCクロストーク

フルスケール・コード変化(全ビット“0”から全ビット“1”への変化、およびその逆変化)に対する応答としての、1つのDACのミッドスケールにおける出力レベルのDC変化と別のDACの出力変化。 $\mu V$ で表示します。

## リファレンス・フィードスルー

DAC出力に変化がない時のDAC出力における信号振幅のリファレンス入力に対する比(すなわち、LDACがハイ)。dB値で表示します。

## チャンネル間アイソレーション

1つのDAC出力における信号振幅と他のDACのリファレンス入力に入力されたサイン波との比。一方の $V_{REF}$ ピンをグラウンドに接続し、他方の $V_{REF}$ ピンに10kHz、4Vp-pのサイン波を入力して測定します。dB値で表示します。

## 主要コード変化時のグリッチ・エネルギー

DACレジスタ内のコードの状態が変化したときに、アナログ出力に注入されるインパルスのエネルギー。通常、nV-secで表すグリッチの面積として規定され、主要なキャリー変化(011...11から100...00へまたは100...00から011...11へ)時に、デジタル・コードが1 LSBだけ変化したときに測定されます。

## デジタル・フィードスルー

DAC出力に書き込みが行われていない( $\overline{CS}$ がハイ)ときの、デバイスのデジタル入力ピンからDACのアナログ出力に注入されるインパルスを表します。nV-secで規定され、デジタル入力ピンでのワーストケース変化、例えば全ビット“0”から全ビット“1”への変化、またはその逆の変化のときに測定されます。

## デジタル・クロストーク

1のDACの入力レジスタにおけるフルスケール・コード変化(全ビット“0”から全ビット“1”への変化、およびその逆変化)から、ミッドスケール・レベルにある別のDACの出力に混入したグリッチ・インパルス。nV-secで表示します。

## アナログ・クロストーク

あるDACの出力変化に起因して、別のDAC出力に混入するグリッチ・インパルス。LDACピンがハイの間に、入力レジスタの1つにフルスケール・コード変化(全ビット“0”から全ビット“1”への変化、およびその逆変化)をロードします。その後で、LDACにロー・パルスを入力して、デジタル・コードが変化しないDACの出力をモニターします。グリッチの面積はnV-secで表示します。

## DAC間クロストーク

デジタル・コードの変化とそれに続くあるDACの出力変化に起因して、別のDAC出力に混入するグリッチ・インパルス。これには、デジタル・クロストークとアナログ・クロストークの両方が含まれます。LDACピンをロー・に設定して、DACの1つにフルスケール・コード変化(全ビット“0”から全ビット“1”への変化、およびその逆変化)をロードして、別のDAC出力をモニターして測定します。グリッチの電力はnV-secで表示します。

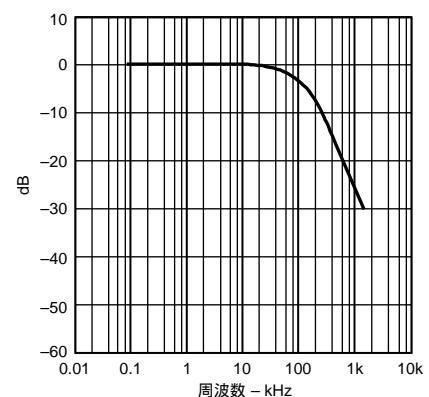

## マルチプル帯域幅

DAC内のアンプは有限な帯域幅を持っています。マルチプル帯域幅はこれを表します。入力された基準サイン波(DACにフルスケール・コードをロード)は、出力に現われます。マルチプル帯域幅は、出力振幅が入力より3dB小さくなる周波数で表します。

## 合計高調波歪み (THD)

理論サイン波とDACを使ったために減衰したそのサイン波との差。DACに対して基準としてサイン波を使ったときに、DAC出力に現われる高調波がTHDになります。dB値で表示します。

# 代表的な性能特性 AD5334/AD5335/AD5336/AD5344

図5 AD5334の代表的なINLプロット

図6 AD5335の代表的なINLプロット

図7 AD5336の代表的なINLプロット

図8 AD5334の代表的なDNLプロット

図9 AD5335の代表的なDNLプロット

図10 AD5336の代表的なDNLプロット

図11 AD5334のINL誤差およびDNL誤差対  $V_{REF} - V$

図12 AD5334のINL誤差およびDNL誤差対 温度

図13 AD5334のオフセット誤差およびゲイン誤差対 温度

# AD5334/AD5335/AD5336/AD5344

図14 オフセット誤差および

ゲイン誤差対  $V_{DD}$

図15  $V_{OUT}$ の電流ソース / シンク能力

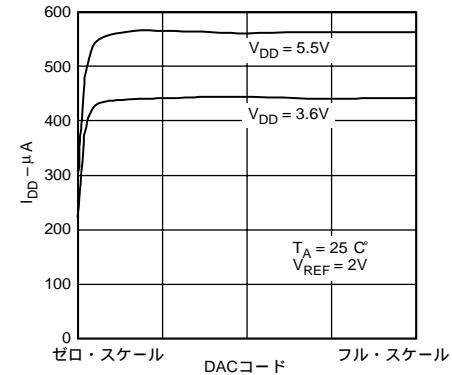

図16 供給電流対 DACコード

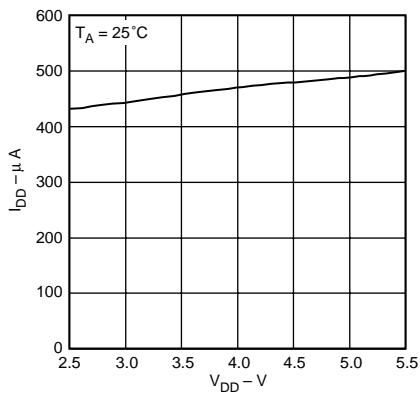

図17 供給電流対電源電圧

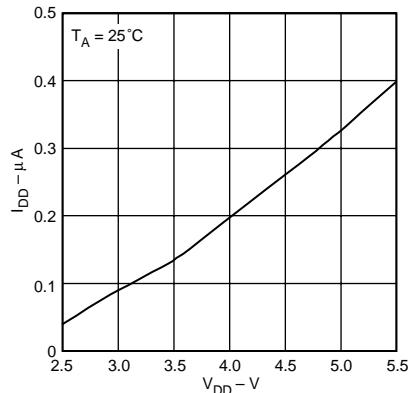

図18 パワーダウン電流対電源電圧

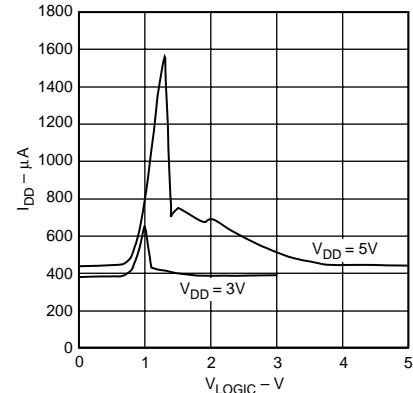

図19 電源電流対ロジック入力電圧

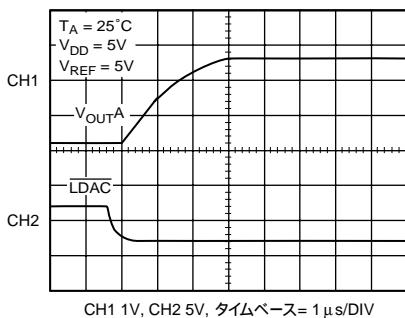

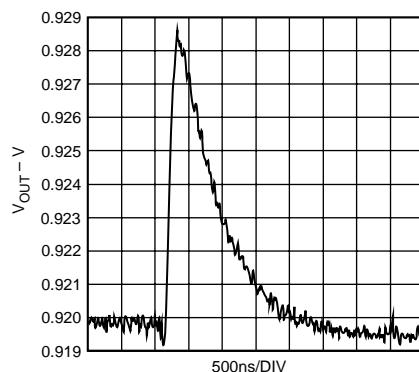

図20 1/2スケール設定 (1/4~3/4

スケールへのコード変化)

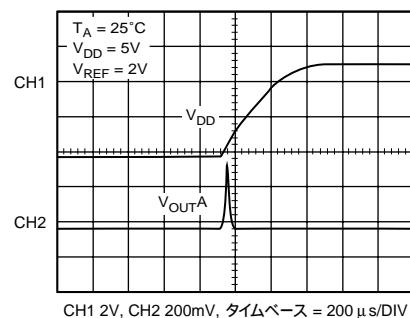

図21 パワーオン・リセット時の

0V出力

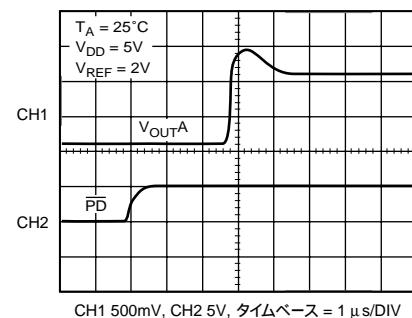

図22 パワーダウン終了時の

ミッドスケール出力

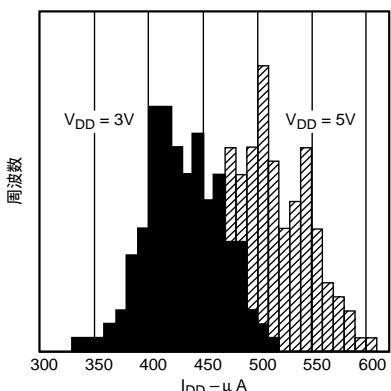

図23  $V_{DD} = 3V$  および  $V_{DD} = 5V$  での  $I_{DD}$  ヒストグラム

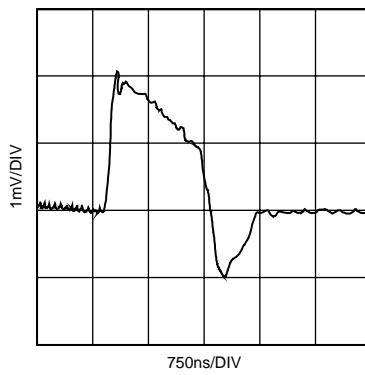

図24 AD5344の主要コード変化時のグリッヂ電力

図25 マルチプル帯域幅(小信号周波数応答)

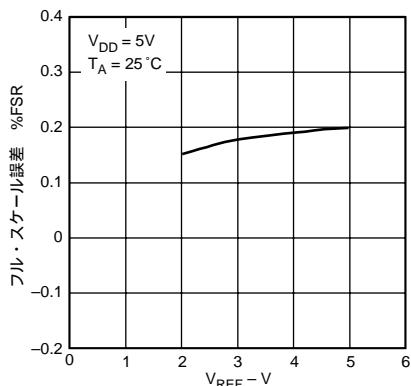

図26 フルスケール誤差 対  $V_{REF}$

図27 DAC間クロストーク

## 機能説明

AD5334 (8ビット) AD5335 (10ビット) AD5336 (10ビット) AD5344 (12ビット) は、CMOSプロセスで製造された抵抗ストリング型クワッドDACです。パラレル・インターフェースを使って書き込みを行い、2.5~5.5V単電源で動作し、出力バッファ・アンプはレールtoレールの出力振幅を提供します。AD5334/AD5336に内蔵のバッファアンプのゲインを1または2に設定して、0~ $V_{REF}$ または0~ $2 \times V_{REF}$ の出力電圧範囲が得られます。AD5335/AD5344はゲイン1の出力バッファを内蔵しています。

これらのデバイスは、消費電流を3Vで80nAまで減少させるパワーダウン機能を持っています。

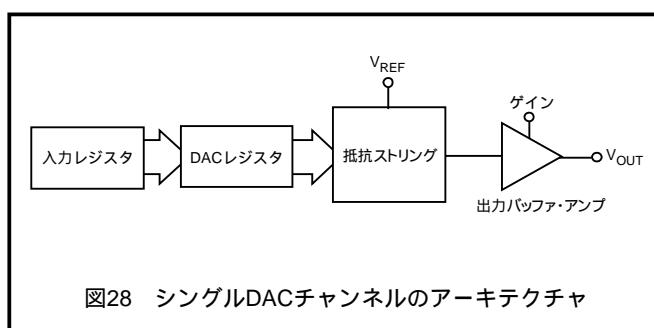

## D/Aコンバータ部

DACチャンネルのアーキテクチャは、リファレンス・バッファと抵抗ストリング型DAC、およびそれに続く出力バッファ・アンプから構成されています。 $V_{REF}$ ピンの電圧は、DACに対するリファレンスを提供します。図28に、DACアーキテクチャのブロック図を示します。DACへの入力コードは自然2進を使っているため、理論出力電圧は次式で得られます。

$$V_{OUT} = V_{REF} \times \frac{D}{2^N} \times \text{Gain}$$

ここで、

D = DACレジスタにロードされるバイナリ・コードの10進数表示。

AD5334 (8ビット) の場合0~255

AD5335/AD5336 (10ビット) の場合0~1023

AD5344 (12ビット) の場合0~4095

N = DACの分解能

GAIN = 出力アンプ・GAIN (1または2)

図28 シングルDACチャンネルのアーキテクチャ

# AD5334/AD5335/AD5336/AD5344

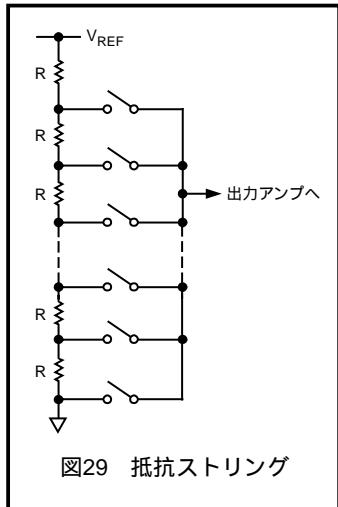

## 抵抗ストリング

図29に、抵抗ストリング部分を示します。各値がRのシンプルな抵抗のストリングになっているため、DACレジスタにロードされるデジタル・コードにより、出力アンプに供給する電圧を取り出すストリング上のノードが決定されます。スイッチの内の1つが閉じてストリングがアンプに接続されて、電圧が取り出されます。抵抗のストリングであるため、単調性が保証されます。

図29 抵抗ストリング

## DACのリファレンス入力

DACは、外部リファレンスを使用して動作します。リファレンス入力にはバッファがなく、入力範囲は0.25V ~ V<sub>DD</sub>です。各DACのインピーダンスは、0 ~ V<sub>REF</sub>モードの場合180k (typ) で、0 ~ 2 × V<sub>REF</sub>モードの場合90k と、大きな値を維持しています。AD5336/AD5344は各DACに対して個別にリファレンス入力を持っていますが、AD5334/AD5335はDACの各対(A/BとC/D)に対してリファレンス入力を持っています。

## 出力アンプ

出力バッファアンプは、両レールの内側1mVまでの出力電圧を発生できます。実際の範囲は、V<sub>REF</sub>、ゲイン、V<sub>OUT</sub>上の負荷、オフセット誤差に依存します。

ゲイン1を選択した場合(GAIN = 0) 出力範囲は0.001V ~ V<sub>REF</sub>になります。

ゲイン2を選択した場合(GAIN = 1) 出力範囲は0.001V ~ 2V<sub>REF</sub>になります。ただし、クランプのため、最大出力はV<sub>DD</sub> - 0.001Vに制限されます。

この出力アンプは、GNDまたはV<sub>DD</sub>に接続された2k と、これに並列接続された500pFの負荷を駆動できます。図15に、出力アンプのソース能力とシンク能力を示します。

スルーレートは0.7V/μsであり、±0.5LSBへのハーフスケール・セッティング・タイム(8ビット)は、出力無負荷で6μsです。図20を参照してください。

## パラレル・インターフェース

AD5334/AD5336/AD5344では、8ビット・ワード、10ビット・ワード、または12ビット・ワード単位としてデータをロードしますが、AD5335では8ビットの下位バイトと2ビットの上位バイトとしてデータをロードします。

## ダブルバッファ化された入力ロジック

AD5334/AD5335/AD5336/AD5344 DACはすべて、入力レジスタとDACレジスタで構成されるダブル・バッファ化されたインターフェースを持っています。DACデータとGAINの各入力(存在する場合)は、チップ・セレクト(CS)と書き込み(WR)ピンの制御のもとで入力レジスタに書き込まれます。

DACレジスタに対するアクセスは、LDAC機能により制御されます。LDACビットがハイに設定されると、DACレジスタがラッチされるため、DACレジスタの内容に影響を与えずに入力レジスタの状態を

変えられます。ただし、LDACがローになると、DACレジスタはトランスペアレントになり、入力レジスタの値がこのレジスタに転送されます。ゲイン・コントロール信号もダブル・バッファ化されており、LDACがローのときのみ更新されます。

この機能は、すべてのDAC出力とペリフェラルの同時更新が必要な場合には便利です。

すべての入力レジスタに個別に書き込んだ後、LDAC入力にロー・パルスを入力して、全出力を同時に更新します。

ダブル・バッファを使うと全データ・ワードを並列に組み立てた後に、DACレジスタを更新できるため、AD5335のようにDACデータが2バイトでロードされる場合にも便利です。また、DACレジスタが上位バイトまたは下位バイトのみで更新された場合の擬似出力を防止することもできます。

これらのデバイスには、追加機能があります。この機能を使うと、LDACがローになった後に入力レジスタの更新が済んでいない場合、これが済むまでDACレジスタの更新を行わないようにできます。通常、LDACがローになると、DACレジスタには入力レジスタの値がロードされます。AD5334/AD5335/AD5336/AD5344の場合、直前のDACレジスタの更新が行われた後でも、入力レジスタの更新が済んでいないれば、DACレジスタの更新は行いません。この機能により不要なクロストークを防げます。

## クリア入力 (CLR)

CLRはアクティブ・ローの非同期クリアであり、入力レジスタとDACレジスタをリセットします。AD5344にはCLR機能がないことに注意してください。

## チップ・セレクト入力 (CS)

CSはアクティブ・ロー入力であり、デバイスを選択します。

## 書き込み入力 (WR)

WRはアクティブ・ロー入力であり、デバイスに対するデータの書き込みを制御します。データはWRの立ち上がりエッジで入力レジスタにラッチされます。

## ロードDAC入力 (LDAC)

LDACは、入力レジスタからDACレジスタにデータを転送します(したがって出力が更新されます)。LDAC機能を使うと、DACデータとGAINデータのダブル・バッファ処理が可能になります。次の2つのLDACモードが存在します。

同期モード:このモードでは、WR入力の立ち上がりエッジで新しいデータが読み込まれた後に、DACレジスタが更新されます。LDACはローに固定できます。あるいは図1のようにパルス入力できます。

非同期モード:このモードでは、入力レジスタが書き込まれると同時に出力は更新されません。LDACがローになったときに、DACレジスタは入力レジスタの値で更新されます。

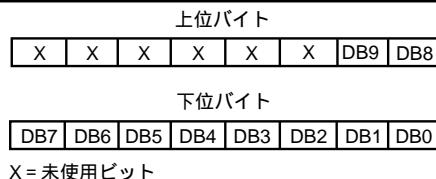

## 上位バイト・イネーブル入力 (HBEN)

上位バイト・イネーブルは、AD5335にのみ存在するコントロール入力であり、上位バイト入力レジスタまたは下位バイト入力レジスタのいずれにデータを書き込むかを指定します。

AD5335の下位データ・バイトはデータ・ビット0 ~ 7(データ入力DB<sub>0</sub> ~ DB<sub>7</sub>)で構成され、上位バイトはデータ・ビット8と9(データ入力DB<sub>8</sub>とDB<sub>9</sub>)で構成されています。上位バイトの書き込み時にはDB<sub>8</sub> ~ DB<sub>9</sub>は無視されます。図30を参照してください。

# AD5334/AD5335/AD5336/AD5344

図30 AD5335のデータ・フォーマット

## パワーオン・リセット

AD5334/AD5335/AD5336/AD5344はパワーオン・リセット機能を内蔵しているため、規定の状態でパワーアップします。

パワーオン状態では、以下の通りになります。

- ・通常動作

- ・出力範囲:  $0 \sim V_{REF}$

- ・出力電圧が0Vに設定。

入力レジスタとDACレジスタにはゼロが設定され、デバイスに有効な書き込みシーケンスが実行されるまでこの状態が維持されます。この機能は、デバイスのパワーアップ時のDAC出力状態が既知である必要のあるアプリケーションで特に便利です。

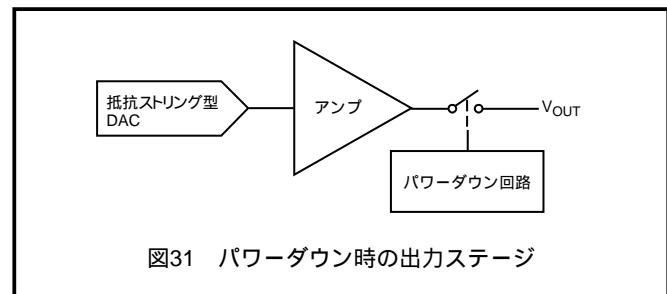

## パワーダウン・モード

AD5334/AD5335/AD5336/AD5344は低消費電力であり、3V電源で1.5mW、5V電源で3mWの低消費電力です。DACをパワーダウン・モードにしてDACを使用しない場合、消費電力をさらに削減できます。 $\overline{PD}$ ピンをローに設定すると、このパワーダウン・モードが選択されます。 $\overline{PD}$ ビットをハイに設定すると、DACは5Vで $600\ \mu A$  (typ) の消費電流で動作します。

作します(3Vでは $500\ \mu A$ )。ただし、パワーダウン・モードでは、DACがパワーダウンすると、供給電流は5Vで $200\ nA$ に減少します(3Vでは $80\ nA$ )。供給電流が減少するだけでなく、出力ステージも内部的にアンプ出力から切り離されてオープンになります。この機能には、デバイスのパワーダウン・モード中に出力がスリーステートになるため、DACアンプ出力に接続されているものに依存せずに一定の入力条件を提供できるというメリットがあります。図31に、出力ステージを示します。

図31 パワーダウン時の出力ステージ

パワーダウン・モードのときは、バイアス・ジェネレータ、出力アンプ、抵抗ストリング、およびその他の関係するすべてのリニア回路はすべてシャットダウンされます。ただし、レジスタの値はパワーダウン・モードで影響を受けることはありません。パワーダウン・モードから抜け出す時間は、 $V_{DD} = 5V$ のときは $2.5\ \mu s$  (typ) で、 $V_{DD} = 3V$ のときは $5\ \mu s$  (typ) です。

この時間は、 $\overline{PD}$ ピンの立ち上がりエッジから、出力電圧がパワーダウン電圧から変化するまでの時間に該当します。図22を参照してください。

表I AD5334/AD5336/AD5344の真理値表

| CLR | LDAC | CS | WR  | A1 | A0 | 機能                                    |

|-----|------|----|-----|----|----|---------------------------------------|

| 1   | 1    | 1  | X   | X  | X  | データ転送なし                               |

| 1   | 1    | X  | 1   | X  | X  | データ転送なし                               |

| 0   | X    | X  | X   | X  | X  | 全レジスタをクリア                             |

| 1   | 1    | 0  | 0 1 | 0  | 0  | DAC A入力レジスタ、GAIN Aをロード(AD5334/AD5336) |

| 1   | 1    | 0  | 0 1 | 0  | 1  | DAC B入力レジスタ、GAIN Bをロード(AD5334/AD5336) |

| 1   | 1    | 0  | 0 1 | 1  | 0  | DAC C入力レジスタ、GAIN Cをロード(AD5334/AD5336) |

| 1   | 1    | 0  | 0 1 | 1  | 1  | DAC D入力レジスタ、GAIN Dをロード(AD5334/AD5336) |

| 1   | 0    | X  | X   | X  | X  | DACレジスタを更新                            |

X = 無視

表II AD5335の真理値表

| CLR | LDAC | CS | WR  | A1 | A0 | HBEN | 機能                   |

|-----|------|----|-----|----|----|------|----------------------|

| 1   | 1    | 1  | X   | X  | X  | X    | データ転送なし              |

| 1   | 1    | X  | 1   | X  | X  | X    | データ転送なし              |

| 0   | X    | X  | X   | X  | X  | X    | 全レジスタをクリア            |

| 1   | 1    | 0  | 0 1 | 0  | 0  | 0    | DAC A下位バイト入力レジスタをロード |

| 1   | 1    | 0  | 0 1 | 0  | 0  | 1    | DAC A上位バイト入力レジスタをロード |

| 1   | 1    | 0  | 0 1 | 0  | 1  | 0    | DAC B下位バイト入力レジスタをロード |

| 1   | 1    | 0  | 0 1 | 0  | 1  | 1    | DAC B上位バイト入力レジスタをロード |

| 1   | 1    | 0  | 0 1 | 1  | 0  | 0    | DAC C下位バイト入力レジスタをロード |

| 1   | 1    | 0  | 0 1 | 1  | 0  | 1    | DAC C上位バイト入力レジスタをロード |

| 1   | 1    | 0  | 0 1 | 1  | 1  | 0    | DAC D下位バイト入力レジスタをロード |

| 1   | 1    | 0  | 0 1 | 1  | 1  | 1    | DAC D上位バイト入力レジスタをロード |

| 1   | 0    | X  | X   | X  | X  | X    | DACレジスタを更新           |

X = 無視

# AD5334/AD5335/AD5336/AD5344

## 推奨データ・バス・フォーマット

多くのアプリケーションでは、AD5334/AD5336のGAIN入力はハード・ワイヤ接続で固定されていますが、さらに柔軟性が必要な場合には、これらをデータ・バスに含めることができます。こうすることにより、GAINがソフトウェアから設定でき、DACの下側半分の範囲での分解能を倍にするオプションを用意できます。バス化したシステムでは、GAINは書き込み動作中にデバイスに書き込みを行い、LDACをローにしてそれを有効にできるため、データ入力として扱えます。これは、複数のDACデバイス内の出力アンプ・ゲインを共通のGAINラインを使って制御できることを意味します。

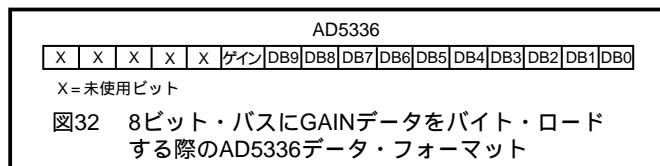

AD5336のデータ・バスは、少なくとも10ビット幅である必要があり、16ビットのデータ・バス・システムに適しています。

GAINを16ビット・データ・バスに出力する際のデータ・フォーマットを図32に示します。実際のDACデータより上の未使用ビットは、GAINに使用できることに注意してください。

## アプリケーション情報

### 代表的なアプリケーション回路

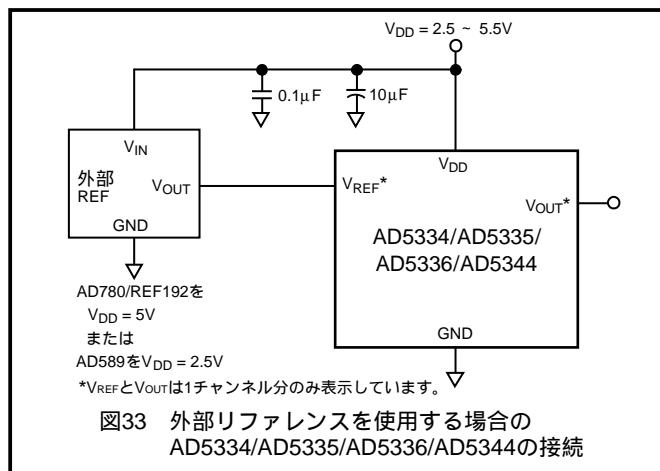

AD5334/AD5335/AD5336/AD5344は、広範囲なリファレンスで使用できます。0.25V ~ V<sub>DD</sub>のリファレンス範囲に対して0.25の整数倍機能を必要とする広範囲なリファレンスで使用できます。一般的には、これらのデバイスは固定の高精度リファレンスと組み合わせて使用できます。図33に、外部リファレンスをリファレンス入力に接続した場合の代表的な接続を示します。5V動作に適するリファレンスは、AD780とREF192( 2.5Vリファレンス )です。2.5V動作に対しては、1.23Vのバンドギャップ・リファレンスを使用する外部リファレンスAD589が適しています。

### V<sub>DD</sub>に対するリファレンスの使用

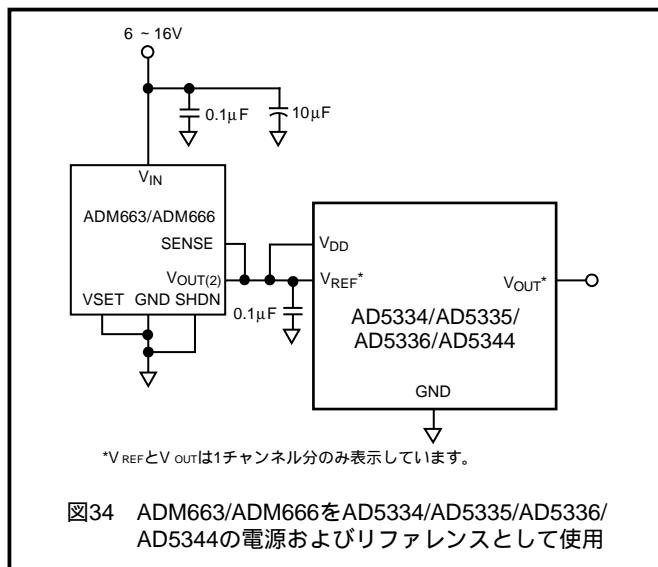

0V ~ V<sub>DD</sub>の出力範囲が必要な場合、最も簡単なソリューションはリファレンス入力をV<sub>DD</sub>に接続することです。この電源は精度が低くノイズが多いので、図34に示すADM663またはADM666のような5Vリファレンスを使ってデバイスに電源を供給することもできます。

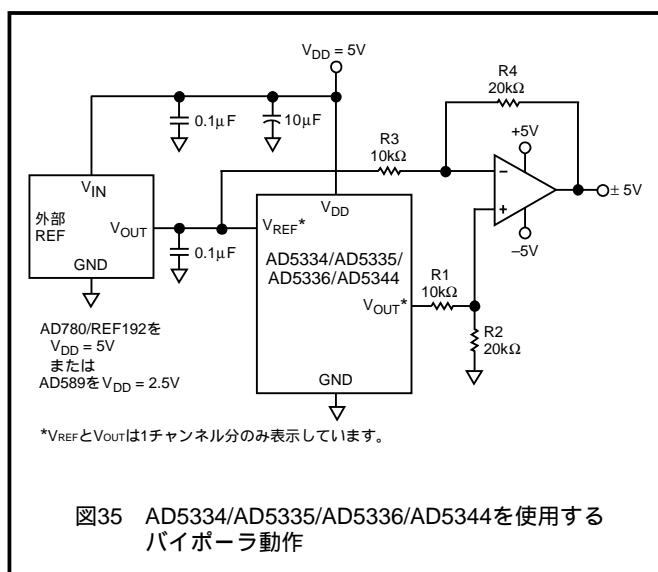

AD5334/AD5335/AD5336/AD5344を使用するバイポーラ動作 AD5334/AD5335/AD5336/AD5344は単電源動作用に設計されていますが、図35に示す回路を使うと、バイポーラ出力範囲も可能です。この回路は -5V < V<sub>o</sub> < +5Vの出力電圧範囲が得られます。出力アンプとしてAD820またはOP295を使用すると、アンプ出力でのレールtoレール動作が可能です。

任意の入力コードに対する出力電圧は次のように計算できます。

$$V_o = [(1 + R4/R3) \times (R2/(R1 + R2) \times (2 \times V_{REF} \times D/2^N))] - R4 \times V_{REF}/R3$$

ここで、

Dは、DACレジスタにロードされるバイナリ・コードの10進数表示。NはDAC分解能で、V<sub>REF</sub>はリファレンス電圧入力にあたり、値は以下の通りです。

$$V_{REF} = 2.5V$$

$$R1 = R3 = 10k$$

$$R2 = R4 = 20k \quad , \quad V_{DD} = 5V$$

$$V_{OUT} = (10 \times D/2^N) - 5$$

## AD5334/AD5335/AD5336/AD5344

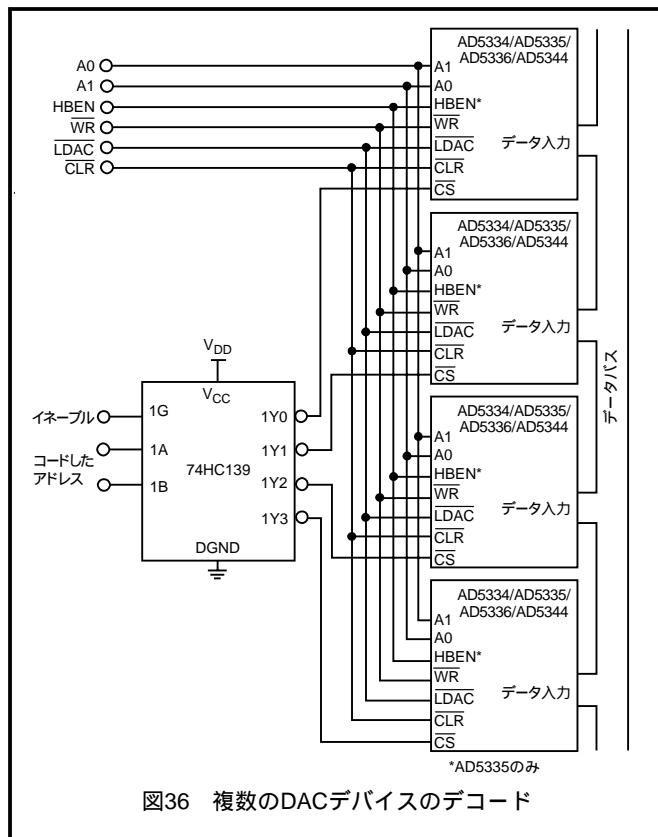

## 複数のAD5334/AD5335/AD5336/AD5344のデコード処理

AD5334/AD5335/AD5336/AD5344の $\overline{CS}$ ピンは、複数のDACをデコードするアプリケーションで使用できます。このアプリケーションでは、システム内のすべてのDACが同じデータと $\overline{WR}$ パルスを受信しますが、複数のDACの内の1つに対する $\overline{CS}$ だけがアクティブにされるため、その $\overline{CS}$ がローになっているDACだけにデータが書き込まれます。複数のAD5343を使用する場合には、選択されたDACの上位バイト・レジスタまたは下位バイト・レジスタのいずれにデータを書き込むかを指定する共通のHBENラインも必要になります。

74HC139は4:2デコーダとして使用されて、システム内のDACの1つをアドレス指定します。タイミング誤差を防止するため、デコードされるアドレス入力の変化中は、イネーブル入力を非アクティブ状態にしておきます。図36に、システム内で複数のデバイスをデコードする代表的な回路を示します。システム内の全DACにデータをシーケンスに沿って書き込んだ後、共通のLDACラインを使って同時に全DACを更新できます。共通のCLRラインは、すべてのDAC出力をゼロにリセットする際にも使うことができます(ただしAD5344は除きます)。

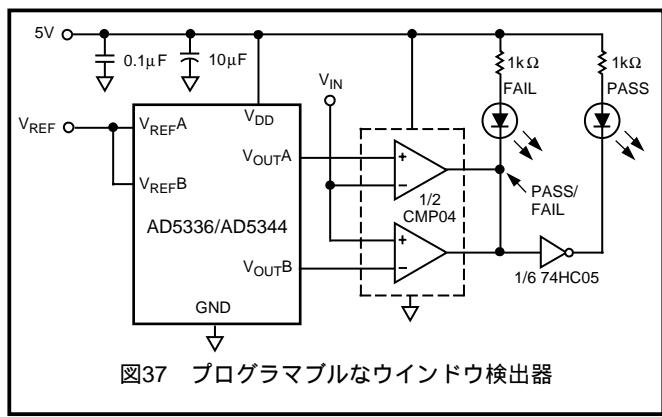

## AD5334/AD5335/AD5336/AD5344をデジタル的にプログラマブルなウインドウ検出器として応用

AD5334/AD5335/AD5336/AD5344内蔵の2個のDACを使用した、デジタル的にプログラマブルな検出器を図37に示します。デバイス内のDACの任意の対を使用できますが、説明を分かり易くするため、ここではDAC AとDAC Bについて説明します。

正しいリファレンス入力をリファレンス源に接続するように注意してください。AD5334/AD5335では、DAC AとDAC Bに対してリファレンス入力  $V_{REF\,A}$ 、B、およびDAC CとDAC Dに対してリファレンス

入力  $V_{REFC}$ 、 $D$  の 2 本しか持ていません。例えば、DACA と DAC B を使用する場合は、 $V_{REFA}$ 、 $B$  が必要です。DAC C と DAC D、および  $V_{REFC}$ 、 $D$  は他の用途に使用できます。AD5336/AD5344 は、各 DAC に対して個別にリファレンス入力を持っています。

テストする上限値と下限値をDACAとDAC Bにロードして、その出力をCMP04に入力します。VIN入力の信号が設定されたウンドウ外にある場合、LEDの点灯によって表示します。

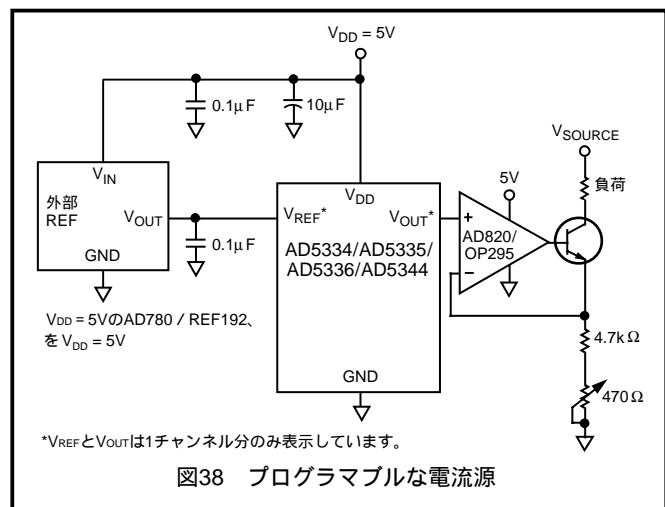

## プログラマブルな電流源

図38に、プログラマブルな電流源の制御要素として使用したAD5334/AD5335/AD5336/AD5344を示します。この例では、フルスケール電流は1mAに設定されています。DAC出力電流は、4.7k $\Omega$ の電流設定抵抗と直列に接続した470 $\Omega$ の調整用ポテンショメータ $\pm 5\%$ の調整が可能を通して出力されます。アンプのフィードバック・ループに使用する適切なトランジスタとしては、BC107や2N3904などがあります。このトランジスタはV<sub>SOURCE</sub>最小6Vからの電流源動作を可能にします。動作範囲はトランジスタの動作特性により決定されます。適するアンプとしてはAD820やOP295などがあり、ともに出力でのレールtoレール動作が可能です。任意の入力コードに対する出力電流値と抵抗値は次のように計算できます。

$$I = G \times V_{REF} \times \frac{D}{(2^N \times R)} \text{ mA}$$

ここで、

GIはバッファアンプのGAIN( 1または2 )

Dはデジタル入力コード

NはDACの分解能(8/10/12ビット)

Rは抵抗と調整用ポテンショメータの合計抵抗値( k<sub>Ω</sub> )

## AD5334/AD5335/AD5336/AD5344

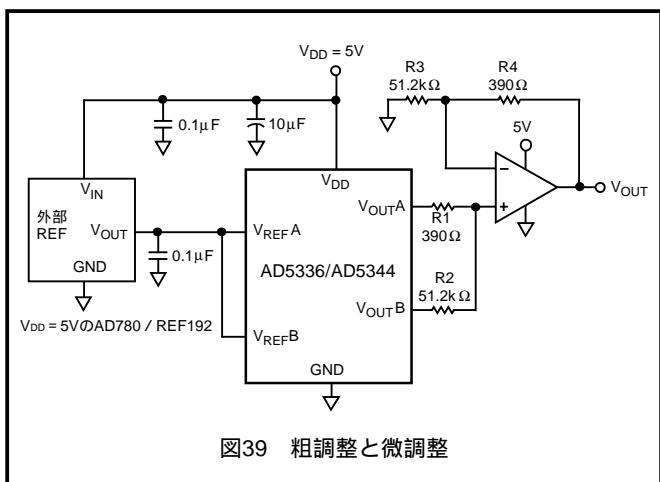

AD5334/AD5335/AD5336/AD5344を使用する粗調整と微調整

AD5334/AD5335/AD5336/AD5344に内蔵されている2個の

DACの対を使用して、粗調整と微調整の機能が実現できま

す（図39）。前述のウインドウ検出器の場合と同様に、DAC

AとDAC Bの例で説明します。リファレンスの接続は使用す

る実際のデバイスに依存します。

DACAは粗調整に、DAC Bは微調整に、それぞれ使用します。R1とR2の比を変えると、粗調整と微調整の相対的效果が変わります。図示した抵抗値を使用すると、DAC A出力に対して出力アンプはゲイン1を持ち、出力範囲は0~( $V_{REF} - 1LSB$ )になります。

DAC Bに対しては、アンプはゲイン $7.6 \times 10^{-3}$ を持ち、DACAの2 LSBに等しい範囲をDAC Bに与えます。

この回路では2.5Vのリファレンスを使用していますが、最大VDDまでのリファレンスを使えます。表示したオペアンプはレールtoレールの出力振幅を可能にします。

## 電源のバイパスとグラウンド接続

精度が重要な回路では、電源とグラウンド・リターンのレイアウトを注意深く行うと、定格性能の保証に役立ちます。AD5334/AD5335/AD5336/AD5344を実装するプリント回路ボードは、アナログ部とデジタル部を分離して、ボードの一定領域にまとめて配置するように設計してください。複数のデバイスがAGNDとDGNDの接続を必要とするシステム内でデバイスを使用する場合は、この接続は1カ所で行う必要があります。デバイスのできるだけ近くに星型のグラウンド・ポイントを構成する必要があります。AD5334/AD5335/AD5336/AD5344に対しては、 $10\text{ }\mu\text{F}$ と $0.1\text{ }\mu\text{F}$ のコンデンサをパラレル接続し、十分な電源バイパスをパッケージのできるだけ近くの電源に、理想的にはデバイスのすぐ隣に接続する必要があります。 $10\text{ }\mu\text{F}$ コンデンサはタンタルのビーズ型を使います。 $0.1\text{ }\mu\text{F}$ コンデンサは、高周波でグラウンドに対する低インピーダンス・パスを提供するセラミック型など、実効直列抵抗（ESR）が小さく、かつ実効直列インダクタンス（ESI）が小さいものを使って、内部ロジックの切替による過渡電流を処理する必要があります。

デバイスの電源ラインには、できるだけ太いパターンを使って低インピーダンス・パスを実現して、電源ライン上のグリッチの効果を抑えてください。クロックなどの高速スイッチング信号はデジタル・グラウンドでシールドして、ボード上の他の部品へノイズを放出しないようにし、リファレンス入力の近くを通らないようにします。デジタル信号とアナログ信号の交差は回避する必要があります。ボードの反対側のパターンは、互いに右角度となるように配置します。これにより、ボードを通過するフィードスルーの効果を削減できます。マイクロストリップ技術の使用は最善ですが、両面ボードでは常に使用できるとは限りません。この技術では、ボードの部品面をグラウンド・プレーン専用にし、信号パターンはハンダ面に配置されます。

# AD5334/AD5335/AD5336/AD5344

表III AD53xxパラレル・デバイスの一覧

| 製品番号   | 分解能 | DNL   | V <sub>REF</sub> ピン数 | セトリング・タイム | 追加ピン機能 |      |      |     | パッケージ | ピン数 |

|--------|-----|-------|----------------------|-----------|--------|------|------|-----|-------|-----|

| シングル   |     |       |                      |           | BUF    | GAIN | HBEN | CLR |       |     |

| AD5330 | 8   | ±0.25 | 1                    | 6μs       | ✓      | ✓    |      | ✓   | TSSOP | 20  |

| AD5331 | 10  | ±0.5  | 1                    | 7μs       |        | ✓    |      | ✓   | TSSOP | 20  |

| AD5340 | 12  | ±1.0  | 1                    | 8μs       | ✓      | ✓    |      | ✓   | TSSOP | 24  |

| AD5341 | 12  | ±1.0  | 1                    | 8μs       | ✓      | ✓    | ✓    | ✓   | TSSOP | 20  |

| デュアル   |     |       |                      |           |        |      |      | ✓   |       |     |

| AD5332 | 8   | ±0.25 | 2                    | 6μs       |        | ✓    |      |     | TSSOP | 20  |

| AD5333 | 10  | ±0.5  | 2                    | 7μs       | ✓      | ✓    |      | ✓   | TSSOP | 24  |

| AD5342 | 12  | ±1.0  | 2                    | 8μs       |        | ✓    |      | ✓   | TSSOP | 28  |

| AD5343 | 12  | ±1.0  | 1                    | 8μs       |        |      | ✓    | ✓   | TSSOP | 20  |

| クワッド   |     |       |                      |           |        |      |      |     |       |     |

| AD5334 | 8   | ±0.25 | 2                    | 6μs       |        | ✓    |      | ✓   | TSSOP | 24  |

| AD5335 | 10  | ±0.5  | 2                    | 7μs       |        | ✓    |      | ✓   | TSSOP | 24  |

| AD5336 | 10  | ±0.5  | 4                    | 7μs       |        | ✓    |      | ✓   | TSSOP | 28  |

| AD5344 | 12  | ±1.0  | 4                    | 8μs       |        |      |      |     | TSSOP | 28  |

表IV AD53xxシリアル・デバイスの一覧

| 製品番号   | 分解能 | DAC数 | DNL   | インターフェース | セトリング・タイム | パッケージ         | ピン数 |

|--------|-----|------|-------|----------|-----------|---------------|-----|

| シングル   |     |      |       |          |           |               |     |

| AD5300 | 8   | 1    | ±0.25 | SPI      | 4μs       | SOT-23, μSOIC | 6,8 |

| AD5310 | 10  | 1    | ±0.5  | SPI      | 6μs       | SOT-23, μSOIC | 6,8 |

| AD5320 | 12  | 1    | ±1.0  | SPI      | 8μs       | SOT-23, μSOIC | 6,8 |

| AD5301 | 8   | 1    | ±0.25 | 2線式      | 6μs       | SOT-23, μSOIC | 6,8 |

| AD5311 | 10  | 1    | ±0.5  | 2線式      | 7μs       | SOT-23, μSOIC | 6,8 |

| AD5321 | 12  | 1    | ±1.0  | 2線式      | 8μs       | SOT-23, μSOIC | 6,8 |

| デュアル   |     |      |       |          |           |               |     |

| AD5302 | 8   | 2    | ±0.25 | SPI      | 6μs       | μSOIC         | 8   |

| AD5312 | 10  | 2    | ±0.5  | SPI      | 7μs       | μSOIC         | 8   |

| AD5322 | 12  | 2    | ±1.0  | SPI      | 8μs       | μSOIC         | 8   |

| AD5303 | 8   | 2    | ±0.25 | SPI      | 6μs       | TSSOP         | 16  |

| AD5313 | 10  | 2    | ±0.5  | SPI      | 7μs       | TSSOP         | 16  |

| AD5323 | 12  | 2    | ±1.0  | SPI      | 8μs       | TSSOP         | 16  |

| クワッド   |     |      |       |          |           |               |     |

| AD5304 | 8   | 4    | ±0.25 | SPI      | 6μs       | μSOIC         | 10  |

| AD5314 | 10  | 4    | ±0.5  | SPI      | 7μs       | μSOIC         | 10  |

| AD5324 | 12  | 4    | ±1.0  | SPI      | 8μs       | μSOIC         | 10  |

| AD5305 | 8   | 4    | ±0.25 | 2線式      | 6μs       | μSOIC         | 10  |

| AD5315 | 10  | 4    | ±0.5  | 2線式      | 7μs       | μSOIC         | 10  |

| AD5325 | 12  | 4    | ±1.0  | 2線式      | 8μs       | μSOIC         | 10  |

| AD5306 | 8   | 4    | ±0.25 | 2線式      | 6μs       | TSSOP         | 16  |

| AD5316 | 10  | 4    | ±0.5  | 2線式      | 7μs       | TSSOP         | 16  |

| AD5326 | 12  | 4    | ±1.0  | 2線式      | 8μs       | TSSOP         | 16  |

| AD5307 | 8   | 4    | ±0.25 | SPI      | 6μs       | TSSOP         | 16  |

| AD5317 | 10  | 4    | ±0.5  | SPI      | 7μs       | TSSOP         | 16  |

| AD5327 | 12  | 4    | ±1.0  | SPI      | 8μs       | TSSOP         | 16  |

当社webサイト、[http://www.analog.com/support/standard\\_linear/selection\\_guides/AD53xx.html](http://www.analog.com/support/standard_linear/selection_guides/AD53xx.html)を参照してください。

## AD5334/AD5335/AD5336/AD5344

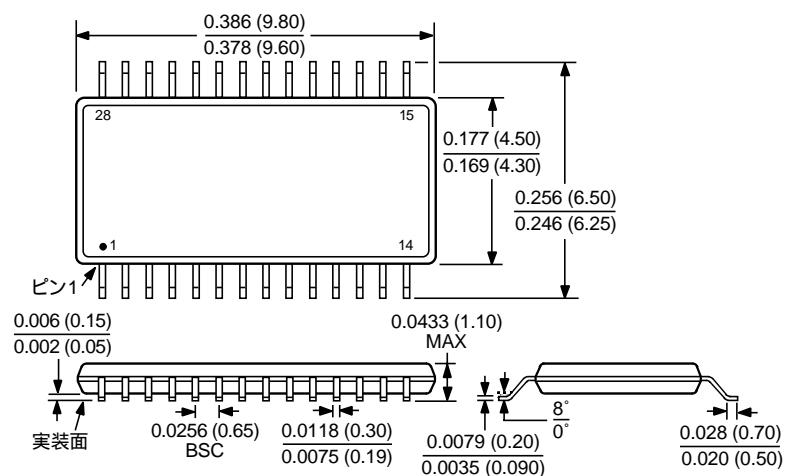

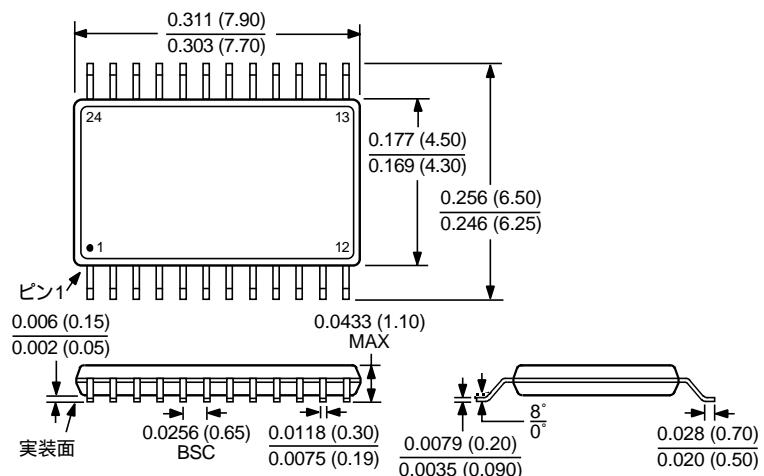

## 外形寸法

サイズはインチと ( mm ) で示します。

## 24ピン薄型シュリンク・スモール・アウトライン・パッケージTSSOP (RU-24)

## 28ピン薄型シュリンク・スマール・アウトライン・パッケージTSSOP (RU-28)