## 特長

256ポジション、4チャンネル

エンド・ツー・エンドの抵抗値20kΩ、50kΩ、200kΩ

ピン選択可能なSPI<sup>®</sup>またはI<sup>2</sup>C<sup>®</sup>互換のインターフェース

ミッドスケールへのパワーオン・プリセット

2本のパッケージ・アドレス・デコード・ピンAD0とAD1

可変抵抗器モード温度係数30ppm/°C

分圧器温度係数5ppm/°C

広い動作温度範囲-40～+125°C

5～15V単電源、±5V両電源

## アプリケーション

機械式ポテンショメータの置き換え

光ネットワークの調整

計装：ゲイン／オフセットの調整

ステレオ・チャンネルのオーディオ・レベル制御

カー・エレクトロニクスの調整

プログラマブル電源

プログラマブルなフィルタ、遅延、時定数

ライン・インピーダンス・マッチング

低分解能DAC／トリマーの置き換え

基地局パワー・アンプのバイアス

センサー・キャリブレーション

## 概要

AD5263は、業界初の選択可能なデジタル・インターフェース付き、クワッド・チャンネル、256ポジションのデジタル・ポテンショメータ<sup>1</sup>です。このデバイスは、高度な分解能、高い信頼性、卓越した低温度係数性能によって、機械式ポテンショメータや可変抵抗器と同じ電子調整機能を行います。

AD5263の各チャンネルは、A端子とワイヤーとの間、またはB端子とワイヤーとの間で、完全にプログラマブルな抵抗値を提供します。A端子とB端子との間の固定抵抗は20kΩ、50kΩ、または200kΩで、公称温度係数は±30ppm/°C、チャンネル間マッチング公差は±1%です。デバイスのもう1つの重要な特長は、+4.5～+15Vもしくは±5Vで動作することです。

パワーオン時に、ワイヤー・ポジションがミッドスケールにプリセットされるようにプログラミングされています。パワーオンした後は、3線式SPIまたは2線式I<sup>2</sup>C互換のインターフェースでVRのワイヤー・ポジションをプログラムします。I<sup>2</sup>Cモードでは、追加のプログラマブルなロジック出力によって、システム内のデジタル負荷、ロジック・ゲート、アナログ・スイッチを駆動できます。

AD5263は狭体TSSOP-24を採用しており、すべてのデバイスは-40～+125°Cの自動車用温度範囲での動作が保証されています。

シングル／デュアル・チャンネル・アプリケーションについては、AD5260/AD5280またはAD5262/AD5282を参照してください。

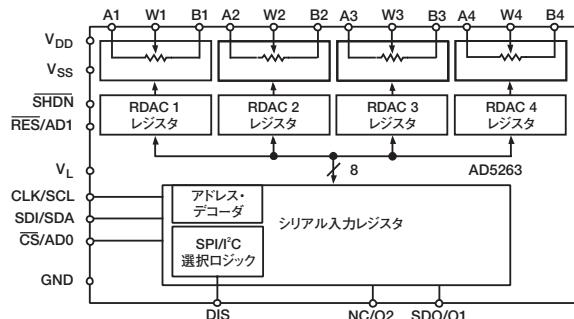

## 機能ブロック図

03142-0-001

図1

<sup>1</sup> デジタル・ポテンショメータ、VR、RDACの用語は、いずれも同じ意味で使用されています。

アナログ・デバイセズ社または同社の二次ライセンスを受けた関連会社からライセンスの対象となるI<sup>2</sup>Cコンポーネントを購入した場合、購入者にはこれらのコンポーネントをI<sup>2</sup>Cシステムで使用するフィリップス社のI<sup>2</sup>Cの特許権にもとづくライセンスが許諾されます。ただし、フィリップス社が規定するI<sup>2</sup>C標準仕様に準拠したシステムが必要です。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を暗示的または明示的に許諾するものもありません。記載の商標および登録商標は、それぞれの企業が所有するものです。

※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

# AD5263

## 目次

|                                          |    |

|------------------------------------------|----|

| 電気的特性—20kΩ、50kΩ、200kΩバージョン               | 3  |

| タイミング特性—20kΩ、50kΩ、200kΩバージョン             | 4  |

| 絶対最大定格                                   | 5  |

| 代表的な性能特性                                 | 6  |

| テスト回路                                    | 11 |

| SPI互換のデジタル・インターフェース (DIS=0)              | 12 |

| I <sup>2</sup> C互換のデジタル・インターフェース (DIS=1) | 13 |

| 動作                                       | 14 |

| 可変抵抗器のプログラミング                            | 14 |

| ポテンショメータ・デバイダのプログラミング                    | 15 |

| ピン選択可能なデジタル・インターフェース                     | 15 |

| SPI互換の3線式シリアル・バス (DIS=0)                 | 15 |

| I <sup>2</sup> C互換の2線式シリアル・バス (DIS=1)    | 16 |

| 追加のプログラマブルなロジック出力                        | 17 |

| 内蔵のシャットダウン機能                             | 17 |

| 1本のバス上の複数デバイス                            | 17 |

| 負電圧動作用のレベル・シフト                           | 17 |

| ESD保護                                    | 18 |

| 端子電圧の動作範囲                                | 18 |

| パワーアップ・シーケンス                             | 18 |

| V <sub>LOGIC</sub> 電源                    | 18 |

| レイアウトと電源のバイパス                            | 18 |

| RDAC回路のシミュレーション・モデル                      | 19 |

|                            |    |

|----------------------------|----|

| アプリケーション                   | 20 |

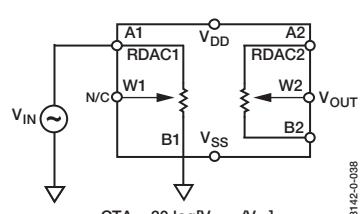

| 両電源によるバイポーラDCまたはAC動作       | 20 |

| ゲイン制御補償                    | 20 |

| プログラマブル・リファレンス             | 20 |

| 8ビットのバイポーラDAC              | 21 |

| バイポーラ・プログラマブル・ゲイン・アンプ      | 21 |

| ブースト出力を持つプログラマブルな電圧源       | 21 |

| 4~20mAのプログラマブルな電流源         | 22 |

| プログラマブルな双方向電流源             | 22 |

| プログラマブルなローパス・フィルタ          | 23 |

| プログラマブルな発振器                | 23 |

| 抵抗のスケーリング                  | 24 |

| 抵抗公差、ドリフト、温度係数の不整合に関する注意事項 | 24 |

| ピン配置とピン機能の説明               | 25 |

| ピン配置                       | 25 |

| ピン機能の説明                    | 25 |

| 外形寸法                       | 26 |

| ESDに関する注意                  | 26 |

| オーダー・ガイド                   | 26 |

## 改定履歴

Rev.0：初稿

## 電気的特性—20kΩ、50kΩ、200kΩバージョン

(特に指定のない限り、 $V_{DD} = +5V$ 、 $V_{SS} = -5V$ 、 $V_L = +5V$ 、 $V_A = +V_{DD}$ 、 $V_B = 0V$ 、 $-40^\circ C < T_A < +125^\circ C$ )

表1

| パラメータ                                   | 記号                       | 条件                                                                    | Min              | Typ <sup>1</sup> | Max              | 単位       |

|-----------------------------------------|--------------------------|-----------------------------------------------------------------------|------------------|------------------|------------------|----------|

| DC特性—可変抵抗器モード (仕様はすべてのVRに適用)            |                          |                                                                       |                  |                  |                  |          |

| 抵抗の微分非直線性 <sup>2</sup>                  | R-DNL                    | $R_{WB}$ 、 $V_A = NC$                                                 | -1               | $\pm 1/4$        | +1               | LSB      |

| 抵抗の非直線性 <sup>2</sup>                    | R-INL                    | $R_{WB}$ 、 $V_A = NC$                                                 | -1               | $\pm 1/2$        | +1               | LSB      |

| 公称抵抗偏差 <sup>3</sup>                     | $\Delta R_{AB}$          | $T_A = 25^\circ C$                                                    | -30              |                  | 30               | %        |

| 抵抗温度係数                                  | $\Delta R_{WB}/\Delta T$ |                                                                       |                  | 30               |                  | ppm/°C   |

| ワイヤー抵抗                                  | $\Delta R_{WA}/\Delta T$ |                                                                       |                  | 30               |                  | ppm/°C   |

|                                         | $R_W$                    | $I_W = 1V/R_{AB}$                                                     |                  | 60               | 150              | Ω        |

| DC特性—ポテンショメータ・デバイダ・モード (仕様はすべてのVRに適用)   |                          |                                                                       |                  |                  |                  |          |

| 分解能                                     | N                        |                                                                       |                  |                  | 8                | ビット      |

| 微分非直線性 <sup>4</sup>                     | DNL                      |                                                                       | -1               | $\pm 1/4$        | +1               | LSB      |

| 積分非直線性 <sup>4</sup>                     | INL                      |                                                                       | -1               | $\pm 1/2$        | +1               | LSB      |

| 分圧器温度係数                                 | $\Delta V_W/\Delta T$    | コード=0x80                                                              |                  | 5                |                  | ppm/°C   |

| フルスケール誤差                                | $V_{WFSE}$               | コード=0xFF                                                              | -2               | -1               | +0               | LSB      |

| ゼロスケール誤差                                | $V_{WZSE}$               | コード=0x00                                                              | 0                | +1               | +2               | LSB      |

| 抵抗端子                                    |                          |                                                                       |                  |                  |                  |          |

| 電圧範囲 <sup>5</sup>                       | $V_{A, B, W}$            |                                                                       | $V_{SS}$         |                  | $V_{DD}$         | V        |

| 容量 <sup>6</sup> $A_x$ 、 $B_x$           | $C_{A, B}$               | $f = 1MHz$ 、GNDに対して測定、<br>コード=0x80                                    | 25               |                  |                  | pF       |

| 容量 <sup>6</sup> $W_x$                   | $C_W$                    | $f = 1MHz$ 、GNDに対して測定、<br>コード=0x80                                    | 55               |                  |                  | pF       |

| コモン・モード・リード電流<br>シャットダウン電流 <sup>7</sup> | $I_{CM}$<br>$I_{SHDN}$   | $V_A = V_B = V_{DD}/2$                                                | 1<br>0.02        |                  | 5                | nA<br>μA |

| デジタル入力                                  |                          |                                                                       |                  |                  |                  |          |

| 入力ロジック・ハイレベル                            | $V_{IH}$                 |                                                                       | 2.4              |                  |                  | V        |

| 入力ロジック・ローレベル                            | $V_{IL}$                 |                                                                       |                  |                  | 0.8              | V        |

| 入力ロジック・ハイレベル<br>(SDAとSCL)               | $V_{IH}$                 | $V_{SS} = 0V$                                                         | $0.7 \times V_L$ |                  | $V_L + 0.5$      | V        |

| 入力ロジック・ローレベル<br>(SDAとSCL)               | $V_{IL}$                 | $V_{SS} = 0V$                                                         | -0.5             |                  | $0.3 \times V_L$ | V        |

| 入力電流                                    | $I_{IL}$                 | $V_{IN} = 0V$ または $+5V$                                               |                  |                  | ±1               | μA       |

| 入力容量 <sup>6</sup>                       | $C_{IL}$                 |                                                                       | 5                |                  |                  | pF       |

| デジタル出力                                  |                          |                                                                       |                  |                  |                  |          |

| SDA                                     | $V_{OL}$                 | $I_{SINK} = 3mA$                                                      |                  |                  | 0.4              | V        |

|                                         | $V_{OL}$                 | $I_{SINK} = 6mA$                                                      |                  |                  | 0.6              | V        |

| O1、O2                                   | $V_{OH}$                 | $I_{SOURCE} = 40\mu A$                                                | 4                |                  |                  | V        |

| O1、O2                                   | $V_{OL}$                 | $I_{SINK} = 1.6mA$                                                    |                  |                  | 0.4              | V        |

| SDO                                     | $V_{OH}$                 | $R_L = 2.2k\Omega \sim V_{DD}$                                        | $V_{DD} - 0.1$   |                  |                  | V        |

| SDO                                     | $V_{OL}$                 | $I_{SINK} = 3mA$                                                      |                  |                  | 0.4              | V        |

| スリーステート・リード電流                           | $I_{OZ}$                 | $V_{IN} = 0V$ または $+5V$                                               |                  |                  | ±1               | μA       |

| 出力容量 <sup>6</sup>                       | $C_{OZ}$                 |                                                                       | 3                |                  | 8                | pF       |

| 電源                                      |                          |                                                                       |                  |                  |                  |          |

| ロジック電源 <sup>8</sup>                     | $V_L$                    |                                                                       | 2.7              |                  | 5.5              | V        |

| 電源範囲—単電源                                | $V_{DD\text{ RANGE}}$    | $V_{SS} = 0V$                                                         | $V_L$            |                  | 16.5             | V        |

| 電源範囲—両電源                                | $V_{DD/SS\text{ RANGE}}$ |                                                                       | $\pm 4.5$        |                  | ±7.5             | V        |

| ロジック電源電流 <sup>9</sup>                   | $I_L$                    | $V_L = +5V$                                                           |                  |                  | 60               | μA       |

| 正電源電流                                   | $I_{DD}$                 | $V_{IH} = +5V$ または $V_{IL} = 0V$                                      |                  |                  | 1                | μA       |

| 負電源電流                                   | $I_{SS}$                 | $V_{SS} = -5V$                                                        |                  |                  | 1                | μA       |

| 消費電力 <sup>10</sup>                      | $P_{DISS}$               | $V_{IH} = +5V$ または $V_{IL} = 0V$ 、<br>$V_{DD} = +5V$ 、 $V_{SS} = -5V$ |                  |                  | 0.6              | mW       |

| 電源電圧感度                                  | PSS                      | $\Delta V_{DD} = +5V \pm 10\%$                                        |                  | 0.002            | 0.01             | %/%      |

| ダイナミック特性 <sup>6, 11</sup>               |                          |                                                                       |                  |                  |                  |          |

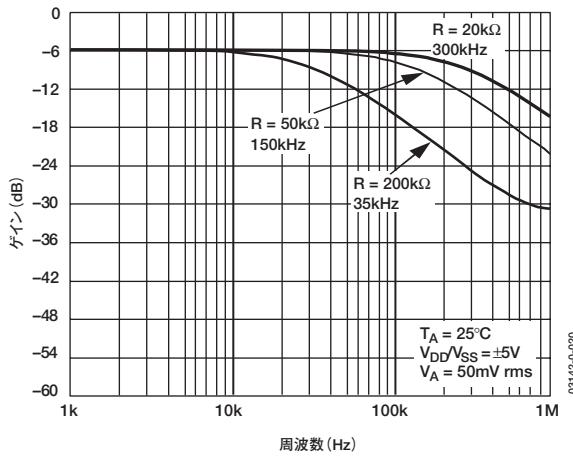

| 帯域幅 (3dB)                               | BW                       | $R_{AB} = 20k\Omega/50k\Omega/200k\Omega$                             |                  | 300/150/35       |                  | kHz      |

| 全高調波歪み                                  | $THD_W$                  | $V_A = 1Vrms$ 、 $V_B = 0V$ 、<br>$f = 1kHz$ 、 $R_{AB} = 20k\Omega$     | 0.05             |                  |                  | %        |

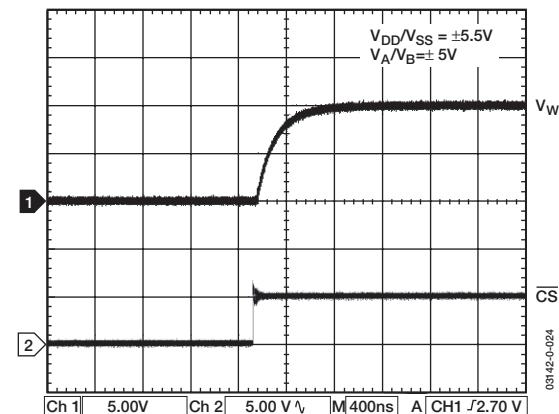

| $V_W$ セトリング・タイム <sup>12</sup>           | $t_S$                    | $V_A = 10V$ 、 $V_B = 0V$ 、<br>$\pm 1LSB$ 誤差帯域                         |                  | 2                |                  | μs       |

| 抵抗ノイズ電圧                                 | $e_{N\_WB}$              | $R_{WB} = 10k\Omega$ 、 $f = 1kHz$ 、 $RS = 0$                          |                  | 9                |                  | nV/√Hz   |

# AD5263

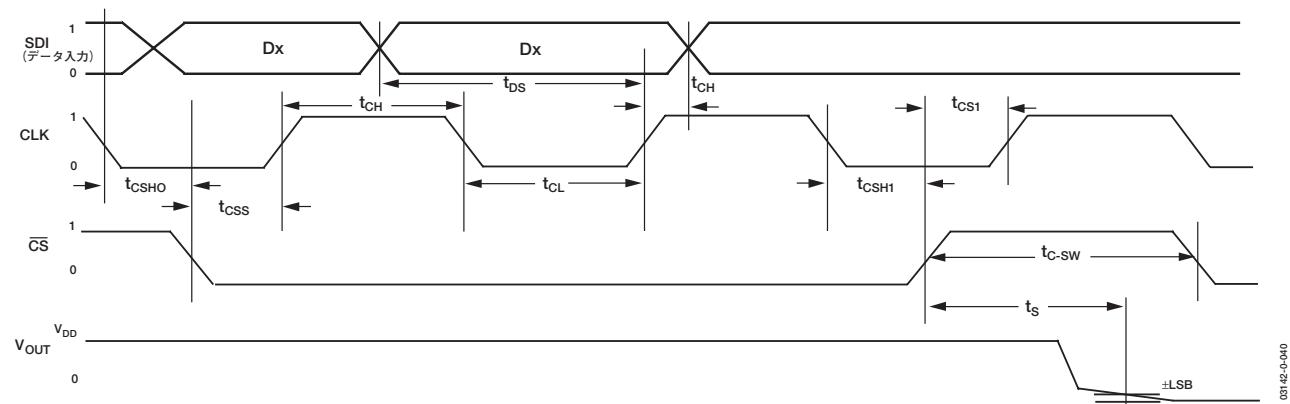

## タイミング特性—20kΩ、50kΩ、200kΩバージョン

(特に指定のない限り、 $V_{DD} = +5V$ 、 $V_{SS} = -5V$ 、 $V_L = +5V$ 、 $V_A = +V_{DD}$ 、 $V_B = 0V$ 、 $-40^\circ C < T_A < +125^\circ C$ )

表2

| パラメータ                                                    | 記号                  | 条件                              | Min | Typ <sup>1</sup> | Max | 単位  |

|----------------------------------------------------------|---------------------|---------------------------------|-----|------------------|-----|-----|

| SPIインターフェース・タイミング特性 (仕様はすべてのデバイスに適用 <sup>6,13)</sup>     |                     |                                 |     |                  |     |     |

| クロック周波数                                                  | $f_{CLK}$           |                                 |     | 25               |     | MHz |

| 入力クロック・パルス幅                                              | $t_{CH}$ 、 $t_{CL}$ | クロック・レベルのハイレベル<br>またはローレベル      | 20  |                  |     | ns  |

| データ・セットアップ・タイム                                           | $t_{DS}$            |                                 | 10  |                  |     | ns  |

| データ・ホールド・タイム                                             | $t_{DH}$            |                                 | 10  |                  |     | ns  |

| $\overline{CS}$ セットアップ・タイム                               | $t_{CSS}$           |                                 | 15  |                  |     | ns  |

| $\overline{CS}$ ハイレベルのパルス幅                               | $t_{CSW}$           |                                 | 20  |                  |     | ns  |

| CLKの立ち下がりから $\overline{CS}$ の<br>立ち下がりまでのホールド・タイム        | $t_{CSH0}$          |                                 | 0   |                  |     | ns  |

| CLKの立ち下がりから $\overline{CS}$ の<br>立ち上がりまでのホールド・タイム        | $t_{CSH1}$          |                                 | 0   |                  |     | ns  |

| $\overline{CS}$ の立ち上がりからクロックの<br>立ち上がりまでのセットアップ・タイム      | $t_{CS1}$           |                                 | 10  |                  |     | ns  |

| リセット・パルス幅                                                | $t_{RS}$            |                                 | 5   |                  |     | ns  |

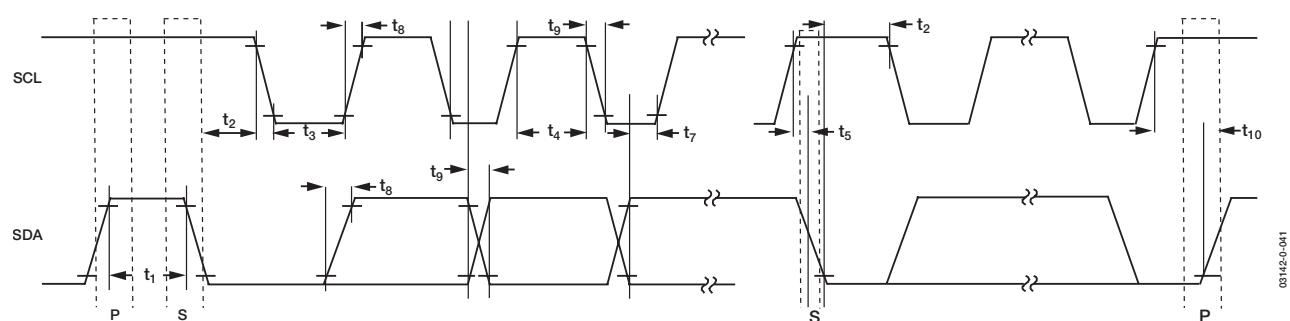

| $I^2C$ インターフェース・タイミング特性 (仕様はすべてのデバイスに適用 <sup>6,13)</sup> |                     |                                 |     |                  |     |     |

| SCLクロック周波数                                               | $F_{SCL}$           |                                 |     | 400              |     | kHz |

| $t_{BUF}$ (STOPとSTART間の<br>バス・フリー・タイム)                   | $t_1$               |                                 | 1.3 |                  |     | μs  |

| $t_{HD STA}$ (ホールド・タイム<br>(反復START))                     | $t_2$               | この期間の後で、最初のクロック・<br>パルスが生成されます。 | 0.6 |                  |     | μs  |

| $t_{LOW}$ (SCLクロックのロー期間)                                 | $t_3$               |                                 | 1.3 |                  |     | μs  |

| $t_{HIGH}$ (SCLクロックのハイ期間)                                | $t_4$               |                                 | 0.6 | 50               |     | μs  |

| $t_{SU STA}$ (START条件のセットアップ・タイム)                        | $t_5$               |                                 | 0.6 |                  |     | μs  |

| $t_{HD DAT}$ (データ・ホールド・タイム)                              | $t_6$               |                                 |     | 0.9              |     | μs  |

| $t_{SU DAT}$ (データ・セットアップ・タイム)                            | $t_7$               |                                 | 100 |                  |     | ns  |

| $t_F$ (SDA信号とSCL信号の立ち下がり時間)                              | $t_8$               |                                 |     | 300              |     | ns  |

| $t_R$ (SDA信号とSCL信号の立ち上がり時間)                              | $t_9$               |                                 |     | 300              |     | ns  |

| $t_{SU STO}$ (STOP条件のセットアップ・タイム)                         | $t_{10}$            |                                 | 0.6 |                  |     | μs  |

注

<sup>1</sup> typ値は、25°C、 $V_{DD} = +5V$ 、 $V_{SS} = -5V$ での平均測定値です。

<sup>2</sup> 抵抗ポジション非直線性誤差 (R-INL) は、最大抵抗ワイヤー・ポジションと最小抵抗ワイヤー・ポジションとの間で測定された理論値からの偏差を表します。R-DNLは、連続タップ・ポジション間での理論値からの相対的ステップ変化を表します。デバイスの単調増加性は保証されています。 $V_{DD} = +5V$  と  $V_{SS} = -5V$  の両方に対して  $I_w = V_{DD}/R$ 。

<sup>3</sup>  $V_{AB} = V_{DD}$ 、ワイヤー ( $V_w$ ) = 非接続。

<sup>4</sup> INLとDNLは、RDACを電圧出力D/Aコンバータと類似のポテンショメータ・デバイダとして設定して、 $V_w$ で測定。 $V_A = V_{DD}$  および  $V_B = 0V$ 。最大±1LSBというDNL仕様の制約は、単調増加性保証の動作条件です。

<sup>5</sup> 抵抗端子A、B、Wの極性は相互に制約されません。

<sup>6</sup> 設計により保証し、出荷テストは行いません。

<sup>7</sup> Ax端子で測定。すべてのAx端子はシャットダウン・モードでオープン。

<sup>8</sup>  $V_L$ は、 $V_{DD}$ または5.5Vのうち小さい方に制約されます。

<sup>9</sup> すべてのロジック入力レベルを2.4Vに設定したとき、ワーストケースの電源電流を消費します。これはCMOSロジックの標準特性です。

<sup>10</sup>  $P_{DSS}$ は、 $(I_{DD} \times V_{DD})$  から計算。CMOSロジック・レベル入力は、最小消費電力になります。

<sup>11</sup> すべてのダイナミック特性で、 $V_{DD} = +5V$ 、 $V_{SS} = -5V$ 、 $V_L = +5V$ を使用。

<sup>12</sup> セトリング・タイムは、 $V_{DD}$ 、 $R_L$ 、 $C_L$ の値に依存します。

<sup>13</sup> 測定値の位置についてはタイミング図を参照してください。すべての入力制御電圧は $t_R = t_F = 2ns$  (+3Vの10~90%)で規定し、1.5Vの電圧レベルからの時間とします。スイッチング特性は、 $V_L = +5V$ を使って測定。

## 絶対最大定格

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ )

表3

| パラメータ                                          | 値                                                                 |

|------------------------------------------------|-------------------------------------------------------------------|

| $V_{DD} \sim GND$                              | $-0.3 \sim +16.5\text{V}$                                         |

| $V_{SS} \sim GND$                              | $0 \sim +7.5\text{V}$                                             |

| $V_{DD} \sim V_{SS}$                           | $+16.5\text{V}$                                                   |

| $V_L \sim GND$                                 | $-0.3 \sim +6.5\text{V}$                                          |

| $V_A, V_B, V_W \sim GND$                       | $V_{SS} \sim V_{DD}$                                              |

| 端子電流、Ax-Bx、Ax-Wx、Bx-Wx<br>断続 <sup>1</sup>      | $\pm 20\text{mA}$                                                 |

| 連続                                             | $\pm 3\text{mA}$                                                  |

| デジタル入／出力電圧～GND                                 | $0 \sim +7\text{V}$                                               |

| 動作温度範囲                                         | $-40 \sim +85^\circ\text{C}$                                      |

| 最大ジャンクション温度 ( $T_{JMAX}$ )                     | $150^\circ\text{C}$                                               |

| 保存温度                                           | $-65 \sim +150^\circ\text{C}$                                     |

| ピン温度 (ハンダ処理、10秒)<br>ペーリング時間 (60秒)<br>赤外線 (15秒) | $300^\circ\text{C}$<br>$215^\circ\text{C}$<br>$220^\circ\text{C}$ |

| 熱抵抗 <sup>2</sup> $\theta_{JA}$<br>TSSOP-24     | $143^\circ\text{C/W}$                                             |

<sup>1</sup> 最大端子電流は、スイッチの最大処理電流、パッケージ最大消費電力、そしてA端子、B端子、W端子のうち任意の2端子間の設定された抵抗での最大入力電圧により制約されます。

<sup>2</sup> パッケージ消費電力： $(T_{JMAX} - T_A) / \theta_{JA}$

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作に関するセクションに記載されている規定値以上でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態にすると、デバイスの信頼性に影響を与えることがあります。

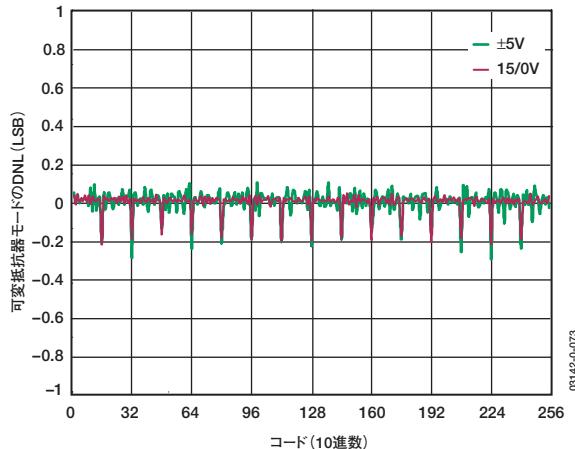

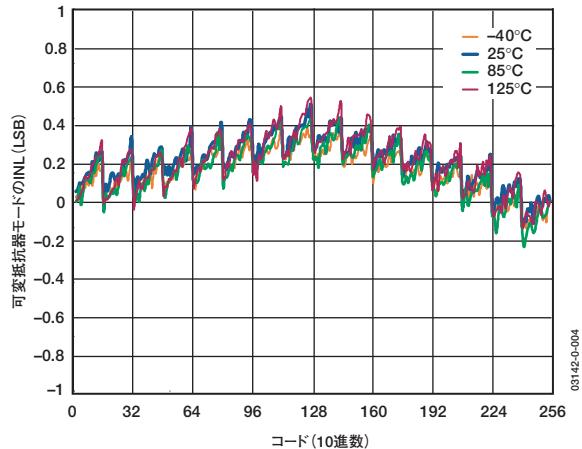

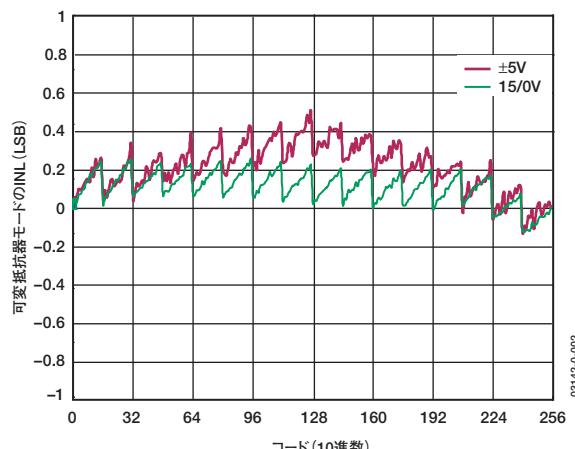

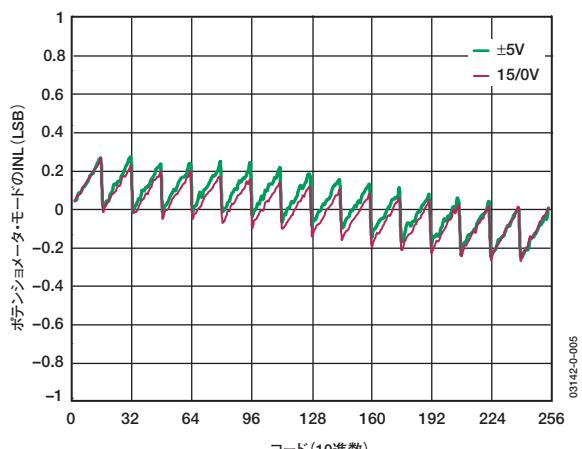

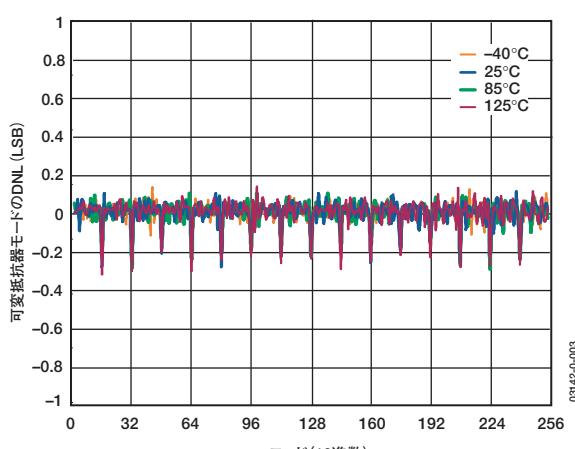

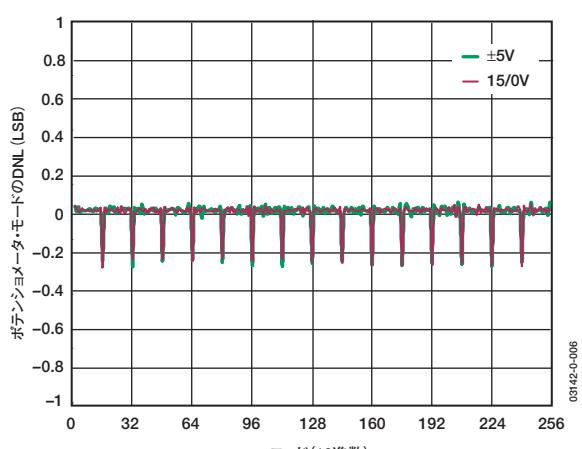

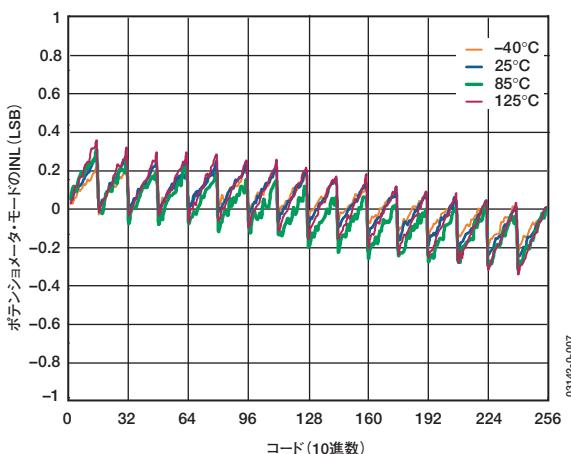

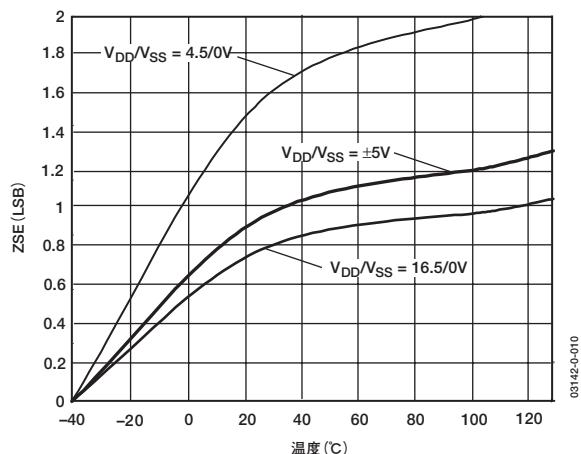

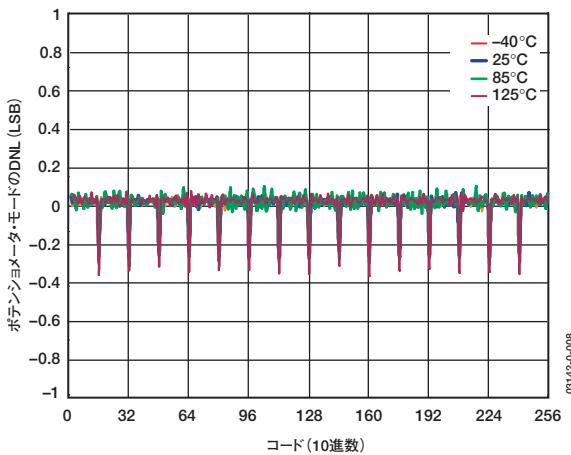

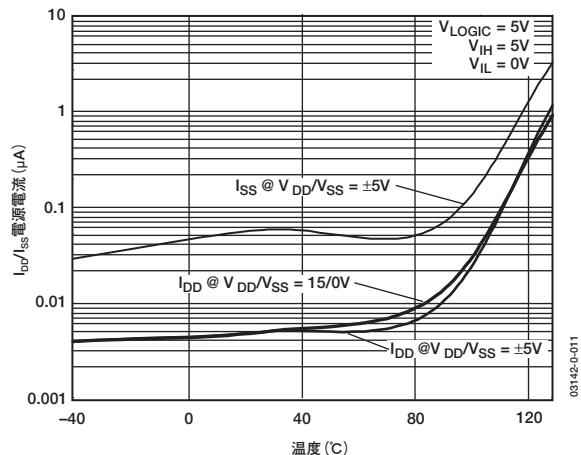

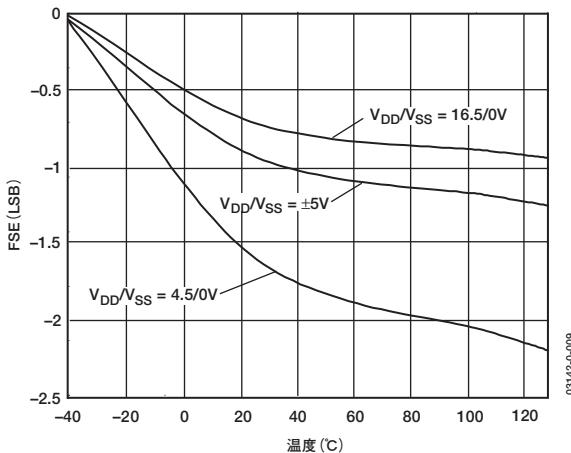

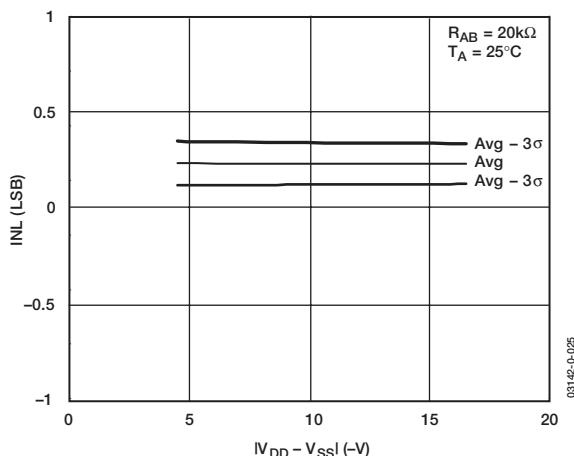

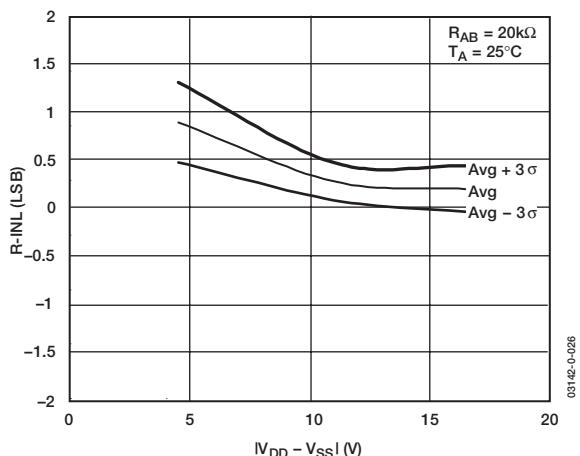

## 代表的な性能特性

(特に指定のない限り、 $R_{AB}=20\text{k}\Omega$ )

図2. R-DNL 対 コード 対 電源電圧

図5. R-INL 対 コード、 $V_{DD}=\pm 5\text{V}$

図3. R-INL 対 コード 対 電源電圧

図6. INL 対 コード 対 電源電圧

図4. R-DNL 対 コード、 $V_{DD}=\pm 5\text{V}$

図7. DNL 対 コード 対 電源電圧

図8. INL 対 コード、 $V_{DD} = \pm 5V$

図11. ゼロスケール誤差対温度

図9. DNL 対 コード、 $V_{DD} = \pm 5V$

図12. 電源電流対温度

図10. フルスケール誤差対温度

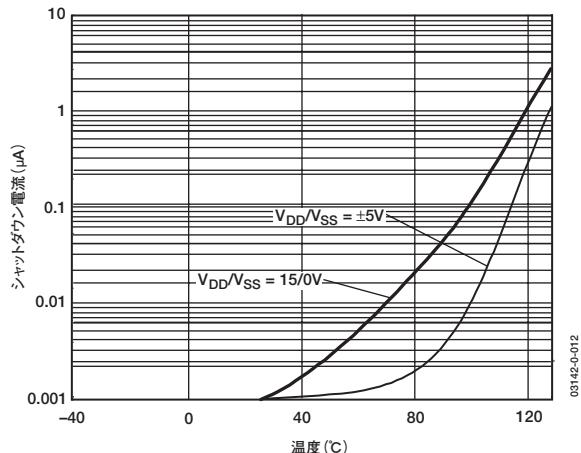

図13. シャットダウン電流対温度

# AD5263

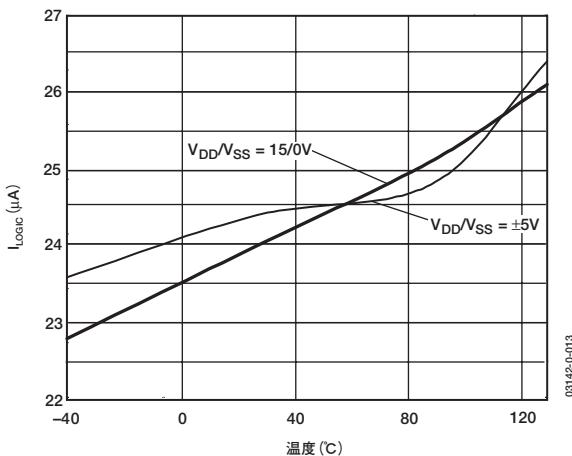

図14.  $I_{LOGIC}$  対 温度

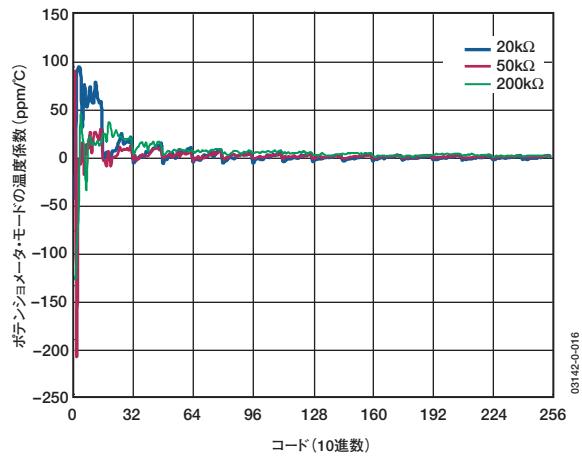

図17. ポテンショメータ・モードの温度係数

$\Delta R_{WB}/\Delta T$  対 コード

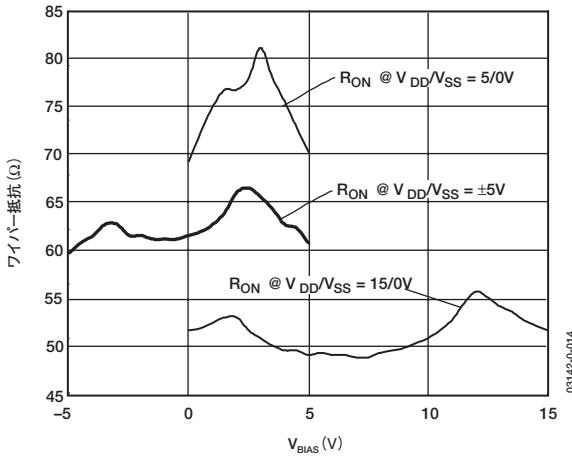

図15. ワイパー・オン抵抗 対 バイアス電圧

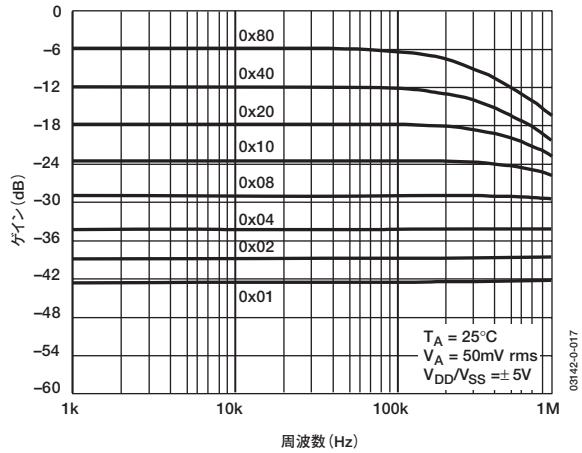

図18. ゲイン 対 周波数 対 コード、 $R_{AB}=20k\Omega$

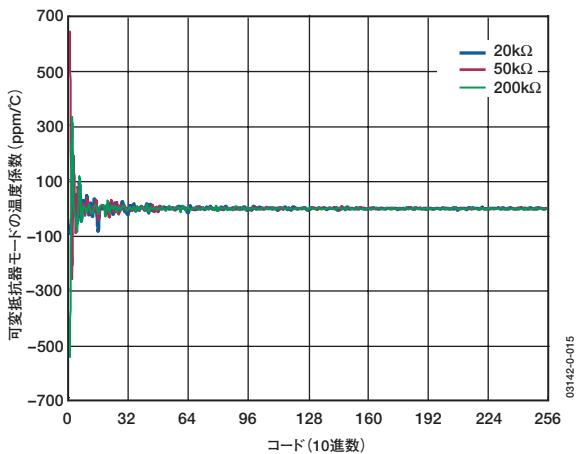

図16. 可変抵抗器モードの温度係数

$\Delta R_{WB}/\Delta T$  対 コード

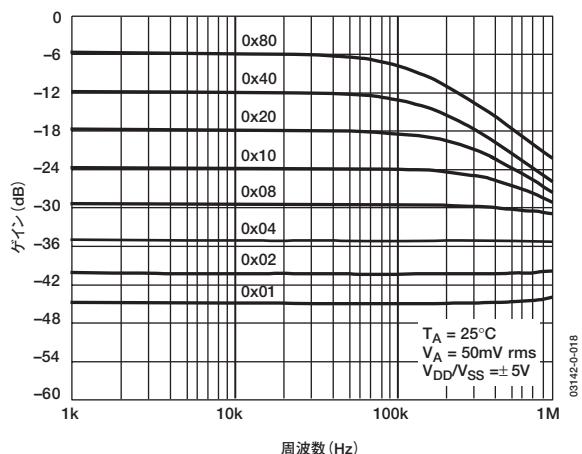

図19. ゲイン 対 周波数 対 コード、 $R_{AB}=50k\Omega$

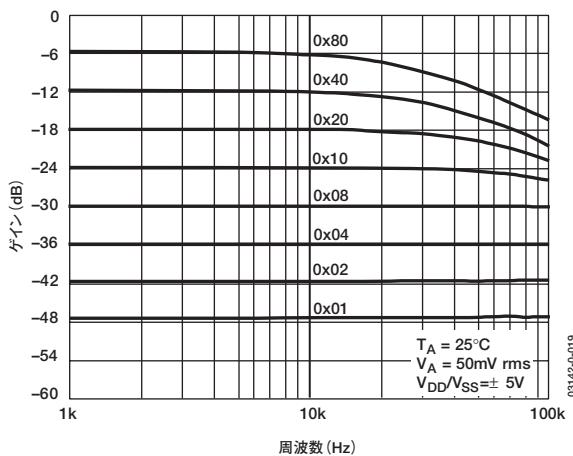

図20. ゲイン対周波数対コード、 $R_{AB}=200\text{k}\Omega$

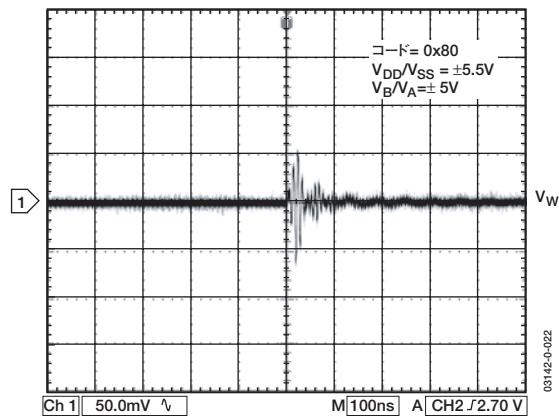

図23. デジタル・フィードスルー

図21. -3dB帯域幅

図24. ミッドスケール・グリッヂ、コード

0x80～0x7F (ワイパーからグラウンド

に4.7nFコンデンサを使用)

図22. PSRR対周波数

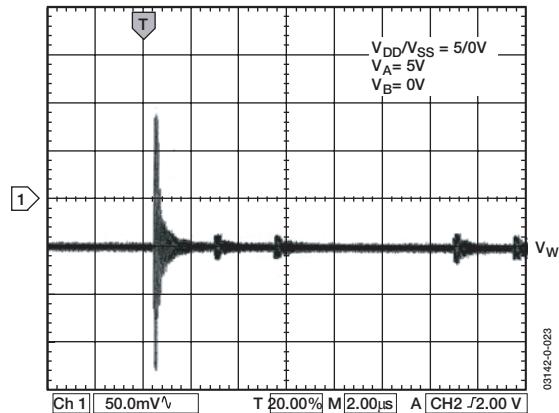

図25. 大信号セトリング・タイム、コード0x00～0xFF

# AD5263

図26. INL 対 電源電圧

図27. R-INL 対 電源電圧

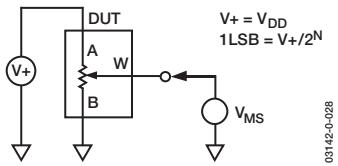

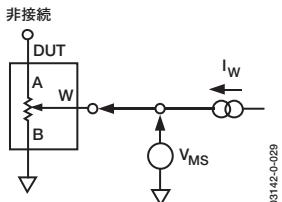

## テスト回路

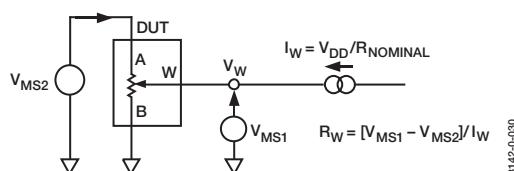

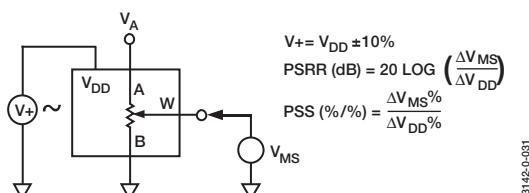

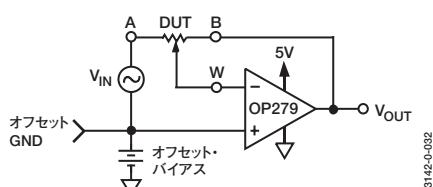

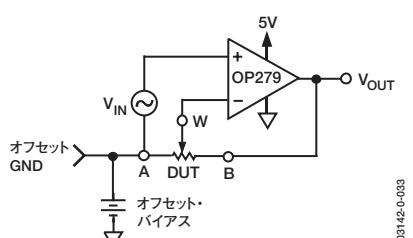

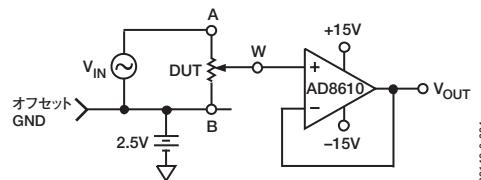

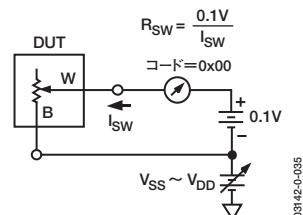

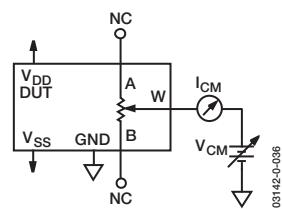

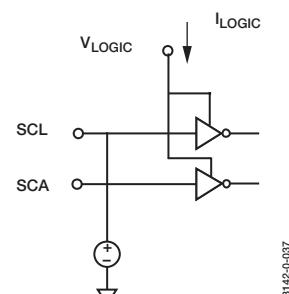

図28~38で、製品仕様表で使用したテスト条件を定義します。

図28. ポテンショメータ・デバイダ非直線性誤差の

テスト回路 (INL、DNL)

図29. 抵抗ポジション非直線性誤差のテスト回路

(可変抵抗器動作、R-INL、R-DNL)

図30. ワイパー抵抗のテスト回路

図31. 電源電圧感度のテスト回路 (PSS、PSSR)

図32. 反転ゲインのテスト回路

図33. 非反転ゲインのテスト回路

図34. ゲイン対周波数のテスト回路

図35. インクリメンタル・オン抵抗のテスト回路

図36. コモン・モード・リーク電流のテスト回路

図37. V<sub>LOGIC</sub>電流対デジタル入力電圧のテスト回路

図38. アナログ・クロストークのテスト回路

# AD5263

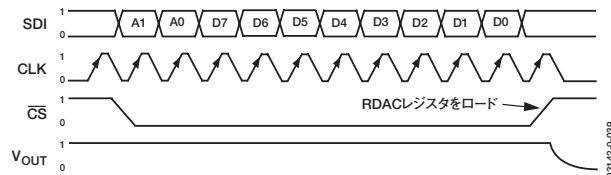

## SPI互換のデジタル・インターフェース (DIS=0)

表4. AD5263のシリアル・データ・ワード・フォーマット

| アドレス  |    | データ   |    |    |    |       |    |    |    |

|-------|----|-------|----|----|----|-------|----|----|----|

| B9    | B8 | B7    | B6 | B5 | B4 | B3    | B2 | B1 | B0 |

| A1    | A0 | D7    | D6 | D5 | D4 | D3    | D2 | D1 | D0 |

|       |    | MSB   |    |    |    | LSB   |    |    |    |

| $2^9$ |    | $2^7$ |    |    |    | $2^0$ |    |    |    |

図39. AD5263のタイミング図

( $V_A=5V$ 、 $V_B=0V$ 、 $V_W=V_{OUT}$ )

図40. 詳細なSPIタイミング図 ( $V_A=5V$ 、 $V_B=0V$ 、 $V_W=V_{OUT}$ )

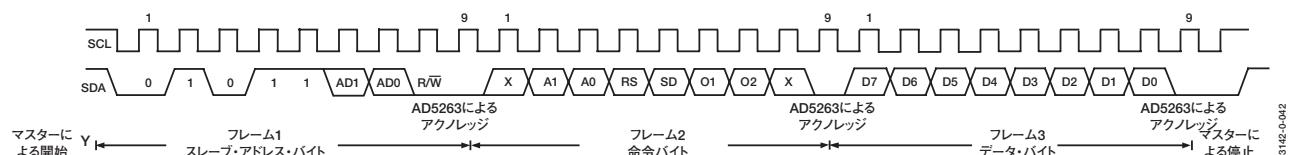

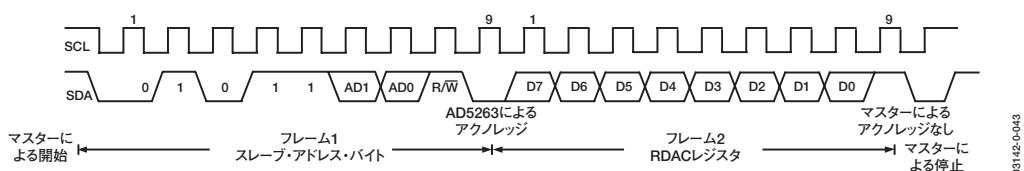

## I<sup>2</sup>C互換のデジタル・インターフェース (DIS=1)

表5. I<sup>2</sup>C書き込みモードのデータ・ワード・フォーマット

|               |   |   |   |   |   |     |     |   |   |       |    |    |    |    |    |    |   |   |    |         |    |    |    |    |    |    |   |   |

|---------------|---|---|---|---|---|-----|-----|---|---|-------|----|----|----|----|----|----|---|---|----|---------|----|----|----|----|----|----|---|---|

| S             | 0 | 1 | 0 | 1 | 1 | AD1 | AD0 | W | A | X     | A1 | A0 | RS | SD | O1 | O2 | X | A | D7 | D6      | D5 | D4 | D3 | D2 | D1 | D0 | A | P |

| スレーブ・アドレス・バイト |   |   |   |   |   |     |     |   |   | 命令バイト |    |    |    |    |    |    |   |   |    | データ・バイト |    |    |    |    |    |    |   |   |

表6. I<sup>2</sup>C読み取りモードのデータ・ワード・フォーマット

|               |   |   |   |   |   |     |     |   |   |         |    |    |    |    |    |    |    |   |   |

|---------------|---|---|---|---|---|-----|-----|---|---|---------|----|----|----|----|----|----|----|---|---|

| S             | 0 | 1 | 0 | 1 | 1 | AD1 | AD0 | R | A | D7      | D8 | D5 | D4 | D3 | D2 | D1 | D0 | A | P |

| スレーブ・アドレス・バイト |   |   |   |   |   |     |     |   |   | データ・バイト |    |    |    |    |    |    |    |   |   |

S=開始条件

P=停止条件

A=アクノレッジ

AD1、AD0=I<sup>2</sup>Cデバイスのアドレス・ビット。ピンAD1、AD0のロジック状態と一致する必要があります。図48を参照。

A1、A0=RDACチャンネル選択

RS=ミッドスケール位置へのソフトウェア・リセット・ワイパー (A1、A0)

SD=シャットダウン・アクティブ・ハイ。ワイパー (A1、A0) を端子Aに接続し、端子Bを開きます。RDACレジスタの内容に影響はありません。シャットダウンを終了するには、RDAC (A1、A0) ごとにコマンドSD=0を実行する必要があります。

O1、O2=I<sup>2</sup>Cモードでのデジタル出力ピンO1、O2へのデータで、外部ロジックの駆動に使用します。ロジック・ハイ・レベルはV<sub>L</sub>によって判定し、ロジック・ロー・レベルはGNDです。

W=書き込み=0

R=読み出し=1

D7、D6、D5、D4、D3、D2、D1、D0=データ・ビット

X=ドント・ケア

図41. 詳細なI<sup>2</sup>Cタイミング図

図42. RDACレジスタへの書き込み

図43. 書き込みモードで以前に選択したRDACレジスタからのデータ読み出し

# AD5263

## 動作

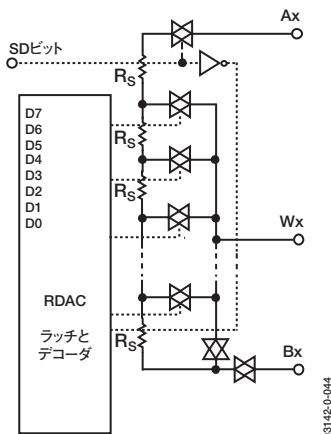

AD5263は、クワッド・チャンネル、256ポジションのデジタル制御可変抵抗器（VR）です。

VR設定値のプログラムについては、前述の「インターフェース」のセクションを参照してください。AD5263にはパワーオン時にワイパーをミッドスケールに置く内部パワーオン・プリセットが備わっているため、パワーアップ時に故障状態から簡単に復帰できます。さらに、AD5263のシャットダウンSHDNピンで、端子Aがオープン・サーキット、ワイパーWが端子Bに接続され、消費電力がほぼゼロの状態にRDACを置きます。これによって、VR構造で消費されるのはリーク電流だけになります。シャットダウン時には、VRのラッチ設定値が維持されますが、新しい設定値をプログラムすることもできます。デバイスがシャットダウンから復帰すると、対応するVR設定値がRDACに適用されます。

図44. AD5263の等価RDAC回路

## 可変抵抗器のプログラミング

### 可変抵抗器動作

端子Aと端子Bとの間のRDACの公称抵抗には、20kΩ、50kΩ、200kΩがあります。公称抵抗値は製品番号の最後の2桁もしくは3桁で示され、20kΩ=20、50kΩ=50、200kΩ=200となります。VRの公称抵抗（R<sub>AB</sub>）には、ワイパー端子がアクセスする256個の接点のほか、B端子接点もあります。RDACラッチ内の8ビット・データをデコードして、256の可能な設定値の中から1つを選択します。20kΩのデバイスを使用する場合、ワイパーの最初の接続は、データ0x00のB端子から始まります。60Ωのワイパー接触抵抗があるため、この接続によって端子Wと端子Bとの間に最小2×60Ωの抵抗が発生します。2番目の接続は最初のタップ・ポイントで、データ0x01の198Ω（R<sub>WB</sub>=R<sub>AB</sub>/256+R<sub>w</sub>=78Ω+2×60Ω）に対応します。3番目の接続は次のタップ・ポイントで、データ0x02の216Ω（R<sub>WB</sub>=78Ω×2+2×60Ω）になります。このようにして、19,982Ω（R<sub>AB</sub>-1LSB+2×R<sub>w</sub>）の最後のタップ・ポイントに到達するまで、LSBデータ値が増加するたびに、ワイパーが抵抗のレベルを1つずつ上に移動します。図44に、等価なRDAC回路の簡略図を示します。ここでは、最後の抵抗列にはアクセスしません。したがって、フルスケールでは、ワイパー抵抗のほかに1LSB小さい公称抵抗が存在することになります。

端子Wと端子Bとの間でデジタルにプログラムする出力抵抗を決める一般式は、次のとおりです。

$$R_{WB}(D) = \frac{D}{256} \times R_{AB} + 2 \times R_w \quad (1)$$

ここで、

Dは、8ビットのRDACレジスタにロードされるバイナリ・コードと等価な10進値です。

R<sub>AB</sub>は、エンド・ツー・エンド抵抗です。

R<sub>w</sub>は、1つの内部スイッチのオノン抵抗に起因するワイパー抵抗です。

要するに、R<sub>AB</sub>=20kΩで、A端子がオープン・サーキットの場合は、次のRDACラッチ・コードによって対応する出力抵抗R<sub>WB</sub>が生じます。

表7. コードと対応するR<sub>WB</sub>抵抗値

| D (dec) | R <sub>WB</sub> (Ω) | 出力状態                                           |

|---------|---------------------|------------------------------------------------|

| 255     | 19,982              | フルスケール (R <sub>AB</sub> -1LSB+R <sub>w</sub> ) |

| 128     | 10,120              | ミッドスケール                                        |

| 1       | 198                 | 1LSB                                           |

| 0       | 120                 | ゼロスケール (ワイパー接触抵抗)                              |

なお、ゼロスケール状態では、120Ωという有限なワイパー抵抗が存在します。この状態で、WとBの間の電流フローについて最大パルス電流が20mAを超えないように制限してください。この値を超えると、内部スイッチ接点の劣化や破損が生じる可能性があります。

機械式ポテンショメータと同様に、ワイパーWと端子Aとの間のRDACの抵抗によって、デジタル制御される相補抵抗R<sub>WA</sub>が生じます。これらの端子を使用する場合、B端子を開くことができます。R<sub>WA</sub>の抵抗値の設定では、抵抗の最大値から始まり、ラッチにロードされるデータの値が増えるにつれて減少します。この動作の一般式は次のとおりです。

$$R_{WA}(D) = \frac{256-D}{256} \times R_{AB} + 2 \times R_w \quad (2)$$

R<sub>AB</sub>=20kΩで、B端子がオープン・サーキットの場合、次のRDACラッチ・コードによって、対応する出力抵抗R<sub>WA</sub>が生じます。

表8. コードと対応するR<sub>WA</sub>抵抗

| D (dec) | R <sub>WA</sub> (Ω) | 出力状態    |

|---------|---------------------|---------|

| 255     | 198                 | フルスケール  |

| 128     | 10,120              | ミッドスケール |

| 1       | 19,982              | 1LSB    |

| 0       | 20,060              | ゼロスケール  |

チャンネル間のエンド・ツー・エンド抵抗 $R_{AB}$ の代表的な分布は、 $\pm 1\%$ 以内で一致します。デバイス間マッチングは、プロセス・ロットに依存し、 $\pm 30\%$ の変動が生じることもあります。抵抗素子は薄膜技術で処理されるため、温度による $R_{AB}$ の変化は、 $30\text{ppm}/^\circ\text{C}$ というきわめて低い温度係数になります。

## ポテンショメータ・デバイダのプログラミング 電圧出力動作

デジタル・ポテンショメータは、端子Aから端子Bまでの入力電圧に比例して、ワイヤー／B間とワイヤー／A間で分圧器を簡単に生成します。 $V_{DD}/V_{SS}$ 間の極性は正でなければなりませんが、A/B、W/A、W/B間の電圧は、 $V_{SS}$ を負電源に接続している限り、いずれの極性も可能です。

概算値を得るためにワイヤー抵抗の影響を無視すると、A端子を5Vに接続し、B端子をグラウンドに接続すれば、ワイヤー／B間に $0\text{V} \sim (5\text{V} - 1\text{LSB})$ の出力電圧が発生します。電圧の各LSBステップは、端子A/B間に印加される電圧をポテンショメータ・デバイダの256ポジションで除算した値に等しくなります。AD5263は両電源に接続できるため、端子Aと端子Bに印加される有効な入力電圧のグラウンドを基準にすると、出力電圧 $V_W$ を定義する一般式は次のようになります。

$$V_W(D) = \frac{D}{256} V_A + \frac{256-D}{256} V_B \quad (3)$$

ワイヤー抵抗の影響を考慮に入れて正確に計算する場合は、 $V_W$ は次のようにになります。

$$V_W(D) = \frac{R_{WB}(D)}{256} V_A + \frac{R_{WA}(D)}{256} V_B \quad (4)$$

デジタル・ポテンショメータをデバイダ・モードで動作させると、さまざまな温度で正確な動作が得られます。可変抵抗器モードとは異なり、出力電圧は主として内部抵抗 $R_{WA}$ と $R_{WB}$ の絶対値ではなく、その比率に依存します。このため、温度ドリフトが $5\text{ppm}/^\circ\text{C}$ に減少します。

### ピン選択可能なデジタル・インターフェース

AD5263は、選択可能なインターフェースによる柔軟性が得られます。デジタル・インターフェース・セレクト (DIS) ピンをローに接続するとSPIモードになり、 $V_L$ 電源にハイで接続するとI<sup>2</sup>Cモードになります。

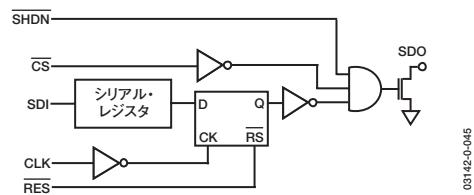

### SPI互換の3線式シリアル・バス (DIS=0)

AD5263には、3線式SPI互換のデジタル・インターフェース (SDI、 $\overline{CS}$ 、CLK) が内蔵されています。10ビットのシリアル・ワードに、アドレス・ビットA1とA0に続けてMSBファーストでデータ・バイトをロードする必要があります。ワードのフォーマットを表4に示します。

シリアル入力レジスタに不正なデータがクロック入力されないように、立ち上がりエッジを検出するCLK入力にはクリーンなクロック遷移が必要です。標準のロジック・ファミリーは、この条件を満たします。製品評価のために機械的スイッチを使用する場合は、フリップフロップやその他の適切な方法によってバウンスを防止してください。 $\overline{CS}$ がローレベルのとき、クロックの各立ち上がりエッジでシリアル・レジスタにデータがロードされます (図39を参照)。

表9. AD5263のアドレス・デコード表

| A1 | A0 | ラッチをロード |

|----|----|---------|

| 0  | 0  | RDAC1   |

| 0  | 1  | RDAC2   |

| 1  | 0  | RDAC3   |

| 1  | 1  | RDAC4   |

有効なタイミング条件は、仕様表のデータ・セットアップ・タイムとデータ・ホールド・タイムによって決まります。AD5263では10ビットのシリアル入力データ・レジスタ・ワードを使用し、 $\overline{CS}$ ラインがロジック・ハイレベルに戻るときにこのワードが内部RDACレジスタに転送されます。なお、デコーダにラッチされるのは、レジスタにクロック入力される最後の10ビットだけです。 $\overline{CS}$ がハイレベルになると、アドレス・デコーダがアクティブになり、表9に従って対応するチャンネルが更新されます。

シャットダウン ( $\overline{SHDN}$ ) 時には、外部プルアップ抵抗での電力消費を回避するために、シリアル・データ出力 (SDO) ピンがロジック・ハイになります。等価なSDO出力回路図を図45に示します。

図45. AD5263の詳細なSDO出力回路図

リセット ( $\overline{RES}$ ) 時には、ワイヤーがミッドスケールに設定されます。なお、 $\overline{SHDN}$ とは異なり、デバイスがリセット状態から出たときもワイヤーはミッドスケール状態のままで、リセット前の設定には戻りません。

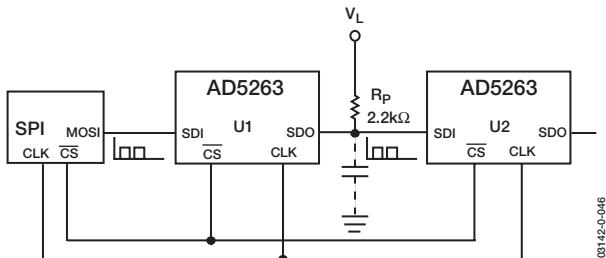

### デイジーチェーン動作

シリアル・データ出力 (SDO) ピンには、オープン・ドレインNチャンネルFETを使用しています。この出力には、次のパッケージのSDIピンにデータを転送するために、プルアップ抵抗が必要です。プルアップ抵抗により、1本のプロセッサ・シリアル・データ・ラインを使って複数のRDACをデイジーチェーン接続することが可能になります。プルアップ抵抗の終端電圧は、 $V_{DD}$ 電源電圧より高くすることも可能です。次のデバイスのSDIピンにプルアップ抵抗を使う場合、クロック周期を長くすることを推奨します。これは、デバイス間のデイジーチェーン・ノード (SDO～SDI) の容量負荷により、後続デバイスに時間遅延が生じる可能性があるためです。データ転送を正しく行うために、ユーザーはこの問題に注意してください (図46を参照)。2個のAD5263をデイジーチェーン接続する場合、合計20ビットのデータが必要になります。表4に示すフォーマットに従って、最初の10ビットはU2に、同じフォーマットで2番目の10ビットはU1に行きます。20ビットがすべてそれぞれのシリアル・レジスタにクロック入力されるまで、 $\overline{CS}$ をローレベルに維持してください。その後で、 $\overline{CS}$ をハイレベルにして動作を完了させ、RDACラッチをロードします。

# AD5263

なお、データはクロックの立ち下がりエッジでSDOに現れるため、次のクロックの立ち上がりエッジで、デイジーチェーン接続されたデバイスの入力に使用できます。

図46. デイジーチェーン構成

## I<sup>2</sup>C互換の2線式シリアル・バス (DIS=1)

I<sup>2</sup>C互換モードでは、RDACはスレーブ・デバイスとしてバスに接続します。

表5と表6に示すように、AD5263の最初のバイトはスレーブ・アドレス・バイトで、7ビットのスレーブ・アドレスとR/Wビットで構成されます。5つのMSBは01011で、次の2ビットはデバイスのAD0ピンとAD1ピンの状態によって決まります。AD0とAD1を使用して、ユーザーは1本のバス上に最高4つのI<sup>2</sup>C互換デバイスを置くことができます。

2線式I<sup>2</sup>Cシリアル・バス・プロトコルは、次のように動作します。

1. マスターが開始条件を確立して、データ転送を開始します。これは、SCLがハイレベルになっている間に、SDAライン上でハイからローへの遷移が発生したときになります（図42を参照）。次のバイトはスレーブ・アドレス・バイトで、7ビットのスレーブ・アドレスとそれに続くR/Wビットで構成されます。スレーブ・デバイスのデータの読み出しをする書き込みを行うかは、このR/Wビットによって決まります。

送信したアドレスに対応するアドレスを持つスレーブが、9番目のクロック・パルス（アクノレッジ・ビットと呼ばれます）中にSDAラインをローレベルにプルすることによって応答します。この段階で、バス上の他のすべてのデバイスはアイドル状態のままでですが、選択されたデバイスは、シリアル・レジスタとの間でデータの読み出しか書き込みが行われるのを待ちます。R/Wビットがハイレベルの場合、マスターはスレーブ・デバイスからデータの読み出しを行い、R/Wビットがローレベルの場合は、スレーブ・デバイスへの書き込みを行います。

2. 書き込みモードでは、2番目のバイトが命令バイトです。命令バイトの先頭ビット（MSB）はドント・ケアです。A1およびA0というラベルの付いた次の2ビットは、RDACサブアドレス選択ビットです。

4番目のMSB（RS）は、ミッドスケール・リセットです。このビットがロジック・ハイの場合、選択されたチャンネルのワイヤーは、R<sub>WA</sub>=R<sub>WB</sub>であるセンター・タップに移動します。この機能によってレジスタの内容が上書きされるため、リセット・モードから出たとき、RDACはミッドスケールのままになります。

5番目のMSB（SD）は、シャットダウン・ビットです。ロジック・ハイであれば、選択されたチャンネルが端子Aでオープン・サーキットとなり、ワイヤーを端子Bに短絡します。この動作によって、可変抵抗器モードでは0Ω、ポテンショメータ・モードでは0Vが生じます。このSDビットは、SHDNピンと同じ機能を果たします。ただし、SHDNピンの場合はアクティブ・ローに反応します。また、SHDNピンがすべてのチャンネルに影響するのに対して、SDビットは書き込み中のチャンネルだけに影響を与えます。なお、重要なことです、シャットダウン動作はレジスタの内容には影響しません。シャットダウンから出ると、RDACには以前の設定値が適用されます。

次の2ビットはO2とO1です。これは追加のプログラマブルなロジック出力で、ほかのデジタル負荷、ロジック・ゲート、LEDドライバ、アナログ・スイッチなどの駆動に使用できます。

LSBはドント・ケアです（表5を参照）。

命令バイトをアクノレッジした後、書き込みモードでの最後のバイトはデータ・バイトになります。連続する9つのクロック・パルス（8つのデータ・ビットとそれに続くアクノレッジ・ビット）で、シリアル・バス上にデータを送信します。SDAライン上での遷移はSCLのロー期間中に生じ、SCLのハイ期間中は安定していかなければなりません（図42を参照）。

3. 読み出しモードでは、データ・バイトはスレーブ・アドレス・バイトのアクノレッジの直後に続きます。連続する9つのクロック・パルス（8つのデータ・ビットに続いてアクノレッジ・ビットがある書き込みモードとは少し違います）で、シリアル・バス上にデータを送信します。この場合も、SDAライン上での遷移はSCLのロー期間中に生じ、SCLのハイ期間中は安定していかなければなりません（図43を参照）。

なお、対象となるチャンネルは、書き込みモードで以前に選択したチャンネルです。両方のチャンネルのRDAC値を読み出す必要がある場合には、最初のチャンネルを書き込みモードでプログラムしてから、読み出しモードに切り替えて、最初のチャンネル値を読み出します。次に、2番目のチャンネルを選択して書き込みモードに戻し、再び読み出しモードで2番目のチャンネル値を読み出す必要があります。それ以降のリードバック動作に対しては、書き込みモードでフレーム3のデータ・バイトを発行する必要はありません。プログラミング・フォーマットについては、図43を参照してください。

4. すべてのデータ・ビットの読み出し／書き込みが終わると、マスターが停止条件を成立させます。停止条件は、SCLがハイレベルの間に生じるSDAライン上でのローレベルからハイレベルへの遷移となります。書き込みモードでは、マスターは10番目のクロック・パルスの間にSDAラインをハイレベルにプルして停止条件を成立させます（図42を参照）。読み出しモードでは、マスターが9番目のクロック・パルスに対して「アクノレッジなし」を発行します（つまり、SDAラインはハイレベルのままで）。続いて10番目のクロック・パルスの前にSDAラインをローレベルにし、ここからSDAラインがハイレベルになって停止条件が成立します（図43を参照）。

書き込み機能の反復を利用すれば、デバイスに一度だけアドレス指定と命令を与えておけば、RDAC出力を何回でも更新できる柔軟性が得られます。たとえば、RDACが書き込みモードでのスレーブ・アドレス・バイトと命令バイトをアクノレッジした後、次に続く各バイトでRDAC出力が更新されるようになります。別の命令が必要な場合には、新しいスレーブ・アドレス、命令、データ・バイトで書き込み／読み出しモードを再開する必要があります。この場合も、RDACの反復読み出し機能が利用できます。

### 追加のプログラマブルなロジック出力

AD5263にはそのほかにプログラマブルなロジック出力O1とO2があり、これを使用すればデジタル負荷、アナログ・スイッチ、ロジック・ゲートを駆動できます。O1とO2は、デフォルトでロジック0になります。電圧レベルは、GNDからV<sub>L</sub>までスイングします。O1とO2のロジック状態は、書き込みモードのフレーム2でプログラムできます（図42を参照）。このロジック出力には、ミリアンペア負荷をシンク／ソースするために十分な電流駆動能力があります。

ユーザーは、ワイヤー設定値を変化させずに以下の3つの方法でO1とO2をアクティブにすることもできます。

1. 開始、スレーブ・アドレス・バイト、アクノレッジ、O1とO2を指定した命令バイト、アクノレッジ、停止。

2. 停止によって書き込みサイクルを完了し、続いて開始、スレーブ・アドレス・バイト、アクノレッジ、O1とO2を指定した命令バイト、アクノレッジ、停止。

3. 停止を発行しないことで書き込みサイクルを完了せず、続いて開始、スレーブ・アドレス・バイト、アクノレッジ、O1とO2を指定した命令バイト、アクノレッジ、停止。

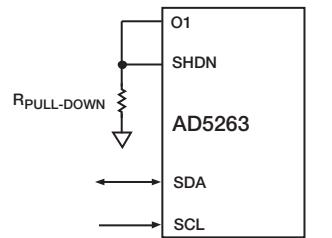

### 内蔵のシャットダウン機能

シャットダウンをアクティブにするには、SHDNピンをストローブするか、書き込みモードの命令バイトでSDビットをプログラムします。さらに、図47に示すように、デバイスのデジタル出力によってもシャットダウンが可能です。この設定では、電源投入時にデバイスがシャットダウンしますが、ユーザーがデバイスのプログラムをすることは可能です。このため、O1をハイレベルにプログラムしていると、デバイスはシャットダウン・モードから出て、新しい設定値に応答します。内蔵シャットダウン機能を使用すれば、電源投入時に完全なシャットダウンが可能になります。これは、危険な環境ではきわめて重要な機能ですが、そのために外部コンポーネントを追加する必要もありません。

図47. 内部ロジック出力によるシャットダウン

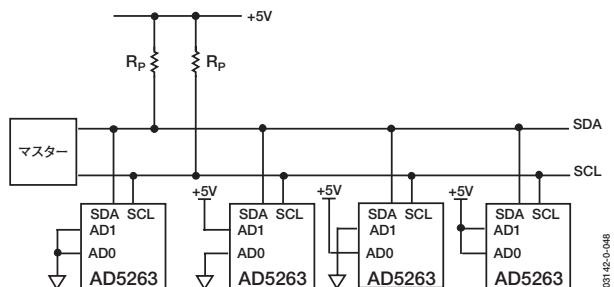

### 1本のバス上の複数デバイス

図48に、同じシリアル・バス上の4つのAD5263デバイスを示します。各AD5263デバイスでは、AD0ピンとAD1ピンの状態が異なるため、スレーブ・アドレスも異なります。これによって、各デバイス内のそれぞれのRDACについて別々に読み出し／書き込みができます。マスターのデバイス出力バス・ライン・ドライバは、I<sup>2</sup>Cに完全互換のインターフェースではオープンンドレインのプルダウンです。

図48. 1本のI<sup>2</sup>Cバス上の複数のAD5263デバイス

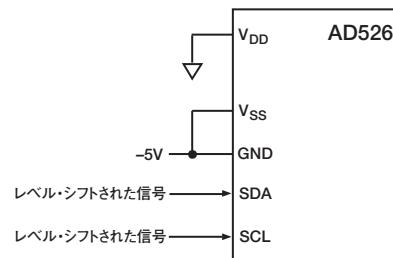

### 負電圧動作用のレベル・シフト

デジタル・ポテンショメータは、レーザー・ダイオード・ドライバやある種の通信機器のレベル設定アプリケーションでよく使用されます。こうしたアプリケーションでは、AC性能を著しく低下させることのある大きなバイパス・コンデンサの使用を避けるため、システムにグラウンドでバイアスをかけられるように、グラウンドと負電源電圧との間で動作させることができます。多くのデジタル・ポテンショメータと同様に、AD5263も負電源で設定できます（図49を参照）。

図49. 負電圧でのバイアス

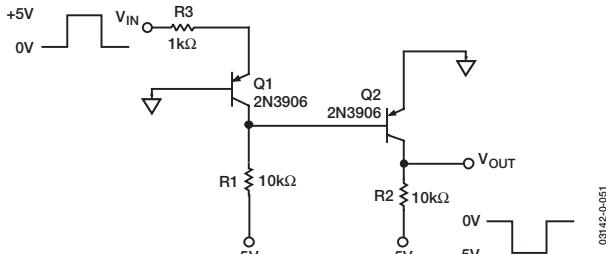

しかし、この場合はグラウンドが負電位を基準としているため、適切な動作を可能にするには、デジタル入力もレベル・シフトする必要があります。その結果、図50に示すようないくつかのトランジスタと抵抗による実装となります。

# AD5263

$V_{IN}$ がハイレベルのとき、Q1がオンになります。そのエミッタがグラウンドより1つ上のスレッショールドでクランプされます。このスレッショールドがQ2のベースに現われるため、Q2はオフになります。この状態で、 $V_{OUT}$ が-5Vに近づきます。 $V_{IN}$ がローレベルのとき、Q1がオフになります。Q2のベースがローレベルにプルされるので、今度はQ2がオンになります。この状態で、 $V_{OUT}$ が0Vに近づきます。なお、デバイスとの正常な通信のためには、適切なタイム・シフトも必要です。

図50. バイポーラ電位動作用のレベル・シフト

## ESD保護

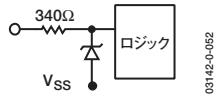

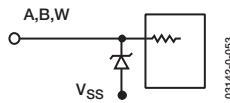

すべてのデジタル入力は、図51と図52に示す直列入力抵抗と並列ツェナーESD構造によって保護されています。デジタル入力ピンSDI/SDA、CLK/SCL、CS/AD0、RES/AD1、SHDNにこの保護が適用されます。

図51. デジタルピンのESD保護

図52. 抵抗端子のESD保護

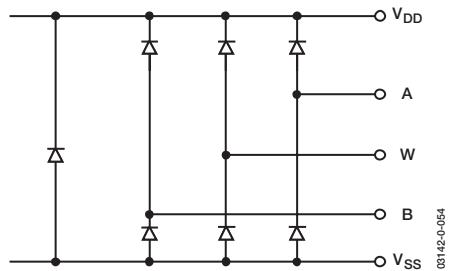

## 端子電圧の動作範囲

AD5263の正 $V_{DD}$ および負 $V_{SS}$ 電源は、適切な3端子デジタル・ポテンショメータ動作のための境界条件を定義します。 $V_{DD}$ または $V_{SS}$ を超える端子A、B、W上に存在する電源信号は、図53に示す順方向バイアスがかけられた内部ダイオードによってクランプされます。

図53.  $V_{DD}$ と $V_{SS}$ によって設定された最大端子電圧

## パワーアップ・シーケンス

ESD保護ダイオードが端子A、B、Wの電圧コンプライアンスを制限しているため（図53を参照）、端子A、B、Wに電圧を印加する前に、 $V_{DD}$ と $V_{SS}$ に電力を供給することが大切です。このようにしないと、ダイオードに順方向バイアスがかけられて、意図せずに $V_{DD}$ と $V_{SS}$ に電力が供給され、残りの回路に影響を与えることがあります。理想的なパワーアップ・シーケンスは、GND、 $V_{DD}$ 、 $V_{SS}$ 、 $V_L$ 、デジタル入力、 $V_{A/B/W}$ という順序です。 $V_A$ 、 $V_B$ 、 $V_W$ 、デジタル入力については、 $V_{DD}$ と $V_{SS}$ の後で電力が供給される限り、この4つの中での順番は重要ではありません。

## $V_{LOGIC}$ 電源

AD5263では、内部ロジック・レベルは5Vでの動作に制限されていますが、それを超える高電圧での動作も可能です。しかし、適切なデジタル信号レベルを保証するために、 $V_L$ を2.7~5.5Vの別電源に常に接続しておく必要があります。 $V_{DD}$ とは無関係に、ロジック・レベルは $V_L$ に制限されます。また、 $V_L$ は必ず $V_{DD}$ より低くしてください。

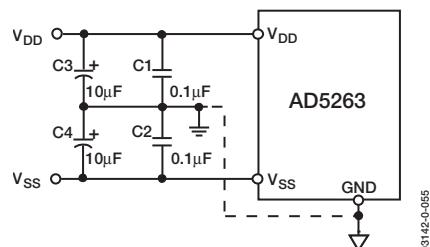

## レイアウトと電源のバイパス

最小リード長のコンパクトなレイアウト設計をお勧めします。入力へのリード線は、最小の導体長で可能な限り短くしてください。グラウンド・バスの抵抗とインダクタンスが、低くなるようにします。

また、最大限の安定性を実現するために、高品質のコンデンサを使用して電源をバイパスすることをお勧めします。デバイスへの電源リード線は、0.01~0.1 $\mu$ Fのセラミック・ディスクまたはチップ・コンデンサを使用してバイパスしてください。過度障害と低周波リップルを最小限に抑えるため、電源には1~10 $\mu$ Fの低ESRタンタル・コンデンサまたは電解コンデンサも使用してください（図54を参照）。グラウンド・バウンスを最小限に抑えるために、デジタル・グラウンドもアナログ・グラウンドに1箇所でリモート結合してください。

図54. 電源のバイパス

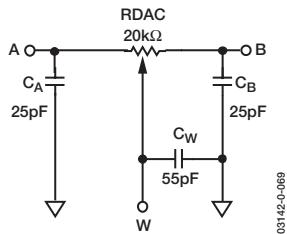

## RDAC回路のシミュレーション・モデル

RDACのAC特性は、内部寄生容量と外部容量性負荷によって決まります。AD5263 (20kΩ抵抗) の-3dB帯域幅は、ポテンショメータ・デバイダとして構成された場合、ハーフスケールで300kHzの値になります。図21に、使用可能な3種類の抵抗(20kΩ、50kΩ、200kΩ)の大信号BODEプロット特性を示します。図55には、寄生シミュレーション・モデルを示します。20kΩRDAC用のマクロ・モデル・ネット・リストは、以下のとおりです。

図55. RDAC=20kΩ用のRDAC回路のシミュレーション・モデル

## リスト1. RDAC用のマクロ・モデル・ネット・リスト

```

.PARAM D=256, RDAC=20E3

*

.SUBCKT DPOT (A,W,B)

*

CA      A      0      25E-12

RWA     A      W      { (1-D/256) *RDAC+60 }

CW      W      0      55E-12

RWB     W      B      {D/256*RDAC+60}

CB      B      0      25E-12

*

.ENDS DPOT

```

# AD5263

## アプリケーション

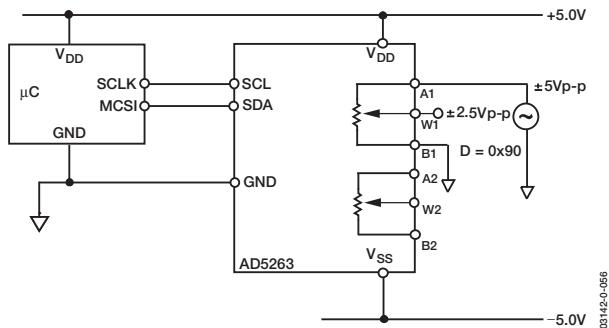

### 両電源によるバイポーラDCまたはAC動作

AD5263は両電源で動作するため、グラウンド基準のAC信号やバイポーラ動作の制御が可能です。 $V_{DD}/V_{SS}$ と同じレベルのAC信号を端子A/B間に直接印加して、端子Wから出力を得ることができます。代表的な回路接続については、図56を参照してください。

図56. 両電源によるバイポーラ動作

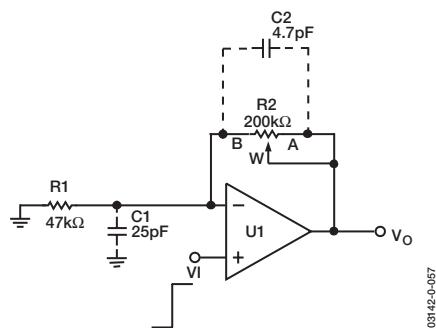

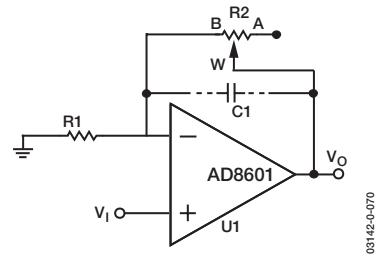

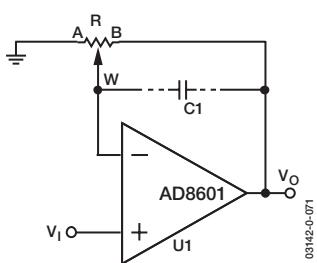

### ゲイン制御補償

デジタル・ポテンショメータは、図57に示す非反転ゲイン・アンプなどのゲイン制御でよく使用されます。

図57. 代表的な非反転ゲイン・アンプ

RDAC B端子の寄生容量がオペアンプの非反転ノードに接続されていることに注目してください。これによって、+20dB/dec を持つ $1/\beta_0$ 項にゼロが導入されますが、代表的なオペアンプ GBPには-20dB/decの特性があります。大きなR2と有限なC1によって、このゼロの周波数がクロスオーバー周波数をはるかに下回ることがあります。このため、クロージャのレートが40dB/decになり、システムはクロスオーバー周波数において0°位相マージンを備えることになります。入力が矩形パルスまたはステップ関数の場合、出力がリンギングしたり発振することがあります。同様に、2つのゲイン値を切り替えるときにも、入力でのステップ変化と等価になるため、リンギングが発生する可能性があります。

オペアンプのGBPにもよりますが、フィードバック抵抗を減らすと、ゼロの周波数が十分高くなつてこの問題を解決できることがあります。もっと良いのは、補償コンデンサC2を組み込んで、C1による効果を相殺する方法です。最適な補償が得られるのは $R1 \times C1 = R2 \times C2$ のときですが、R2が変動するため、この方法は利用できません。このため、上の関係を使用しながら、R2が最大値をとると仮定してC2の大きさを調整します。こうすると、補償が過度に行われて、R2に低い値が設定されたときに性能が若干低下することもあります。しかし、最悪の場合に、ゲイン・ピーキング、リンギング、発振を回避できます。クリティカルなアプリケーションでは、ニーズに合うC2値を経験的に探してください。一般に、補償には数pFから10分の数pF以下の範囲のC2で十分です。

同様に、出力（図には示されていません）にはWとAの端子容量も接続されています。幸いに、このノードでの効果はあまり重要ではなく、多くの場合補償は必要ありません。

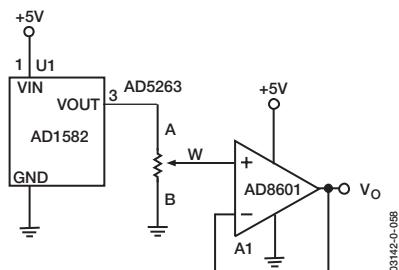

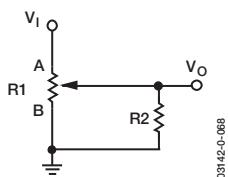

### プログラマブル・リファレンス

分圧器モード動作の場合（図58）、負荷が $R_{WB}$ よりずっと大きい場合を除き、デジタル・ポテンショメータの出力をバッファリングするのが普通です。バッファは、インピーダンス変換に役立つだけでなく、もっと大きい負荷の駆動も可能にします。

図58. プログラマブル・リファレンス

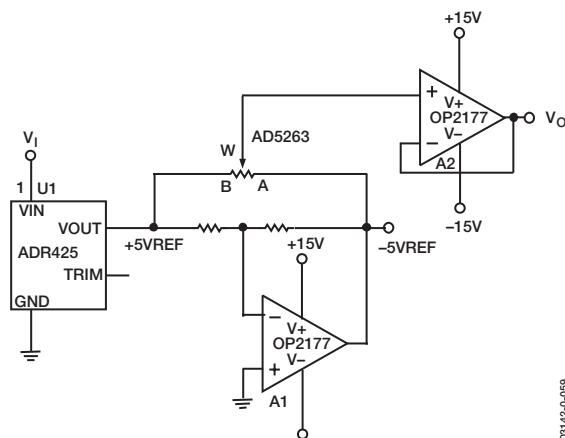

## 8ビットのバイポーラDAC

図59に、低価格の8ビットのバイポーラDACを示します。このバイポーラDACは、従来のDACと同じ数の調節可能なステップを提供しますが、精度は劣ります。デジタル・ポテンショメータのワイヤー抵抗の影響によって、特に低値コードで直線性と温度係数が歪められます。この回路の出力は次のとおりです。

$$V_o = \left( \frac{2D}{256} - 1 \right) \times V_{REF} \quad (5)$$

図59. 8ビットのバイポーラDAC

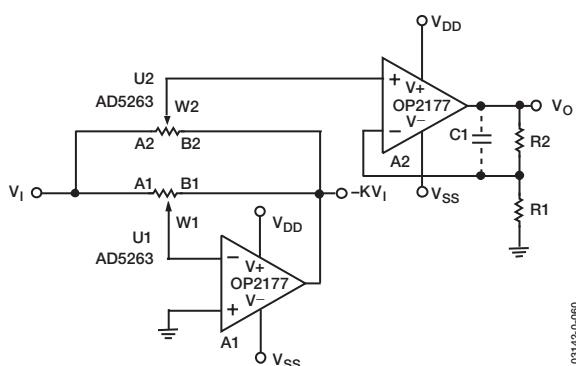

**バイポーラ・プログラマブル・ゲイン・アンプ**

バイポーラ・ゲインを必要とするアプリケーションについて、図60に前の回路に類似した実装形態を1つ示します。デジタル・ポテンショメータU1が、調整レンジを設定します。これにより、与えられたU2設定において $V_1 \sim -KV_1$ の間でW2でのワイヤー電圧をプログラムできます。A2を非反転モードで設定すると、直線的なゲインと減衰が得られます。伝達関数は次のとおりです。

$$V_o = \left( 1 + \frac{R2}{R1} \right) \times \left( \frac{D2}{256} \times (1 + K) - K \right) \quad (6)$$

ここで、KはU1によって設定された $R_{WB1}/R_{WA1}$ の比率です。

図60. バイポーラ・プログラマブル・ゲイン・アンプ

前の例と同様に、 $K=1$ という単純なケース（よくあるケース）では、単一のチャンネルを使用し、U1の代わりに整合した抵抗ペアによってデジタル・ポテンショメータの両端に $V_I$ と $-V_I$ を印加します。その関係を次に示します。

$$V_o = \left( 1 + \frac{R2}{R1} \right) \times \left( \frac{2 \times D2}{256} - 1 \right) \times V_I \quad (7)$$

$R2$ が大きい場合には、ゲイン・ピークリングを回避するために数pFの補償コンデンサが必要なこともあります。

表10には、A2をユニティ・ゲイン、2のゲイン、10のゲインで設定して、Dを調整した結果を示します。結果は、直線的でプログラマブルなゲインと256ステップの分解能を持つバイポーラ・アンプです。

表10. バイポーラ・ゲイン・アンプの結果

| D   | $R1 = \infty, R2 = 0$ | $R1 = R2$ | $R2 = 9 \times R1$ |

|-----|-----------------------|-----------|--------------------|

| 0   | -1                    | -2        | -10                |

| 64  | -0.5                  | -1        | -5                 |

| 128 | 0                     | 0         | 0                  |

| 192 | 0.5                   | 1         | 5                  |

| 255 | 0.968                 | 1.937     | 9.680              |

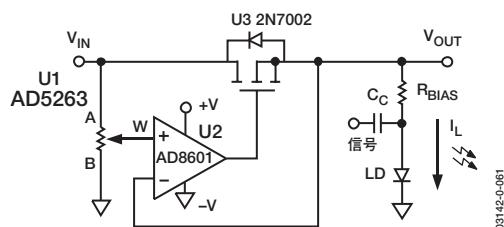

## ブースト出力を持つプログラマブルな電圧源

レーザー・ダイオード・ドライバや波長可変レーザーなど、大電流の調整を必要とするアプリケーションの場合には、ブースト電圧源を検討することができます。図61を参照してください。

図61. プログラマブルなブースター電圧源

この回路では、オペアンプの反転入力によって、 $V_{OUT}$ がデジタル・ポテンショメータによって設定されたワイヤー電圧と等しくなります。これによって、電源からNチャンネルのFET N1を介して負荷電流を供給します。N1の電力処理は、 $(V_{IN} - V_{OUT}) \times I_L$ に等しい電力消費に十分なものとする必要があります。この回路では、5V電源によって最大100mAを供給できます。高精度のアプリケーションでは、デジタル・ポテンショメータのA端子にADR421、ADR03、ADR370などのリファレンスを使用できます。

# AD5263

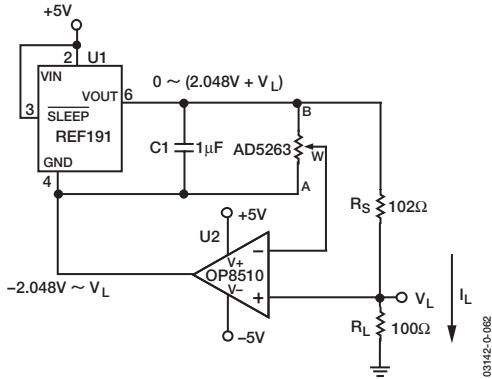

## 4~20mAのプログラマブルな電流源

図62に示す回路によって、4~20mAのプログラマブルな電流源を実装できます。REF191は、低電源ヘッドルームと大電流処理能力を備えたユニークな高精度リファレンスで、+2.048Vで20mAを供給できます。負荷電流は、デジタル・ポテンショメータの端子B/W間の電圧を $R_s$ で除算した値になります。

$$I_L = \frac{V_{REF} \times D}{R_s \times 2^N} \quad (8)$$

図62. 4~20mAのプログラマブルな電流源

この回路は単純ですが、2つの点に注意してください。まず、REF191のグラウンド電位がポテンショメータ設定のゼロスケールでの-2.048Vからフルスケールでの $V_L$ までスイングするため、両電源オペアンプが理想的という点です。回路は単電源でも動作しますが、システムのプログラマブル分解能は減少します。

大電流を必要とするアプリケーションの場合には、図62の回路を少し変更するだけで数百mAの範囲で調整可能な電流が得られます。まず、リファレンスをADP3333などの大電流のロードロップアウトのレギュレータに置き換え、オペアンプをAD8532などの大電流の両電源モデルと交換する必要があります。希望する電流範囲に応じて、適切な $R_s$ 値を計算する必要があります。負荷に大電流が流れるため、正側レールを超えてオペアンプを駆動しないように、負荷インピーダンスに注意する必要があります。

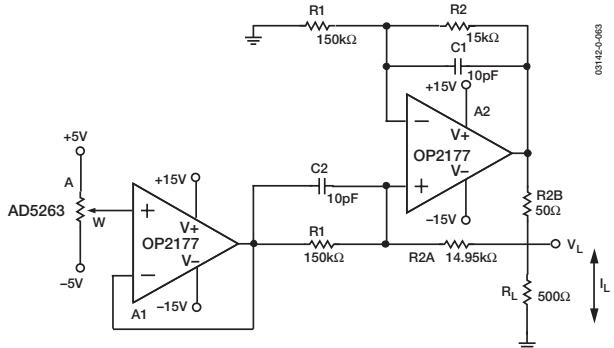

## プログラマブルな双向電流源

双向の電流制御や高い電圧コンプライアンスを必要とするアプリケーションの場合には、Howland社の電流ポンプが適しています（図63を参照）。抵抗が整合している場合には、負荷電流は次のとおりです。

$$I_L = \frac{(R2A + R2B) / R1}{R2B} \times V_W \quad (9)$$

図63. プログラマブルな双向電流源

理論上は、R2Bを必要なだけ小さくして、A2の出力電流駆動能力の範囲内で必要な電流を得ることができます。この回路では、OP2177はいずれの方向にも±5mAを供給でき、電圧コンプライアンスは+15Vに近づきます。出力インピーダンスは次のとおりです。

$$Z_o = \frac{R1' \times R2B (R1 + R2A)}{R1 \times R2' - R1' (R2A + R2B)} \quad (10)$$

抵抗R1' と R2' がそれぞれR1 と R2A + R2B に正しく整合する場合には、この出力インピーダンスは無限大になります。しかし、抵抗が整合しない場合には、出力インピーダンスが負になることもあります。その結果、発振を防ぐには1~10pFの範囲のC1が必要になります。

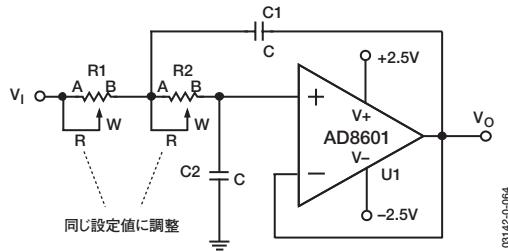

## プログラマブルなローパス・フィルタ

A/D変換アプリケーションでは、サンプリング信号を帯域制限するために、通常アンチエイリアシング・フィルタを組み込みます。デュアル・チャンネルのデジタル・ポテンショメータを使用すれば、二次のSallen-Keyローパス・フィルタを構築できます(図64を参照)。設計の式は次のとおりです。

$$\frac{V_o}{V_i} = \frac{\omega_o^2}{S^2 + \frac{\omega_o}{Q} S + \omega_o^2} \quad (11)$$

$$\omega_o = \sqrt{R_1 \times R_2 \times C_1 \times C_2} \quad (12)$$

$$Q = \frac{1}{R_1 \times C_1} + \frac{1}{R_2 \times C_2} \quad (13)$$

ユーザーは、最初にコンデンサに都合のよい値を選択できます。 $Q = 0.707$ で最大限に平坦な帯域幅を得るには、 $C_1$ を $C_2$ の2倍のサイズにし、 $R_1 = R_2$ にします。このようにして、ユーザーが $R_1$ と $R_2$ を同じ設定値に調整すれば、希望する帯域幅を得ることができます。

図64. Sallen-Keyローパス・フィルタ

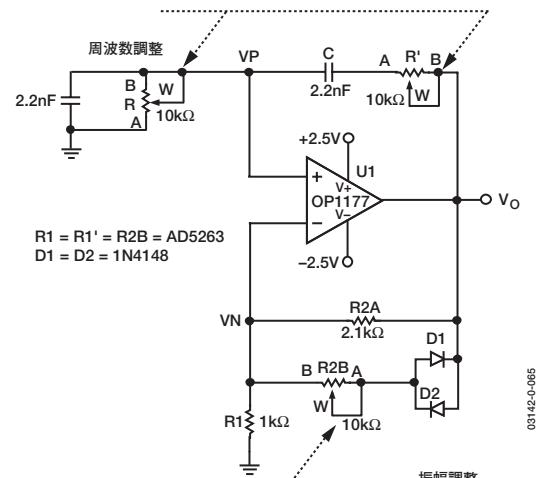

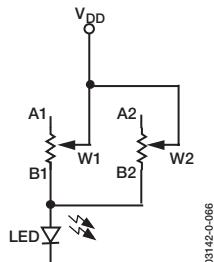

## プログラマブルな発振器

古典的なウェーンブリッジ発振器(図65)では、ウェーン・ネットワーク( $R$ 、 $R'$ 、 $C$ 、 $C'$ )が正のフィードバックを提供し、 $R_1$ と $R_2$ が負のフィードバックを提供します。共振周波数 $f_o$ で、全体的な位相シフトがゼロになり、正のフィードバックによって回路が発振します。

$R = R'$ 、 $C = C'$ 、 $R_2 = R_2A \parallel (R_2B + R_{\text{DIODE}})$ で、発振周波数は次のようになります。

$$\omega_o = \frac{1}{RC} \text{ または } f_o = \frac{1}{2\pi RC} \quad (14)$$

ここで、 $R$ は $R_{WA}$ に等しく、次のようになります。

$$R = \frac{256 - D}{256} R_{AB} \quad (15)$$

共振時に、次のように設定します。

$$\frac{R_2}{R_1} = 2 \quad (16)$$

これによって、ブリッジがバランスします。実際には、発振を確実に開始できるように、 $R_2/R_1$ には2より少し大きな値を設定してください。これに対し、ダイオードD1とD2を交互にオンにすると、 $R_2/R_1$ が瞬間に2より小さくなるため発振が安定します。

周波数を設定したら、発振振幅を $R_2B$ によって調整できます。これは、次の式が成立するためです。

$$\frac{2}{3} V_o = I_o \times R_2B + V_D \quad (17)$$

ここで、 $V_o$ 、 $I_o$ 、 $V_D$ は相互依存の変数です。 $R_2B$ を適切に選択すると、 $V_o$ が収束する均衡状態になります。 $R_2B$ を単体の抵抗と直列に配置して振幅を増やすことはできますが、出力が飽和するほど合計抵抗を大きくしてはいけません。

図65. 振幅制御によるプログラマブルな発振器

# AD5263

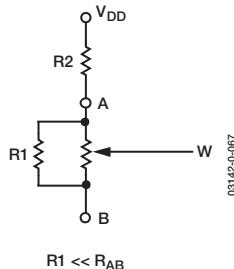

## 抵抗のスケーリング

AD5263は、20k $\Omega$ 、50k $\Omega$ 、200k $\Omega$ の公称抵抗を提供します。低い抵抗で、同じ数のステップ調整を必要とするユーザーの場合、複数のデバイスを並列に置くことができます。例として、図66に2つのチャンネルを並列に使用する単純な方法を示します。ステップごとに抵抗の半分を直線的に調整するには、両方のチャンネルに同じ設定値をプログラムする必要があります。

図66. 直線調整特性によって抵抗を半減する場合

分圧器モードに限りますが、図67に示すように、単体の抵抗を並列に接続することによって、それに比例した低い電圧が端子Aに生じます。端子Wでのステップ・サイズはさらに小さくなるので、精度をさらに向上させることになります。電圧は次のようになります。

$$V_W(D) = \frac{D}{256} \times \left( \frac{V_{DD}}{R2 + (R_{AB}||R_I)} \right) \times (R_{AB}||R_I) \quad (18)$$

図67. 公称抵抗を下げるステップ・サイズを減らす場合

図66と図67に示すアプリケーションでは、デジタル・ポテンショメータが直線的にステップを変更します。一方、ボリューム・コントロールなどのアプリケーションでは、一般に対数テバ調整が好まれます。図68に示すもう1つの抵抗スケーリング方法では、疑似対数テバ出力を生成します。この回路では、 $R_{AB}$ を基準にして $R2$ の値が小さくなればなるほど、出力が対数型に近づきます。

図68. 対数調整特性による抵抗のスケーリング

## 抵抗公差、ドリフト、温度係数の不整合に関する注意事項

図69に示すゲイン制御回路などの可変抵抗器モード動作では、デジタル・ポテンショメータと単体の抵抗との間の公差の不整合によって、さまざまなシステム間で再現性の問題が生じることがあります。シリコン・プロセスには本来的な整合性があるため、この種のアプリケーションでは、マルチチャンネル・デバイスが実際的です。この場合、R1をデジタル・ポテンショメータのチャンネルの1つに置き換えてください。R1には特定の値をプログラムし、R2は調節可能なゲインに使用します。この方法はコストを高くしますが、R1とR2との間の公差と温度係数の不整合を最小限に抑えることができます。さらに、この方法では、時間の経過とともに抵抗ドリフトを追跡できます。その結果、このような非理想パラメータも、システム変動に左右されにくくなります。

図69 抵抗公差とドリフトを追跡する線形ゲイン制御

なお、図70に示す回路を使用しても、このアプリケーションの公差、温度係数、ドリフトを追跡できます。ただし、伝達関数の特性は、線形から疑似対数ゲイン関数に変化します。

図70. 抵抗公差とドリフトを追跡する非線形ゲイン制御

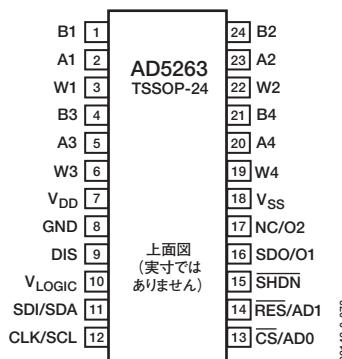

## ピン配置とピン機能の説明

## ピン配置

図71. 24ピンTSSOP

## ピン機能の説明

表11

| ピン | 名前                 | 説明                                                                                                                      |

|----|--------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1  | B1                 | 抵抗端子B1                                                                                                                  |

| 2  | A1                 | 抵抗端子A1 (ADDR=00)                                                                                                        |

| 3  | W1                 | ワイヤー端子W1                                                                                                                |

| 4  | B3                 | 抵抗端子B3                                                                                                                  |

| 5  | A3                 | 抵抗端子A3                                                                                                                  |

| 6  | W3                 | ワイヤー端子W3 (ADDR=10)                                                                                                      |

| 7  | V <sub>DD</sub>    | 正電源、+5~+15Vの動作仕様                                                                                                        |

| 8  | GND                | グラウンド                                                                                                                   |

| 9  | DIS                | デジタル・インターフェース・セレクト (SPI/I <sup>2</sup> C選択)。<br>DIS=0のときSPI、DIS=1のときI <sup>2</sup> Cになります。                              |

| 10 | V <sub>LOGIC</sub> | 2.7~5.5Vのロジック電源電圧。ロジック電源電圧は、必ずV <sub>DD</sub> 以下にしてください。<br>さらに、V <sub>DD</sub> の値にかかわらず、ロジック・レベルをロジック電源電圧に制限する必要があります。 |

| 11 | SDI/SDA            | SDI=3線式シリアル・データ入力。SDA=2線式シリアル・データ入／出力。                                                                                  |

| 12 | CLK/SCL            | シリアル・クロック入力                                                                                                             |

| 13 | CS/AD0             | SPIモードでチップ・セレクト。I <sup>2</sup> Cモードでデバイス・アドレス・ビット0。                                                                     |

| 14 | RES/AD1            | SPIモードでリセット。I <sup>2</sup> Cモードでデバイス・アドレス・ビット1。                                                                         |

| 15 | SHDN               | シャットダウン。ワイヤーを端子Bに短絡し、端子Aを開きます。使用しない場合は+5V電源に接続します。V <sub>DD</sub> >5Vの場合はV <sub>DD</sub> に接続しないでください。                   |

| 16 | SDO/O1             | SPIモードではシリアル・データ出力で、オープンドレイン・トランジスタにはプルアップ抵抗が必要です。I <sup>2</sup> Cモードではデジタル出力O1で、外部ロジックの駆動に使用できます。                      |

| 17 | NC/O2              | SPIモードでは非接続。I <sup>2</sup> Cモードではデジタル出力O2で、外部ロジックの駆動に使用できます。                                                            |

| 18 | V <sub>SS</sub>    | -5~0Vの動作仕様の負電源                                                                                                          |

| 19 | W4                 | ワイヤー端子W4 (ADDR=11)                                                                                                      |

| 20 | A4                 | 抵抗端子A4                                                                                                                  |

| 21 | B4                 | 抵抗端子B4                                                                                                                  |

| 22 | W2                 | ワイヤー端子W2 (ADDR=01)                                                                                                      |

| 23 | A2                 | 抵抗端子A2                                                                                                                  |

| 24 | B2                 | 抵抗端子B2                                                                                                                  |

# AD5263

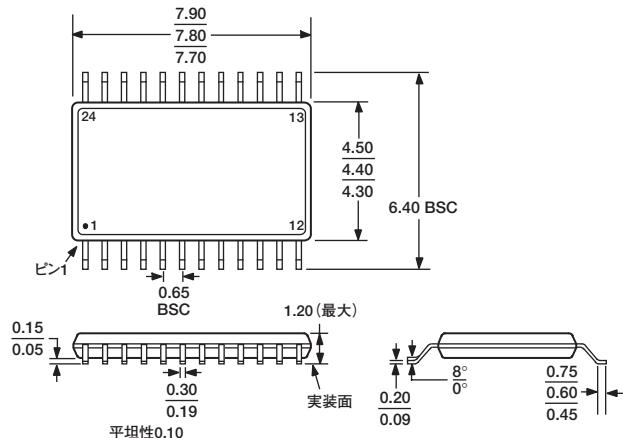

## 外形寸法

図72. 24ピン薄型シュリンク・スモール・アウトライン・パッケージ[TSSOP]

(RU-24)

寸法はミリメートルで表示

### ESDに関する注意

ESD（静電放電）の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されます。本製品は当社独自のESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

## オーダーガイド

表12

| モデル <sup>1</sup>   | $R_{AB}$ (k $\Omega$ ) | 温度         | パッケージ    | パッケージ・オプション | 製品パッケージ当たりの部品数 |

|--------------------|------------------------|------------|----------|-------------|----------------|

| AD5263BRU20        | 20                     | -40~+125°C | TSSOP-24 | RU-24       | 62             |

| AD5263BRU20-REEL7  | 20                     | -40~+125°C | TSSOP-24 | RU-24       | 1,000          |

| AD5263BRU50        | 50                     | -40~+125°C | TSSOP-24 | RU-24       | 62             |

| AD5263BRU50-REEL7  | 50                     | -40~+125°C | TSSOP-24 | RU-24       | 1,000          |

| AD5263BRU200       | 200                    | -40~+125°C | TSSOP-24 | RU-24       | 62             |

| AD5263BRU200-REEL7 | 200                    | -40~+125°C | TSSOP-24 | RU-24       | 1,000          |

| AD5263EVAL         | 注2を参照                  |            | 評価ボード    |             |                |

<sup>1</sup> パッケージ表示：1行目にはモデル番号、2行目にはエンド・ツー・エンド抵抗、3行目には日付コードYYWWが記載されています。

<sup>2</sup> 評価ボードは20k $\Omega$ の $R_{AB}$ 抵抗オプションに同梱されています。ただし、この評価ボードは、使用可能なすべての抵抗値オプションに対応しています。

AD5263には5,184個のトランジスタが含まれています。チップ・サイズ：108ミル×198ミル=21,384平方ミル

**AD5263**

**AD5263**

C03142-0-6/03(0)

PRINTED IN JAPAN