## AD5024/AD5044/AD5064

### 特長

INL  $\pm 1$  LSB の低消費電力クワッド 12/14/16 ビット DAC

リファレンス電圧ピンが個別 /共通使用可能

レール to レール動作

電源電圧: 4.5 V~5.5 V

パワー・オン時にゼロ/ミッド・スケールにリセット

3種類のパワーダウン機能

チャンネルごとのパワーダウン機能

パワー・アップ時に低グリッチ

ハードウェア LDAC、LDAC優先機能

プログラマブルなコードのCLR機能

16 ピンの TSSOP を採用

リファレンス電圧バッファと出力アンプを内蔵

### アプリケーション

プロセス制御

データ・アクイジション・システム

携帯型バッテリ駆動の計装機器

ゲインとオフセットのデジタル調整

プログラマブルな電圧源と電流源

プログラマブルな減衰器

表 1. 関連デバイス

| Part No.      | Description                                |

|---------------|--------------------------------------------|

| AD5666        | Quad,16-bit buffered DAC,16 LSB INL, TSSOP |

| AD5063/AD5062 | 16-bit nanoDAC, 1 LSB INL                  |

| AD5061        | 16-/14-bit nanoDAC, 4 LSB INL, SOT-23      |

| AD5060/AD5040 | 16-/14-bit nanoDAC, 1 LSB INL, SOT-23      |

### 概要

AD5024/AD5044/AD5064 は、INL1 LSB の相対精度仕様と個別リファレンス・ピンを持ち、4.5 V~5.5 V の単電源で動作できる低消費電力のクワッド 12/14/16 ビット・バッファ付き電圧出力 nanoDAC® DAC です。また、AD5024/AD5044/AD5064 デバイスは $\pm 1$  LSB の差動精度仕様を持っています。このデバイスは、最大 50 MHz のクロック・レートで動作し、かつ標準 SPI、QSPI™、MICROWIRE™、DSP インターフェースの各規格と互換性を持つ多機能の低消費電力 3 線式シリアル・インターフェースを内蔵しています。リファレンス・バッファも内蔵しています。AD5024/AD5044/AD5064 は、パワー・オン・リセット回路を内蔵しており、この回路により、パワー・アップ時に DAC 出力を 0 V またはミッドスケールにし、デバイスに対する有効な書き込みが行われるまでこの出力電圧を維持することができます。AD5024/AD5044/AD5064 は消費電流を 5 V で 400  $\mu$ A (typ)まで削減するパワーダウン機能を内蔵し、さらにパワーダウン・モードではソフトウェアから選択可能な出力負荷を提供します。デバイスの未調整総合誤差は、2 mV 以下です。

### 製品のハイライト

- 16 ピン TSSOP パッケージで 4 チャンネルを提供。

- 16 ビット精度、INL: 1 LSB。

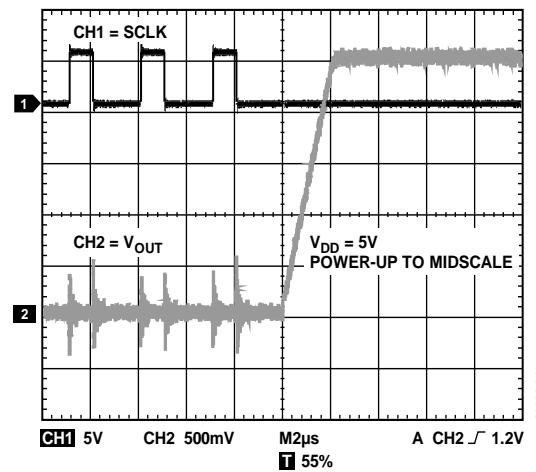

- パワー・アップ時に低グリッチ

- 最大 50 MHz のクロック速度を持つ高速シリアル・インターフェースを内蔵。

- 出力電圧をゼロスケールまたはミッドスケールにリセット。

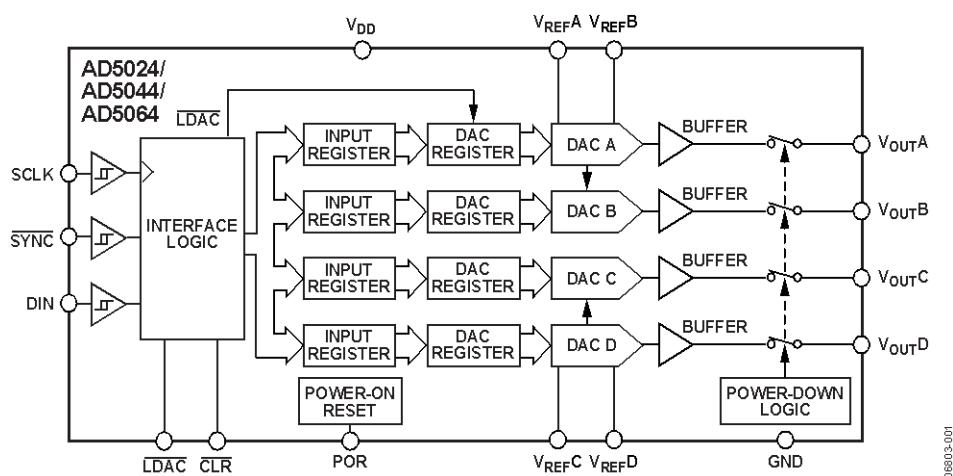

### 機能ブロック図

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2008 Analog Devices, Inc. All rights reserved.

# 目次

|               |    |                                             |    |

|---------------|----|---------------------------------------------|----|

| 特長            | 1  | 出力アンプ                                       | 18 |

| アプリケーション      | 1  | シリアル・インターフェース                               | 18 |

| 概要            | 1  | スタンドアロン・モード                                 | 18 |

| 製品のハイライト      | 1  | 入力シフトレジスタ                                   | 18 |

| 機能ブロック図       | 1  | <u>SYNC</u> 割り込み                            | 19 |

| 改訂履歴          | 2  | パワー・オン・リセット                                 | 20 |

| 仕様            | 3  | パワーダウン・モード                                  | 20 |

| AC 特性         | 5  | クリア・コード・レジスタ                                | 21 |

| タイミング特性       | 6  | <u>LDAC</u> 機能                              | 21 |

| 絶対最大定格        | 7  | 電源のバイパスとグラウンド接続                             | 21 |

| ESD の注意       | 7  | マイクロプロセッサ・インターフェース                          | 23 |

| ピン配置およびピン機能説明 | 8  | アプリケーション                                    | 24 |

| 代表的な性能特性      | 9  | リファレンス電圧の電源としての使用                           | 24 |

| 用語            | 16 | バイポーラ動作                                     | 24 |

| 動作原理          | 18 | AD5024/AD5044/AD5064 の電流絶縁型インターフェースでの<br>使用 | 24 |

| DAC セクション     | 18 | 外形寸法                                        | 25 |

| DAC アーキテクチャ   | 18 | オーダー・ガイド                                    | 25 |

| リファレンス電圧バッファ  | 18 |                                             |    |

## 改訂履歴

8/08—Revision 0: Initial Version

## 仕様

特に指定のない限り、 $V_{DD} = 4.5 \text{ V} \sim 5.5 \text{ V}$ 、 $R_L = 5 \text{ k}\Omega$  (GND に接続)、 $C_L = 200 \text{ pF}$  (GND に接続)、 $2.5 \text{ V} \leq V_{REFIN} \leq V_{DD}$ 。特に指定のない限り、すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

表 2.

| Parameter                                 | B Grade <sup>1</sup> |            |             | A Grade <sup>2</sup> |                              |                                                                                                                                                | Unit | Conditions/Comments |

|-------------------------------------------|----------------------|------------|-------------|----------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|

|                                           | Min                  | Typ        | Max         | Min                  | Typ                          | Max                                                                                                                                            |      |                     |

| <b>STATIC PERFORMANCE<sup>3</sup></b>     |                      |            |             |                      |                              |                                                                                                                                                |      |                     |

| Resolution                                | 16                   |            | 16          |                      |                              |                                                                                                                                                | Bits | AD5064              |

|                                           | 14                   |            |             |                      |                              |                                                                                                                                                |      | AD5044              |

|                                           | 12                   |            |             |                      |                              |                                                                                                                                                |      | AD5024              |

| Relative Accuracy                         | $\pm 0.5$            | $\pm 1$    | $\pm 0.5$   | $\pm 4$              | LSB                          | AD5064; $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$                                                                               |      |                     |

|                                           | $\pm 0.5$            | $\pm 2$    | $\pm 0.5$   | $\pm 4$              |                              | AD5064; $T_A = -40^\circ\text{C} \text{ to } +125^\circ\text{C}$                                                                               |      |                     |

|                                           | $\pm 0.25$           | $\pm 0.5$  |             |                      | LSB                          | AD5044; $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$                                                                               |      |                     |

|                                           | $\pm 0.25$           | $\pm 1$    |             |                      |                              | AD5044; $T_A = -40^\circ\text{C} \text{ to } +125^\circ\text{C}$                                                                               |      |                     |

|                                           | $\pm 0.12$           | $\pm 0.25$ |             |                      | LSB                          | AD5024; $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$                                                                               |      |                     |

|                                           | $\pm 0.12$           | $\pm 0.5$  |             |                      |                              | AD5024; $T_A = -40^\circ\text{C} \text{ to } +125^\circ\text{C}$                                                                               |      |                     |

| Differential Nonlinearity                 | $\pm 0.2$            | $\pm 1$    | $\pm 0.2$   | $\pm 1$              | LSB                          |                                                                                                                                                |      |                     |

| Offset Error                              | $\pm 0.2$            | $\pm 1.8$  | $\pm 0.2$   | $\pm 1.8$            | mV                           | Code 512 (AD5064), Code 128 (AD5044), Code 32 (AD5024) loaded to DAC register                                                                  |      |                     |

| Offset Error Drift <sup>4</sup>           | $\pm 2$              |            | $\pm 2$     |                      | $\mu\text{V}/^\circ\text{C}$ |                                                                                                                                                |      |                     |

| Full-Scale Error                          | $\pm 0.01$           | $\pm 0.07$ | $\pm 0.01$  | $\pm 0.07$           | % FSR                        | All 1s loaded to DAC register. $V_{REF} < V_{DD}$                                                                                              |      |                     |

| Gain Error                                | $\pm 0.005$          | $\pm 0.05$ | $\pm 0.005$ | $\pm 0.05$           | % FSR                        |                                                                                                                                                |      |                     |

| Gain Temperature Coefficient <sup>4</sup> | $\pm 1$              |            | $\pm 1$     |                      | ppm                          | Of FSR/°C                                                                                                                                      |      |                     |

| DC Crosstalk                              | 40                   |            | 40          |                      | $\mu\text{V}$                | Due to single channel full-scale output change, $R_L = 5 \text{ k}\Omega$ to GND or $V_{DD}$                                                   |      |                     |

|                                           | 40                   |            | 40          |                      | $\mu\text{V}/\text{mA}$      | Due to load current change                                                                                                                     |      |                     |

|                                           | 0.5                  |            | 40          |                      | $\mu\text{V}$                | Due to powering down (per channel)                                                                                                             |      |                     |

| <b>OUTPUT CHARACTERISTICS<sup>4</sup></b> |                      |            |             |                      |                              |                                                                                                                                                |      |                     |

| Output Voltage Range                      | 0                    | $V_{DD}$   | 0           | $V_{DD}$             | V                            |                                                                                                                                                |      |                     |

| Capacitive Load Stability                 | 1                    |            | 1           |                      | nF                           | $R_L = 5 \text{ k}\Omega$ , $R_L = 100 \text{ k}\Omega$ , and $R_L = \infty$                                                                   |      |                     |

| DC Output Impedance                       |                      |            |             |                      | $\Omega$                     |                                                                                                                                                |      |                     |

| Normal Mode                               | 0.5                  |            | 0.5         |                      |                              |                                                                                                                                                |      |                     |

| Power-Down Mode                           |                      |            |             |                      |                              |                                                                                                                                                |      |                     |

| Output Connected to 100 kΩ Network        | 100                  |            | 100         |                      | kΩ                           | Output impedance tolerance $\pm 400 \Omega$                                                                                                    |      |                     |

| Output Connected to 1 kΩ Network          | 1                    |            | 1           |                      | kΩ                           | Output impedance tolerance $\pm 20 \Omega$                                                                                                     |      |                     |

| Short-Circuit Current                     | 60                   |            | 60          |                      | mA                           | DAC = full scale, output shorted to GND                                                                                                        |      |                     |

|                                           | 45                   |            | 45          |                      | mA                           | DAC = zero-scale, output shorted to $V_{DD}$                                                                                                   |      |                     |

| Power-Up Time                             | 4.5                  |            | 4.5         |                      | μs                           | Time to exit power-down mode to normal mode of AD5024/AD5044/AD5064, 32 <sup>nd</sup> clock edge to 90% of DAC midscale value, output unloaded |      |                     |

| DC PSRR                                   | -92                  |            | -92         |                      | dB                           | $V_{DD} \pm 10\%$ , DAC = full scale. $V_{REF} < V_{DD}$                                                                                       |      |                     |

| <b>REFERENCE INPUTS</b>                   |                      |            |             |                      |                              |                                                                                                                                                |      |                     |

| Reference Input Range                     | 2.5                  | $V_{DD}$   | 2.5         | $V_{DD}$             | V                            |                                                                                                                                                |      |                     |

| Reference Current                         | 35                   | 50         | 35          | 50                   | μA                           | Per DAC channel                                                                                                                                |      |                     |

| Reference Input Impedance                 | 120                  |            | 120         |                      | kΩ                           | Individual reference option                                                                                                                    |      |                     |

| <b>LOGIC INPUTS</b>                       |                      |            |             |                      |                              |                                                                                                                                                |      |                     |

| Input Current <sup>5</sup>                |                      | $\pm 1$    |             | $\pm 1$              | $\mu\text{A}$                |                                                                                                                                                |      |                     |

| Input Low Voltage, $V_{IL}$               |                      | 0.8        |             | 0.8                  | V                            |                                                                                                                                                |      |                     |

| Input High Voltage, $V_{IH}$              | 2.2                  |            | 2.2         |                      | V                            |                                                                                                                                                |      |                     |

| Pin Capacitance <sup>4</sup>              | 4                    |            | 4           |                      | pF                           |                                                                                                                                                |      |                     |

| <b>POWER REQUIREMENTS</b>                 |                      |            |             |                      |                              |                                                                                                                                                |      |                     |

| $V_{DD}$                                  | 4.5                  | 5.5        | 4.5         | 5.5                  | V                            | DAC active, excludes load current                                                                                                              |      |                     |

| $I_{DD}$ <sup>6</sup>                     |                      |            |             |                      |                              | $V_{IH} = V_{DD}$ and $V_{IL} = \text{GND}$                                                                                                    |      |                     |

| Normal Mode                               | 3                    | 6          | 3           | 6                    | mA                           |                                                                                                                                                |      |                     |

| All Power-Down Modes <sup>7</sup>         | 0.4                  | 2          | 0.4         | 2                    | μA                           | $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$                                                                                       |      |                     |

|                                           |                      | 30         |             | 30                   | μA                           | $T_A = -40^\circ\text{C} \text{ to } +125^\circ\text{C}$                                                                                       |      |                     |

<sup>1</sup> 25°Cでの温度範囲(typ)は、-40°C～+125°C。

<sup>2</sup> AグレードはAD5064のみ提供。

<sup>3</sup> 直線性はコード範囲を縮小して計算—AD5064:コード512～コード65,024、AD5044:コード128～コード16,256、AD5024:コード32～コード4096。出力は無負荷。

<sup>4</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

<sup>5</sup> 各々のデジタル・ピンに流入する電流。

<sup>6</sup> インターフェースは非アクティブ状態。すべてのDACはアクティブ状態。DAC出力は無負荷。

<sup>7</sup> 4個すべてのDACがパワーダウン。

## AC 特性

$V_{DD} = 4.5 \text{ V} \sim 5.5 \text{ V}$ 、 $R_L = 5 \text{ k}\Omega$  (GND に接続)、 $C_L = 200 \text{ pF}$  (GND に接続)、 $2.5 \text{ V} \leq V_{REFIN} \leq V_{DD}$ 。特に指定のない限り、すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

表 3.

| Parameter <sup>1,2</sup>         | Min  | Typ | Max | Unit   | Conditions/Comments <sup>3</sup>                                                                                                                                                                     |

|----------------------------------|------|-----|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

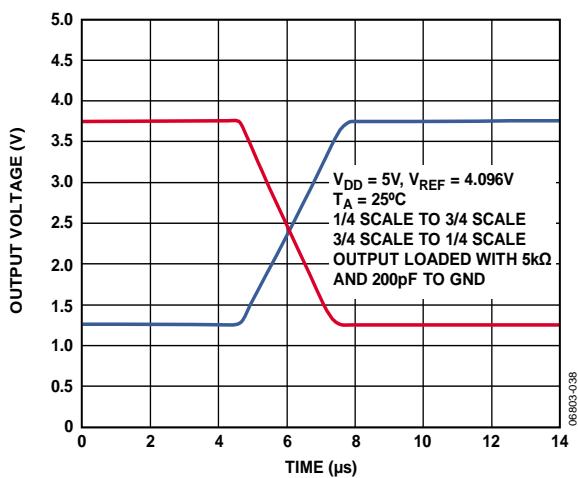

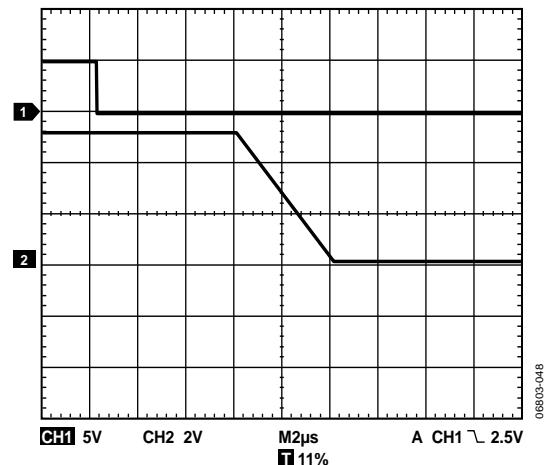

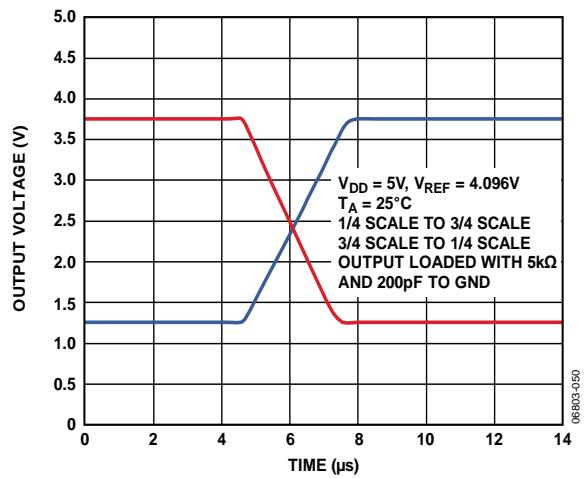

| Output Voltage Settling Time     | 5.8  | 8   |     | μs     | $\frac{1}{4}$ to $\frac{3}{4}$ scale and $\frac{3}{4}$ to $\frac{1}{4}$ scale settling to $\pm 1 \text{ LSB}$ , $R_L = 5 \text{ k}\Omega$ , single channel update including DAC calibration sequence |

|                                  | 10.7 | 13  |     | μs     | $\frac{1}{4}$ to $\frac{3}{4}$ scale and $\frac{3}{4}$ to $\frac{1}{4}$ scale settling to $\pm 1 \text{ LSB}$ , $R_L = 5 \text{ k}\Omega$ , all channel update including DAC calibration sequence    |

| Slew Rate                        | 1.5  |     |     | V/μs   |                                                                                                                                                                                                      |

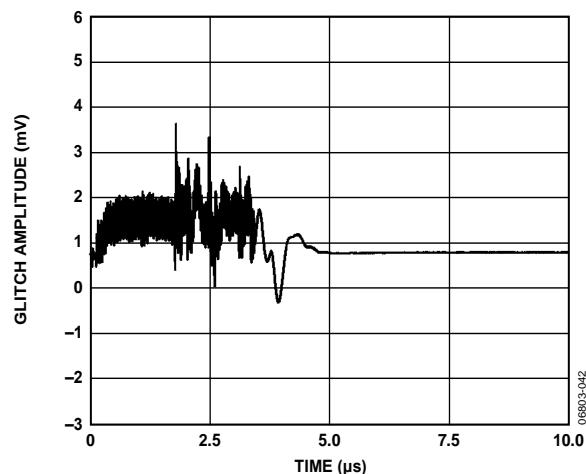

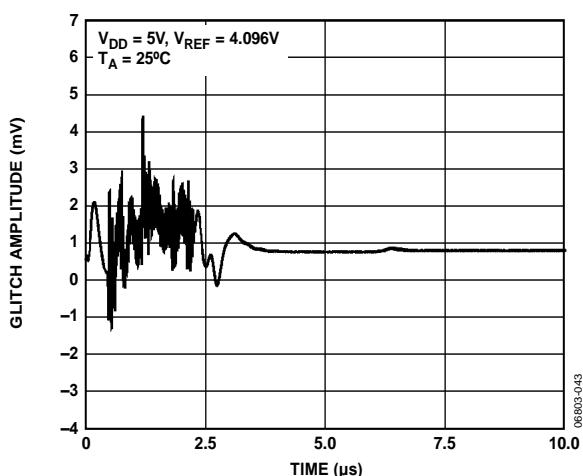

| Digital-to-Analog Glitch Impulse | 3    |     |     | nV-s   | 1 LSB change around major carry                                                                                                                                                                      |

| Reference Feedthrough            | -90  |     |     | dB     | $V_{REF} = 3 \text{ V} \pm 0.86 \text{ V p-p}$ , frequency = 100 Hz to 100 kHz                                                                                                                       |

| Digital Feedthrough              | 0.1  |     |     | nV-s   |                                                                                                                                                                                                      |

| Digital Crosstalk                | 1.9  |     |     | nV-s   |                                                                                                                                                                                                      |

| Analog Crosstalk                 | 2    |     |     | nV-s   |                                                                                                                                                                                                      |

| DAC-to-DAC Crosstalk             | 3.5  |     |     | nV-s   |                                                                                                                                                                                                      |

| AC Crosstalk                     | 6    |     |     | nV-s   |                                                                                                                                                                                                      |

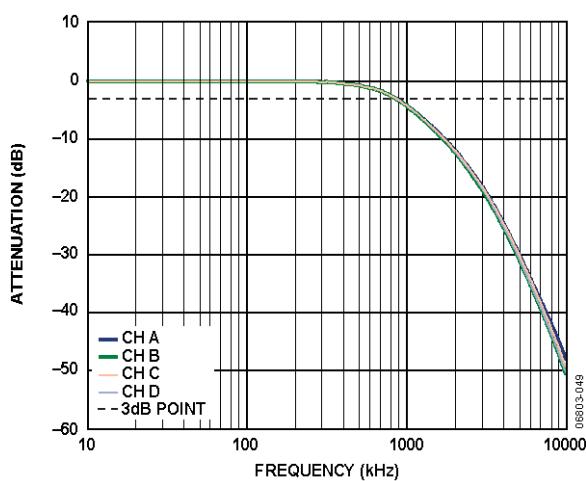

| Multiplying Bandwidth            | 340  |     |     | kHz    | $V_{REF} = 3 \text{ V} \pm 0.86 \text{ V p-p}$                                                                                                                                                       |

| Total Harmonic Distortion        | -80  |     |     | dB     | $V_{REF} = 3 \text{ V} \pm 0.2 \text{ V p-p}$ , frequency = 10 kHz                                                                                                                                   |

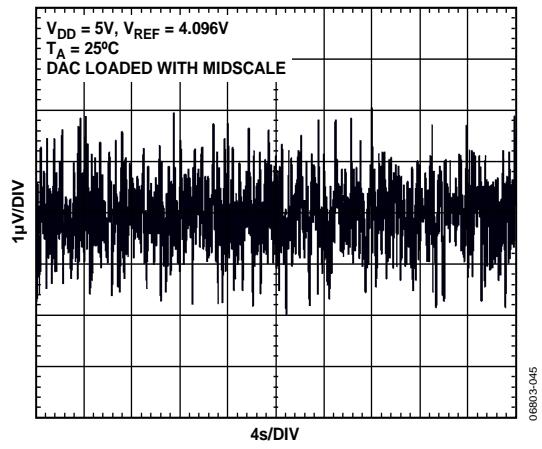

| Output Noise Spectral Density    | 64   |     |     | nV/√Hz | DAC code = 0x8400, 1 kHz                                                                                                                                                                             |

|                                  | 60   |     |     | nV/√Hz | DAC code = 0x8400, 10 kHz                                                                                                                                                                            |

| Output Noise                     | 6    |     |     | μV p-p | 0.1 Hz to 10 Hz                                                                                                                                                                                      |

<sup>1</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

<sup>2</sup> 用語のセクション参照。

<sup>3</sup> 25°Cでの温度範囲(typ)は、-40°C～+125°C。

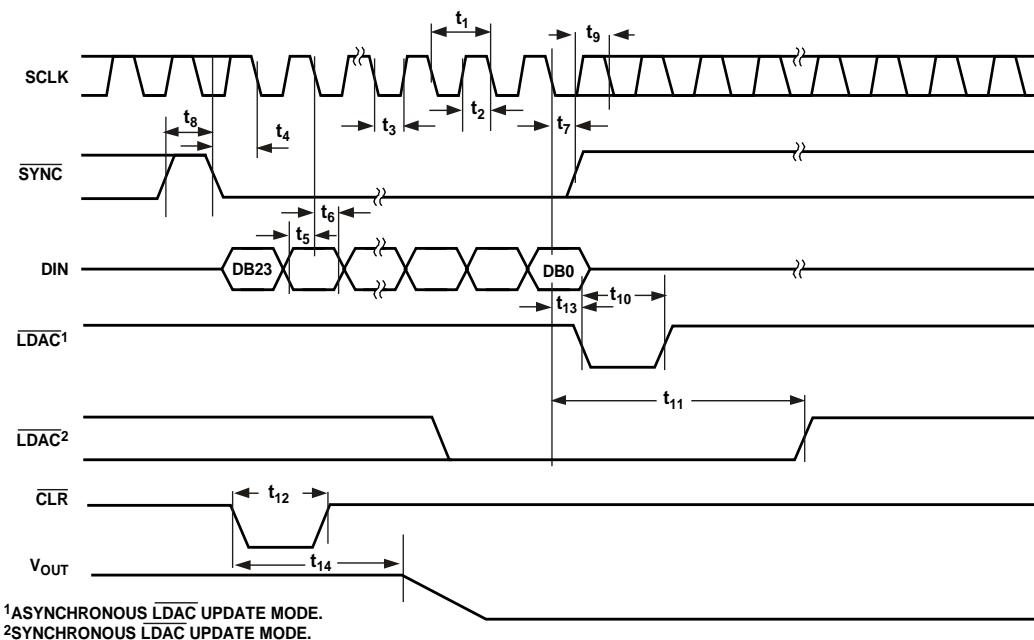

## タイミング特性

すべての入力信号は  $t_r = t_f = 1$  ns ( $V_{DD}$  の 10% から 90%) で規定し、 $(V_{IL} + V_{IH})/2$  の電圧レベルからの時間とします。図 2 を参照してください。 $V_{DD} = 4.5 \sim 5.5$  V。特に指定のない限り、すべての仕様は  $T_{MIN} \sim T_{MAX}$  で規定。

表 4.

| Parameter <sup>1</sup> | Limit at $T_{MIN}, T_{MAX}$ ;<br>$V_{DD} = 4.5$ V to 5.5 V | Unit        | Conditions/Comments                                         |

|------------------------|------------------------------------------------------------|-------------|-------------------------------------------------------------|

| $t_1$                  | 20                                                         | ns min      | SCLK cycle time                                             |

| $t_2$                  | 10                                                         | ns min      | SCLK high time                                              |

| $t_3$                  | 10                                                         | ns min      | SCLK low time                                               |

| $t_4$                  | 16.5                                                       | ns min      | $\overline{SYNC}$ to SCLK falling edge setup time           |

| $t_5$                  | 5                                                          | ns min      | Data setup time                                             |

| $t_6$                  | 5                                                          | ns min      | Data hold time                                              |

| $t_7$                  | 0                                                          | ns min      | SCLK falling edge to $\overline{SYNC}$ rising edge          |

| $t_8$                  | 1.9                                                        | $\mu$ s min | Minimum $\overline{SYNC}$ high time (single channel update) |

|                        | 10.5                                                       | $\mu$ s min | Minimum $\overline{SYNC}$ high time (all channel update)    |

| $t_9$                  | 17                                                         | ns min      | $\overline{SYNC}$ rising edge to SCLK fall ignore           |

| $t_{10}$               | 20                                                         | ns min      | $\overline{LDAC}$ pulse width low                           |

| $t_{11}$               | 20                                                         | ns min      | SCLK falling edge to $\overline{LDAC}$ rising edge          |

| $t_{12}$               | 10                                                         | ns min      | $\overline{CLR}$ pulse width low                            |

| $t_{13}$               | 10                                                         | ns min      | SCLK falling edge to $\overline{LDAC}$ falling edge         |

| $t_{14}$               | 10.6                                                       | $\mu$ s min | $\overline{CLR}$ pulse activation time                      |

<sup>1</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

図 2. シリアル書き込み動作

## 絶対最大定格

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 5.

| Parameter                                   | Rating                                 |

|---------------------------------------------|----------------------------------------|

| $V_{DD}$ to GND                             | -0.3 V to +7 V                         |

| Digital Input Voltage to GND                | -0.3 V to $V_{DD} + 0.3$ V             |

| $V_{OUT}$ to GND                            | -0.3 V to $V_{DD} + 0.3$ V             |

| $V_{REF}$ to GND                            | -0.3 V to $V_{DD} + 0.3$ V             |

| Operating Temperature Range<br>Industrial   | -40°C to +125°C                        |

| Storage Temperature Range                   | -65°C to +150°C                        |

| Junction Temperature ( $T_{J\text{ MAX}}$ ) | 150°C                                  |

| TSSOP Package                               |                                        |

| Power Dissipation                           | $(T_{J\text{ MAX}} - T_A)/\theta_{JA}$ |

| $\theta_{JA}$ Thermal Impedance             | 113°C/W                                |

| Reflow Soldering Peak Temperature           |                                        |

| Pb Free                                     | 260°C                                  |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の節に記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## ESD の注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

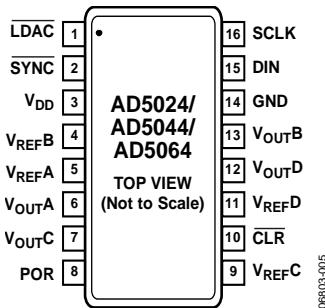

## ピン配置およびピン機能説明

図 3.16 ピン TSSOP (RU-16)のピン配置

表 6. ピン機能の説明

| ピン番号 | 記号                | 説明                                                                                                                                                                                                                       |

|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | LDAC              | このピンにロー・レベルのパルスを入力すると、入力レジスタに新しいデータが存在する場合、任意またはすべてのDACレジスタを更新することができます。この信号を使うと、全DAC出力を同時に更新することができます。あるいは、外部でロー・レベルに固定することもできます。                                                                                       |

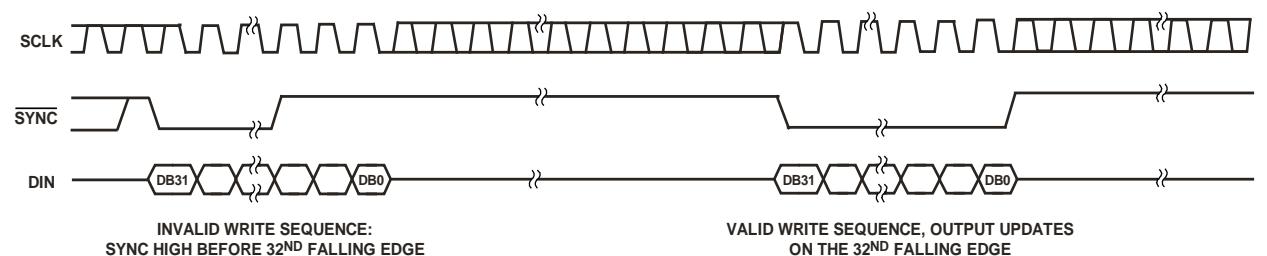

| 2    | SYNC              | アクティブ・ローのコントロール入力。これは、入力データに対するフレーム同期信号です。SYNCがロー・レベルになると、SCLKバッファとDINバッファがパワー・オンし、入力シフトレジスタがイネーブルされます。データは、次のクロックの32個の立ち下がりエッジで転送されます。32番目の立ち下がりエッジの前にSYNCをハイ・レベルにすると、SYNCの立ち上がりエッジは割り込みとして機能するため、デバイスは書き込みシーケンスを無視します。 |

| 3    | V <sub>DD</sub>   | 電源入力。これらのデバイスは4.5 V～5.5 Vで動作し、電源は10 μFのコンデンサと0.1 μFのコンデンサとの並列接続によりGNDへデカッピングする必要があります。                                                                                                                                   |

| 4    | V <sub>REFB</sub> | DAC Bのリファレンス電圧入力。これは、DAC Bのリファレンス電圧入力ピンです。                                                                                                                                                                               |

| 5    | V <sub>REFA</sub> | DAC Aのリファレンス電圧入力。これは、DAC Aのリファレンス電圧入力ピンです。                                                                                                                                                                               |

| 6    | V <sub>OUTA</sub> | DAC Aのアナログ電圧出力。出力アンプはレールtoレールの動作を行います。                                                                                                                                                                                   |

| 7    | V <sub>OUTC</sub> | DAC Cのアナログ電圧出力。出力アンプはレールtoレールの動作を行います。                                                                                                                                                                                   |

| 8    | POR               | パワー・オン・リセット。このピンをGNDに接続すると0 Vから、V <sub>DD</sub> に接続するとミッドスケールから、それぞれデバイスがパワーアップします。                                                                                                                                      |

| 9    | V <sub>REFC</sub> | DAC Cのリファレンス電圧入力。これは、DAC Cのリファレンス電圧入力ピンです。                                                                                                                                                                               |

| 10   | CLR               | 非同期のクリア入力。CLR入力は、立ち下がりエッジで検出されます。CLRがロー・レベルの間、すべてのLDACパルスは無視されます。CLRが入力されると、入力レジスタとDACレジスタは、CLRコード・レジスタに格納されているデータ(ゼロ、ミッドスケール、またはフルスケール)で更新されます。デフォルト設定では、出力は0 Vにクリアされます。                                                |

| 11   | V <sub>REFD</sub> | DAC Dのリファレンス電圧入力。これはDAC Dのリファレンス電圧入力ピンです。                                                                                                                                                                                |

| 12   | V <sub>OUTD</sub> | DAC Dのアナログ電圧出力。出力アンプはレールtoレールの動作を行います。                                                                                                                                                                                   |

| 13   | V <sub>OUTB</sub> | DAC Bのアナログ電圧出力。出力アンプはレールtoレールの動作を行います。                                                                                                                                                                                   |

| 14   | GND               | デバイス上の全回路に対するグラウンドリファレンス電圧ポイント。                                                                                                                                                                                          |

| 15   | DIN               | シリアル・データ入力。このデバイスは、32ビットのシフト・レジスタを内蔵しています。データは、シリアル・クロック入力の立ち下がりエッジでレジスタに入力されます。                                                                                                                                         |

| 16   | SCLK              | シリアル・データ入力。データは、シリアル・クロック入力の立ち下がりエッジでシフト・レジスタに入力されます。データは最大50 MHzのレートで転送できます。                                                                                                                                            |

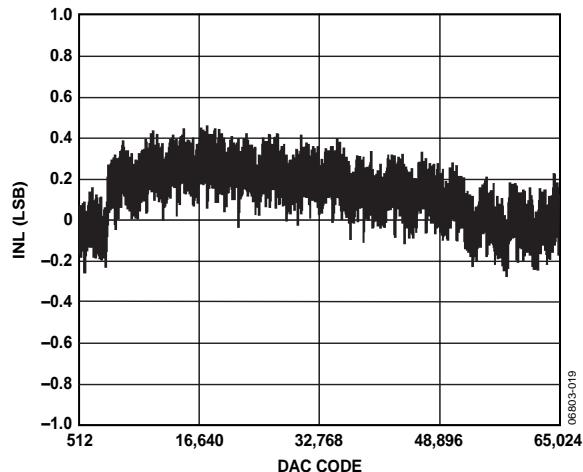

## 代表的な性能特性

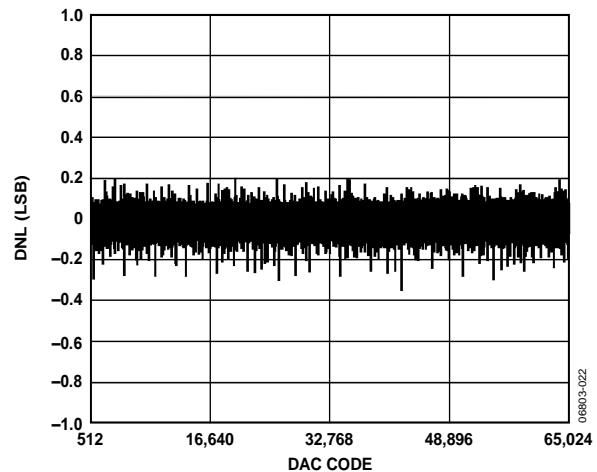

図 4.AD5064 の INL

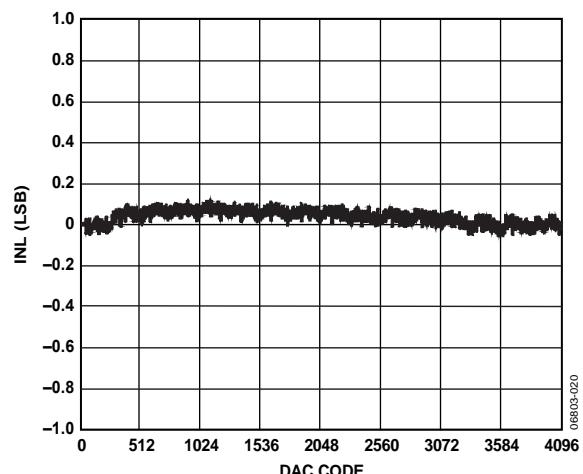

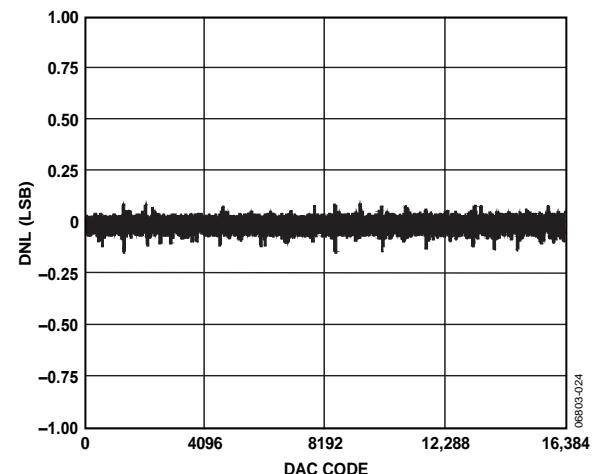

図 7.AD5064 の DNL

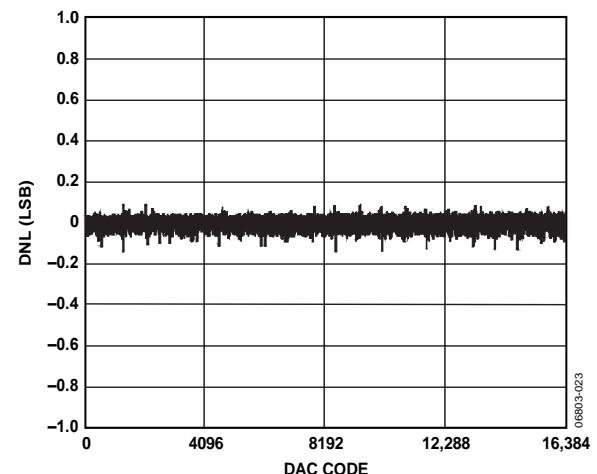

図 5.AD5044 の INL

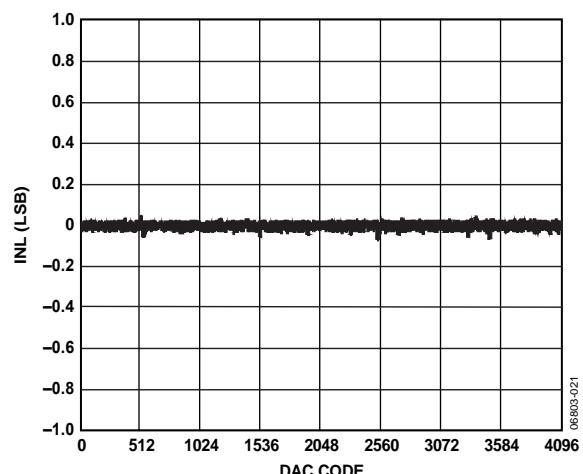

図 8.AD5044 の DNL

図 6.AD5024 の INL

図 9.AD5024 の DNL

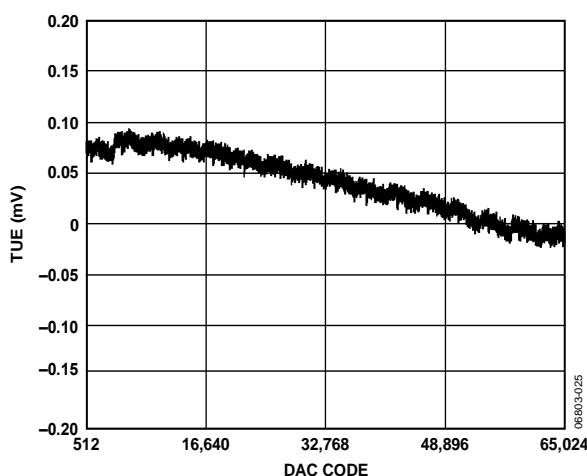

図 10. 総合未調整誤差(TUE)

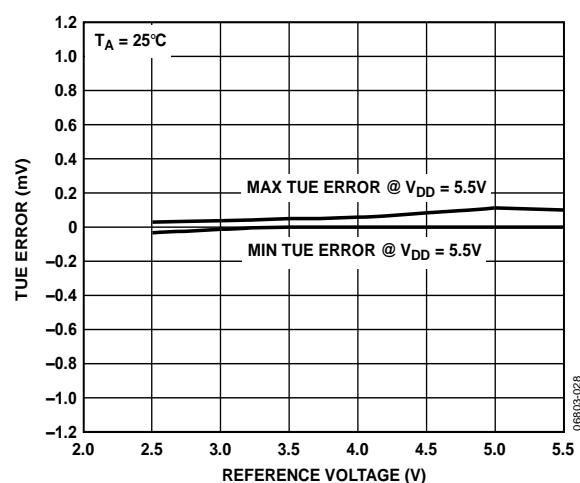

図 13. TUE 对リファレンス入力電圧

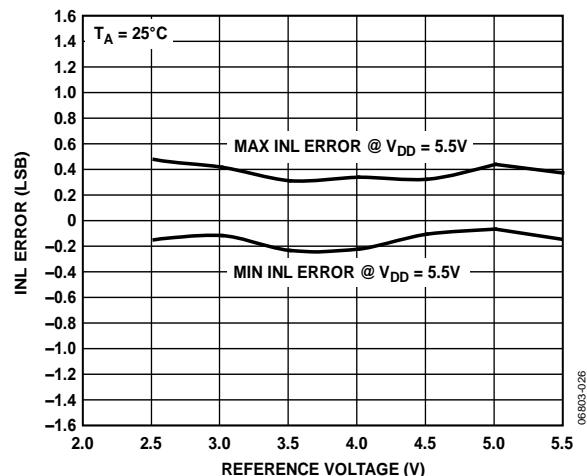

図 11. INL 对リファレンス入力電圧

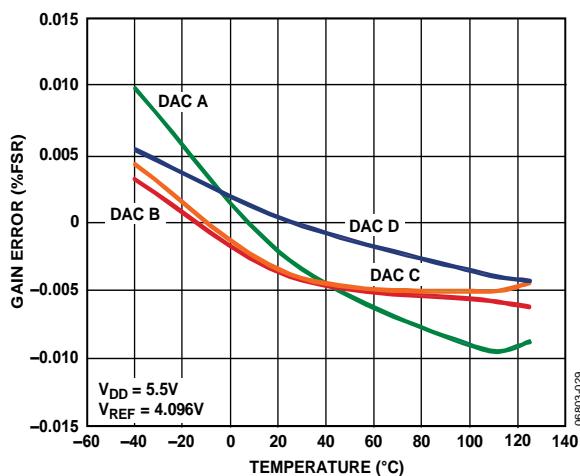

図 14. ゲイン誤差の温度特性

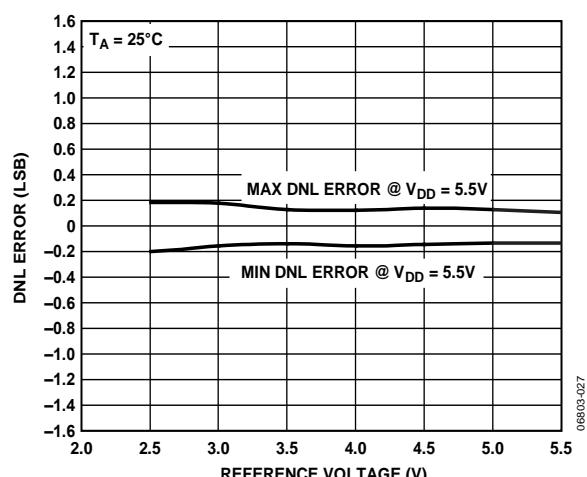

図 12. DNL 对リファレンス入力電圧

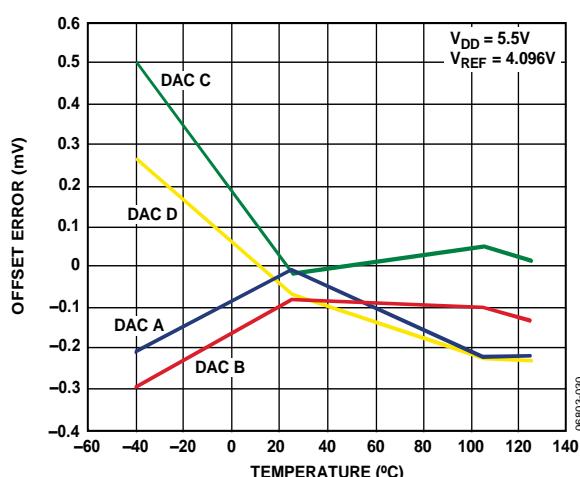

図 15. オフセット誤差の温度特性

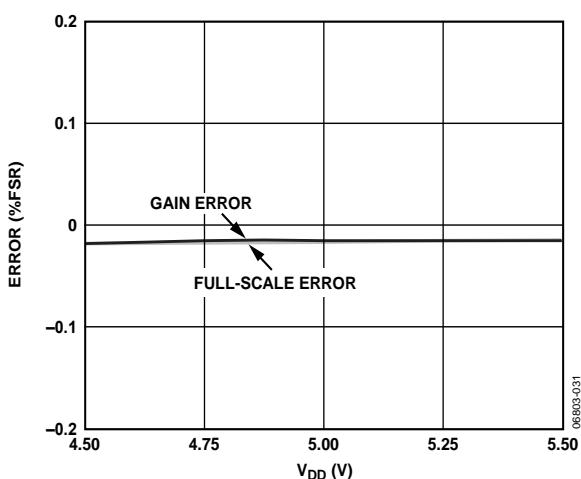

図 16. ゲイン誤差およびフル・スケール誤差対電源電圧

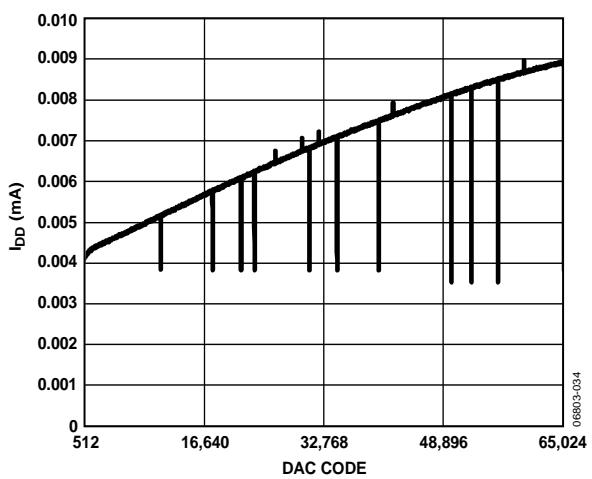

図 19. 電源電流対コード

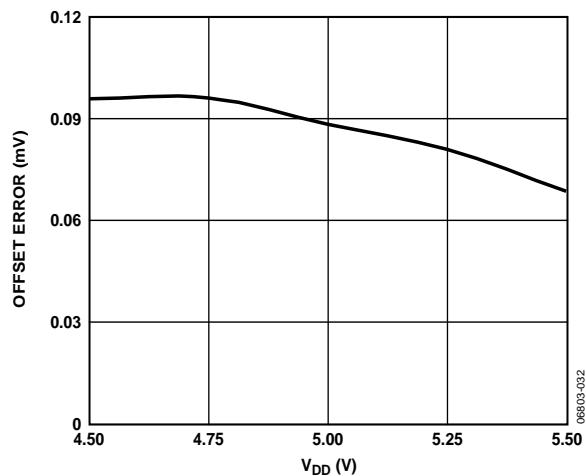

図 17. オフセット誤差電圧対電源電圧

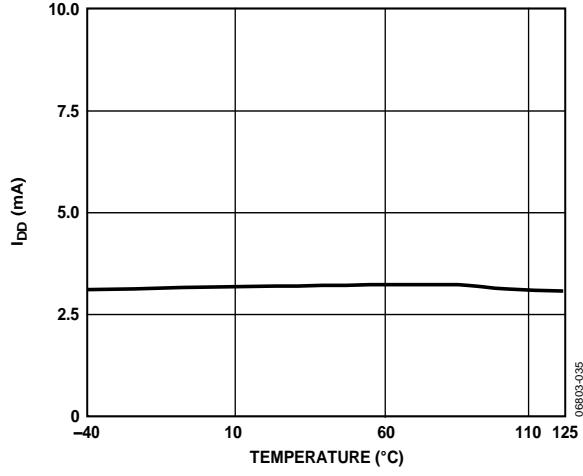

図 20. 電源電流の温度特性

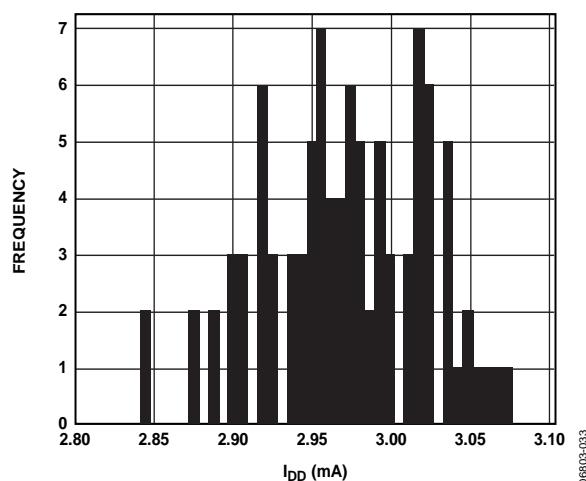

図 18.  $I_{DD}$  のヒストグラム、 $V_{DD} = 5.0$  V

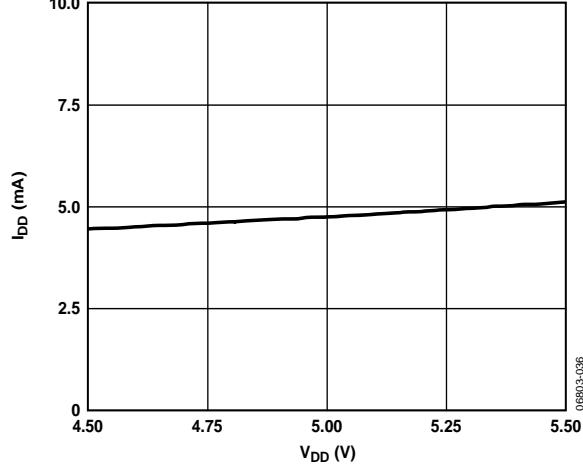

図 21. 電源電流対電源電圧

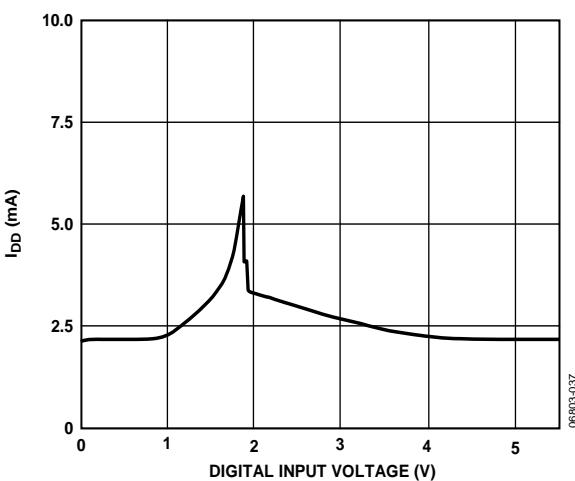

図 22.電源電流対デジタル入力電圧

図 25.ミッドスケールへのパワーオン・リセット

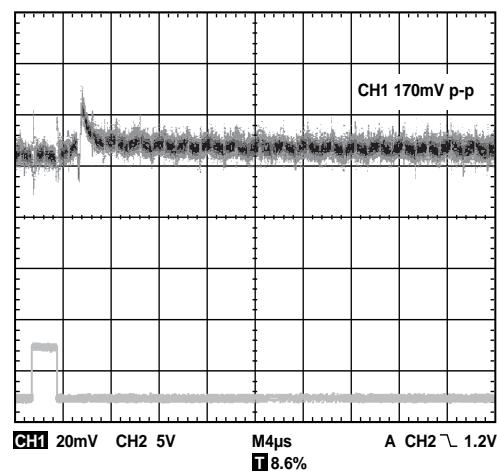

図 23.セトリング・タイム

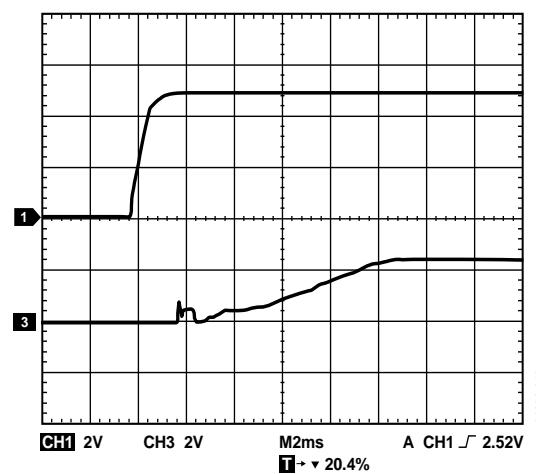

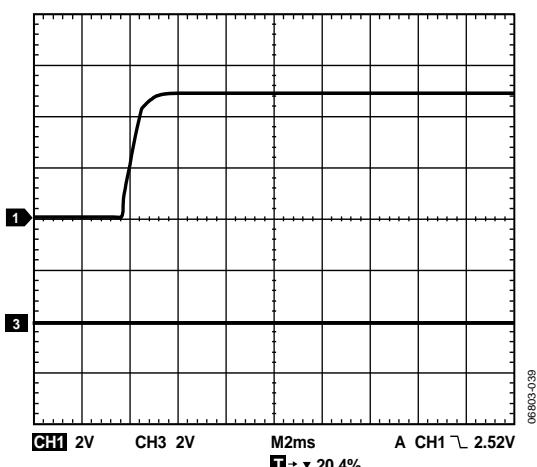

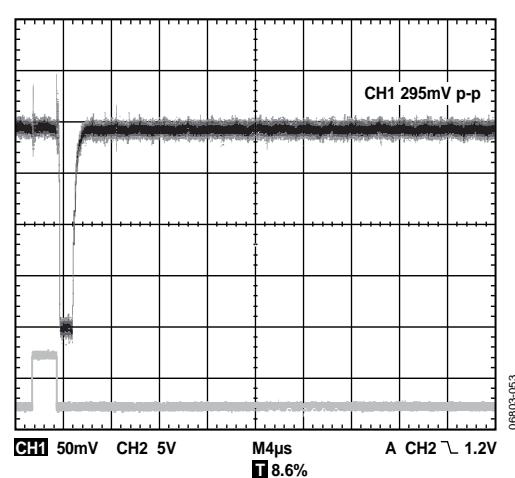

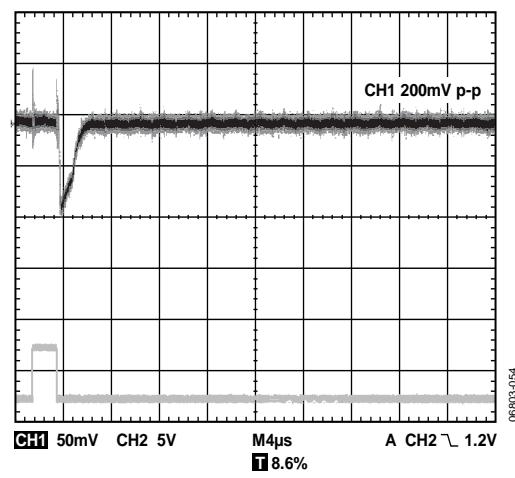

図 26.ミドスケールへのパワーダウン終了

図 24.0 Vへのパワーオン・リセット

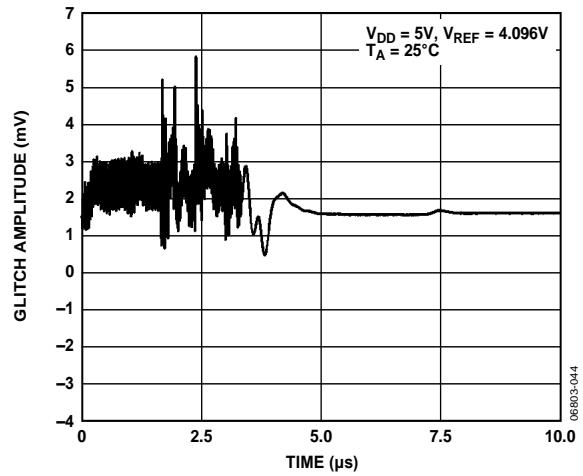

図 27.デジタルからアナログへのグリッチ・インパルス

図 28.アナログ・クロストーク

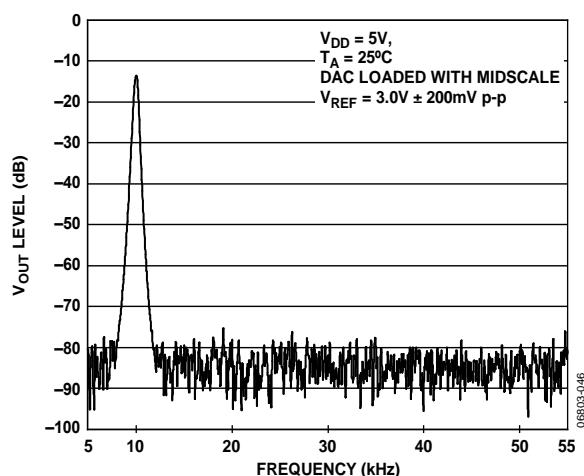

図 31.総合高調波歪み

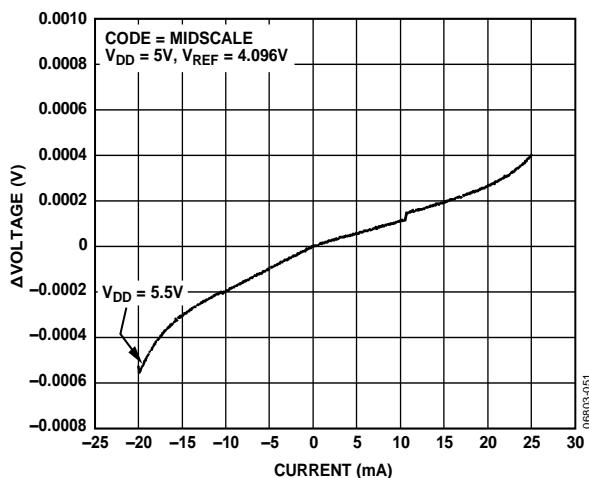

図 29.DAC 間クロストーク

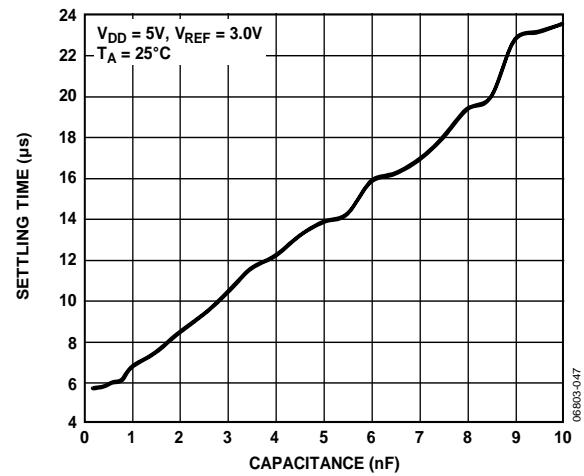

図 32.セトリング・タイム対容量負荷

図 30.0.1 Hz~10 Hz 出力ノイズのプロット

図 33.ハードウェア CLR

図 34. 乗算帯域幅

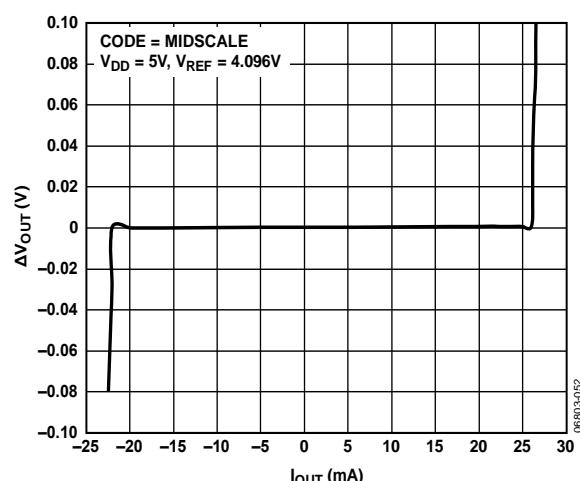

図 37. 電流制限機能のプロット (Typ)

図 35. 出力スルーレート (Typ)

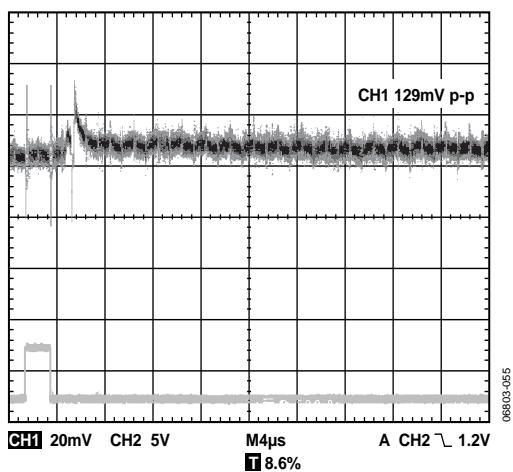

図 38. ゼロ・スケールへのパワーダウン開始時のグリッチ無負荷

図 36. 負荷レギュレーション (Typ)

図 39. ゼロ・スケールへのパワーダウン開始時のグリッチ 5 kΩ/200 pF 負荷

図 40.ゼロ・スケールからのパワーダウン終了時のグリッチ

無負荷

図 41.ゼロ・スケールからのパワーダウン終了時のグリッチ

5 kΩ/200 pF 負荷

# 用語

## 相対精度

DACの場合、相対精度すなわち積分非直線性(INL)は、DAC伝達関数の上下両端を結ぶ直線からの最大乖離(LSB数で表示)を表します。図4、図5、図6に、INL対コードのプロットを示します。

## 微分非直線性(DNL)

DNLは、隣接する2つのコードの間における測定された変化と理論的な1 LSB変化との差をいいます。最大1 LSBの微分非直線性の仕様は、単調性を保証するものです。このDACはデザインにより単調性を保証しています。図7、図8、図9に、DNL対コードのプロットを示します。

## オフセット誤差

オフセット誤差は、伝達関数の直線領域での $V_{OUT}$ (実測値)と $V_{OUT}$ (理論)の差を表し、mVで表示されます。オフセット誤差は、DACレジスタにコード512(AD5064)、コード128(AD5044)、コード32(AD5024)をロードしたデバイスで測定。mVで表され、正または負の値になります。

## ゲイン誤差

ゲイン誤差はDACのスパン誤差を表します。理論値からのDAC伝達特性の傾きの差をフルスケール範囲のパーセント値で表したもので

## オフセット誤差ドリフト

オフセット誤差ドリフトは、温度変化によるオフセット誤差の変化を表し、 $\mu V/^\circ C$ で表示されます。

## ゲイン温度係数

ゲイン誤差ドリフトは、温度変化によるゲイン誤差の変化を表し、(フルスケール範囲のppm)/ $^\circ C$ で表示します。

## フル・スケール誤差

フルスケール誤差は、フルスケール・コード(0xFFFF)をDACレジスタにロードしたときの出力誤差として測定されます。理論的には出力は $V_{REF} - 1$  LSBである必要があります。フルスケール範囲のパーセント値で表示します。 $V_{REF} < V_{DD}$ で測定します。

## デジタルからアナログへのグリッチ・インパルス

デジタルからアナログへのグリッチ・インパルスは、DACレジスタ内の入力コードが変化したときに、アナログ出力に混入するインパルスを表します。通常、nV·secで表すグリッチの面積として規定され、主要なキャリ変化(0x7FFFから0x8000)時に、デジタル・コードが1 LSBだけ変化したときに測定されます。図27を参照してください。

## DC電源除去比(PSRR)

電源電圧変化のDAC出力に対する影響を表します。PSRRは、DACフルスケール出力での、 $V_{OUT}$ 変化の $V_{DD}$ 変化に対する比です。dB値で表示します。 $V_{REF}$ を2.5 Vに固定して、 $V_{DD}$ を±10%変化させます。 $V_{REF} < V_{DD}$ で測定します。

## DCクロストーク

別のDAC出力変化に起因する1つのDACの出力レベルでのDC変化。ミッドスケールに維持した別のDACをモニターしながら、1つのDAC上(またはソフト・パワーダウンとパワーアップ)でのフル・スケール出力変化を測定します。 $\mu V$ で表されます。

負荷電流変化に起因するDCクロストークは、1つのDAC上の負荷電流変化がミッドスケールに維持された別のDACへ及ぼす影響を表します。 $\mu V/mA$ で表されます。

## リファレンス・フィードスルー

DAC出力が更新されない(すなわちLDACがハイ・レベル)ときのDAC出力における信号振幅のリファレンス電圧入力に対する比。dB値で表示します。

## デジタル・フィードスルー

DAC出力に書き込みが行われていない(SYNCがハイ・レベル)ときの、デバイスのデジタル入力ピンからDACのアナログ出力に注入されるインパルスを表します。nV·secで規定され、1個のデータとクロック・パルスを同時にDACに与えて測定します。

## デジタル・クロストーク

1のDACの入力レジスタにおけるフルスケール・コード変化(全ビット0から全ビット1への変化、およびその逆変化)から、ミッドスケール・レベルにある別のDACの出力に混入するグリッチ・インパルスを意味します。スタンダードアロン・モードで測定し、nV·secで表します。

## アナログ・クロストーク

DACの出力変化に起因して、別のDAC出力に混入するグリッチ・インパルス。LDACピンのハイ・レベル中に、入力レジスタの1つにフルスケール・コード変化(全ビット0から全ビット1への変化、およびその逆変化)をロードして、LDACピンにロー・レベル・パルスを入力し、デジタル・コードに変化のないDAC出力をモニタすることにより測定します。グリッチの面積はnV·secで表示します。

**DAC 間クロストーク**

デジタル・コードの変化とそれに続く DAC の出力変化に起因して、別の DAC 出力に混入するグリッヂ・インパルス。これには、デジタル・クロストークとアナログ・クロストークの両方が含まれます。LDAC ピンをロー・レベルにして、DAC の 1 つにフルスケール・コード変化(全ビット 0 から全ビット 1 への変化、およびその逆変化)をロードして、別の DAC 出力をモニタすることにより測定します。グリッヂのエネルギーは nV-sec で表示します。

**乗算帯域幅**

DAC 内のアンプは有限な帯域幅を持っています。乗算帯域幅はこれを表します。入力された基準正弦波(DAC にフルスケール・コードをロード)は、出力に現われます。乗算帯域幅は、出力振幅が入力より 3 dB 小さくなる周波数で表します。

**総合高調波歪み(THD)**

理論正弦波と DAC を使ったために減衰したその正弦波との差。DAC に対してリファレンスとして正弦波を使ったときに、DAC 出力に現われる高調波が THD になります。dB 値で表示します。

## 動作原理

### DAC セクション

AD5024/AD5044/AD5064 は、12/14/16 ビット、シリアル入力の電圧出力 DAC です。このデバイスは、4.5 V～5.5 V の電源電圧で動作します。データは、3 線式シリアル・インターフェースを経由して 32 ビット・ワード・フォーマットで AD5024/AD5044/AD5064 に書き込まれます。AD5024/AD5044/AD5064 は、DAC 出力が既知の出力状態でパワーアップするようにするパワーオン・リセット回路を内蔵しています。このデバイスには、消費電流を  $2 \mu\text{A}$  未満に減少させるソフトウェア・パワーダウン・モードがあります。

DAC への入力コーディングはストレート・バイナリを使っていて、外部リファレンスを使ったときの理論出力電圧は次式で与えられます。

$$V_{\text{OUT}} = V_{\text{REFIN}} \times \left( \frac{D}{2^N} \right)$$

ここで、D は DAC レジスタにロードされるバイナリ・コードの 10 進数表示であり、0～65,535 の値。N は、DAC の解像度。

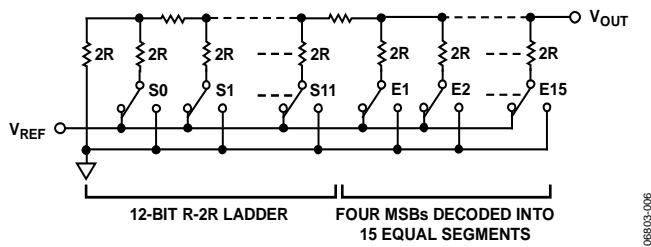

### DAC アーキテクチャ

AD5064 の DAC アーキテクチャは、2 つの一致した DAC セクションから構成されています。簡略化した回路図を図 42 に示します。16 ビット・データ・ワードの上位 4 ビットは、デコードされて 15 個のスイッチ E1～E15 を駆動します。これらの各スイッチは、GND または  $V_{\text{REF}}$  バッファ出力に接続された、15 個の一致した抵抗の 1 つに接続されます。データ・ワードの残りの 12 ビットは、12 ビット電圧モード R-2R ラダー回路のスイッチ S0～S11 を駆動します。

図 42.DAC ラダーの構造

### リファレンス電圧バッファ

AD5024/AD5044/AD5064 は、外付けのリファレンス電圧を使用して動作します。各 DAC には専用のリファレンス電圧ピンがあります。リファレンス入力ピンの入力範囲は 2.5 V～ $V_{\text{DD}}$  です。この入力電圧は、DAC コアに対するバッファされたリファレンス電圧の発生に使用されます。

### 出力アンプ

出力バッファ・アンプは、出力でレール to レール電圧を発生することができ、0 V～ $V_{\text{DD}}$  の出力範囲を発生します。GND に接続された  $5 \text{ k}\Omega$  と、これに並列接続された  $200 \text{ pF}$  の負荷を駆動することができます。スルーレートは  $1.5 \text{ V}/\mu\text{s}$  で、 $1/4$ スケールから  $3/4$ スケールへのセトリング・タイムは  $13 \mu\text{s}$  です。

### シリアル・インターフェース

AD5024/AD5044/AD5064 は、SPI、QSPI、MICROWIRE の各インターフェース規格、および大部分の DSP インターフェース規格と互換性を持つ 3 線式シリアル・インターフェース(SYNC、SCLK、DIN)を内蔵しています。代表的な書き込みシーケンスのタイミング図については、図 2 を参照してください。

### スタンダードアロン・モード

SYNC ラインをロー・レベルにすると、書き込みシーケンスが開始されます。DIN ラインからのデータは、SCLK の立ち下がりエッジで 32 ビット・シフトレジスタに入力されます。シリアル・クロック周波数は 50 MHz まで上げることができます。AD5024/AD5044/AD5064 は高速 DSP と互換性を持つことができます。32 番目の立ち下がりクロック・エッジで最後のデータ・ビットが入力されて、プログラムされた機能が実行されます (DAC レジスタ値の変更および/または動作モードの変更)。この時点で、SYNC ラインをロー・レベルに維持するか、ハイ・レベルにすることができます。いずれの場合でも、SYNC の立ち下がりエッジが次の書き込みシーケンスを確実に開始できるようになります。次の書き込みシーケンスの前に最小 1.9 ns 間(シングル・チャンネル)SYNC をハイ・レベルにする必要があります。

$V_{\text{IN}} = 0.8 \text{ V}$  の場合よりは  $V_{\text{IN}} = 2.2 \text{ V}$  の場合の方が SYNC バッファを流れる電流が大きくなるため、各書き込みシーケンスの間も SYNC をアイドル・ロー・レベルに維持して、前述のようにさらにデバイス消費電力を削減するようにします。ただし、前述のように、次の書き込みシーケンスの開始前に SYNC を 1 度ハイ・レベルに戻す必要があります。

表 7.コマンドの定義

| Command |    |    |    | Description                                           |

|---------|----|----|----|-------------------------------------------------------|

| C3      | C2 | C1 | C0 |                                                       |

| 0       | 0  | 0  | 0  | Write to Input Register n                             |

| 0       | 0  | 0  | 1  | Update DAC Register n                                 |

| 0       | 0  | 1  | 0  | Write to Input Register n, update all (software LDAC) |

| 0       | 0  | 1  | 1  | Write to and update DAC Channel n                     |

| 0       | 1  | 0  | 0  | Power down/power up DAC                               |

| 0       | 1  | 0  | 1  | Load clear code register                              |

| 0       | 1  | 1  | 0  | Load LDAC register                                    |

| 0       | 1  | 1  | 1  | Reset (power-on reset)                                |

| 1       | 0  | 0  | 0  | Reserved                                              |

| 1       | 0  | 0  | 1  | Reserved                                              |

| 1       | 1  | 1  | 1  | Reserved                                              |

表 8.アドレス・コマンド

| Address (n) |    |    |    | Selected DAC Channel |

|-------------|----|----|----|----------------------|

| A3          | A2 | A1 | A0 |                      |

| 0           | 0  | 0  | 0  | DAC A                |

| 0           | 0  | 0  | 1  | DAC B                |

| 0           | 0  | 1  | 0  | DAC C                |

| 0           | 0  | 1  | 1  | DAC D                |

| 1           | 1  | 1  | 1  | All DACs             |

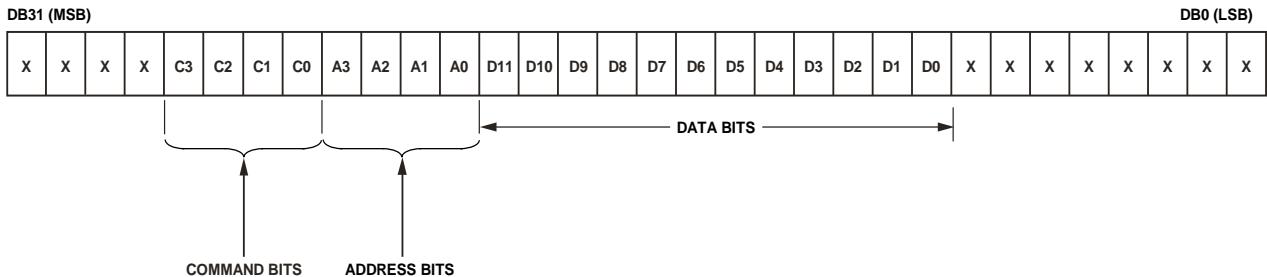

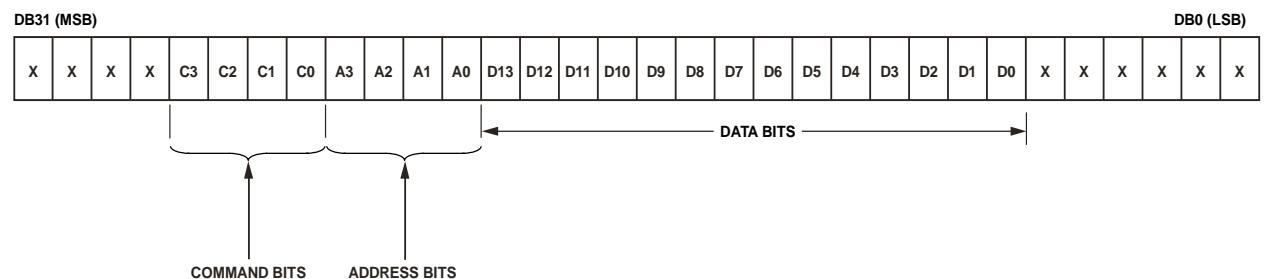

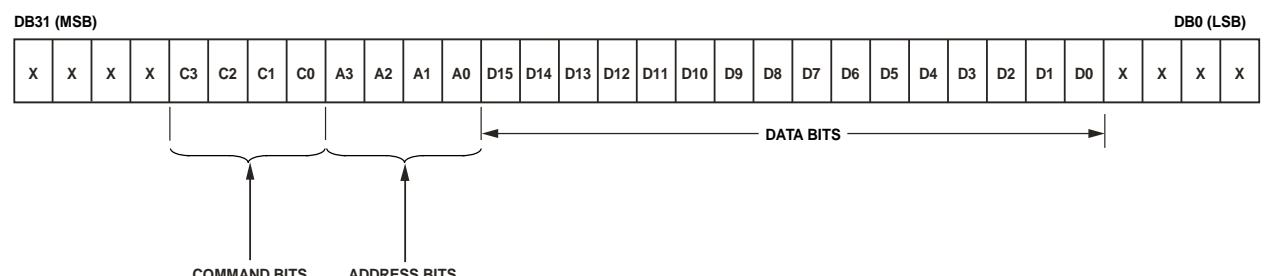

### 入力シフトレジスタ

AD5024/AD5044/AD5064 の入力シフト・レジスタ幅は、32 ビットです。最初の 4 ビットは don't care です。次の 4 ビットはコマ

ンド・ビット C3~C0 (表 7 参照)で、その後ろに 4 ビットの DAC アドレス・ビット A3~A0 (表 8 と)とビットのデータ・ワードが続きます。データ・ワードは AD5024/AD5044/AD5064 に対して、それぞれ 12、14、または 16 ビットの入力コード、その後ろに 8、6、4 ビットの don't care が続きます (図 43、図 44、図 45 参照)。これらのデータ・ビットは、SCLK の 32 番目の立ち下がりエッジで DAC レジスタに転送されます。

### SYNC 割り込み

通常の書き込みシーケンスでは、SYNC ラインは SCLK の少なくとも 32 個の立ち下がりエッジ間ロー・レベルに維持され、DAC は 32 番目の立ち下がりエッジで更新されます。ただし、32 番目の立ち下がりエッジの前に SYNC をハイ・レベルにすると、これは書き込みシーケンスへの割り込みとして機能します。ソフトレジスタがリセットされて、書き込みシーケンスは無効と見なされます。DAC レジスタ値の更新も、動作モードの変更も行われません (図 46 参照)。

図 43.AD5024 入力レジスタの値

図 44.AD5044 入力レジスタの値

図 45.AD5064 入力レジスタの値

図 46.SYNC の割り込み機能

## パワーオン・リセット

AD5024/AD5044/AD5064 は、パワーアップ時に出力電圧を制御するパワーオン・リセット回路を内蔵しています。POR ピンをロー・レベルに接続すると、AD5024/AD5044/AD5064 出力はゼロスケールでパワーアップします。これは DAC のリニア領域外であることに注意してください。POR ピンをハイ・レベルに接続すると、AD5024/AD5044/AD5064 出力はミッドスケールでパワーアップします。デバイスに有効な書き込みシーケンスが実行されるまで出力のこの状態が維持されます。この機能は、デバイスのパワーアップ時の DAC 出力状態が既知である必要のあるアプリケーションで特に便利です。DAC をパワーオン・リセット・コードへリセットするソフトウェアからのリセット機能表 9)。

表 9 に、ビットの状態と対応するデバイスの動作モードを示します。該当する 4 ビット (DB3, DB2, DB1, DB0) を 1 に設定すると、対応する DAC (DAC D～DAC A) を選択したモードへパワーダウンさせることができます。パワーダウン/パワーアップ動作時の入力シフト・レジスタ値については、表 10 を参照してください。

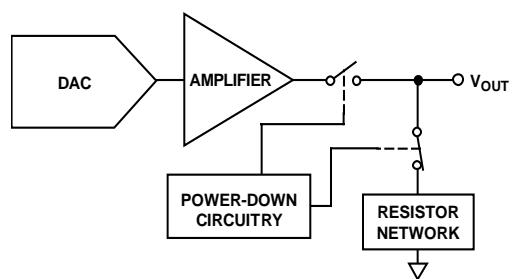

コントロール・レジスタのビット DB9 とビット D8 がともに 0 に設定されると、デバイスは通常の消費電力 (3 mA, 5 V) で通常動作しますが、3 つのパワーダウン・モードでは、電源電流は 5 V で 0.4  $\mu$ A に削減されます。電源電流が削減されるだけでなく、出力ステージも内部でアンプ出力から既知の値の抵抗回路へ切り替えられます。この方法には、デバイスの出力インピーダン

もあります。コマンド 0111 はこのリセット機能用に指定されています (表 7 参照)。パワーオン・リセット時には、LDAC または CLR の動作は無視されます。

## パワーダウン・モード

AD5024/AD5044/AD5064 には 4 つの動作モードがあります。コマンド 0100 はこのパワーダウン機能用に指定されています (表 7 参照)。これらのモードは、コントロール・レジスタの 2 ビット (DB9 と DB8) を設定することによりソフトウェアから設定可能です(

スが既知であると同時にデバイスがパワーダウン・モードになるという利点があります。次の 3 つのオプションがあります。出力が内部で 1 k $\Omega$  の抵抗または 100 k $\Omega$  の抵抗を経由して GND に接続されるか、または出力がオープン(スリー・ステート)になります。図 47 に、出力ステージを示します。

パワーダウン・モードのときは、バイアス・ジェネレータ、出力アンプ、抵抗ストリング、およびその他の関係するすべてのリニア回路はすべてシャットダウンされます。ただし、DAC レジスタの値はパワーダウン・モードで影響を受けることはありません。パワーダウン・モードから抜け出す時間は、V<sub>DD</sub> = 5 V のとき 4.5  $\mu$ s (typ) です(図 26 参照)。

表 9.動作モード

| DB9 | DB8 | Operating Mode        |

|-----|-----|-----------------------|

| 0   | 0   | Normal operation      |

|     |     | Power-down modes:     |

| 0   | 1   | 1 k $\Omega$ to GND   |

| 1   | 0   | 100 k $\Omega$ to GND |

| 1   | 1   | Three-state           |

表 10.パワーアップ/パワーダウン機能に対する 32 ビット入力シフトレジスタの値

| MSB          |                         |      |      |      |                                     |      |      |      |              |             |                 | LSB         |                                                              |       |       |       |  |

|--------------|-------------------------|------|------|------|-------------------------------------|------|------|------|--------------|-------------|-----------------|-------------|--------------------------------------------------------------|-------|-------|-------|--|

| DB31 to DB28 | DB27                    | DB26 | DB25 | DB24 | DB23                                | DB22 | DB21 | DB20 | DB10 to DB19 | DB9         | DB8             | DB4 to DB7  | DB3                                                          | DB2   | DB1   | DB0   |  |

| X            | 0                       | 1    | 0    | 0    | X                                   | X    | X    | X    | X            | PD1         | PDO             | X           | DAC D                                                        | DAC C | DAC B | DAC A |  |

| Don't cares  | Command bits (C2 to C0) |      |      |      | Address bits (A3 to A0)—don't cares |      |      |      |              | Don't cares | Power-down mode | Don't cares | Power-down/power-up channel selection—set bit to 1 to select |       |       |       |  |

図 47.パワーダウン時の出力ステージ

## クリア・コード・レジスタ

AD5024/AD5044/AD5064 には、非同期クリア入力のハードウェア CLR ピンがあります。CLR 入力は、立ち下がりエッジで検出されます。CLR ラインをロー・レベルにすると、入力レジスタ値がクリアされ、各 DAC レジスタにユーザ設定可能な CLR レジスタ内のデータがロードされて、この値に基づきアナログ出力が設定されます(表 11 参照)。この機能は、ゼロ・スケール、ミッド・スケールまたはフル・スケールを全チャンネルにロードするイン・システム・キャリブレーションで使うことができます。ゼロ・スケールとフルスケールは DAC リニア領域外であることに注意してください。これらクリア・コード値は、コントロール・レジスタの 2 ビット(DB1 と DB0)を設定することによりユーザーから設定可能です(表 11 参照)。デフォルト設定では出力が 0 V にクリアされます。コマンド 0101 はクリア・コード・レジスタのロード用に割り当てられています(表 7 参照)。

デバイスは、デバイスに対する次の書き込みの 32 番目の立ち下がりエッジでクリア・コード・モードから抜け出します。書き込みシーケンス中に CLR がアクティブになると、書き込みが中止されます。

CLR のパルス・アクチベーション・タイム (CLR の立ち下がりエッジから出力変化が開始されるまでの時間) は、10.6  $\mu$ s (typ) です。DAC リニア領域の外側の場合には、CLR の実行から出力変化が開始されるまでの時間としては 10.6  $\mu$ s (typ) を要します(図 33 参照)。

クリア・コード・レジスタのロード動作時の入力シフト・レジスタ値については、表 12 を参照してください。

## LDAC 機能

### ハードウェア LDAC ピン

すべての DAC 出力は、ハードウェア LDAC ピンを使って同時に更新することができます(図 2 参照)。

同期 LDAC: 新しいデータを読み出した後、DAC レジスタが 32 番目の SCLK パルスの立ち下がりエッジで更新されます。LDAC はロー・レベルに固定するか、ロー・パルスで駆動することができます。

非同期 LDAC: 出力は入力レジスタへの書き込みと同時に更新されません。LDAC がロー・レベルになると、DAC レジスタは入力レジスタ値で更新されます。

### ソフトウェア LDAC 機能

ソフトウェア LDAC 機能を使って、入力レジスタ n に書き込みを行いすべての DAC レジスタを更新すると、すべての DAC 出力を同時に更新することができます。コマンド 0010 はこのソフトウェア LDAC 機能用に割り当てられています。

LDAC レジスタを使うと、ハードウェア LDAC ピンを柔軟に制御することができます(表 14 参照)。DAC チャンネルに対して LDAC ビット・レジスタ (DB0~DB3) を 0 設定することは、こ

のチャンネルの更新がハードウェア LDAC ピンから制御されることを意味します。このビットを 1 に設定すると、このチャンネルが同期的に更新されます。すなわち、DAC レジスタが新しいデータを読み出した後に、ハードウェア LDAC ピンの状態に無関係に更新されます。

これは、ハードウェア LDAC ピンがロー・レベルに固定されているのと実質的に同じです(LDAC レジスタの動作モードについては表 13 を参照してください)。この柔軟性は、選択したチャンネルを更新すると同時に残りのチャンネルも同期的に更新することが必要なアプリケーションで便利です。

コマンド 0110 を使って DAC へ書き込みを行うと、4 ビットの LDAC レジスタ (DB3~DB0) がロードされます。各チャンネルのデフォルト値は 0 です。すなわち、LDAC ピンは通常の動作を行います。これらのビットを 1 に設定することは、LDAC ピンの状態に無関係に DAC チャンネルを更新することを意味します。

## 電源のバイパスとグラウンド接続

高精度が重要な回路では、ボード上の電源とグラウンド・リターンのレイアウトを注意深く行うことが役立ちます。AD5024/AD5044/AD5064 を実装するプリント回路ボードでは、アナログ部とデジタル部を分離する必要があります。複数のデバイスが AGND と DGND の接続を必要とするシステム内で AD5024/AD5044/AD5064 を使用する場合は、この接続は 1 カ所行う必要があります。グラウンド・ポイントは AD5024/AD5044/AD5064 のできるだけ近くに配置する必要があります。

AD5024/AD5044/AD5064 の電源は、10  $\mu$ F と 0.1  $\mu$ F のコンデンサでバイパスする必要があります。コンデンサはデバイスのできるだけ近くに配置し、0.1  $\mu$ F のコンデンサは理想的にはデバイスの近くに配置することが望されます。10  $\mu$ F コンデンサはタンタルのビーズ型を使います。0.1  $\mu$ F コンデンサは、セラミック型コンデンサのような実効直列抵抗 (ESR) が小さく、かつ実効直列インダクタンス (ESL) が小さいものを使う必要があります。この 0.1  $\mu$ F のコンデンサは、内部ロジックのスイッチングにより発生する過渡電流に起因する高周波に対してグラウンドへの低インピーダンス・パスを提供します。

電源ラインはできるだけ太いパターンにしてインピーダンスを小さくし、電源ライン上のグリッチによる影響を軽減させるようにします。クロックとその他の高速スイッチング・デジタル信号は、デジタル・グラウンドを使ってボード上の他の部分からシールドする必要があります。デジタル信号とアナログ信号の交差は、できるだけ回避する必要があります。ボードの反対側のパターンは、互いに右角度となるように配置してボードを通過するフィードスルー効果を減少させます。最適なボード・レイアウト技術は、ボードの部品側をグラウンド・プレーン専用として使い、信号パターンはハンダ面に配置するマイクロトリップ技術ですが、2 層ボードでは常に可能とは限りません。

表 11.クリア・コード・レジスタ

| Clear Code Register |     | Clears to Code |

|---------------------|-----|----------------|

| DB1                 | DB0 |                |

| CR1                 | CR0 |                |

| 0                   | 0   | 0x0000         |

| 0                   | 1   | 0x8000         |

| 1                   | 0   | 0xFFFF         |

| 1                   | 1   | No operation   |

表 12.クリア・コード機能に対する 32 ビット入力シフトレジスタ値

| MSB         | DB31 to DB28            | DB27 | DB26 | DB25 | DB24                    | DB23 | DB22 | DB21 | DB20        | DB2 to DB19                      | DB1 | LSB<br>DB0 |

|-------------|-------------------------|------|------|------|-------------------------|------|------|------|-------------|----------------------------------|-----|------------|

| X           | 0                       | 1    | 0    | 1    | X                       | X    | X    | X    | X           | X                                | 1/0 | 1/0        |

| Don't cares | Command bits (C3 to C0) |      |      |      | Address bits (A3 to A0) |      |      |      | Don't cares | Clear code register (CR1 to CR0) |     |            |

表 13.LDAC 優先定義

| Load DAC Register      |              | LDAC Operation                                                                         |

|------------------------|--------------|----------------------------------------------------------------------------------------|

| LDAC Bits (DB3 to DB0) | LDAC Pin     |                                                                                        |

| 0                      | 1 or 0       | Determined by the <u>LDAC</u> pin                                                      |

| 1                      | X—don't care | DAC channels update, overrides the <u>LDAC</u> pin. DAC channels see <u>LDAC</u> as 0. |

表 14.LDAC優先機能に対する 32 ビット入力シフトレジスタ値

| MSB         | DB31 to DB28            | DB27 | DB26 | DB25 | DB24                                    | DB23 | DB22 | DB21 | DB20        | DB4 to DB19                               | DB3   | DB2   | DB1   | LSB<br>DB0 |

|-------------|-------------------------|------|------|------|-----------------------------------------|------|------|------|-------------|-------------------------------------------|-------|-------|-------|------------|

| X           | 0                       | 1    | 1    | 0    | X                                       | X    | X    | X    | X           | DAC D                                     | DAC C | DAC B | DAC A |            |

| Don't cares | Command bits (C3 to C0) |      |      |      | Address bits (A3 to A0)—<br>don't cares |      |      |      | Don't cares | Setting LDAC bits to 1 overrides LDAC pin |       |       |       |            |

## マイクロプロセッサ・インターフェース

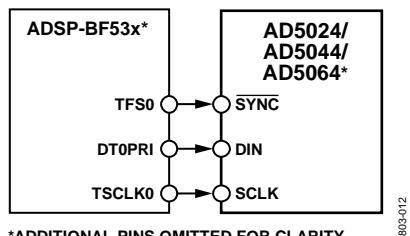

### AD5024/AD5044/AD5064 と Blackfin ADSP-BF53x とのインターフェース

図 48 に、AD5024/AD5044/AD5064 と Blackfin ADSP-BF53x マイクロプロセッサとの間のシリアル・インターフェースを示します。ADSP-BF53x ファミリは、シリアル通信とマルチプロセッサ通信用に 2 個のデュアル・チャンネル同期シリアル・ポート (SPORT0 と SPORT1) を内蔵しています。SPORT0 を使って AD5024/AD5044/AD5064 に接続し、DT0PRI が AD5024/AD5044/AD5064 の DIN ピンを駆動し、TSCLK0 がデバイスの SCLK を駆動するようにインターフェースを構成します。SYNC ピンは TFS0 で駆動します。

\*ADDITIONAL PINS OMITTED FOR CLARITY.

0603-012

図 48. AD5024/AD5044/AD5064 と Blackfin ADSP-BF53x とのインターフェース

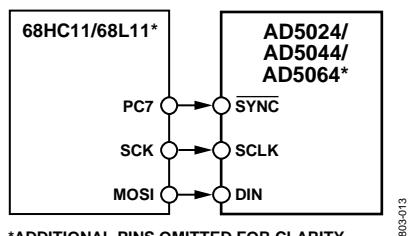

### AD5024/AD5044/AD5064 と 68HC11/68L11 とのインターフェース

図 49 に、AD5024/AD5044/AD5064 と 68HC11/68L11 マイクロコントローラとの間のシリアル・インターフェースを示します。68HC11/68L11 の SCK が AD5024/AD5044/AD5064 の SCLK を駆動し、MOSI 出力が DAC のシリアル・データ・ラインを駆動します。

\*ADDITIONAL PINS OMITTED FOR CLARITY.

0603-013

図 49. AD5024/AD5044/AD5064 と 68HC11/68L11 とのインターフェース

SYNC 信号は、ポート・ライン (PC7) から発生されます。このインターフェースの正常動作のためには、68HC11/68L11 で CPOL ビット = 0 かつ CPHA ビット = 1 の設定を行う必要があります。データを DAC に転送するときは、SYNC ラインをロー・レベルにします (PC7)。68HC11/68L11 が上記のように設定された場合には、MOSI に出力されるデータは SCK の立下がりエッジで有効になります。シリアル・データは 68HC11/68L11 から 8 ビット・バイトで転送され、送信サイクル内の 8 個の立ち下がりクロック・エッジが使用されます。データは MSB ファーストで転送されます。データを AD5024/AD5044/AD5064 にロードするときは、最初の 8 ビットが転送された後にも PC7 をロー・レベルのままにして、DAC に対して 2 番目のシリアル書き込み動作を実行します。このプロセージャの終わりに、PC7 をハイ・レベルにします。

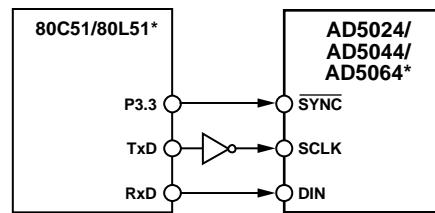

### AD5024/AD5044/AD5064 と 80C51/80L51 とのインターフェース

図 50 に、AD5024/AD5044/AD5064 と 80C51/80L51 マイクロコントローラとの間のシリアル・インターフェースを示します。このインターフェースでは、80C51/80L51 の TxD が AD5024/AD5044/AD5064 の SCLK を駆動し、RxD がこのデバイスのシリアル・データ・ラインを駆動します。SYNC 信号は、この場合もポートのビット・プログラマブルなピンから発生されます。このケースではポート・ライン P3.3 を使用しています。データを AD5024/AD5044/AD5064 に転送するときは、P3.3 をロー・レベルにします。80C51/80L51 はデータを 8 ビット・バイトとして転送するため、送信サイクル内の 8 個の立ち下がりクロック・エッジを使います。データを DAC にロードするときは、最初の 8 ビットが転送された後にも P3.3 をロー・レベルのままにして、2 番目の書き込みサイクルを実行すると、データの 2 番目のバイトの転送が開始されます。このサイクルの完了後に P3.3 をハイ・レベルにします。80C51/80L51 は、LSB ファーストのフォーマットでシリアル・データを出力します。AD5024/AD5044/AD5064 は、MSB ファーストでデータを受信する必要があります。80C51/80L51 の送信ルーチンでは、このことを考慮しておく必要があります。

\*ADDITIONAL PINS OMITTED FOR CLARITY.

0603-014

図 50. AD5024/AD5044/AD5064 to 80C51/80L51 インターフェース

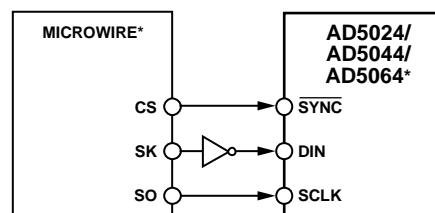

### AD5024/AD5044/AD5064 と MICROWIRE とのインターフェース

図 51 に、AD5024/AD5044/AD5064 と任意の MICROWIRE 互換デバイスとの間のインターフェースを示します。シリアル・データはシリアル・クロックの立下がりエッジで出力され、SCLK の立上がりエッジで AD5024/AD5044/AD5064 に入力されます。

\*ADDITIONAL PINS OMITTED FOR CLARITY.

0603-015

図 51. AD5024/AD5044/AD5064 と MICROWIRE とのインターフェース

## アプリケーション

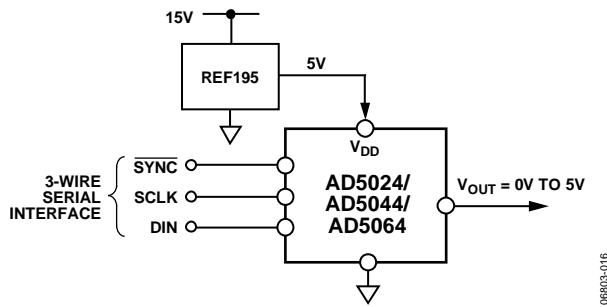

## リファレンス電圧の電源としての使用

AD5024/AD5044/AD5064 で要求される電源電流は極めて小さいため、リファレンス電圧をデバイスの電源として使うオプションがあります (図 52 参照)。この機能は、電源のノイズが多い場合 またはシステム電源電圧値が 5 V 以外の値である場合 (たとえば 15 V) に特に便利です。リファレンス電圧出力は、AD5024/AD5044/AD5064 に対する安定した電源電圧になります。低ドロップアウトの [REF195](#) を使用する場合、DAC 出力負荷なしで 3 mA の電流を AD5024/AD5044/AD5064 に供給する必要があります。DAC 出力に負荷がある場合は、REF195 は負荷にも電流を供給する必要があります。必要な合計電流は次のようになります (DAC 出力に 5 k $\Omega$  の負荷)。

$$3 \text{ mA} + (5 \text{ V}/5 \text{ k}\Omega) = 4 \text{ mA}$$

REF195 の負荷レギュレーションは 2 ppm/mA(typ)であるため、4 mA の電流出力に対して 3 ppm (27  $\mu$ V) の誤差になります。この値は、0.196 LSB の誤差に対応します。

図 52. AD5024/AD5044/AD5064 の電源としての REF195

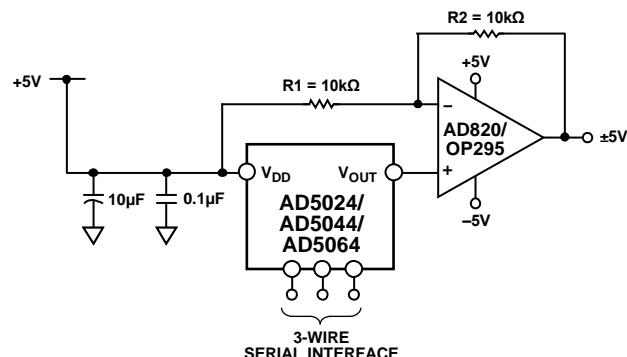

## バイポーラ動作

AD5024/AD5044/AD5064 は単電源動作作用にデザインされていますが、に示す回路を使うと、バイポーラ出力範囲も可能です。この回路は $\pm 5\text{ V}$  の出力範囲を可能にします。[AD820](#) または [OP295](#) を出力アンプとして使うと、アンプ出力でのレール to レール動作が可能です。

$V_{DD} = V_{REF}$  の場合、任意の入力コードに対する出力電圧 は次のように計算されます。

$$V_{OUT} = \left[ V_{DD} \times \left( \frac{D}{65,536} \right) \times \left( \frac{R1 + R2}{R1} \right) - V_{DD} \times \left( \frac{R2}{R1} \right) \right]$$

ここで、D は入力コードに等価な 10 進値(0~65,535)を表します。

VDD = 5 V、R1 = R2 = 10 kΩ のときは、

$$V_{OUT} = \left( \frac{10 \times D}{65,536} \right) - 5 \text{ V}$$

±5 V の出力電圧範囲になり、0x0000 は-5 V の出力に、0xFFFF は+5 V の出力に、それぞれ対応します。

図 53.バイポーラ動作

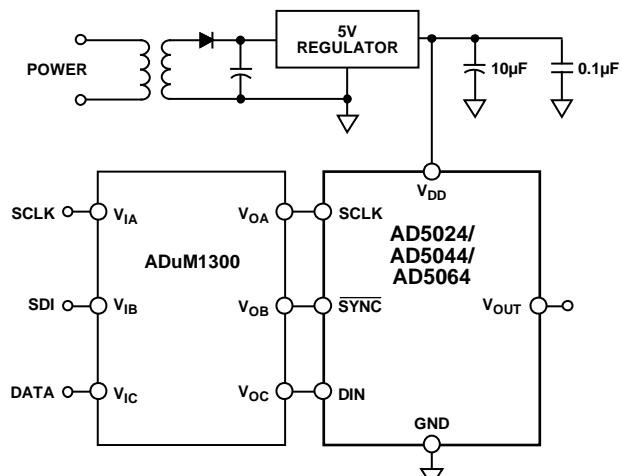

## AD5024/AD5044/AD5064 の電流絶縁型インターフェースでの使用

工業用環境のプロセス制御アプリケーションでは、光アイソレーション・インターフェースを使って、DAC が動作している領域で発生する有害な同相モード電圧から制御回路を保護するため電流によりアイソレーションすることが必要となることがあります。iCoupler®は 2.5 kV を超えるアイソレーションを提供します。AD5024/AD5044/AD5064 は 3 線式シリアル・ロジック・インターフェースを使っているので、3 チャンネル・デジタル・アイソレータ ADuM1300 は必要なアイソレーションを提供します(図 54 参照)。デバイスの電源もトランスを使ってアイソレーションする必要があります。トランスの DAC 側では、5 V のレギュレータが 5 V 電源を AD5024/AD5044/AD5064 に供給しています。

図 54.AD5024/AD5044/AD5064 の電流絶縁型インターフェースでの使用

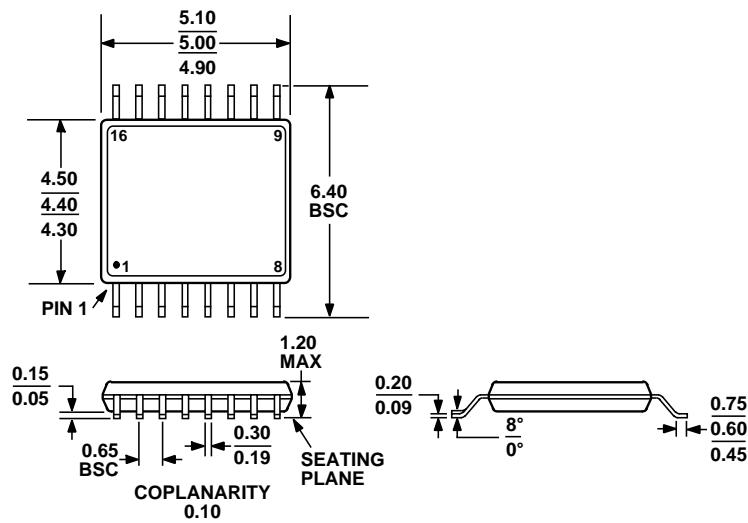

図 55.16 ピン薄型シュリンク・スマール・アウトライン・パッケージ[TSSOP]

(RU-16)

寸法: mm

## オーダー・ガイド

| Model                         | Temperature Range | Accuracy   | Resolution | Package Description | Package Option |

|-------------------------------|-------------------|------------|------------|---------------------|----------------|

| AD5064BRUZ <sup>1</sup>       | -40°C to +105°C   | ±1 LSB INL | 16 Bits    | 16-Lead TSSOP       | RU-16          |

| AD5064BRUZ-REEL7 <sup>1</sup> | -40°C to +105°C   | ±1 LSB INL | 16 Bits    | 16-Lead TSSOP       | RU-16          |

| AD5044BRUZ <sup>1</sup>       | -40°C to +105°C   | ±1 LSB INL | 14 Bits    | 16-Lead TSSOP       | RU-16          |

| AD5044BRUZ-REEL7 <sup>1</sup> | -40°C to +105°C   | ±1 LSB INL | 14 Bits    | 16-Lead TSSOP       | RU-16          |

| AD5024BRUZ <sup>1</sup>       | -40°C to +105°C   | ±1 LSB INL | 12 Bits    | 16-Lead TSSOP       | RU-16          |

| AD5024BRUZ-REEL7 <sup>1</sup> | -40°C to +105°C   | ±1 LSB INL | 12 Bits    | 16-Lead TSSOP       | RU-16          |

<sup>1</sup> Z = RoHS 準拠製品