## マルチチップ・アプリケーションにおけるADV202の使用方法

著者 : Christine Bako

## はじめに

本書では、HDTV、1080iモードにおいて2個のADV202を接続する方法を説明します。

60フィールド／秒のSMPTE274M 1080iビデオは、合計1.485Gbpsのデータレートに変換されます。

10ビット・データでは、これは約124Mバイト／秒のアクティブ・ビデオの入力データレートに変換されます。V рDATAインターフェースを使用する場合、ADV202への入力データレートは、不可逆モードで65MSPS、可逆モードで32MSPSが上限です。このため、1080i用の入力データレートを処理するには、少なくとも2個のADV202が必要です。

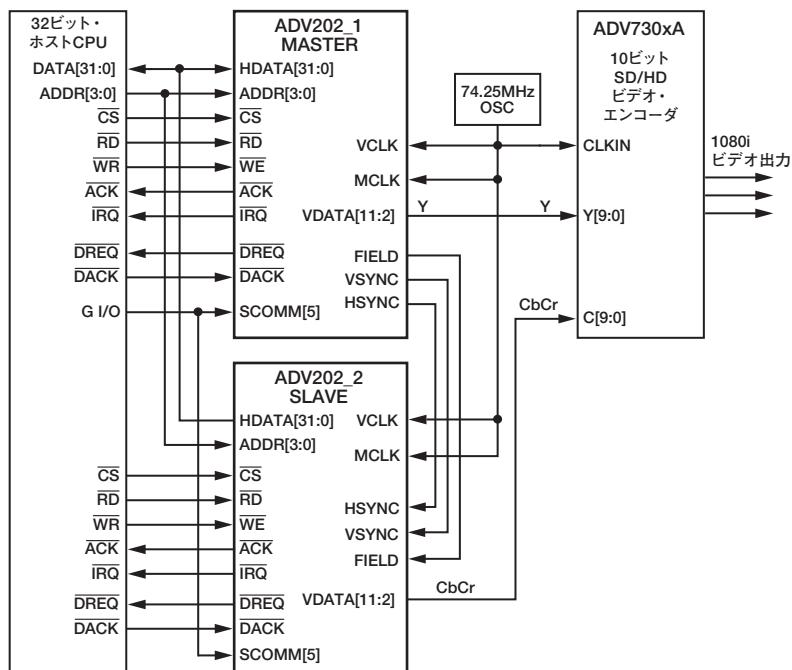

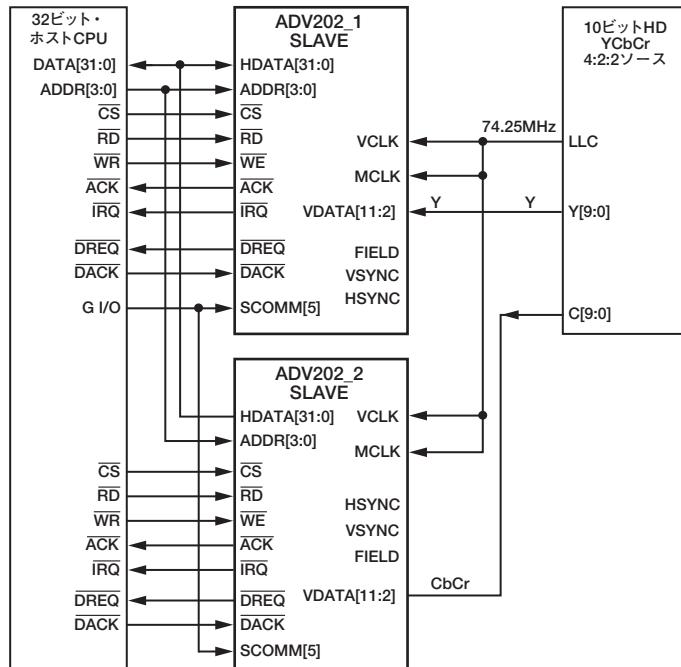

HDTVモードで2個のADV202を使用する場合、YとCbCrは別のバス上にあることが必要です。ADV202\_1では1080i輝度信号データを処理し、ADV202\_2では色差データを処理します。

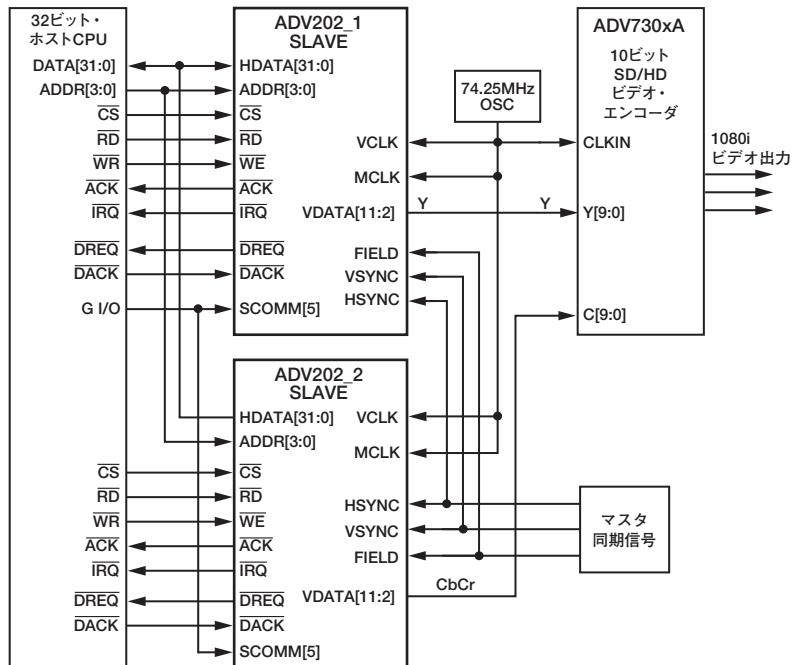

このモードのアプリケーションで2つの出力の同期をとるには、2つのデータ・ストリームがEAV/SAVコードを含む必要があります。デコードでは、マスター/スレーブまたはスレーブ/スレーブでの設定が可能です（図1と図2を参照）。エンコードでは、ADV202は常にスレーブです。

HDTVアプリケーション（1080i）において、2個のADV202で処理を行うためには、以下の条件が必要です。

- 最大入力データレート：それぞれのADV202（ADV202-150）に対して65MSPS。

- インターフェース：V рDATAバス（非圧縮ビデオ・データの入出力用）

- 圧縮モード：不可逆

1080iロスレスなどの高性能が必要な場合は、3個以上のADV202の使用を推奨します。本書で説明する原理は、3個以上のADV202を使用するアプリケーションにも適用されます。

本書は、ADV202のビデオ出力が、エンコーダやシリアルアイザなどの受信デバイスの色差／輝度信号データ入力（P.2「推奨インターフェース」を参照）の同期を必要とするデバイスに直結されるアプリケーションに適用されます。ADV202のビデオ出力がバッファやFPGAに送信される場合は、同期は重要ではありません。

REV. 0

アナログ・デバイセズ株式会社

本 社／〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル

電話03(5402)8200

大阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号

電話06(6350)6868

## 推奨インターフェース

## デコード・マスタ／スレーブ設定

図1. デコード・マスタ／スレーブ時のADV202マルチチップ・アプリケーション

## デコード・スレーブ／スレーブ設定

図2. デコード・スレーブ／スレーブ時のADV202マルチチップ・アプリケーション

## エンコード設定

図3. エンコード時のADV202マルチチップ・アプリケーション

### HDATAバスでの転送速度

HDATAバスを通じて最高のデータレートを達成するには、バースト転送設定で外部DMA DREQ/DACKモードを使用します。

### 32ビット・データに対する最大転送速度

1080iアプリケーションでは、74.25MHzのVCLKを必要とします。ADV202のデータシートによれば、最大バースト周波数は $0.35 \times JCLK$ とすることが推奨されており、これは約50MHzになるため、JCLKは少なくとも $2 \times VCLK$ であることが必要です。これは、読み出し／書き込みパルスの最大周波数です。

圧縮データが格納されるCODE FIFOの大きさは、256個以上の32ビット・ワードのサイズに設定します。32ビット幅のデータでは、アクセスの最大数は256に制限されます。16ビット幅のデータでは、512に制限されます。

したがって、HDATAバスでの32ビット・データに対する最大スループット・レートは、次のとおりです。

$$4\text{ バイト} \times 50\text{MHz} = 200\text{Mバイト/秒}$$

バースト長を128アクセスと仮定すると、CODE FIFOが圧縮フィールドの最終部分に対して128ワードを含まない場合は、フィールドがバースト境界で終了するように、FIFOはゼロで埋められます。

HDATAバスでの16ビット・データに対する最大転送速度は、次のとおりです。

$$2\text{ バイト} \times 50\text{MHz} = 100\text{Mバイト/秒}$$

バースト長を256アクセスと仮定すると、CODE FIFOが圧縮フィールドの最終部分に対して256ワードを含まない場合は、フィールドがバースト境界で終了するように、FIFOはゼロで埋められます。アプリケーションで使用するインターフェース（圧縮データをPCシステムに転送／格納するためのPCIイン

ターフェースなど）のデータ・スループット・レートは、これらの最大データレートに対応することが重要です。

### ビデオ入力－エンコード・モード

YCbCrデータは4:2:2フォーマットで、EAV/SAVタイミング・コードを伴うことが必要です。

次に、32ビットのバスが2つのADV202で共有されている場合に、32ビットのホスト・インターフェースを使用して2つのADV202をマルチチップ同期モードで設定する方法の概要を示します。

詳細については、最新のADV202データシートおよびテクニカル・ノート『ADV202入門 プログラミング・ガイド』を参照してください。

### ADV202\_1の設定

1. PLL\_HIレジスタに0x0008hを書き込み、PLL\_LOレジスタに0x0084を書き込みます。（VCLK=74.25MHz）。

2. PLL安定のため、20μs待ちます。

3. BOOTレジスタに0x008Aを書き込みます。このブート・モードは、デバイスにファームウェアをロードする必要のあるアプリケーションに使用します。

4. BUSMODEに0x000Aを書き込みます。これにより、ホスト制御データ幅が32ビットに、DMAデータ幅が32ビットに設定されます。

5. MMODEに0x000Aを書き込みます。これにより、間接データ・アクセス幅と間接アドレス・ステップ・サイズは32ビットに設定されます。

6. IADDRに0x00050000を書き込んで、プログラム・メモリの開始位置を設定します。

7. IDATAにファームウェアのすべての32ビット値を書き込んで、メモリにプログラムをロードします。

8. BOOTレジスタに0x008Dを書き込んで、リブートを開始します。これによりプログラム実行が開始されます。

9. BUSMODEに0x000Aを書き込みます。

10. MMODEに0x000Aを書き込みます。

## ADV202\_1の初期化前ルーチン

1. IADDRに0x00057F00を書き込みます。これにより、ADV202にロードされるエンコード・パラメータの開始アドレスが設定されます。

2. IDATAに0x2010503を書き込みます。これらは実際のエンコード・パラメータです。

この例では、

02=1080i輝度

01=10ビット精度

05=5レベルのウェーブレット変換

03=Y、Cユニポーラ

3. エンコード・パラメータの続き

IDATAに0x03000000を書き込みます。

03=コードブロック・サイズ128×32

00=不可逆9×7、固定テーブルを使用

00=フィールドのスキップなし

00=属性データの出力なし

4. エンコード・パラメータの続き

IDATAに0x01019500を書き込みます。

01=ビデオ・フィールド／フレームごとのターゲット・サイズ

019500=ターゲット・サイズ値（輝度の場合は103,680バイト／フィールド、または圧縮率10:1）

5. エンコード・パラメータの続き

IDATAに0x00000000を書き込みます。

00=LRCPプログラレーション・スタイル

00=EAV/SAVコードを使用、すべての同期は負極性

00=Qfactorは1×

00=j2cフォーマット

6. 残りのすべてのパラメータ位置を対象として、IDATAに0x00000000を書き込みます。

## ADV202\_1の初期化ルーチン

1. EIRQIEに0x0C00を書き込んで、SWIRQ0とSWIRQ1（アドレス0x5h）をマスク解除します。SWIRQ1をマスク解除すると、マルチチップ同期機能がイネーブルになります。

2. IRQがアサートされるのを待ちます（SWIRQ0はアドレス0x6h、ビット10でセットされ、ローレベルになります）。

3. アプリケーションIDを読み出して、プログラムが正しく初期化されたことを確認します。ここでは、0xFF82の値になります。

## ADV202\_1用にDMAチャンネルを設定する初期化後ルーチン

1. IADDRに0xFFFF1408を書き込みます。

2. IDATAに0x00120000を書き込みます。これにより、DMAチャンネル0は8バーストの32ビット・ワードに設定され、圧縮／コードブロック・データFIFOに割り当てられます。

3. IADDRに0xFFFF1408を書き込みます。

4. IDATAに0x00130000を書き込みます。

## ADV202\_2の設定

1. PLL\_HIレジスタに0x0008hを書き込み、PLL\_LOレジスタに0x0084を書き込みます。

2. PLL安定のため、20μs待ちます。

3. BOOTレジスタに0x008Aを書き込みます。このブート・モードは、デバイスにファームウェアをロードする必要のあるアプリケーションに使用します。

4. BUSMODEに0x000Aを書き込みます。これにより、ホスト制御データが32ビットに、DMAデータ幅が32ビットに設定されます。

5. MMODEに0x000Aを書き込みます。これにより、間接データ・アクセス幅と間接アドレス・ステップ・サイズは32ビットに設定されます。

6. IADDRに0x00050000を書き込んで、プログラム・メモリの開始位置を設定します。

7. IDATAにファームウェアのすべての32ビット値を書き込んで、メモリにプログラムをロードします。

8. BOOTレジスタに0x008Dを書き込んで、リブートを開始します。

9. BUSMODEに0x000Aを書き込みます。

10. MMODEに0x000Aを書き込みます。

## ADV202\_2の初期化前ルーチン

1. IADDRに0x00057F00を書き込みます。これにより、ADV202にロードされるエンコード・パラメータの開始アドレスが設定されます。

2. IDATAに0x03010503を書き込みます。これらは実際のエンコード・パラメータです。

- この例では、

- 03=1080i色差

- 01=10ビット精度

- 05=5レベルのウェーブレット変換

- 03=Y、Cユニポーラ

3. エンコード・パラメータの続き

- IDATAに0x03000000を書き込みます。

- 03=コードブロック・サイズ128×32

- 00=不可逆9×7、固定テーブルを使用

- 00=フィールドのスキップなし

- 00=属性データの出力なし

4. エンコード・パラメータの続き

- IDATAに0x01008700を書き込みます。

- 01=ビデオ・フィールド／フレームごとのターゲット・サイズ

008700=ターゲット・サイズ値（色差の場合は34,560バイト／フィールド、または圧縮率30:1）

5. エンコード・パラメータの続き

IDATAに0x00000001を書き込みます。

00=LRCPプログラレーション・スタイル

00=EAV/SAVコードを使用、すべての同期は負極性

00=Qfactorは1×

00=j2cフォーマット

6. 残りのすべてのパラメータ位置を対象として、IDATAに0x00000000を書き込みます。

**ADV202\_2の初期化ルーチン**

1. EIRQIEに0x0C00を書き込んで、SWIRQ0とSWIRQ1をマスク解除します。SWIRQ1をマスク解除すると、マルチチップ同期機能がイネーブルになります。

- 2 IRQがアサートされるのを待ちます (SWIRQ0はアドレス0x6h、ビット10でセットされ、ローレベルになります)。

3. アプリケーションIDを読み出して、プログラムが正しく初期化されたことを確認します。ここでは、0xFF82の値になります。

**ADV202\_2用にDMAチャンネルを設定する初期化後ルーチン**

1. IADDRに0xFFFF1408を書き込みます。

2. IDATAに0x00120000を書き込みます。これにより、DMAチャンネル0は8バーストの32ビット・ワードに設定され、圧縮／コードブロック・データFIFOに割り当てられます。

3. IADDRに0xFFFF1408を書き込みます。

4. IDATAに0x00130000を書き込みます。

**ADV202\_1用のプログラムを起動**

ADV202\_1のEIRQFLG (アドレス0x6h) に0x0400を書き込んでソフトウェア割込み (SWIRQ0) をクリアし、プログラムを起動します。

**ADV202\_2用のプログラムを起動**

ADV202\_2のEIRQFLG (アドレス0x6h) に0x0400を書き込んでソフトウェア割込み (SWIRQ0) をクリアし、プログラムを起動します。

**データ転送**

DREQ0がアクティブになると、ADV202ではCODE FIFOからのデータを送信する準備が整います。

ホストではその後、ADV202データシート (Rev0、13ページ「外部DMAモード — FIFO読み出し、バースト・モード」) で説明するタイミング仕様に基づいて、データ転送を開始してください。

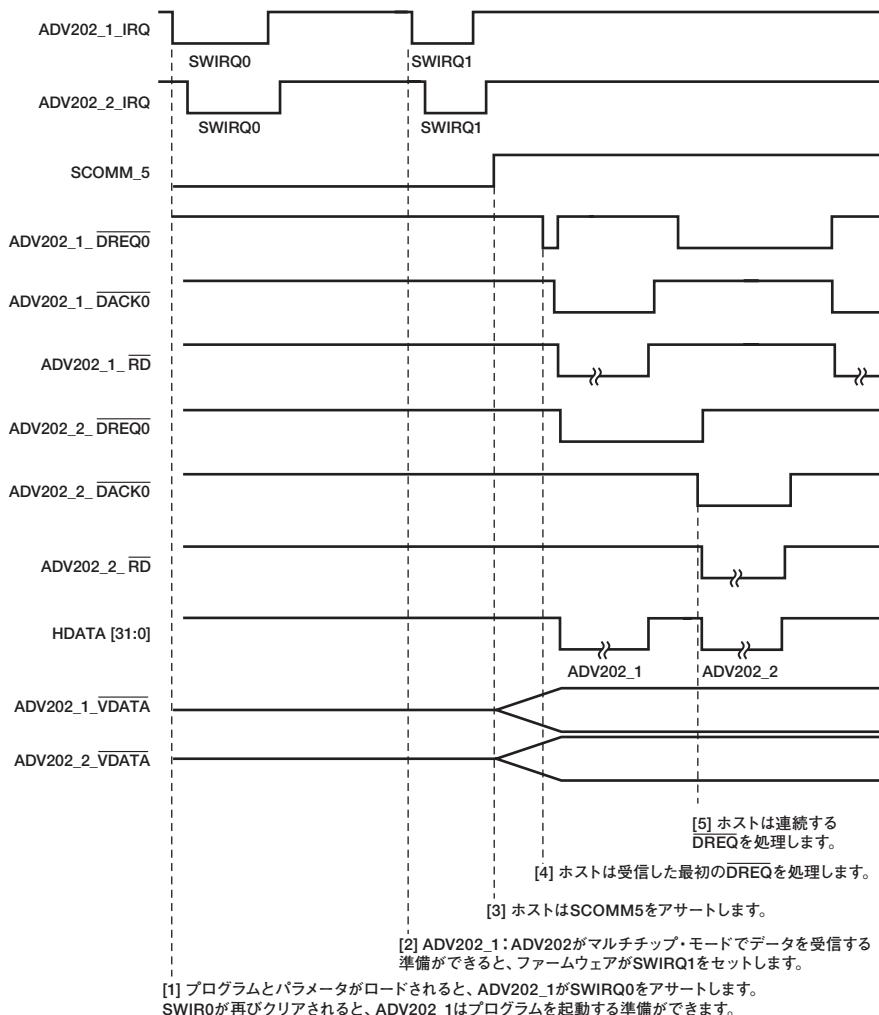

**エンコード・モード — タイミング**

図4. エンコード・モードのタイミング図

エンコード・モードでは、データ・バスは次のようにになります。VDATAバス — ウエーブレット変換エンジン／エントロピー・コーデック — 内部メモリ — CODE FIFO — HDATAバス。詳細については、アプリケーション・ノートAN-790を参照してください。

SWIRQ0は、ADV202でプログラムの起動準備ができるとすぐに各ADV202によってアサートされますが[1]、プログラムを起動するにはアドレス0x6hに0x0400を書き込んでそれをクリアする必要があります。SWIRQ1は、この直後にアサートされ[2]、ADV202でマルチチップ・モードでのデータ受信の準備ができていることを示します。ホストは、アドレス0x6hでこのビットをポーリングしなければなりません。2つのSWIRQ1がセットされてからクリアされると、ホストはSCOMM[5]ピンをアサートし、それを維持し続けます。SCOMM[5]ピンのアサートにより、ADV202はビデオ入力データのクロック入力を開始します[3]。

図4のタイミング図は、ADV202がDREQ/DACK DMAバースト・モードで設定されており、2個のADV202が32ビットのHDATAバスを共有している場合を示します。各ADV202のDMAチャンネル0は8アクセス(8×32ビット・ワード)に設定され、DREQは、RDとDACKがアサートされるまでアサート状態を維持するように設定されます(EDMODレジスタ)。

2個のADV202では、ほぼ同時にCODE FIFOから圧縮データを出力する準備ができるものと想定できます。ホストでは、受信した最初のDREQ0を処理し、各ADV202からのデータを別のメモリ位置に割り当てます。ADV202\_1からのDREQ0が処理される間に、ADV202\_2はすでにDREQ0をアサートしています。ADV202\_2からのDREQ0は、ホストがADV202\_2へのDACKとRDをアサートするまで、アサートされた状態にあります。

32ビット・アクセスを使用するDREQ/DACK DMAバースト・モードでの最大アクセス数は、256とされています(『ユーザ・ガイド』の「EDMODレジスタ」を参照)。1080iモードで、32ビットのHDATAバスを2個のADV202で共有する場合は、アクセス数を8×32ビット・アクセスに設定することを推奨します。これにより、高圧縮率を使用する場合に、CODE FIFOからのデータ・フローを一定にできます。

## ビデオ出力—デコード・モード

圧縮されたビデオ・データは、HDATAバスを通じてADV202にロードされます。以下では、32ビットのホスト・インターフェースを使用して、2個のADV202をマルチチップ同期モードで設定する方法の概要を示します。特に明記しない限り、この手順はマスタ／スレーブのアプリケーションでもスレーブ／スレーブのアプリケーションでも同じです。詳細については、最新のADV202データシートおよびテクニカル・ノート『ADV202入門 プログラミング・ガイド』を参照してください。

## ADV202\_1の設定

1. PLL\_HIレジスタに0x0008hを書き込み、PLL\_LOレジスタに0x0084を書き込みます。

2. PLL安定のため、20μs待ちます。

3. BOOTレジスタに0x008Aを書き込みます。このブート・モードは、デバイスにファームウェアをロードする必要のあるアプリケーションに使用します。

4. BUSMODEに0x000Aを書き込んでイネーブルにします。これにより、ホスト制御データ幅が32ビットに、DMAデータ幅が32ビットに設定されます。

5. MMODEに0x000Aを書き込みます。これにより、間接データ・アクセス幅と間接アドレス・ステップ・サイズは32ビットに設定されます。

6. IADDRに0x00050000を書き込んで、プログラム・メモリの開始位置を設定します。

7. IDATAにファームウェアのすべての32ビット値を書き込んで、メモリにプログラムをロードします。

8. BOOTレジスタに0x008Dを書き込んで、リブートを開始します。これにより、プログラム実行が開始されます。

9. BUSMODEに0x000Aを書き込みます。

10. MMODEに0x000Aを書き込みます。

## ADV202\_1の初期化ルーチン

1. IADDRに0x00057F00を書き込みます。これにより、ADV202にロードされるデコード・パラメータの開始アドレスが設定されます。

2. IDATAに0x0201XX03を書き込みます。これらは実際のデコード・パラメータです。

この例では、

02=1080i輝度

01=10ビット精度

XX=この情報はコード・ストリームから得られます

03=Y, Cユニポーラ

これらの値は、エンコード・モードで使用したものと一致させてください。

3. デコード・パラメータの続き

IDATAに0xFFFFFFFFXXを書き込みます。この情報は、コード・ストリームから得られます。

4. デコード・パラメータの続き

スレーブ／スレーブ設定では、IDATAに0xXX0000XXを書き込みます。

XX=この情報はコード・ストリームから得られます

00=デコード・スレーブ・モード

00=デコード分解能設定

XX=この情報はコード・ストリームから得られます

マスタ／スレーブ設定では、IDATAに0xXX0010XXを書き込みます。

XX=この情報はコード・ストリームから得られます

10=デコード・マスタ・モード

00=予備

XX=この情報はコード・ストリームから得られます

## ADV202\_1の初期化ルーチン

1. EIRQIEに0x0C00を書き込んで、SWIRQ0とSWIRQ1をマスク解除します。SWIRQ1をマスク解除すると、マルチチップ同期機能がイネーブルになります。

2. IRQがアサートされる(ローレベルになる)のを待ちます。

3. アプリケーションIDを読み出して、プログラムが正しく初期化されたことを確認します。ここでは、0xFFA2の値となります。

**ADV202\_1用にDMAチャンネルを設定する初期化後****ルーチン**

1. IADDRに0xFFFF1408を書き込みます。

2. IDATAに0x00120000を書き込みます。これにより、DMAチャンネル0は8バーストの32ビット・ワードに設定され、圧縮／コードブロック・データFIFOに割り当てられます。

3. IADDRに0xFFFF1408を書き込みます。

4. IDATAに0x00130000を書き込みます。

**ADV202\_2の設定**

1. PLL\_HIレジスタに0x0008hを書き込み、PLL\_LOレジスタに0x0084を書き込みます。

2. PLL安定のため、20μs待ちます。

3. BOOTレジスタに0x008Aを書き込みます。このブート・モードは、デバイスにファームウェアをロードする必要のあるアプリケーションに使用します。

4. BUSMODEに0x000Aを書き込みます。これにより、ホスト制御データ幅が32ビットに、DMAデータ幅が32ビットに設定されます。

5. MMODEに0x000Aを書き込みます。これにより、間接データ・アクセス幅と間接アドレス・ステップ・サイズは32ビットに設定されます。

6. IADDRに0x00050000を書き込んで、プログラム・メモリの開始位置を設定します。

7. IDATAにファームウェアのすべての32ビット値を書き込んで、メモリにプログラムをロードします。

8. BOOTレジスタに0x008Dを書き込んで、リブートを開始します。

9. BUSMODEに0x000Aを書き込みます。

10. MMODEに0x000Aを書き込みます。

**ADV202\_2の初期化前ルーチン**

1. IADDRに0x00057F00を書き込みます。これにより、ADV202にロードされるデコード・パラメータの開始アドレスが設定されます。

2. IDATAに0x0301XX03を書き込みます。これらは実際のデコード・パラメータです。

この例では、

03=1080i色差

01=10ビット精度

XX=この情報はコード・ストリームから得られます

03=Y、Cユニポーラ

3. デコード・パラメータの続き

IDATAに0xFFFFFFFFXXを書き込みます。この情報はコード・ストリームから得られます。

**4. デコード・パラメータの続き**

スレーブ／スレーブ設定では、IDATAに0xXX0000XXを書き込みます。

XX=この情報はコード・ストリームから得られます

00=デコード・スレーブ・モード

00=デコード分解能設定

XX=この情報はコード・ストリームから得られます

マスター／スレーブ設定では、IDATAに0xXX0010XXを書き込みます。

XX=この情報はコード・ストリームから得られます

10=デコード・マスター・モード

00=予備

XX=この情報はコード・ストリームから得られます

**ADV202\_2の初期化ルーチン**

1. EIRQIEに0x0C00を書き込んで、SWIRQ0とSWIRQ1をマスク解除します。SWIRQ1をマスク解除すると、マルチップ同期機能がイネーブルになります。

2. IRQがアサートされる（ローレベルになる）のを待ちます。

3. アプリケーションIDを読み出して、プログラムが正しく初期化されたことを確認します。ここでは、0xFFA2の値となります。

**ADV202\_2用にDMAチャンネルを設定する初期化後****ルーチン**

1. IADDRに0xFFFF1408を書き込みます。

2. IDATAに0x00120000を書き込みます。これにより、DMAチャンネル0は8バーストの32ビット・ワードに設定され、圧縮／コードブロック・データFIFOに割り当てられます。

3. IADDRに0xFFFF1408を書き込みます。

4. IDATAに0x00130000を書き込みます。

**ADV202\_1用のプログラムを起動**

ADV202\_1のEIRQFLG（アドレス0x6h）に0x0400を書き込んでソフトウェア割込み（SWIRQ0）をクリアし、プログラムを起動します。

**ADV202\_2用のプログラムを起動**

ADV202\_2のEIRQFLG（アドレス0x6h）に0x0400を書き込んでソフトウェア割込み（SWIRQ0）をクリアし、プログラムを起動します。

**データ転送**

DREQ0がアクティブになると、ADV202ではデータを受信する準備が整います。ホストではその後、ADV202データシート（Rev0、12ページ「外部DMAモード—FIFO書き込み、バースト・モード」）で説明するタイミング仕様に基づいて、データ転送を開始してください。

## デコード・モード—タイミング

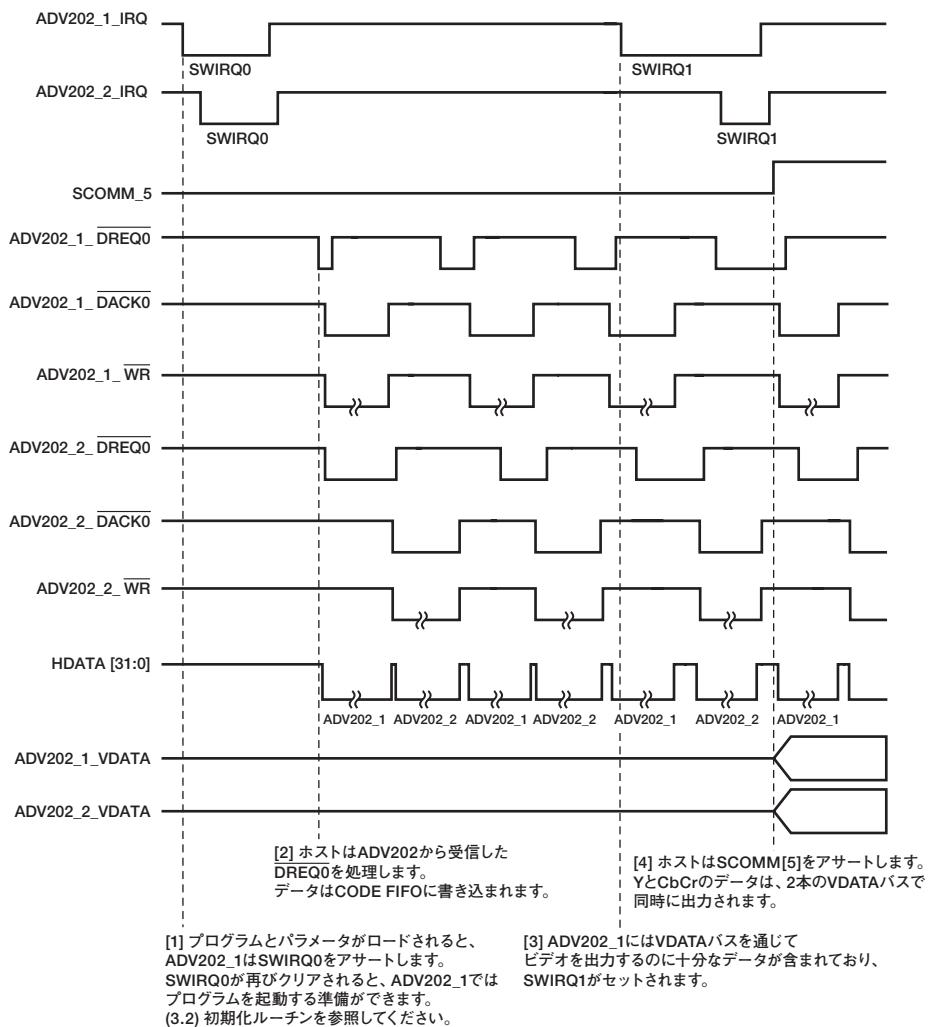

図5. デコード・モードのタイミング図

デコード・モードでは、データ・バスは次のようにになります。HDATAバス — CODE FIFO — ウエーブレット変換エンジン／エントロピー・コーデック — 内部メモリ — ピクセル・インターフェースVDATAバス。詳細については、アプリケーション・ノートAN-790を参照してください。

SWIRQ0は、ADV202でプログラムの起動準備ができるとすぐにADV202によってアサートされますが[1]、プログラムを起動するにはアドレス0x6hに0x0400を書き込んでそれをクリアする必要があります。2つのADV202は、ほぼ同時に $\overline{DREQ0}$ をアサートします。ホストでは、受信した最初の $\overline{DREQ0}$ を処理し[2]、もう一方のADV202からの $\overline{DREQ0}$ と交互に処理してください。

図5のタイミング図に示す例では、ADV202は、32ビットのHDATAバスを共有して $\overline{DREQ}/\overline{DACK}$  DMAバースト・モードで設定されています。 $\overline{DREQ}$ は、 $\overline{DACK}$ と $\overline{WR}$ がアサートされるまで、アサート状態を維持するように設定されます。

CODE FIFOが満杯になり、コードストリーム・データがエントロピー・コーデックとウェーブレット変換エンジンを介してピクセル・インターフェースに渡されると、ADV202では、VDATAバスを通じて非圧縮のビデオ・データを出力する準備ができています。この時点では、SWIRQ1がアサートされます[3]。ホストは、アドレス0x6hでこのビットをポーリングしな

ければなりません。2つのSWIRQ1がセットされてからクリアされると、ホストは、SCOMM[5]ピンをアサートし、このピンをアサートし続けます[4]。SCOMM[5]ピンのアサートにより、ADV202は2つのVDATAバスでビデオの出力を開始します[4]。

2個のADV202は、ほぼ同時にデータを要求する準備ができるものと想定できます。ホストでは、受信した最初の $\overline{DREQ0}$ を処理し、エンコード・モードであらかじめADV202に割り当てられた外部ロケーションから当該ADV202にデータを書き込みます。ADV202\_1からの $\overline{DREQ0}$ を処理した後では、ADV202\_2はすでに $\overline{DREQ0}$ をアサートしているはずです。ADV202\_2からの $\overline{DREQ0}$ は、ホストがADV202\_2への $\overline{DACK0}$ と $\overline{WR}$ をアサートするまで、アサートされた状態になります。ホストでは、ADV202\_2に割り当てられた外部ロケーションからのデータをHDATAバスに書き込みます。

連続的なビデオ・データ出力を保証し、CODE FIFOのオーバーフローを回避するには、アクセス数を8アクセスの32ビット・ワードに設定することを推奨します。

### マルチチップ同期

入力での同期（エンコード・モード）は、各ADV202が同時に同じフィールドのエンコードを開始するために必要です。

出力での同期（デコード・モード）は、別個の出力がHDビデオ・エンコーダ／シリアルライザ（すべてのデータが入力において整列していることが必要なデバイス）に直接送信される場合にだけ必要です。YとCbCrのストリームを最初にバッファやFPGAに送信するというような、別の設定を使用する場合は、ADV202の出力での同期は必要ありません。

複数のADV202を使用するアプリケーションでは、出力での同期はいくつかの要因によって決定されます。

デコード—マスタ／スレーブ設定では、マスタのH、V、F出力はスレーブのH、V、F入力に接続され、各SCOMM[5]ピンはホスト上の同じGPIO出力に接続されることになります。デコード—スレーブ／スレーブ設定では、2個のADV202に共通のHVFが外部マスターによって生成され、各SCOMM[5]ピンはホスト上の同じGPIO出力に接続されます。EAV/SAVタイミング・コードは、HVF入力に基づいて生成されます。

エンコード設定では、タイミング情報は、入力データに含まれるEAV/SAVコードから得られます。

デコードまたはエンコード・モードでマルチチップ同期をイネーブルにするには、2個のデバイスでEIRQIEレジスタのソフトウェア割込み1、SWIRQ1をマスク解除することが必要です。ホストは、2個のADV202にポーリングして、EIRQFLGレジスタのSWIRQ1フラグがセットされているかどうかを調べる必要があります。2つのSWIRQ1がアクティブの場合にだけ、ホストはSCOMM[5]をアサートしてください。マルチチップ同期モードでは、SCOMM[5]ピンには、デバイスがデコード・モードに設定されている場合にVDATAバスでの出力を開始する機能があり、エンコード・モードではVDATAバスを介してデータのクロック入力を開始する機能があります。

デコード—マスター／スレーブ設定では、以下のことも考慮する必要があります。

すべてのスレーブADV202には、HSYNC<sup>1</sup>アクティブ入力からビデオ・データ出力までに一定のタイミング遅延があります。ADV202では、設計により7CLKサイクルになっています。この遅延の補償に必要なレジスタは、マスターADV202のファームウェアによって設定されます。

デバイスがマルチ同期モードに設定されている（SWIRQ1がイネーブルなど）とき、ファームウェアは、このレジスタの値をマスター・デバイスの0xFFFF0440レジスタに書き込みます。

ADV202についての詳細は、弊社製品ページ（[www.analog.com/jp/ADV202](http://www.analog.com/jp/ADV202)）をご覧ください。