# 高速 CMOS 入力 DAC のセットアップ時間とホールド時間の測定 by Steve Reine

高速 DAC から最適な性能を得るには、セットアップ時間とホールド時間が十分確保されなければなりません。200 MSPS から 250 MSPS のクロックレートでの FPGA/ASIC/DAC の全タイミング時間を推定する事は簡単な作業ではありません。回路設計者がタイミングの検証を完了できるようにするには、データシートのタイミング仕様が明確にレイアウトされ、十分に規定されていなければなりません。

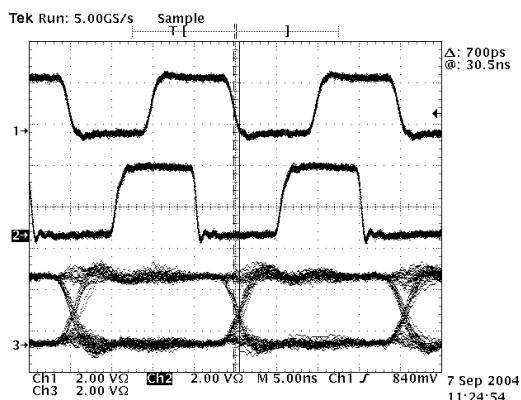

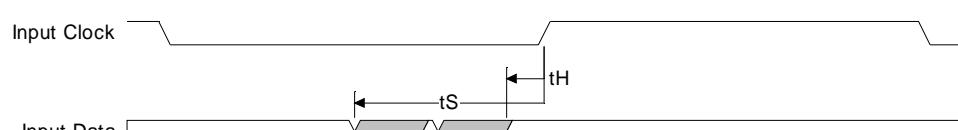

セットアップ時間、ホールド時間の仕様を満たしていれば、クロック・エッジがラッチする瞬間、DAC 内部のラッチのデータは安定します。逆にラッチを行うクロック・エッジが来た瞬間、データが過度的な状態で変化していると、ラッチされたデータは最終的に決定したものではなく、DAC アナログ出力のノイズフロアが増大します。AD9777 または AD9786 のような DAC では ns の数分の 1 仕様を満たしていないとも、DAC のノイズフロアに劇的なインパクトを与える可能性があります。図 1、図 2、図 3 は AD9786 のクロック入力/出力信号とデータ信号のオシロスコープ測定結果を示しますが、図 1 はセットアップ時間の仕様がちょうど満たされている時、図 2 はセットアップ時間の仕様が 0.1ns 満たされていない場合、図 3 はセットアップ時間の仕様が 0.5ns 満たされていない場合です。この場合、AD9786 は、1 倍インターポレーションでマスター モードです。従って入力サンプル・レートは、DAC 出力のサンプル・レートと同じです。図 1 はこれらの条件下ではこの DAC のセットアップ時間が-0.7 ns になっている事に注目してください。負のセットアップ時間はキープ・アウト・ウインドがラッチを行うクロック（この場合立下り）エッジの完全に右側にシフトしている事によります。すべての 3 つのグラフで、点線はクロック・エッジの中央を示します。又実線は、データ変移の中間を示します。

図1.セットアップ仕様をちょうど満たしているDACのタイミング

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利⽤によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示または暗示で許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語資料はREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

REV. 0

アナログ・デバイセズ株式会社

本 社／〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウス

タワービル

電話 03 (5402) 8200

大阪営業所／〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラス

タワー

電話 06 (6350) 6868

従来、セットアップ時間はラッチを行うクロック・エッジが来る（この時点ではデータが安定していないければなりません）前に必要な時間量です。この時間は、通常最小値として仕様に規定されています。デジタル回路設計者は、ラッチを行うエッジが来る前にデータが安定しなければならない最小時間としてセットアップ時間を規定します。例えば、1ns (min) のセットアップ時間は、ラッチを行うクロック・エッジが来る少なくとも 1ns 前に、データが安定していないなければならないことを意味します。

ホールド時間は、ラッチを行うエッジの後にデータが正しく取得されるように、データが安定していないなければならない時間量です。この時間は、通常最小時間として規定されています。たとえば 2ns (min) のホールド時間は、ラッチを行うクロック・エッジ後少なくとも 2 ns の間は、データが安定している必要があることを意味します。

キープ・アウト・ウインドはラッチを行うクロック・エッジ前後の全期間として定義されますが、セットアップ時間とホールド時間の両方を含みます。前に示したセットアップ時間 1 ns、ホールド時間 1ns の例では、キープ・アウト・ウインドはラッチを行うクロック・エッジの 1ns 前からクロック・エッジの 1ns 後までです。

セットアップおよびホールドの従来の定義は簡単に理解できます。しかし、高速 DAC では、複雑なクロックツリーと高サンプル・レートにより、ときどき外部から印加されたラッチを行うクロック・エッジと、実際にデータがラッチする時間との間の時間的ずれがクロックサイクルのかなり大きな部分を占める可能性があります。

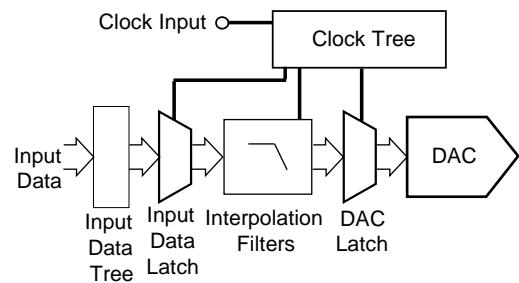

代表的な DAC クロックツリーとラッチ構成を図 4 に示します。

図 4. 代表的なインター・ポレーション DAC のクロック

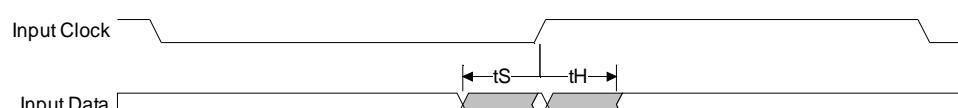

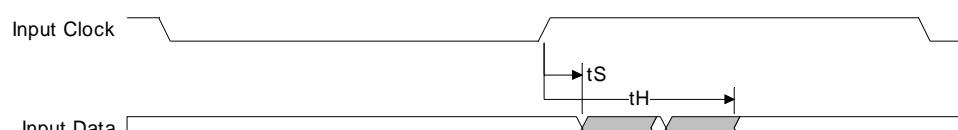

アナログ・デバイセズのインター・ポレーション DAC、AD9777 や AD9786 の場合、この条件ではキープ・アウト・ウインドは大幅に遅延して、セットアップ時間が 0.0、又は負の数にさえなる可能性があります。特定の DAC は、セットアップ時間が -1.0 ns およびホールド時間が 3.0 ns になる可能性もあります。この場合のキープ・アウト・ウインドはラッチを行うクロック・エッジの 1 ns 後からそのエッジの 3ns 後までです。可能性はより低いですが、DAC の内部同期のために、実際にはキープ・アウト・ウインドは左に移動、又は時間的に進む可能性もあります。この場合、セットアップ時間は正で、ホールド時間は負の数になります。図 5a、図 5b と図 5c に、キープ・アウト・ウインドがラッチを行うクロック・エッジに対し対称の場合、右にシフトしている場合（セットアップ時間は負）、左にシフトしている場合（ホールド時間は負）の各状況についてまとめてあります。

図 5a. セットアップ時間およびホールド時間は、ラッチを行うクロック・エッジに対して対称 ( $t_s$  および  $t_h$  は両方とも正)

図 5b. セットアップ時間およびホールド時間は、ラッチを行うクロック・エッジよりも遅れている ( $t_s$  は負、 $t_h$  は正)

図 5c. セットアップ時間およびホールド時間は、ラッチを行うクロック・エッジより進んでいる。 ( $t_s$  は正、 $t_h$  は負)

デジタル回路設計者にとっては、セットアップ時間やホールド時間が負である事はそれほど重要ではありません。全キープ・アウト・ウインドができるだけ短い事の方がはるかに重要です。DACのタイミング仕様は、DACに対するFPGA又はASICデジタルインターフェイスの全タイミング時間の一部しか表していません。しばしば、アプリケーション・エンジニアはセットアップ時間、ホールド時間、キープ・アウト・ウインドがどのように変動するか（ときどき温度に対する変動も含む）を確認ために一つ又は複数のロットについて多数の部品をテストしなければなりません。DACのデジタル入力を駆動するFPGAやASICに、DLL又は他の同様の同期デバイスが使用される場合もありますが、それらはそれら自信の変動もあります。高速CMOS入力DACは、250MSPS（全サイクル・タイムが4nsになります。）程度の高速で動作する可能性あります。このような場合、DAC自信のキープ・アウト・ウインドはおそらく1nsから1.5nsのオーダーです。これは、タイミングに必要な時間の25%以上が既にDACによって使用されている事を意味します。従ってデジタル設計者はDACを駆動するデジタル駆動回路の中のタイミングについてよく注意する必要があります。

## セットアップ時間、ホールド時間の測定

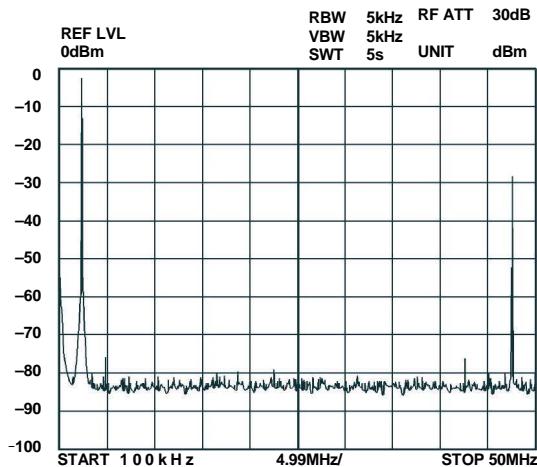

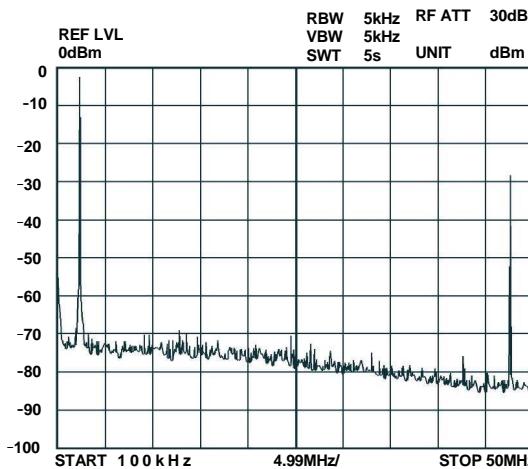

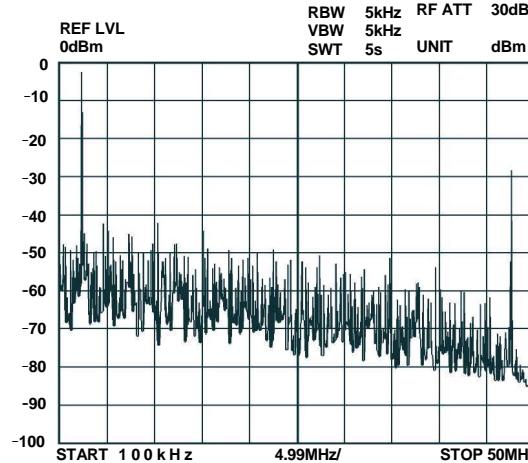

高速DACはワイヤレス・トランスマッタ・アプリケーションによく使用されます。このため、それらの仕様の多くは時間領域ベースではなくスペクトルで表します。その例が、スプリアス・フリー・ダイナミック・レンジ(SFDR)、スペクトル・ノイズ密度、そして隣接チャネル・リーケ比(ACLR)です。高速DACのセットアップ時間、ホールド時間はそれ故スペクトル的に測定されます。図6は50MSPSでサンプリングし、2.4MHzで信号を再生しているDACを示します。図6はセットアップ時間、ホールド時間の仕様が満たされています。図7では、キープアウト領域がわずか0.1nsだけDACのタイミング仕様を満たしていません。セットアップ時間又はホールド時間のどちらのタイミング設定を満たしていないかに関係なく、これらの条件のいずれかを満足しないと同じ現象になります。図7に注目すればノイズフロアがどのように著しく上昇しているかがわかります。これはタイミング仕様を満足していない現れです。図8では、タイミング仕様を0.5ns満たしていないので、タイミング同期回路が動作不能になっていて、そのDACのアナログ出力の性能が大幅に劣化していることが明らかにわかります。

図6. セットアップ時間、ホールド時間の仕様を満足するDACタイミング

図7. セットアップ時間、ホールド時間の仕様を0.1ns満足しないDACタイミング

図8. セットアップ時間、ホールド時間の仕様を0.5ns満足しないDACタイミング