# アプリケーション・ノート

### CMOS DAC とオペアンプをベースにしたプログラマブル・ゲイン・アンプ Part I

著者: John Wynne

アンプのゲインをソフトウェアでプログラムできることは設計 者にとって非常に便利なことです。このプログラム可能なゲイ ンとは、単に 3 種類か 4 種類のゲイン・レベルを設定できると いうことではなく、ゲイン・レベルを非常に細かくプログラム するための要件に関するものです。PGA 回路の制御用としては CMOS D/A コンバータ (DAC) が適しています。CMOS DAC は 上の 2 つの条件を満たすだけではなく、低価格、高精度という 特徴も備えています。CMOS DAC を使って PGA を作成する従 来の方法では、シンプルな反転オペアンプ回路の帰還ループ内 に DAC を配置します。DAC はプログラマブル抵抗として動作 し、回路ゲインのデジタル制御を実現します。高い回路ゲイン は、大きな値の実効帰還抵抗を必要とします。しかし、実効帰 還抵抗が大きくなると、正確な値が次第に不明確なものになっ てしまいます。その結果、回路のゲイン精度はゲインが高くな るにつれて低下します。このアプリケーション・ノートは Part I と Part II からなる 2 部構成となっています。この Part I では、シ ングル DAC をベースにした PGA 回路について解説し、その回 路から発生するゲイン誤差を分析します。また、PGA の精度を 制限する DC 誤差の発生源についても解説します。アナログ・ デバイセズから最近リリースされた 2 つの CMOS DAC 製品 「AD7534」と「AD7538」を組み合わせることで、PGA 回路内 での用途に適した多くの機能を実現できます。AD7534 は 20 ピ ン、0.3 インチ幅のパッケージを採用しており、8 ビット+6 ビットのフォーマットでデータをロードします。AD7538 は 24 ピン、0.3 インチ幅のパッケージを採用しており、14 ビットの パラレル・ローディング・フォーマットをサポートしています。 この 2 つの製品の仕様は類似しています。14 ビット AD7534 ベースの PGA 回路と 12 ビット AD7545 ベースの PGA 回路の性 能については詳細な比較を行っています。アプリケーション・ ノートの Part II では、デュアル DAC を使って作成した PGA 回 路について解説しています。これらの回路のメリットは、シン グル DAC ソリューションより広いダイナミックレンジで優れた 精度を提供できる点です。現在提供中のモノリシック・デュア ル 8 ビット DAC (AD7528) と 12 ビット DAC (AD7537、 AD7547、AD7549) で、費用効果的なソリューションを手にす ることができます。

# 基本的な式

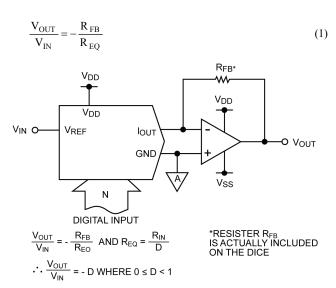

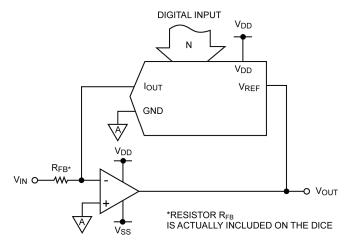

DACをPGAの構成要素にする場合は、反転オペアンプ回路構成 の入力経路とは逆の帰還経路にその回路を挿入します。図 1 に この 2 つの構成を示します。図 1aの伝達関数は次のように表さ れます。

図 1a. 減衰機能を備えた標準 DAC 構成

$R_{EO}$ は  $V_{REF}$  ピンから  $I_{OUT}$  ピンまでの DAC の等価伝達インピーダ ンスです。

$$R_{EQ} = \frac{2^n R_{IN}}{N} \tag{2}$$

ここで、

nはDACの分解能です。

Nは10進数のDAC入力コードです。

$R_{IN}$ は DAC(R-2R DAC の  $R_{LAD}$  =  $R_{IN}$ )の一定の入力イン ピーダンスです。

この式を式 1 に代入し、DAC のゲイン誤差がゼロだとすると  $(R_{IN} = R_{FB})$ 、伝達関数は次のように簡素化されます。

$$\frac{V_{OUT}}{V_{IN}} = -\frac{N}{2^n} \tag{3}$$

この比は一般に D で表されます。したがって、この比はデジタ ル入力ワードの分数表現です。

$$\frac{V_{OUT}}{V_{IN}} = -D \tag{4}$$

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本語の戦力を開発は大び登録商標は、各社の所有に属 します。※日本語資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

© Analog Devices, Inc. All rights reserved.

AN-320A

DACネットワーク(回路)と帰還抵抗 $R_{FB}$ を 図 1bに示すように取り換えると、理論上の伝達関数は式 3 の逆数となります。

GAIN IDEAL =

$$\frac{V_{OUT}}{V_{IN}} = \frac{-2^{n}}{N} = \frac{-1}{D}$$

(5)

図 1b. 回路要素を取り換えた DAC 構成でゲインを提供

8 ビット DAC の場合、式 5 は回路のゲインが 255 ステップで 256 (入力コード 00000001) からユニティ (実際は 256/255 = 全 ビット 1 の入力コード) まで変化することを示しています。全 ビット 0 のコードは使用されません。これによってオープン・ループ状態を回避し、アンプが飽和するのを防ぐことができます。すべてがゼロ(全ビットがオフ)のコードを除外すれば、 $2^n$ -1 のコードが有効となり、 $2^n$ -1 の出力レベルが選択可能となります。 dB の単位で表すと、ダイナミックレンジは次のようになります。

$$20\log_{10}(2^{n}-1) \tag{6}$$

8 ビット・デバイスの場合、ダイナミックレンジは約 48dBです。 コンバータの分解能が 1 ビット上がると、ダイナミックレンジ は 6dB増大します。したがって、12 ビット・デバイスでは最大

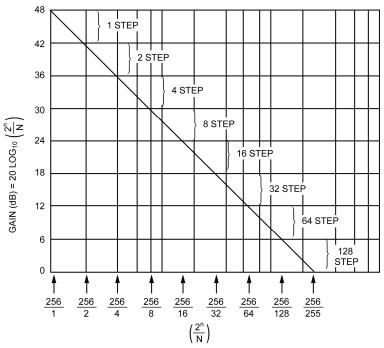

ダイナミックレンジが 72dBとなります。使用可能なプログラマ ブル・ゲインの数と密接な関係にあるのは、最小ゲインから最 大ゲインまでの範囲におけるその分布です。図2は式5をグラ フ化したもので、回路のゲインはdB単位でプロットされていま す(8ビットDACの場合)。このグラフでは、使用可能な全ス テップ数またはLSBの 1/2 (128) が 0~+6dBの範囲 (1~2 のゲ イン) に対応し、ステップ数の 1/4 (64) が次の 6dBゲイン (+6  $\sim +12dB$ または 2 $\sim 4$  のゲイン) に対応し、ステップの 1/8(32) が次の 6dB (+12~+18dBまたは 4~8 のゲイン) に対応し ています(以下同様)。図 2 は、回路ゲインが 6dBバンド単位 で増大するにつれて使用可能なゲイン・ステップ数が減ること を明確に示しています。図2からわかるように、最後の6ビッ ト・ゲイン・バンド (+42dB~+48dBまたは 128~256 ゲイン) は 1 ステップでのみ対応しています。これは、DACデジタル・ コードが 10 進数の 2 から 1 に変化するときに起こります。プロ グラマブル・ゲイン・ステップの大部分はゲイン範囲の最下部 に集中しており、隣り合うゲイン設定間の分解能は非常に高精 細なもの(0.05dB未満)となります。図 2 からこのステップの 「集中」がPGA回路の唯一の欠点に思えるかも知れませんが、実 際にはそうではありません。さまざまな誤差源を考慮すると、 実際の性能は理論値をかなり下回ります。

### 誤差の定義

性能低下は主に DAC の積分直線性の問題に起因しており、これによってゲイン増に伴うシステム精度の急激な劣化が生じます。この原因を理解するのは難しくありません。たとえば、使用するデバイスが 8 ビット DAC で、必要なゲインが 16 と仮定すると、DAC 入力コードは 16 (10 進値) となります。DAC が 8 ビットの直線性、すなわち $\pm$ 0.2%FS または $\pm$ 1/2LSB を示す場合、有効な入力コードの範囲は 15.5 $\sim$ 16.5 です。これは、式 5 のシステム・ゲインの変動幅が 256/15.5 (= 16.51)  $\sim$ 256/16.5 (= 15.51) であることを意味します。DAC 自身の最大誤差が $\pm$ 0.2%であっても、誤差は $\pm$ 3%となります。ゲインが大きくなると、誤差も大きくなります。

図 2. 8 ビット DAC のデジタル・コード 対 ステップ分布 (dB)

式2の伝達関数は、DACにゲイン誤差がないものと仮定してします。しかし、DACのゲイン誤差は実際に存在するので、式5の理論上のゲイン誤差はユニティに近い項で乗算されます。この乗算項は、ゲイン誤差が小さいほどユニティに近づきます。直線性誤差とゲイン誤差の両方が含まれる場合、システム・ゲイン式は次のようになります。

GAIN ACTUAL =

$$\frac{V_{OUT}}{V_{IN}} = -\frac{2^{n}}{(N+X)(1+\Delta)}$$

(7)

ここで、Xは直線性誤差(LSB)です。

さらに、

$$(1+\Delta) = \frac{R_{FB}}{R_{IN}}$$

理論上のゲインと実際のゲインの差は、パーセンテージ項で次のように表されます。

$$E(\%) = -\left[\frac{\Delta}{(1+\Delta)} + \frac{1}{(1+\Delta)} \left(\frac{X}{N+X}\right)\right] \bullet 100\% \tag{8}$$

DAC のゲイン誤差はゼロに調整できますが、積分非直線性を低減する方法はないので、最初に DAC の非直線性のみに起因するゲイン誤差(%) について考え、次に DAC ゲイン誤差項を加えるのが有益です。

#### 役に立つクイック・ガイドライン

DAC ゲイン誤差がゼロの場合、式8は次のように簡素化できます。

$$E(\%) = -\left(\frac{X}{N+X}\right) \bullet 100\% \tag{9a}$$

この式は、追加誤差項を式 9a に加える場合に、ユニティ以外のすべてのゲイン設定に適用できます。R-2R ラダー・ネットワー

クの場合、最大出力電流(DAC に全ビット 1 が適用される)は 必ず入力電流より 1LSB 小さな値となります。LSB で表される 「損失」電流は、ラダー終端抵抗経由で信号グラウンドに流れま す。したがって、ユニティのゲイン設定では、1LSB に相当する 固有の誤差項(%)を式 9a の誤差式(%)に追加する必要があ ります。

式 9a を変形すれば、有用なゲイン誤差(%) 式を得ることができます。この場合、プログラムされたゲインと DAC 直線性(精度)に基づいて次のように表します。

$$E(\%) = -\left(\frac{2^{n}}{N+X}\right)\left(\frac{X}{2^{n}} \bullet 100\%\right)$$

(9b)

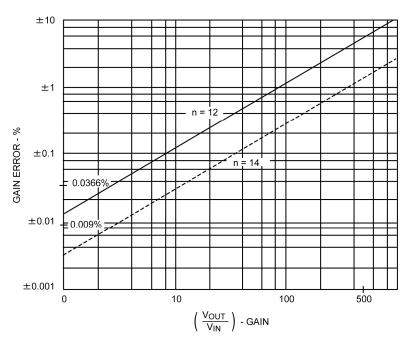

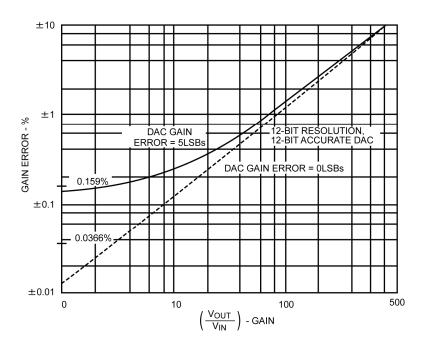

要するに、最大ゲイン誤差(%)は、DAC直線性(%)と必要なゲインとの積になります。これは、ユニティより大きなゲインに対して出力誤差を評価する際のクイック・ガイドラインとなります。図3の直線は式9aをグラフ化したもので、12 ビット精度/12 ビット分解能のDACに関するものです。この図では、ゲインの増大に伴ってゲイン誤差も増大しています。これと比較するために、同図には14 ビット精度/14 ビット分解能のDACに関するグラフを破線で示しています。直線性誤差Xは負または正の値なので、図3の縦軸は±E(%)で目盛られています。しかし、これは優れた図ですが、式9aの近似的なグラフに過ぎません。図3のゲインと誤差の関係を示す直線は、正と負の最大ゲイン誤差が全ゲイン範囲において対称的であることを示唆しています。しかし、実際には非常に高いゲインでは最大ゲイン誤差はかなり非対称的であり、ゲインが増大するとその誤差の非対称性も増大します。

これは式 9aの分母の±X直線性項によるもので、ゲインが増大する(Nが小さくなる)と、影響も大きくなります。非対称性の大きさは、付録1の表AIの結果から確認できます。

図 3. 12 ビット精度/12 ビット分解能 DAC ベースの PGA システムと 14 ビット精度/14 ビット分解能 DAC ベースの PGA システムの最悪時 ゲイン誤差の比較(DAC ゲイン誤差はどちらの場合もゼロ)

AN-320A

この表では、正と負の両方の直線性項を使用するAD7545LNに関して、式 9aの計算値を示しています。たとえば、ゲインが 128 の場合、正の最大ゲイン誤差は+1.587%、負の最大ゲイン誤差は-1.538%となり、不均衡性すなわち非対称性は 0.049%となります。ゲインが 16 の場合は、ゲイン誤差の非対称性は 0.008%でごくわずかです。したがって、小さなゲイン設定の場合、図 3 はDACゲイン誤差がゼロのDAC-PGA回路から予測されるゲイン誤差にかなり近似したものとなります。全ビット 1 またはユニティ・ゲイン設定では、ラダー終端でLSB相当の信号電流が失われるため、ゲインはごくわずかですが常にユニティより大きくなります。表A1 に示したAD7545LNの計算値に関しては、1 倍のゲイン誤差に 1LSBまたは+0.0244%が含まれます。

#### スキューの原因となるDACゲイン誤差

非ゼロのゲイン誤差を持つDACを使用する場合は、全誤差の計算のためにより精度の高い式 8 を使用する必要があります。式 8 からは、非ゼロのDACゲイン誤差が 2 つの面で影響を及ぼすことがわかります。その一つは、前の分析の誤差結果がユニティに近い  $\frac{1}{(1+\Delta)}$  項で乗算されるということです。この影響は

全体的に小さく、任意のゲイン設定でゲインの非対称誤差を増大または減少させるということだけです。(非対称性は正のDACゲイン誤差により減少します。)もう一つはDACゲイン誤差による大きな影響であり、これによってゲイン設定に依存しない誤差項が追加されます。この項は一定なので、低ゲイン設定において最も大きな影響を及ぼし、図3の伝達曲線を正または負の方向に歪めます。(正のDACゲイン誤差は負の歪みを発生させます。)付録1の表A2には、DACゲイン誤差と直線性誤差の全組合せについて式8の計算値を示しています。ユニティ・ゲイン値は、ラダー終端による追加の+0.0244%誤差項を含んでいます。図4は、この表の最悪時の値をもとにプロットされています。図中の破線は図3の伝達曲線を示しています。±5LSBという厳しいゲイン誤差仕様を持つ12ビット分解能、12

ビット精度を備えたDAC( $X = \pm 1/2$ LSB)の場合でも、最悪時のシステム・ゲイン誤差は、ゲイン 1 に対して 0.159%という大きな値になります。

ゲイン誤差分析によって 図 4 が導出されましたが、この場合は、システムのループ・ゲイン値が十分に大きいため、感知されるほどの誤差は生じないものと仮定しています。AD OP-07 の場合、極端なゲイン設定をしなければ、この仮定はDCや低周波数領域で有効です。ループ・ゲインがいかにゲイン誤差に影響するかは、付録 2Aの式A7 で確認できます。信号周波数とゲイン設定が大きいと、有限のループ・ゲインがシステムのゲイン誤差の一因となります。このテーマは、アプリケーション・ノートのPart IIで詳しく取り上げています。

# DCオフセット誤差の原因となる その他の誤差源

こういったゲイン誤差は、図 1bのPGA回路に影響を与える唯一の誤差ではありません。他の誤差源により、オペアンプの出力にゲイン依存のDCオフセット電圧が発生します。DAC関連のその他の誤差源としては、コード依存の出力抵抗や出力リーク電流があります。オペアンプ関連の誤差源は、入力オフセット電圧、入力バイアス電流、有限オープン・ループ・ゲインなどです。付録 2 には、出力に対する各誤差源の影響を大まかに示しています。ここでは、PGAは  $1\sim16$  のゲインを持つものとします。また、使用できる部品はAD7546LN、AD OP-07Eとします。表Iと表IIに、これらの部品の関連仕様(温度条件  $25^{\circ}$ C)を示します。これらの表の最小値と最大値を式A7 に代入すると、最悪時の出力電圧(N=64 $_{10}$ 、すなわちゲイン 64 で発生)は次のようになります。

$$V_{OUT} = -64.58V_{IN} \pm 29.1mV \tag{10}$$

図 4. DAC ゲイン誤差がある場合とない場合の AD7545 ベース・システムの最悪時ゲイン誤差(理論値)

Application Note AN-320A

ゲイン誤差は約 0.9%です。29.1mV の全 DC オフセット誤差項のうち、6.5mV だけが入力オフセット電圧  $V_{OS}$  に起因します。残りは、DAC リーク電流  $I_{LKG}$  (16.1mV の主な要因)とオペアンプ入力バイアス電流  $I_{B}$  (-) です。オペアンプの入力オフセット電圧誤差項を計算するために、式 A7 で  $R_{O}$  =  $3R_{FB}$  の値を使用しました。 $V_{IN}$  が DC 信号の場合、29.1mV の DC オフセット誤差は出力信号と区別することはできません。DC オフセット誤差項をシステム入力に換算すると、入力誤差は 29.1mV/64mV すなわち 0.455mV となります。したがって、64 倍(X (X (X (X (X )) のゲイン設定で X 1%未満の場合の最小入力信号 X X 10 です。X 0.9%のゲイン誤差には、さらにこの誤差が加わります。

#### 温度上昇とともに増大する誤差

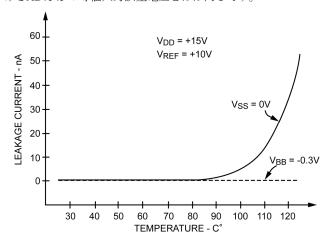

PGAを広範な温度範囲で正確に動作させるには、温度変化に伴 う誤差源のドリフト性能が重要になります。多かれ少なかれ、 式A7 の項はすべて温度に影響されます。この点に関し、データ 仕様を用いた約 70℃での回路の分析では、ゲイン誤差はほとん ど同じままですがDCオフセット誤差は大幅に変化することが示 されました。この温度範囲で、入力オフセット電圧はほぼ 80%、 入力オフセット電流は 40%増大し、すでに主要成分となってい るDACリーク電流ILKGは 400%増大する可能性があります。これ らの最悪時の増加率が出力電圧に変換されると、入力オフセッ ト電圧項で 5.2mVが加わります。入力バイアス電流項で 2.5mV が加わりますが、DACリーク電流項では 64mVが加わります。 しかし、従来の経験からわかるように、DACリーク電流は実際 には 85°C超の温度からしか増大しません。図 6 には、CMOS DACの出力リーク電流の代表的な温度特性を実線で示していま す。軍用規格の温度範囲-55~+125°CでPGA回路を使用する場合 は、従来の商用レベルの製品に代えてAD7545UDやAD OP-07H レベルの製品を使用するようにしてください。表Iと表IIには、 これらの高温対応デバイスの仕様を示しています。式A7 にこれ らの数値を当てはめると、+125°CでのPGAの出力電圧は次のよ うになります。

$$V_{OUT} = -64.59V_{IN} \pm 349.6mV \tag{11}$$

| Parameter                              | AD OP-07E<br>T <sub>A</sub> = +25°C | AD OP-07E<br>T <sub>A</sub> = +70°C | AD OP-07H<br>T <sub>A</sub> = +125°C |

|----------------------------------------|-------------------------------------|-------------------------------------|--------------------------------------|

| Open Loop Gain, A <sub>OI</sub>        | 2.10 <sup>6</sup> min               | 1.8.10 <sup>6</sup> min             | 1.5.10 <sup>6</sup> min              |

| Input Bias Current, I <sub>B</sub> (-) | 4nA max                             | 5.6nA max                           | 6nA max                              |

| Input Offset Voltage, Vos              | 75μV max                            | 134µV                               | 200μV max                            |

NOTE:  $V_{DD} = +15V$ ,  $V_{SS} = -15V$

表 I.  $T_A$  = +25°C、+70°C、+125°C での AD OP-07 の仕様

| Parameter                         | AD7545LN<br>$T_A = +25$ °C | AD7545LN<br>T <sub>A</sub> = +70°C | AD7545UD<br>T <sub>A</sub> = +125°C |

|-----------------------------------|----------------------------|------------------------------------|-------------------------------------|

| Resolution, n                     | 12-bits                    | 12-bits                            | 12-bits                             |

| Relative Accuracy, x              | $\pm 1/2LSB\ max$          | $\pm 1/2LSB\ max$                  | $\pm 1/2LSB\ max$                   |

| (Integral Linearity)              |                            |                                    |                                     |

| Gain Error                        | $\pm 5LSBsmax$             | ±6LSBs max                         | ±6LSBs max                          |

| Output Leakage, I <sub>LKG</sub>  | 10nA max                   | 50nA max                           | 200nA max                           |

| Input Resistance, R <sub>IN</sub> | $25k\Omega$ max            | $25k\Omega$ max                    | $25k\Omega$ max                     |

NOTE:  $V_{DD} = +5V$

表 II. T<sub>A</sub> = +25°C、+70°C、+125°C での AD7545 の仕様

回路のプログラマブル・ゲインはここでも 64 です。ゲイン誤差は、25°Cの値からほとんど変わっていません(式 10 を参照)。しかし、DCオフセット誤差は 1 桁増大しています。349.6mVのうち、9.7mVはオペアンプのバイアス電流によるもの、17.4mVは入力オフセット電圧によるものです。残りの 322.5mVの電圧はDACリーク電流に起因します。349.6mVをシステム入力に換算すると、349.6/64mV(すなわち 5.5mV)の 64 倍のゲイン設定で、等価的な入力誤差が得られます。64 倍のゲイン設定で誤差が 1%未満の場合、最小DC入力信号 $V_{\rm IN}$ は 550mVです。これは温度が+125°C時のもので、+25°C時の最小入力信号より 1 桁大きな値です。表IVaには、+25°C、+70°C、+125°Cの条件で式A7から導出したゲイン誤差とDCオフセット誤差を示しています(12 ビットAD7545 を使用)。

### 誤差の低減

#### ゲイン誤差

図4のグラフからは、いささか意外な結論を導き出すことができます。高精度アプリケーションでは、DACゲイン誤差がDAC積分直線性と同じぐらい大きなシステム誤差要因となります。これは、DACゲイン誤差によって、最も正確なゲイン設定に最も大きな影響を与える固定誤差項が生じるからです。たとえば、ゲイン設定が1のとき、図4の誤差は±0.159%となります。これは、±5LSBのDACゲイン誤差を持つ12ビット分解能/12ビット精度のDACの場合です。DACゲイン誤差がなければ(図4の破線)、最大システム誤差は±0.036%で、前の値の1/5となります。もちろん、ポテンショメータでDACゲイン誤差をゼロに調整(トリミング)することができます。しかし、そのゼロ調整部品の温度係数はDACの薄膜ラダー抵抗のものとは異なるため、全温度範囲でDACゲイン誤差が変化します。CMOS DACの最小ドリフトの調整については、参考文献1でさらに詳しく取り上げています。

プログラマブル・ゲイン設定値が大きくなると(Nが小さくな る)、DAC積分非直線性はシステム・ゲイン誤差の主な要因と なります。たとえば、ゲイン設定が64の場合、図4のシステム 誤差は約±0.9%となります。そのうちの±0.78%はDAC積分非直 線性によるものです。単一ゲイン段の代わりに、直列接続した 2個のゲイン段を使って、同じトータル・ゲインを提供するこ とができます。各ゲイン段のゲイン設定の積はトータル・ゲイ ンと等しいので、各ゲイン段のゲイン設定はかなり小さく、精 度は向上します。2 つのゲイン段を使用できる場合(各段は 図 4 に示す性能と同じような性能を持つ)、同じ 64 のトータル・ ゲイン設定に対し(各ゲイン設定=8)、システム・ゲイン誤差 は約±0.44%となります。この誤差の半分以上はDACゲイン誤差 によるものです。システム全体のコスト、複雑さ、およびサイ ズを最小限に抑えるためには、このアプリケーションに最適な アナログ・デバイセズのモノリシック・デュアル 8 ビット/12 ビットDACを使用してください。AD7528 は並列負荷構造の デュアル 8 ビットDACです。AD7537、AD7547、AD7549 はそ れぞれ8+4、完全並列、ニブル(4ビット)負荷構造のデュア ル 12 ビットDACです。これらの回路の性能は、本アプリケー ション・ノートのPart IIで取り上げます。

#### DCオフセット誤差

DC オフセット誤差は、アプリケーションによって重要である場合とそうでない場合があります。この DC 電圧を除去するための理想的な解決策は、出力信号を AC 結合することです。しかし、DC レベルが重要ではないアプリケーションの場合でも、この解決策が必ずしも有効とは限りません。当該周波数が数へルツという低値にまで拡張された場合は、結合コンデンサの値(および物理的なサイズ)の選択と、低周波の減衰によるゲイン誤差の増大という 2 つの問題で相反する対応を迫られます。要求される回路の性能やアプリケーションに応じて、その回路において最も重要となるパラメータ見定めた上で、最も費用効果的なソリューションとなるよう、部品を選択してください。

DAC 出力リーク電流は、DC オフセット誤差の非常に大きな要因です。高温条件下では特にそうです。今日でも、軍用規格の温度範囲で小さな出力リーク電流を備えた CMOS DAC は提供されていません。

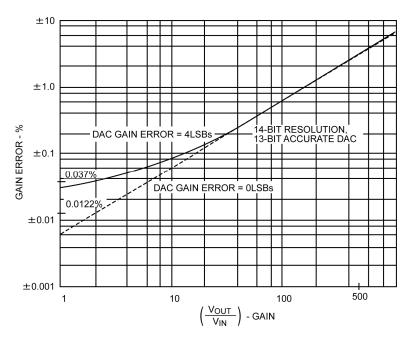

# シングルDACソリューション

アナログ・デバイセズから最近発売された 2 つ高分解能CMOS DACは、PGAモード時のDAC動作にとって理想に近い仕様を備えています。AD7534 とAD7538 は低価格の 14 ビット分解能DACで、DACゲイン誤差の仕様はきわめて厳しく最大±4LSBとなっています。また、13 ビット精度の仕様と、高温度のもとで超低リーク電流を維持する特許技術の低リーク技術 (US Pat No. 4,590,456) により、ゲイン誤差とDCオフセット誤差は前のケースよりも大幅に低減されます。表IIIに、+25°CでのAD7534KNの関連仕様を示します。図 5 は、AD7534KNについて式 8 をグラフ化したものです。この図には式 9 もグラフ化されていますが、この場合、DACゲイン誤差はゼロと仮定しています。これらの

カーブを 図4のものと比較してください。付録1の表A3とA4には、DACゲイン誤差と直線性誤差のすべての組合せに対して、式9と式8の計算値をそれぞれ示しています。

AD7534 には専用ピン $V_{SS}$ があり、これを 0V(通常のDAC出力リーク)または-300mV(低減されたDAC出力リーク)に接続して特許技術の低リーク技法を実装できます。図 6 は、両条件におけるリーク電流の温度特性をプロットしたものです。この図には、低リーク技法による誤差の改善が明確に示されています。表IIIの仕様を式A7 に代入すると(表IのAD OP-07E仕様を使用)、ゲイン 64 ( $N=256_{10}$ ) での最悪時の出力電圧は次のようになります。

$$V_{OUT} = -64.264V_{IN} \pm 11.1mV$$

(12)

ゲイン誤差は約0.41%です。この結果値は25% に関するものであり、式10の結果値と比較する必要があります。ゲイン誤差とDC オフセット誤差はともに半分以下となっています。

| Parameter                                    | AD7534KN<br>$T_A = +25$ °C | AD7534KN<br>$T_A = +70$ °C | AD7534TD<br>$T_A = +125$ °C |

|----------------------------------------------|----------------------------|----------------------------|-----------------------------|

| Resolution, n                                | 14-bits                    | 14-bits                    | 14-bits                     |

| Relative Accuracy, x<br>(Integral Linearity) | ±1LSB max                  | ±1LSB max                  | ±1LSB max                   |

| Gain Error                                   | $\pm 4LSBsmax$             | ±4LSBs max                 | ±4LSBs max                  |

| Output Leakage, I <sub>LKG</sub>             | ±5nA max                   | ±10nA max                  | ±20nA max                   |

| Input Resistance, R <sub>IN</sub>            | $10k\Omega$ max            | $10k\Omega$ max            | 10kΩ max                    |

NOTE:  $V_{DD} = +5V$ ,  $V_{SS} = -0.3V$

表 III. T<sub>A</sub> = +25°C、+70°C、+125°C での AD7534 の仕様

オペアンプの入力オフセット電圧誤差項を計算するために、A7では $R_0 = 15R_{FB}$ の値が使用されています。表IVbには、DCオフセット誤差項の各要素を示しています。この分析は+70°Cと+125°Cで繰り返し行い、その結果も表IVbに示しています。

図 5. DAC ゲイン誤差がある場合とない場合の AD7534 ベース・システムの最悪時ゲイン誤差(理論値)

表IVaと 表IVbの結果を比較すると、AD7534 における低スキーム技法の効果は一目瞭然です。+125°CでのDCオフセット誤差は、AD7534 で 1 桁小さくなっています。この技法の効果は次の事実によっても証明されています。つまり、同じゲイン設定の場合に、+125°CにおけるAD7534 の等価入力誤差電圧は+25°CにおけるAD7545 の等価入力誤差電圧とほぼ同じです。

図 6. 代表的なリーク電流の温度特性

### ノイズ・ゲイン

PGA 回路の基本要件は単調増加性を備えていることです。すな わち、DAC デジタル・コードが変わってゲインが増大すると、 回路ゲインが実際に増大するか、あるいは少なくとも回路ゲイ ンは減少しません。DAC の直線性が、分解能すなわち 12 ビッ ト精度の DAC の 12 ビット分解能に付随して生じる場合、その DAC は単調増加性を備えており、理論上はすべての可能な入力 コードをゲイン設定に使用できます。しかし、直線性が分解能 より小さい場合、すなわち DAC が 11 ビット精度で 12 ビットの 分解能を有する場合は、隣接コードがオーバーラップして非単 調増加性の動作が生じます。11 ビット精度/12 ビット分解能の DAC の場合は、次にくるすべてのコード、すなわち隣接コード は使用してはなりません。DAC 仕様がもっと極端な場合、すな わち 10 ビット精度で 12 ビット分解能の場合は、3 つおきの コードのみを使用します。したがって、プログラム可能な(単 調増加性保証) ゲイン設定の数は全ステップ数の 1/4 となりま す。

AD7534KNは 13 ビットの相対精度を持つ 14 ビット分解能DAC です。このデバイスは、全温度範囲で14ビットまで単調増加性 が保証されます。理論的には、16384 コードのすべてをゲイン 設定に使用できます。しかし、考慮しなければならない誤差源 はほかにも存在します。DCオフセット誤差(回路のノイズ・ゲ インによる) に対する入力オフセット電圧Vosの影響については すでに説明しました。このノイズ・ゲインによって、DC項はオ ペアンプの出力から減算または加算されます。システムが非単 調増加となる可能性が最も高いのは、DAC入力コードがある コード設定から次の隣接コード設定に変わるときです。隣接 コードへの遷移の中で最も重大なのは、DAC出力インピーダン スRoが低い値から高い値に遷移することです。しかし、最も重 大なコード遷移の場合でも、アナログ入力信号電圧VINがオペア ンプの入力オフセット電圧Vosに対して十分に大きければ、非単 調増加ステップは避けられます。1~64 倍のゲイン範囲(整数 ステップ)でAD7534を分析すると、最悪時のコード遷移は最 後のコード遷移であることがわかります。出力インピーダンス  $R_0$ は、63 倍のゲイン設定(N=260<sub>10</sub>)時の $R_0$  = 6.7 $R_{FB}$ から 64 倍 のゲイン設定  $(N=256_{10})$  時の $R_0 = 15R_{FB}$ に変わります。また、 最悪時のコード遷移に対して式A7を解くと、予想される非単調 増加動作のスレッショールド値である、VINの最小値が得られま す。この値は 6Vosです。この値より大きな入力信号レベルでは、 非単調増加遷移の発生を避けることができます。3倍、5倍、6 倍など、2の整数乗ではない整数ゲインの場合は、個々のケー スで、一番近い 14 ビット・コードが選択されています。付録 3 の表A5には、使用されているデジタル入力コードと、1~64倍

のゲイン範囲における各整数ゲイン設定の $\left(1+\frac{R_{FB}}{R_O}\right)$ 比を記載

しています。

クローズドループ・サーボ・システムなどのアプリケーションでは、整数ゲインのインクリメントよりもゲインの微調整が必要です。図 2 に示すように、コードの総数の半数  $(2^{n-1})$  は  $1\sim2$  倍のゲイン範囲に対応しています。AD7534 の場合は、 $1\sim2$  倍の範囲のゲイン設定に 8192 コードを使用できるので、ゲインをかなり微調整することができます。 $1\sim64$  倍間では、16,000 を少し上回るゲイン設定しかできません。しかし、多くのゲイン設定を得ようとすると、単調増加性のために $V_{\rm IN}/V_{\rm OS}$ の最小比が求められます。コンピュータ分析で示されるように、 $1\sim64$  倍のコード表における隣接コード・ペア間の非単調増加性遷移を避けるには、最小アナログ入力電圧 $V_{\rm IN}$ を  $1350V_{\rm OS}$ より大きくしなければなりなせん。一見すると、これはきわめて大きな比になりますが、よく考えてみれば、これは予測される値です。

#### DC ERRORS

| TEMPERATURE           | <b>GAIN ERROR</b> | $I_{LKG}$ | I <sub>S</sub> (-) | Vos    | TOTAL   |

|-----------------------|-------------------|-----------|--------------------|--------|---------|

| $T_A = +25$ °C        | 0.91%             | 16.1mV    | 6.5mV              | 6.5mV  | 29.1mV  |

| $T_A = +70$ °C        | 0.91%             | 80.1mV    | 9mV                | 11.7mV | 100.8mV |

| $T_A = +125^{\circ}C$ | 0.92%             | 322.5mV   | 9.7mV              | 17.4mV | 349.6mV |

表 IVa. AD7545 の全温度範囲にわたる誤差分析(ゲイン = 64)

#### DC ERRORS

| TEMPERATURE           | GAIN ERROR | $I_{LKG}$ | I <sub>S</sub> (-) | Vos    | TOTAL  |

|-----------------------|------------|-----------|--------------------|--------|--------|

| $T_A = +25$ °C        | 0.41%      | 3.2mV     | 2.6mV              | 5.3mV  | 11.1mV |

| $T_A = +70$ °C        | 0.41%      | 6.4mV     | 3.6mV              | 9.5mV  | 19.5mV |

| $T_A = +125^{\circ}C$ | 0.41%      | 12.8mV    | 3.8mV              | 14.1mV | 30.7mV |

表 IVb. AD7534 の全温度範囲にわたる誤差分析 (ゲイン = 64)

隣接する 14 ビット・コードを使用するとき、ゲインの増加率 (%) はごくわずかなパーセンテージです。これは特に低ゲイン 設定に当てはまります。しかし、同じコード遷移に対するノイズ・ゲインの変化率は、何桁か大きくなる可能性があります。 たとえば、 $16379_{10}$  から  $16378_{10}$  へのコード遷移の場合、信号ゲインは 0.006%増大しますが、ノイズ・ゲインは 0.775%変化します。このコード遷移で単調増加性を保証するために必要な  $V_{IN}$ 対  $V_{OS}$ の比は 400 です。

ノイズ・ゲインは、一般に DC 誤差項のみに寄与し、オペアンプの入力オフセット電圧 (Vos) のみに作用するものと考えられています。しかし、付録 2 の式 A1 は、ノイズ・ゲインがシステムのゲイン誤差にも寄与することを示しています。ただ、AD OP-07 では非常に高いオープン・ループ・ゲインで、誤差への影響を無視できる程度に抑えています。

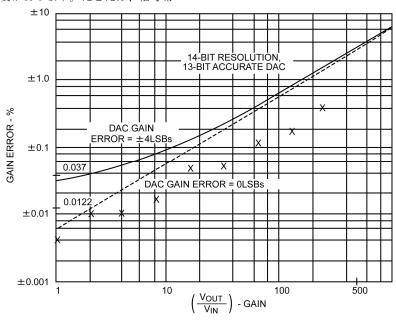

### 試験結果

多くのAD7534KN/AD OP-07Eを組み合せ、 $+25^{\circ}$ CでDC測定を行いました。その結果得られた代表値を 図 7 に示します。図中の×印は、 $1\sim256$  倍の範囲から選択したゲイン設定における測定誤差を示しています。各ゲイン設定では、DC入力信号レベルが5Vの出力信号レベルを提供できるように調整されています。誤差を比較できるように、図 7 には 図 5 の最悪時の理論誤差曲線も含まれています。DACゲイン誤差も入力オフセット電圧も調整はいっさい行っていません。測定はDCについて行われたので、図 7 に示す誤差曲線は $+25^{\circ}$ Cでのオフセット誤差を含んでいます。しかし、これらは約  $40\mu$ Vで測定されており、入力試験信号レベルと比較して無視できる範囲の値です。

ゲイン 64 の場合、システムの 3dB 帯域幅は一般に 7kHz です。 オペアンプの減衰によるゲイン誤差を避けるために、信号の帯 域幅は適当に制限を設ける必要があります。たとえば、信号帯 域幅を 100Hz 未満 (3dB 周波数の 1/70) に制限すると、減衰による追加ゲイン誤差は 0.01%未満になります (単純な単極減衰を想定)。AD OP-07より大きな帯域幅を持つオペアンプで信号帯域幅を増大することはできますが、そうすると誤差源が 1 つかそれ以上増える可能性があります。ゲインが 1 倍の場合、3dB帯域幅は約 500kHz となります。

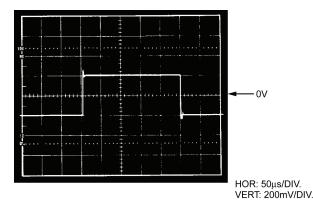

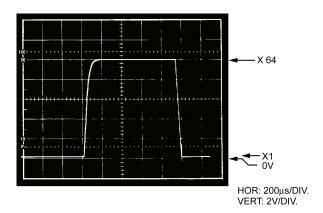

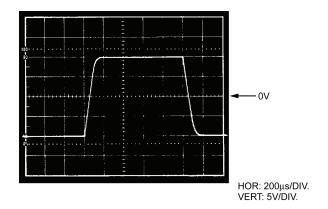

出力電圧のセトリング時間は、AD OP-07のスルーレートによって制限されます。ステップ入力変化に対する出力電圧のセトリング時間は、2つの固定のゲイン設定(1倍および64倍)で測定しました。出力応答は、図8aと8bのオシロスコープ写真に示しています。

図 8a(1 倍のゲイン)における入力ステップ・サイズは±200mVで、図 8b(64 倍のゲイン)の場合は±154mVです。入力信号の立上がり時間は、どちらの場合も時間点 10%から 90%までで1µsでした。ゲインが1倍の場合の±0.01%内までのセトリング時間は 30µs未満で、64 倍の場合は 300µs未満です。出力電圧のセトリング時間の測定は、安定した入力信号を使って、変化するゲイン設定(すなわちDACコード)に対しても行いました。8cのオシロスコープ写真は、ゲイン設定が1倍から64倍に変化するときの出力応答を示しています。入力信号レベルは一定で-154mVです。±0.01%に収まるまでの出力電圧セトリング時間は、1倍から64倍に変化するとき約300µsで、64倍から1倍に変化するときは約60µsです。AD7545LNとAD OP-07E PGAを組み合せた回路の動的応答も同じように測定しましたが、上記と異なるような結果は得られませんでした。

AC 信号を増幅する場合は、システムの非直線性または歪みが 重要な意味を持ちます。CMOS DAC は、超低ノイズと非常に小 さい電圧係数を持つ高品質の薄膜抵抗を使って製造されます。 また、ラダー・ネットワークの信号ステアリング・スイッチの 両端には、入力信号電圧のごくわずかしか発生しません。した がって、出力信号の歪みの大部分はオペアンプによるものです。

図 7. AD7534 ベースのシステムにおける最悪時のゲイン誤差―測定値と理論値

Application Note AN-320A

表Vでは、12 ビットAD7545LNと 14 ビットAD7534KNの高調波 歪み性能を比較しています。どちらの場合も、任意のゲイン設 定では入力信号レベルが 6V RMSの出力信号レベルを提供する よう調整しました。テスト周波数は 200Hzであり、歪みレベル はヒューレット・パッカードのHP339A歪み測定セットを使っ て測定しました(内蔵の 3 次、30kHzローパス・フィルタ機能 は信号パスに切り替えます)。2 つのPGAシステムに関する結 果は非常に似ています。表VIでは、22Hz~22kHzの帯域幅で、2 つのシステムの電圧ノイズ性能を比較しています。比較しやすいように、同じ低ノイズAD OP-27 オペアンプを両方の回路で使用しました。AD7534 ベースのシステムはAD7545 より性能が優れていますが、これはDACラダー抵抗の値が小さいためです。

図 8a. ゲイン 1: ±200mV ステップ入力に対する出力応答 (AD7534 システム)

図 8c. 1 倍と 64 倍の間でゲインを切替えた時の出力応答、-154mV の一定の入力信号(AD7534 システム)

| GAIN | AD7545LN<br>& AD OP-07 | AD7534KN<br>& AD OP-07 |

|------|------------------------|------------------------|

| X 1  | 5.5μV                  | 4.5μV                  |

| X 2  | $9\mu V$               | $7\mu V$               |

| X 4  | 18μV                   | $12\mu V$              |

| X 8  | $35\mu V$              | $23\mu V$              |

| X 16 | $72\mu V$              | $45\mu V$              |

| X 32 | 145µV                  | $89\mu V$              |

| X 64 | $285 \mu V$            | 175μV                  |

表 VI. ゲイン設定 対 出力電圧ノイズ (読取り値は 22Hz~22kHz RMS)

図 8b. ゲイン 64:±154mV ステップ入力に対する出力応答 (AD7534 システム)

| GAIN | AD7545LN<br>& AD OP-07 | AD7534KN<br>& AD OP-07 |

|------|------------------------|------------------------|

| X 1  | <-90dB                 | <-90dB                 |

| X 2  | <-90dB                 | <-90dB                 |

| X 4  | <-90dB                 | <-90dB                 |

| X 8  | -89dB                  | -88dB                  |

| X 16 | -86dB                  | -86dB                  |

| X 32 | -82dB                  | -83dB                  |

| X 64 | -76dB                  | -79dB                  |

表 V. ゲイン設定 対 全高調波歪みのレベル (一定の 6V RMS 出力信号)

# 参考文献

- 1. アプリケーション・ノート『Gain Error and Gain Temperature Coefficient of CMOS Multiplying DACs』Phil Burton 著、アナログ・デバイセズから提供、Publication No. E630c5-386

- 2. ハンドブック『CMOS DAC Application Guide』 アナログ・デバイセズから提供、Publication No. G872a-15-4/86

- 3. 『Operational Amplifiers, Second Edition』 GB Clayton 著、Butterworths (1979)

- 4. トランザクション要約: 『Expression for the Output Resistance of a Switched R-2R Ladder Network』 E. David Erb、Gregory M. Wierzba 著、IEEE Trans. Circuits & Systems、Vol. CAS-30、No.3、1983 年 3 月、pp. 167-169

### 付録1

|      |           | SYSTEM G                         | SYSTEM GAIN ERROR                |      |           |                                |                                |

|------|-----------|----------------------------------|----------------------------------|------|-----------|--------------------------------|--------------------------------|

| GAIN | CODE<br>N | RELATIVE<br>ACCURACY<br>X = +0.5 | RELATIVE<br>ACCURACY<br>X = -0.5 | GAIN | CODE<br>N | RELATIVE<br>ACCURACY<br>X = +1 | RELATIVE<br>ACCURACY<br>X = −1 |

| 1    | 4095      | +0.0122%                         | +0.0366%                         | 1    | 16383     | 0%                             | +0.0122%                       |

| 2    | 2048      | -0.0244%                         | +0.0244%                         | 2    | 8192      | -0.0122%                       | +0.0122%                       |

| 4    | 1024      | -0.0488%                         | +0.0489%                         | 4    | 4096      | -0.0244%                       | +0.0244%                       |

| 8    | 512       | -0.0976%                         | +0.0978%                         | 8    | 2048      | -0.0488%                       | +0.0488%                       |

| 16   | 256       | -0.195 %                         | +0.1957%                         | 16   | 1024      | -0.0976%                       | +0.0978%                       |

| 32   | 128       | -0.389 %                         | +0.3922%                         | 32   | 512       | -0.195 %                       | +0.1957%                       |

| 64   | 64        | -0.775 %                         | +0.7874%                         | 64   | 256       | -0.389 %                       | +0.3922%                       |

| 128  | 32        | -1.539 %                         | +1.587 %                         | 128  | 128       | -0.775 %                       | +0.7874%                       |

| 256  | 16        | -3.03 %                          | +3.226 %                         | 256  | 64        | -1.539 %                       | +1.578 %                       |

| 512  | 8         | -5.88 %                          | +6.666 %                         | 512  | 32        | -3.03 %                        | +3.226 %                       |

$$\operatorname{Error}(\%) = -\left(\frac{X}{N+X}\right) \bullet 100\% \tag{9a}$$

$$\operatorname{Error}(\%) = -\left(\frac{X}{N+X}\right) \bullet 100\%$$

表 A1. 式 9a の計算値、12 ビット分解能(n = 12)/12 ビット精度(X = ±0.5LSB)DAC、DAC ゲイン誤差ゼロ。ユニティ・ゲイン値は、本文に示した追加の+0.0244%誤差項を含みます

表 A 3. 式 9a の計算値、14 ビット分解能(n = 14) / 13 ビット精度(X = ±1LSB)DAC、DAC ゲイン誤差ゼロ。ユニティ・ゲイン値は、本文に示した追加の+0.0061%誤差項を含みませ

#### SYSTEM GAIN ERROR

|      |           | DAC GAIN ERR             | OR, $\Delta = +0.0012$   | DAC GAIN ERROR, $\Delta = -0.0012$ |                          |  |

|------|-----------|--------------------------|--------------------------|------------------------------------|--------------------------|--|

| GAIN | CODE<br>N | REL ACCURACY<br>X = +0.5 | REL ACCURACY<br>X = −0.5 | REL ACCURACY<br>X = +0.5           | REL ACCURACY<br>X = -0.5 |  |

| 1    | 4095      | -0.109%                  | -0.085%                  | +0.134%                            | +0.159%                  |  |

| 2    | 2048      | -0.146%                  | -0.098%                  | +0.096%                            | +0.145%                  |  |

| 4    | 1024      | -0.171%                  | -0.073%                  | +0.071%                            | +0.169%                  |  |

| 8    | 512       | -0.219%                  | -0.024%                  | +0.022%                            | +0.218%                  |  |

| 16   | 256       | -0.317%                  | +0.074%                  | -0.075%                            | +0.318%                  |  |

| 32   | 128       | -0.511%                  | +0.270%                  | -0.270%                            | +0.513%                  |  |

| 64   | 64        | -0.896%                  | +0.665%                  | -0.656%                            | +0.908%                  |  |

| 128  | 32        | -1.658%                  | +1.464%                  | -1.420%                            | +1.709%                  |  |

| 256  | 16        | -3.148%                  | +3.1 %                   | -2.914%                            | +3.349%                  |  |

| 512  | 8         | -5.977%                  | +6.537%                  | -5.769%                            | +6.795%                  |  |

Error(%) =

$$-\left[\left(\frac{\Delta}{1+\Delta}\right) + \left(\frac{1}{1+\Delta}\right)\left(\frac{X}{N+X}\right)\right] \bullet 100\%$$

(8)

表 A2. 式 8 の計算値、12 ビット分解能(n = 12) / 12 ビット精度(X =  $\pm 0.5$ LSB)DAC、DAC ゲイン誤差 $\pm 5$ LSB( $\Delta = \pm 5/4096$ )。ユニティ・ゲイン値は、本文に示した追加の+0.0244%誤差項を含みます

| SYSTEM |  |

|--------|--|

|        |  |

|      |       | DAC GAIN ERRO | $PR, \Delta = +0.000244$ | DAC GAIN ERROR, $\Delta = -0.000244$ |              |  |

|------|-------|---------------|--------------------------|--------------------------------------|--------------|--|

|      | CODE  | REL ACCURACY  | REL ACCURACY             | REL ACCURACY                         | REL ACCURACY |  |

| GAIN | N     | X = +1.0      | X = -1.0                 | X = +1.0                             | X = -1.0     |  |

| 1    | 16383 | -0.025%       | -0.012%                  | +0.024%                              | +0.037%      |  |

| 2    | 8192  | -0.037%       | -0.012%                  | +0.012%                              | +0.037%      |  |

| 4    | 4096  | -0.049%       | 0 %                      | 0 %                                  | +0.049%      |  |

| 8    | 2048  | -0.073%       | -0.024%                  | -0.024%                              | +0.073%      |  |

| 16   | 1024  | -0.122%       | +0.073%                  | -0.073%                              | +0.122%      |  |

| 32   | 512   | -0.219%       | +0.171%                  | -0.171%                              | +0.22 %      |  |

| 64   | 256   | -0.413%       | +0.368%                  | -0.365%                              | +0.417%      |  |

| 128  | 128   | -0.799%       | +0.763%                  | -0.751%                              | +0.812%      |  |

| 256  | 64    | -1.562%       | +1.563%                  | -1.514%                              | +1.612%      |  |

| 512  | 32    | -3.054%       | +3.2 %                   | -3.007%                              | +3.251%      |  |

$$\operatorname{Error}(\%) = -\left[ \left( \frac{\Delta}{1+\Delta} \right) + \left( \frac{1}{1+\Delta} \right) \left( \frac{X}{N+X} \right) \right] \bullet 100\% \tag{8}$$

表 A4. 式 8 の計算値、14 ビット分解能(n = 14) / 13 ビット精度(X = ±1LSB)DAC、ゲイン誤差±4LSB(Δ = ±4/16,384)。ユニティ・ゲイン値は、本文に示した追加の+0.0061%誤差項を含みます

### 付録2

DAC関連の誤差源は、直線性誤差のほかに、コード依存の出力抵抗、リーク電流、およびゲイン誤差があります。オペアンプ関連の誤差源は、入力オフセット電圧、入力バイアス電流、および有限オープン・ループ・ゲインです。すべての誤差源を合わせると、出力電圧の完全な(いくらか扱いづらい)式が得られます。誤差源への対策に、より完璧を期する場合は、参考文献 2,3 を参照してください。図 1 のオペアンプのオープン・ループ・ゲインが AoLの場合、回路の出力電圧は次式で表されます。

$$V_{OUT} = -V_{IN} \bullet \frac{R_{EQ}}{R_{FB}} \bullet \left\{ \frac{1}{1 + \left(\frac{1}{A_{OL}}\right) \left(1 + \frac{R_{EQ}}{R_{FB} \| R_0}\right)} \right\}$$

(A1)

この式の

$$\left(1+rac{\mathbf{R}_{\,\mathrm{EQ}}}{\mathbf{R}_{\,\mathrm{FB}} \|\mathbf{R}_{\,0}}

ight)$$

項は、回路のクローズド・ループ・ゲイ

ン 1/β またはノイズ・ゲイン  $G_N$  に相当します。 $R_O$  は DAC のコード依存の出力抵抗であり、オペアンプ加算ジャンクションと AGND の間で発生します。

$\mathrm{DAC}$  リーク電流  $\mathrm{I}_{\mathrm{LKG}}$ 、オペアンプ入力オフセット電圧  $\mathrm{V}_{\mathrm{OS}}$ 、および入力バイアス電流  $\mathrm{I}_{\mathrm{B}}$ (-)に起因する出力電圧は、これらの個別の誤差源を一つにまとめて入力オフセット誤差源  $\mathrm{E}_{\mathrm{OS}}$  とすることで手際よく求めることができます。この誤差源による出力電圧は次のように表されます。

$$\left(\frac{1}{\beta}\right) \bullet E_{OS} = G_{N} \bullet E_{OS}$$

$$\Xi \Xi C, \quad E_{OS} = \pm V_{OS} \pm I_{LKG} \bullet R \pm I_{B}(-) \bullet R \tag{A2}$$

R は、AGND に接続された反転入力の実効ソース・インピーダンスです。すなわち、

$$\begin{split} R &= R_{FB} \left\| R_O \right\| R_{EQ} \\ &\sharp \mathcal{L} \mathcal{U}, \\ R &= \frac{R_{EQ}}{G_N} \end{split} \tag{A3}$$

Eosによる出力電圧は次のように表されます。

$$\pm V_{OS} \bullet G_N \pm I_{LKG} \bullet R_{EQ} \pm I_B(-) \bullet R_{EQ}$$

または、  $\pm V_{OS} \bullet G_N + (I_{LKG} + I_B(-)) \bullet R_{EQ}$  (A4)

ノイズ・ゲイン  $G_N$ (クローズド・ループ・ゲイン  $1/\beta$ )は DAC 出力抵抗の関数です。この抵抗は、デジタル入力コードのかなり複雑な関数であり、DAC コードがすべて 1 からすべて 0 に変わるとほぼ最小値から最大値に増大します(参考文献 4)。

DAC 出力抵抗は、DAC の設計で使用されるラダー・ネットワーク型のデバイスからも影響されます。ここで比較している2 つの DAC は、2 つの異なるネットワークを使用しています。その一つの AD7545 はストレート R-2R ラダー設計、もう一つのAD7534 はセグメント化された設計を用います。これは、ノイズ・ゲイン項が両 DAC と異なることを意味します。

これらをすべて加算すると、出力電圧式は次のようになります。

$$\begin{split} V_{OUT} &= -V_{IN} \bullet \frac{R_{EQ}}{R_{FB}} \left\{ \frac{1}{1 + \left(\frac{1}{A_{OL}}\right) \left(1 + \frac{R_{EQ}(R_{FB} + R_{0})}{R_{FB} \bullet R_{0}}\right)} \right\} \\ &\pm (I_{LKG} + I_{B}(-)) \bullet R_{EQ} \\ &\pm V_{OS} \bullet \left(1 + \frac{R_{EQ}(R_{FB} + R_{0})}{R_{FB} \bullet R_{0}}\right) \end{split} \tag{A5}$$

$R_{EQ}$  を  $\frac{2^{n}R_{IN}}{N+x}$  に置き換え、次のように DAC ゲイン誤差を計算に入れると、

$$\frac{R_{FB}}{R_{IN}} = (1 + \Delta)$$

$$\simeq \simeq \mathcal{C}, \quad \Delta = \frac{R_{FB} - R_{IN}}{R_{IN}}$$

(A6)

出力式は以下のようになります。

$$\begin{split} V_{OUT} &= -V_{IN} \bullet \frac{2^{n}}{(N+x)(1+\Delta)} \left\{ \frac{1}{1 + \left(\frac{1}{A_{OL}}\right) \left\{ 1 + \left(\frac{2^{n}}{(N+x)(1+\Delta)}\right) \left(1 + \frac{R_{FB}}{R_{0}}\right) \right\}} \right. \\ & \left. \pm (I_{LKG} + I_{B}(-)) \bullet \frac{2^{n} R_{IN}}{N+x} \right. \\ & \left. \pm V_{OS} \left\{ 1 + \left(\frac{2^{n}}{(N+x)(1+\Delta)}\right) \left(1 + \frac{R_{FB}}{R_{0}}\right) \right\} \right. \end{split} \tag{A7}$$

誤差源に対する DAC 直線性および DAC ゲイン誤差の影響はほとんど無視できる程度のものなので、式 A7 は簡素化できます。同様に、考慮中のシステム・ゲインについては、式 A1 のゲイン誤差係数はユニティになるものと仮定できます。

$$\frac{1}{1 + \left(\frac{1}{A_{OL}}\right)G_{N}} \approx 1 \tag{A8}$$

この仮定のもとで、式 A7 は次のように簡素化できます。

$$\begin{split} V_{OUT} &= -V_{IN} \, \frac{2^{n}}{(N+X)\,(1+\Delta)} \\ &\pm \left\{ I_{LKG} + IB(-) \right\} \bullet R_{IN} \bullet (SYSTEM \, GAIN) \\ &\pm V_{OS} \left\{ 1 + (SYSTEM \, GAIN) \left( 1 + \frac{R_{\,FB}}{R_{\,0}} \right) \right\} \end{split} \tag{A9}$$

システム・ゲインが増大すると、リーク電流や入力オフセット電圧に起因する DC オフセット誤差も増大します。

### 付録3

| SYSTEM |                    |                    | SYSTEM |                    |                    | SYSTEM |                    |                    |

|--------|--------------------|--------------------|--------|--------------------|--------------------|--------|--------------------|--------------------|

| GAIN   | CODE <sub>10</sub> | $(1+R_{FB}/_{RO})$ | GAIN   | CODE <sub>10</sub> | $(1+R_{FB}/_{RO})$ | GAIN   | CODE <sub>10</sub> | $(1+R_{FB}/_{RO})$ |

| 1      | 16383              | 1.08               | 24     | 683                | 1.31               | 47     | 349                | 1.27               |

| 2      | 8192               | 1.00               | 25     | 655                | 1.25               | 48     | 341                | 1.30               |

| 3      | 5461               | 1.31               | 26     | 630                | 1.25               | 49     | 334                | 1.25               |

| 4      | 4096               | 1.00               | 27     | 607                | 1.24               | 50     | 328                | 1.20               |

| 5      | 3277               | 1.28               | 28     | 585                | 1.27               | 51     | 321                | 1.21               |

| 6      | 2731               | 1.31               | 29     | 565                | 1.28               | 52     | 315                | 1.26               |

| 7      | 2341               | 1.21               | 30     | 546                | 1.21               | 53     | 309                | 1.28               |

| 8      | 2048               | 1.00               | 31     | 529                | 1.14               | 54     | 303                | 1.25               |

| 9      | 1820               | 1.20               | 32     | 512                | 1.06               | 55     | 298                | 1.26               |

| 10     | 1638               | 1.25               | 33     | 496                | 1.13               | 56     | 293                | 1.27               |

| 11     | 1489               | 1.25               | 34     | 482                | 1.20               | 57     | 287                | 1.22               |

| 12     | 1365               | 1.31               | 35     | 468                | 1.22               | 58     | 282                | 1.24               |

| 13     | 1260               | 1.22               | 36     | 455                | 1.25               | 59     | 278                | 1.24               |

| 14     | 1170               | 1.24               | 37     | 443                | 1.26               | 60     | 273                | 1.22               |

| 15     | 1092               | 1.18               | 38     | 431                | 1.26               | 61     | 269                | 1.24               |

| 16     | 1024               | 1.03               | 39     | 420                | 1.22               | 62     | 264                | 1.15               |

| 17     | 964                | 1.18               | 40     | 410                | 1.25               | 63     | 260                | 1.15               |

| 18     | 910                | 1.23               | 41     | 400                | 1.17               | 64     | 256                | 1.07               |

| 19     | 862                | 1.23               | 42     | 390                | 1.22               |        |                    |                    |

| 20     | 819                | 1.28               | 43     | 381                | 1.23               |        |                    |                    |

| 21     | 780                | 1.20               | 44     | 372                | 1.22               |        |                    |                    |

| 22     | 745                | 1.27               | 45     | 364                | 1.23               |        |                    |                    |

| 23     | 712                | 1.21               | 46     | 356                | 1.22               |        |                    |                    |

表 A5. AD7534 のシステム・ゲイン 対 デジタル入力コードと算出した比(1 +  $R_{FB}/R_O$ )

© Analog Devices, Inc. All rights reserved. 商標および登録商標は各社の所有に属します。