# DESIGN NOTES

## 昇圧レギュレータの短絡保護 - デザインノート154

Jeff Witt

基本的な昇圧レギュレータのトポロジーには短絡保護はありません。出力が低くなると、入力からインダクタとキャッチ・ダイオードを通して大きな電流が流れる可能性があります。この電流はこれらの部品の直列抵抗によってのみ制限されます。そのため、昇圧レギュレータ、負荷、または電源が損傷するおそれがあります。本デザインノートでは、この問題を解決するための方法をいくつか紹介します。

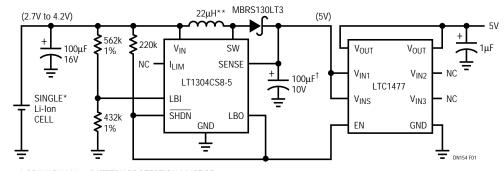

#### LTC1477による短絡保護と負荷の切離し

LTC®1477の保護付きハイサイド・スイッチは、低損失のNMOSパワー・スイッチを内蔵し、2つの方法で外部回路を保護します。すなわち、スイッチ電流は0.85A、1.5A、または2Aに制限され(構成に応じて決まる)また電力損失によってダイ温度が130 になるとサーマル・シャットダウン回路がスイッチをターンオフします。図1では、LTC1477がマイクロパワー昇圧レギュレータLT®1304と負荷を過電流から保護します。負荷電流の増加は最初に0.85Aに制限され、スイッチの電力損失がさらに増えるとLTC1477はスイッチをサイクルして平均電流を制限し、損失を許容レベルに抑えます。イネーブル・ピンは出力を切り離すのに使用できます。この回路では、LT1304は内蔵のバッテリ電圧低下検知器を使用して、バッテリ電圧が2.7V以下に低下すると自身をシャットダウンして、負荷を切り離します。

より高電力のアプリケーションの場合は、LTC1477の  $V_{\text{IN2}}$ ピンと $V_{\text{IN3}}$ ピンも入力に接続しなければなりません。これによって電流制限は2Aとなり、スイッチ抵抗はわずか 0.07 です。LTC1477は2.7V ~ 5.5 Vで動作し、SO-8 パッケージで提供されます。LTC1478はデュアル・バージョンであり16ピンSOで提供されます。

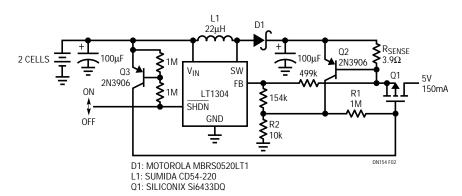

### 電流制限付昇圧レギュレータ

重負荷時の出力電流を中断しないで、制限するほうが望ましい場合があります。図2に出力電流を150mAに制限した、2セルから5Vの昇圧コンバータを示します。LT1304は、R1とR2を通してゲートが接地されたQ1のソースに5Vを生成し、Q1がターンオンすると出力に電流を供給します。負荷電流が増加してR<sub>SENSE</sub>両端の電圧が0.6VになるとQ2がターンオンし、R2を流れる電流によって帰還ピンの電圧が上昇します。するとLT1304は出力電流が150mAになるよう調整を開始します。出力電圧が入力電圧より低くなると、LT1304は出力電流を制御できなくなりQ2はQ1のゲートをプルアップして出力電流を調整します。出力がグランドに短絡したとき、Q1での電力損失は約0.4Wであることに注意してください。LT1304がシャットダウンすると、追加されているトランジスタ(Q3)が負荷を切り離します。R<sub>SENSE</sub>は全負荷状態に近い場合の効率を低下させ

**▲ブ**、LTC、LTはリニアテクノロジー社の登録商標です。

- \* PRIMARY Li-Ion BATTERY PROTECTION MUST BE PROVIDED BY AN INDEPENDENT CIRCUIT

- \*\* SUMIDA CD54-220

- <sup>†</sup> AVX TPSD107M010R0100

図1. 短絡保護と負荷の自動切離し機能を持つ昇圧コンバータ

ますが、本質的にこの追加回路がLT1304の優れた軽負荷時の効率に影響を与えることはありません。

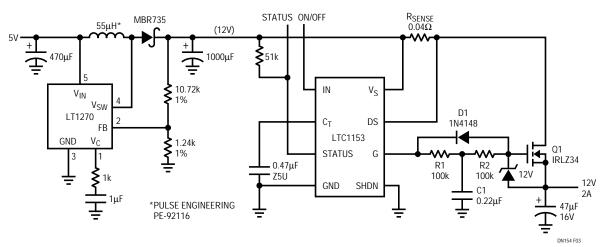

#### 高電力時の短絡保護

高電流時には、高効率を維持しまた電力損失を処理可能な範囲に抑えるために、低R<sub>DSON</sub>のトランジスタと低電圧での電流センシングが必要です。LTC1153回路ブレーカICは、電流センス抵抗両端の電圧が100mVを超えると、外付けハイサイドNチャネルFETをドライブしてFETをターンオフします。トリップ遅延時間とリセット時間は外付け部品で設定可能です。

LT1270昇圧コンバータは5V入力から12V/2Aを生成できます(図3)。2.5AでトリップするようにLTC1153をプログラムして、出力短絡に対する保護が行われています。起動時、

LTC1153はフィルタ(R1とC1)を通してQ1のゲートをドライブします。これによって、出力でのdV/dtを制限し、容量性負荷への突入電流を制御します。R<sub>SENSE</sub>での電圧降下が100mVを超えたことをLTC1153が検知すると、Q1のゲートはダイオードD1を通して接地されます。FETはC<sub>T</sub>ピンに接続されたコンデンサによって決まる期間だけオフになります。リセット時間をトリップ遅延時間(最大60μs)およびQ1のターンオン時間(~R1 C1)より長く設定すると、平均出力電流はピーク電流よりもはるかに低くなります。これにより、FETと負荷の電力損失を安全なレベルに維持します。LTC1153のSTATUSピンのオープン・コレクタは、回路ブレーカの状態を示します。INピンを"L"にすれば出力を切り離すことができます。LTC1153は4.5V~18Vで動作し、8ピンPDIPまたはSOパッケージで供給されます。

図2. 負荷切離し機能を備えた電流制限付昇圧コンバータ

図3. 回路ブレーカ(ポスト・レギュレータ)、ブレーカ・ステータス・フィードバック、およびランプアップする出力を備えた2A/12V昇圧レギュレータ