# OPアンプの実装と 周辺回路の実用技術

## OPアンプ大全 第5巻

ANALOG DEVICES アナログ・デバイセズ 著

電子回路技術研究会 訳

# OPアンプの実装と 周辺回路の実用技術

OPアンプ大全（第5巻）

ANALOG DEVICES アナログ・デバイセズ 著

電子回路技術研究会 訳

CQ出版社

本書は下記の出版物を著作権者の許諾に基づいて全5巻に分けて日本語訳したものです。

Op Amp Applications

Copyright © 2002 By Analog Devices, Inc.

Original : Printed in the United States of America (ISBN 0-916550-26-5)

All rights reserved. This book, or parts thereof, must not be reproduced in any form without permission of the copyright owner. Information furnished by Analog Devices, Inc. is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices, Inc. for its use.

Analog Devices, Inc. makes no representation that the interconnections of its circuits as described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of licenses to make, use, sell equipment constructed in accordance therewith. Specifications are subject to change without notice.

## 謝 辞

本書のような規模の書籍は、多くの人々の協力がなければ完成させることはできません。この“Op Amp Applications”の編纂を通して、多大の貢献、協力を提供してくれた以下の方々に、心からの謝意をおくります。

まず、このプログラムの推進を励まし、助力してくれたアナログ・デバイセズ社(ADI)にお礼を述べたいと思います。

次に、ADIセントラル・アプリケーション・グループのウォルト・ケスター氏に深く感謝いたします。かれは、ADIでの長年にわたるセミナーノート編纂に携わった経験による、多くの知識や助言を惜しみなく提供してくれました。本書の材料となる資料の著者である、ケスター氏とそのグループの方々に感謝いたします。

同じく、多くのコメントや書評を寄せていただいた、ADIフィールド・エンジニアリング・グループとセントラル・アプリケーション・グループのスタッフにお礼を申し上げます。エド・グロカルスキイ氏、ブルース・ホーマン氏、ボブ・マーウィン氏、そしてアーノルド・ウイリアムズ氏には、多くの有用なコメントをいただきました。加えて、かつてADI社のアプリケーション・エンジニアであったウェス・フリーマン氏には、ほとんどの原稿に目を通してください、有益なフィードバックをいただきました。

ADI社のダン・シャインゴールド氏には、特に感謝の意を示したいと思います。氏は、本書の内容に対する数え切れないほどの指摘や書評を提供してくれただけでなく、氏が真空管OPアンプ時代に過ごしたジョージ・A・フィルブリック・リサーチ社(GAP/R)の頃からの長年にわたる経験をもとにした、多くの示唆にとんだ見識を示してくれました。

このほか、それぞれのセクションの最後に特記してある、個別のコメントなどを提供してくださった多くの協力者の皆さんに感謝します。

ジュディス・ドーヴィル女史には、索引の作成および原稿に対する多くの助言をいただき、感謝しています。

最後に、スライドの準備、タイピング、文章スタイルのデザイン等を行ってくれたW<sup>2</sup>グラフィックス社に感謝いたします。

ウォルト・ユング(Walt Jung), 2002年8月

Analog Devices Inc. Central Applications Department.

## まえがき

「OPアンプ大全（全5巻）」の第2冊目として、本書 第5巻が発行の運びとなりました。第1巻の次に第2巻ではなく、第5巻が先に発行された理由について、簡単にご説明しておきます。本書は、次ページ下部の一覧にあるように、原著では最終章を飾る“Chapter-7 Hardware and Housekeeping Techniques”を翻訳して1冊にまとめたものです。“Housekeeping”とは、辞書によれば「家事」のことですが、ここではおそらく「やりくり」といったような意味合いで使われているものと思われます。

今日、OPアンプは多種多様な用途で利用されていますが、OPアンプICだけでは回路は動作しません。OPアンプを応用した一般のエレクトロニクス機器は、抵抗、コンデンサに代表される受動部品、それらを実装するためのプリント配線板、回路を収めるケース、電源回路などの周辺回路や構造部品から成り立っています。

スタープレイヤばかりを集めたチームがかならずしも常勝できるわけではないのと同様に、よく考えられたバランスの良い設計のなされた電子回路は、ただ闇雲に高価な部品を採用した電子回路に勝ります。

設計の成果である「製品」あるいは「作品」は、周辺回路を含めた技術の積み重ねです。工業製品であるかぎり、できるだけ安価なコストでより良い性能を実現しなければなりません。性能とコストのバランスを取るためにには、周辺回路の性能とコストの知識が欠かせません。

さらに、この第5巻では、最近の機器の小型化に伴ってますます重要性が増してきた熱の問題とEMIについて解説しています。また、回路設計に欠かせないアナログ・シミュレーションと回路動作の確認を行うためのプレッドボード製作やプロトタイピングに必要な技術について触っています。

その結果、OPアンプ回路のみならず、アナログ/デジタルを問わず電子回路一般で役に立つ技術を取り扱うことになりました。機器設計に必要な知識のエッセンスが詰まっています。これらのエッセンスを逸早く読者のもとに届けたいとの思いから、第5巻の翻訳作業が先行されたわけです。

本シリーズの翻訳チームのメンバは、そのほとんどが現役の回路設計者です。厳しい納期要求のなかで、回路設計以上に部品の配置やプリント配線板のレイアウト・パターンの1本1本に、昼夜を問わずに奮闘努力しています。

訳出に際しては単に英語を日本語に置き換えるだけでなく、原著者の意図する内容を理

解し、日本語の文章に書き直すようにしました。

本書で解説されている内容を、これまで「ノウハウ」として片付けてきた技術を体系的に理解する手助けとして、また「転ばぬ先の杖」として利用していただければ喜びです。

訳者代表：北村 透

#### ►OPアンプ大全(全5巻)の構成と原著との対応

- 第1巻 第1部 ..... Chapter - H Op Amp History

- 第2部 ..... Chapter - 1 Op Amp Basics

- 第2巻 第3部 ..... Chapter - 2 Specialty Amplifiers

- 第4部 ..... Chapter - 3 Using Op Amps with Data Converters

- 第5部 ..... Chapter - 4 Sensor Signal Conditioning

- 第3巻 第6部 ..... Chapter - 5 Analog Filters

- 第4巻 第7部 ..... Chapter - 6 Signal Amplifiers

- 第5巻 第8部 ..... Chapter - 7 Hardware and Housekeeping Techniques

## 目 次

### 第8部 ハードウェアとトラブル対策

|                                     |           |

|-------------------------------------|-----------|

| <b>第1章 受動部品</b>                     | <b>13</b> |

| 1-1 コンデンサ.....                      | 14        |

| ●誘電体吸収 (Dielectric Absorption ; DA) | 15        |

| ●コンデンサの寄生インピーダンスと損失                 | 17        |

| ●誤差, 温度とその他の影響                      | 18        |

| ●重要な部品は最後に実装のこと                     | 19        |

| 1-2 抵抗とポテンショメータ.....                | 21        |

| ●抵抗の寄生リアクタンス                        | 24        |

| ●熱電対効果                              | 24        |

| ●電圧感度, 不良発生の仕組みとエージング効果             | 26        |

| ●抵抗の発生するノイズ                         | 27        |

| ●半固定抵抗                              | 27        |

| 1-3 インダクタンス.....                    | 29        |

| ●ストレイン・インダクタンス (浮遊インダクタンス)          | 29        |

| ●相互インダクタンス                          | 30        |

| ●リング                                | 32        |

| ●インダクタンスの寄生効果                       | 33        |

| ●Q(クオリティ・ファクタ)                      | 34        |

| 1-4 細かなことも見逃してはいけない.....            | 34        |

| <b>第2章 プリント基板設計の諸問題</b>             | <b>37</b> |

| 2-1 導体の抵抗.....                      | 38        |

| 2-2 信号線での電圧降下…ケルビン・フィードバック.....     | 40        |

| 2-3 信号の帰還電流.....                    | 41        |

| ●グラウンド・ノイズとグラウンド・ループ                | 42        |

| ●スター・グラウンド (star ground)            | 45        |

| ●アナログ・グラウンドとデジタル・グラウンドの分離           | 45        |

| ●グラウンド・プレーン (ground plane)          | 48        |

| ●表皮効果 (skin effect)                 | 49        |

|                                        |    |

|----------------------------------------|----|

| ● 伝送線路                                 | 50 |

| ● グラウンド・プレーンの切れ目に注意                    | 51 |

| ● グラウンド・アイソレーションの技術                    | 53 |

| ● 静的な基板の影響                             | 56 |

| ● MINIDIP と SOIC の OP アンプのガード電極レイアウトの例 | 59 |

| ● 動的な基板の影響                             | 61 |

| 2-4 浮遊容量 (stray capacitance) .....     | 62 |

| ● 容量性ノイズとファラデー・シールド                    | 63 |

| ● 電気的に浮いたシールドの問題                       | 64 |

| ● ロジック・ノイズに対して A-D コンバータにバッファを付ける      | 66 |

|                                          |           |

|------------------------------------------|-----------|

| <b>第3章 OPアンプ用の電源システム</b>                 | <b>69</b> |

| 3-1 リニア IC による安定化 .....                  | 70        |

| ● リニア型電圧レギュレータの基礎                        | 71        |

| ● パス・デバイス                                | 73        |

| ● 可変電圧 IC を使用した ±15V レギュレータ              | 73        |

| ● 低ドロップアウト・レギュレータのアーキテクチャ                | 75        |

| ● 固定電圧型の 50/100/200/500 mA 出力 LDO レギュレータ | 77        |

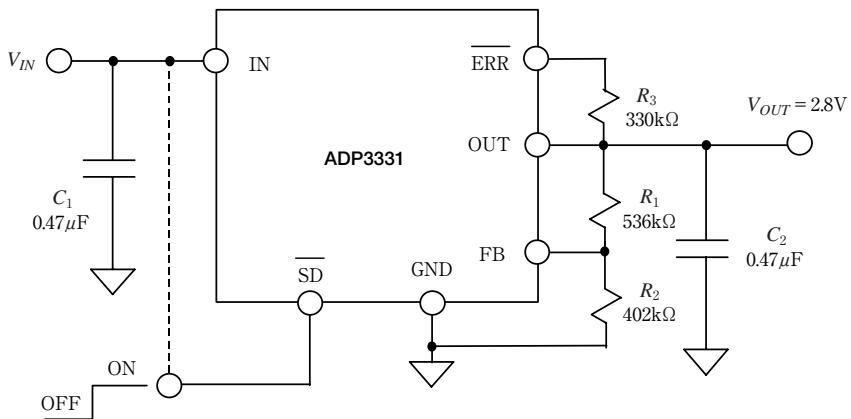

| ● 電圧設定が可能な 200 mA LDO レギュレータ             | 78        |

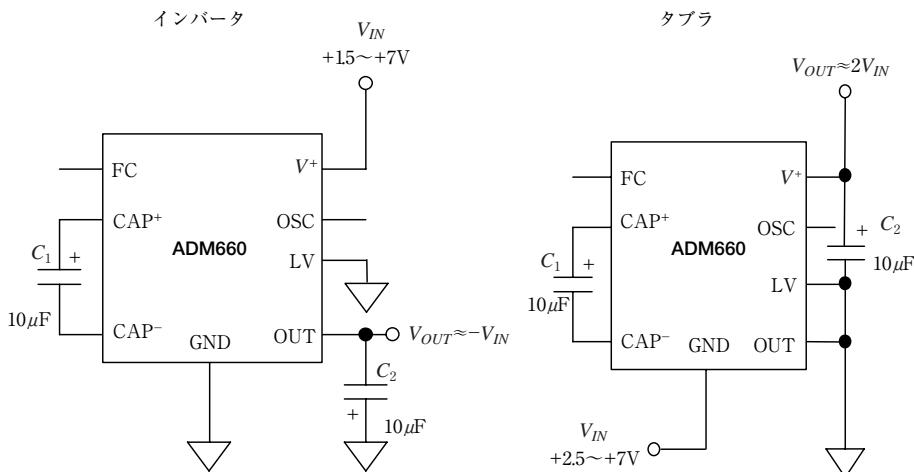

| 3-2 チャージ・ポンプ型電圧コンバータ .....               | 80        |

| ● 非安定化チャージ・ポンプ型電圧インバータ / ダブル             | 82        |

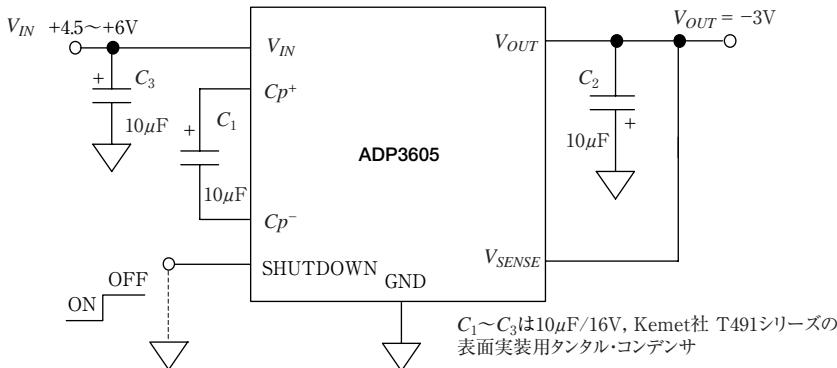

| ● 出力電圧を安定化したチャージ・ポンプ型電圧コンバータ             | 83        |

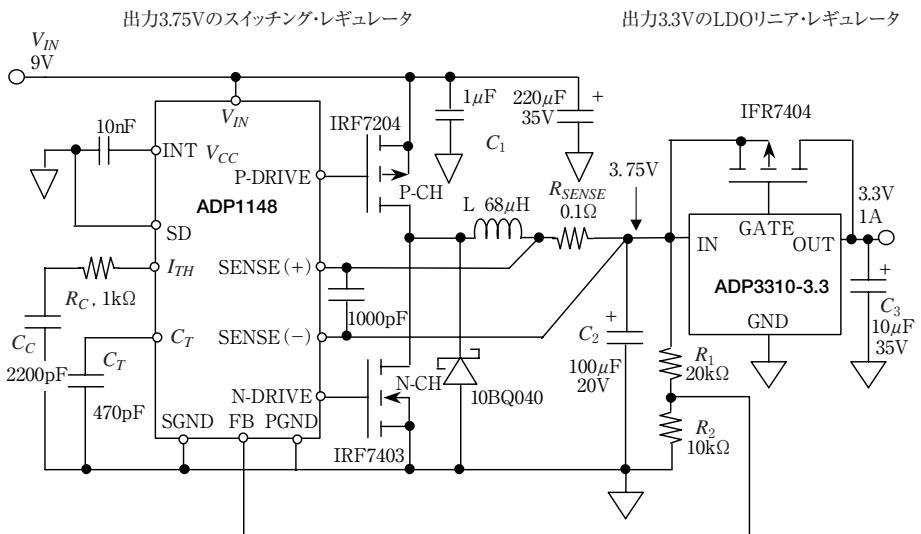

| 3-3 スイッチング電源用のリニア型ポスト・レギュレータ .....       | 84        |

| 3-4 電源のノイズ低減とフィルタリング .....               | 86        |

| ● コンデンサ                                  | 87        |

| ● フェライト                                  | 91        |

| ● カード入力用フィルタ                             | 92        |

| ● レール・バイパス / 配電フィルタ                      | 93        |

| ● 局所的な高周波バイパス / デカップリング                  | 95        |

## 目 次

### 第8部 ハードウェアとトラブル対策

|                                      |            |

|--------------------------------------|------------|

| <b>第4章 OPアンプの保護</b>                  | <b>99</b>  |

| 4-1 通電時の過電圧保護回路.....                 | 99         |

| ●一般的な同相入力電圧の制限                       | 100        |

| ●クランプ・ダイオードの漏れ電流                     | 102        |

| ●応用の広いボルテージ・フォロワ保護回路                 | 103        |

| 4-2 CMOSチャネル保護素子を利用した同相過電圧保護回路 ..... | 105        |

| ●同相電圧耐入力の高い計装アンプを利用した同相過電圧保護回路       | 106        |

| ●反転回路を利用した保護回路                       | 108        |

| 4-3 アンプ出力電圧の位相反転(フェイズ・リバーサル) .....   | 109        |

| ●出力位相反転確認試験                          | 110        |

| ●出力位相反転の解決方法                         | 111        |

| 4-4 差動電圧入力からの保護.....                 | 112        |

| ●計装アンプを過電圧から保護する                     | 113        |

| 4-5 回路実装以前における過電圧からの保護.....          | 118        |

| 4-6 ESDのモデル化とテスト .....               | 123        |

| <b>第5章 热に関する考察</b>                   | <b>129</b> |

| 5-1 热についての基本.....                    | 130        |

| 5-2 放热.....                          | 131        |

| <b>第6章 EMIとRFIへの対策</b>               | <b>139</b> |

| 6-1 EMI/RFIのメカニズム .....              | 140        |

| ●EMIノイズの発生源                          | 140        |

| ●EMIの結合経路                            | 141        |

| ▶ノイズの電磁結合のメカニズム                      | 141        |

| ●共通インピーダンスによるノイズを低減する                | 142        |

| 6-2 近傍電磁界干渉によるノイズ.....               | 143        |

| ●容量結合によるノイズを低減させる                    | 143        |

| ●磁気結合によるノイズを低減させる                    | 144        |

|                                        |     |

|----------------------------------------|-----|

| ●受動部品：EMIに対抗するための味方                    | 145 |

| ●EMIに対してのシステム感度を低減させる                  | 146 |

| 6-3 シールドとは何か……………                      | 147 |

| ●ケーブルとシールドについての一般的な注意点                 | 150 |

| 6-4 入力段でのRFI整流作用の感度……………               | 156 |

| ●予備知識：OPアンプと計装アンプのRFI整流作用の感度のテスト方法     | 156 |

| ●解析的アプローチ：バイポーラ・トランジスタのRFI整流作用         | 158 |

| ●解析的アプローチ：FETのRFI整流作用                  | 159 |

| 6-5 OPアンプや計装アンプ回路においてRFI整流作用を低減する…………… | 160 |

| ●OPアンプの入力                              | 161 |

| ●計装アンプ（インスツルメンテーション・アンプ）の入力端子          | 162 |

| ●増幅器の出力とEMI/RFI                        | 165 |

| 6-6 EMI/RFI対策のためのプリント基板の設計……………        | 166 |

| ●ロジック・デバイスの選定に注意！                      | 167 |

| ●よく考えてプリント基板を設計する                      | 167 |

| ●インピーダンス・コントロールされた配線をプリント基板上に設計する      | 168 |

| ●マイクロストリップによるプリント基板伝送線路                | 169 |

| ●マイクロストリップにおけるいくつかの概算方法                | 171 |

| ●対称型ストリップ・ラインのプリント基板伝送線路               | 172 |

| ●信号線を内層に通すことの利点と欠点                     | 173 |

| ●伝送線路の終端に関する概算方法                       | 174 |

## **第7章 シミュレーションとブレッドボードとプロトタイピング**

**179**

|                                  |     |

|----------------------------------|-----|

| 7-1 アナログ回路シミュレーション……………          | 179 |

| ●マイクロモデルとマクロモデル                  | 181 |

| 7-2 ADSpiceにおけるOPアンプのマクロモデル…………… | 182 |

| ●入力段とゲイン/ポール段                    | 183 |

| ●周波数特性の設定段                       | 184 |

| ●マクロモデルの出力段                      | 186 |

# 目 次

## 第8部 ハードウェアとトラブル対策

|                                      |     |

|--------------------------------------|-----|

| ● モデルの過渡応答特性                         | 187 |

| ● ノイズ・モデル                            | 188 |

| 7-3 電流帰還型 OP アンプのモデル .....           | 190 |

| 7-4 シミュレーションはブレッドボードの置き換えにはならない..... | 192 |

| ● シミュレーションは賢く使うべきツール                 | 193 |

| ● モデルのことを知る                          | 193 |

| ● プリント基板の寄生要素を理解する                   | 194 |

| ● シミュレーションは設計サイクルをスピードアップする          | 196 |

| ● SPICE のサポート状況                      | 196 |

| ● モデルのサポート                           | 197 |

| 7-5 ブレッドボードとプロトタイプ製作のテクニック .....     | 198 |

| ● 「デッド・バグ」によるプロトタイプ                  | 199 |

| ● はんだ付け実装によるプロトタイプ                   | 202 |

| ● 表面切削型プリント基板によるプロトタイプの製作            | 203 |

| ● ソケットの使用には注意が必要                     | 205 |

| ● プロトタイプ製作のそのほかのポイント                 | 206 |

| 7-6 評価用ボード .....                     | 207 |

| ● 汎用の OP アンプ評価ボード                    | 207 |

| ● 専用に用意されている OP アンプ評価ボード             | 208 |

| ● まとめ                                | 210 |

| 索引 .....                             | 212 |

OPアンプ大全 第8部

ハードウェアとトラブル対策

Chapter-7 Hardware and Housekeeping Techniques

|                               |     |

|-------------------------------|-----|

| 受動部品                          | 13  |

| プリント基板設計の諸問題                  | 37  |

| OPアンプ用の電源システム                 | 69  |

| OPアンプの保護                      | 99  |

| 熱に関する考察                       | 129 |

| EMIとRFIへの対策                   | 139 |

| シミュレーションとブレッドボードと<br>プロトタイピング | 179 |

8

## はじめに

この大全の中でも最も長い第8部（原著では Chapter-7）で述べる OPアンプの周辺技術は、今まで述べてきた基本的な OPアンプ回路技術と同じように重要です。

ここでは、システムのハードウェアや周辺回路技術に隠された問題点について述べます。「周辺回路技術に隠された回路やシステムの問題点」とは、OPアンプ以外の回路動作に必要なOPアンプ周辺の回路技術です。

このなかには、受動部品の特性、プリント基板の設計、電源回路、過大電圧や熱の影響からOPアンプを保護する方法、EMI/RFIの問題、そしてシミュレーションやブレッドボード、プロトタイプの製作が含まれます。いくつかの項目は直接にはデザインの手順と関係ありませんが、正しいデバイスや周辺回路定数の選択と同じように重要なものです。

**Walt Kester, James Bryant, Walt Jung／訳：北村透**

# 第 1 章

## 受動部品

James Bryant, Walt Jung, Walt Kester／訳：北村 透

OP アンプやその他の高精度アナログ IC を利用した回路設計をするとき、性能の悪い受動部品を利用しないようにしなければなりません。不適当な受動部品を選択すると、最高の OP アンプやデータ・コンバータを利用しても、その回路設計は失敗に終わってしまいます。本章では、OP アンプ回路における受動部品の一般的な「落とし穴」について述べることにします。

高価な高精度 OP アンプやデータ・コンバータを基板に実装したところ、システムが要求仕様を満足していないことに気付くことがあります。ドリフトや周波数特性、ときには発振で苦しむこともあるでしょう。あるいは単に期待した性能が出ないこともあるでしょう。このとき、デバイスを疑うまえに、受動部品…たとえばコンデンサ、抵抗、ポテンショメータあるいはプリント基板…を十分に吟味したほうがよいでしょう。受動部品の小さな誤差、温度、寄生効果、経時変化、実装工程などが、あなたが意識しない影響を回路に与えているかもしれません。これらの影響は受動部品メーカーが規定していない特性（あるいはデータシートでちょっとだけ触れている特性）の影響なのです。

一般的に、12 ビット以上の分解能のデータ・コンバータか数百円の OP アンプを利用する場合、受動部品に十分な注意を払わなければなりません。12 ビットの D-A コンバータを例にあげると、 $1/2 \text{ LSB}$  はフルスケールの 0.012 % (122 ppm) に当たります。複数の受動部品の誤差の累積は、この値をはるかに越える誤差をもたらします。しかし、問題を解決するために最も高価な受動部品を購入する必要はありません。通常、数十円の適切なコンデンサを選択すれば十分な性能と、非常に高価な部品と比較しても、コストパフォーマンスの優れた設計ができます。受動部品の基本的な理解と解析に労力を払う価値が十分にあります。

## 1-1 コンデンサ

ほとんどの設計者は、入手可能な種々のコンデンサについて慣れ親しんでいることと思います。しかし、コンデンサの種類があまりに多いために、コンデンサを利用した高精度回路における動的/静的な誤差発生のメカニズムを忘れてしまうことがあります。コンデンサの種類は、ガラス・コンデンサ、アルミ箔電解コンデンサ、固体タンタル・コンデンサ、タンタル箔電解コンデンサ、マイカ・コンデンサ、セラミック・コンデンサ、テフロン・コンデンサ、そしてポリエスチル、ポリカーボネート、ポリスチレン、ポリプロピレンを含むフィルム・コンデンサなどがあります。さらに、実装方法で区分すると、従来からあるリード・タイプと最近多数利用されている表面実装タイプがあります。

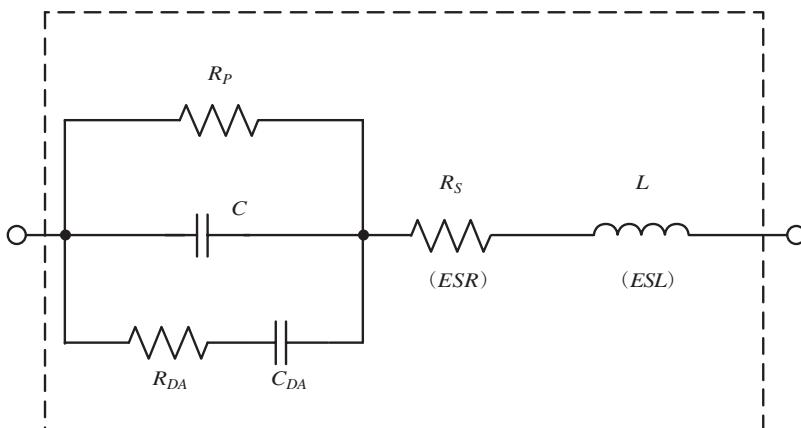

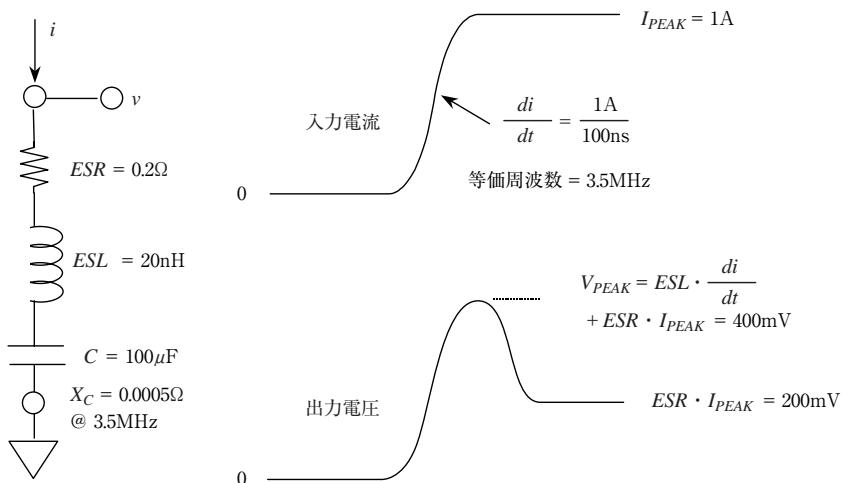

図1-1にコンデンサの動作モデルを示します。キャパシタンス  $C$  が、絶縁抵抗（漏れ電流を生じる）を表す並列抵抗  $R_P$  で短絡されています。コンデンサのリード線や電極の抵抗を代表する第2の抵抗  $R_S$ （等価直列抵抗；  $ESR$ ）は、コンデンサに直列に接続されます。

コンデンサの特性を各要素に分離することは簡単ではありません。個々の特性とモデルの関係を明確に説明することは困難です。インダクタンス  $L$ （等価直列インダクタンス；  $ESL$ ）は、リード線や電極のインダクタンスを表します。抵抗  $R_{DA}$  とキャパシタンス  $C_{DA}$  の組み合わせは、誘電体吸収（dielectric absorption；  $DA$ ）を単純化したモデルです。この誘電体吸収効果は、高速および低速回路の動特性に大きな影響を与えることがあります。実際のコンデンサは、 $R_{DA}$  と  $C_{DA}$  の直列回路を複数個並列接続した回路と考えることができます。これらの寄生  $RC$  素子は、タイミング回路の特性を劣化させることができます。以下に現象の詳細を述べます。

〈図1-1〉寄生素子を含む実際のコンデンサの等価回路

### ●誘電体吸収 (Dielectric Absorption ; DA)

誘電体吸収（「ソーケイジ (soakage)」または「誘電体ヒステリシス」とも呼ばれる）は、コンデンサの寄生効果のなかで大きな影響を与える可能性をもった効果であるにもかかわらず、あまりよく理解されてはいません。放電時に、ほとんどのコンデンサは、メモリ効果により充電した電荷をすべて放電することができません。

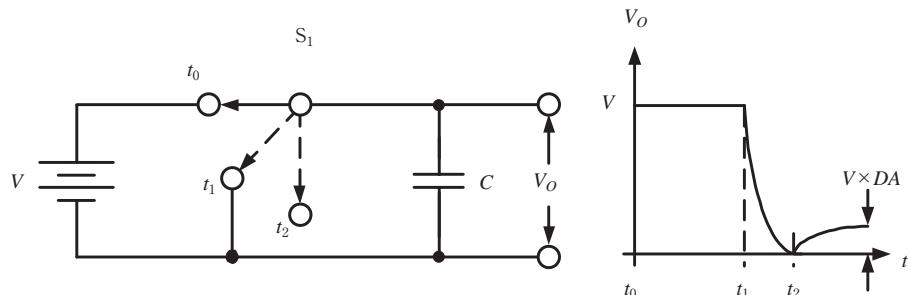

図1-2にこの現象を図示します。左図に示されるように、コンデンサは電源電圧  $V$  まで充電されたのち、時刻  $t_1$  でスイッチ  $S_1$  により短絡されて放電します。その後、 $t_2$ においてコンデンサの端子は開放されます。すると端子電圧はゆっくりと上昇し、ほぼ一定の電圧に達します。この残留電圧の原因は誘電体吸収であり、右図に示されるように充電－放電－復帰シーケンスの時間と電圧で決定されます。復帰電圧の誤差は充電電圧  $V$  と使用されているコンデンサの誘電体吸収の特性に比例します。

誘電体吸収を測定あるいは規定する標準的な方法は極めて少ないとえます。測定結果は、コンデンサに充電された電圧と、再び現れた電圧の比をパーセントで表します。標準的な試験手順は以下のとおりです。まず、コンデンサを十分に長い時間充電し、その後、短い一定時間だけ短絡します。さらにコンデンサを開放状態で一定時間放置し、端子電圧を測定します〔詳細は参考文献(8)を参照のこと〕。ここでは基本的な現象を説明しましたが、実際のコンデンサは極めて広い範囲の誘電体吸収による誤差を示し、その誤差は誘電体の種類により決定され、1%程度か、それ以下の値を示します。実際の誘電体吸収はいろいろな形で現れます。積分器がリセット後に0Vにならない、電圧－周波数変換回路が予期しない非直線性を示す、あるいはサンプル&ホールド回路が一定とならない誤差を示したりします。サンプル&ホールド回路で発生する現象は、データ収集システムの隣り合ったチャネルに、フルスケールに近い電位差が印加されたとき特に大きな影響を与えます。

図1-2 誘電体吸収を規定する充放電後の開放残留電圧

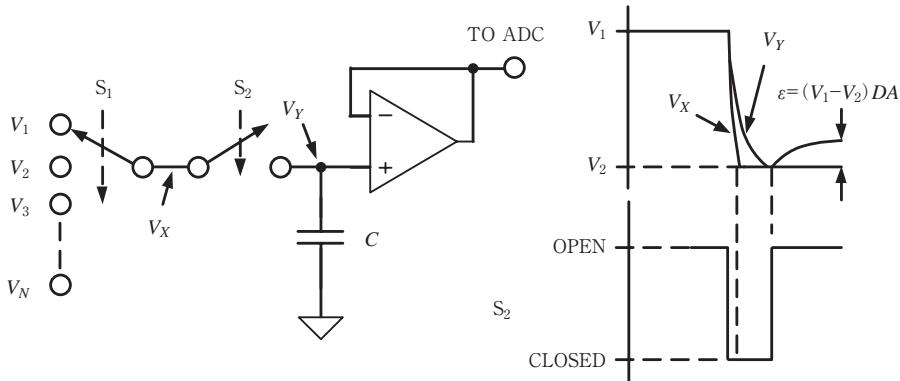

〈図1-3〉サンプル&amp;ホールド回路において誘電体吸収が発生する誤差

図1-3は簡単なサンプル&ホールド回路における誘電体吸収誤差を示します。左図において、スイッチ \$S\_1\$ と \$S\_2\$ はそれぞれサンプル&ホールド回路のマルチプレクサとサンプル&ホールド・スイッチを示しています。ここで、マルチプレクサの出力電圧を \$V\_X\$、A-Dコンバータに印加するためにOPアンプで増幅した後に\$C\$でホールドする電圧を\$V\_Y\$とします。右のタイミング図に示されるように、誘電体吸収による誤差電圧\$\varepsilon\$はコンデンサが開放されているホールド・モードの間に現れます。この電圧は\$V\_1\$と\$V\_2\$の差に比例するため、それぞれの電圧がダイナミック・レンジの最大値と最小値を取ったとき、もっとも大きな値となります。サンプル&ホールド回路の誘電体吸収による誤差を最小にする現実的な方法は、最良のコンデンサを利用することです。

誘電体吸収現象は、コンデンサの製造工程や電極材料により影響を受けることもあります。おもに誘電体材料の特性で決定されます。誘電体吸収は充電電圧に対して発生する電圧のパーセントで定義されます。テフロン、ポリスチレン、ポリプロピレン・コンデンサにおいては0.02%ですが、電解コンデンサでは10%か、あるいはそれ以上のこともあります。特殊なポリスチレン・コンデンサの誘電体吸収は約0.002%です。

一般的な高誘電率セラミック・コンデンサやポリカーボネート・コンデンサの誘電体吸収は0.2%程度ですが、この値は8ビットでの1/2 LSBに相当します。シルバード・マイカ、ガラス、タンタル・コンデンサはさらに大きく1~5%程度の値を示し、ポリエステルは0.5%程度を示します。コンデンサの規格表に、利用しようとしている電圧レンジや時間における誘電体吸収が規定されていなければ注意してください。そのような場合は、低い誘電体吸収を規定しているほかのタイプのコンデンサを選択したほうが無難でしょう。

誘電体吸収は、ハイパス・フィルタやACアンプの高速セトリング回路などの過渡応答

において長いセトリングの原因となります。このような用途に利用されるコンデンサでも、図1-1に示した  $R_{DA}$  と  $C_{DA}$  で決定される時定数が数msを示すことがあります。さらに長い時定数もまれではありません。複数の異なる時定数をもつ  $R_{DA}, C_{DA}$  並列回路でモデル化されるデバイスもあります。高速充電、高速放電用途で誘電体吸収はアナログ・メモリのようにふるまいます。コンデンサが過去の充電電圧を思い出そうとしているかのようです。

回路によっては誘電体吸収の特性が単純で、簡単に定義できる場合もあり、特別な調整を実施することにより補正することができます。たとえば、積分器の積分コンデンサと並列に誘電体吸収と等価な負性抵抗帰還回路を接続することで補正できます。このような補正を施すことにより、サンプル&ホールド回路の性能を10倍以上高めることができます [文献(6) 参照]。

### ●コンデンサの寄生インピーダンスと損失

図1-1にコンデンサの漏れ抵抗  $R_P$  と等価直列抵抗  $R_S$ 、そして直列インダクタンス  $L$  を示しました。これらの寄生インピーダンスは回路の特性を劣化させます。これらの効果をまとめて損失(DF)と定義することがあります。

コンデンサの漏れ電流は、電圧を加えたときに誘電体に流れる微小電流です。等価回路は単純なコンデンサに並列接続された絶縁抵抗  $R_P$  ですが、このリーク電流は実際には電圧に対して非直線な値を示します。製造メーカは誘電体の自己放電時定数として、リーク抵抗と容量の積をとり、 $M\Omega \cdot \mu F$  [秒] として表すこともあります。リークの多い電解コンデンサの場合、この値は1秒より小さな値をとり、セラミック・コンデンサの場合は100秒程度です。ガラス・コンデンサの場合、自己放電時定数は1000秒以上です。しかし、もっとも漏れ電流が少ないコンデンサはテフロン・コンデンサや特定のフィルム・コンデンサ(ポリスチレン、ポリプロピレン)で、1,000,000  $M\Omega \cdot \mu F$  に達します。このようなコンデンサでは、リーク電流は誘電体内部ではなく、素子のケースや配線など機構構成物の表面を流れます。

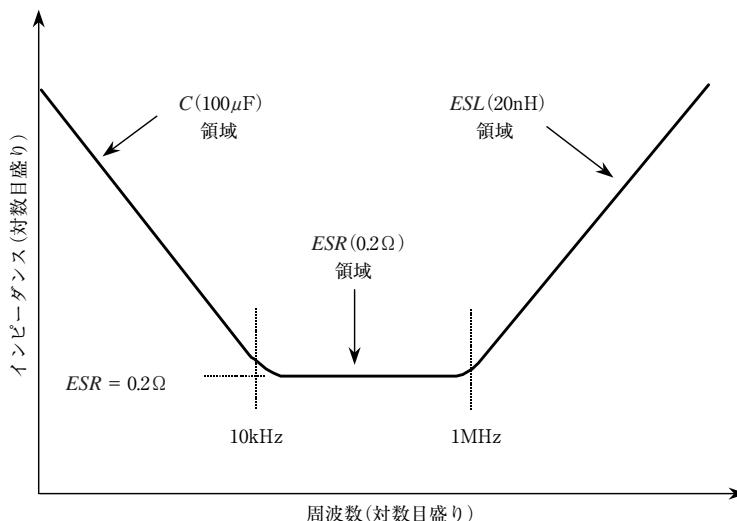

等価直列インダクタンス  $ESL$  (図1-1参照) は、コンデンサのリード配線や電極で発生し、高周波において本来なら容量性のリアクタンスを示すコンデンサ特性が誘導性になってしまいます。 $ESL$  の値はコンデンサの内部構造に強く依存します。金属箔を巻いた筒状タイプのコンデンサは、モールドされたラジアル・リードのコンデンサと比較して、かなり大きな  $ESL$  を示します。多層セラミック・コンデンサやフィルム・タイプのコンデンサは最も小さな直列インダクタンスを示し、タンタル・コンデンサや電解コンデンサは一般に最も大きな値を示します。その結果、一般的な電解コンデンサだけで高速信号をバイパスすることは適当ではありません。高速信号のバイパス・コンデンサ用に作られた特殊なタンタル・コンデンサやアルミ電解コンデンサを利用します。これらは、次章で述べ

るよう、スイッチング電源用に設計されたタンタル・コンデンサやアルミ電解コンデンサです。

コンデンサの製造メーカーは、等価直列インピーダンスをインピーダンス－周波数特性のグラフで定義する場合もあります。このカーブは低周波の部分ではほぼ容量性ですが、高い周波数では直列インダクタンスの影響によりインピーダンスが増加します。

等価直列抵抗  $ESR$  (図1-1では抵抗  $R_S$ ) の原因は、コンデンサのリードや電極の抵抗です。すでに述べたように多くのメーカーは  $ESR$ ,  $ESL$ , リーク電流をひとまとめにし、損失  $DF$  (Dissipation Factor) で表しています。損失はコンデンサの効率の悪さを示します。製造メーカーは、コンデンサの1サイクル中に失われたエネルギーと保存されたエネルギーの比として定義しています。ある周波数における  $ESR$  とコンデンサの総リアクタンスの比は、 $DF$  の値にはほぼ等しく  $Q$  の逆数と等価な値となります。よって、 $Q = 1/DF$  ( $DF$  は数値で示される) と近似されます。たとえば  $DF$  が 0.1% あれば、この値は 0.001 ですから、逆数を計算すれば  $Q$  は 1000 となります。この損失は温度と周波数によって変化します。マイカ・コンデンサやガラス・コンデンサの  $DF$  は一般に 0.03% ~ 1.0% です。一般的なセラミック・コンデンサの  $DF$  は室温において 0.1% ~ 2.5% です。電解コンデンサは通常大きな値を取ります。フィルム・コンデンサは最も良く、0.1%未満です。安定なセラミック・コンデンサ、特に C0G (あるいは NPO と呼ばれている。訳者注：C0G が一般的な呼び名になってきている) タイプのコンデンサの  $DF$  は、フィルム・コンデンサと同等かそれ以下の値です。

### ●誤差、温度とその他の影響

一般的に、高精度コンデンサは高価で入手が困難な場合もあります。実際に利用できるのは、限られた範囲の容量値と限られた誤差のコンデンサです。大容量コンデンサについて考えると、比較的性能のよいフィルム・コンデンサは  $10 \mu F$  以下に限られています (大きさと価格の制約がある)。容量誤差の小さなコンデンサは、C0G (NPO) セラミック・コンデンサとある種のフィルム・コンデンサで、 $\pm 1\%$  誤差のものが入手可能ですが、納期が長い場合があります。 $\pm 1\%$  の各種フィルム・コンデンサは一般に受注生産品です。

ほとんどのコンデンサは温度により特性が変化します。誘電体吸収や誘電体損失、容量値は温度とともに変化します。コンデンサの特性は温度とともに直線的に変化するものもありますが、非直線的に変化するものもあります。サンプル＆ホールド回路においてコンデンサ容量値の温度変化は一般に重要ではありませんが、極端に大きな温度係数  $TC$  (Temperature Coefficient, ppm/ $^{\circ}C$  で表される) は高精度積分器、V-F変換回路や発振回路の性能を劣化させます。C0G (NPO) セラミック・コンデンサは、 $TC$  が  $30 \text{ ppm}/^{\circ}C$  で最高の安定度を示します。ついでポリスチレンやポリプロピレン・コンデンサが  $100 \sim$

200 ppm/°Cと安定です。コンデンサの安定度が重要な場合、数百 ppm/°Cのコンデンサや温度係数が非直線的なコンデンサを選択してはいけません。

予想される環境条件から、コンデンサの最高動作温度を考慮する必要があります。たとえば、ポリスチレン・コンデンサは約 85 °Cで溶け始めますが、テフロン・コンデンサは 200 °Cでも動作します。

実際の回路において、誘電体吸収や容量値は印加電圧の影響を受け（電圧係数と呼ばれる）、コンデンサが要求性能を満たさなくなることがあります。コンデンサ・メーカーは必ずしも電圧係数を明確に定義していませんが、設計者は電圧係数の影響を考えなければなりません。たとえば、高誘電率系のセラミック・コンデンサに定格ぎりぎりの電圧を印加すると、容量値は半分以下になってしまいます。このことは歪みの発生を意味しますから、高誘電率系のセラミック・コンデンサをフィルタ回路などに用いることはできませんが、電源のバイパス・コンデンサであれば問題はありません。面白いことに C0G (NPO) タイプは同じセラミックのなかでも安定な誘電体で、低い電圧係数を備えています。

同じように、コンデンサの容量値や誘電体損失は、誘電率の周波数依存性により周波数とともに大きく変化します。ポリスチレン、ポリプロピレンやテフロンはこの特性が良い誘電体材料と言えます。

### ●重要な部品は最後に実装のこと

設計者の心配は回路設計が終了しても尽きません。最高のデザインをもってしても、プリント基板への実装時の問題がすべてをだめにしてしまうことがあります。たとえば、一般的に利用されているある洗浄液は電解コンデンサに浸透していきます（ゴムで蓋がしてあるタイプはとりわけ洗浄時に問題が起きやすい）。

さらに悪いことに、フィルム・コンデンサ（特にポリスチレン・コンデンサ）の種類によっては、洗浄液に触れると溶けてしまうこともあります。これ以外の種類のコンデンサであっても、リード線を粗雑に扱うと再現しにくい間欠的な故障を引き起こします。金属箔をエッキングしたタイプは、このような問題を引き起こしやすいといえます。問題を避けるために、できるならばこのような部品は最後に実装するのがよいでしょう。

表1-1 にいろいろなコンデンサの特徴をまとめ、おおよそ誘電体吸収特性の良い順に並べました。この表をまとめるにあたり、部品メーカーのカタログを参照しました（本章最後の参考文献を参考のこと）。

設計者はコンデンサの故障モードも考慮しなければなりません。たとえば、メタライズド・フィルム・コンデンサは自己修復性を備えています。最初に、絶縁膜の小さなピンホールにより電極間が短絡します。しかし、電極間に流れる電流が熱を発生し、短絡は融け去り、若干の容量の減少を伴いますが元の状態に復帰します。ただし、高インピーダンス

回路では十分な電流が流れないために短絡は溶融されず、故障は解消されません。

タンタル・コンデンサはフィルム・コンデンサとは様子が異なり、故障発生箇所の温度がゆっくりと上昇すると自己修復作用が認められます。したがって、タンタル・コンデン

〈表1-1〉各種コンデンサの比較

| タイプ                     | 代表的な DA      | 長 所                                                              | 短 所                                              |

|-------------------------|--------------|------------------------------------------------------------------|--------------------------------------------------|

| ポリスチレン                  | 0.001～0.02 % | 安価<br>DA 小<br>高安定度 (0～120 ppm/°C)                                | 温度により劣化 (> 85 °C)<br>大きい<br>インダクタンス大<br>ペンダが限られる |

| ポリプロピレン                 | 0.001～0.02 % | 価格は中程度<br>DA 小<br>安定 (0～200 ppm/°C)<br>広範囲の容量あり                  | 温度により劣化 (> 105 °C)<br>大きい<br>インダクタンス大            |

| テフロン                    | 0.003～0.02 % | 小 DA 品あり<br>高安定<br>動作温度範囲が広い (+125 °C以上)<br>広範囲の容量あり             | 高価<br>大きい<br>インダクタンス大                            |

| ポリカーボネート                | 0.1%         | 高安定<br>安価<br>動作温度範囲が広い<br>広範囲の容量あり                               | 大きい<br>DA は 8 ビット相当<br>インダクタンス大                  |

| ポリエステル                  | 0.3～0.5 %    | 安定度は中程度<br>安価<br>動作温度範囲が広い<br>インダクタンス小<br>(フィルムの積み重ね構造)          | 大きい<br>DA は 8 ビット相当<br>インダクタンス大 (通常品)            |

| セラミック (COG)             | 0.1 %以下      | 小型<br>安価、多数のペンダ<br>高安定 (30 ppm/°C)<br>1 %精度あり<br>インダクタンス小 (チップ品) | DA は一般的に小 (規格なし)<br>高容量はなし (10 nF 以下)            |

| モノリシック・セラミック<br>(高誘電率系) | 0.2 %以上      | インダクタンス小 (チップ品)<br>容量範囲大                                         | 不安定<br>DA 大<br>電圧係数大                             |

| マイカ                     | 0.003 %以上    | 高周波のロス小<br>インダクタンス小<br>高安定<br>1 %精度あり                            | 大きい<br>高容量はなし (10 nF 以下)<br>高価                   |

| アルミ電解                   | 極めて大         | 大容量<br>大電流<br>高耐圧<br>小型                                          | リーケージ電流大<br>一般的には有極性<br>安定度、精度ともに悪い<br>インダクタンス大  |

| タンタル                    | 極めて大         | 小型<br>大容量<br>中程度のインダクタンス                                         | リーケージ電流大<br>一般的には有極性<br>高価<br>安定度、精度ともに悪い        |

サでは故障部分に流れる電流が制限され、温度が徐々に上昇する高インピーダンス回路で自己修復性が高くなります。高電流回路でタンタル・コンデンサを利用するときは注意が必要です。

電解質を利用したコンデンサの寿命は、内部の電解質がケースの蓋から染み出る割合によって決まります。エポキシ封止はゴム封止より良い封止性を示しますが、逆電圧や過大電圧が印加されると破裂することがあります。有極性コンデンサは絶対最大定格を越える電圧印加から保護しなければなりません。

## 1-2 抵抗とポテンショメータ

抵抗は、ソリッド・カーボン抵抗、カーボン・フィルム抵抗、金属抵抗、金属箔抵抗、巻き線抵抗、無誘導巻き線抵抗など、きわめて豊富な種類が存在します。最も基本的でおそらく最もトラブルの少ない電子部品であるために、抵抗器が高精度回路の誤差要因となることを見過ごしがちです。

不適当な抵抗の選択は、12ビット・クラスのシステムにおいて122 ppm(1/2 LSB相当)を大きく越える誤差を発生します。あなたが最後に抵抗のカタログを読んだのはいつですか？ カタログ・データを再検討してみたら、きっと驚くに違いありません。

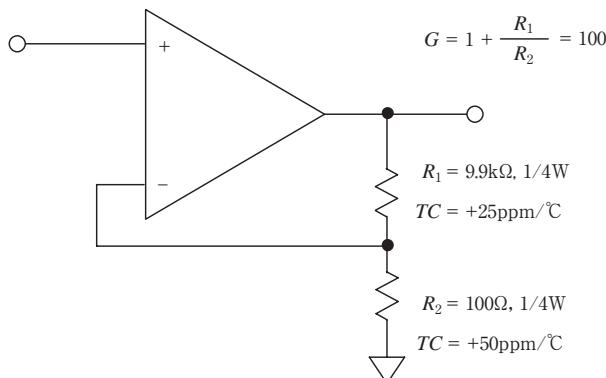

図1-4に示す、 $R_1$ と $R_2$ によってゲイン100に設定された非反転回路を考えてみましょう。この二つの抵抗の温度係数は明らかに誤差要因となります。OPアンプのエラーは無

〈図1-4〉抵抗の温度係数の差によって発生する回路のゲイン誤差

- 10 °Cの温度変化は250 ppmのゲイン誤差を発生する

- 250 ppmは12ビット・システムの1 LSBに相当し、16ビット・システムではさらに大きな誤差となる

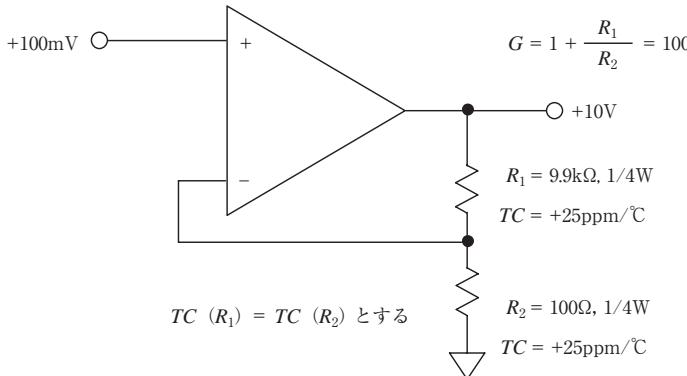

図1-5 理想的なTC特性を示す抵抗において発熱量の差に起因するゲイン誤差

$R_1$  および  $R_2$  の熱抵抗:  $125\text{ }^\circ\text{C/W}$

$P_D = 9.9\text{mW}$  で  $R_1$  の温度上昇は  $1.24\text{ }^\circ\text{C}$

$P_D = 0.1\text{mW}$  で  $R_2$  の温度上昇は無視できる程度

ゲイン変化は 31 ppm, すなわち 14 ビット・システムの 1/2 LSB 相当

見えるほど小さく、抵抗は  $25\text{ }^\circ\text{C}$ において 99 : 1 の比になっていたと仮定してみましょう。もし仮に抵抗の温度係数の差が  $25\text{ ppm}/^\circ\text{C}$  だったとしても、 $10\text{ }^\circ\text{C}$  の温度変化でアンプのゲインは  $250\text{ ppm}$  変化します。この値は 12 ビット・システムにおいておおよそ 1 LSB に相当し、16 ビット・システムにおいてはとんでもなく大きな誤差となります。温度変化はいくつかの点で図1-4 の增幅回路の精度を制限しています。この回路において抵抗の相対値が一致していれば(他の OP アンプの回路でもゲインは部品定数の比で決定される)，絶対値の温度係数はあまり重要ではありません。しかしそうであっても、いくつかの種類の抵抗は高精度回路に向きません。たとえば、ソリッド・カーボン抵抗は約  $1500\text{ ppm}/^\circ\text{C}$  の温度係数をもち、高精度回路には向ません。カーボン抵抗の相対誤差が、仮に 1% (ありえない話だが) であったとしても、 $15\text{ ppm}$  の相対温度係数は  $8\text{ }^\circ\text{C}$  の温度変化で  $120\text{ ppm}$  の誤差を発生します。

さまざまなメーカーから、絶対温度係数が  $\pm 1\text{ ppm} \sim \pm 100\text{ ppm}$  の金属皮膜抵抗や金属箔抵抗が発売されています。抵抗の  $TC$ 、特に異なる製造バッチから選ばれた抵抗の  $TC$  は大きな誤差要因となることに注意しましょう。この種のトラブルを避けるために、相対温度係数が  $2 \sim 10\text{ ppm}/^\circ\text{C}$  のペア抵抗を利用することができますが、高価です。また、集合金属皮膜抵抗は安価なうえ相対誤差が少ないためよく利用されています。

図1-5に示す回路の抵抗  $R_1, R_2$  が  $1/4\text{ W}$  抵抗で、温度係数がどちらもちょうど  $25\text{ ppm}/^\circ\text{C}$  であったと仮定してみましょう。ぴったり  $25\text{ ppm}/^\circ\text{C}$  の温度係数であっても大き

〈表 1-2〉 抵抗の温度誤差を最小にするために重要な点

- ・抵抗温度係数のマッチングを近くする

- ・絶対温度係数の小さな抵抗を利用する

- ・熱抵抗の小さな抵抗を利用する(大電力なら大きなものを使う)

- ・熱結合された抵抗を利用する(集合抵抗の利用)

- ・抵抗比が大きいときはステップ・アッテネータの採用を考慮する

な誤差が発生します。入力信号が 0 V のときは、抵抗で電力は消費されません。しかし、入力信号が 100 mV になると  $R_1$  の端子電圧は 9.9 V となり、9.9 mW の電力が消費されます。温度上昇は 1.24 °C になります(1/4 W 抵抗の 125 °C/W の熱抵抗による)。この 1.24 °C の温度上昇は 31 ppm の抵抗値の変化を発生し、同じだけ回路のゲインが変化します。しかし、 $R_2$  の端子電圧は 100 mV であり、0.0125 °C というほとんど無視できるような温度上昇しか発生しません。その結果として、31 ppm の総合ゲイン誤差は、14 ビット・システムにおいて 1/2 LSB のフルスケール誤差となり、16 ビット・システムではさらに大きな誤差となります。

さらに悪いことに、自己発熱の影響は(電圧の 2 乗に比例するため)非直線誤差を発生します。入力信号が図 1-5 の 1/2(50 mV)だとすると、自己発熱による誤差は 15 ppm となります。別の言いかたをすれば、フルスケール入力のときと 1/2 フルスケール入力のとき(あるいは他の値であっても)にゲインを決定する抵抗の自己発熱による温度変化が一致していなければ、回路のゲインは一定ではありません。これは特殊な例ではありません。外形の小さな抵抗は熱抵抗がさらに高く、その結果ゲインの変動はさらに大きくなります。

これらの誤差を最小にするためには、抵抗値と温度係数のよく一致した抵抗を熱的に結合させ、さらに電力軽減を十分に考慮することが重要です。IC 内部あるいは金属箔抵抗で、同一サブストレート上に形成された抵抗ネットワークが最適といえます。

抵抗値が小さい場合( $10\Omega$ 以下)、接続回路の安定度が重要になります。たとえば、銅線やプリント基板上のパターンの抵抗温度係数は見逃されがちです。銅の抵抗温度係数はおよそ  $3900 \text{ ppm}/\text{°C}$  です。 $10\Omega$ ,  $10 \text{ ppm}/\text{°C}$  の高精度巻き線抵抗と  $0.1\Omega$  の銅配線の直列回路は  $10.1\Omega$ ,  $50 \text{ ppm}/\text{°C}$  の抵抗となります。

最後に動作周囲温度の広い回路で考慮しなければならない、通電状態で高低温サイクルを実施すると抵抗値が変化するという温度再現性(temperature retrace)の問題があります。温度再現性は、抵抗値が安定な金属箔抵抗を利用しても 10 ppm を越えることがあります。

回路抵抗の温度係数に起因する誤差を最小にするためには、表 1-2 の各項目を部品コストとトレードオフしながら検討する必要があります。

## ●抵抗の寄生リアクタンス

抵抗には無視できない寄生インダクタンスと寄生キャパシタンスが存在し、特に高周波においてこの影響が顕著です。部品メーカは、この寄生リアクタンスの影響を直流抵抗と測定周波数におけるインピーダンスの比をとってパーセントや ppm で定義しています。

巻き線抵抗は寄生リアクタンスが大きい部品です。巻き線抵抗メーカは、通常の巻き線抵抗以外に無誘導巻き線抵抗を作っていますが、無誘導巻き線抵抗であっても、寄生リアクタンスは回路設計者を悩ませます。10 kΩ以下の無誘導巻き線抵抗は誘導性(20 μH 程度)です。10 kΩ以上の無誘導巻き線抵抗には5 pF 程度の並列容量が存在します。

これらの寄生リアクタンスは、回路の過渡応答に大きな影響を与えます。特に 10 kΩ以上の巻き線抵抗は大きく影響を受け、ピーキングや発振さえも起こしかねません。この現象は数 kHz 帯域の回路ではっきりと観察することができます。

もっと低い周波数においても、巻き線抵抗の寄生リアクタンスは問題を引き起こします。指数関数的にセトリングする回路では、最終値の 1 ppm に信号が静定するために時定数の 20 倍以上の時間を要することもあります。巻き線抵抗と寄生リアクタンスの時定数が、回路全体の時定数に無視できない影響を与えることもあります。

巻き線抵抗以外の抵抗であっても、リアクタンスが無視できないことがあります。たとえば、ある種の金属皮膜抵抗のリードがもつキャパシタンスは高周波において問題となります。カーボン抵抗は高周波において、端子間容量が比較的少ないといえます。

## ●熱電対効果

抵抗の熱電対効果 (thermocouple effect, thermal EMF) にも注意を払わなければなりません。異種金属の接合点があれば必ず熱起電力が発生します。第2巻の第5部 (原著では Chapter-4) で紹介しているように、熱電対効果は温度測定に利用されています。いかなる異種金属の接合も熱電対を構成するため、高精度 OP アンプ回路において熱電対効果は誤差要因となります。実際に、高精度回路においては熱起電力が最大の誤差要因となっている場合があります。

寄生熱電対を形成する多くの接続間に温度差が生じると、誤差が生じます。熱電対の定義から、回路の入力端に二つの接続点があれば、少なくとも一つの熱電対が構成されます。この二つの接続点が異なる温度であれば、温度依存性をもった電圧が発生します。別の見かたをすれば、二つの接続点の温度がまったく同一であれば熱起電力はキャンセルされてゼロとなります。

回路を形成するとき異種金属の接合点は避けることができません。しかし、回路全体を等温化すれば、熱電対効果をキャンセルすることができます。

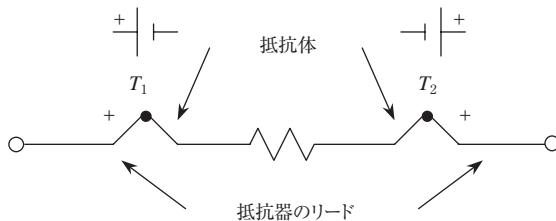

寄生熱電対効果を避けることは非常に困難です。このことを理解するために、たとえば

図 1-6 すべての抵抗に存在する抵抗体とリード線で構成された 2 組の熱電対

#### 代表的な抵抗の熱起電圧

- ・ 固体カーボン抵抗 :  $400 \mu\text{V}/^\circ\text{C}$

- ・ 金属皮膜抵抗 :  $20 \mu\text{V}/^\circ\text{C}$

- ・ EVENOHM, あるいはマンガニン巻き線抵抗 :  $2 \mu\text{V}/^\circ\text{C}$

- ・ RCD Component HP シリーズ :  $0.05 \mu\text{V}/^\circ\text{C}$

銅の接続点を考えてみましょう。銅の合金同士の接続点であっても、 $1 \mu\text{V}/^\circ\text{C}$ 程度の熱起電力が発生することがあります。ほかの部品に目を向けると、抵抗のような一般的な部品であってもさらに大きな熱起電力は発生します。

図 1-6 に示す抵抗のモデルを考えてみましょう。抵抗両端の抵抗体とリード線の接続は熱電対接続  $T_1, T_2$  を形成します。この熱電対の起電力はカーボン抵抗で  $400 \mu\text{V}/^\circ\text{C}$  にも達し、特別な抵抗 [文献 (15) 参照] を利用した場合は  $0.05 \mu\text{V}/^\circ\text{C}$  です。通常の金属皮膜抵抗 (RN タイプ) は約  $20 \mu\text{V}/^\circ\text{C}$  です。

この熱電対効果は AC 信号には大きな影響を与えません。DC 信号であっても、すでに述べたように抵抗が一様な温度であれば抵抗の両端で発生する熱起電圧はキャンセルされます。しかしながら、抵抗の消費電力が大きかったり、あるいは熱源に対して非対称に配置された抵抗は熱起電力による誤差を発生します。一般的な金属皮膜抵抗の両端温度差が  $1^\circ\text{C}$  あれば、熱起電力は  $20 \mu\text{V}$  です。この誤差は OP177 のような高精度 OP アンプのオフセット電圧ドリフトと比較して大きな値であると言え、さらにオフセット電圧ドリフトが  $1 \mu\text{V}/^\circ\text{C}$  以下のチョッパ・スタビライズド・アンプと比較するときわめて影響が大きいといえます。

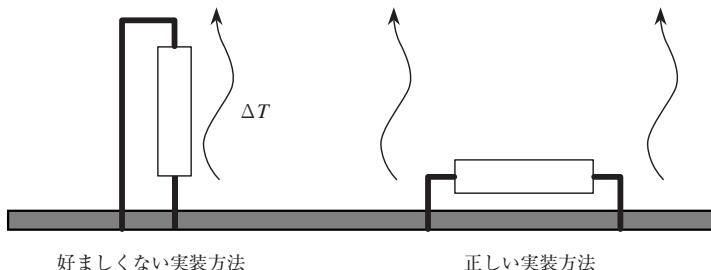

図 1-7 に、抵抗の実装方法による熱起電力の違いを示します。基板面積を減らすために、左図に示したように抵抗を立てて配置すると温度勾配が発生します。特に消費電力が大きいと、この温度勾配はさらに大きくなります。一方、右図に示すように抵抗を基板に寝かせて取り付ければ、温度勾配の発生を避けることができます。しかしながら、抵抗に沿って風の流れが発生すると温度勾配が生じます。このような場合、風の流れに垂直に抵抗を配置すると、風が抵抗両端を等温化するために熱起電力による誤差を最小にすることができます。

図1-7 熱起電圧を最小化するために適正に配置され、等温化された抵抗

きます。

上述の内容は、垂直に配置されたプリント基板に実装された抵抗にも適用できます。このような場合、通常はプリント基板の下から上へ空気は流れます。抵抗を対流と垂直に配置すれば、熱電効果による誤差を最小にすることができます。小さな表面実装抵抗を利用すると抵抗両端の熱結合が密になるため、熱電効果の誤差を少なくすることができます。

一般的に、高感度回路では温度勾配が発生しないようにしなければなりません。そのためには、熱源を高感度回路から分離することが重要です。大きな温度分布の変化は低周波におけるノイズのような誤差を発生します。

### ●電圧感度、不良発生の仕組みとエージング効果

抵抗は印加電圧によって値が変化します。特に数  $M\Omega$  の酸化金属皮膜抵抗は電圧係数が大きく、 $1 \text{ ppm/V} \sim 200 \text{ ppm/V}$  を示します。このことは、高電圧分圧器のような高精度用途において注意しなければなりません。

抵抗の一般的な不良発生の仕組みを事前に十分検討しておく必要があります。たとえば、ソリッド・カーボン抵抗は開放モードで故障します。したがって、ある種の用途ではソリッド・カーボン抵抗に第2の機能としてヒューズの機能をもたせることもできます。このような抵抗をカーボン・フィルム抵抗で置き換えると、短絡モードで故障するために問題が発生します（金属皮膜抵抗も通常是開放モードで故障する）。

すべての抵抗は使用年数にしたがって抵抗値が変化します。抵抗の製造メーカーは長期安定度を  $\text{ppm/年}$  で規定しています。金属皮膜抵抗であっても、 $50 \sim 75 \text{ ppm/年}$  という値は達成が困難な値です。高感度回路では、金属皮膜抵抗を実負荷で最低1週間以上動作させるべきです（一般にバーンインと呼ぶ）。この間、抵抗値は  $100 \sim 200 \text{ ppm}$  ほど変化するでしょう。金属皮膜抵抗を完全に枯らすためには、4000～5000時間の動作時間が必要となります。

## ●抵抗の発生するノイズ

ほとんどの方は、抵抗のジョンソン・ノイズ(熱雑音)についてご存知のことと思います。しかしながら、抵抗が発生するエクセス・ノイズ(過剰雑音)についてはあまり知られていません。高精度OPアンプやデータ・コンバータ回路において、問題となる抵抗に電流が流れたときだけ発生する現象です。ここで簡単に復習すると、熱雑音は抵抗中の電子のランダムな動きが発生するノイズです。電子のランダムな動きによる電流の平均値は0[A]ですが、電子の動きにより端子間に瞬時電圧が発生します。

一方、エクセス・ノイズは、たとえばソリッド・カーボン抵抗の小さな導体にDC電流が不連続に流れたときに発生します。ソリッド・カーボン抵抗の粒子に不均一に流れる電流が、微小粒子の動きを引き起こします。この現象が熱雑音に加えて $1/f$ ノイズを増加させます。別の言葉でいうと、エクセス・ノイズは周波数の平方根に反比例します。

不注意な回路設計者はエクセス・ノイズに驚くでしょう。通常、抵抗の熱雑音とOPアンプの入力ノイズでOPアンプ回路のノイズ・フロアが決定されます。しかし、入力抵抗に電圧が印加され、電流が流れたときにだけエクセス・ノイズが現れ、しかもしばしば最も支配的な値を取るからです。一般的に、ソリッド・カーボン抵抗がもっとも多くエクセス・ノイズを発生します。抵抗体がより均一になるとエクセス・ノイズは減少します。炭素皮膜抵抗や金属皮膜抵抗は特性がよく、巻き線抵抗やバルク・メタル抵抗がこれに続きます。

製造会社は、ノイズ指標を抵抗両端電圧あたりの $\mu\text{V}_{\text{RMS}}$ として10倍の周波数帯域(decade)ごとに規定しています。ノイズ指標は10 dB( $3 \mu\text{V}/\text{V}/\text{decade}$ )以上増加することがあります。100 kHz以上では熱雑音が優勢ですが、低周波領域ではエクセス・ノイズが支配的です。

## ●半固定抵抗

固定抵抗で発生するほとんどの問題は半固定抵抗でも発生します。さらに、半固定抵抗固有の問題に注意を払わなければなりません。

たとえば、多くの半固定抵抗は開放型なので、基板の洗浄剤や高湿度環境で劣化します。振動や手荒な扱いで抵抗体や摺動子が劣化することもあります。半固定抵抗を利用すると、摺動ノイズ、温度係数、寄生回路や調整レンジが問題となることがあります。さらに、巻き線型半固定抵抗の分解能、サーメット・トリマやプラスチック・トリマ抵抗の分解能を制限する要因(ヒステリシス、温度係数の違い、回転の遊び)で設定分解能や設定安定度が制限されます。これらの問題点を避けるために、半固定抵抗を利用するときは次の二つのことに注意しましょう。

**【ルール1】**手動調整の半固定抵抗を利用するときは最大限の注意を払い、調整レンジは最小にする。

**[ルール2]** 手動調整の半固定抵抗はできるだけ利用しない。半固定抵抗と同等の機能をもつ調整用D-Aコンバータの利用を考える〔文献(17)参照〕。

さらに、回路調整用に設計された安価な電圧出力D-Aコンバータを使用することもできます。

表1-3に固定抵抗と集合抵抗の特性を要約しておきます。実際に抵抗器を選択するときは、各ベンダが提供する情報を参照してください(参考文献を参照のこと)。

〈表1-3〉各種抵抗器の比較

|         | タイプ                    | 長所                                                                                                                  | 短所                                                                  |

|---------|------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| ディスクリート | ソリッド・カーボン              | 安価<br>高電力/小型<br>抵抗範囲が大きい                                                                                            | 精度が低い(5%)<br>温度係数が大きい<br>(1500 ppm/°C)                              |

|         | 巻き線抵抗                  | 高精度(0.01%)<br>温度係数良(1 ppm/°C)<br>大電力                                                                                | リアクタンス大<br>大きい<br>もっとも高価                                            |

|         | 金属皮膜                   | 高精度(0.1%)<br>温度係数良(1 ~ 100 ppm/°C)<br>中程度の価格<br>抵抗範囲が大きい<br>電圧係数が低い                                                 | 安定化のためにはバーンインが必要<br>許容電力が小さい                                        |

|         | バルク・メタル<br>あるいは<br>金属箔 | 高精度(0.005%)<br>温度係数良(1 ppm/°C以下あり)<br>リアクタンス小<br>電圧係数が低い                                                            | 許容電力が小さい<br>極めて高価                                                   |

|         | ハイ・メガオーム               | 高抵抗( $10^8 \sim 10^{14}$ )<br>特定回路においてほかに選択肢なし                                                                      | 大きい電圧係数(200 ppm/V)<br>壊れやすいガラス・ケース<br>取り扱い注意<br>高価                  |

| 集合抵抗    | 厚膜                     | 安価<br>高電力<br>レーザ・トリムが可能<br>入手性良                                                                                     | 中程度の相対精度(0.1%)<br>TC悪い(100 ppm/°C以上)<br>温度係数マッチングが悪い<br>(10 ppm/°C) |

|         | 薄膜                     | 相対精度良(0.01%以下)<br>温度係数良(100 ppm/°C以下)<br>温度係数トラッキングが良い<br>(2 ppm/°C)<br>価格は中程度<br>レーザ・トリムが可能<br>静電容量小<br>ハイブリッドで利用可 | 外形が大きい<br>抵抗値と抵抗の組み合わせに制限あり                                         |

## 1-3 インダクタンス

### ●ストレイ・インダクタンス(浮遊インダクタンス)

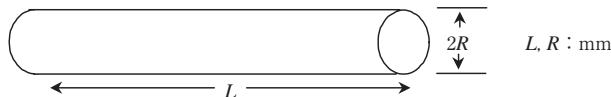

すべての導体はインダクタンスをもちます。きわめて短い配線やプリント基板の配線も高周波では重要です。自由空間に置いた、長さ  $L$  [mm]、断面の半径  $R$  [mm] の配線がもつインダクタンスを表す式を図1-8に示します。

自由空間中の幅  $W$  [mm]、厚さ  $H$  [mm] のストリップ・ライン(プリント基板上のパターンを想定)のインダクタンスを表す式も同様に図1-8に示します。

これらの式を用いれば、実際の回路でどの程度のインダクタンスとなるか概算値を得ることができます。この式によれば、長さ 1 cm、直径 0.5 mm の配線は 7.26 nH のインダクタンスであり、長さ 1 cm、幅 0.25 mm のプリント基板のパターンは 9.59 nH です。これらの値は実際の測定値と十分に近い値です。

10 MHzにおいて、7.26 nH のインダクタンスは  $0.46\Omega$  のインピーダンスとなり、 $50\Omega$  の回路で 1 % の誤差を発生します。

〈図1-8〉線材とストリップ回路のインダクタンスの計算

$$\text{線材のインダクタンス} = 0.0002L \left[ \ln\left(\frac{2L}{R}\right) - 0.75 \right] \mu\text{H}$$

例：長さ1cm、直径0.5mmの線材のインダクタンスは7.26nH

( $2R = 0.5\text{mm}$ ,  $L = 1\text{cm}$ )

$$\text{ストリップ・ラインのインダクタンス} = 0.0002L \left[ \ln\left(\frac{2L}{W+H}\right) + 0.2235 \left( \frac{W+H}{L} \right) + 0.5 \right] \mu\text{H}$$

例：長さ1cm、幅0.25mmのパターンのインダクタンスは9.59nH

( $H = 0.038\text{mm}$ ,  $W = 0.25\text{mm}$ ,  $L = 1\text{cm}$ )

## ●相互インダクタンス

もうひとつの注意すべきインダクタンスは、流れ出る電流と流れ込む電流が形成する閉回路のインダクタンスです。

詳細を後で述べますが、キルヒ霍ッフの法則によれば流れ出る電流があれば必ず流れ込む電流があり、閉回路を形成します。この回路は1回巻きのインダクタを形成します。

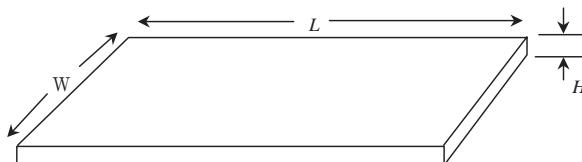

図1-9に、この原理を実際のパターンで例示します。閉回路で囲まれた部分が広ければ(上の図に示した理想的でないプリント基板のパターン)，インダクタンス(AC信号インピーダンス)は大きくなります。一方、下の図(改善されたプリント基板のパターン)に示すように電流が流れ出る配線と流れ込む配線が近ければ、インダクタンスは小さくなります。

図1-9に示す理想的でないプリント基板パターンは、このほかにも欠点があります。導体で囲まれた閉回路は大きな磁気回路を形成し、誘導性の結合でほかの回路に不要な信号を伝達します。同様に、大きな閉回路は外部磁界の影響で内部に不要な信号を発生します。

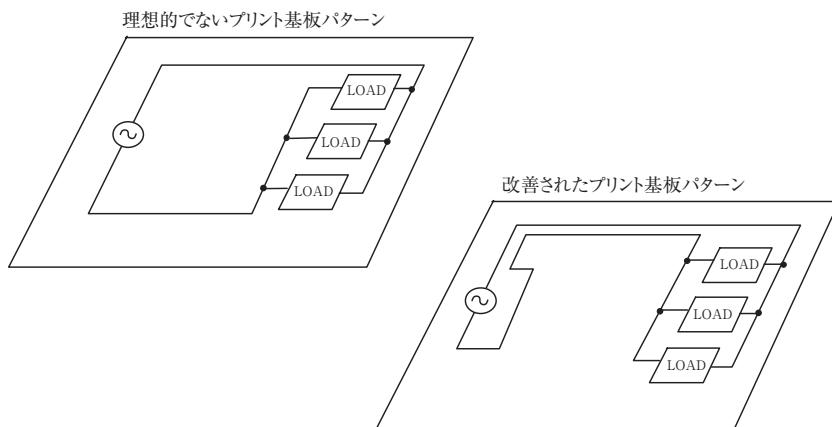

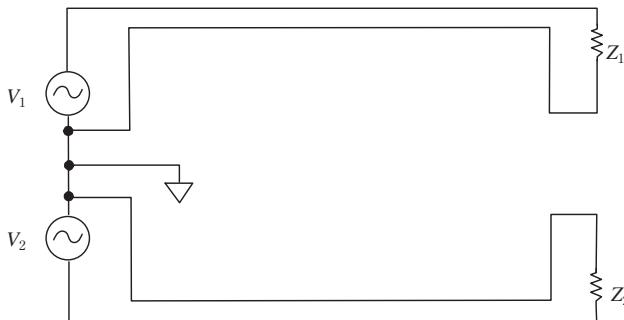

図1-10に、二つの閉回路で形成されたトランスによる不用信号(ノイズ)の発生原理を示します。

そのほかのノイズ源と同様に、発生原理が明確になればその対策を考えることができます。この場合、図1-10に示した式の各項を小さくすれば結合を減らすことができます。電流の値や周波数を減少させることはできないでしょうから、回路の距離を離したり、どちらか一方あるいは両方の閉回路の面積を減らし、相互インダクタンスを減少させます。

〈図1-9〉理想的でないプリント基板パターンと改善されたプリント基板パターン

図 1-10 誘導性結合の基本原理

図 1-11 誘導性結合を減少させる信号配置とレイアウト

レイアウトの変更例を図 1-11 に示します。 $Z_1$ ,  $Z_2$  の負荷をもつ閉回路のそれぞれの面積を可能な限り小さくします。

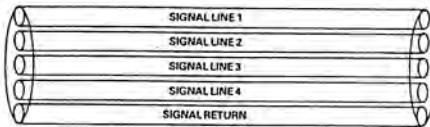

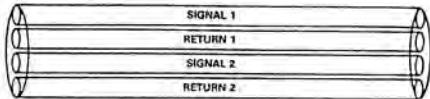

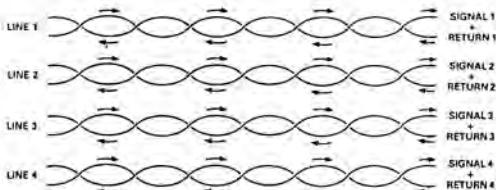

図 1-12 に示すように、相互インダクタンスはケーブルで信号を伝送するときも問題となります。リボン・ケーブルの相互インダクタンスは大きく、特に複数の信号のグラウンド線を共通にしたときに大きくなります(上図)。それぞれの信号に専用のグラウンド線を用いると改善することができます(真中の図)。一番下の図に示すように、ツイスト・ペア線をそれぞれの信号に利用するとさらに改善されます(しかしながらツイスト・ペア

〈図1-12〉信号ケーブルの相互インダクタンスによる結合

单一グラウンド線をもつフラット・ケーブルは相互インダクタンスが大きい

交互に配置された信号線とグラウンド線は相互インダクタンスが減少する

ツイスト・ペア線はさらに相互インダクタンスが小さい

線は必ずしも必要ではなく、また高価です).

相互インダクタンスを減少させるために磁気シールドを利用することもありますが、静電シールド(ファラデー・シールドとも言う、次章で述べる)ほど簡単ではありません。密閉した導体(静電シールドは小さな穴があってもよいが磁気シールドでは問題となる)は、高周波の磁気を遮断することができます。このときに必要な導体の厚さは遮断しようとする信号周波数の表皮効果で決定されるため、高周波であればそれほど厚い導体は必要ありません。低周波や直流信号はミューメタル(パーマロイ)で遮断することができます。ミューメタルは高価な高透磁率の合金です。機械的なストレスで性能が劣化し、また高磁界中で飽和し、機能を果たさなくなります。ですから、できれば利用を避け、最後の手段とすべきです。

## ●リングング

インダクタンスと直列あるいは並列にコンデンサを接続すると、共振回路(同調回路)が形成されます。共振回路は、共振周波数近傍の狭い周波数領域でインピーダンスが大きく変化します。共振の鋭さは共振回路のQ値で表されます。共振現象は狭帯域回路の周波数特性を決定するために広く利用されていますが、一方で問題を引き起こすこともあります。

ストレイン・インダクタンスとコンデンサ(浮遊容量の場合もそうでない場合もあるが)

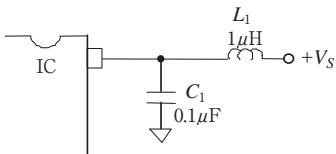

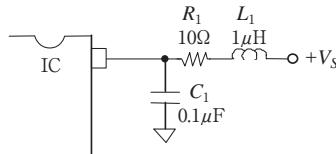

図 1-13 電源のデカップリング回路に形成される共振回路

電源のデカップリング回路の等価回路が示す共振周波数  $f$

$$f = \frac{1}{2\pi\sqrt{LC}}$$

IC 近傍に小さな直列抵抗を入れて  $Q$  を減少させる

が共振回路を形成し、回路中の信号で駆動されると共振周波数でリンギング (ringing) を発生します。

図 1-13 の例では、電源ラインのデカップリング・コンデンサとインダクタンスが共振回路を形成し、IC のパルス状の電源電流で駆動されています。

配線のインダクタンスと  $0.01 \mu\text{F} \sim 0.1 \mu\text{F}$  の一般的なデカップリング・コンデンサは、数 MHz の共振回路を形成します。たとえば、 $0.1 \mu\text{F}$  のコンデンサと  $1 \mu\text{H}$  のインダクタンスの共振周波数は  $500 \text{ kHz}$  です。図 1-13 の左側の回路では共振の問題が発生します。電源配線の共振が引き起こす問題は、回路の  $Q$  を低下させることで影響を軽減することができます。いちばん簡単な方法は図 1-13 の右側に示すように、IC の電源ピンの直近に小さな抵抗 ( $10 \Omega$  以下) を入れることです。

### ●インダクタンスの寄生効果

インダクタンスは電子回路の基本的な素子であるにもかかわらず、抵抗やコンデンサと比べるとあまり利用されません。特に高精度のインダクタンスの利用は稀です。インダクタは抵抗やコンデンサと比較すると製造が難しく、安定度が劣り、そして機械的に弱いためです。数 nH から数 mH 程度の安定なインダクタは比較的製造が容易ですが、数 mH を越えるインダクタは特性が不安定で、形状が大きくなってしまいます。

このような理由から、高精度インダクタができるだけ利用せずに回路設計を行います。高周波狭帯域回路の共振回路を除き、アナログ回路で高精度高安定インダクタは利用されません。もちろん、電源フィルタやスイッチング電源など、精度の要求されない回路では一般的に利用されています。

電源フィルタやスイッチング電源で利用されるインダクタの重要な特性は、最大電流と飽和特性、そして  $Q$  値です。本来、空芯コイルのインダクタンスは流れる電流とは無関

〈表1-4〉インダクタのQ値

$$\cdot Q = \frac{2\pi f L}{R}$$

- ・共振回路あるいはインダクタンスのQはリアクタンスと抵抗成分の比で規定される

- ・直流抵抗ではなく高周波数で測定した抵抗分

- ・単共振回路の3dB帯域は中心周波数 $f_c$ に対し $f_c/Q$ で決定される

係で一定です。一方、磁性体（鉄芯やフェライト）に巻かれたコイルは大電流を流すとインダクタンスは非直線的に変化し、飽和特性を示します。このようにインダクタンスが飽和特性を示すと回路の効率は低下し、ノイズや高調波歪みが発生します。

すでに述べたように、インダクタンスにコンデンサが接続されると共振回路が形成されます。すべてのインダクタは浮遊容量があるために自己共振周波数（通常データシートに記載されている）があり、高精度インダクタとして利用するためには、使用する周波数と比較して十分に高い自己共振周波数のインダクタを選択しなければなりません。

### ● Q(クオリティ・ファクタ)

インダクタンスのQ値も重要な特性です。Q値は表1-4に示すように、リアクタンスと抵抗の比で表されます。

高い周波数では表皮効果（磁性体コアを利用した場合はコアのロスがさらに加わる）により、直流で測定した抵抗値から計算したQ値よりも実際のQ値は必ず小さくなります。ほとんどの場合、直流抵抗からQ値を計算することはできません。

Q値は共振回路の特性も示します（コンデンサのQ値も存在するが、十分に高い値を示すため普通は無視される）。共振回路のQ値は、その回路で使われているコイルのQ値とほぼ同じ値を取り（抵抗を利用して積極的にQを下げている場合を除く）、共振点付近のバンド幅から計算することができます。LC同調回路のQ値は大体100以下（3dBバンド幅は共振周波数の1%）ですが、セラミック振動子は1000程度、水晶振動子は10000程度の値です。

## 1-4 細かなことも見逃してはいけない

OPアンプやデータ・コンバータを利用して設計した回路が要求仕様を満たさないとき、誤差の要因を見過ごさないようにしましょう。能動素子だけでなく、受動素子を解析し、不適当な仮定や思い込みがないか考えてみましょう。

たとえば、固定されていないケーブルが動き回ると静電荷を発生し、特に高インピーダンス回路では誤差の原因となります。ケーブルを固定するか、あるいは高価なローノイズ・テフロン・ケーブルを利用すれば、この問題を解決することができます。

高精度高速OPアンプが利用できるようになり、システムの動作速度や精度の向上が要求されるようになりました。そのためには、本章で述べた（また、この後の章で述べる）誤差要因を完全に理解することが大切です。

この後に述べる電源回路フィルタで利用する受動素子に関する解説は本章を補完するものです。また、次章で述べるプリント基板のレイアウト・デザインも本章の内容を補完します。EMI/RFIの章もあわせて参照してください。

#### ◆参考文献◆

- (1) James E. Buchanan, "Dielectric Absorption. It Can Be a Real Problem In Timing Circuits", EDN, January 20, 1977, p.83.

- (2) Lew Counts and Scott Wurcer, "Instrumentation Amplifier Nears Input Noise Floor", Electronic Design, June 10, 1982.

- (3) W. Doeling, W. Mark, T. Tadewald, and P. Reichenbacher, "Getting Rid of Hook: The Hidden PC-Board Capacitance", Electronics, October 12, 1978, pp.111 ~ 117.

- (4) Carlton Fleming, "Data-Acquisition System (DAS) Design Considerations", WESCON '81 Professional Program Session Record No. 23.

- (5) Walter G. Jung and Richard Marsh, "Picking Capacitors, Parts I and II", Audio, February and March, 1980.

- (6) Robert A. Pease, "Understand Capacitor Soakage to Optimize Analog Systems", EDN, October 13, 1982, p.125.

- (7) Andy Rappaport, "Capacitors", EDN, October 13, 1982, p.105.

- (8) Specification MIL-PRF-19978G, Capacitors, Fixed, Plastic (or Paper-Plastic) Dielectric (Hermetically Sealed in Metal, Ceramic or Glass Cases), Established and Non-Established Reliability General Specification for, May 27, 1999.

- (9) Specification MIL-PRF-123B, Capacitors, Fixed, Ceramic Dielectric, (Temperature Stable and General Purpose), High Reliability, General Specification for, August 6, 1990.

- (10) Tantalum and Ceramic Surface Mount Capacitor Catalog, Kemet Electronics Corporation, P.O. Box 5928, Greenville, SC, 29606, 864-963-6300.

- (11) A general capacitor information resource, <http://www.faradnet.com/>

- (12) Southern and F-Dyne film capacitors, Southern Electronics, 215 Research Drive, Milford, CT, 06460, 203-876-7488.

- (13) Wesco film capacitors, Wesco Electrical Company, 201 Munson Street, Greenfield, MA, 01301, 413-774-4358.

- (14) Doug Grant and Scott Wurcer, "Avoiding Passive Component Pitfalls", The Best of Analog Dialogue, Analog Devices, 1991, pp.143-148.

- (15) RCD Components, Inc., 520 E. Industrial Park Drive, Manchester NH, 03109, 603-669-0054, <http://www.rcd-comp.com>

- (16) Steve Sockolov and James Wong, "High-Accuracy Analog Needs More Than Op Amps",

Electronic Design, October 1, 1992, p.53.

(17) Selection guide for digital potentiometers, [http://www.analog.com/support/standard\\_linear/selection\\_guides/dig\\_pot.pdf](http://www.analog.com/support/standard_linear/selection_guides/dig_pot.pdf)

(18) Precision Resistor Co., Inc., 10601 75th St. N., Largo, FL, 33777-1427, 727 541-5771, <http://www.precisionresistor.com>

(19) Ohmite Victoreen MAXI-MOX Resistors, 3601 Howard Street, Skokie, IL 60076, 847-675-2600, <http://www.ohmite.com/victoreen/>.

(20) Vishay/Dale Resistors, 2300 Riverside Blvd., Norfolk, NE, 68701-2242, 402 371-0800, <http://www.vishay.com>

(21) Beyschlag Resistor Products, PO Box 1220, D-25732 Heide, Germany, <http://www.beyschlag.com>

(22) B. I. & B. Bleaney, Electricity & Magnetism, Oxford at the Clarendon Press, 1957, pp.23, 24, 52.

(23) Henry W. Ott, Noise Reduction Techniques in Electronic Systems, 2nd Edition, John Wiley, Inc., 1988, ISBN : 0-471-85068-3.

(24) G. W. A. Dummer, Materials for Conductive and Resistive Functions, Hayden, 1970.

#### 謝辞：

本章と次章の一部分は, Doug Grant 氏と Scott Wurcer 氏による"Avoiding Passive Component Pitfalls" (Analog Dialogue 17-2, 1983 年) から引用させていただきました。

## 第2章

# プリント基板設計の諸問題

James Bryant／訳：細田裕司

プリント回路基板は、現代の電子回路を組み立てるうえで最も一般的な方法です。プリント回路基板は、1層または複数層の銅箔による導電パターンと、絶縁層がサンドイッチのように積層された構造をもちますが、そのことでさまざまな誤差要因が回路に入り込む可能性があります。とりわけ、回路の動作が高精度や高速な場合に影響が顕著になります。高精度回路において、プリント基板は目に見えない部品としてふるまうからです。設計者が常にプリント基板の電気的特性を回路の余分な構成要素として考えているわけではないので、えてして全体の性能は期待したレベルに届かないことになります。この章では、この一般的な話題が明確になるよう、さまざまな切り口で説明することにします。

精密な回路の性能に対するプリント基板からの悪影響には、リーケージ抵抗、銅箔パターンやビア<sup>\*1</sup>、グラウンド面における意図しない電圧降下、浮遊容量や誘電吸収(dielectric absorption；DA)などに関連するものがあります。加えて、基板が水分を吸収しやすい傾向、つまり吸湿性は、しばしば日々の湿度変化により、回路が影響を受ける度合いが変化する原因となります。

一般的に、プリント基板の影響は大きく二つに分類できます。それらは、回路の静的な、すなわち直流動作に顕著に影響するものと、動的な、すなわち交流動作に顕著なもので

基板設計は非常に多岐にわたる話題ですが、そのなかにグラウンド処理の問題があります。グラウンド処理は、すべてのアナログ回路設計にとって、それ自体が重要な問題であり、回路を基板化することでその事実が変わるわけではありません。幸いにも、高品質なグラウンド処理に関する原則、たとえばグラウンド・プレーンの使用は、プリント基板では容易に実現できます。これはアナログ回路を基板化する重要な利点の一つであり、この

\* 1 : 【訳注】ビア(via)は、回路基板において、異なる層間の電気的接続を取るために設ける導電めっきした小口径の穴のこと。ビア・ホール。

章のかなりの部分は、この問題についての解説に費やされています。

きちんとした管理が必要なグラウンド処理関係のこのほかの問題として、回路性能を劣化させかねないグラウンドと信号帰路に発生する不要電圧の制御があります。これらの電圧の発生原因には、外部信号の結合や共通電位を流れる電流、あるいは単純なグラウンドでの過大な抵抗性電圧降下といったものがあります。適切な導体パターンの引き回し寸法の選択と並んで、信号の差動処理やグラウンド分離といったテクニックを使うことで、それらの不要電圧を制御することが可能になります。

グラウンド処理で考慮すべき最後の領域には、ミックスト・シグナル、つまりアナログ/ディジタル混在環境における適切なグラウンド処理があります。これは、本書が全体として特に重要視しているポイントではありませんが、A-DコンバータやD-Aコンバータとのインターフェースは、OPアンプの主たる用途の一つであることは事実ですので、見逃すわけにはいきません。実際に、高品位のグラウンド処理の問題が、高性能なアナログ/ディジタル混在基板のレイアウト設計の方針を左右することがありますし、本来そういうものなのです。

## 2-1 導体の抵抗

第1章で幅広く述べられたように、抵抗器の特質について熟知したエンジニアは数少ないのですが、その小さな円筒型にワイヤや端子のついた抵抗器はごく身近な部品です。しかし、実際のシステムや回路を構成する、すべてのワイヤと基板のパターン(トレース)もまた抵抗であることを理解しているエンジニアの数はさらに少なくなります。より高精度なシステムでは、それらの基板のパターンや配線の抵抗分でさえ性能に悪影響を及ぼすことがあります。銅は決して超電導体ではありませんが、多くのエンジニアはそう考えているかのようです。

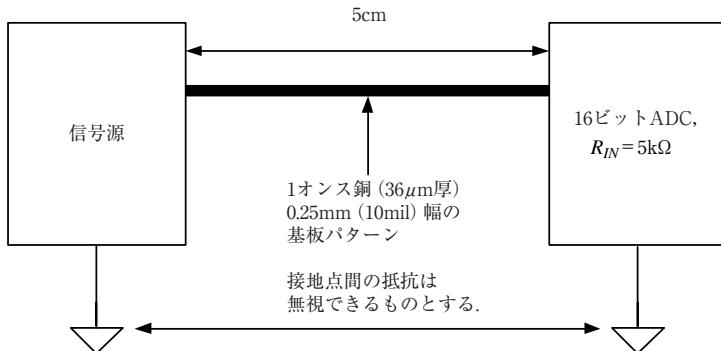

図2-1は、長さ $Z$ 、幅 $X$ 、厚み $Y$ の銅の直方体のシート抵抗 $R$ を計算する方法を示しています\*2。

25°Cにおいて、純銅の抵抗率は $1.724 \times 10^{-6} \Omega\text{cm}$ になります。標準的な1オンス(約31g)の基板銅箔の厚みは、0.036mm(0.0014inch)となります。ここで示された関係式を使うと、そのような銅の導体の抵抗は $0.48 \text{ m}\Omega/\square$ となります。この導体の端と端をつないで必要な長さにすれば、簡単に直線パターンの抵抗が計算できます。直線の長さが $Z$ 、幅が $X$ である場合、図に示したように、直線の抵抗 $R$ は、 $Z/X$ と□当たりの導体の抵抗

\*2：【訳注】ここでは $36 \mu\text{m}$ を標準的な銅箔厚としているが、個々のケースで確認が必要。なお、現実の基板では、ベースとなる銅箔はさらに層数の構成に応じてめっきをかけられて、最終の厚さが決まる。

〈図 2-1〉標準的な基板銅箔のシート抵抗と線分抵抗の計算

$$R = \frac{\rho Z}{XY}$$

$\rho$  = 抵抗率

1オンス銅 (36  $\mu\text{m}$ 厚) の銅箔のシート抵抗の計算

$$\rho = 1.724 \times 10^{-6} \Omega\text{cm}, Y = 0.0036 \text{cm}$$

$$R = 0.48 \frac{Z}{X} \text{m}\Omega$$

$$\frac{Z}{X} = \text{正方形の数}$$

$$R = \text{正方形1個あたりのシート抵抗 } (Z=X) \\ = 0.48 \text{m}\Omega / \square$$

を単純に掛け合わせたものになります。

与えられた銅の質量とパターン幅に対して、単位長さ当たりの抵抗値が計算できます。たとえば、0.25 mm (10 mil) 幅のパターンは基板設計でよく使用されますが、単位長さ当たりの抵抗値は約 19 m $\Omega$ /cm (48 m $\Omega$ /inch) に相当し、実に大きいものといえます。さらに、銅の抵抗の温度係数は、室温付近で 1°C当たり約 0.4 %です。これは、特に低インピーダンスの高精度回路では温度変化で正味のインピーダンスが変動することになり、無視してはならない要素となります。

図 2-2 に示すように、条件によっては、基板パターンの抵抗が重大な誤差となる場合があります。1 オンス銅箔の幅 0.25 mm、長さ 5 cm のパターンで信号源から駆動される、入力抵抗 5 k $\Omega$  の 16 ビット A-D コンバータを考えてみましょう。0.1  $\Omega$  近くになるパターンの抵抗は、5 k $\Omega$  の負荷と分圧器を構成することになり、誤差が生じます。結果として発生する電圧降下は、0.1/5 k (約 0.0019 %) のゲイン誤差となり、これは A-D コンバータの 1 LSB (16 ビットでは 0.0015 %) を優に越えてしまいます。

というわけで、高精度な回路を扱う場合には、プリント基板の導体抵抗のような単純な設計要素さえ、慎重に取り扱うことが重要です。この問題に対処する方法は、いろいろあります。パターン幅をより広くすること(余分なスペースを使う)、銅箔をより厚くする

図 2-2 オームの法則から基板導体での電圧降下により 1 LSB を越える誤差が予想される

こと（コストが高くなる）、あるいは単純に高入力インピーダンスの A-D コンバータを用いる手もあります。しかしながら、一番大事なことは、一見無害そうな事柄でも見落とさずに注意を払い、すべてを熟慮した設計を行うことです。

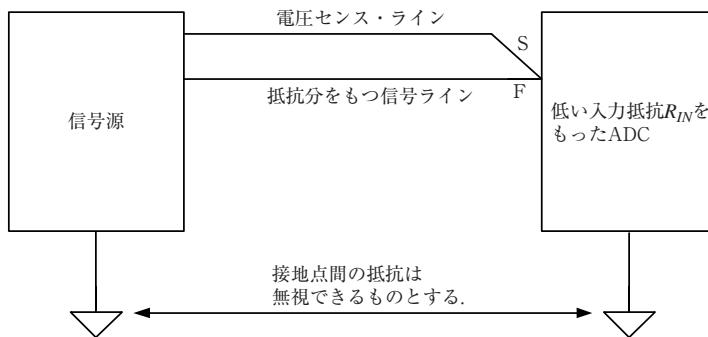

## 2-2 信号線での電圧降下…ケルビン・フィードバック

高精度回路や高分解能（たとえば図 2-2 の例）、あるいは大電流が流れる箇所にかぎると、プリント基板の信号線の抵抗性の電圧降下から生じるゲイン誤差が重要になります。負荷インピーダンスが一定かつ抵抗性である場合、システム全体でのゲインを調整することで、誤差は補償できます。それ以外の状況では、図 2-3 に示すように、ケルビン（電圧センス）フィードバック技術を使うことで、多くの場合は誤差を取り除くことができます。

図 2-2 の事例に対する図 2-3 の改善案でも、依然として、高精度で入力インピーダンスの低い A-D コンバータを駆動するために、抵抗分の無視できない長い基板パターンが使われています。しかしながら、この場合でも、信号線での電圧降下は誤差を増大させません。A-D コンバータの入力ピンから直接に電圧が帰還され、駆動源に戻されているからです。この手法では、信号線での電圧降下にかかわらず、A-D コンバータに印加される信号電圧には完全な精度が得られます。

負荷における電圧印加点 (F) とセンス点 (S) を分離することにより、印加電圧ラインでの電圧降下による誤差が取り除かれます。これはもちろん、負帰還をかけたシステムでのみ可能なことです。また、複数の負荷を等しい精度で駆動するためには、このような構成を使うことはできません。負帰還は 1 箇所からしか取れないからです。また、この非常に単純化されたシステムでは、信号源と負荷との間のコモン・ラインでの誤差は無視されて

図 2-3 検出用ラインを使うことで負荷の接続点で精度を補償する

います。つまり、グラウンド経路での発生電圧は無視できるという仮定にたっています。多くのシステムでは、必ずしもそうはならず、その場合には以下に述べるようにさらに手を打つ必要が生じます。

## 2-3 信号の帰還電流

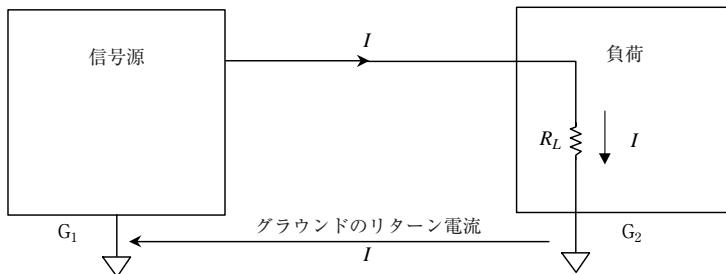

キルヒ霍フの法則によれば、回路の任意の点において、電流の代数的総和はゼロになります。このことにより、回路を解析するにあたっては、図 2-4 のように、回路のループを流れるすべての電流を、特に帰路を通るリターン電流をつねに考慮しなければならないことがわかります。

一般的な多くの失敗の結果として思い知らされることは、グラウンド処理の問題を考慮する際には、回路を正確に考察することが解析のために非常に重要だということです。完全な差動回路の検討をしている場合、ほとんどのエンジニアにとって、グラウンドを戻ってくる電流 $I$ を考慮することは容易なことです。

しかしながら、シングルエンドの信号がグラウンドを基準に参照されるような、より一般的な回路を検討している場合では、グラウンド記号で表される回路図上のすべてのポイントが同一電位であると仮定してしまうことがほとんどです。あいにくと、必ずしも、そのような申し分ない状況になっているわけではないのです。

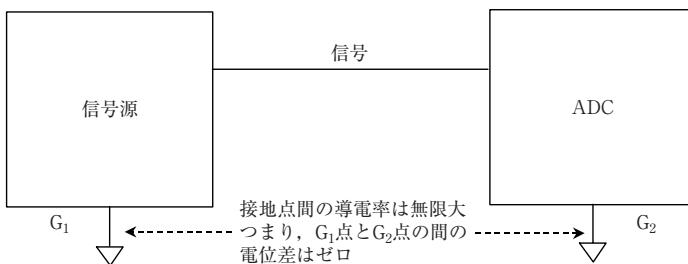

例として、非常に楽観的なグラウンドの取り扱いを図 2-5 に示します。もし実際に、グラウンドの導電率が無限大であるとしたら、電源グラウンド $G_1$ と負荷グラウンド $G_2$ の間の電圧差はゼロになります。ところが、これは不正確であり、高精度回路では、とんでもない結果をもたらしかねません。

図2-4 電源と負荷からなる完結した回路での電圧降下を解析するにはキルヒ霍ッフの法則が手がかりになる

回路の任意の点において、電流の代数和はゼロになる。

言いかえるならば、出ていった電流は戻ってこなくてはならないわけで、片側が接地されているものを含めて、電圧源はすべて差動で扱わなければならぬ、という結論になる。

図2-5 このような楽観的な図は間違い…電源と負荷のグラウンド間の導電率を無限大だと仮定するのは現実的ではない

グラウンド導体を理想に近づけるより現実的な手法は、内在するインピーダンスを解析し、不要な電圧ノイズを最小限にすることです。

### ●グラウンド・ノイズとグラウンド・ループ

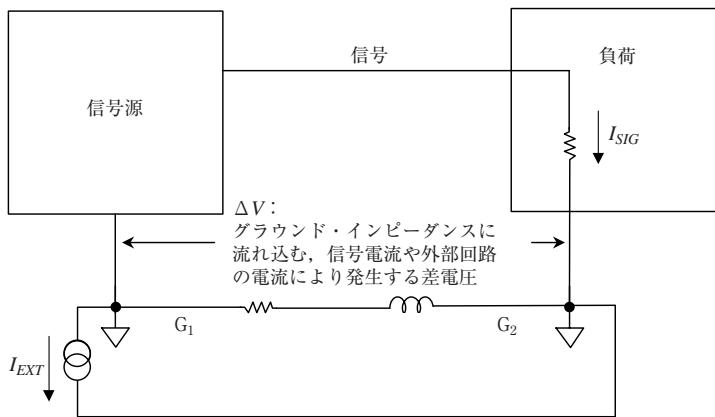

より現実的なグラウンド回路のモデルを図2-6に示します。図のようにグラウンド・ポイント  $G_1$  と  $G_2$  の間の複素インピーダンスを信号の戻り電流が流れ、この経路で電圧降下  $\Delta V$  を引き起こします。しかし、ここで  $I_{EXT}$  のように外部電流が追加して流れる場合に注目しましょう。そのような電流は、 $G_1$  と  $G_2$  の間に(電流の大きさとグラウンド・イン

図 2-6 G<sub>1</sub>-G<sub>2</sub> 間のインピーダンスおよび信号と無関係な外部電流の影響を考慮した、より現実的な電源-負荷間のグラウンド系

ピーダンスに応じて) 信号と相關をもたないノイズ電圧を発生させることを理解しておくことが重要です。

これらの好ましくない電圧のうち、あるものは信号の負荷側に現れるかもしれません、それが伝送信号を劣化させてしまう可能性があります。

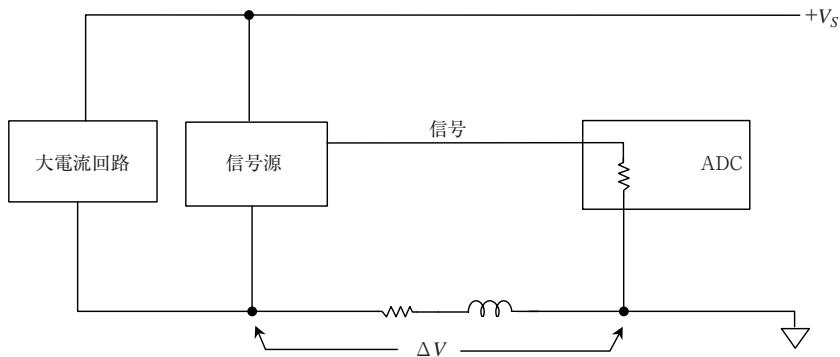

もし電流経路があるなら、グラウンド・インピーダンスを通して余計な電流が流れることは明らかです。この場合、信号源とグラウンド・ループの一部を共有する大電流回路によって、問題が発生することがあります。

図 2-7 は、そのような信号源と大電流回路がその一部を共有している共通グラウンドの経路を表していて、電源から大きな変動する電流が流れています。この電流は共通なグラウンド経路を流れ、誤差電圧  $\Delta V$  を発生させます。

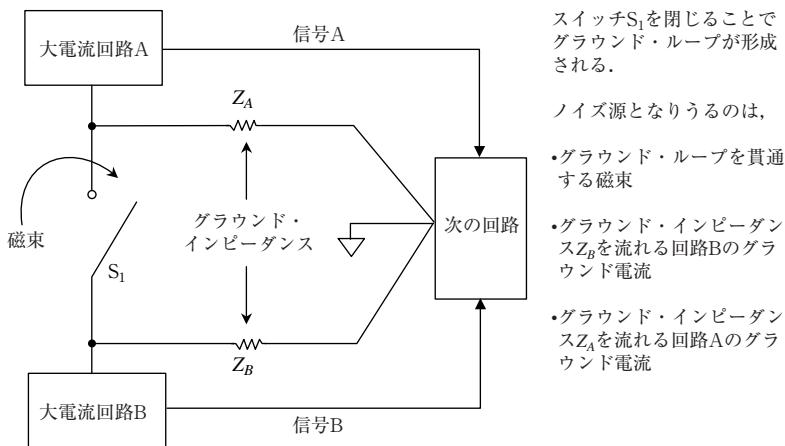

また、図 2-8 から、もしグラウンド系がループや円形のグラウンド導体形状 ( $S_1$  が閉じている状態) である場合、明らかに外部磁界により発生する起電力の影響を受けやすくなる危険が増大します。また、大電流の流れる領域から漏れたグラウンド電流により発生した信号が、システム内の高感度な回路へノイズとして影響を与える危険性も現実のものとなります。

これらの理由により、回路内のすべてのリターン電流の経路を共通電位点まで個別配線することで、最も有効にグラウンド・ループの形成を避けることができます。図 2-8 の回路の場合では、右中ほどにあるのが共通グラウンド点です。このような接続が成り立つのは、 $S_1$  が開いている状態です。

〈図2-7〉共通グラウンドを流れる電流は誤差を発生させうる

$\Delta V$ : 共通グラウンド・インピーダンスに、

信号電流に加えて、大電流が流れることで

発生する電圧。

〈図2-8〉グラウンド・ループ

当面、現実的とは言えない超電導グラウンド（！）の利用はわきにおくとしても、このグラウンド・ノイズの問題に対処する方法はいくつもあります。ただし、ある一つの方法をとれば、他の方法はとらなくてすむようなことは稀で、一般に現実のシステムでは複数の方法をあわせて実施します。以下に、各手法を個別に取り上げて説明します。

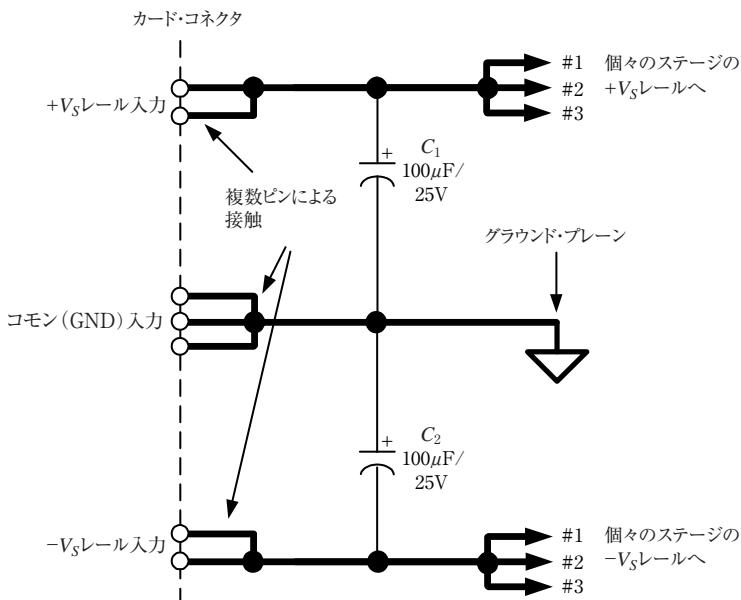

### ●スター・グラウンド (star ground)

スター・グラウンドは、回路において電圧基準となるグラウンド・ポイントを、ただ一つに限定する考えにもとづいています。これは、スター・グラウンド点として知られています。共通のグラウンドから、放射状に延びる複数の導体が星(star)の形に見えるとすると、理解しやすくなります。また、これは図2-8において、共通点からもっと多くのグラウンド・リターンが出ていると考えることで理解できます。スター・ポイントは、星のように見えなければならない必要はありません。それは、グラウンド・プレーン上で的一点でもよいわけですが、スター・グラウンド系で肝心なのは、すべての電圧はグラウンド・ネットワークにおける特定の1点を基準に規定されるということで、(プローブのグラウンドを適当につないだ) ただのグラウンドは基準点ではありません。表2-1に、この考え方を簡潔にまとめました。

このスター・グラウンドの考え方たは論理的には適切ですが、現実に実施しようとする困難に直面することがあります。たとえば、信号の相互作用、ハイ・インピーダンス信号やグラウンド・パスの影響を最小限にしようと、すべての信号経路を引いてスター・グラウンドを設計したとすると、しばしば実装の問題に突き当たります。回路図に電源を付け加えた場合、それは本来は欲しくないグラウンド・パスを加えてしまうか、電源から既存グラウンド・パスへ大きな電流を流し込んでノイズ源となるか、またはその両方となって信号伝送を台無しにしてしまいます。この問題は、各回路ごとに電源(とそのためのグラウンド・リターン)を分離することで防げることが珍しくありません。たとえば、ミックスト・シグナルのアプリケーションでは、分離したアナログ・グラウンドとデジタル・グラウンドに対応する、別々のアナログ電源とデジタル電源をスター・グラウンド点で接続することが一般的です。

### ●アナログ・グラウンドとデジタル・グラウンドの分離

デジタル回路がノイズを発生するのは事実です。飽和型論理回路は、スイッチング時に電源からスパイク状の大きな高速電流を引き込みます。しかし、数百mV(あるいはそれ以上)のノイズ耐力をもつ論理回路ステージは、通常、電源の厳重なデカップリングが必要になることはほとんどありません。一方アナログ回路は、電源ラインとグラウンドの双方のノイズに非常に脆弱です。それゆえ、アナログ性能が損なわれるのを防ぐために、

〈表2-1〉スター・グラウンドの概念

システム内のすべての信号電圧がただ1点を基準に規定される場合、

その点をシステムのスター・グラウンドと呼ぶ

アナログ回路とデジタル回路を分離するのは、理にかなったことです。それには、ミックスト・シグナル・システムでは厄介なことがあります。グラウンド・リターンと電源ラインの双方を分離することが含まれます。ミックスト・シグナル・システムが最大限の性能を発揮するには、面倒でもアナログ・グラウンドとデジタル・グラウンドを分離し、電源も別々にすることが非常に重要になります。アナログ回路には単一5Vで動作するものがありますが、それはマイクロプロセッサやDRAM、電動ファン、事によってはソレノイド・ハンマまでが使用するノイズだらけの5Vラインを共用しても、申し分ない動作をすることを意味しているわけではありません。要求されることは、アナログ回路部分はそのような低電圧電源から最大性能で動作するということであって、ただ動作すればよいわけではありません。この違いを達成するには、電源ラインとグラウンドの接続について非常に注意深く検討する必要があります。

表2-2と表2-3は、システム設計時に役に立つ、アナログとデジタルの電源とグラウンド処理についてのコンセプトをまとめています。

システムのアナログ・グラウンドとデジタル・グラウンドは、信号が共通電位に対して参照されるように、どこかで接続されなければなりません。このスター・グラウンド・ポイント、すなわちアナログ/デジタルの共通ポイントは、システムのアナログ部分のグラウンドにデジタル回路の電流が流れ込まないように選びます。したがって、しばし

〈表2-2〉ミックスト・シグナル・システムに適した電源とグラウンド・ノイズに関するコンセプト

- デジタル回路からはノイズが発生する

- アナログ回路は静かである

- 電源とグラウンド・ラインからもたらされるデジタル回路からのノイズは精密なアナログ回路を台無しにすることがある

- システムのデジタルとアナログの電源およびグラウンドは分離するのが賢明である

- アナログ回路とデジタル回路のグラウンドは1点で接続されなければならない

〈表2-3〉ミックスト・シグナル・システムのデータ・コンバータに関するアナログ・グラウンドとデジタル・グラウンドの取り扱い

- モノリシックおよびハイブリッドA-Dコンバータは、しばしばAGND端子とDGND端子を別々にとっており、デバイスの近傍で一緒に接続しなければならない。

- これは、内部で両グラウンド間の接続をすると、ボンディング・ワイヤでの電圧降下が大きくなりすぎるからである。

- この要請から起きるグラウンド処理の問題についての最良の解決策は、両方の端子をシステムのアナログ・グラウンドに接続することである。

- これにより、デジタル・ノイズがシステムのアナログ・グラウンドに持ち込まれたり、デジタル回路のノイズ耐力が落ちてシステム性能にひどい悪影響をもたらすといった懸念は小さい。

ば電源部分で両者をつなぐのが好都合になります。

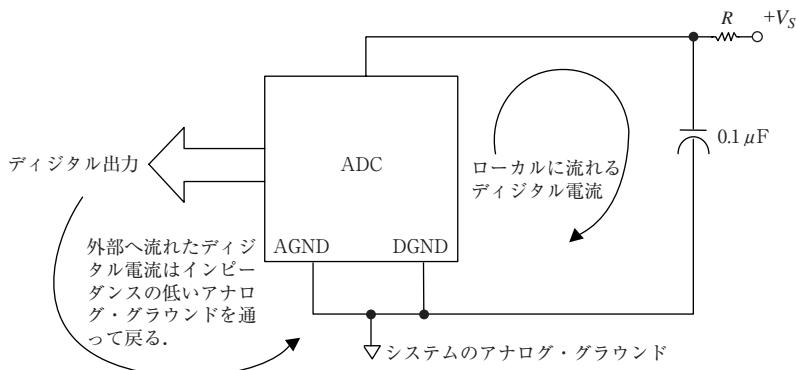

同様に、多くの A-D コンバータや D-A コンバータはアナログ・グラウンド端子 (AGND) とデジタル・グラウンド端子 (DGND) を別々にもっていることに注意すべきです。デバイスのデータシートでは、これらの端子はパッケージの近傍で一緒につなぐよう薦めています。このことは、アナログ・グラウンドとデジタル・グラウンドを電源のところでつなぐという先ほどのアドバイスと、複数のコンバータのあるシステムではアナログ・グラウンドとデジタル・グラウンドを一箇所で接続するようにというアドバイスに反しているように思えます。

実は、アドバイスに反しているわけではありません。これらの端子のアナログ・グラウンドとデジタル・グラウンドという名称は、端子がつながっているコンバータ内の部品に対応しているのであって、それらがつながるべきシステム・グラウンドに対応しているのではないからです。たとえば、A-D コンバータについて言えば、一般にこれらの二つの端子は一緒に接続されて、システムのアナログ・グラウンドにつながるべきです。IC のパッケージ内で二つの端子を接続することはできません。なぜなら、コンバータのアナログ部分の回路は、チップのボンディング・ワイヤを流れるデジタル電流による電圧降下を許容できないのです。しかし、それらはデバイスの外部では接続できるわけです。

図 2-9 は、この考え方を A-D コンバータのグラウンド接続を例にして図にしたものです。これらの端子が図のように接続されたとすると、コンバータのデジタル回路のノイズ耐力は、デジタルとアナログのシステム・グラウンド間のコモンモード・ノイズのぶんだけ多少損なわれます。しかしながら、デジタル回路のノイズ耐力は数百から数千

図 2-9 データ・コンバータのアナログ・グラウンド端子 (AGND) とデジタル・グラウンド端子 (DGND) はシステムのアナログ・グラウンドに接続される必要がある

mVのオーダーがありますので、そのことが問題になることは稀でしょう。

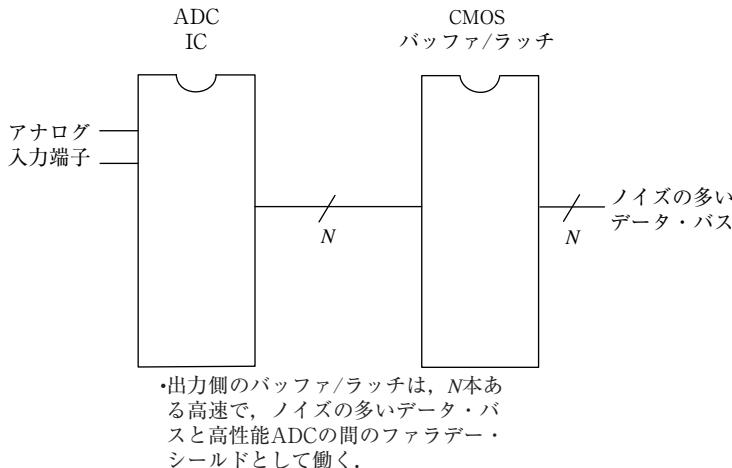

アナログ回路のノイズ耐力は、アナログ・グラウンドを流れるコンバータから外部へのデジタル電流のぶんだけ減少します。これらの電流はごく小さく抑えるべきで、コンバータの出力負荷を重くしないことで最小限にできます。このために良い解決法は、A-Dコンバータの出力にCMOSバッファ・レジスタICのような、入力電流の少ないバッファを使うことです。

もし、コンバータのデジタル電源が低い抵抗値(図2-9中のR)でアイソレーションされ、すぐ近傍の $0.1\ \mu F$ のコンデンサでアナログ・グラウンドにデカップリングされているなら、コンバータのデジタル回路の急峻に変化する電流はコンデンサを通してグラウンドに流れてしまい、外部のグラウンド回路には現れないでしょう。アナログ・グラウンドのインピーダンスがアナログ回路の性能に見合うように低く保たれるなら、外部のデジタル・グラウンドに流れる電流によるノイズの増加はほとんど問題になりません。

### ●グラウンド・プレーン(ground plane)

前述したスター・グラウンドに関連するのが、グラウンド・プレーンの使用です。グラウンド・プレーンを実装するには、両面基板や多層基板の一つの層の全面に銅箔を残し、それをグラウンドとして使います。これは、十分な分量の金属の抵抗が非常に小さくなることにもとづいています。広い導体平面であることにより、インダクタンスもまた小さくなります。グラウンド各点での電位差が最小になるという意味で、グラウンド・プレーンにすると最良の低抵抗グラウンドを作ることができます。

グラウンド・プレーンの考え方たは、電源プレーンにも拡張可能であることに注目しましょう。電源プレーンの利点は、非常にインピーダンスの低い導体ということでグラウンド・プレーンに似ていますが、グラウンドではなく、一つあるいは複数の電源に割り当てられます。したがって、システムにはグラウンド・プレーンと同様に一つ以上の電源プレーンが存在することがあります。

製造および組み立て時にトラブルを起こしやすいということで、グラウンド・プレーンは使うべきでないという議論がときどき起ります。そのような議論は、基板の製造に使用する接着剤が未発達で、ウェーブ・ソルダリングが信頼性に欠けたプロセスであり、また、ソルダ・レジスト技術に対する理解が欠けていた過去の議論であって、今日では状況は変わっています。

グラウンド・プレーンの構成および動作に関連したポイントを表2-4にまとめました。

グラウンド・プレーンを使うことで、多くのグラウンド・インピーダンスによる問題が解決されますが、万能ではないことも理解しておくべきです。連続した銅箔シートであっても、抵抗とインダクタンスは残っています。そして状況によっては、それらが回路の機

〈表 2-4〉グラウンド・プレーンの特徴

- 基板の片面あるいは 1 層の全面をつながったグラウンド導体とする。

- これによりグラウンドの抵抗とインダクタンスが最小になるが、それでグラウンドに関係する問題のすべてが解決されるわけではない。

- グラウンド・プレーンを分割することは回路の性能を向上させる場合もあれば、低下させる場合もあって、一般化したルールはない。

- 昔は、グラウンド・プレーンは製造するのが困難であったが、今日では問題ない。

- 多層基板、グラウンド/電源プレーンを用いた基板設計は一般的なものである。

能を妨げことがあります。設計者は、グラウンド・プレーンに大電流を流すことに慎重でなくてはなりません。それは、高感度の回路に干渉するような電圧降下を発生するかもしれませんのです。

### ● 表皮効果 (skin effect)

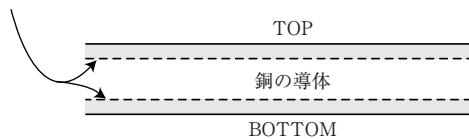

高周波においては、誘導により電流が導体の外側表面に集まって流れてしまう表皮効果について考察することも必要です。これは、この章で先に解説した、導体の直流抵抗とは対極にあることに注意しましょう。

表皮効果により、導体は高周波での抵抗が増大します。この効果は、高周波になるにつれて増大する導体の自己インダクタンスによるものとは別物であることにも注意が必要です。

表皮効果は非常に複雑な現象で、詳細な計算はここでの議論を越えるものです。しかしながら、銅導体について、電流が流れる表面からの深さは、 $6.61/\sqrt{f}$  [cm] ( $f$  の単位は Hz) という式により、よい近似値が得られます。

図 2-10 に、代表的なプリント基板の銅箔での表皮効果についてまとめました。この銅箔パターンの断面は、電流の流れる方向を横から見ている図になります。

表皮効果の深さが導体の厚さの 50 % より小さくなると影響が無視できなくなると仮定すると、代表的な銅箔<sup>\*3</sup>の場合、約 12 MHz 以上の周波数では表皮効果を考慮しなくてはならなくなります。

表皮効果が重要になってくる領域では、銅の抵抗は  $2.6 \times 10^{-7} \times \sqrt{f}$  [ $\Omega/\square$ ] と表せます。表皮効果の深さが導体厚より大きい場合には(つまり直流や低周波において), この式は当てはまりません。

図 2-11 は、基板パターンとその直下のグラウンド・プレーンに隔てられた場合に、導体を流れる電流を表しています。

\* 3 : 【訳注】厚みで 36  $\mu\text{m}$  と考える。

〈図 2-10〉基板導体での表皮の深さ

◆高周波電流は表面のみを流れる

◆表皮効果の深さ :  $6.61/\sqrt{f}$  cm,  $f$  の単位はHz

◆表皮の抵抗 :  $2.6 \times 10^{-7}\sqrt{f} \Omega/\square$ ,  $f$  の単位はHz

◆表皮効果による電流はパターンの両面を流れるので、上記の表皮の抵抗については、このことを考慮する必要がある。

〈図 2-11〉基板導体とグラウンド・プレーンでの表皮効果

この図で、点線で表された高周波電流の流れる領域が、表皮効果で狭くなっていることに注目してください。プリント基板での表皮効果を計算する際、一般には基板の銅箔の両面を電流が流れるので（これはマイクロストリップ・ラインの場合は必ずしも当てはまらない、後述）、銅箔の抵抗は先に示した値の半分となります。

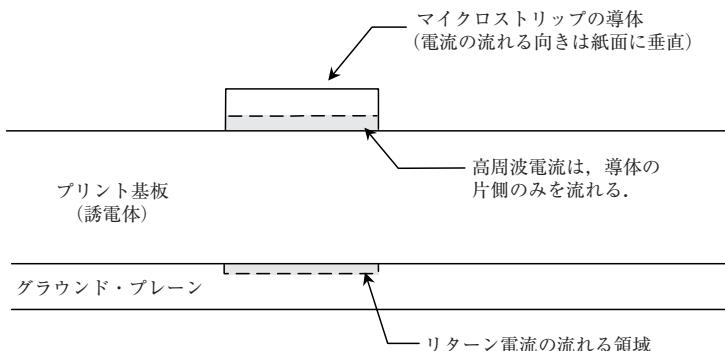

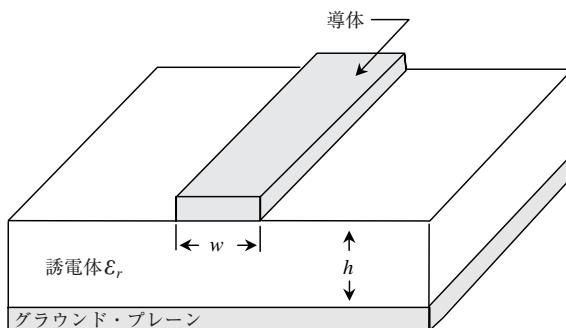

### ●伝送線路

ここまでとのところで、往路と復路が互いに接近して配置された信号の経路では、インダクタンスが減少するという利点を見てきました。前掲の図 2-11 で示したように、基板のグラウンド・プレーンの上を通過するパターンを高周波電流が流れるとき、その導体の構成はマイクロストリップ伝送線路として動作し、グラウンド・プレーンを流れる帰路電流

の大部分はストリップ・ラインの直下を流れます。

図2-12は、導体幅を $w$ 、誘電体の厚みを $h$ 、誘電率を $\epsilon_r$ としたときの、マイクロストリップ伝送線路の定数を示しています。

このようなマイクロストリップ・ラインの特性インピーダンスは、パターン幅と厚み、そして基板の誘電率に依存して決まります。マイクロストリップ・ラインの設計の詳細については、本書の第6章で触れることにします。

ほとんどの直流と低周波でのアプリケーションでは、基板パターンの特性インピーダンスはあまり重要ではないでしょう。グラウンド・プレーン上のパターンが伝送線路としてふるまうような周波数においてさえ、自由空間での信号の波長が線路の長さの10倍以上あるなら、特性インピーダンスや適切な終端処理に頭を悩ませる必要はありません。

しかしながら、超高周波(VHF)やそれ以上の周波数では、適切な終端をした伝送システムにおけるマイクロストリップ伝送線路として基板パターンを使うことができます。インターフェースを容易にするため、一般的には $50\Omega$ ,  $75\Omega$ ,  $100\Omega$ のような標準の同軸ケーブルのインピーダンスと整合するようにマイクロストリップ・ラインを設計します。

そのようなシステムでの損失を最小限にするためには、基板材料に高周波での損失が小さいものを選ばなくてはなりません。このことから、一般にはテフロンや類似の低損失基板材料を使うことになります。しかし、短い線路であれば、安価なガラス・エポキシ基板でも、多少の損失があるにしても十分に使用できることも多いのです。

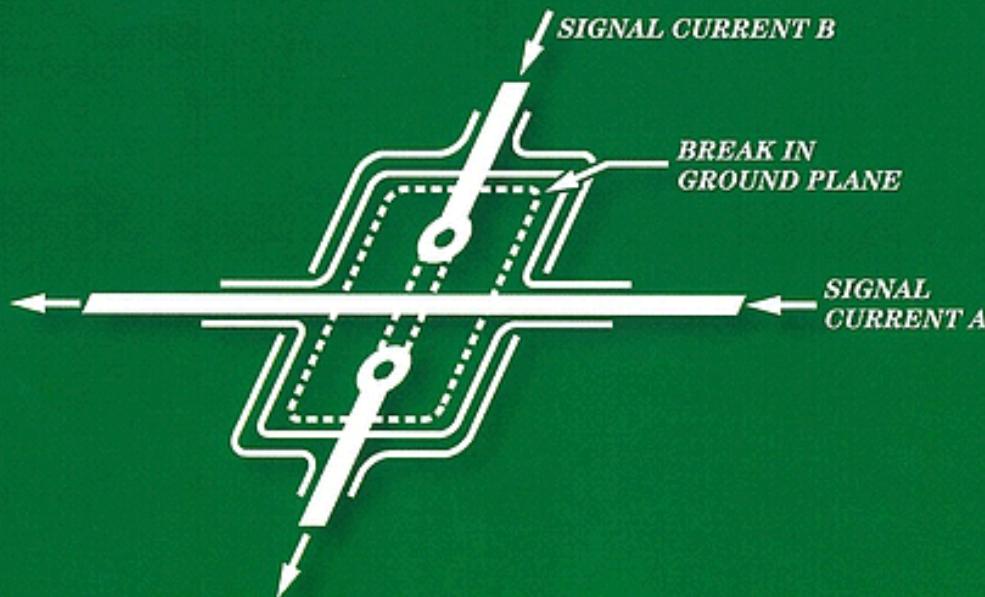

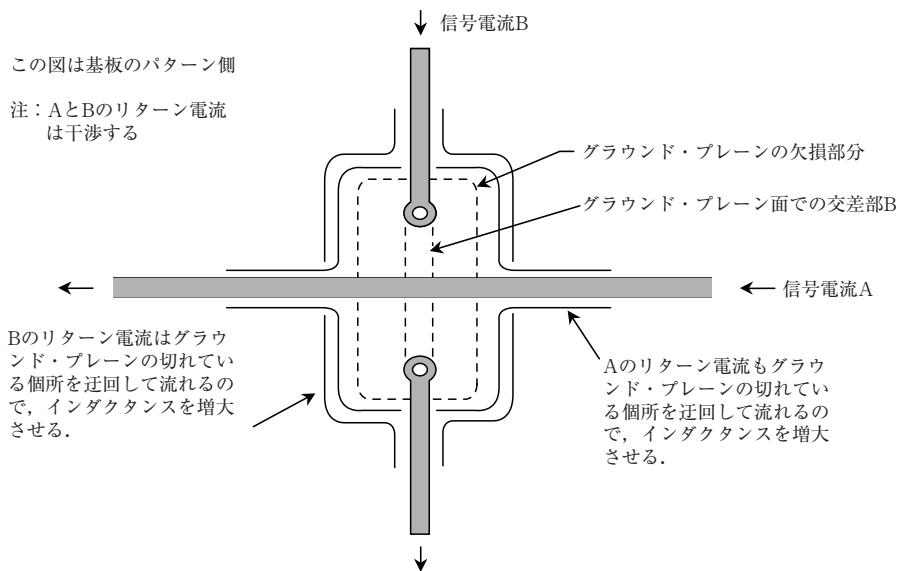

### ●グラウンド・プレーンの切れ目に注意

導体直下のグラウンド・プレーンに欠損部分がある場合には、帰還電流はその周りを迂

〈図2-12〉プリント基板のマイクロストリップ伝送線路は特性インピーダンスを制御された導体ペアの例である

図2-13 グラウンド・プレーンの切れ目により回路のインダクタンスが増加して外部電磁界の影響を受けやすくなる

回して流れざるをえません。その結果、回路のインピーダンスが高くなり、外部電磁界から影響を受けやすくなります。図2-13では、基板上でパターンAとBが交差する必要がある部分において、その様子を示しています。

二つの直交する導体が交差するように欠損部分を作るなら、かわりに後から交差しようとする信号にジャンパ・ワイヤを使って、もう一つの信号とグラウンド・プレーンを横切るようにすると、ずっと良い結果が得られます。そのようにすれば、グラウンド・プレーンは二つの信号導体間のシールドとして働き、表皮効果により信号と反対のグラウンド・プレーン面を流れる双方の信号のリターン電流の干渉が避けられます<sup>\*4</sup>。

多層基板では、ジャンパ・ワイヤを使わないで、信号の交差と連続したグラウンド・プレーンを収めることができます。多層基板は単純な両面基板より高価ですし、トラブルシュートも大変ですが、より良好なシールドと信号の引き回しを可能にします。基本となる原理が変わるものではありませんが、レイアウトをするうえでの選択肢が増えるからです。高性能のミックスド・シグナル回路を設計するうえで、良好な結果をもたらす方法の一

\*4：【訳注】正確には銅箔の厚みと信号の周波数が関係する。

つは、電気的に切れ目のないグラウンド・プレーンを、少なくとも一つ設けた両面基板や多層基板を使うことです。一般に、そういうグラウンド・プレーンのインピーダンスは十分に低く、システムのアナログ部品とデジタル部品の両方の単一グラウンド・プレーンとして使うことができます。しかし、それが可能であるかどうかは、必要とされる分解能と帯域、そしてシステム内のデジタル・ノイズの量に依存します。

### ● グラウンド・アイソレーションの技術

グラウンド・プレーンを使うことで、インピーダンスが低下し、グラウンド・ノイズを大きく下げるのに効果がある一方、それでもまだ許容できないレベルのノイズが存在するような状況もあります。そのような場合には、グラウンド電位誤差の最小化とアイソレーションの技術が役に立ちます。

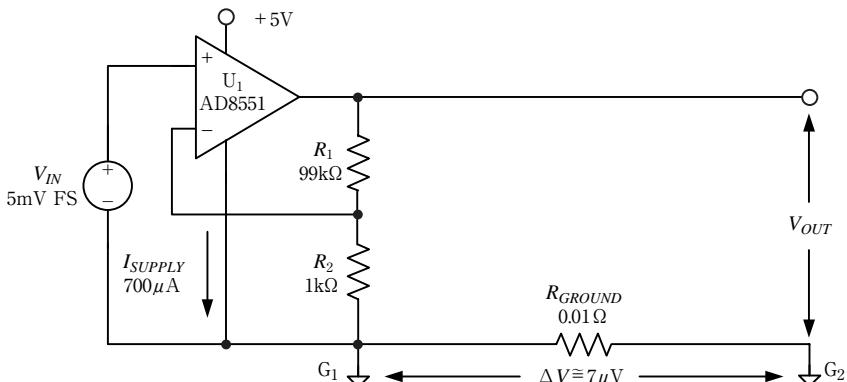

共通グラウンドの結合による問題のもう一つの例を図2-14に示します。この回路では、直流精度を最良にするため、AD8551 チョッパ・アンプを使ったプリアンプが低レベル信号  $V_{IN}$  を正確にゲイン 100 で増幅しています。負荷側において、信号  $V_{OUT}$  は近傍のグラウンドである  $G_2$  を基準に規定されます。AD8551 のわずか  $700\ \mu A$  の電源電流でも  $G_1$  と  $G_2$  の間を流れると、 $7\ \mu V$  のグラウンド電位誤差が発生することになりますが、これはこのOPアンプで予想される入力オフセット電圧の約7倍にも達します。

この誤差は、OPアンプの負電源端子の供給電流を  $G_1$  でなく、分離したパターンでスター・グラウンド  $G_2$  へつなぐことで簡単に防ぐことができます。この方法で、 $G_1$ - $G_2$  間の電源電流パスはなくなり、グラウンド区間による電圧誤差が最小限になります。電圧の現れる  $V_{OUT}$  端子側では、負荷に流れる電流が小さいかぎり誤差はほとんど発生しないこと

図2-14 精密増幅器では注意を怠ると共通グラウンドを流れる微小電流でさえ精度を劣化させてしまうことがある

に着目してください。

場合によっては、信号源のグラウンドと、電圧が参照される点である負荷のグラウンドとの間の電圧差を防ぐことが容易ではないことがあります。同一基板内にかぎった議論の範囲では、これは数十mVオーダーのグラウンド電圧誤差を除去するという問題になるでしょう。もし、信号が基板の外にある信号源から発生している場合には、除去しなくてはならないコモンモード電圧の大きさはすぐに数Vオーダーに（あるいは数十Vにさえ）なってしまうことがあります。

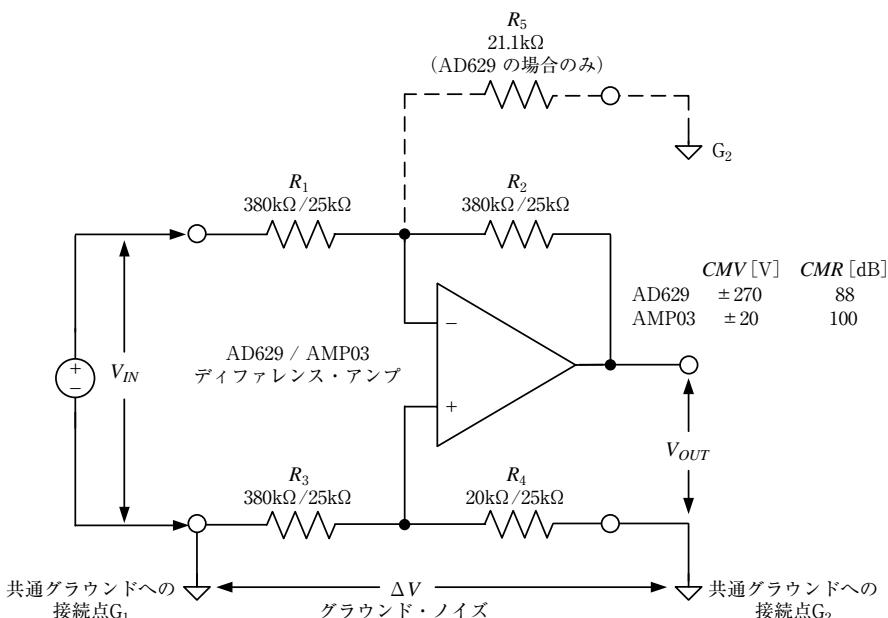

幸いにも、先に解説した原理を用いれば、そのような大きいノイズ電圧があっても信号伝送の精度を保つことが可能です。それには差動入力のグラウンド分離アンプを使うことです。グラウンド分離アンプは信号を差動処理し、一般に60dB以上コモンモード(CM)電圧を除去することで、各ステージ間でのグラウンド電位誤差による影響を最小限に抑えます。グラウンド分離アンプを使う手法を図2-15に示します。この構成には、 $\pm 270\text{ V}$ までのコモンモード電圧を扱う場にはAD629を、 $\pm 20\text{ V}$ までならAMP03をそれぞれ使うことができます。

図2-15 差動入力グラウンド分離アンプは信号源グラウンド  $G_1$  と測定点グラウンド  $G_2$  の間の誤差電圧を除去することで高精度の信号伝送を可能にする

この回路において、入力  $V_{IN}$  は  $G_1$  が基準になっていますが、出力は  $G_2$  点を基準にして参照されなければなりません。高い CMR をもったユニティ・ゲインのディファレンス・アンプ（差電圧アンプ）を使うことで、二つのグラウンド間にノイズ電圧  $\Delta V$  は容易に取り除かれます。AD629 は代表値で 88 dB の CMR があり、AMP03 では代表値で 100 dB に達します。高同相圧用のアッテネータと、それにつづく正味の差動ゲインが 1 の差動アンプの組み合わせにより、AD629 の高いコモンモード電圧定格が得られています。AD629 を使用する場合の図の  $R_1$  から  $R_4$  の値は、それぞれ二つ示されている抵抗値の左側の値になります。AMP03 では、図の右側に示したように、25 kΩ の  $R_1$  ~  $R_4$  の抵抗を使った、精密な 4 抵抗差動増幅器として動作します。どちらのデバイスもグラウンド分離アンプとして必要な部品が 1 パッケージに収められたものです。

この方法によると、グラウンドでの電圧降下を厳密に制御したり、そのような誤差電圧を最小にするように追加のパターンや大きなグラウンド・プレーンを作ったりする必要性が少なくなります。この方法は、図示したように固定ゲインのディファレンス・アンプを使って実現することもできれば、ゲイン 1 にした標準的な計装アンプを使っても実現できます。片電源動作が必要であれば、たとえば AD623 が使用できます。どちらの場合でも、差動アンプの入力を単に入れ換えることによって、信号の極性を自由に選ぶことができます。

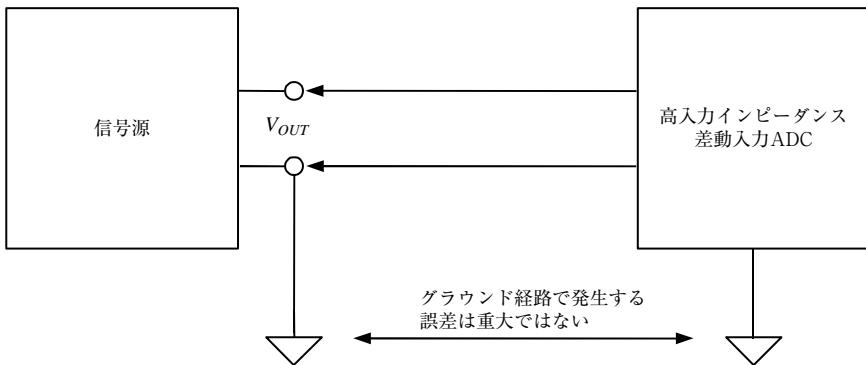

一般的な条件では、測定や処理を行うために信号を基板上のある点から別の点に伝送することは、互いに関連する重要な二つの技術によって最適化できます。それは高インピーダンスで、差動信号処理を使う方法です。信号を高インピーダンスの計装アンプで受けることで負荷効果が減って電圧降下が小さくなり、また離れた点の電圧を差動で検出することでグラウンド・ノイズから受けける影響が小さくなります。

さらに A-D コンバータで信号を処理する場合、これらの伝送に関する要求レベルは差動グラウンド分離アンプ段を付け加えなくても実現できます。それには差動で動作する A-D コンバータを選べばよいのです。A-D コンバータの高い入力インピーダンスは、プリント基板の配線抵抗による負荷の影響を小さくします。加えて、差動入力では信号を出力端子（たとえそれがシングルエンドであっても）から直接に検出することができます。そして、A-D コンバータの CMR は A-D コンバータと信号源グラウンド間のノイズ電圧による影響を取り除いてくれます。

この高インピーダンスの差動入力 A-D コンバータを使った場合の考え方を、図 2-16 に示します。これは、負荷を駆動するほとんどすべての信号源に対して当てはめることができます。すべての負荷は、シングルエンドであっても、適切な差動入力段を加えることで差動になります。

高性能の高インピーダンス計装アンプや、多くの場合は図 2-15 のような単純な減算 OP アンプ回路を使うことで、そのような差動入力を設けることができます。

図 2-16 高インピーダンス差動入力 A-D コンバータでは信号源と負荷の間での高い信号伝送精度も得ることができる

### ● 静的な基板の影響

プリント基板の静的な影響のうち、代表的なものは漏れ抵抗です。基板の表面がフラックス残渣、塩（ナトリウム化合物）の付着、その他の残渣で汚れることで、回路のノード間に漏れ電流の経路が作られることになります。十分に清浄な基板であっても、15 V の電源ラインの近くのノードに 10 nA あるいはそれ以上のリーク電流が発生することは、特別な現象ではありません。不都合なノードへ数 nA のリーク電流が流れ込めば、回路出力では数 V 単位の誤差が発生することになります。たとえば、10 MΩ の抵抗に 10 nA の電流が流れると 0.1 V の誤差となります。あいにくなことに標準的な OP アンプの端子配列では、 $-V_S$  電源端子を非反転入力端子のとなりに配置してありますが、非反転入力端子はしばしば高インピーダンスで使われます。リーク電流に敏感なノードを見分けるのは簡単です。仮に数 nA かそれ以上の不要電流が流れ込んだとして、問題が起きるかどうかを考慮すればよいのです。

すでに回路ができあがってしまっていたら、古典的な試験方法によって疑わしいノードが湿度に敏感であるかどうか確認することができます。回路の動作を観察しながら、あやしい箇所をストロウで吹いてみます。ストロウにより息の中の水蒸気が集められ、その場所にさしかかれば基板上の塩分とあいまって、回路の動作が妨げられることになります。

表面でのリーク電流の問題を防ぐのには、簡単な手段があります。プリント基板を徹底的に洗浄して残渣を取り除くことはかなりの効き目があります。イソプロピル・アルコールで十分にブラシ洗いして、非電離水で洗い流し、85 °C で数時間ベーキングする方法もあります。しかし、基板を洗うための溶剤の選択には注意が必要です。ある種の溶剤で洗うと、水溶性フラックスによっては塩が析出して、かえってリーケージをひどくしてしまう

います。

もし、回路がリークに対して敏感であることがわかった場合には、いくら徹底的に洗浄しても、一時の気休め程度にしかなりかねません。人が触れたり、清浄でない環境や高い湿度によって、すぐに問題が再発します。回路のふるまいを安定化するには、さらなる手段として、表面コーティングなどの方法を検討しなければなりません。

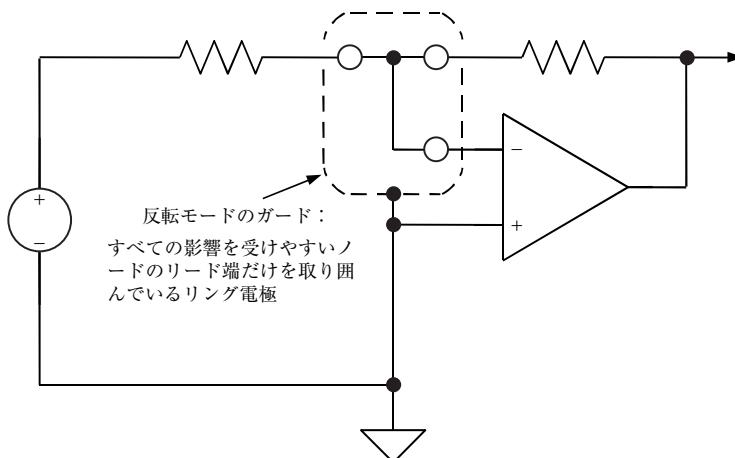

幸いにして、ガーディングに代表される、信頼性の高い恒久的な表面リークに対する解決策があります。慎重に設計したガードは、産業機械のように苛酷な環境にさらされる回路であっても、リークの問題を解消することができます。代表的な、反転/非反転のOPアンプ回路に適用したガーディングの基本原理を二つの図で説明します。

図2-17は、反転増幅回路に適用したガード電極です。この場合、OPアンプの基準となる入力の電位はグラウンドですから、ガード電極は点線で示したように、反転入力端子につながるすべてのリードを囲う接地されたリング形状（ガード・リング）になります。

ガーディングの基本原理は単純です。影響を受けやすいノードを、迷走電流を容易に取り込む導体で囲み、ガードの導体と囲まれているノードの電位を厳密に同一に保持することです（そのようにしないとガード電極がリークの発生源になってしまいます）。たとえば、ノードに流れ込むリーク電流を  $1\text{ pA}$  以下 ( $1000\text{ M}\Omega$  のリーク抵抗を仮定) に抑えるには、ガード電極とノードとの間の電位差は  $1\text{ mV}$  以下でなくてはなりません。一般に、現在のOPアンプは十分に低オフセットであり、このような用途に適しています。

図2-17 反転増幅回路のガード電極では設置したガード・リングが反転入力のすべての接続を取り囲んでいる

真に高品位のガードを実装するには、重要な注意点があります。伝統的なスルー・ホール基板による接続で好結果を得るには、ガードのパターンを基板の両面に設けるべきです。そしてまた、その全周にわたって複数のビアで相互接続する必要があります。最後に重要な点として、システム設計の要求値から懸念があつたり、必要とされるときには、最初から基板設計にガード電極を含めておくことです。あとからの付け足しで、まともなガード電極ほどの効果を発揮する方法はありません。

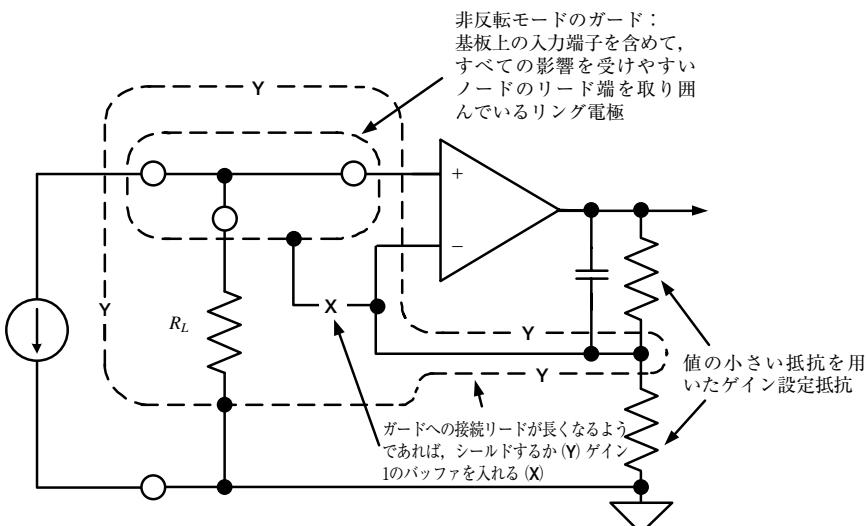

図2-18は、非反転増幅回路でガードを設ける場合を示しています。この場合、OPアンプが参照する入力は信号源によって直接駆動されているので、少々複雑になっています。ここでもまた、ガード・リングが入力ノードへの接続をすべて囲んでいます。しかしここでは、ガードは反転入力に接続された低インピーダンスの帰還分圧抵抗から駆動されています。

通常、ガードと分圧抵抗の間は直接に接続されますが、場合によってはケーブル・シールドを駆動するために、あるいはガード・リングのインピーダンスを非常に低く保つために、ゲイン1のバッファがX印の点に使われます。

バッファを使うかわりに、さらに直接接地したスクリーン・リングYを配置して、その内側にガード電極と帰還ノードを図のように囲むのも別の有効な方法です。この方法では、基板レイアウトにかかる時間を除けば費用がかかりませんし、内部ガード・リングへ

図2-18 非反転増幅回路のガードはOPアンプの非反転入力接続のすべてを低インピーダンス駆動されたガード・リングで囲む

のリークの影響を大きく緩和してくれます。

さて、どのようにすればOPアンプ自体を、これらのガードに守られた安全地帯に性能面を損なわずに接続できるかという点については、ここまで触れてきませんでした。TO99の金属パッケージのデバイスを使う伝統的な方法では、両面基板でのガード・リングを使って、二つの入力リードをガード・リングの中に配置していました。

第2巻の第5部（原著ではChapter-4）で解説されている「ハイ・インピーダンス・センサ」では、この方法を使っています。次の項では、どのように最近のICパッケージを基板の配線パターンに配置すれば、ガードと低リーク動作の利点を得ることができるのかを示します。

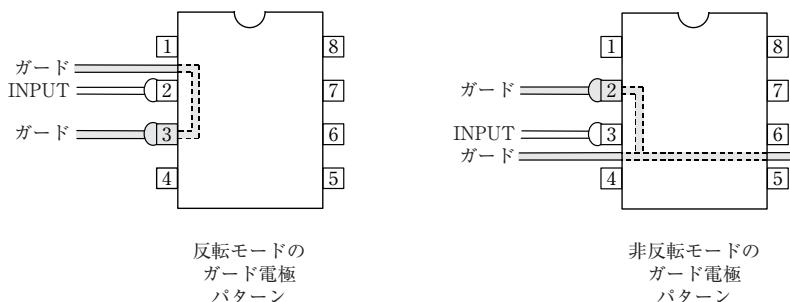

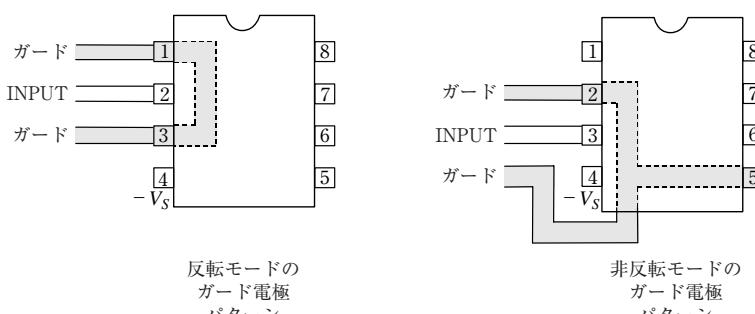

### ● MINIDIP と SOIC の OP アンプのガード電極レイアウトの例

最近の回路の実装では、より小型の8ピンMINIDIPやSOICといったプラスチック・パッケージが好まれます。これらのパッケージを使った場合のガード回路の推奨パターンを、次の二つの図で示します。SOT23のように、もっと小さいOPアンプでもガード電極を引くことは可能ですが、必要なパターン間隔はさらに限定されてしまい、レイアウト設計者にとっても、基板の製造工程にとっても難易度が増します。

アナログ・デバイセズ社のNタイプMINIDIPパッケージについて、反転増幅（図の左側）と非反転増幅（右側）の各動作モードでガードを行う方法を図2-19に示します。この配置は、ピン1あるいはピン4に比較的高い電圧が発生する他のOPアンプにも適用することができます。標準の8ピンDIPパッケージを使うと、隣接するピンとピンの間の0.1インチの間にパターン（ガード・パターン）を通すことができます。これが、DIPパッケージの場合にガードを有効に使ううえで肝心な点です。これで、4番ピンの負電源端子からのリークや、同様に電位が高い1番ピンからのリークを十分に防げるわけです。

図2-19 8ピンMINIDIP(N)パッケージOPアンプの反転/非反転モードに対するガード・パターン

図の左側の反転モードでは、3番ピンとグラウンドに接続されたガード・パターンが反転入力の2番ピンを囲んでいて、入力のパターンと平行に伸びています。このガードは、図2-17に示した回路やその類似の回路において、信号源と帰還の接続点にまで伸ばします。もしケーブルを使うのであれば、その入力端まで伸ばします。右側の非反転モードでは、ガード電位は2番ピンの帰還分圧器の電圧になります。図2-18のように、これは増幅器の反転入力ノードに対応します。

図2-19のどちらの場合でも、ガード・パターンの部分的な接続のみを示しているので、現実のレイアウトでは回路内の影響を受けやすいすべてのノードを含めます。MINIDIPや他のスルー・ホール・タイプのパッケージのアンプを使った場合、反転/非反転動作のどちらでも基板のガード・パターンは両面に設けて、両者はいくつかのビアでつなぐべきです。

SOICの面実装パッケージにガードを設ける場合、0.05インチのピン間隔では、ピン間にトレースを通すのは大変で、事態はもう少し複雑になります。しかしながら、少なくとも反転増幅回路の場合には、有効なガードを設ける方法があります。図2-20に、アナログ・デバイセズ社のRタイプSOICでガードを設けたパターン例を示します。

このSOIC(R)パッケージのシングルOPアンプの多くでは、1番ピン、5番ピン、8番ピンが未接続になっていることに着目します。このような場合、そのピンの位置にガード・パターンを引くことが可能です。図の左の反転モードでは、1番ピンと3番ピンをグラウンドにつないだガード・パターンとすることで、依然として完全に有効なガードが可能です。性能の低下を許容する必要がない、申し分のないガードです。またSOICのOPアンプでは、回路の周囲にはあまりスルー・ホール部品は配置されないでしょう。そのような場合には、ガード・リングはOPアンプのある部品面だけで済むかもしれません。

図2-20 8ピンSOIC(R)パッケージOPアンプの反転/非反転モードに対するガード・パターン

注：多くの“R”パッケージ・デバイスでは、1, 5, 8番ピンはオープンになっている

図の右側のボルテージ・フォロワでは、ガード・パターンは4番の負電源ピンの周りを通らなければなりません。そのため、4番ピンと3番ピンの間のリークは防ぎきれません。この理由により、両電源を使う場合はガードができないので、SOICパッケージのOPアンプを使ったハイ・インピーダンスの精密ボルテージ・フォロワは一般的にお勧めできません。しかし、非反転段に単電源OPアンプを使う場合は、この例外となります。たとえば、AD8551を使ったとすると4番ピンはグラウンドになります、そのままである程度のガード効果が期待できます。

### ●動的な基板の影響

基板の静的な影響が湿度変化や基板の汚れにより出たり消えたりするのに対して、回路の動的な特性に非常に顕著に影響するような問題は、通常は比較的同じ状況を保ちます。設計のやり直し以外に、洗浄やそのほかのちょっとした対処では問題は解決されません。そのため、設計仕様と性能に悪影響を与えつけます。リードや部品配置と関連する浮遊容量による問題は、大多数の回路設計者のかなりよく理解するところです。リードの配置は、正しいレイアウトをすれば解決済みとなるので、残る問題は組み立て作業者が部品の向きやリードの曲げを正しく行うようトレーニングするだけです。

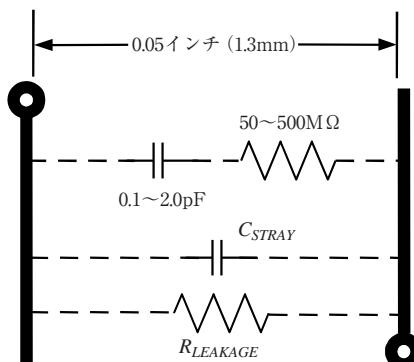

その一方で、誘電体吸収(DA)が問題となることがあります。あまりよく理解されていない回路基板での現象を代表するものと言えます。個別部品のコンデンサと同様に、プリント基板の誘電体吸収は、接近したノード間を抵抗と容量を直列接続したモデルで考えることができます。その影響は、ノード間の距離に反比例し、長さに比例します。

図2-21に示すように、このRCモデルの等価的な容量値は0.1～2.0 pFであり、抵抗値は50～500 MΩの範囲です。0.5 pFと100 MΩが代表値です。したがって、回路基板の誘

〈図2-21〉誘電吸収はプリント基板回路の動的応答に悪い影響を与える

電体吸収は、ハイ・インピーダンス回路に最も影響を及ぼします。

基板の誘電体吸収は、回路の動的な応答、たとえばセトリング・タイムに最も顕著に影響を与えます。回路のリークとは異なり、その効果は通常では湿度やその他の環境条件とは関係しません。どちらかというと、むしろ基板の誘電特性と関係したものになります。スルー・ホールめっきを作成する過程にかかる化学作用が、問題を深刻にするように思われます。もし、自分の回路が期待した過渡応答の仕様を満足しないとしたら、基板の誘電体吸収が影響している可能性を考慮すべきです。

幸いなことに、これには解決する手段があります。コンデンサの誘電体吸収の場合では、その影響を補償するために外部に部品を追加します。重要なことは、寄生的な結合から敏感なノードを分離しているガード電極が、しばしばこの問題を取り除いてくれるということです（スルー・ホール部品ではこれらのガードは基板の両面に設けるべきであることに注意）。先ほど述べたように、低損失の基板誘電材を用いることもできます。

誘電体吸収とは異なるものの、類似するプリント基板の落とし穴としては、実際の回路基板の容量が周波数によって変化することが挙げられます〔参考文献(1)を参照〕。一般に、それは基板容量が回路において全容量のかなりの部分を占めている場合に、ハイ・インピーダンス回路の過渡応答に影響を与えます。10 kHz以下で動作している回路が影響を受けやすくなります。回路基板の誘電吸収と同様に、基板の化学的性質が大きく影響しています。

## 2-4 浮遊容量 (stray capacitance)

二つの導体が互いに接触していなかったり、導電性のスクリーン（ファラデー・シールド）で完全に覆われていない場合には、両者の間に容量が存在します。それにより、どのようなプリント基板でも、全体の回路としては（回路モデルで考慮されているものも、考慮されていないものも）膨大な数のキャパシタが存在することになります。高い周波数での性能が問題になる場合（直流や超低周波回路であっても  $f_L$  の高い素子を使うかもしれません、その場合は高周波での安定性に問題を生じる），この浮遊容量による影響を考慮することが非常に大切になります。

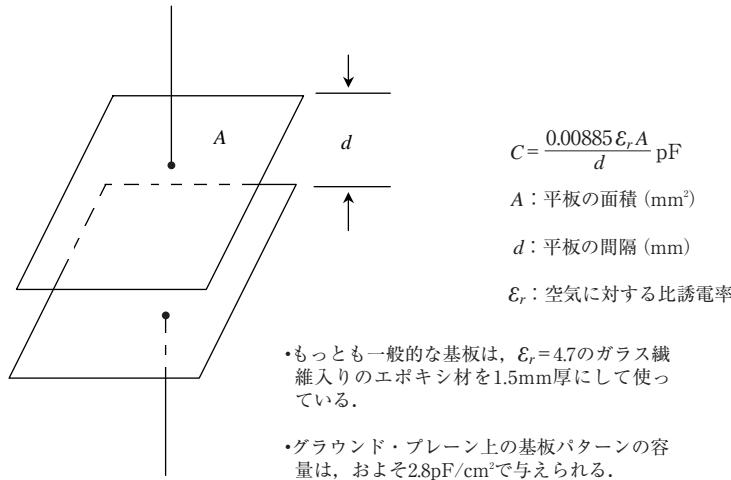

基本的な教科書ならどれも、平行したワイヤ間や、その他の形状での容量を与える式が載っています〔参考文献(9), (10)を参照〕。ここで考慮すべき例は、平行平板コンデンサであり、しばしば基板両面に配置された導体がこの構成になります。図2-22に、この容量を表す概念を示します。

端面での効果を無視すると、面積が  $A \text{ mm}^2$  で、間隔が  $d \text{ mm}$  の、空気との比誘電率  $\epsilon_r$  の媒体内の平行平板の容量は、 $0.00885 \epsilon_r (A/d) [\text{pF}]$  になります。

図 2-22 二つの平行平板間の容量

この式から、一般的な基板材料 ( $\epsilon_r = 4.7$ ,  $d = 1.5 \text{ mm}$ ) について計算をすることができる、基板の両面にある導体間の容量は  $3 \text{ pF/cm}^2$  弱になります。一般に、そのくらいが浮遊容量であり、それらが回路の性能に影響しないように設計しなければなりません。

基板の容量を、個別部品の容量の代わりに使うことも可能ですが、普通の基板材料の誘電特性では性能のよいコンデンサにはなりません。温度係数はかなり高くなり、高周波での  $Q$  が低くなりますので、多くの用途では使用に耐えません。損失の少ないテフロンのような誘電体でできた基板は高価ですが、よいコンデンサが作れます。

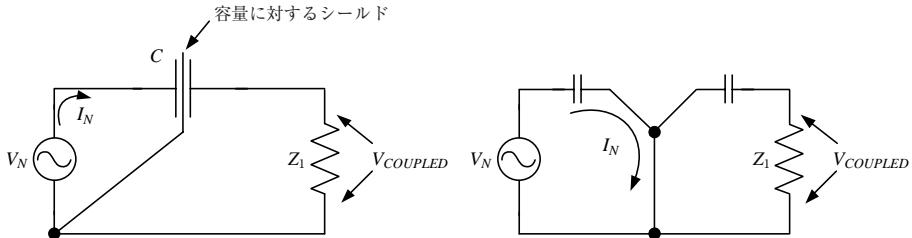

### ● 容量性ノイズとファラデー・シールド

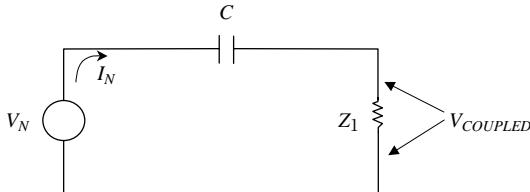

空気であっても真空であっても、誘電体で分けられた二つの導体間には、かならず容量が存在します。片方の電位が変化すると、他方で電荷の移動が起こります。図 2-23 では、この基本モデルを示しています。

何らかの手段によって、 $Z_1$  を流れるノイズ電流を減らすことで、 $Z_1$  に現れるノイズ電圧  $V_{COUPLED}$  を減らすことができます。それらの手段とは、信号電圧  $V_N$  を減らすことであり、関連する周波数を下げるることであり、容量を減らすことであり、あるいは  $Z_1$  そのものを減らすことです。しかしながら、あいにくどの回路定数も自由に変えることができないため、別の手段によって干渉を小さくする必要があります。 $C$  の効果によるノイズ結合を低減する最も良い手段は、ノイズ源と影響を受ける回路との間に、ファラデー・シー

〈図 2-23〉容量結合による等価回路モデル

$Z_1$ ：回路のインピーダンス

$$Z_2 = 1/j\omega C$$

$$V_{COUPLED} = V_N \left( \frac{Z_1}{Z_1 + Z_2} \right)$$

ルドとして知られる接地された導体を挿入することです。これにより、 $Z_1$ を流れるノイズ電流を減少させる効果があり、結果としてノイズ電圧  $V_{COUPLED}$  が小さくなります。

図 2-24 にファラデー・シールドのモデルを示します。図の左側に示したように、結合容量  $C$  の分割を考えることで、シールドの働きが理解されます。図の右側には、 $Z_1$  に現れる結合電圧の正味の影響が示されています。ノイズ電流  $I_N$  は、依然としてシールドを流れるのですが、その大部分は  $Z_1$  に到達することはありません。つまり、 $Z_1$  に現れる結合電圧  $V_{COUPLED}$  が減小することになります。

ファラデー・シールドは、容易に実装できて、多くの場合で有効に働きます。したがって、容量性結合が手におえないような問題になることはまれです。しかし、完全に有効なものにするには、ファラデー・シールドはノイズ源とシールドされた回路の間の電界を完全に遮断しなくてはなりません。またシールドは、変移電流がそのおもとに戻るよう、つまり回路に流れ込んでノイズを発生しないように接続されていなければなりません。

### ●電気的に浮いたシールドの問題

最後に、非常に重要な注意点について述べておきます。それは、ファラデー・シールドとして設けられた導体が電気的に浮いていると、ほとんどの場合、容量が増大してノイズの問題を悪化させてしまうので、決して電気的に浮いた状態のままにしてはいけないということです。

この浮いたシールドの問題の例は、サイド・ブレーズされたセラミック IC パッケージに見られます。これらの DIP パッケージには、小さい正方形のコバルト合金のリッド (lid ; 蓋) が、セラミック・パッケージ上部のメタライズされたリム (rim ; 縁) にろう付

図 2-24 ファラデー・シールドの動作モデル

けされています。パッケージの製造者は、二つの選択肢しか提供していません。メタライズされたリムを、パッケージの四隅にあるピンのどれか一つに接続するか、未接続のままにするかです。

ほとんどのロジック IC では、パッケージの隅のピンがグラウンドになっているので、リッドはグラウンドにつながっています。しかし、多くのアナログ IC では、グラウンド・ピンは隅にないので、リッドが浮いたままで、ノイズを引き寄せるアンテナになっています。そのような回路は、まったくシールドされていないプラスチック DIP パッケージに入れた同じチップよりも、電界ノイズに対して遙かに弱いものになってしまいます。

可能なら、製造メーカーがリッドをグラウンドに落としていないサイド・プレーズされたセラミック IC のリッドを自分でグラウンドに落とすことで、実効的なファラデー・シールドを実装したことになるので、有効な手段となります。これを行うには、リッドにワイヤをはんだ付けします（チップは熱的にも電気的にもリッドとつながっていないので、デバイスがダメージを受けることはない）。リッドへのはんだ付けができないなら、グラウンドに接続したリン青銅クリップや、グラウンド・ピンとリッドの間を導電性塗料でつなぐことで接地できます。

この作業で安全に関する注意事項があります。まず最初に、リッドがどこにも接続されていないことを確認してからグラウンドにつなぎましょう。グラウンドの代わりに、リッドを電源につないだデバイスもたまにあるからです。

IC のボンディング・ワイヤ間の干渉は重要な関心事ですが、ボンディング・ワイヤ間にファラデー・シールドを入れるのは現実的ではありません。ボンディング・ワイヤと関係するリード・フレーム間の浮遊容量の代表的な値は 0.2 pF であり、一般的な実測値で 0.05 ~ 0.6 pF の間です。

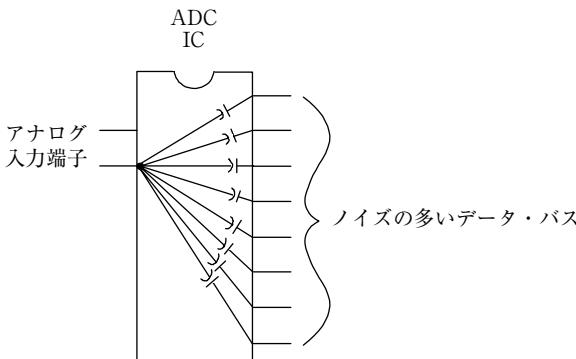

図 2-25 高速データ・バスにつながった高速 A-D コンバータではディジタル・ノイズがアナログ・ポートに結合して性能が制約される

### ●ロジック・ノイズに対して A-D コンバータにバッファを付ける

もし、高い分解能の A-D/D-A コンバータを、 $2 \sim 5 \text{ V/ns}$  のエッジ速度のロジック・ノイズが伝播する高速データ・バスにつなぐとしたら、このノイズはデバイスの浮遊容量を伝わって、コンバータのアナログ・ポートに簡単に結合してしまいます。データ・バスが生きている場合はつねに、許容できない量のノイズがアナログ・ポートに容量的に結合して、性能が著しく劣化することになります。

この現象を図 2-25 では、パッケージの多くの浮遊容量により A-D コンバータのデータ・バスからアナログ入力にロジック・ノイズ信号が結合される様子として示しています。

IC デバイス内部で起きる問題に対しては、これまで述べてきた技術では改善できません。この問題は、このほかにもシングル・チップにアナログとディジタルが混在した広帯域のモノリシック・ミックスド・シグナル IC から得られる性能に制約を与えます。幸いにも、この結合ノイズの問題は、データ・バスをコンバータに直結しないことで、簡単に避けることが可能です。

直結する代わりに、図 2-26 のように CMOS ラッチ/バッファをコンバータとバスとのインターフェースとして使います。これで、CMOS バッファ IC がフェラーリ・シールドとして働き、ディジタル・バスからのノイズの結合を劇的に減少させます。この解決策は、費用とボード面積を必要とし、(ほんの少し)信頼性を低下させ、電力消費を増やし、設計を複雑にします。しかし、まさしくコンバータの信号対ノイズ比を改善してくれます。設計者は個々の事例について、その必要性を判断しなくてはなりませんが、一般的に強く推奨できる手法です。

図2-26 出力にCMOSバッファ・ラッチをつけた高速A-Dコンバータはディジタル・データ・バスのノイズの影響を受けてくる

### ◆参考文献◆

- (1) W. Doeling, W. Mark, T. Tadewald, and P. Reichenbacher, "Getting Rid of Hook: The Hidden PC-Board Capacitance", Electronics, October 12, 1978, pp.111 ~ 117.

- (2) Alan Rich, "Shielding and Guarding", Analog Dialogue, Vol.17, No.1, 1983, p.8.

- (3) Ralph Morrison, Grounding and Shielding Techniques in Instrumentation, 3rd Edition, John Wiley, Inc., 1986, ISBN : 0-471-83805-5.

- (4) Henry W. Ott, Noise Reduction Techniques in Electronic Systems, 2nd Edition, John Wiley, Inc., 1988, ISBN : 0-471-85068-3.

- (5) Paul Brokaw, "An IC Amplifier User's Guide to Decoupling, Grounding and Making Things Go Right for a Change", Analog Devices AN202.

- (6) Paul Brokaw, "Analog Signal-Handling for High Speed and Accuracy", Analog Deices AN342.

- (7) Paul Brokaw and Jeff Barrow, "Grounding for Low- and High-Frequency Circuits", Analog Devices AN345.

- (8) Jeff Barrow, "Avoiding Ground Problems in High Speed Circuits", RF Design, July 1989.

- (9) B. I. & B. Bleaney, Electricity & Magnetism, Oxford at the Clarendon Press, 1957, pp.23, 24, 52.

- (10) G. W. A. Dummer, H. Nordenberg, Fixed and Variable Capacitors, McGraw-Hill, 1960, pp.11 ~ 13.

**謝辞：**

この章の一部分は、Analog Dialogue 17-2 (1983) で発表された Doug Grant 氏と Scott Wurcer 氏による "Avoiding Passive Component Pitfalls" からの転載です。

# 第3章

## OPアンプ用の電源システム

Walt Jung, Walt Kester／訳：額田忠之

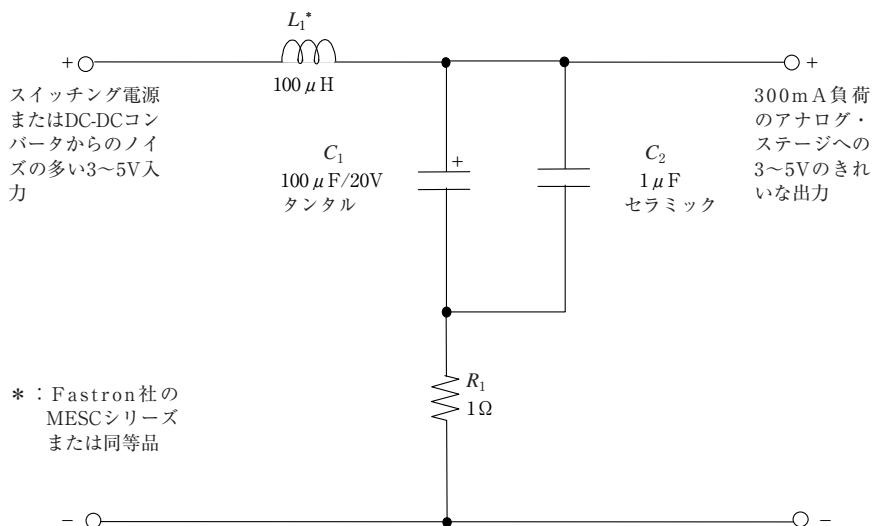

OPアンプ回路の電源は、従来では良好に安定化された低ノイズのリニア・レギュレータから供給されていました。このようなタイプの電源システムは、電力変換の効率が中程度以下であることが特徴的です。リニア型の安定化電源は、発生する放射性のノイズ成分の少なさでは通常はずば抜けて優れています。非常に単純なシステムの設計であれば、そのようなよく知られた方法を継続していても、効率が良く副作用が最低限度のものを作ることができます。

しかし、設計という仕事はそれほど単純なものではありません。最近のシステムでは、リニア型の安定化電源を使用する場合でも、複数の出力電圧レベルや負電圧が必要になることがあります。このことは、DC-DCコンバータの使用が効率的であることを意味しますが、不幸なことに出力ノイズは大きくなってしまいます。

本章では、OPアンプ応用システムの電源設計について述べます。この際、最もよく使われていると思われる電源安定化技術について考察します。一次的な直流電源としては、交流電源を整流して平滑化したもの（商用電源の利用）、バッテリ（電池）によるもの、スイッチング・レギュレータによるものなどがあります。スイッチング・レギュレータによるものは、バッテリおよび商用電源を整流した電源の双方から給電することができます。

表3-1に示すように、リニア型の電源安定化方式は、あらゆる場合において最適な方法として一般的に推奨されています（最初の◆）。しかしながら、場合によっては完全なリニア型からスイッチング型までの安定化方式の間で、ある程度のハイブリッド化を必要とすることもあります（2番目の◆）。このことは、効率またはその他の種々の理由によります。

高精度アナログ回路に電源を供給するときには、スイッチング型の安定化電源を使用する場合には、ノイズ低減が設計上の問題になることがあります。したがって、本章では、スイッチング電源を使用する際のノイズを最小限度に抑えることに焦点を合わせます。

〈表3-1〉OPアンプ用電源システムでの安定化の優先度

- ◆高性能なアナログ電源システムでは、リニア型の安定化電源を使用する。電力は以下のいずれかから供給される。

- ・ACライン

- ・バッテリ・システム

- ・DC-DCコンバータ

- ◆可能な場合には、スイッチング型の安定化電源の使用は避ける。避けられない場合には下記の対策を取る。

- ・ノイズ抑制技術を使用する

- ・品質の高いレイアウトと接地を使用する

- ・EMIについて考慮する

### 3-1 リニアICによる安定化

電源用のリニアICレギュレータは、長期にわたって電源システムの標準的な構成要素でした。開発された当時は、5V動作のデジタル回路用の電圧安定化用でしたが、3～24Vの標準電圧に拡張され、また出力電流レベルも100mA以下だったものが5A以上を取り扱えるようになってきています。優れたいくつかの理由があったため、リニアICによる電圧安定化回路は、当初から貴重なシステム・コンポーネントでありつづけてきました。前述のように、基本的な理由はスイッチング型の安定化電源と比べるとノイズが少ないということです。その他の理由は、個別部品で安定化回路を構成する場合と比べて部品点数が少ないと、全体的に単純であることがあげられます。しかし、電力損失が大きいため、このリニア型の安定化回路は非効率的であることも知られていました。初期の世代のデバイスは（なかには現在でも入手可能なものもある）、安定化された出力電圧よりも2V以上も高い入力電圧を必要としたので、電力損失が大きかったのです。

しかしながら最近、入出力の電圧差が小さくてすむリニアICレギュレータが開発されました。この入出力電圧差は、ドロップアウト電圧としてよく知られていますが、そのことから低ドロップアウト・レギュレータ（Low DropOut regulator）と呼ばれており、略してLDOと表記されることもあります。ドロップアウト電圧( $V_{MIN}$ )は、レギュレータの出力電圧が2%低下する最小の入出力電圧差として定義されます。例をあげると、入出力電圧差が0.5Vの条件下で、公称値5.0VのLDO出力が4.9V(-2%)に低下した場合には、このLDOレギュレータのドロップアウト電圧は0.5Vとなります。

ドロップアウト電圧は、リニア型の安定化電源の電力効率に決定的（あるいは重大）な影響を及ぼします。レギュレータの入出力間電圧を低く保ったまま安定した出力電圧を維持できれば、結果としてレギュレータが消費する電力を少なくすることができます。レギュレータのドロップアウト電圧が小さいということが、このことに関する鍵となります。

ドロップアウト電圧が小さければ、入力電圧が低くても安定化を維持できるからです。LDO レギュレータの性能面での特徴は、より多くの有効な電力を負荷に供給でき、レギュレータ内で発生する熱が少ないことです。LDO レギュレータは、携帯型コンピュータや携帯電話などのように、バッテリから安定した電圧を供給する必要のある電源システムでは鍵となるデバイスです。これらの電源システムでは、安定化出力をバッテリの放電曲線上の低いほうに設定したいからです。また、従来の商用電源から電力を供給されている DC 電源では、LDO レギュレータの採用により電源トランジスタの 2 次電圧を低くすることができ、電圧低下時でもシステムのシャットダウンの危険性を減らすことができ、また発熱も少くなります。

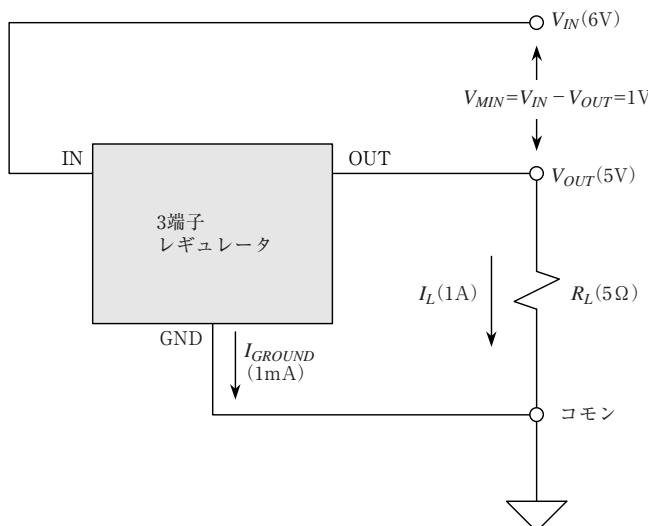

### ●リニア型電圧レギュレータの基礎

LDO レギュレータについて理解するまえに、3 端子リニア・レギュレータの基礎について簡単におさらいしておくことにします。現在使用可能な一般的な 3 端子レギュレータのほとんどは、ポジティブ・レグ (positive leg) の直列型のレギュレータです。それは、正の非安定化入力と直列に接続されるパス・デバイスにより、安定化された出力電圧を制御するという意味です。また、数は少ないのですが、ネガティブ・レグ (negative leg) の直列型のレギュレータもあり、これらはポジティブ・レグのデバイスとコンプリメンタリに動作します。

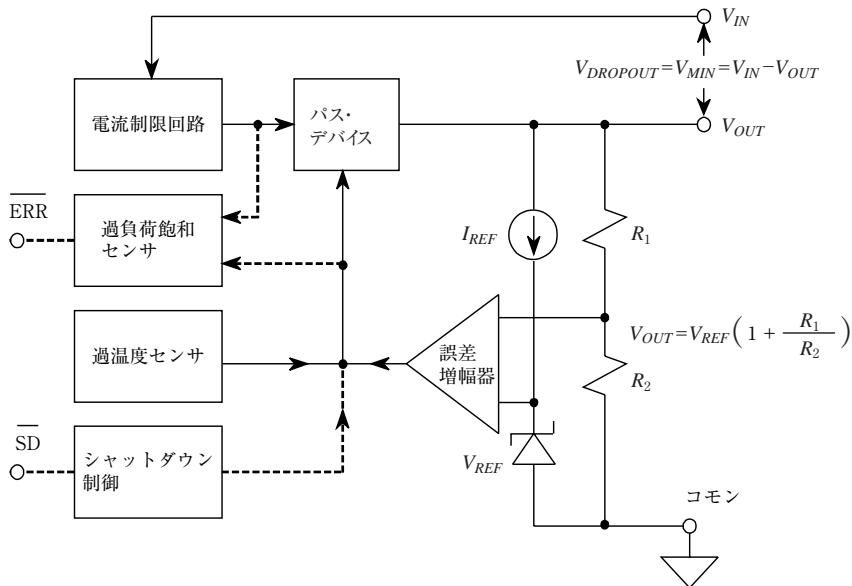

〈図 3-1〉3 端子レギュレータの基本的な構成（正電圧、負電圧ともに同じ）

3端子レギュレータの基本的な構成を図3-1に示します。基本的な機能という意味では、多くの標準的なレギュレータは図に示すように、3端子型でシリーズ・モードで動作します。この図からわかるように、3本のI/O端子は  $V_{IN}$ , GND(またはコモン), および  $V_{OUT}$ です。このレギュレータのブロック図では電圧の極性が示されていませんが、基本的には正電圧レギュレータです。ですが、負電圧レギュレータとしても通用します。両者とも動作原理は同じであり、端子もコモン、入力および出力です。

動作時には、二つの電力成分がレギュレータ内で消費されます。そのうちの一つは  $V_{IN} - V_{OUT}$  と  $I_L$  の関数であり、もう一つは  $V_{IN}$  と  $I_{GND}$  の関数です。通常は、これらのうちで前者が支配的です。動作を分析すれば、ドロップアウト電圧  $V_{MIN}$  が減少することで、レギュレータは入力電力の多くの部分を負荷に供給できるため、効率よく、低温度で省電力動作ができることがわかります。最近のLDOタイプのレギュレータは、主にこの点をアピールしています[参考文献(1)参照]。

図3-2に示す代表的な電圧レギュレータのブロック図の内部を詳細に調べてみると、いろいろな構成要素があることがわかります。すべてのレギュレータには、実線で接続された機能要素が含まれています。破線で示してある接続はオプションであり、3本以上のI/Oピンが使用できる場合に実装されます。

〈図3-2〉代表的な電圧レギュレータの機能構成図

動作時には、基準電圧ブロックは安定な電圧  $V_{REF}$  を生成します。この  $V_{REF}$  はほとんどの場合、シリコンのバンド・ギャップ電圧（約 1.2 V）を基準にしています [参考文献 (2) 参照]。このため、5 V 程度の低い入力から 3 V 以上の出力電圧を得ることができます。この電圧は、誤差増幅器の一方の入力を駆動し、誤差増幅器のもう一方の入力は分圧器  $R_1-R_2$  に接続されています。誤差増幅器はバス・デバイスを駆動し、バス・デバイスは出力電圧を制御します。この結果、得られる安定化電圧は次式で簡単に表すことができます。

## ●パス・デバイス

パス・デバイス (pass device) は、レギュレータの主要部分であり、ここで解説するタイプのほとんどすべてのレギュレータで性能に強い影響力をもっています。なかでも最も顕著なのがドロップアウト電圧、つまり  $V_{MIN}$  です。インバート・モードのパス・トランジスタを使用すると、パス・デバイスを効果的に飽和領域まで動作させることができます。そこで発生する電圧損失を最低限にすることができます。したがって、この要因により、最も好ましい LDO レギュレータ用のパス・デバイスは、PNP 型のバイポーラ・トランジスタか PMOS 型の FET となります。これらのタイプのデバイスを使用すると、LDO 動作に必要な  $V_{IN} - V_{OUT}$  のレベルを最も低くすることができます。それに対し、NPN 型のバイポーラ・トランジスタは、低ドロップアウトという観点から見るとパス・デバイスとしては不十分であると言わざるをえません。とくに、ダーリントン接続をしたときにはこのことが顕著になります。

標準的な電圧固定型の IC レギュレータのアーキテクチャは、パス・デバイスに関するこの点を説明してくれています。例をあげると、電圧固定型の LM309 (5 V レギュレータ) や、7805, 7815 などの派生製品 (および、それらの種々の低電流および中程度の電流製品) は、ドロップアウト電圧という観点から見ると貧弱です。これらのレギュレータの設計ではダーリントン接続のパス・デバイスが使用されているため、低ドロップアウトではなく (通常約 1.5 V), 低静止電流でもありません (約 5 mA).

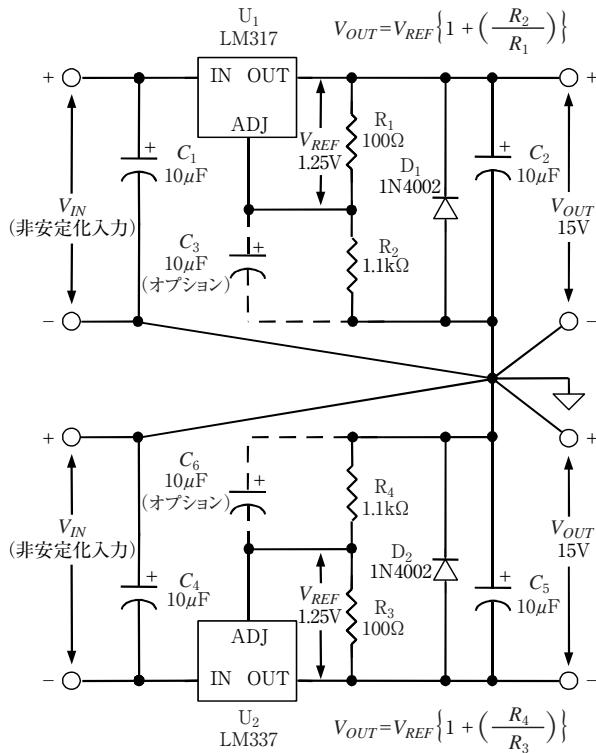

#### ●可変電圧 IC を使用した±15V レギュレータ

基準電圧の技術と3端子レギュレータ技術が後に発展して、電圧可変レギュレータが開発されました。この考え方を使用した最初のICはLM317正電圧レギュレータでした。このデバイスは、1.25 V の固定した基準電圧を発生し、この電圧は IC の  $V_{OUT}$  ピンと ADJ ピンの間に現れます。外部の調節用抵抗器により、所望の出力電圧を設定します。

調節できる範囲は 1.25 V ~ 30 V です。これとコンプリメンタリなデバイス LM337 も同様な動作をし、負の電圧を安定化します。

標準的な電圧可変 3 端子レギュレータを使用して、±15 V のリニア型電源を実現した応用例を図 3-3 に示します。この回路は、一般的な OP アンプ用の電源レールに電力を供給することができます。この回路は、たとえば 7815 や 7915 などの標準の固定電圧型のレギュレータ IC を使用した同様な回路と比べると、ライン・レギュレーション性能が良好です。しかしながら、電力効率という観点から見ると、この回路は卓越しているとは言えません。この回路で使用している IC は、動作時に 2V 以上のヘッド・ルーム（動作電圧の余裕）が必要だからです。

この回路の上半分では、LM317 電圧可変レギュレータが使用されており、 $R_2$  と  $R_1$  の定数は上部の出力端子に 15 V の出力が得られるように選択します。必要であれば、図中の  $V_{OUT}$  を示す式に従って他の出力電圧に設定することも容易にできます。このとき、抵抗

〈図 3-3〉電圧可変型レギュレータ IC を使用した代表的な±15 V、1 A リニア型安定化電源

$R_1$  の値は変更してはいけません。この抵抗は、レギュレータの最小ドレンが 10 mA 以上になるように設定されているからです。

この回路では、コンデンサ  $C_1$  と  $C_2$  はタンタル型にする必要があり、 $R_1$  と  $R_2$  は金属皮膜抵抗器にする必要があります。 $C_3$  はオプションですが、出力電圧のノイズ・レベルを最小にしたい場合には、取り付けを強く推奨します。通常は逆バイアスとなるダイオード  $D_1$  は保護用の出力クランプで、片側の電源が故障したような場合に出力電圧が反転してしまうのを防ぎます。この回路は、AC 電源を整流して平滑したような非安定化電源  $V_{IN}$  で動作します。 $V_{IN}$  の極性は図に示されています。出力電流は、適切な電流容量をもったレギュレータ IC を選択することによって決定します。

負電圧側の回路では、LM317 の姉妹品である LM337 を使用しています。したがって、この回路の下部は上部と同じ動作をし、一番下の出力端子に -15 V が出力されます。LM337 の出力電圧の調節は LM317 の場合と同様に、抵抗  $R_4$  と  $R_3$  で設定します。 $R_4$  を電圧設定用に使用し、 $R_3$  の抵抗値は変更してはいけません。同様に、 $C_6$  はオプションですが、ノイズを最小にしたい場合には取り付けを推奨します。

### ●低ドロップアウト・レギュレータのアーキテクチャ

ダーリントン接続または単一の NPN パス・デバイスによる従来の 3 端子レギュレータに対し、LDO レギュレータでは、電圧の閾値がより低いパス・デバイスを使用しています。この基本的な動作の違いにより、LDO レギュレータは、 $V_{MIN}$  が 100 ~ 200 mV 程度での効率的な動作が可能になっています。システム内での使用という観点から見ると、この点は相当重要な動作時の利点となります。

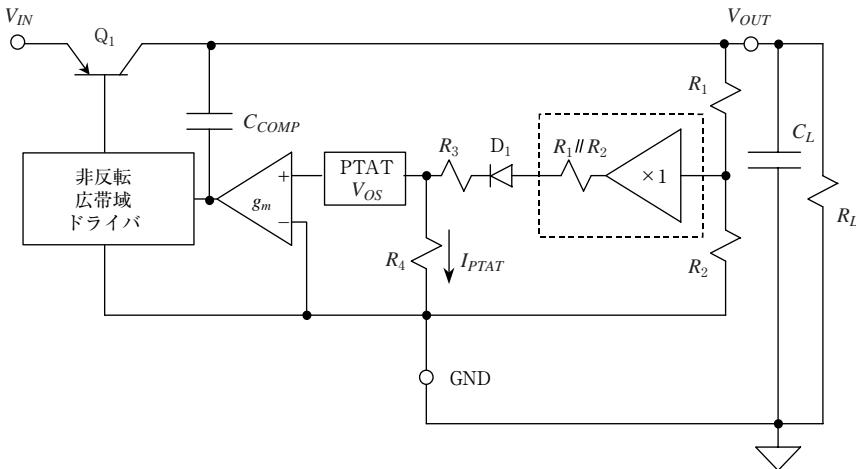

いくつかの重要な LDO レギュレータの機能を効果的に実現しているものとして、アナログ・デバイセズ社の「anyCAP シリーズ」の製品群があります。この ADP330x シリーズは、容量の大きさと ESR (等価直列抵抗) の両面において、出力コンデンサによる影響を受けないため、このような名称が付けられています。アナログ・デバイセズ社の「サーマル・ココストライン」などの高電力効率パッケージ (またはその他の熱特性が改善されているパッケージ) で供給され、スタンダードアローン LDO としても LDO コントローラとしても (外付けの PMOS FET を使用する) 利用できます。また、これらの固定出力範囲は 1.8 ~ 5 V と広く、定格出力電流は最大 500 mA です。ユーザが出力電圧を調節できるバージョンも用意されています。このファミリの単純化されたブロック図を図 3-4 に示します。

ADP330x LDO シリーズの大きな特徴の一つは、高利得バーチカル型 PNP パス・デバイスを使用していることであり、これにより出力電流 200 mA 以下ではドロップアウト電圧は 1 mV/mA 程度に抑えられています。

回路の動作時には、 $R_1$  と  $R_2$  の比で決定されるゼロ出力インピーダンス分圧器の出力が

図 3-4 ADP330x における anyCAP LDO アーキテクチャには、直流的性能と交流的性能の両面に利点がある

$V_{REF}$ となります。図では抽象的に示していますが、 $V_{REF}$ となるのは  $R_1/R_2$  の分圧器を入力とするゲイン 1 のバッファ・アンプ（破線内）の出力です。この基準電圧は直列に接続されている  $R_1 \parallel R_2$ （破線内）に入力され、実際の部品  $D_1$ 、 $R_3$ 、 $R_4$  などに入力されます。このレギュレータの出力電圧は、次の式で表されます。

ADP330x シリーズの個々のデバイスでは、標準的な出力電圧として 1.8 V, 2.5 V, 2.7 V, 3.0 V, 3.2 V, 3.3 V, 5.0 V の出力電圧をラインナップするように  $R_1$  と  $R_2$  が調整されています。レギュレータは、 $R_1$  と  $R_2$  からなる通常の分圧器の働きと同じように、誤差増幅器全体がオフセット電圧  $V_{REF}$  をもっているかのようにふるまうのです。

このような ADP330x シリーズの性能改善には大いに価値がありますが、さらにすばらしい改善は AC 関連の性能 있습니다. 容量性の負荷による不安定性は、LDI レギュレータを簡単に応用する際の大きな妨げになります. 増幅器のレスポンス・ポールの変動に対する耐性を上げる一つの方法は、ポール・スプリッティング (pole splitting) と呼ばれる周波数補償技術を使用することです. 図 3-4 の回路では、 $C_{COMP}$  がポール・スプリッティング・コンデンサとして機能し、バッファリングされているため  $C_L$  に依存しないシングル・ポール応答を実現しています. その結果、周波数応答はレギュレータ内部の補償機能によ

る制御が支配的となり、負荷容量  $C_L$  の値や  $ESR$  の影響を比較的受けにくくなっています。

この特徴により、事実上どのようなタイプの出力コンデンサでも使用できる設計が可能になっています。負荷容量  $C_L$  は  $0.47 \mu F$  程度に小さくでき、多層セラミック・コンデンサ (MLCC) 型でもよいため、レギュレータ回路全体の物理的なサイズを非常に小さくすることができます。

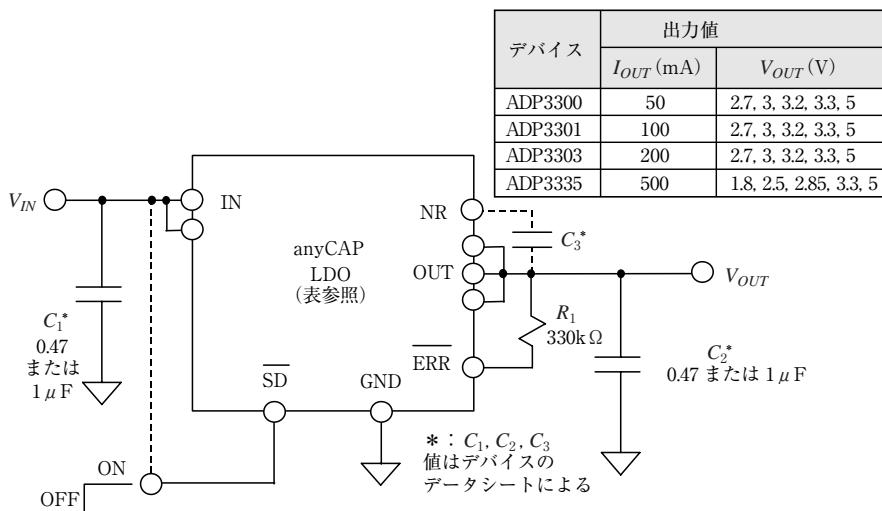

### ● 固定電圧型の 50/100/200/500 mA 出力 LDO レギュレータ

ADP330x シリーズの固定電圧デバイスに共通な、レギュレータ応用回路の基本構成を図 3-5 に示します。それぞれの端子の機能や内部動作については後述します。この概略のブロック図を特定の電流/電圧仕様に適合させるためには、図中の表から出力電流が要求に合うデバイスを選択してください。次に、表にあるパート番号サフィックスによって出力電圧を選択してください。

この回路は一般的なものであり、共通点を示したものです。例をあげると、ADP3300 は 50 mA の基本 LDO レギュレータであり、図中の表に示されている固定出力電圧用に設計されています。実際の ADP3300 デバイスの発注時の型番は ADP3300ART-YY となります。ここで、“YY”は電圧を指定するサフィックスであり、表にある電圧に対して 2.7, 3, 3.2, 3.3, 5 となります。型番の “ART” 部分はパッケージ (SOT23, 6 リード) を指定します。この回路から 5 V を得るために、ADP3300ART-5 を使用します。型番の構成

図 3-5 50 mA ~ 500 mA のデバイスを選択するのに役立つ LDO レギュレータの基本回路

(固定電圧は表から選択する)