# パイプライン型のADCって、どんなもの？

アナログ電子回路コミュニティのスレッドから

## 質問

A/Dコンバータ（ADC）について記された書籍などを読んでいると、シグマ・デルタ（ΣΔ）型と逐次比較（SAR）型に関する記述がほとんどです。

実際の製品としてはパイプライン型のADCも数多く存在するようですが、この方式について詳しく説明された資料はあまり見当たりません。

パイプライン型のADCとはどのようなものなのでしょうか。そして、どのような点に気を付けて使用すればよいのでしょうか？

「OK」ボタンをクリックしてください。すると、製品ごとに、「Pipelined」、「SAR」、「Sigma-Delta」といった変換方式名が表示されます。

ちなみに、この一覧表では項目の追加／削除だけでなく、「分解能が12ビット以上」、「サンプリング・レートが80MSPS以上」といった条件を設定して絞り込みを行うことも可能です。

変換方式にかかわらず、ADCを使用する場合に最も注意を払うべき個所は入力部でしょう。実際、書籍などを見ると、「アンチエイリアシング（折返し誤差防止）フィルタ」（以下、AAF）や「サンプル&ホールド回路」などについて詳細に解説されているはずです。

AAFの必要性については、サンプリング・システムでは、必ず折返しが発生するということを理解しておく必要があります。それを除去したければ、SAR型でもΣΔ型でもパイプライン型でもAAFが必要になります。

注意が必要なのはΣΔ型のADCについてです。この種のADCの場合、デジタル・フィルタを内蔵しており、それによって折返しを除去できると誤解されている方がいるからです。通常のΣΔ型ADCでは、スイッチド・キャパシタによって信号をサンプリングし、その段階で折返しノイズが発生します。それらが発生する帯域によってはデジタル・フィルタを使っても簡単には除去できません。そのため、ΣΔ型ADCの入力部にもAAFを外付けで配置するべきです。

ただ、ΣΔ型のADCでは、通常はオーバーサンプリング技術が併用されるので、AAFに求められる要件が緩和されます（緩やかな減衰特性的ものでも事足りるということです）。一方、サンプル&ホールド回路については、現在では、変換方式にかかわらず、ほぼ外付けする必要はありません。パイプライン型のものも含めて、最近のADCの多くはサンプル&ホールド回路を内蔵しているからです。

このように、変換方式にかかわらず、あらゆるADCに共通して当てはまる事柄があります。それらに加え、パイプライン型ADCの仕組みや、それによって生じる独特の注意点について把握すれば、どのような点に注意して使えばよいのか理解しやすくなります。

そこで、以下ではパイプライン型ADCについて詳細に解説していきます。その最初のステップとしては、フラッシュ型のADCを取り上げます。パイプライン型のADCでは、フラッシュ型のADCを内部ブロックとして使用するからです。

## 回答

パイプライン型というのは、SAR型やΣΔ型と並ぶADCの主要なアーキテクチャ（変換方式）です。特に、高速、高分解能を特徴とする製品の多くは、パイプライン型で実現されています。ΣΔ型でもSAR型でもパイプライン型でも、ADCに関する一般的な注意事項は同じように適用する必要があります。それに加えて、それぞれの方式に特有の注意点などにも配慮しなければなりません。

ところが、質問者の方が指摘しているように、パイプライン型ADCの原理や使用上の注意点などについて詳しく説明した資料は意外に少ないようです。そこで、本稿ではパイプライン型のADCについて要点をまとめてみます。

そもそも、ADC製品のデータシートを見ても、その冒頭に「この製品はパイプライン型のADCである」ということが大書されているとは限りません。

そこで、まずは各製品がどのような変換方式を採用しているのかを調べる方法を紹介しておきます。アナログ・デバイセズのADC製品の場合、変換方式については、製品選択用の一覧表で確認することができます。ここでは、「[高速ADC > 10MSPS](#)」の表を例にとります。この表は、サンプリング・レートが10MSPS（メガサンプル/秒）以上の高速ADC製品を効率良く選択するためのものです。

その左上隅を見ると、「パラメータを選ぶ」というメニューがあります。これをクリックすると表示される数々の項目のうち、「Device Architecture」のチェック・ボックスにチェックを入れて

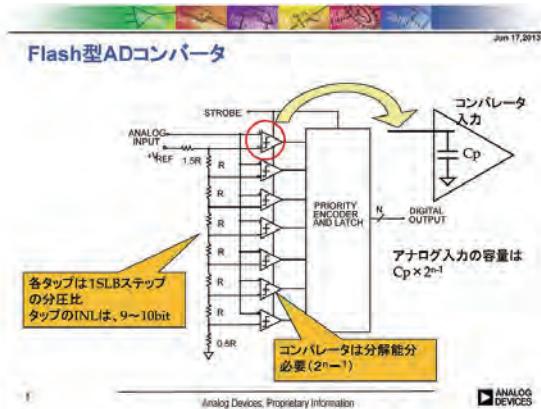

## フラッシュ型の ADC

フラッシュ型ADCの仕組みは単純です。ごく基本的なA/D変換の原理そのものに従っていると表現することができます。図1のように、リファレンス電圧（基準電圧であり、フルスケール電圧でもあります）を、分解能の分だけ用意した抵抗列で分圧します。

図1. フラッシュ型のADC

そして、各ノードの値をコンパレータ（電圧比較器）に入力します。ここでは、分解能が8ビットのケースを考えます。その場合、255個 ( $2^8 - 1$ ) の抵抗とコンパレータが必要になります。それらのコンパレータには入力電圧が並列に入力されます。すると、いちばん下のコンパレータから、入力電圧と同じレベルのコンパレータまでの出力がハイになります。例えていうなら、温度計のような動作です。このときのコンパレータからの出力をデコードし、8ビットのデジタル値を生成します。このA/D変換にかかる時間は、セトリングに要する時間などを除けば、ほぼコンパレータの反応速度だけで決まります。つまり、高速のコンパレータを使用すれば、非常に高速のADCを実現することが可能です。これがフラッシュ型のADCです。この種のICは、高速のデジタル・オシロスコープでよく使われています。

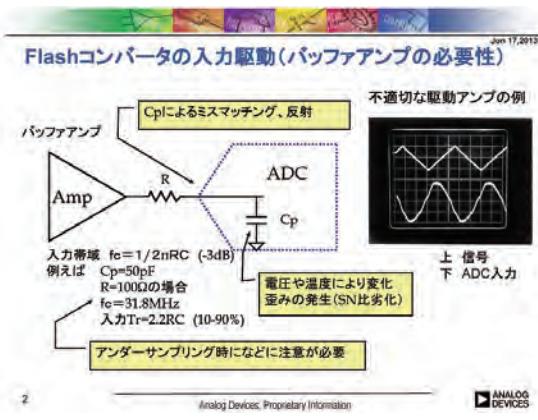

フラッシュ型のADCにおいて注意すべき事柄としては、コンバーラータを並列に接続することから入力容量が非常に大きくなる点が挙げられます。それが原因で生じる歪みを抑えるためには、アナログ信号の入力用に強力なバッファ・アンプが必要になります。図2の右上の写真は、あえて非力なバッファ・アンプを使用した場合のADCへの入力波形です。もともとの信号は三角波であったのに、適切に駆動しきれていないことがわかります。

図2. 強力なバッファ・アンプの必要性

フラッシュ型ADCの特徴を、以下にまとめておきます。

- ・最も高速に動作します。数GSPS以上に対応するものもあります。

- ・任意のタイミングでサンプリングを実施できます。バースト動作やランダム動作などに対応可能です。

- ・入力負荷が非常に重いので、強力なバッファ・アンプが必要になります。

- ・多くの電力を消費します。

- ・分解能を高めるのは容易ではありません（10ビット程度まで）

- ・ $\Sigma\Delta$ 型のADCやサブレンジング型（後述）のADCの内部エンコーダとして多用されています。

- ・ADC製品の内部回路としては広く使われていますが、フラッシュ型ADCというくくりの単体製品は少なくなりつつあります。

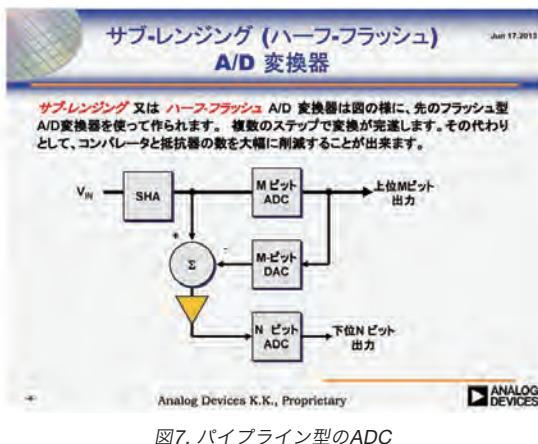

## サブレンジング型の ADC

フラッシュ型ADCの高速性は大きな魅力です。しかし、上記のとおり弱点も存在します。特に分解能を高めようとすると、コンパレータの数が2乗で増えていく点は非常に大きなネックです。

例えば、分解能を12ビットに高めたい場合、コンパレータは4095個も必要になります。これは、ICとして実装するうえでは非現実的な数です。この部分を改善し、高速、高分解能のA/D変換を実現したのが、サブレンジング型ADCです。そして、このサブレンジ型ADCを応用したものがパイプライン型のADCです。サブレンジ型のADCでは、フラッシュ型ADCほどの高速性は得られません。しかし、高い分解能（12～16ビット）と十分に高い変換速度（2GSPS～）を実現できます。

図3. サブレンジング型のADC

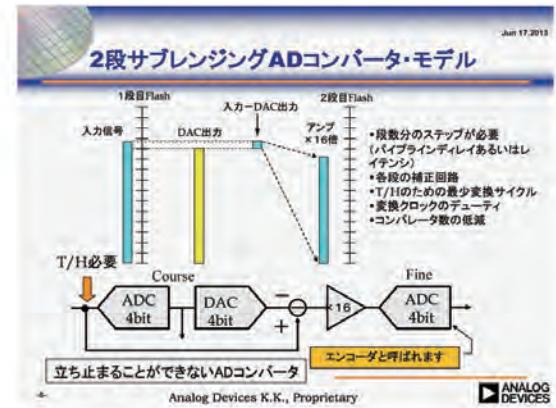

図3に示したのがサブレンジ型ADCのブロック図です。この例では、2つのADCと1つのDACがICの内部ブロックとして使われています。

この回路では、まず1段目のADC（図ではMビット）によって入力信号をA/D変換します。その結果として得られたデジタル値をD/A変換してアナログ信号に戻し、元の信号から差し引くという処理を行います。その引き算の結果を再び2段目のADC（図ではNビット）でデジタル値に変換しています。

単純に言えば、上位ビット用のADCと下位ビット用のADCで得られた結果をつなぎ合わせて、高い分解能のデータを作り出しているということです。これらIC内部のADCはフラッシュ型のADCによって実現されています。

この方式による変換の詳細を図4に示しました。図中の左側にある水色の部分がもともとのアナログ入力信号です。1段目の

ADC（4ビット）による変換結果は、信号を16段階でデジタル化したものになります。

図4. サブレンジング型ADCによる変換処理の詳細

そのデジタル値を4ビットのDACに入力すると、黄色の部分のアナログ値が得られます。このアナログ値を元のアナログ入力信号から引くと、1段目のADCによる変換誤差に当たる信号が得られます。

これは、1段目のADCの1 LSB以下のアナログ値であるはずです。その値を、例えばアンプで16倍し、2段目の4ビットADCに入力してA/D変換を実施します。1段目で得られた4ビットのデータと2段目で得られた4ビットのデータをつなげば、A/D変換全体

の結果として8ビットのデータが得られます。

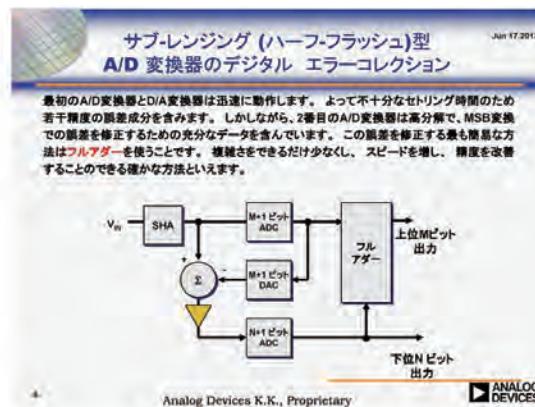

ただ、現実の回路では、1段目と2段目の結果がきれいにつながることは少なく、多少のずれが生じます。これを補正するのがエラー・コレクション回路です。図5、図6で説明していますが、各ADC/DACのビット数に余裕を持たせ、それをつなぎの部分で生じるずれの補正に使用します。この場合も、各ADCとしては、フラッシュ型のものが使われます。

サブレンジング型の最大の特徴は、フラッシュ型に比べてコンパレータと抵抗の数を圧倒的に減らすことです。例として、分解能が8ビットのフラッシュ型ADCと同8ビットのサブルレンジング型ADCを比較してみます。前者に必要なコンパレータ、抵抗の数は、それぞれ255個、256個です。それに対し、後者では、それぞれ30個、32個で済みます。このことは、チップのサイズ(コスト)や消費電力の面で大きなメリットになります。サブルレンジング型のそれ以外の特徴についてまとめると以下のようになります。

- ・フラッシュ型と比較して、それほど複雑ではなく、消費電力も多くはなく、適度な分解能と速度（12ビット以上、50MSPS以上）を実現できます。

- ・内蔵するDACのセッティング時間によって速度が制限されるので、フラッシュ型と比べると最高速度に限界があります。

- ・ADC全体としての精度は1段目のADCの変換精度に大きく依存します。1段目のADCがMビット、2段目のADCがNビットの分解能であるとすると、1段目のADCにはM + Nビットの精度が必要になります。

- ・変換速度には下限値もあります（後述）。

### エラー・コレクションの仕組み

図5

図6

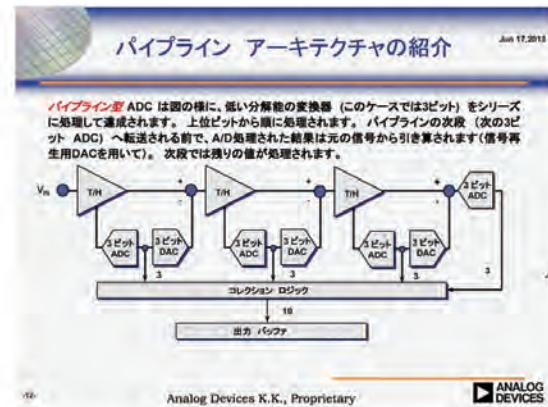

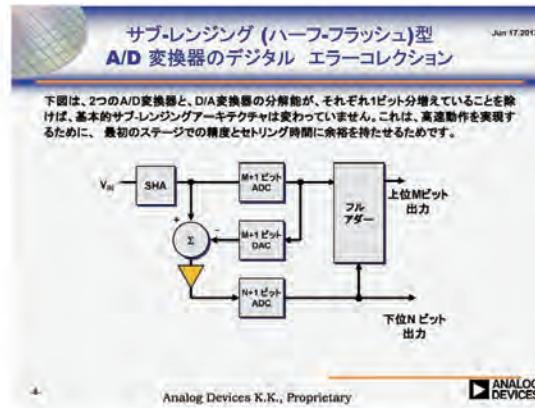

## パイプライン型のADC

先述したように、サブレンジング型では、エラー・コレクションを適用することで、より分解能の高いADCを実現します。ただ、10ビット、12ビット、あるいはそれ以上の分解能のADCを実現したい場合、サブレンジング型ADCのブロックが1つでは足りなくなります。

そこで、図7に示すように、いくつかのブロックを直列に接続して多ビット化を実現します。これがパイプライン型ADCと呼ばれるものです。図7の場合、先ほどのサブレンジング型のブロックが3段、LSB側の部分にフラッシュ型ADCが1つ使用されています。各ブロックは3ビットに対応するので、そのままつなげば12ビットになるはずです。ただ、実際にはエラー・コレクションに下位のビットを使用します。そのため、この例の場合、ADC全体としての分解能は10ビットになります。

図7. パイプライン型のADC

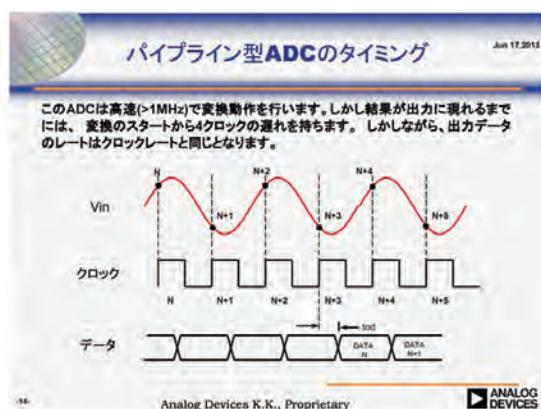

パイプライン型の動作において、各段は、変換が終わって次の段へデータを引き渡せば、全体の変換終了を待っている必要はありません。つまり、各段は次の入力を変換する動作に即座に移行できます。その場合、各段は、クロックごとに変換結果を次の段に引き渡すことになります。したがって、全体のデジタル出力を得るには、1つのクロックではなく、いくつかの変換クロックを入力する必要があります（図8）。

図8. パイプライン型ADCの動作タイミング図

このタイプのADCのデータシートには、この処理においてどれだけのパイプライン・ディレイ（レイテンシ）が生じるかが必ず規定されています。

パイプライン型ADC内部のブロック間ではアナログ信号の引き渡しが行われます。これには、サンプル&ホールド・アンプが使われます。

そのため、あまりにも低速で動作させると、ドループによって電圧が低下し、正確な変換が行えなくなってしまいます。このことから、パイプライン型ADCでは、最高動作速度に加えて最低動作速度も規定されます。低速でサンプリングしたい場合には、変換クロックの周波数を下げるのではなく、規格にのっとったクロック周波数でサンプリングを行い、得られた出力データに対してデシメーションを施すという対応が必要になります。また、多くの場合、サンプリング・クロックのデューティ比にも制限があります。クロックの両エッジを使うため、そのタイミングが重要な意味を持つからです。これは、他の方式のADCにはあまりない制約であり、注意が必要です。加えて、SAR型のように任意のタイミングでA/D変換を実施するのは容易ではありません。パイプライン型ADCを使う場合、ある程度の期間、変換を行っていくことが前提になります。これはΣΔ型のADCにも共通する特徴です。

以下に、パイプライン型ADCの特徴を改めてまとめておきます。

- ・高い分解能で（16ビット程度まで）、高速（GSPSレベル）にA/D変換を実現できます。

- ・変換速度には下限値が存在します。

- ・多くの場合、サンプリング・クロックのデューティ比に制限があります。

- ・パイプライン・ディレイ（レイテンシ）と呼ばれる遅延が発生します。

- ・サンプリングの開始位置（タイミング）を正確に設定することが困難です。

- ・入力帯域の広い製品が多く、アンダーサンプリングや周波数変換の用途に適しています。

- ・通信機器や、RF/IF対応の計測装置、医療用画像装置など、多くのアプリケーションで使用されています。

上述した特徴から、パイプライン型ADCを使用する際に注意すべき事柄が浮かび上がってくるでしょう。

まず、入力側の注意点については、他の一般的なADCの場合と同じです。入力用のバッファ・アンプを内蔵していない製品の場合には、十分な帯域幅、セトリング性能を備えるアンプを外付けする必要があります。

なお、最新の製品では、入力が差動形式である場合が多いので、その点も考慮する必要があります。また、パイプライン型のADCは高速信号向けに使われることが多いので、入力部のインピーダンスが50Ω対応になっているものがあります。さらに、単電源で動作させられるように、入力部にDCバイアス回路を内蔵しているものも少なくありません。

これらを活用するためには、インピーダンス・マッチングのための計算を行ったり、信号の振幅調整／シフトのための回路（アンプやバラン・トランス）を設けたりするための知識なども必要です。これらについては、各製品のデータシートに詳しく記載されているはずなので、必ず参照してください。

最後に、パイプライン型のADCについて学べる書籍（英文）を2つ紹介しておきます。

- ・「The Data Conversion Handbook」：「Chapter 3: Data Converter Architectures」のp.3.61に「Subranging, Error Corrected, and Pipelined ADCs」という節があり、25ページほどにわたって解説されています。

- ・「High Speed Design Techniques」の「Section 4: High Speed Sampling and High Speed ADCs」：p.35以降に「Subranging (Pipelined) ADCs」という節があります。

## Engineer Zone

設計上の困難な課題に関する質問をしたり、豊富な技術情報を参照したりすることが出来ます。また、新しい技術やエンジニアによるブログ記事も公開していますので、是非ご覧ください。

## PartnerZone

アナログ・デバイセズのパートナー企業とお客様との交流を目的としたネットワーク・コミュニティ PartnerZone（英語）では、簡単にアナログ・デバイセズのパートナー企業にコンタクトを取ることができます。

## アナログ電子回路コミュニティとは

アナログ電子回路コミュニティは、アナログ・デバイセズが技術者同士の交流のために提供していた掲示板サイトで、2018年3月に諸般の事情からサービスを終了しました。

アナログ電子回路コミュニティには日々の回路設計活動での課題や疑問などが多く寄せられ、アナログ・デバイセズのエンジニアのみならず、業界で活躍する経験豊富なエンジニアの皆様からも、その解決案や意見などが活発に寄せられました。

ここでは、そのアナログ電子回路コミュニティに寄せられた多くのスレッドの中から、反響の大きかったスレッドを編集し、技術記事という形で公開しています。アナログ電子回路コミュニティへのユーザ投稿に関するライセンスは、アナログ電子回路コミュニティの会員登録時に同意いただいたおりました、アナログ・デバイセズの「[利用規約](#)」ならびに「[ADIのコミュニティ・ユーザ・フォーラム利用規約](#)」に則って取り扱われます。

アナログ電子回路コミュニティへ寄せられた疑問と回答

## アナログ・デバイセズ株式会社

本 社 〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワー10F

大 阪 営 業 所 〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪トラストタワー10F

名古屋営業所 〒451-6040 愛知県名古屋市西区牛島町6-1 名古屋ルーセントタワー38F

©2019 Analog Devices, Inc. All rights reserved.

本紙記載の商標および登録商標は、

各社の所有に属します。

Ahead of What's Possible は

アナログ・デバイセズの商標です。

BBS09JP-07/19

[www.analog.com/jp](http://www.analog.com/jp)

想像を超える可能性を

AHEAD OF WHAT'S POSSIBLE™