# 商用電源のノイズへの対処法、 コンパレータにヒステリシスを 設けるには？

アナログ電子回路コミュニティのスレッドから

## 質問

200VACの商用電源を分圧し、その電圧を直接コンパレータで受け取っています。この部分が、ノイズの影響で誤動作を起こしてしまうため、対策としてコンパレータにヒステリシスを設けたいと考えています。その場合、具体的にはどのような方法を採用するのが適切なのでしょうか？

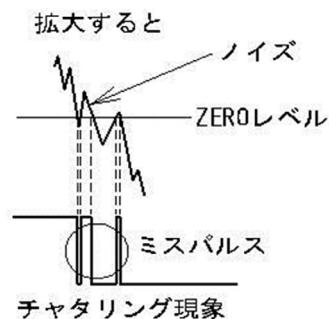

していたというのです。具体的には、図2に示すように、コンパレータにチャタリングが生じて想定外のパルスが発生してしまうということでした。

## 回答

質問者が直面した問題は、海外から輸入した産業用装置で発生したそうです。

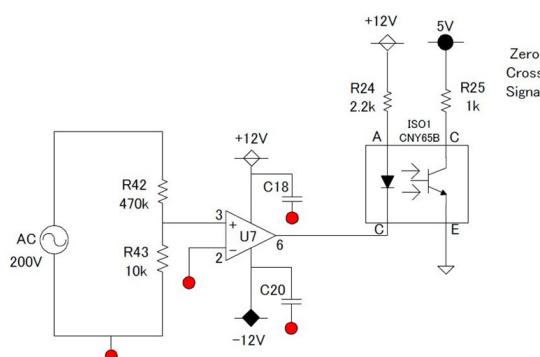

その装置には、ゼロクロス回路が使われていました。200VACの商用電源の電圧がゼロを通過する瞬間にトリガとして使用するための回路です。その実現方法は、図1に示すようなものでした。

図2. 誤動作の原因と現象

図1. 誤動作の生じる回路

200VACを抵抗分割によって分圧し、それを直接コンパレータに入力してゼロクロスを検出するということです。ところが、商用電源の電圧に重畠されるノイズにより、この回路が誤動作

図1の回路については、そもそも、非絶縁型で構成されている点に問題があると考えられます。つまり、それが原因でノイズに弱いということです。本来であれば、抵抗分圧回路の部分は絶縁型のトランジストに置き換えるべきでしょう。また、フォトカプラについても、AC対応の製品を使用する方が適切です。つまり、図1の回路は本質的に問題を抱えたものであると言っても過言ではないでしょう。

ただ、この回路は既に完成品として輸入された装置に実装されているものでした。そのため、大幅な変更を加えることはできませんでした。そこで、質問者はコンパレータにヒステリシスを設けることで対処できないかと考えました。それであれば、外付けの抵抗を追加するくらいで対応できそうだからです。

ただ、そもそも、このような高電圧につながる回路に対してそのような対処を施すのはいかがなものなのかといった懸念も感じたそうです。そのため、質問者は、対処法についてのアドバイスを求めたという次第です。

コンパレータにヒステリシスを追加する方法はいくつかあります。

例えば、ラッチ入力を備えるコンパレータであれば、そこにデジタル信号ではなくアナログ電圧を加えることでヒステリシスを実現できます。ヒステリシスの幅はアナログ電圧の値に応じて変えることが可能です。これであれば、抵抗分圧器によって任意の電圧を生成し、ラッチに入力するだけで済みます。使用すべき抵抗の値や、電圧とヒステリシス幅の関係については、コンパレータの内部回路に依存します。

したがって、コンパレータ製品のデータシートを確認する必要があります。ラッチ入力を備えるコンパレータ製品の場合、必ずと言ってよいほど、データシートにはこの使い方についての記載があります。

では、「LM339」のように、ラッチ入力に対応していないコンパレータについてはどうすればよいのでしょうか。その場合、オープンループではなく、オペアンプを使う場合と同じようにわずかにフィードバックをかけることでヒステリシスを設定することができます。

この回路では、実際にはJFET入力で低消費電力のオペアンプ「TL061C」をコンパレータとして使用していました。

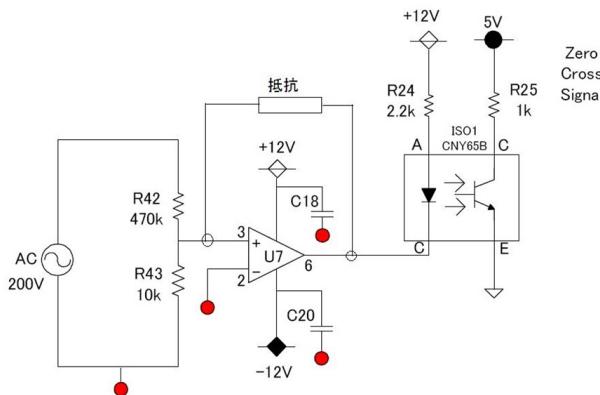

図3に示したのが、このコンパレータ回路にヒステリシスを設けるための1つの案です。470kΩ、10kΩの2つの抵抗によって200Vの電圧を分圧しているので、コンパレータへの入力は約4Vになります。

図3. 対策後の回路

一方で、この分圧用の抵抗はコンパレータ回路側からは、470kΩと10kΩの抵抗が並列に接続されている状態に見えます（つまりほぼ10kΩ）。したがって、テブナンの定理から、4Vの信号源に10kΩの出力抵抗が接続されている回路と等価だと見なすことができます。結論としては、図3のように、必要なヒステリシスの幅が得られるように100kΩ～470kΩ程度の抵抗を接続すればよいはずです。

このような手法を採用し、質問者は、コンパレータに約5%程度のヒステリシスを付加しました。200VACの商用電源に対し、ゼロクロスの付近に幅が約30Vの不感帯を設けることができました。

結果として実用に耐える回路に修正することができたと言います。なお、この方法の場合、ヒステリシスを設けることで、スイッチングに影響を及ぼす位相のずれが生じるのではないかという懸念がありました。ただ、実際には位相のずれは数°程度に収まります。これであれば、ゼロクロス付近でスイッチングに遅れは生じますが、最終段の電力出力にはほとんど影響は及びません。

ここまで説明したとおり、このケースではコンパレータにヒステリシスを設けるという対策が採用されました。

ただ、それ以外に、抵抗R43と並列にコンデンサを加えてノイズのレベルを抑えるという対策方法も考えられます。

200VACの商用電源を信号源インピーダンスがゼロの交流信号であると見なせば、1次フィルタを付加することでノイズの抑制効果が得られるはずです。この装置で問題が発生していたとき、実際にオシロスコープで観測を行ったところ、数10kHzの成分で大きな変動が起きてゼロクロスの部分でスイッチングの誤動作が生じていたそうです。

そのため、カットオフ周波数を1kHz程度に設定する（例えば、430kΩの抵抗と0.006μFのコンデンサを組み合わせる）ことでも対策になる可能性があります。その場合にも、位相のずれについての検討が必要になりますが、カットオフ周波数を1kHzに設定した場合、60Hzにおける位相の遅れは5°以内に収まるはずです。ヒステリシスを付加した場合に生じる位相のずれと大差はないので、恐らく影響は少ないと考えられます。

この例では、実機での検証などは行っていませんが、ヒステリシスを設ける方法との併用も含めて、検討の余地があると言えるでしょう。なお、アナログ・デバイセズは、[数多くのコンパレータ製品をラインアップしています](#)。超高速、高性能の製品なども豊富に取り揃えているので、それらの製品の活用を検討してみてもよいでしょう。

## Engineer Zone

設計上の困難な課題に関する質問をしたり、豊富な技術情報を参照したりすることができます。また、新しい技術やエンジニアによるブログ記事も公開していますので、是非ご覧ください。

## PartnerZone

アナログ・デバイセズのパートナー企業とお客様との交流を目的としたネットワーク・コミュニティ PartnerZone（英語）では、簡単にアナログ・デバイセズのパートナー企業にコンタクトを取ることができます。

## アナログ電子回路コミュニティとは

アナログ電子回路コミュニティは、アナログ・デバイセズが技術者同士の交流のために提供していた掲示板サイトで、2018年3月に諸般の事情からサービスを終了しました。

アナログ電子回路コミュニティには日々の回路設計活動での課題や疑問などが多く寄せられ、アナログ・デバイセズのエンジニアのみならず、業界で活躍する経験豊富なエンジニアの皆様からも、その解決案や意見などが活発に寄せられました。

ここでは、そのアナログ電子回路コミュニティに寄せられた多くのスレッドの中から、反響の大きかったスレッドを編集し、技術記事という形で公開しています。アナログ電子回路コミュニティへのユーザ投稿に関するライセンスは、アナログ電子回路コミュニティの会員登録時に同意いただいたおりました、アナログ・デバイセズの「[利用規約](#)」ならびに「[ADIのコミュニティ・ユーザ・フォーラム利用規約](#)」に則って取り扱われます。

アナログ電子回路コミュニティへ寄せられた疑問と回答

## アナログ・デバイセズ株式会社

本 社 〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワー10F

大 阪 営 業 所 〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪トラストタワー10F

名古屋営業所 〒451-6040 愛知県名古屋市西区牛島町6-1 名古屋ルーセントタワー38F

©2019 Analog Devices, Inc. All rights reserved.

本紙記載の商標および登録商標は、各社の所有に属します。

Ahead of What's Possible®はアナログ・デバイセズの商標です。

BBS06JP-0-07/19

[www.analog.com/jp](http://www.analog.com/jp)

想像を超える可能性を

AHEAD OF WHAT'S POSSIBLE™