# スイッチング電源で使用する トランスのシミュレーション手法

アナログ電子回路コミュニティのスレッドから

## 質問

スイッチング電源で使用するトランスの設計をより手軽に行う方法はありませんか？無償のシミュレーション・ツールなどを使用できると非常にありがたいのですが……。

## 回答

スイッチング電源で使用するトランスの設計には多くの時間と経験を要します。特に初級者が設計作業を行う場合には、シミュレーション・ツールが心強い味方になるでしょう。もちろん、そのツールは無償で使用できるに越したことはありません。そこで、本稿では「LTspice®」によるトランスのシミュレーション手法を紹介します。

LTspiceは、アナログ・デバイセズが提供するSPICEシミュレータです。もともとは、旧リニアテクノロジー（現在はアナログ・デバイセズと合併）から提供されていました。

LTspiceによるトランスのシミュレーション手法としては、複数のインダクタに結合係数を設定したモデルを使用するという

ものが考えられます。結合係数の値としては、実測したデータが存在するならばそれを使えばよいでしょう。また、トランスの巻き数を設定する前の段階なら、複数の集中モデルによって磁路を近似的に置き換えたものを使って計算します。コア材料のメーカーが提供するデータを基に損失を推定する方法を見出し、それをシミュレーションに反映することも可能です。

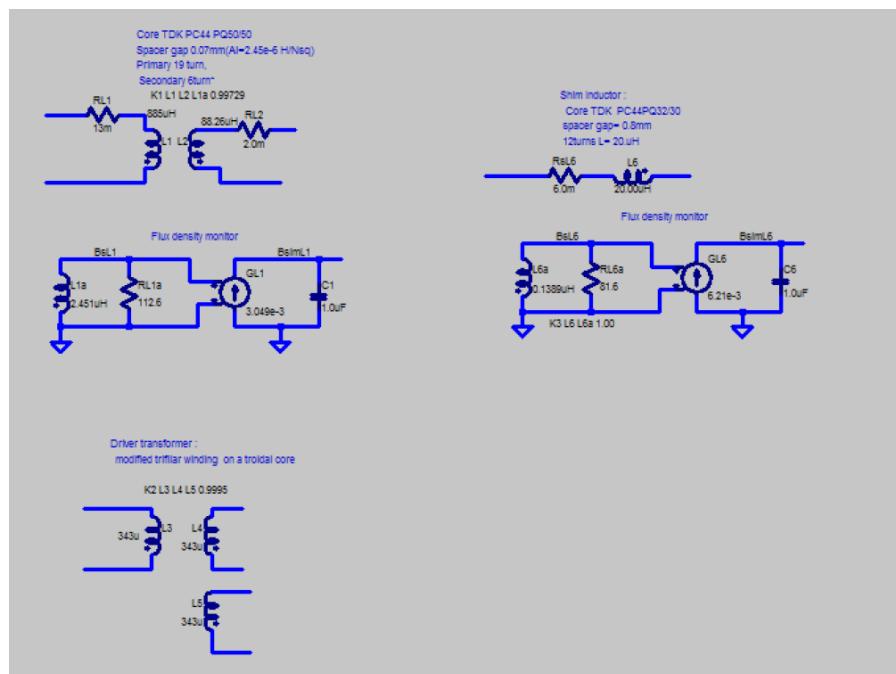

では、トランスのモデルとしては、具体的にはどのようなものを用意すればよいのでしょうか。図1に示したのが、その一例です。このモデルは、フルブリッジZVS（ゼロ・ボルト・スイッチング）方式の部分共振電源のシミュレーションに使われたものです。制御周期が150kHzの電源を設計するために作成されました。このモデルの主要な要素は3つあります。以下、それぞれについて説明します。

フルブリッジZVS（ゼロ・ボルト・スイッチング）方式の

部分共振電源のシミュレーションモデル

## メインのトランス

左上に示したのがメインのトランスのモデルです。L1、L2がそれぞれ1次、2次の巻線です。LTspiceでは、インダクタの等価直列抵抗の値をパラメータとして設定することができます。デフォルトの値は1mΩです。ただ、この例では、そのパラメータを使うのではなく、明示的に抵抗素子を付加しています。つまり、RL1、RL2が、それぞれL1、L2の等価直列抵抗に相当します。

L1、L2のモデルの下に示したL1aは、コアの磁束密度の変化を確認するために設けた仮想的な部品です。これは1ターンのコイルを模したものとなっています。磁束密度などは、このような仮想的な巻線を付加するのではなく、コイルのパラメータを変更することでも表現できます。ただ、1ターンの巻線を使用すると、考え方が簡単になります。また、設計に変更を加える際、トランスにおける巻線の巻き数を変更しなければならなくなったりしたときに、モニター回路を変更しなくて済むというメリットもあります。

L1aに生じた電圧は、電圧制御電流源GL1とコンデンサC1によって積分します。そのうえで、BsimL1を使用し、1Vを1Tに換算することで磁束密度の値を表現します。

RL1aは、コアで生じる損失のうち、渦電流損を表現するためのモデルです。コアの損失は、この渦電流損とヒステリシス損から成ります。なお、ここでは省略していますが、この回路の場合、実際にはヒステリシス損の方が大きくなります。RL1aの抵抗値や、ヒステリシス損を表す計算式を求めるには、コアのデータを分析する必要があります。

K1は巻線間の結合係数です。ここでは、試作品の測定結果を基にして得られた値を使用しています。2次側の開放時と短絡時のそれについて、使用する周波数領域内の何点かで1次インダクタンスの値と漏れインダクタンスの値を測定し、その結果から結合率を計算によって求めました。

このモデルでは、トランスの浮遊容量は省略しています。シミュレーションの対象となる回路では、大きな静電容量が並列に接続されるので、トランス自体の静電容量については無視しています。

## ドライバのトランス

左下に示したのは、トロイダル・コアに3本の線材を並べて巻いたトランスのモデルです。これは、FETのゲートを絶縁駆動するためのものです。K2は結合係数であり、実測結果を基にした値を使用しました。このモデルでは、損失などについて厳しい条件は存在しなかったので細かい設定は行っていません。

## シム・インダクタ

ZVS回路では、共振に関連する回路のインダクタンス成分としてトランスの漏れインダクタンスを使用できます。ただ、それだけではインダクタンスの値が不足することがあります。そのような場合に、追加するのがシム・インダクタ(Shim Inductor)です。シム・インダクタは、整流段に続くローパス・フィルタ用のチョーク・インダクタとは異なり、大きな振幅の

信号を扱います。そのため、コアの損失の評価を適切に行う必要があります。図の右側に示したモデルでは、渦電流損を考慮するために、メインのトランスと同様に磁束密度とコアの渦電流損を表現するための部品を付加しています。メインのトランスと同じく、ヒステリシス損の表現は割愛しています。磁束密度の表示や、渦電流損の評価については、メインのトランスよりもシム・インダクタに対して実施する方が重要になります。なお、図中のパラメータには細かい数字が記載してありますが、それだけの精度/確度があるというわけではありません。

## コアで生じる損失

上述した例では、モデルのパラメータの値を算出する方法については説明を割愛しています。実測が可能であれば実測すればよいのですが、現物が存在しないため測定が行えない場合には、コアのメーカーが公表しているデータを基に、いくつかの簡単な計算を行うことで近い値を得ることになります。ただし、AL値(インダクション係数)などは、製品によって20%もばらつく可能性があるため注意が必要です。ギャップ付きのコアの場合、AL値は、材料の特性よりもギャップに大きく依存するようになります。

上記の例では適宜割愛していますが、損失モデルがより重要な検討項目になるケースもあり得ます。先ほども少し触れたように、コアの損失は、周波数に比例するヒステリシス損とコア内の電界強度の2乗に比例する渦電流損の和によって表現できます。この考え方に基づけば、メーカーが公表している損失のデータを分析することによってそれぞれの値を導き出すことが可能です。

まず、ヒステリシス損については以下の式を使用することで算出できます。

$$[\text{単位体積当たりのヒステリシス損}] = K1 \times Bm^{K2} \times f$$

ここで、K1、K2は正弦波データから抽出したパラメータ、Bmは最大磁束密度、fは周波数です。Bmとしては磁束密度を観測して得た値を使用します。ここでは、磁束密度がゼロの状態を中心として動作すると仮定しています。

一方、渦電流損については以下のよう式を使用します。

$$[\text{単位体積当たりの渦電流損}] = K3 \times Bm^{K4} \times (dB/dt)^2$$

ここで、K3、K4は正弦波データから抽出したパラメータ、dB/dtは時間当たりの磁束密度の変化量です。これにコアの実効断面積をかけると、コイルの1ターン当たりの電圧になります。これらの計算式は、ある瞬間の電力を対象としたものです。波形が複雑なケースについて損失を計算したい場合、シミュレータを利用する方が現実的です。そのため、先述したようなモデリングを行ったということです。

以上、本稿では、LTspiceの利用を前提として解説を行いました。なみに、有償のツールとしては、Intusoftが提供している「[Magnetics Designer](#)」などが有名です。同製品については、日本語の解説書も出版されていますし、セミナーも開催されています。無償のデモ版も用意されているので、まずはそちらを試してみるとよいかもしれません。

注釈：記事中の画像は、HN : MUSUSU2さんより、アナログ電子回路コミュニティへ投稿されたものです。

## Engineer Zone

設計上の困難な課題に関する質問をしたり、豊富な技術情報を参照したりすることができます。また、新しい技術やエンジニアによるブログ記事も公開していますので、是非ご覧ください。

## PartnerZone

アナログ・デバイセズのパートナー企業とお客様との交流を目的としたネットワーク・コミュニティ PartnerZone (英語) では、簡単にアナログ・デバイセズのパートナー企業にコンタクトを取ることができます。

## アナログ電子回路コミュニティとは

アナログ電子回路コミュニティは、アナログ・デバイセズが技術者同士の交流のために提供していた掲示板サイトで、2018年3月に諸般の事情からサービスを終了しました。

アナログ電子回路コミュニティには日々の回路設計活動での課題や疑問などが多く寄せられ、アナログ・デバイセズのエンジニアのみならず、業界で活躍する経験豊富なエンジニアの皆様からも、その解決案や意見などが活発に寄せられました。

ここでは、そのアナログ電子回路コミュニティに寄せられた多くのスレッドの中から、反響の大きかったスレッドを編集し、技術記事という形で公開しています。アナログ電子回路コミュニティへのユーザ投稿に関するライセンスは、アナログ電子回路コミュニティの会員登録時に同意いただいたおりました、アナログ・デバイセズの「[利用規約](#)」ならびに「[ADIのコミュニティ・ユーザ・フォーラム利用規約](#)」に則って取り扱われます。

アナログ電子回路コミュニティへ寄せられた疑問と回答

## アナログ・デバイセズ株式会社

本 社 〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワー10F

大阪 営 業 所 〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪トラストタワー10F

名古屋 営 業 所 〒451-6040 愛知県名古屋市西区牛島町6-1 名古屋ルーセントタワー38F

©2019 Analog Devices, Inc. All rights reserved.

本紙記載の商標および登録商標は、

各社の所有に属します。

Ahead of What's Possible® は

アナログ・デバイセズの商標です。

BBS04JP-0-07/19

[www.analog.com/jp](http://www.analog.com/jp)

想像を超える可能性を

AHEAD OF WHAT'S POSSIBLE™