# MAX96793 Single CSI-2 to GMSL3 Serializer User Guide

Authored by: GMSL SerDes Applications Team UG-2232

#### **Device Overview**

This user guide is intended to be used in conjunction with other documents such as the MAX96793 data sheets, errata documents, and other user and design guides. It provides explanations, examples, and instructions to help set up video configurations and use various features.

Examples may be shown without errata writes that are necessary to ensure reliable operation in production. Contact the Analog Devices, Inc. field applications engineer or representative to obtain the errata documents. The user should include any relevant errata writes in the final production software. In addition to the errata, it is also important to have the latest revision of the GMSL device for testing.

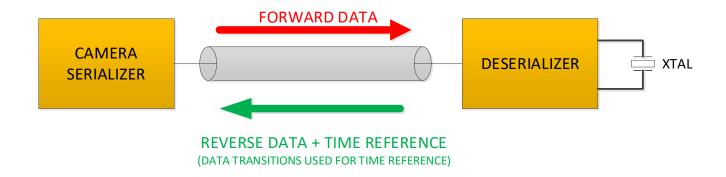

The GMSL3 serial links use packet-based, bidirectional architecture with forward and reverse channels. The forward channel transfers data from the serializer to the deserializer; the reverse channel transfers data from the deserializer to the serializer. The GMSL3 devices have a forward channel serial bit rate of 3Gbps, 6Gbps, or 12Gbps and reverse channel serial bit rate of 187.5Mbps. See *Table 1* for supported data rates/features by part number.

The MAX96793 is a full featured GMSL3/2 serializer device. The MAX96793 is capable of 3Gbps, 6Gbps, or 12Gbps forward link rate (selectable with resistors connected to the CFG pin or with register writes) with a 187.5Mbps reverse direction rate.

Table 1. MAX96793 High-Level Features

| Part Number | Forward Link<br>Rate       | Coax/STP    | MIPI Input   | GMSL Links | ASIL Rating |

|-------------|----------------------------|-------------|--------------|------------|-------------|

| MAX96793    | 3Gbps, 6Gbps, or<br>12Gbps | Coax or STP | DPHY or CPHY | 1          | В           |

Note: This is not a complete list of device differences. See the device data sheets for all feature details.

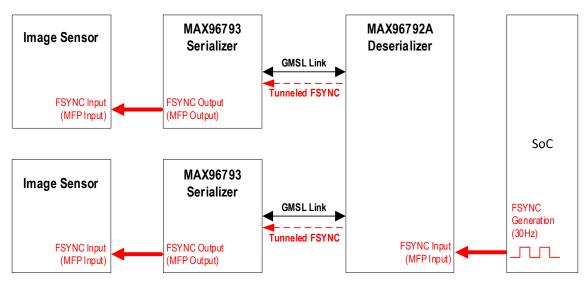

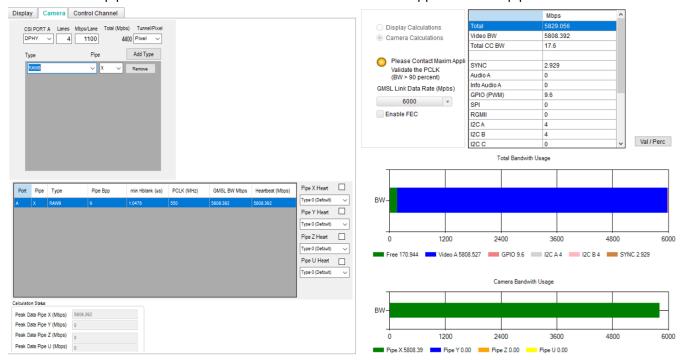

# **Application Use Case**

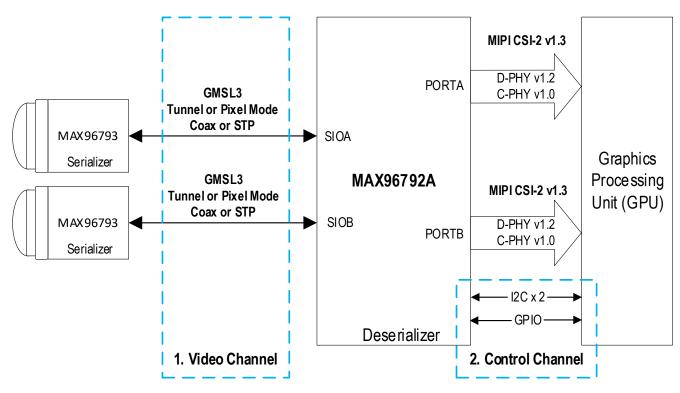

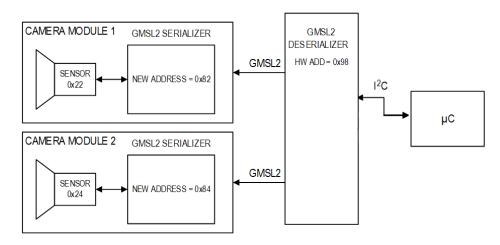

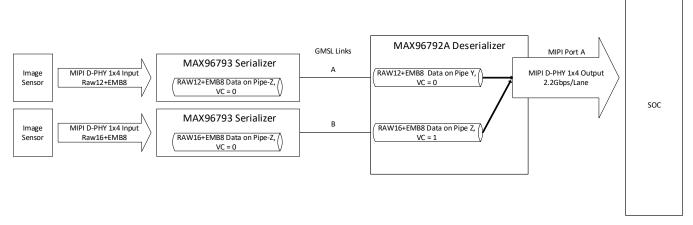

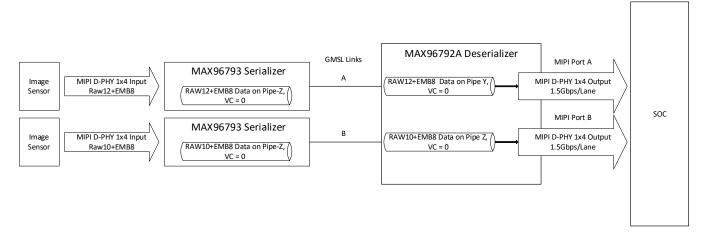

In a typical configuration, the MAX96793 serializer accepts mobile industry processor interface (MIPI) CSI-2 D-PHY or C-PHY video data from an image sensor in the 8MP to 17MP range, see *Figure 1*. The MAX96793 serializer then takes that data, converts it to GMSL, and sends it out over the link to a GMSL3 deserializer. In *Figure 1*, there are two MAX96793s operating independently and sending data out to a MAX96792A deserializer. Coax or shielded twisted-pair (STP) cables can be used for the GMSL link.

Figure 1. MAX96793 Two Camera Application Example

# **Architecture**

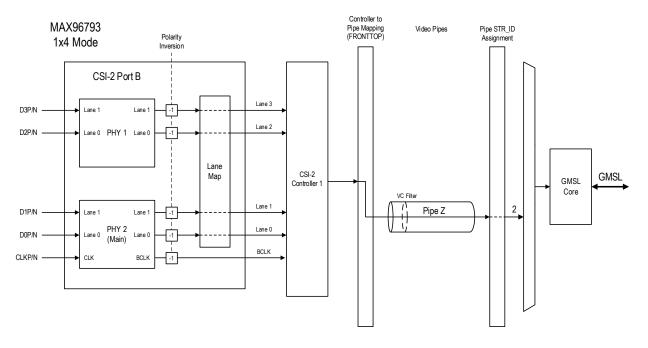

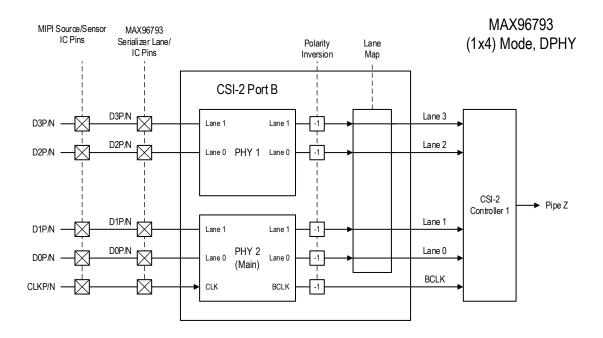

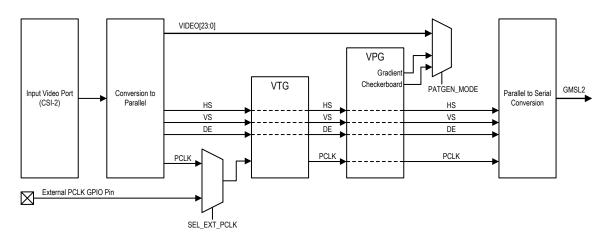

The MAX96793 video path starts with one MIPI PHY that connects to a CSI-2 controller which then routes to internal Pipe Z and ends with a GMSL PHY. The default video path settings are shown in *Figure 2*.

Figure 2. MAX96793 Video Path (1x4 D-PHY Mode)

# **Startup and Programming Sequence**

The GMSL3 SerDes devices have many application use cases and features that work in conjunction with each other. To avoid feature and system sequencing issues, *Table 2* outlines the preferred sequence order. Features or configuration changes may not be required and may be skipped in the start-up sequence. This depends on system requirements and data configurations.

Table 2. GMSL3 SerDes Start-Up Sequence

|                                                                  | GMSL3 Start-Up and                                              | <b>Programming Sequence</b>                                                                                                                                                                                                          |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sequence<br>Number                                               | Configuration Setup                                             | Notes                                                                                                                                                                                                                                |  |  |

| r                                                                |                                                                 | -No power supply voltage sequencing required; voltage rails are internally independent and managed by on-chip power management block.                                                                                                |  |  |

| 1                                                                | Release PWNDB Pin (L→H)<br>(If necessary)                       |                                                                                                                                                                                                                                      |  |  |

|                                                                  | I <sup>2</sup> C Wake-Up Time                                   | Time from power-up or rising edge of PWDNB for local register access. For remote register access, I <sup>2</sup> C wakeup is the same as GMSL Link Lock time.                                                                        |  |  |

| 2                                                                | CFG Pins Automatically Set Link                                 | -CFG pins sampled on every power-on reset (POR) and/or PWDNB L→H transition                                                                                                                                                          |  |  |

| 3 Link Configuration (Single Link vs. Multilink Operation Setup) |                                                                 | k vs.  Some deserializers power up in single-link mode while others in multilink modes. Read register map for correct registers to set up correct link operation mode.  See <i>Multilink Operation</i> section for more information. |  |  |

| 4                                                                | GMSL Link Lock is Established                                   | -If GMSL Link Lock is not established, verify the following:  1) Voltage rails are correct per DS specification.  2) Datarate, Coax/STP mode, and GMSL settings match between serializer and deserializer.                           |  |  |

| 5                                                                | I <sup>2</sup> C Rate Adjustment<br>(If necessary)              | SerDes has I <sup>2</sup> C rate register settings that need to match up to I <sup>2</sup> C main.                                                                                                                                   |  |  |

| 6                                                                | SER I <sup>2</sup> C Device Address Reassignment (If necessary) | Reassigning SER I <sup>2</sup> C device address can help in multicamera systems                                                                                                                                                      |  |  |

| 7                                                                | Disable DES CSI Output                                          | -Set register bitfield CSI_OUT_EN=0                                                                                                                                                                                                  |  |  |

| 8                                                                | DES Errata Settings<br>(If necessary)                           | -Ensure errata settings match DEV_REV and use case                                                                                                                                                                                   |  |  |

| 9                                                                | DES MIPI TX Configuration                                       | -MIPI Port Config -Lane Count -Lane Mapping/Polarity Swap -Pipe to Controller Mapping -Deskew (>1.5Gbps/Lane) -MIPI Data Rate                                                                                                        |  |  |

| 10                                                               | DES GPIO and Other Feature<br>Configuration                     | -GPIO Forwarding<br>-FSYNC                                                                                                                                                                                                           |  |  |

|    |                                         | 120/11407 0 1 1 0 1                                           |

|----|-----------------------------------------|---------------------------------------------------------------|

|    |                                         | -I <sup>2</sup> C/UART Pass-through Channels                  |

|    |                                         | -Line Fault                                                   |

| 11 | DES Interrupt Handling (ERRB) and ASIL  | -See <i>Error Flags</i> section and Safety Documents of the   |

|    | Configuration                           | Deserializer for more information                             |

| 12 | SER Errata Settings                     | -Ensure Errata settings match DEV_REV and use case            |

|    | (If necessary)                          |                                                               |

| 13 | SER MIPI RX Configuration               | -Lane Count                                                   |

|    |                                         | -Lane Mapping/Polarity Swap                                   |

|    |                                         | -Pipe to Controller Mapping                                   |

|    |                                         | -Deskew (>1.5Gbps/Lane)                                       |

|    |                                         | -MIPI Continuous vs. Noncontinuous Mode                       |

| 14 | SER GPIO and Other Feature              | -GPIO Forwarding                                              |

|    | Configuration                           | -FSYNC                                                        |

|    |                                         | -I2C/UART Pass-through Channels                               |

|    |                                         | -Reference Clock Out                                          |

|    |                                         | -ADC                                                          |

|    |                                         | -Line Fault                                                   |

| 15 | SER Interrupt Handling (ERRB) and ASIL  | -See <i>Error Flags</i> section and Safety Documents of the   |

|    | Configuration                           | Serializer for more information.                              |

| 16 | RESET LINK=1                            | -Reset whole data path to allow configuration and errata      |

|    |                                         | settings to take effect. (While this bit is '1' remote access |

|    |                                         | to link is not possible.)                                     |

| 17 | RESET LINK=0                            | -Release of reset, link relocks. Remote access is possible    |

|    |                                         | after link is locked.                                         |

| 18 | DES Enable CSI Output                   | -Set register bitfield CSI_OUT_EN=1                           |

| 19 | Enable Deserializer Register CRC Safety | Review Safety documents of the Deserializer for more          |

|    | Mechanism (If necessary)                | information.                                                  |

|    | -                                       |                                                               |

|    |                                         | See <i>Register CRC</i> section for more information.         |

| 20 | Enable Serializer Register CRC Safety   | Review Safety documents of the Serializer for more            |

|    | Mechanism (If necessary)                | information.                                                  |

|    |                                         |                                                               |

|    |                                         | See Register CRC section for more information.                |

| 21 | Start Video Source                      |                                                               |

## Note(s):

- Perform any configuration changes before video starts.

- If changes are needed after video has started; stop the video, then make changes, and restart the video.

- Dynamic configuration is not supported.

# **Video Configuration**

## **Overview**

The forward video paths of the MAX96793 serializers are configured with the following programming:

- Pixel and Tunneling Mode

- Link Initialization

- Link Lock Check

- MIPI Controller and PHY Settings

- Datatype (DT)/Virtual Channel (VC) Filtering and Overrides

Enable the video only after the video path is configured; dynamic configuration is not supported. The following subsections detail the operation of each of these steps with descriptions of relevant registers and programming examples.

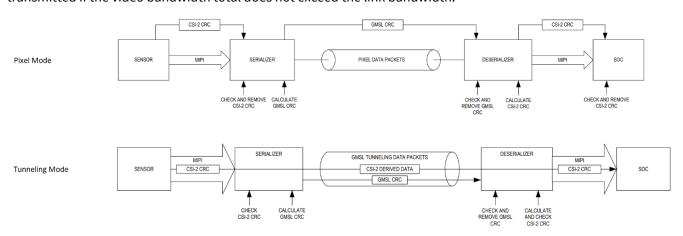

#### **Pixel and Tunneling Mode**

The MAX96793 supports both pixel and tunneling modes. Always ensure that both serializer and deserializer are in pixel or tunneling mode.

Pixel mode provides the ability for systems to manipulate data types, bits per pixel (BPP), and virtual channels. This mode can be used when the incoming data must be manipulated over the serial link before outputting from the deserializer.

Tunneling mode can be used when data integrity is a major system concern as it ensures end-to-end data integrity. End-to-end data protection is a common requirement for Advanced Driver Assistance Systems (ADAS), where data may not be altered from the transmitter to the downstream receiver. In tunneling mode, data may not be changed as it is protected with an end-to-end cyclic redundancy check (CRC) and is passed from serializer to deserializer without any manipulation. In tunneling mode, any combination of data type, BPP, and virtual channel may be transmitted if the video bandwidth total does not exceed the link bandwidth.

Figure 3. Pixel and Tunneling Mode Comparison

The following tables show MAX96793 registers to enable pixel or tunneling mode and the mode differences.

Table 3. MAX96793 Pixel and Tunneling Mode Register Settings

| Register<br>Address | Bitfield Name | Bits | POR | Decode                                 |

|---------------------|---------------|------|-----|----------------------------------------|

| 0x383               | TUN_EN        | 7    | 0b0 | 0b0: Pixel Mode<br>0b1: Tunneling Mode |

Table 4. MAX96793 Features Supported by Pixel Mode vs. Tunneling Mode

| Feature                                                          | Pixel Mode    | Tunneling Mode |

|------------------------------------------------------------------|---------------|----------------|

| Video Processing (Watermarking)*                                 | Supported     | Not Supported  |

| Virtual Channel Reassignment                                     | Supported     | Not Supported  |

| Synchronous Aggregation                                          | Not Supported | Not Supported  |

| First Come First Serve Aggregation                               | Supported     | Supported**    |

| Compatibility with Legacy GMSL2 Pixel Parts                      | Supported     | Not Supported  |

| D-PHY to C-PHY Translation                                       | Supported     | Not Supported  |

| C-PHY to D-PHY Translation                                       | Supported     | Not Supported  |

| Mixed Mode (One GMSL Link is C-PHY and other GMSL Link is D-PHY) | Supported     | Supported      |

| End-to-End CRC Coverage for Video                                | Not Supported | Supported      |

| Video Line CRC (LCRC)                                            | Supported     | Supported      |

| GMSL Packet CRC (VID_PXL_CRC)                                    | Supported     | Supported      |

| Line Length >8k pixels at 24BPP                                  | Not Supported | Supported      |

| 16-Channel Virtual Channel Support                               | Supported     | Supported      |

<sup>\*</sup>Check device data sheet to verify watermarking is supported.

#### **Link Initialization**

Link initialization establishes the device link modes and speeds. The MAX96793 device family is a GMSL3 Single CSI-2 to GMSL3 Serializer that can support coax or STP cables. Using the following registers, select the GMSL link rate and coax or STP connectivity. Any changes to the GMSL link should be followed by a link reset to reinitialize the link (toggle RESET\_LINK=1 and then RESET\_LINK=0). The CFG pins are the preferred method of setting up the GMSL rate and transmission mode. The selected configuration becomes the new default on power-up once the CFG pins are set and the part is power cycled. The following tables show capabilities of MAX96793 devices and its link initialization registers.

Table 5. MAX96793 Basic Settings (CFG1 Pin)

| CFG1 Value | Coax/STP | Data Rate | Transmission Mode |

|------------|----------|-----------|-------------------|

| 0          | STP      | 6Gbps     | Tunneling Mode    |

| 1          | STP      | 12Gbps    | Tunneling Mode    |

| 2          | STP      | 3Gbps     | Pixel Mode        |

| 3          | STP      | 6Gbps     | Pixel Mode        |

| 4          | Coax     | 6Gbps     | Tunneling Mode    |

| 5          | Coax     | 12Gbps    | Tunneling Mode    |

| 6          | Coax     | 3Gbps     | Pixel Mode        |

| 7          | Coax     | 6Gbps     | Pixel Mode        |

**Table 6. MAX96793 Link Initialization Registers**

<sup>\*\*</sup>Video source needs to set different VCs, as VC reassignment is not supported in tunneling mode.

| Register Address | Bitfield Name | Bits | POR  | Decode                           |

|------------------|---------------|------|------|----------------------------------|

| 0x0001           | TX_RATE       | 3:2  | 0b10 | 0b00: RSVD                       |

|                  |               |      |      | 0b01: 3Gbps                      |

|                  |               |      |      | 0b10: 6Gbps                      |

|                  |               |      |      | 0b11: 12Gbps                     |

| 0x0011           | CXTP_A        | 0    | 0b1  | 0b0: Shielded twisted pair drive |

|                  |               |      |      | 0b1: Coax drive                  |

| 0x0010           | RESET_ALL     | 7    | 0b0  | 0b0: No action                   |

|                  |               |      |      | 0b1: Activate chip rest          |

| 0x0010           | RESET_LINK    | 6    | 0b0  | 0b0: Release link A reset        |

|                  |               |      |      | 0b1: Activate link A reset       |

| 0x0010           | RESET_ONESHOT | 5    | 0b0  | 0b0: No action                   |

|                  |               |      |      | 0b1: Reset data path             |

Note: A link reset on CSI-2 serializers resets the entire data path of any video connected to the PHY. Link resets should not be used when video is being fed to the device. Doing this can corrupt data and have unintended consequences.

#### **Multilink Operation**

The MAX96793 has only one GMSL link so it does not have multilink operation. Although multicamera systems can be created with multiple MAX96793 and single, dual, and quad CSI-2 deserializers.

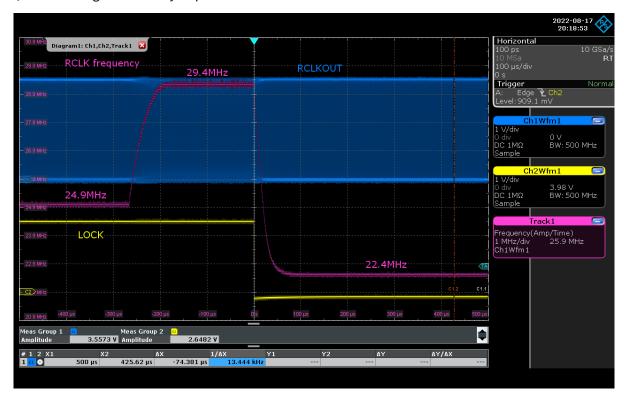

#### **Link Lock Check**

If the MAX96793 device configuration is correct, the link automatically locks upon connection.

Pin #17 (MFP3) can be used as LOCK indication if enabled by register write. Bit 3 in register 0x0013 asserts if link is locked.

# **Video Pipe Selection**

Video pipes must be configured to match video streams between the deserializer and serializer. This programming step is typically done following link initialization and ensures that the deserializer properly receives video data from the serializer. By default, the deserializer is programmed to accept the most common stream from the serializers and configuration is not usually needed.

The MAX96793 has one video pipe (video pipe Z) that can select one of the four stream IDs. By default, the MAX96793 pipe Z stream ID is set to 0b10.

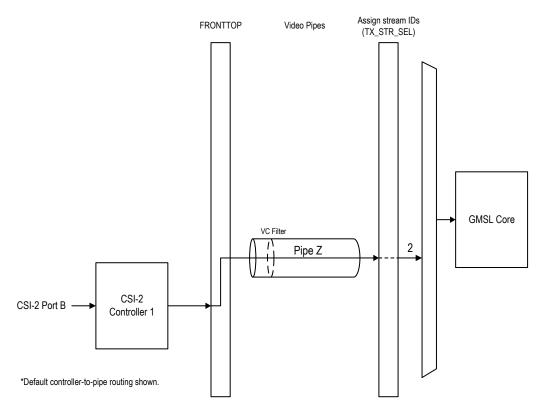

Figure 4. MAX96793 Video Pipe Path

#### **Video Pipe Selection Registers**

Select the serializer stream ID to match the video streams (STR\_ID) from the serializers for each deserializer video pipe. The GMSL3 camera serializers can have up to four video pipes (X, Y, Z, and U). These are annotated as 2 bits representing the stream ID. Pipe X = 0b00, Pipe Y = 0b01, Pipe Z = 0b10, and Pipe U = 0b11.

By default, the MAX96793 serializer selects stream ID 0b10, which is the default for most CSI-2 deserializers.

Table 7. MAX96793 Video Pipe Selection Registers

| Register<br>Address | Bitfield Name       | Bits | POR  | Decode                                                                   |

|---------------------|---------------------|------|------|--------------------------------------------------------------------------|

| 0x5B                | TX_STR_SEL (Pipe Z) | 00   | 0b10 | 0b00: str_id=00<br>0b01: str_id=01<br>0b10: str_id=10<br>0b11: str_id=11 |

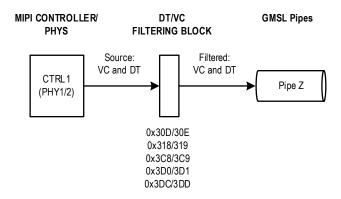

#### Video Pipe to MIPI Controller Mapping (VC/DT Mapping and Filtering)

As data comes in through the MIPI PHY on serializer input, the pixel data goes to a CSI-2 controller then is routed to internal video pipes. Video pipes are then mapped to a GMSL PHY that is sent over the GMSL link. Pixel data within video pipes can be filtered by DT or VC.

The MAX96793 has only one CSI-2 input port (B) and one video pipe (Z). This means the video routing is much simpler since there is only one path for video data to flow. Register 0x0308, shown in the Video Pipe and Filtering Registers table (see *Table 8*), contains the bits for enabling/disabling MIPI port B.

**Default Mapping:**

MIPI PHY1/2  $\rightarrow$  MIPI Controller 1  $\rightarrow$  Video Pipe Z

Figure 5. MAX96793 MIPI Controller to Video Pipe Block Diagram

Using the default video routing, any data received on the MIPI input port B is automatically routed onto video pipe Z, unless filtering by DT or VC is being used. Every CSI-2 packet includes a header that indicates the DT and VC. If pixel mode is being used, this information can be used to route the incoming data throughout the serial link system. The DT and VC filtering is not supported in tunneling mode.

The data within the serializer's controller can be filtered so that the user can control what data, if not all, gets serialized and sent across the GMSL link. The mem\_dt\_selz registers are used to filter the controller data by CSI-2 datatype code at the FRONTTOP before it reaches the video pipe. When using DT filtering, up to four datatypes can be routed from the controller to pipe Z. The pixel datatype codes to be routed must be set in mem\_dt{1,2,7,8}\_selz. Bits [5:0] in these registers must match the incoming datatype code. Bit 6 enables the filter.

Another form of filtering is by VC which is configured with the VC\_SELZ bitfield. In pixel mode, when multiple data streams are transmitted over the same pipe with different virtual channels, the VC\_SELZ\_L and VC\_SELZ\_H bits must be set to represent the virtual channels present on that pipe. Each bit place represents a VC within these registers. For example, if VC\_SELZ\_L[0] = 1 and VC\_SELZ\_L[1] = 1, then pipe Z would expect to have VC 0 and 1 on the pipe. When a bit position is set to zero, that VC is not allowed to enter that pipe. The VC\_SELZ\_L/H registers on this part have a default value of 0xFF, meaning that all 16 VCs (0-15) are allowed onto the pipe unless programmed otherwise.

Table 8. MAX96793 Video Pipe and Filtering Registers

| Register | Bitfield Name | Bits | Default<br>Value | Decode                                                                 |

|----------|---------------|------|------------------|------------------------------------------------------------------------|

| 0x0308   | START_PORTB   | 5    | 0b1              | 0 = CSI-2 on port B disabled<br>1 = CSI-2 on port B enabled            |

| 0x0308   | CLK_SELZ      | 2    | 0b1              | 0 = Reserved (Port A does not exist)<br>1 = Port B selected for pipe Z |

| 0x0002   | VID_TX_EN_Z   | 6    | 0b1              | 0 = Video transmit on pipe Z disabled                                  |

|         |                           |     |          | 1 = Video transmit on pipe Z enabled                           |

|---------|---------------------------|-----|----------|----------------------------------------------------------------|

| 0x005B  | TX_STR_SEL[1:0]           | 1:0 | 0b10     | 00 = Stream ID for pipe Z is 0                                 |

|         |                           |     |          | 01 = Stream ID for pipe Z is 1                                 |

|         |                           |     |          | 10 = Stream ID for pipe Z is 2                                 |

|         |                           |     |          | 11 = Stream ID for pipe Z is 3                                 |

| 0x0318, | mem_dt{1,2,7,8}_selz[6]   | 6   | 0b0      | 0 = Datatype filtering disabled                                |

| 0x0319, |                           |     |          | 1 = Datatype filtering enabled                                 |

| 0x03DC, |                           |     |          |                                                                |

| 0x03DD  |                           |     |          |                                                                |

| 0x0318, | mem_dt{1,2,7,8}_selz[5:0] | 5:0 | 0b000000 | The value of bits 5:0 in this register should equal the        |

| 0x0319, |                           |     |          | datatype ID of the datatype the user wishes to allow onto      |

| 0x03DC, |                           |     |          | the video pipe (e.g., RAW12 = 0x2C).                           |

| 0x03DD  |                           |     |          |                                                                |

| 0x03C8, | mem_dt{3,4}_selz[7:6]     | 7:6 | 0b00     | These two bits select the two LSBs of the virtual channel      |

| 0x03C9  |                           |     |          | that is to be filtered onto the video pipe                     |

| 0x03C8, | mem_dt{3,4}_selz[5:0]     | 5:0 | 0b000000 | The value of bits 5:0 in this register should equal the        |

| 0x03C9  |                           |     |          | datatype ID of the datatype the user wishes to allow onto      |

|         |                           |     |          | the video pipe.                                                |

| 0x03D1  | mem_dt{3,4}_selz_en       | 1:0 | 0b00     | 0 = Disable filtering set in registers 0x3C8, 0x3C9            |

|         |                           |     |          | 1 = Enable filtering set in registers 0x3C8, 0x3C9             |

| 0x030D  | VC_SELZ_L                 | 7:0 | 0xFF     | Bits 0-7 represent VC0-VC7, respectively. If a bit is high, it |

|         |                           |     |          | means that VC is allowed onto the video pipe (e.g., if only    |

|         |                           |     |          | bits 0 and 2 are HIGH, then only VC0 and VC2 are               |

|         |                           |     |          | accepted).                                                     |

| 0x030E  | VC_SELZ_H                 | 7:0 | 0xFF     | This register works the same as register 0x30D except bits     |

|         |                           |     |          | 0-7 represent VC8-VC15, respectively                           |

#### **Video Pipe to Controller Routing Example**

This example filters video pipe Z for RAW12 datatype and virtual channel 1 on the MAX96793.

0x80, 0x0318, 0x6C, #enable DT filter for RAW12 (ID = 0x2C)

0x80, 0x030D, 0x02, #only VC1 allowed onto pipe

#### **Video Lock Check**

In pixel mode, the MAX96793 register 0x112 bit 7 (PCLKDET) asserts if it is receiving valid MIPI long packets (pixel data) and GMSL Link LOCK=1.

In tunneling mode, the MAX96793 register 0x112 bit 7 (PCLKDET) asserts if it is receiving valid CSI-2 clock and GMSL Link LOCK=1.

# **DT/VC Software Override**

The software override manually overrides the video DT (i.e., packet header), VC number, or BPP. This operation affects the video data between the video pipe(s) and the MIPI controller(s). Overriding the DT and VC information is used for MIPI controller mapping. If the received video data is from a serializer in parallel mode (e.g., GMSL1 serializers), it is necessary to specify the desired DT, VC, and BPP with the software override.

**Note**: The VC can be changed individually. However, DT and BPP must be adjusted together to ensure settings compatibility.

#### Input DT BPP Manipulation (Pixel Mode Only)

One advantage of pixel mode is that the data can be manipulated, such as by doubling or zero padding. Doubling the BPP of a data type allows for more efficient bandwidth usage. Zero padding is used to match the BPP of two or more data types so that they can share a video pipe.

#### **Double Mode**

Double mode is a data arrangement available for data types with BPP = 8, 10, or 12. With double mode enabled, two input pixels are concatenated and processed as a single pixel within the video pipe. This concatenation reduces the internal PCLK and increases the GMSL3 bandwidth efficiency. Double mode is enabled on a BPP basis.

Further, user-defined 8-bit data types (UDP or UDT), which have header codes 0x30, 0x31–0x37, or 0x10–0x11 can alternatively be combined and transmitted by the serializer as 24-bit data. Set ctrl1\_mode\_UDT = 1 to treat these data types as 24BPP. This mode cannot be used simultaneously while bpp8dblz = 1, and tripled data types can only share a pipe with data types that use 24BPP or other tripled 8-bit data types.

When using double or triple mode, the new internal BPP must be programmed into the serializer in addition to enabling the mode. Video pipe Z has a soft\_bppz bitfield that must be set to the new BPP (e.g.,  $8 \rightarrow 16$ ,  $8 \rightarrow 24$ ,  $10 \rightarrow 20$ ,  $12 \rightarrow 24$ ) and a soft\_bpp\_en bit.

| Register | Bitfield Name  | Bits | Default<br>Value | Decode                                                          |

|----------|----------------|------|------------------|-----------------------------------------------------------------|

| 0x312    | bpp8dblz       | 2    | 0b0              | 0: Send as 8-bit pixels 1: Send 8-bit pixels as 16-bit pixels   |

| 0x313    | bpp10dblz      | 2    | 0b0              | 0: Send as 10-bit pixels 1: Send 10-bit pixels as 20-bit pixels |

| 0x313    | bpp12dbl{Z}    | 6    | 0b0              | 0: Send as 12-bit pixels 1: Send 12-bit pixels as 24-bit pixels |

| 0x337    | ctrl1_mode_UDT | 5    | 0b0              | 0: Treat UDP as 8 bits 1: Treat UDP as 24 bits                  |

#### **Zero Padding**

Pixel data being received by the MAX96793 can be zero padded as it enters a video pipe up to a resulting BPP of 16. With zero padding, an input with multiple BPP rates can be routed through its video pipe if the following conditions are met:

- 1.  $8 \le bpp \le 16$  for all incoming bpp rates that are routed to the video pipe

- a. Zero padding occurs after doubling. The 8 ≤ bpp ≤ 16 requirement applies to the resulting bpp after doubling.

- 2. Bandwidth is lost proportionally to the amount of zero padding. Some amount of GMSL3 bandwidth is dedicated to sending zeros instead of the original CSI-2 data. Ensure system bandwidth requirements can be met by using the calculations shown in the User Guide *Bandwidth Efficiency Optimization* section.

- 3. Video pipe Z's PCLK Drift detection must be disabled.

Zero padding applies to all data being routed in the pipe. When enabled, the pipe PCLK is set to the fastest incoming PCLK (smallest BPP) and all data within the pipe is treated as having a pixel width set by the BPP bitfield.

To enable zero padding, set AUTO\_BPP = 0, BPP = largest bpp in the pipe ( $\leq$ 16), soft\_bpp = smallest bpp in the pipe, and soft\_bpp\_en = b1. PCLK drift detection must also be disabled using the pipe's DRIFT\_DET\_EN bit. Using this method, all incoming data types with a BPP < BPP (Register) are zero padded so that all BPP rates within the pipe are equal. See *Table 10* for zero padding registers.

The zero-padded data is automatically recovered correctly on the deserializer based on the DT information that is automatically transmitted to the deserializer. But any DT that were "doubled" in the serializer must be "undoubled" in the deserializer.

Table 10. MAX96793 Zero Padding Registers

| Register | Bitfield Name | Bits | Default<br>Value | Decode                                          |

|----------|---------------|------|------------------|-------------------------------------------------|

| 0x110    | AUTO_BPP      | 3    | 0b1              | 0: Use BPP from BPP register                    |

|          |               |      |                  | 1: Use BPP from MIPI receiver                   |

| 0x111    | BPP           | 5:0  | 0b011000         | Number of bits per pixel (AUTO_BPP must = 0)    |

| 0x112    | DRIFT_DET_EN  | 1    | 0b1              | Enables PCLK frequency drift detection,         |

|          |               |      |                  | resets video pipeline upon error and reports it |

#### **Double Mode and Zero Padding Example**

EMB8, RAW12, and RAW16 share Pipe Z. EMB8 is doubled to 16BPP. RAW12 is zero padded to 16BPP. RAW16 is unmodified. All data types are 16BPP inside of the pipe. EMB8 is doubled rather than zero padded because doubling is more efficient than zero padding, and EMB8 (DBL) has a BPP equal to the largest BPP in the pipe (RAW16).

- 1. AUTO\_BPP = 0 Do not set BPP based on CSI-2 header (Pipe Z).

- 2. BPP = 0x10 Force Pipe Z BPP to 16 by zero-padding.

- 3. soft\_bppz = 0x0C This must be set to the smallest input BPP (before padding and after doubling).

- 4. soft\_bppz\_en = 1 This enables software override of BPP.

- 5. bpp8dblz = 1 This doubles all incoming BPP = 8 DTs.

- 6. DRIFT\_DET\_EN = 0 PCLK frequency drift detection is disabled for Pipe Z.

#### **Software Override**

The data type, virtual channel, and bpp overrides must be enabled to take effect. The following table are the required registers on the MAX96793.

Table 11. MAX96793 Software Override Registers

| Register | Bitfield Name  | Bits | Default<br>Value | Decode                                                                                                              |

|----------|----------------|------|------------------|---------------------------------------------------------------------------------------------------------------------|

| 0x031E   | soft_dtz_en    | 7    | 0b0              | 0 = Data type software override disabled on pipe Z<br>1 = Data type software override enabled on pipe Z             |

| 0x031E   | soft_vcz_en    | 6    | 0b0              | 0 = Virtual channel software override disabled on pipe Z<br>1 = Virtual channel software override enabled on pipe Z |

| 0x031E   | soft_bppz_en   | 5    | 0b0              | 0 = BPP software override disabled on pipe Z<br>1 = BPP software override enabled on pipe Z                         |

| 0x031E   | soft_bppz[4:0] | 4:0  | 0b11000          | These bits should be set to the smallest input BPP (before padding and after doubling).                             |

| 0x0320   | soft_vcz[1:0]  | 5:4  | 0b00             | 00 = VC0                                                                                                            |

|        |               |     |          | 01 = VC1                                                  |

|--------|---------------|-----|----------|-----------------------------------------------------------|

|        |               |     |          | 10 = VC2                                                  |

|        |               |     |          | 11 = VC3                                                  |

| 0x0323 | soft_dtz[5:0] | 5:0 | 0b110000 | These bits should be set to the appropriate data type ID. |

#### **Software Override Programming Examples**

Some examples of software override settings are as follows:

• DT: soft\_dtz[5:0]

DT = 0x24 = 0b100100 for RGB888

VC: soft\_vcz[1:0]

VC = 0x03 = 0b11 for VC3

• BPP: soft\_bppz[4:0]

BPP = 0xC = 0b01100 for RAW12

#### **Extended Virtual Channels**

Virtual channels allow the serial link system to differentiate video inputs by the VC assigned to them. When extended VCs are enabled, the standard 2-bit VC selection is extended to 4-bit (D-PHY), increasing the number of available VCs to 16 for D-PHY applications. The increase in available VCs allows systems to support more camera inputs.

Extended VCs are enabled by the ctrl1\_vcx\_en bit. Once this feature is enabled, VCs 0-16 can be accommodated on the serializer input. If this bit is disabled, the VC is limited to the least significant 2 bits. Virtual channel remapping is available if the incoming video streams cannot be changed at the video source.

The VC remapping is typically done at the deserializer but can be remapped on the serializer using ctrl1\_vc\_map\_en and ctrl1\_vc\_map0-15 bit fields. When the mapping is enabled, each ctrl1\_vc\_map field remaps its respective VC. For example, when ctrl1\_vc\_map0 bit field is set to 0101b, then the input VC0 would remap to VC5. Similarly, ctrl1\_vc\_map1 would allow for the remapping of input VC1.

Table 12. MAX96793 New Virtual Channel Mapping (Extended VC)

|          | CTRL1_VC_Map 0-15 |          |       |       |       |       |  |  |

|----------|-------------------|----------|-------|-------|-------|-------|--|--|

| VC Input | Ctrl1_vc_map      | VC Remap | Bit 7 | Bit 6 | Bit 5 | Bit 4 |  |  |

| 0        | ctrl1_vc_map0     | VC = 5   | 0     | 1     | 0     | 1     |  |  |

| 1        | ctrl1_vc_map1     | VC = 4   | 0     | 1     | 0     | 0     |  |  |

| 3        | ctrl1_vc_map3     | VC = 2   | 0     | 0     | 1     | 0     |  |  |

Table 13. MAX96793 Extended Virtual Channel Registers

| Register | Bits | Default Value | Description                                                      |

|----------|------|---------------|------------------------------------------------------------------|

| 0x0330   | 7    | 0             | Ctrl1_vcx_en: 0 = VC Extension Disabled 1 = VC Extension Enabled |

| 0x0331   | 5    | 0             | Ctrl1_vc_map_en: 0 = VC Remapping Disabled                       |

|        |     |      | 1 = VC Remapping Enabled                 |

|--------|-----|------|------------------------------------------|

| 0x0345 | 7:4 | 0x00 | Ctrl1_vc_map0:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC0  |

| 0x0346 | 7:4 | 0x00 | Ctrl1_vc_map1:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC1  |

| 0x0347 | 7:4 | 0x00 | Ctrl1_vc_map2:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC2  |

| 0x036C | 7:4 | 0x00 | Ctrl1_vc_map3:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC3  |

| 0x036D | 7:4 | 0x00 | Ctrl1_vc_map4:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC4  |

| 0x036E | 7:4 | 0x00 | Ctrl1_vc_map5:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC5  |

| 0x036F | 7:4 | 0x00 | Ctrl1_vc_map6:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC6  |

| 0x0377 | 7:4 | 0x00 | Ctrl1_vc_map7:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC7  |

| 0x0378 | 7:4 | 0x00 | Ctrl1_vc_map8:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC8  |

| 0x0379 | 7:4 | 0x00 | Ctrl1_vc_map9:                           |

|        |     |      | Bits [7:4]: New Virtual Channel for VC9  |

| 0x037A | 7:4 | 0x00 | Ctrl1_vc_map10:                          |

|        |     |      | Bits [7:4]: New Virtual Channel for VC10 |

| 0x037B | 7:4 | 0x00 | Ctrl1_vc_map11:                          |

|        |     |      | Bits [7:4]: New Virtual Channel for VC11 |

| 0x037C | 7:4 | 0x00 | Ctrl1_vc_map12:                          |

|        |     |      | Bits [7:4]: New Virtual Channel for VC12 |

| 0x037D | 7:4 | 0x00 | Ctrl1_vc_map13:                          |

|        |     |      | Bits [7:4]: New Virtual Channel for VC13 |

| 0x037E | 7:4 | 0x00 | Ctrl1_vc_map14:                          |

|        |     |      | Bits [7:4]: New Virtual Channel for VC14 |

| 0x037F | 7:4 | 0x00 | Ctrl1_vc_map15:                          |

|        |     |      | Bits [7:4]: New Virtual Channel for VC15 |

#### **Pixel Mode**

Pixel mode supports VC extension as well as overriding VC in the deserializer. If the incoming video source is using extended VCs, VCX needs to be enabled on the serializer and deserializer.

See *Table 13* for extended virtual channel and VC override registers details.

#### **Pixel Mode Programming Example**

This example enables the extended VCs on the MAX96793 and remaps VCs 0 and 1 to be 5 and 6.

# Turn on VC extension

0x80, 0x331, 0xB0

# Enable VC remapping

0x80, 0x330, 0x20

# VC remap of VC0 to VC5

0x80, 0x345, 0x50

# VC remap of VC1 to VC6

0x80, 0x346, 0x60

#### **Tunneling Mode**

Tunnel mode does not support overriding of the VC; however, it supports VC extension. If the incoming video source is using extended VCs, VCX needs to be enabled on serializer and deserializer.

#### **Tunneling Mode Programming Example**

0x04,0x80,0x03,0x31,0xB0, // ctrl1\_vcx\_en=1, enable VCX on Serializer controller 1

0x04,0x98,0x04,0x4A,0xD8, // CSI\_VCX\_EN=1, enable VCX on Deserializer controller 1

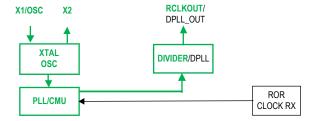

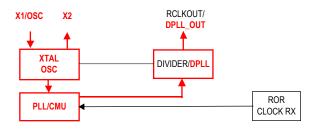

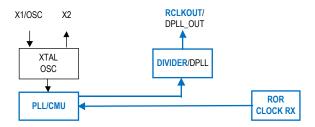

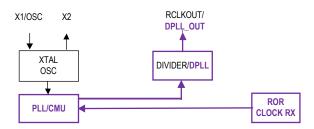

# MIPI Controller and PHY Settings MIPI PHY Settings

The MIPI PHY settings contain programming options for continuous vs. noncontinuous clock modes, number of lanes, lane mapping, polarity swapping, and port selection.

The MAX96793 CSI-2 to GMSL3 Serializer has two 2-lane capable MIPI PHYs (PHY 1, 2) controlled by one MIPI controllers (Ctrl 1) to establish up to one 4-lane input port. The 0 contains the MIPI PHY setting registers.

The 1x1, 1x2, 1x3, and 1x4 configurations use lane count settings. See *Table 14* for register write details.

Table 14. MAX96793 MIPI PHY Setting Registers

| Register | Bitfield Name        | Bits | Default Value | Description                                      |

|----------|----------------------|------|---------------|--------------------------------------------------|

| 0x0330   | mipi_noncontclk_en   | 6    | 0b0           | 0 = enables MIPI continuous clock                |

|          |                      |      |               | 1 = enables MIPI noncontinuous clock             |

| 0x0330   | ctrl1_vc_map_en      | 5    | 0b0           | 0 = disables VC mapping                          |

|          |                      |      |               | 1 = enables VC mapping                           |

| 0x0330   | mipi_rx_reset        | 3    | 0b0           | 0 = do not reset MIPI receiver                   |

|          |                      |      |               | 1 = resets MIPI receiver                         |

|          |                      |      |               | (This bit should be toggled HIGH and then LOW    |

|          |                      |      |               | before any video is received—per errata.)        |

| 0x0330   | phy_config[2:0]      | 2:0  | 0b000         | 0 = 1x4 (only available option)                  |

| 0x0331   | ctrl1_vcx_en         | 7    | 0b0           | 0 = extended VC disabled                         |

|          |                      |      |               | 1 = extended VC enabled                          |

| 0x0331   | ctrl1_deskewen       | 6    | 0b0           | 0 = deskew calibration disabled                  |

|          |                      |      |               | 1 = deskew calibration enabled                   |

| 0x033C,  | phy{1,2}_hs_err[7:6] | 7:6  | 0b0000        | Bit 7 represents lane 0, Bit 6 represents lane 1 |

| 0x033E   |                      |      |               | 0 = Deskew calibration pattern flag not received |

|          |                      |      |               | 1 = Deskew calibration pattern flag received     |

| 0x033C,  | phy{1,2}_hs_err[5:4] | 5:4  | 0b0000        | Bit 5 represents lane 0, Bit 4 represents lane 1 |

| 0x033E   |                      |      |               | 0 = Default                                      |

|          |                      |      |               | 1 = Deskew calibration failure                   |

| 0x0331   | ctrl1_num_lanes[1:0] | 5:4  | 0b11          | 00 = 1 data lane                                 |

|          |                      |      |               | 01 = 2 data lanes                                |

|         |                    |     |        | 10 = 3 data lanes                                  |

|---------|--------------------|-----|--------|----------------------------------------------------|

|         |                    |     |        | 11 = 4 data lanes                                  |

| 0x0332  | phy1_lane_map[3:2] | 7:6 | 0b11   | 00 = map lane0 to lane3                            |

|         |                    |     |        | 01 = map lane1 to lane3                            |

|         |                    |     |        | 10 = map lane2 to lane3                            |

|         |                    |     |        | 11 = map lane3 to lane3                            |

| 0x0332  | phy1_lane_map[1:0] | 5:4 | 0b10   | 00 = map lane0 to lane2                            |

|         |                    |     |        | 01 = map lane1 to lane2                            |

|         |                    |     |        | 10 = map lane2 to lane2                            |

|         |                    |     |        | 11 = map lane3 to lane2                            |

| 0x0333  | phy2_lane_map[3:2] | 3:2 | 0b01   | 00 = map lane0 to lane1                            |

|         |                    |     |        | 01 = map lane1 to lane1                            |

|         |                    |     |        | 10 = map lane2 to lane1                            |

|         |                    |     |        | 11 = map lane3 to lane1                            |

| 0x0333  | phy2_lane_map[1:0] | 1:0 | 0b00   | 00 = map lane0 to lane0                            |

|         |                    |     |        | 01 = map lane1 to lane0                            |

|         |                    |     |        | 10 = map lane2 to lane0                            |

|         |                    |     |        | 11 = map lane3 to lane0                            |

| 0x0334  | phy1_pol_map[1]    | 5   | 0b0    | 0 = normal polarity for data lane 3                |

|         |                    |     |        | 1 = inverse polarity for data lane 3               |

| 0x0334  | phy1_pol_map[0]    | 4   | 0b0    | 0 = normal polarity for data lane 2                |

|         |                    |     |        | 1 = inverse polarity for data lane 2               |

| 0x0335  | phy2_pol_map[2]    | 2   | 0b0    | 0 = normal polarity for clock lane                 |

|         |                    |     |        | 1 = inverse polarity for clock lane                |

| 0x0335  | phy2_pol_map[1]    | 1   | 0b0    | 0 = normal polarity for data lane 1                |

|         |                    |     |        | 1 = inverse polarity for data lane 1               |

| 0x0335  | phy2_pol_map[0]    | 0   | 0b0    | 0 = normal polarity for data lane 0                |

|         |                    |     |        | 1 = inverse polarity for data lane 0               |

| 0x0345- | ctrl1_vc_map{0,15} | 7:4 | 0b0000 | VC reassignment registers. See the <i>Extended</i> |

| 0x0347, |                    |     |        | Virtual Channels section for description.          |

| 0x036C- |                    |     |        |                                                    |

| 0x036F, |                    |     |        |                                                    |

| 0x0377- |                    |     |        |                                                    |

| 0x037F  |                    |     |        |                                                    |

#### **MIPI Data Lane and Polarity Swap**

The MAX96793 supports lane swapping for pins on the same MIPI port.

The data pins can be swapped within each port, but the clock location is fixed. For example, in 2x4 mode, the default mappings of the D0, D1, D2, and D3 pairs can be swapped to different output pins. Additionally, the polarity of each output data and clock pair can be inverted.

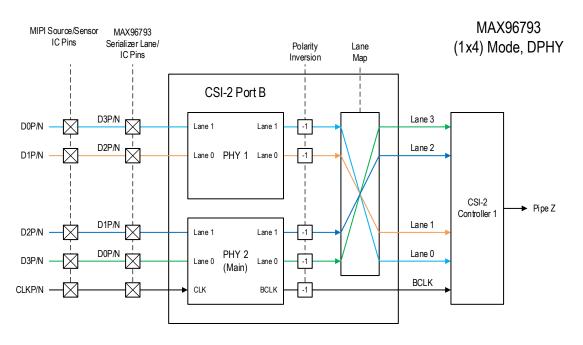

See *Table 14* for relevant registers. *Figure 6* shows the default lane mapping that matches device pinout. *Figure 7* demonstrates the polarity swap exatabe.

Figure 6. MAX96793 1x4 DPHY Default Lane Mapping

Figure 7. MAX96793 1x4 DPHY Lane Swap Example

#### **Lane Swap Programming Example**

Figure 7 lane swap example register writes are seen in the following description.

#SER I2C Address=0x80

# Set lane mapping for all 4 lanes on ctrl 1. This is written to completely swap the device pinout from default as shown in the figure.

0x80,0x0332,0x10 #D0 mapped to D3, D1 mapped to D2

0x80,0x0333,0x0B #D2 mapped to D1, D3 mapped to D0

#### **MIPI D-PHY Deskew Settings**

The D-PHY deskew mechanism is only relevant to lane speeds greater than 1.5Gbps per lane (Deskew optional for data rates below 1.5Gbps/lane). Periodic deskew requires a continuous clock and the clock lane always in the high-speed mode. Deskew is initiated by the transmitter under CSI-PPI control.

The MAX96793 serializer only has one bit for enabling deskew calibration (ctrl1\_deskewen) which can be found in REG 0x331. See *Table 14* for more information.

#### **Deskew Register Example**

#SER I2C Address=0x80

# Enable deskew calibration on the serializer

0x80, 0x331, 0x70

# I<sup>2</sup>C Control Channels

#### **Overview**

The primary I<sup>2</sup>C control channel is used to provide access to both serializer and deserializer registers across the GMSL link. This provides flexibility where the registers for both serializer and deserializer are accessible from whichever side the main microcontroller resides (for camera applications, the main microcontroller typically resides on the deserializer side).

The pass-through I<sup>2</sup>C channels are used to send I<sup>2</sup>C data across the GMSL Link. The pass-through channels can access the remote-side devices connected through the corresponding pass-through ports but cannot access the serializer or deserializer registers.

When making changes to any of the serializer's or deserializer's I<sup>2</sup>C configuration, such as enabling or disabling an I<sup>2</sup>C channels, a 10µs delay from the write acknowledgment (ACK) to the next transaction is required.

# **Port Access and Routing**

The multifunction pins (MFPs) shown in *Table 15* are used for the I<sup>2</sup>C primary and pass-through channels.

Table 15. MAX96793 MFPs for I<sup>2</sup>C

| MFP<br>Pin | Default Function | I <sup>2</sup> C Function #1 | I <sup>2</sup> C Function #2 | Notes                                                 |

|------------|------------------|------------------------------|------------------------------|-------------------------------------------------------|

| MFP7       | GPI7             | SDA1_RX1                     | N/A                          | Enables I <sup>2</sup> C pass-<br>through by register |

| MFP8  | GPIO         | SCL1_TX1     | N/A      | Enables I <sup>2</sup> C pass-    |

|-------|--------------|--------------|----------|-----------------------------------|

|       |              |              |          | through by register               |

| MFP9  | SDA_RX or RX | SDA_RX or RX | SDA2_RX2 | I <sup>2</sup> C or UART function |

|       |              |              |          | selected by CFG0 pin or           |

|       |              |              |          | Enables I <sup>2</sup> C pass-    |

|       |              |              |          | through by register               |

| MFP10 | SCL_TX or TX | SCL_TX or TX | SCL2_TX2 | I <sup>2</sup> C or UART function |

|       |              |              |          | selected by CFG0 pin or           |

|       |              |              |          | Enables I <sup>2</sup> C pass-    |

|       |              |              |          | through by register               |

On power-up, the device should be set to I<sup>2</sup>C mode by the CFG0 latch. The function names in the MFPs table and following I<sup>2</sup>C sections assume that the device has been configured for I<sup>2</sup>C mode.

By default, the primary I<sup>2</sup>C control channel lines are brought out on MFP9 and MFP10 for SDA and SCL, respectively. The user can disable the primary control channel's line access by setting field DIS\_LOCAL\_CC in register 0x1. Also, the access to remote device control can be disabled by setting field DIS\_REM\_CC in register 0x1.

# **CRC for I<sup>2</sup>C and Message Counter Transactions**

The MAX96793 devices have the option to add CRC and a message counter to the I<sup>2</sup>C interface. The interface protocols are the same as in legacy designs, but there are new bytes introduced in the packets to support CRC and a message counter. The ECU and SerDes device each keep a copy of a message counter, which increments each transaction. The message counter and CRC bytes are sent in each transaction to ensure data integrity. Features are available only on primary I<sup>2</sup>C control channel, not supported for pass-through channels. Features are disabled by default and need to be enabled with register writes.

Note: These features can only be used with I<sup>2</sup>C host controller that supports addition of this CRC.

#### CRC for I<sup>2</sup>C Transactions

The CRC feature is used to detect corrupt data written on the serializer's primary I<sup>2</sup>C control channel. Each I<sup>2</sup>C transaction has a corresponding CRC packet associated with it. If a CRC is detected, the command is not executed, and the transaction is reported as Not Acknowledge (NACK).

The MAX96793 CRC feature is enabled by setting fields CC\_CRC\_EN and CC\_CRC\_MSGCNTR\_OVR in register 0x4.

#### Message Counter for I<sup>2</sup>C Transactions

The message counter feature is used to detect missing or repeated I<sup>2</sup>C transactions. For every transaction, the message counter is incremented accordingly while a copy of the counter is maintained on both ends of the I<sup>2</sup>C link. If a mismatch between copies is found, then the transaction is rejected.

The MAX96793 message counter feature is enabled by setting fields CC\_MSGCNTR\_EN and CC\_CRC\_MSGCNTR\_OVR in register 0x4.

#### **Enabling CRC for I<sup>2</sup>C and Message Counter**

Following are the register writes to enable CRC for I<sup>2</sup>C and Message counter for primary I<sup>2</sup>C control channel.

(This only works with I<sup>2</sup>C host controller that supports CRC/Message counter.)

#SER I2C Address=0x80

#Enable CRC and Message Counter on SER in XTAL Mode

0x80,0x4,0x1D

# I<sup>2</sup>C Registers

*Table 16* has registers that are needed to enable/disable primary and pass-through I<sup>2</sup>C channels.

Table 16. MAX96793 I<sup>2</sup>C Registers

| Register | Bits | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0001   | 7:4  | 0x08          | Bit [7]: Enables pass-through I <sup>2</sup> C Control Channel 2 (SDA2, SCL2) Bit [6]: Enables pass-through I <sup>2</sup> C Control Channel 1 (SDA1, SCL1) Bit [5]: Disables main I <sup>2</sup> C Control Channel connection to SDA and SCL pins Bit [4]: Disables access to remote device Control Channel over GMSL3 connection                                                                           |

| 0x0004   | 4:2  | 0x18          | Enable CRC and Message Counter Register: Bit [4]: Enables I <sup>2</sup> C message counter. Note: Only active when Bit [2] is also set to 1. Bit [3]: Enables I <sup>2</sup> C CRC packeting. Note: Only active when Bit [2] is also set to 1. Bit [2]: Enables manual override of I <sup>2</sup> C CRC or message counter configuration. If set to a 0, then CRC and message counter features are disabled. |

| 0x0006   | 4    | 0x80          | I <sup>2</sup> C Selection Register: Bit [4]: Enables I <sup>2</sup> C when set to a 1 or UART when set to a 0 Note: This bit is set according to the CFG0 pin value on power-up. Writing to this register is not recommended.                                                                                                                                                                               |

| 0x1D00   | 3    | 0x00          | <b>Enable CRC Computation Register:</b> Bit [3]: Computes register CRC after every I <sup>2</sup> C register write                                                                                                                                                                                                                                                                                           |

| 0x1D08   | 0    | 0x00          | Message Counter Reset Register: Bit [0]: Resets Message Counter value to 0                                                                                                                                                                                                                                                                                                                                   |

| 0x1D09   | 1:0  | 0x00          | CRC Reset Register: Bit [1]: Resets Message Counter error count to 0 Bit [0]: Resets CRC error count to 0.                                                                                                                                                                                                                                                                                                   |

| 0x1D0A   | 7:0  | 0x00          | Read CRC Value Register: Bits [7:0]: CRC value for the last write transaction                                                                                                                                                                                                                                                                                                                                |

| 0x1D0B   | 7:0  | 0x00          | Read Message Counter Low Bits Register: Bits [7:0]: Low bits of current message counter value                                                                                                                                                                                                                                                                                                                |

| 0x1D0C   | 7:0  | 0x00          | Read Message Counter High Bits Register: Bits [7:0]: High bits of current message counter value                                                                                                                                                                                                                                                                                                              |

# **Enabling I<sup>2</sup>C Pass-Though Channels**

When enabling an I<sup>2</sup>C pass-through channel, other MFP functions must be disabled first.

With the MAX96793, the user can bring out the first pass-through I<sup>2</sup>C channel (SDA1\_RX1/SCL1\_TX1) on MFP7/MFP8. The second pass-through I<sup>2</sup>C channel (SDA2\_RX2/SCL2\_TX2) can be programmed on MFP9/MFP10. Pass-through channels are enabled by setting the fields IIC\_1\_EN and IIC\_2\_EN in register 0x1.

# **Control Channel Programming Example**

The following example shows the register writes needed to enable I<sup>2</sup>C pass-through channel 1 on the MAX96793.

#DES I2C Address=0x98

#SER I2C Address=0x80

#Enable I2C Pass-through channel 1 on DES

0x98,0x0001,0x42

#Disable UART Pass-through channel 1 on DES

0x98,0x0003,0x43

#Enable I2C Pass-through channel 1 on SER

0x80,0x0001,0x48

# I<sup>2</sup>C Broadcasting

#### **Overview**

When transmitting to a multiple-link input deserializer or multiple deserializers, each device on the serializer side requires a unique address for individual programming and identification. Through I<sup>2</sup>C translation and address reassignment, each serializer and image sensor can have both a unique address and a broadcasting address. This allows for selective programming of each device and the ability to broadcast commands to all devices simultaneously. When broadcasting, if any remote GMSL I<sup>2</sup>C port ACKs the packet, it ACKs for all remote GMSL I<sup>2</sup>C ports.

**Note**: When making changes to any of the serializer or deserializer's  $I^2C$  configuration, such as enabling or disabling an  $I^2C$  port, at least a 10 $\mu$ s delay from the write ACK to the next transaction is required.

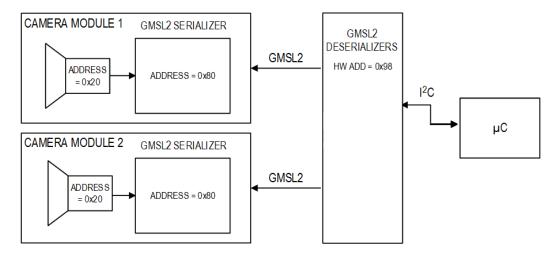

An example of I<sup>2</sup>C broadcasting is discussed in the following section. Two equivalent camera modules, including an image sensor and GMSL3 serializer with the same respective addresses, are connected to two GMSL3 deserializers with different device addresses. Each of the camera modules comprises a serializer at the default I<sup>2</sup>C address 0x80 and an image sensor at address 0x20.

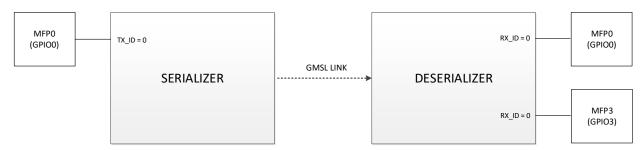

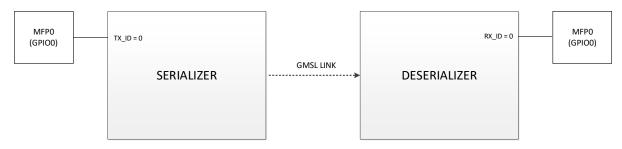

Figure 8. I<sup>2</sup>C Interfaced Camera-Module System with Default Address Settings and Dual Deserializer

#### **I2C Broadcasting Technique**

The I<sup>2</sup>C broadcasting technique helps to communicate with multiple camera-serializer modules with a single microcontroller, which in turn streamlines the transmission process.

The general procedure is to:

- Isolate a single camera/serializer module for remote I<sup>2</sup>C access, meaning no other device with the same address should be connected to the I<sup>2</sup>C data line.

- Change the serializer address to a unique address.

- Modify the first I<sup>2</sup>C address translation register with a common source address but the unique destination address. This is to streamline the interface with the serializer.

- Modify the second I<sup>2</sup>C address translation register with a unique source address but the default image sensor addresses for the destination address. This is to streamline the interface with the image sensor.

- Repeat this process for each camera serializer module.

**Note**: When making changes to any of the serializer or deserializer's  $I^2C$  configuration, such as enabling or disabling an  $I^2C$  port, at least a 10 $\mu$ s delay from the write ACK to the next transaction is required.

#### I<sup>2</sup>C Broadcasting GMSL3 Use Case Example

The procedure for the I<sup>2</sup>C broadcasting example is as follows:

- Isolate camera module 1 by disabling camera module 2's GMSL link (RESET\_LINK = 1).

- Change the serializer device address in camera module 1 from 0x80 to 0x82. This is done with a register write to DEV\_ADDR[6:0] located in REG0.

- Modify the first address translation register in this serializer to give a broadcast address (0xC4) to the serializer. Program 0xC4 into the source register SRC\_A[6:0], and 0x82 in the destination register DST\_A[6:0]. Thus, for the serializer in camera module 1, anything sent to address 0xC4 is sent to address 0x82 instead.

- Modify the second translation register in this serializer to give a unique address to the image sensor. Program 0x22 into the source register SRC\_B[6:0] and 0x20 into the destination register DST\_B[6:0]. Thus, for the serializer in camera module 1, anything sent to address 0x22 is sent to address 0x20 instead.

- Isolate camera module 2 by disabling camera module 1's GMSL link (RESET\_LINK = 1) and enabling camera 2's GMSL link (RESET\_LINK = 0).

- Change the serializer device address in camera module 2 from 0x80 to 0x84. This is done with a register write to DEV\_ADDR[6:0] located in REG0.

- Modify the first address translation register in this serializer to give a broadcast address (0xC4) to the serializer. Program 0xC4 into the source register SRC\_A[6:0] and 0x84 in the destination register DST\_A[6:0]. Thus, for the serializer in camera module 2, anything sent to address 0xC4 is sent to address 0x84 instead.

- Modify the second translation register in this serializer to give a unique address to the image sensor. Program 0x24 into the source register SRC\_B[6:0] and 0x20 into the destination register DST\_B[6:0]. Thus, for the serializer in camera module 2, anything sent to address 0x24 is sent to address 0x20 instead.

- Now, enable all the links for remote primary I<sup>2</sup>C port access.

- All devices should be present on the I<sup>2</sup>C bus. Continue with any additional required system configuration.

Figure 9. Two Camera-Module System with Translated Address Settings and Dual Deserializer

Table 17. I<sup>2</sup>C Broadcasting Example - Serializer

| Old I <sup>2</sup> C Address | New I <sup>2</sup> C Address | SRC_A<br>(SER, 0x42) | DST_A<br>(SER, 0x43) | Sink Devices                  |

|------------------------------|------------------------------|----------------------|----------------------|-------------------------------|

| 0x80                         | 0x82                         | 0xC4                 | 0x82                 | Serializer in Camera Module 1 |

| 0x80                         | 0x84                         | 0xC4                 | 0x84                 | Serializer in Camera Module 2 |

0 shows how the serializers are assigned a single device address to allow writes to all devices as a broadcast. This allows I<sup>2</sup>C host controller to broadcast with address 0xC4.

Table 18. I<sup>2</sup>C Broadcasting Example - Image Sensor

| Old I <sup>2</sup> C Address | New I <sup>2</sup> C Address | SRC_B<br>(SER, 0x44) | DST_B<br>(SER, 0x45) | Sink Devices                  |  |  |

|------------------------------|------------------------------|----------------------|----------------------|-------------------------------|--|--|

| 0x20                         | 0x22                         | 0x22                 | 0x20                 | Serializer in Camera Module 1 |  |  |

| 0x20                         | 0x24                         | 0x24                 | 0x20                 | Serializer in Camera Module 2 |  |  |

*Table 18* shows how each image sensor is assigned a unique device address. This allows I<sup>2</sup>C host controller to isolate I<sup>2</sup>C commands to only one image sensor.

#### I<sup>2</sup>C Broadcasting Programming Example

This script sets up the I<sup>2</sup>C broadcasting as shown in *Figure 9*.

#DES I2C Address=0x98

# Disable GMSL Link B

0x98,0x0013,0x1

# Change I2C address for this Link A serializer

0x80,0x0000,0x82

# Set Ser source to 0xC4

0x82,0x0042,0xC4

# Set Ser destination to 0x82

0x82,0x0043,0x82

# Set Image sensor source to 0x22

0x82,0x0044,0x22

# Set Image sensor destination to 0x20

0x82,0x0045,0x20

# Enable GMSL Link B

0x98,0x0013,0x10

# Disable GMSL Link A

0x98,0x0010,0x51

# Change I2C address for this Link B serializer

0x80,0x0000,0x84

# Set Ser source to 0xC4

0x84,0x0042,0xC4

# Set Ser destination to 0x84

0x84,0x0043,0x84

# Set Image sensor source to 0x24

0x84,0x0044,0x24

# Set Image sensor destination to 0x20

0x84,0x0045,0x20

# Enable GMSL Link A

0x98,0x0010,0x31

#### **UART Control Channel**

#### **Overview**

The primary universal asynchronous receiver/transmitter (UART) control channel is used to provide access to both serializer and deserializer registers across the GMSL link. This provides flexibility where the registers for both serializer and deserializer are accessible from whichever side the main microcontroller resides (for camera applications, the main microcontroller typically resides on the deserializer side).

The pass-through UART channels are used to send UART data across the GMSL Link. The pass-through channels can access the remote-side devices connected through the corresponding pass-through ports but cannot access the serializer or deserializer registers.

**Note**: When making changes to any of the serializer or deserializer's UART configuration, such as enabling or disabling an UART channels, a 10µs delay from the write ACK to the next transaction is required.

#### **Base Mode**

Base mode allows the device registers of both the serializer and the deserializer to be accessed by the host microcontroller. It is the default mode for the primary UART control channel on power-up.

# **Bypass Mode**

In the bypass mode, both the serializer and deserializer ignore all UART commands from the microcontroller. The serializer/deserializer registers are not accessible and the microcontroller can freely communicate with any peripherals using its defined UART protocol. In this mode, the UART commands are still sent over the GMSL3 link. This mode prevents inadvertent programming of the serializer/deserializer registers and can be switched in and out of during normal operation.

# **Port Access and Routing**

The MFPs shown in *Table 19* are used for the UART primary and pass-through channels.

Table 19. MAX96793 MFP Pins for UART

| MFP<br>Pin | Default Function | UART Function #1 | UART Function #2 | Notes                                                                                                     |

|------------|------------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------|

| MFP7       | GPI7             | RX1              | N/A              | Enables UART pass-<br>through by register                                                                 |

| MFP8       | GPIO             | TX1              | N/A              | Enables UART pass-<br>through by register                                                                 |

| MFP9       | SDA_RX or RX     | SDA_RX or RX     | RX2              | I <sup>2</sup> C or UART function<br>selected by CFG0 pin or<br>Enables UART pass-<br>through by register |

| MFP10      | SCL_TX or TX     | SCL_TX or TX     | TX2              | I <sup>2</sup> C or UART function<br>selected by CFG0 pin or<br>Enables UART pass-<br>through by register |

On power-up, the device should be set to UART mode by the CFG0 latch. The function names in this MFP table and following UART sections assume the device has been configured for UART mode.

By default, the primary UART control channel lines are brought out on MFP9 and MFP10 for RX and TX, respectively. The user can disable the primary control channel's line access by setting field DIS\_LOCAL\_CC in register 0x01. One can also disable access to remote device control by setting field DIS\_REM\_CC in register 0x01.

# **CRC for UART and Message Counter Transactions**

The MAX96793 devices have the option to add CRC and a message counter to the UART interface. The interface protocols are the same as in legacy designs, but there are new bytes introduced in the packets to support CRC and a message counter. The ECU and SerDes device each keep a copy of a message counter, which increments each transaction. The message counter and CRC bytes are sent in each transaction to ensure data integrity. Features are available only on primary UART control channel, not supported for pass-through channels. Features are disabled by default and need to be enabled with register writes.

Note: These features can only be used with UART Host controller that supports addition of this CRC.

#### **CRC for UART Transactions**

The CRC feature is used to detect corrupt data written on the UART control channel. Each UART transaction has a corresponding CRC packet associated with it. The host microcontroller must compute and send a CRC byte after each data byte.

- If the host microcontroller is writing to the serializer registers, then the serializer receives the data byte, calculates the CRC using an identical CRC engine, and verifies a match before accepting the data byte. If a mismatch is detected, then the write is not accepted, and the error counter is incremented.

- If the host microcontroller is reading the serializer registers, then the serializer calculates the CRC byte and appends it to the output data stream. The host microcontroller's CRC engine should then calculate its own CRC byte and compare it with the one received from the serializer to determine if there is a mismatch.

The MAX96793 CRC feature is enabled by setting fields CC\_CRC\_EN and CC\_CRC\_MSGCNTR\_OVR in register 0x4.

#### **Message Counter for UART Transactions**

The message counter feature is used to detect missing or repeated UART transactions. For every transaction, the message counter is incremented accordingly while a copy of the counter is maintained on both ends of the UART transaction. If a mismatch between copies is found, then the transaction is rejected.

The MAX96793 message counter feature is enabled by setting fields CC\_MSGCNTR\_EN and CC\_CRC\_MSGCNTR\_OVR in register 0x4.

#### **Enabling CRC for UART and Message Counter**

Following are the register writes to enable CRC for UART and Message counter for primary UART control channel. (It only works with UART Host controller that supports CRC/Message counter.)

#SER UART Address=0x80

#Enable CRC and Message Counter on SER in XTAL Mode

0x98,0x4,0x1D

# **UART Registers**

The following table has registers that are needed to enable/disable primary and pass-through UART channels.

#### Table 20. MAX96793 UART Registers

| Register | Bits | Default Value | Description                                                                                       |

|----------|------|---------------|---------------------------------------------------------------------------------------------------|

| 0x0001   | 5:4  | 0x08          | UART Control Channel Enable Register:                                                             |

|          |      |               | Bit [5]: Disables main UART Control Channel connection to                                         |

|          |      |               | TX/RX pins                                                                                        |

|          |      |               | Bit [4]: Disables access to remote device control channel over                                    |

|          |      |               | GMSL3 connection                                                                                  |

| 0x0003   | 5:4  | 0x00          | UART Pass-Through Channel Enable Register:                                                        |