## Evaluating the AD4884, Dual-Channel 16-Bit, 20MSPS, SAR ADC with Analog Front End

### FEATURES

- ▶ Fully-featured evaluation board for the [AD4884](#)

- ▶ [Analysis | Control | Evaluation \(ACE\) Software](#) plug-in available for device configuration, data capture, and performance evaluation

- ▶ Flexible analog front end

- ▶ On-board power solution and precision reference

- ▶ On-board clock generation circuitry with sampling frequency control via the ACE software

- ▶ FMC compatible

### EVALUATION KIT CONTENTS

- ▶ EVAL-AD4884-FMCZ evaluation board

- ▶ Micro-SD memory card with SD adapter, containing system board boot software and Linux OS

- ▶ PCB stand-offs

### EQUIPMENT NEEDED

- ▶ PC running Windows® 10 operating system or higher

- ▶ Digilent ZedBoard with 12V wall adapter power supply

- ▶ Precision signal source

- ▶ SMA cables to connect a signal source to the EVAL-AD4884-FMCZ

### DOCUMENTS NEEDED

- ▶ AD4884 data sheet

### GENERAL DESCRIPTION

The EVAL-AD4884-FMCZ evaluation board is designed to demonstrate the performance of the AD4884 dual channel ADC with integrated analog front end (AFE) and provide access to a limited set of features from the chip in the ACE software environment. The EVAL-AD4884-FMCZ evaluation kit supports the following AD4884 features:

- ▶ Low-voltage digital signaling (LVDS) data output interface.

- ▶ Analog-to-digital converter (ADC) configuration via serial peripheral interface (SPI).

- ▶ Internal or external generation of 1.1V regulated supply rails.

- ▶ Sampling rate capability between 1.25MSPS and 20MSPS.

The EVAL-AD4884-FMCZ evaluation board is designed for use with the Digilent ZedBoard via the field programmable gate array (FPGA) mezzanine card (FMC) connector. The ZedBoard uses a Xilinx Zynq7000 system on chip (SoC) that runs Analog Devices, Inc., Kuiper Linux and LIBIIO included on the SD card supplied in the evaluation board kit to facilitate communication with the EVAL-AD4884-FMCZ, enabling ADC configuration and data capture. The ZedBoard also provides the communication link to the host PC and the **ACE Software** plug-in.

Full specifications on the AD4884 are available in the AD4884 data sheet available from Analog Devices, Inc., and must be consulted with this user guide when using the EVAL-AD4884-FMCZ evaluation board.

For the current schematics, layouts, and bill of materials, refer to the EVAL-AD4884-FMCZ product page.

**TABLE OF CONTENTS**

|                                      |   |                                                  |    |

|--------------------------------------|---|--------------------------------------------------|----|

| Features.....                        | 1 | Digital Interface.....                           | 6  |

| Evaluation Kit Contents.....         | 1 | Evaluation Hardware Setup Procedure.....         | 7  |

| Equipment Needed.....                | 1 | Software Support.....                            | 8  |

| Documents Needed.....                | 1 | Evaluation Software.....                         | 8  |

| General Description.....             | 1 | Embedded Software.....                           | 8  |

| EVAL-AD4884-FMCZ Evaluation Board    |   | Host PC Software.....                            | 8  |

| Photograph.....                      | 3 | Evaluating the AD4884 with the ACE Software..... | 9  |

| Evaluation Board Hardware Guide..... | 4 | AD4884 Memory Maps.....                          | 9  |

| Hardware Overview.....               | 4 | ANALYSIS Tab.....                                | 10 |

| Input Stage.....                     | 5 | Time Domain (Waveform) Plot.....                 | 10 |

| Gain Configuration.....              | 5 | Frequency Domain (FFT) Plot.....                 | 11 |

| Voltage Reference.....               | 5 | Histogram Plot.....                              | 11 |

| Power Supplies.....                  | 6 | Configuring the AD4884 Integrated Digital        |    |

| ADC Power Supplies.....              | 6 | Filters.....                                     | 12 |

| Amplifier Power Supplies.....        | 6 |                                                  |    |

| Conversion and Data Clock Generation |   |                                                  |    |

| Circuit.....                         | 6 |                                                  |    |

**REVISION HISTORY****1/2026—Revision 0: Initial Version**

## EVAL-AD4884-FMCZ EVALUATION BOARD PHOTOGRAPH

Figure 1. EVAL-AD4884-FMCZ Evaluation Board Photograph

## EVALUATION BOARD HARDWARE GUIDE

### HARDWARE OVERVIEW

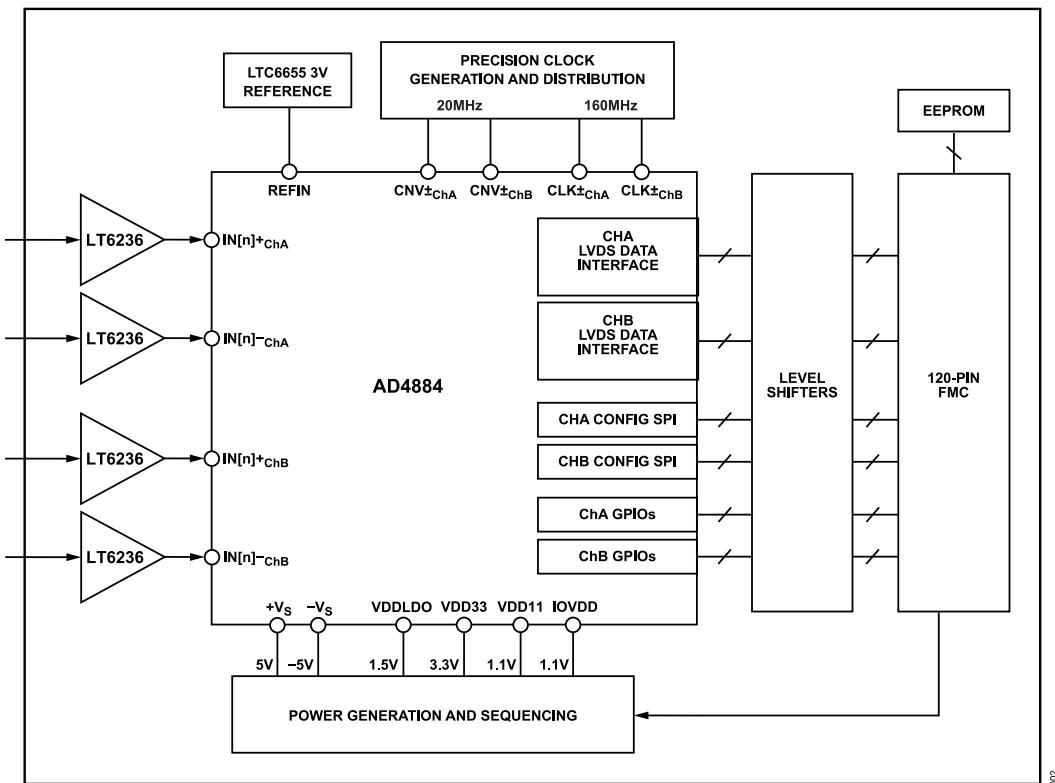

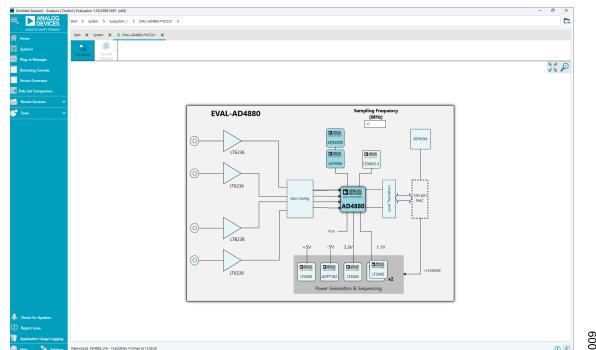

A simplified block diagram of the EVAL-AD4884-FMCZ hardware is shown in [Figure 2](#). This evaluation board showcases the performance and features of the [AD4884](#) and highlights the recommended companion components.

The EVAL-AD4884-FMCZ enables simple evaluation of the AD4884. All circuitry necessary to operate the ADC is included on the EVAL-AD4884-FMCZ.

*Figure 2. Simplified Block Diagram of the EVAL-AD4884-FMCZ*

## EVALUATION BOARD HARDWARE GUIDE

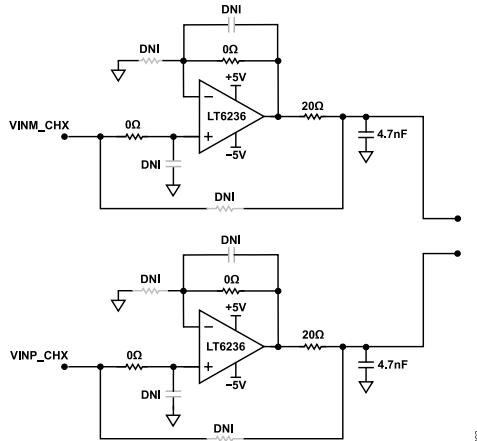

### INPUT STAGE

The input stage for each AD4884 channel consists of a pair of LT6236 op amps (U22 and U23, U32 and U33). The LT6236 is selected for its exceptional wideband (90MHz), low noise, favorable distortion performance and low power consumption. The op amps are setup as unity-gain buffers, ensuring that a preceding signal source or sensor is presented with a high impedance. With supply rail values of +5V and -5V, the valid range at each input of this stage is -3V to +3.7V (factoring in the input requirements of both LT6236 and the FDA inside AD4884). As long as this valid range is respected, there is freedom to set the common mode of the driving signal. The input stage is designed in principle to take in a fully-differential signal, with a differential voltage span of  $\pm 2.91V$ , the full span of the ADC is exercised. A single-ended signal can also be applied at the input, but modifications such as adding gain or a bias level to one of the op amps might be needed to exercise the full span of the ADC, depending on the input signal characteristics.

Figure 3. Input Stage Simplified Schematic for One Channel

The following can be configured in this stage:

- ▶ Stage bandwidth

- ▶ Additional band limiting through RC input filter and/or capacitors across amplifier feedback

- ▶ Stage gain

- ▶ Unity gain (default)

- ▶ Non-inverting gain setting

- ▶ Stage bypass

- ▶ No bypass (default)

- ▶ Bypass

- ▶ Bypass via amplifier mezzanine card (AMC), this is an option for Channel A only

### GAIN CONFIGURATION

By default, EVAL-AD4884-FMCZ is configured with a gain of 1.03x, and 220pF capacitors (C52, C53, C54, and C55) fitted for noise filtering across the feedback network of the AD4884 on-chip FDAs.

In this default configuration, an SNR of around 91.9dB is typically expected.

Changing the gain at the AD4884 FDA stage requires light rework on the PCB (removing/adding 0402 SMD resistors and/or shorting 0402 solder pads), to modify the arrangement of the internal AD4884 gain-setting resistors. For the possible gain options and node shorting requirements, refer to the AD4884 data sheet.

### VOLTAGE REFERENCE

The AD4884 requires an external 3V voltage reference. To achieve the specified performance, a suitable precision, low-noise voltage reference must be used. The ADC does include an internal reference buffer and capacitor, which makes reference selection easier and eliminates the need for an external buffer.

The following can be configured in this circuit:

#### ▶ Reference selection

- ▶ The LTC6655-3 is the default. The evaluation hardware includes LTC6655-3 (U40) as the primary recommended option, providing exceptional noise performance (0.1Hz to 10Hz noise specification of 0.25ppm p-p), combined with an initial accuracy of 0.025%, and a low temperature drift of 2ppm/°C.

- ▶ The LT6657-3 (U41) is also mounted and provided as a second option. For a comparison of recommended references, see Table 1.

Table 1. 3V Reference Comparison of the LT6657 and LTC6655

| Parameter                        | LT6657          | LTC6655         |

|----------------------------------|-----------------|-----------------|

| Accuracy                         | 0.10%           | 0.025%          |

| Temperature Coefficient (ppm/°C) | 1.5             | 2               |

| 0.1Hz to 10Hz Noise (ppm p-p)    | 0.5             | 0.25            |

| Maximum Load (mA)                | ±10             | ±5              |

| Load Regulation (ppm/mA)         | 0.7             | 3               |

| Maximum Supply                   | 40V             | 13.2V           |

| Shutdown                         | Yes             | Yes             |

| Reverse Supply Protected         | Yes             | No              |

| Reverse Output Protected         | Yes             | No              |

| Current Limit                    | Yes             | Yes             |

| Thermal Protection               | Yes             | No              |

| Shunt Mode                       | Yes             | No              |

| Supply Current, $I_S$ (mA)       | 1.2             | 5               |

| $T_A$                            | -40°C to +125°C | -40°C to +125°C |

| 100% Tested Temperatures         | 5               | 3               |

## EVALUATION BOARD HARDWARE GUIDE

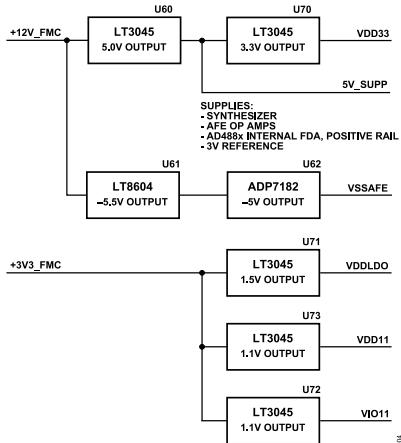

### POWER SUPPLIES

The EVAL-AD4884-FMCZ is designed to operate from the 12V and 3.3V supplies provided from the host controller board via the FMC connector. The FMC supplies are regulated down using a combination of switching regulators and linear dropout (LDOs) regulators to generate the necessary power rails for the on-board circuitry.

Figure 4. Evaluation Board Power Tree

### ADC POWER SUPPLIES

The [AD4884](#) requires three major power supplies:

- ▶ VDD33: 3.3V analog supply rail

- ▶ VDD11: 1.1V ADC core supply

- ▶ IOVDD: 1.1V digital interface supply

The AD4884 includes integrated power supply decoupling capacitors. Therefore, no external power supply decoupling are included on the evaluation board for the ADC power supply rails.

The following can be configured in this circuit:

- ▶ 1.1V rails (VDD11 and IOVDD) source

- ▶ On-board generated rails (default): The rails are taken in from the [LT3045](#) regulators (U72 and U73), as shown in [Figure 4](#).

- ▶ Internal AD4884 LDO regulator: An LDO internal to the ADC can be enabled and used to power both 1.1V rails. For more details pertaining to the power supply rails and requirements, refer to the AD4884 data sheet.

- ▶ Off-board external supply.

- ▶ 3.3V rail source

- ▶ On-board generated rail (default): The rail is supplied by an LT3045 LDO regulator (U71), as shown in [Figure 4](#).

- ▶ Off-board external supply.

### AMPLIFIER POWER SUPPLIES

A +5V rail (VDDAFE) and a -5V rail (VSSAFE) are generated on the EVAL-AD4884-FMCZ evaluation board. These rails power all analog front end circuitry, which includes the four [LT6236](#) discrete operational amplifiers (U22, U23, U32, and U33) in the input stage as well as the on-chip fully differential amplifiers inside [AD4884](#) (via the +V<sub>S</sub> and -V<sub>S</sub> pins).

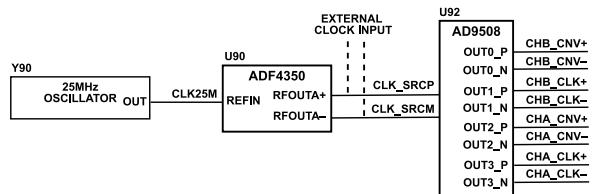

### CONVERSION AND DATA CLOCK GENERATION CIRCUIT

The EVAL-AD4884-FMCZ contains the necessary circuits to generate low jitter data (CLK+ and CLK-) and conversion (CNV+ and CNV-) clocks across the full operating range of the AD4884. This low jitter circuitry allows processing with fidelity full-scale input signals up to 4MHz.

The circuit consists of a 25MHz complementary metal–oxide semiconductor (CMOS) reference oscillator (Y90), the [ADF4350](#) wide-band synthesizer, and the [AD9508](#) clock fan-out buffer, as shown in [Figure 5](#). The synthesizer takes in the 25MHz signal from the oscillator and produces a higher frequency output with the frequency multiplication factor being programmable by the software. The synthesizer output is then fed to the clock buffer, which generates the clock (CLK+ and CLK-) and convert (CNV+ and CNV-) signals, from which, it can apply separate programmable frequency division factors. Therefore, the software sets the CLK and CNV signal frequencies by programming the ADF4350 and AD9508 through their serial interfaces. In practice, the user must change the sample rate through the interface offered by the [ACE Software](#).

Figure 5. Simplified Diagram of the Clock Circuitry

### DIGITAL INTERFACE

The EVAL-AD4884-FMCZ utilizes the FMC connector (P120) from the ZedBoard to support ADC device configuration via the 4-wire SPI, conversion result access using the LVDS interface, and conversion control in LVDS mode. The ZedBoard acts as the conduit for communication between the [ACE Software](#) plug-in and the EVAL-AD4884-FMCZ hardware.

The AD4884 operates with a 1.1V digital interface supply voltage. To translate between this 1.1V level and the digital interface voltage level of the ZedBoard (VADJ), SN74AVC1T45DCKR bidirectional level translators are used on the EVAL-AD4884-FMCZ hardware.

## EVALUATION HARDWARE SETUP PROCEDURE

The following procedure must be followed to get the hardware ready for evaluation:

1. Insert the SD card from the EVAL-AD4884-FMCZ kit into the SD card slot (J12) of the ZedBoard.

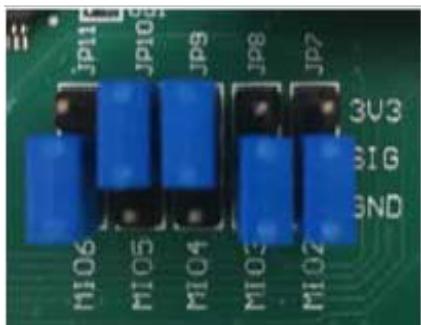

2. Ensure that the ZedBoard boot configuration jumpers (JP7 to JP11) are set, as shown in [Figure 6](#).

006

Figure 6. ZedBoard JP7 to JP11 Settings for the SD Card Mode

3. Ensure that the VADJ SELECT jumper (J18) is in the **2V5** position.

4. Connect the FMC connector (P3) of the EVAL-AD4884-FMCZ to the FMC connector (J1) of the ZedBoard.

5. Connect the 12V power supply included in the ZedBoard kit to the DC barrel jack (J20) of the ZedBoard, one USB cable between the PC and the USB on the go (OTG) connector (J13), and the other USB cable between the PC and the USB universal asynchronous receiver-transmitter (UART) connector (J14).

6. Slide the power switch (SW8) to the **ON** position to power up the ZedBoard and evaluation hardware.

- a. If using any external power supplies for the evaluation hardware, turn these supplies on with the ZedBoard.

7. The hardware is now ready to be used through the [ACE Software](#).

## SOFTWARE SUPPORT

### EVALUATION SOFTWARE

The EVAL-AD4884-FMCZ hardware is controlled and configured through the [ACE Software](#). ACE is a desktop software application that allows the evaluation and control of multiple evaluation systems from across the Analog Devices, Inc., product portfolio. The controller board supported by ACE with the EVAL-AD4884-FMCZ evaluation board is the ZedBoard.

For ACE installation and documentation instructions, refer to the [ACE Software](#). Make sure to follow the instructions to install the necessary EVAL-AD4884-FMCZ board plug-in and do the following:

1. If the machine that ACE is installed on has internet access, a user can find/install/update plug-ins directly from the ACE application. For environments without internet access, a user can download these plug-ins from the previous link to portable storage and install them into ACE.

Note that the user can find the product specific documentation for the evaluation software within the ACE plug-in.

### EMBEDDED SOFTWARE

The embedded software used for evaluation is built using open-source firmware examples, drivers, and HDL. When available, a user can find the links in the software section on relevant the product page.

Note that if a user does not find the embedded software available, then submit a request from the product page.

The EVAL-AD4884-FMCZ evaluation board comes with an SD card in the box. The SD card provides a version of ADI Kuiper Linux for Evaluation that can boot the controller board. The ACE evaluation board plug-in provides product specific configuration data and files.

Note that if there is an issue with the provided SD Card or a user has an outdated version, a download the latest version ADI Kuiper Linux for Evaluation image at [Analog Devices Kuiper Linux](#). This page also provides details on how to format and set up your SD card correctly.

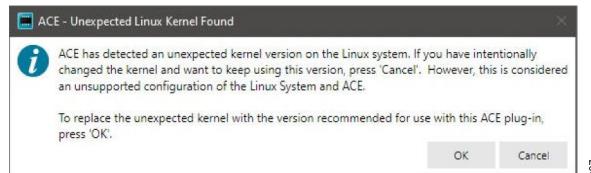

The latest version of ADI Kuiper Linux for Evaluation contains support Linux Runtime Configuration (LRC) of ACE Plug-Ins, via the [ACE Software](#) application. With the ACE application running, once a powered Zedboard, with the EVAL-AD4884-FMCZ evaluation board fitted has been connected to the PC, the ACE application detects the connected evaluation board. If the ADI Kuiper Linux kernel running on from the SD card is not already configured for the connected evaluation board, the following pop-up appears, as shown in [Figure 7](#). Click **OK** to install the updated kernel to support the connected hardware.

Note that once user clicks **OK**, the kernel update is downloaded to the board and the kernel is then reinitialized. Initialization takes approximately 60seconds to 80seconds to complete. Once completed, the ACE plug-in opens, as described in the [Evaluating the AD4884 with the ACE Software](#) section.

*Figure 7. ACE LRC Reconfiguration of Kuiper Linux Prompt on Detection of EVAL-AD4884-FMCZ Board*

### HOST PC SOFTWARE

The embedded Linux stack is based on the IIO (Industrial I/O) architecture. This enables tools such as Python, through the pyadi-iio package, or MATLAB, with the Precision Toolbox, on a host PC to communicate with the evaluation and controller board. Where available, a user can find the links in the software section on the ADC product page.

Note that if a user does not find the Python or MATLAB software available, then submit a request from the product page.

There are generic, not product specific, IIO tools such as IIO Oscilloscope, Scopy, and IIO command line tools that provide basic, low-level functionality and work with any IIO platform.

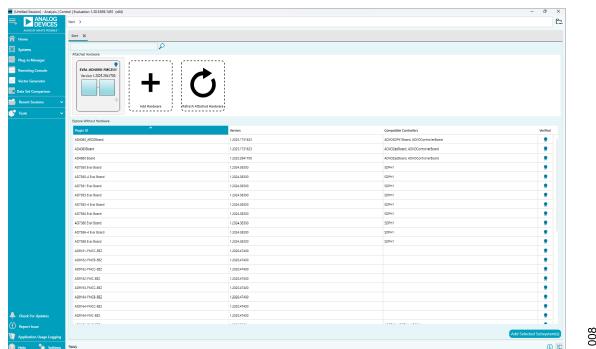

## EVALUATING THE AD4884 WITH THE ACE SOFTWARE

After the hardware setup is complete as per the [Evaluation Hardware Setup Procedure](#) section, and the software is installed as specified in the [Software Support](#) section, then run the ACE software for evaluation.

When ACE opens, the EVAL-AD4884-FMCZ is automatically detected and appears in the **Attached Hardware** panel, as shown in [Figure 8](#).

**Figure 8.** Auto Detection of the EVAL-AD4884-FMCZ in the ACE Start Tab

Double-click on the EVAL-AD4884-FMCZ icon and a new tab **EVAL-AD4884-FMCZ** opens that shows a block diagram of the EVAL-AD4884-FMCZ, as shown in [Figure 9](#).

**Figure 9.** EVAL-AD4884-FMCZ Tab Open in the ACE Software

This offers a **Board Level** view of the EVAL-AD4884-FMCZ. The sampling frequency can be configured within this window because it can control the required configuration of the supporting clocking components, [ADF4350](#) and [AD9508](#), as well as controlling the synchronization of the EVAL-AD4884-FMCZ data with the ZedBoard. As a default, the **Sampling Frequency (MHz)** field is configured for 20MHz. Any required update to the sampling frequency, in the range of 1.25MHz to 20MHz, can be made to this field. When a new value is entered in this field, the supporting clock components are updated, and the ZedBoard interface is automatically resynchronized. The same sampling frequency is applied to both channel in this implementation.

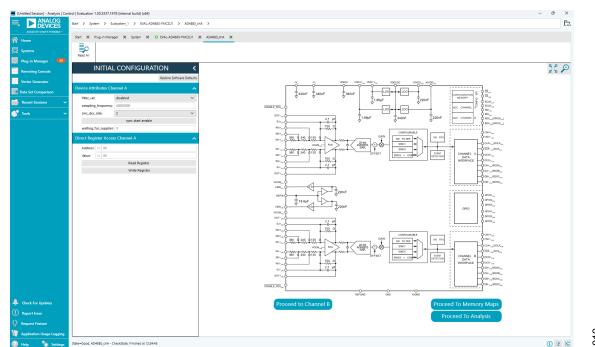

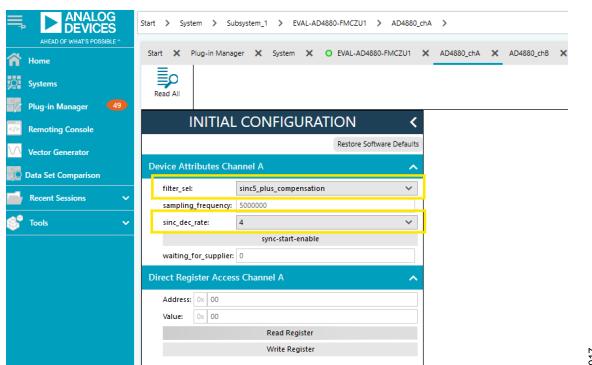

From the block diagram, double-click on the AD4884 to open the **AD4884\_cha** tab. This tab displays:

- A block diagram of the full AD4884 chip.

► An **INITIAL CONFIGURATION** pane on the left, showing device attributes and direct register access for Channel A. The **sampling\_frequency** device attribute is only informative, the sampling frequency can be changed for both channels at the same time in the **Board Level** view. The **filter\_sel** and **sinc\_dec\_rate** attributes control the digital filtering functionality of the AD4884. Any change to these parameters is applied to both Channel A and Channel B, this is a limitation of this evaluation board and associated software, in which both channels are simultaneously sampled and their displayed data is superimposed on one plot. In other applications, the sampling and digital filtering of each channel can be independently configured.

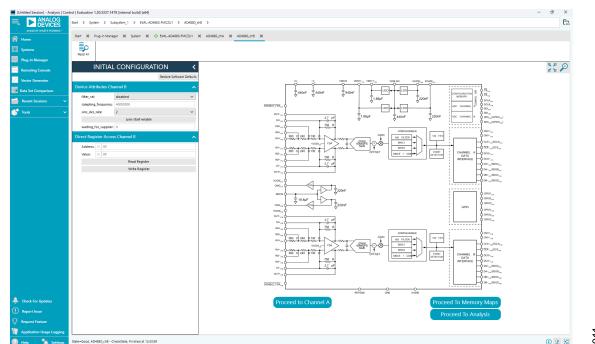

- A **Proceed to Channel B** button at the bottom left (open the **AD4884\_chb** tab, which is similar to this one, but whose **INITIAL CONFIGURATION** pane shows device attributes and direct register access for Channel B).

- Two buttons in the lower-right corner (**Proceed to Memory Maps** and **Proceed to Analysis**), which are shown in [Figure 10](#).

**Figure 10.** AD4884 Channel A Tab in the ACE Software

The tabs that are accessed through the **Proceed to Memory Maps** and **Proceed to Analysis** buttons provide the means to evaluate the AD4884 chip. For more details, see the [AD4884 Memory Maps](#) and the [ANALYSIS Tab](#) sections.

**Figure 11.** AD4884 Channel B Tab in the ACE Software

## AD4884 MEMORY MAPS

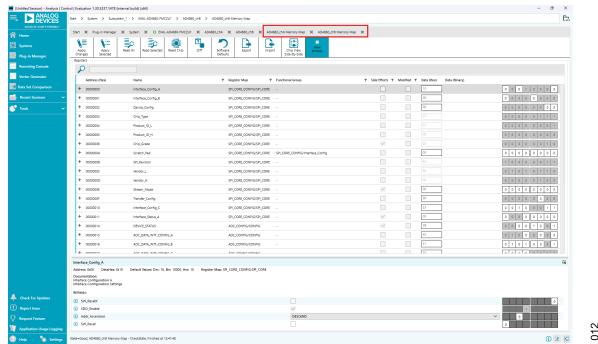

Clicking on the **Proceed to Memory Maps** button within either the **AD4884\_cha** or the **AD4884\_chb** tab opens two tabs:

## EVALUATING THE AD4884 WITH THE ACE SOFTWARE

**AD4884\_chA Memory Map** and **AD4884\_chB Memory Map**, as shown in [Figure 12](#).

**Figure 12.** AD4884 Memory Map Tabs in the ACE Software

The **AD4884\_chA Memory Map** shows the registers from Channel A, and the **AD4884\_chB Memory Map** tab shows the registers for Channel B. These tabs allow reading and writing (if applicable) register contents. For basic operation of the evaluation kit, no modifications are required to the ADC registers.

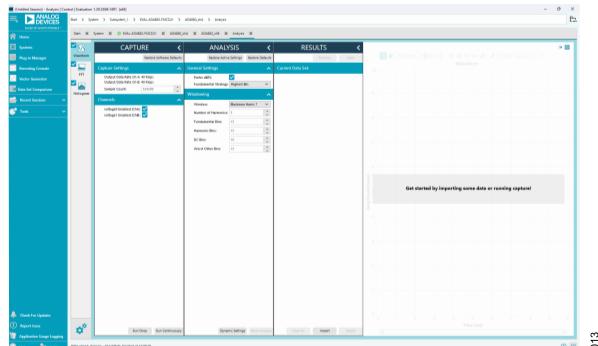

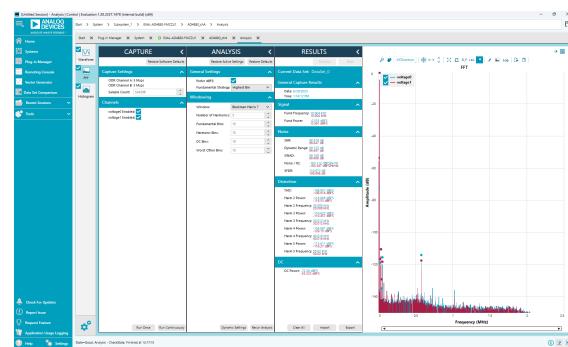

### ANALYSIS TAB

Click **Proceed to Analysis** within either the **AD4884\_chA** or **AD4884\_chB** tab to open the **ANALYSIS** tab. This tab is used for capturing data for both channels through the evaluation board and analyzing the obtained data. Data capture is simultaneous for both channels and at the same sampling rate. Same configuration of digital filtering is also forced.

**Figure 13.** Analysis Tab in the ACE Software

The **ANALYSIS** tab contains three panels (**CAPTURE**, **ANALYSIS**, and **RESULTS**) and a data plot area to the right. To hide any of the three panels, click the arrow located to the right of the panel name and is useful to leave more space for the data plot area when needed.

- The **CAPTURE** panel allows setting the number of samples to be captured per data set, triggering the acquisition of a single data set, and initiating or stopping the continuous acquisition of a data set.

- The **ANALYSIS** panel shows options related to the frequency domain analysis.

- The **RESULTS** panel provides metrics for the current data set that appears in the plot area. Different metrics are provided depending on the kind of plot that is selected (for more details, see the [Time Domain \(Waveform\) Plot](#), [Frequency Domain \(FFT\) Plot](#), and [Histogram Plot](#) sections). This panel also allows navigating between the data sets acquired during the session, and importing and exporting data sets in the internal format used by the **ACE Software** is also facilitated.

The user has the option to display the acquired data sets as a time domain waveform (default option), a frequency domain plot through a fast Fourier transform (FFT) or as a histogram, which is selected by clicking on any of the three corresponding buttons located to the left of the **CAPTURE** panel (see [Figure 13](#)).

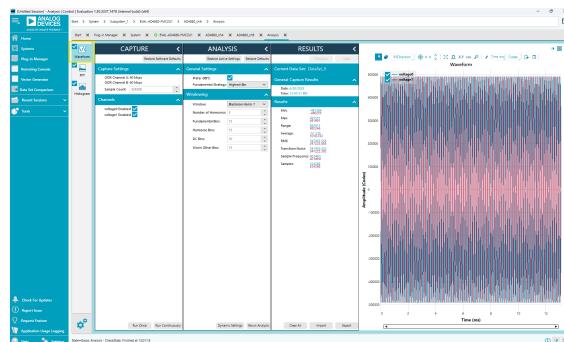

### TIME DOMAIN (WAVEFORM) PLOT

The active data set appears as a time domain waveform by clicking on the **Waveform** area highlighted in red in [Figure 14](#), which is the default view. Note that how the **CAPTURE** and **ANALYSIS** panels hide for an improved display of the plot.

When the data set is plotted as a time domain waveform, the **RESULTS** panel shows metrics relevant to time domain analysis: minimum, maximum, average, and RMS.

**Figure 14.** Data Set Plotted as Time Domain Waveform

## EVALUATING THE AD4884 WITH THE ACE SOFTWARE

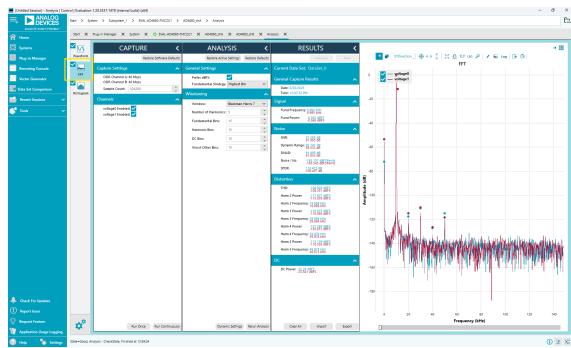

### FREQUENCY DOMAIN (FFT) PLOT

The active data set appears as a frequency domain waveform by clicking on the **FFT** area highlighted in red in [Figure 15](#). The plot then shows the FFT of the active data set. In this case, the **Log Scale** is selected for the **Frequency (MHz)** axis above the graph.

When the data set is plotted as a frequency domain waveform, the **RESULTS** panel shows metrics relevant to frequency domain analysis: signal-to-noise ratio (SNR) and total harmonic distortion (THD).

[Figure 15. Data Set Plotted in the Frequency Domain](#)

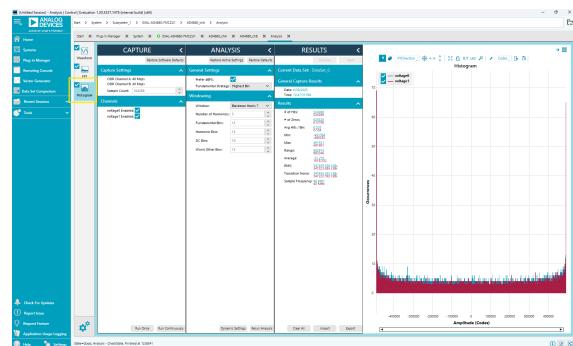

### HISTOGRAM PLOT

The active data set appears as a histogram by clicking on the **Histogram** area highlighted in red in [Figure 16](#). In this view, the vertical axis shows occurrences (bin hits) and the horizontal one can be set to display either code or volt amplitude bins.

When the data set is plotted as a histogram, the **RESULTS** panel shows metrics relevant to histogram analysis, such as minimum code, maximum code, and RMS.

[Figure 16. Data Set Plotted as a Histogram](#)

## CONFIGURING THE AD4884 INTEGRATED DIGITAL FILTERS

The **AD4884** includes the option of enabling integrated digital filters for applications where noise rejection by bandwidth limiting is required. For more details on the function and performance of these flexible filters, refer to the AD4884 product data sheet. While in principle each channel in AD4884 is fully independent, in the implementation for use with the ACE software the same configuration is forced for both channels. The configuration can be done on any of the two channel tabs (**AD4884\_chA** and **AD4884\_chB**), in the INITIAL CONFIGURATION area, as shown in [Figure 17](#) (with **AD4884\_chA** tab). The set configuration is automatically applied to both channels by ACE.

**Figure 17. Digital Filter Configuration from the AD4884 Tab in the ACE Software**

The values set in Figure 17 correspond to a sinc5 + compensation filter with a sinc decimation rate of 4. The **sampling\_frequency** attribute is read only and shows the effective output data rate, which in this case results from dividing the (default) 40MHz sampling frequency by 8 (4x from the sinc, and an additional 2x by the compensation). Figure 18 shows measurement results for this scenario, where the improvement in SNR can be observed.

**Figure 18. Increasing SNR with the Integrated Digital Filter**

**NOTES****ESD Caution**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

**Legal Terms and Conditions**

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Analog Way, Wilmington, MA 01887-2356, U.S.A. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed. All Analog Devices products contained herein are subject to release and availability.