# ADV212 JPEG2000 Video Processor User's Guide

Revision 1.1 December 11, 2006

Analog Devices, Inc.

One Technology Way

Norwood, Mass. 02062-9106

### **Copyright Information**

© 2006 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc. Printed in the USA.

#### **Disclaimer**

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

# ABOUT THIS DOCUMENT

### **Purpose**

This document describes the features of the ADV212 single-chip JPEG 2000 codec and provides the information necessary to integrate the ADV212 into a system.

### **Audience**

This document is intended for hardware engineers working on systems that include the ADV212. This document is also intended for software engineers who write applications for these systems.

### **Related Documents**

The following supporting documentation can be downloaded from http://www.analog.com under ADV212 Technical Documentation:

- ADV212 datasheet This document contains the package specifications and all electrical and timing specifications.

- ADV212 Programming Guide This is a programming guide containing configuration examples for all modes mentioned in this *User's Guide*. This also includes information on loading the firmware.

- Firmware Up-to-date firmware can be downloaded from http://www.analog.com under ADV212 Technical Documentation.

- Product Change Notices and Errata sheets.

**Under ADV202 Technical Documentation:**

- HIPI Mode and Still-Image Applications This document contains configuration examples for host interface pixel interface (HIPI) mode. While this document was written for the ADV202, it also applies to the ADV212.

- AN-799 Test Modes This document lists recommended test procedures

to verify correct hardware configuration. While this document was written for

the ADV202, it also applies to the ADV212.

### **Conventions**

This document uses certain conventions to assist you in identifying, locating, and understanding information.

### **Numbering Systems**

Hexadecimal values are represented with the prefix "0x" followed by the value. For example: 0xFFFF.

# **Typographic Notation**

The following typographic notations are used throughout this document:

| Example    | Description                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| [n]        | A number enclosed in brackets represents a single bit in a register or in memory.                                                       |

| [n:m]      | Numbers enclosed in brackets and separated by a colon represent the endpoints of a continuous range of bits in a register or in memory. |

| <b>(i)</b> | A note provides supplementary information on a related topic.                                                                           |

| $\bigcirc$ | A caution identifies conditions or inappropriate usage of the product that could lead to undesirable results or product damage.         |

# **Special Terms**

The following terms have special meanings:

| Term      | Meaning                                                                                                                                               |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| assert    | Refers to the state of a signal as follows:  • An active-high signal is asserted when high (1).  • An active-low signal is asserted when low (0).     |  |

| byte      | An 8-bit data object                                                                                                                                  |  |

| deassert  | Refers to the state of a signal as follows:  • An active-high signal is deasserted when low (0).  • An active-low signal is deasserted when high (1). |  |

| half-word | A 16-bit data object                                                                                                                                  |  |

| space     | A FIFO slot available for a word entry                                                                                                                |  |

| word      | A 32-bit data object                                                                                                                                  |  |

# **CONTENTS**

| 1 ADV212 INTRODUCTION                             | 7  |

|---------------------------------------------------|----|

| Features                                          | 8  |

| Typical Applications                              | 8  |

| ADV212 Core Architecture                          | 9  |

| Functional Description                            | 9  |

| Wavelet Engine                                    | 9  |

| Entropy Codecs                                    | 10 |

| Embedded Processor System                         | 10 |

| Memory System                                     |    |

| Internal DMA Engine                               | 10 |

| Configurable FIFO Access                          | 10 |

| 2 ADV212 PHYSICAL INTERFACE                       | 11 |

| ADV212 Pixel and Host Interfaces                  | 11 |

| Internal Embedded Processor                       |    |

| Pixel Interface and VDATA Bus                     |    |

| EAV/SAV Mode                                      |    |

| HVF Mode                                          |    |

| Raw Video Mode                                    | 12 |

| Host Interface and HDATA Bus                      |    |

| Pixel Input on the Host Interface                 |    |

| HDATA Bus Configuration                           |    |

| Pin Configuration and Bus Modes                   | 14 |

| 32-bit Host/32-bit Data Mode                      | 14 |

| 16-bit Host/32-bit Data Mode                      |    |

| 16-bit Host/16-bit Data Mode                      |    |

| 16-bit Host/8-bit Data in JDATA Bus Mode          |    |

| Registers                                         | 14 |

| Direct Registers                                  |    |

| Indirect Registers                                |    |

| External DMA Interface                            |    |

| Video Input Formats                               |    |

| 3 VIDEO APPLICATIONS                              |    |

| Video Applications                                |    |

| Encode in a Multi-chip Application                |    |

| Decode in Multi-chip Applications                 |    |

| Digital Still Camera and Camcorder Applications   |    |

| Encode and Decode SDTV Video Application          |    |

| 32-bit Host/32-bit ASIC Application               |    |

| HIPI (Host Interface Pixel Interface) Application |    |

| JDATA Application                                 | 24 |

| JDATA Mode in a CCIR656 Application               | 24 |

| Raw Video Mode and JDATA Mode                     | 25 |

| 4 System Registers                                                          | 26 |

|-----------------------------------------------------------------------------|----|

| Direct Registers                                                            | 28 |

| PLL Rules For Various Speed Grades                                          | 39 |

| Internal Hardware Registers                                                 | 40 |

| Indirect Registers: Configuration and Status                                | 43 |

| Indirect Registers: Video Timing and Dimension                              | 44 |

| Indirect Registers: External DMA                                            | 51 |

| EDMOD Register Descriptions                                                 | 55 |

| External DMA Width                                                          |    |

| DMA Mode - DREQ/DACK DMA Mode and FLY-BY DMA Mode                           | 55 |

| DMA Mode - Dedicated Chip Select (DCS) DMA Mode                             | 55 |

| JDATA - DATA Mode                                                           |    |

| Single Transfer - DREQ/DACK DMA                                             |    |

| Burst Transfer - DREQ/DACK DMA                                              |    |

| Burst Length                                                                |    |

| Indirect Registers: FIFO Threshold                                          |    |

| Chip Identification                                                         |    |

| Host 32- and 16-bit Accesses to Direct/Indirect Registers and Indirect Memo |    |

| Accesses Using A 32-bit Host                                                |    |

| Accesses Using a 16-bit Host                                                |    |

| Video Modes                                                                 |    |

| Encode Mode                                                                 |    |

| Decode Slave Mode                                                           |    |

| EAV/SAV Mode with Interlaced Modes                                          |    |

| Decode Slave Frame Drop                                                     |    |

| Vdata Output Delays                                                         |    |

| Decode Master Mode                                                          |    |

| Video Input Formats                                                         |    |

| Pin Input Formats on HDATA and VDATA bus                                    |    |

| Video Input Formats on HDATA bus                                            |    |

| Video Input Formats on VDATA bus                                            |    |

| 12-bit Pixel Interface                                                      | 78 |

# 1 ADV212 INTRODUCTION

The ADV212 is a single-chip JPEG2000 codec targeted for video and high-bandwidth image compression applications that can benefit from the enhanced quality and features provided by the JPEG2000 (J2K)–ISO/IEC15444-1 image compression standard. The ADV212 implements the computationally intensive operations of the JPEG2000 image compression standard and provides fully compliant code-stream generation for most applications.

Depending on the particular application requirements, the ADV212 can also provide varying levels of JPEG2000 compression support. It can provide raw code-block and attribute data output that allows the host software to have complete control over the generation of the JPEG2000 code-stream and other aspects of the compression process such as bit-rate control.

The ADV212 contains a dedicated wavelet transform engine, three entropy codecs, an on-board memory system, and an embedded RISC processor that can provide a complete JPEG2000 compression or decompression solution. The wavelet processor supports the 9/7 irreversible wavelet transform and the 5/3 wavelet transform in reversible and irreversible modes. The entropy codecs support all features in the JPEG2000 Part 1 specification, except for Maxshift ROI.

Capable of encoding and decoding both still images and video, the ADV212 operates on a rectangular array of pixel samples called a tile. A tile may contain a complete image up to the maximum supported size, or some portion of an image. The maximum horizontal tile size supported depends on the wavelet transform selected and the number of samples in the tile. Images larger than the ADV212's maximum tile size may be broken into individual tiles and then sent sequentially to the chip while still maintaining a single, fully compliant, JPEG2000 codestream for the entire image. As an example of its throughput, the ADV212BBCZ-150 is capable of processing in real-time up to two D1 (720x480) video streams, while two ADV212BBCZ-150s are capable of processing high-definition video (720p/60 or 1080i/60) signals.

### **Features**

The ADV212 has the following features:

- Complete single-chip JPEG2000 compression or decompression solution for video and still images. No external memory is required.

- Patented Spatial Ultra-efficient Recursive Filtering (SURF™) technology enables low-power and low-cost wavelet-based compression.

- Supports both 9/7 and 5/3 wavelet transforms with up to six levels of transform.

- The 5/3 wavelet has programmable tile or image size with widths up to 2048 pixels in the pixel interface's three-component 4:2:2 mode, and up to 4096 pixels in single-component mode. The maximum tile or image height is 4096 pixels. For the 9/7 wavelet, those values are cut in half.

- Pixel interface directly supporting ITU.R-BT656, SMPTE125M PAL/ NTSC, SMPTE274M, SMPTE293M [525p], ITU.R-BT1358[625p] or any video format with a maximum input rate of 65 Msamples/sec for irreversible mode or 40 Msamples/sec for reversible mode. Two or more ADV212s can be combined to support full-frame SMPTE274M HDTV [1080i] or SMPTE296M [720p].

- Compression on a field-by-field basis or using de-interlaced fields for standard-definition television (SDTV) video sources for improved performance and compression efficiency.

- Flexible asynchronous SRAM-style host interface allows glueless connection to most 16- or 32-bit microcontrollers and ASICs.

- 2.5-3.3 V I/O and 1.5 V core supply.

- 12 mm x 12 mm 121-ball fpBGA, speed grade 115 MHZ or 13 mm x13 mm 144-ball fpBGA, speed grade 150 MHz.

# **Typical Applications**

The type of applications the ADV212 is used for includes the following:

- Image archival and retrieval for standard-definition television (SDTV), highdefinition television (HDTV), and high-resolution still images

- Digital closed-circuit television (CCTV) for security / surveillance systems

- Digital cinema systems

- · Professional and HDTV video editing and recording systems

- Professional digital camcorders and high-resolution digital still cameras

- Networked video and image distribution systems

- · Wireless video and image distribution

### **ADV212 Core Architecture**

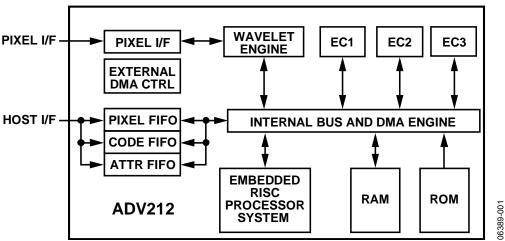

Figure 1. Processor Block Diagram

# **Functional Description**

For a typical encode application, video or pixel data is input to the ADV212's pixel interface. Valid samples are then passed on to the wavelet engine, where each tile or frame is decomposed into subbands using the 5/3 or 9/7 filters. The resultant wavelet coefficients are then written to internal memory. The entropy codecs then code the wavelet data so that it conforms to the JPEG2000 standard. An internal direct memory access (DMA) engine provides high-bandwidth memory-to-memory transfers as well as high-performance transfers between functional blocks and memory.

## **Wavelet Engine**

The ADV212 provides a dedicated wavelet transform processor based on Analog Devices' SURF technology. This processor can perform up to six wavelet decomposition levels on a tile.

In encode mode, the wavelet transform processor takes in uncompressed samples, performs the wavelet transform, and writes the wavelet coefficients in all frequency subbands to internal memory. Each of these subbands is then further broken down into code-blocks. The code-block dimensions can be user-defined, and are used by the wavelet transform processor to organize the wavelet coefficients into code-blocks when writing to internal memory. Each completed code-block is then entropy-coded by one of the entropy codecs.

In decode mode, wavelet coefficients are read from internal memory and are decoded into uncompressed samples.

# **Entropy Codecs**

Each entropy codec block performs context modeling and arithmetic coding on a code block of the wavelet coefficients. Additionally, this block also performs the distortion metric calculations during compression that are required for optimal rate-distortion performance. Since the entropy coding process is the most computationally intensive operation in the JPEG2000 compression process, three dedicated hardware entropy codecs are provided on the ADV212.

## **Embedded Processor System**

The ADV212 incorporates an embedded 32-bit RISC processor. This processor is used for configuration, control, and management of the dedicated hardware functions, as well as for code parsing and generation. **Memory System**

The memory system's main functions are to manage wavelet coefficient data and interim code-block and attribute data, and to provide temporary work space for creation, parsing, and storage of the JPEG2000 code-streams. The memory system can also be used as program and data memory for the embedded processor.

# **Internal DMA Engine**

The internal DMA engine provides high-bandwidth memory-to-memory transfers as well as high-performance transfers between memory and functional blocks. This function is critical for high-speed code-stream generation and parsing.

## **Configurable FIFO Access**

FIFOs are provided for pixel data, code-stream data, and attribute data. The FIFOs can be accessed directly from the host interface using normal addressed read and write cycles, or by external host DMA accesses using a DREQ/DACK protocol, or by one of the dedicated hardware handshake protocols. Each FIFO has a threshold that can be programmed to generate one interrupt when that threshold is reached.

# 2 ADV212 PHYSICAL INTERFACE

This chapter describes the ADV212 pixel and host interfaces.

### **ADV212 Pixel and Host Interfaces**

There are several possible modes that can be used to interface to the ADV212. The designer can use the pixel interface VDATA bus and the host interface HDATA bus, or the HDATA bus alone.

#### Internal Embedded Processor

The ADV212 is a System-on-Chip (SoC) implementation, which means that it incorporates dedicated hardware functions including a processor and on-board firmware and software. It also means that configuration and management of the operations of the chip can be handled by the on-chip processor and its software. Other than basic bus and I/O configurations that the user has to set up, most of the configuration and control of the ADV212 is handled by the firmware. The firmware is responsible for setting registers in different functional blocks of the ADV212, scheduling events, and similar functions. These functional blocks are entirely controlled by the firmware; the user has no access to them.

ADV212 configuration and firmware load procedures are described in detail in the ADV212 programming guide.

#### Pixel Interface and VDATA Bus

The pixel interface can be used in applications where uncompressed pixel data is on a separate bus from compressed data. For example, when an ADV212 is in encode mode, a typical application has 8- or 10-bit digital input video on the VDATA bus. Often this comes from a video decoder (such as the ADV7189B), which converts the analog video into a digital format. When used with the VDATA interface, the HDATA bus is used to output compressed data from the ADV212.

A typical decode mode application uses a processor or DMA to write the compressed JPEG2000 stream using the HDATA bus and to drive a video encoder with the VDATA bus. This video encoder (such as the ADV7301A) converts the digital video back into an analog output.

The pixel interface can support input and output video data or still-image data in 8-, 10-, and 12-bit monochrome or YCbCr format. All pixel interface formats are left-justified (MSB) on the VDATA bus. If YCbCr data is used, it must be in 4:2:2 mode.

Video data can be input and output in several different modes on the VDATA bus. For these modes, the pixel clock must be input on the VCLK pin.

Optionally, the ADV212 can be used in de-interlaced mode when used in NTSC or PAL format, where two consecutive fields are interleaved and processed as one frame. This mode yields significantly better compression performance and efficiency for SDTV NTSC or PAL sources.

Additionally, high-definition digital video, such as SMPTE-274M (1080i) is supported using two or more ADV212 devices.

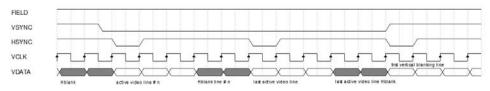

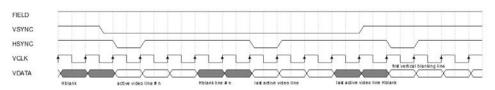

#### **EAV/SAV Mode**

The ADV212 can accept CCIR656 video formats. These modes use embedded time codes such as EAV and SAV in the video stream. This mode is set up by the user in the firmware parameters.

#### **HVF Mode**

The ADV212 can also accept video data accompanied by separate HSYNC, VSYNC, and FIELD (HVF) signals, where video data is interleaved onto a single bus. This is set up by the user in the firmware parameters.

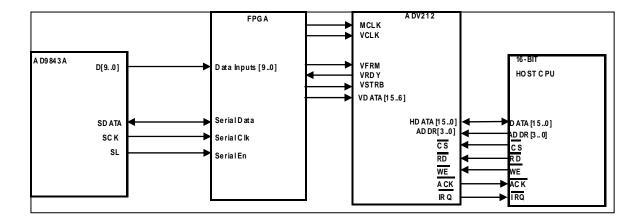

#### **Raw Video Mode**

This mode is used for still-picture data and non-standard video. Video frame (VFRM), video strobe (VSTRB), and video ready (VRDY) are used to transfer pixel data between the host and the pixel interface. In this mode, the pixel interface can support up to 16-bit sample data. Since no timing codes or sync signals are associated with the data on the pixel interface, dimension registers (XTOT, YTOT) must be programmed to indicate the size of the image.

#### Host Interface and HDATA Bus

The ADV212 can connect directly to a wide variety of 16- and 32-bit host processors and ASICs using an asynchronous SRAM-style interface, DMA accesses, or a JDATA-mode interface. The ADV212 supports 16- and 32-bit buses for control and 8-, 16-, and 32-bit buses for data transfers. The control and data-channel bus widths can be specified independently, which allows the ADV212 to support applications that require control and data buses of different widths. The host interface is used for configuration, control, and status functions as well as for transferring compressed data streams. The host interface can be used for uncompressed data transfers in certain modes. The host interface may be shared for control and status communications, uncompressed data input and compressed data output, or compressed data input and uncompressed data output. The data streams may include:

- Uncompressed tile data (such as still-image data)

- Fully encoded JPEG2000 code-stream or unpackaged code-blocks

- · Code-block attributes

The ADV212 uses big-endian word alignment for 16- and 32-bit transfers. All data is left-justified. This means that in a 32-bit system, the most significant byte is located at bits [31:24].

#### **Pixel Input on the Host Interface**

Pixel input on the host interface supports 8-, 10-, 12-, 14- or 16-bit raw pixel data formats. It can be used for pixel [still-image] input or compressed data output in encode mode, or compressed data input or pixel data output in decode mode. Since no timing codes or sync signals are associated with the input data on the host interface, dimension registers (XTOT, YTOT) must be programmed to indicate the size of the image.

See the application note *HIPI Mode and Still Image Applications* for details on how to use the ADV212 in HIPI mode.

#### **HDATA Bus Configuration**

The host interface provides several HDATA bus configurations to meet specific system requirements. The default bus mode uses the same HDATA pins to transfer both data and control information between the host and the ADV212.

The ADV212 can support 16- or 32-bit control transfers and 8-, 16-, or 32-bit data transfers. The size of the control and data buses can be selected independently by writing to the direct and indirect registers that configure bus size. This allows a 16-bit microcontroller to configure and control the ADV212 while still providing 32-bit data transfers to an ASIC or external memory system.

### **Pin Configuration and Bus Modes**

The ADV212 provides a wide variety of control and data configurations that allow it to be used in many applications with little or no glue logic. The modes described below are configured using the BUSMODE register.

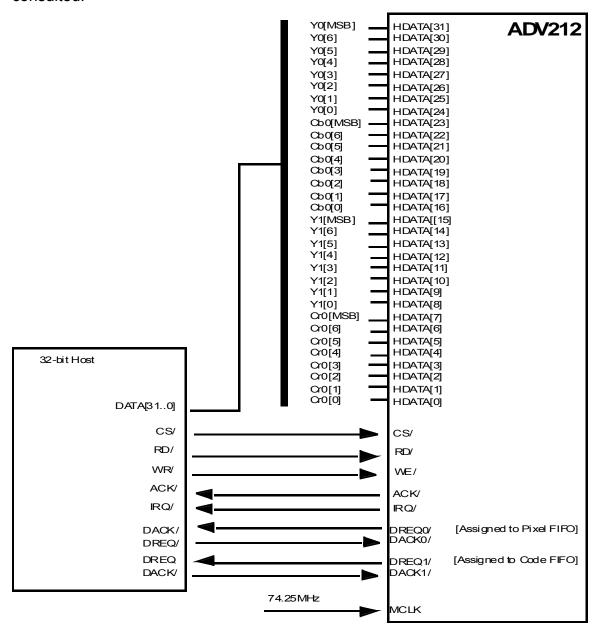

#### 32-bit Host/32-bit Data Mode

In this mode the HDATA[31..0] pins provide full 32-bit-wide data access to the PIXEL, CODE, and ATTR FIFOs, as well as internal memory and registers.

#### 16-bit Host/32-bit Data Mode

This mode allows a 16-bit host to configure and communicate with the ADV212 while still allowing 32-bit accesses to the PIXEL, CODE, and ATTR FIFOs using the external DMA capability. All addressed host accesses are 16-bits and therefore only use the HDATA[15..0] pins. The HDATA[31..16] pins are used to provide the additional 16-bits necessary to support the 32-bit external DMA transfers to and from the FIFOs for data.

#### 16-bit Host/16-bit Data Mode

This mode uses 16-bit transfers if used for host interface transfers or external DMA data transfers. This mode allows for use of the extended pixel interface modes.

#### 16-bit Host/8-bit Data in JDATA Bus Mode

This mode provides separate data input/output and host control interface pins. Host control accesses are 16 bits and use HDATA[15..0], while the compressed data is transferred over the dedicated 8-bit JDATA interface. JDATA uses a valid/hold synchronous transfer protocol based on MCLK. The direction of the JDATA bus is determined by the mode of the ADV212. If the ADV212 is encoding (compression) then JDATA[7..0] is an output. If the ADV212 is decoding (decompression) then JDATA[7..0] is an input. Host control accesses remain asynchronous. Host interface accesses are independent from JDATA data transfers.

### Registers

Direct and indirect registers and internal memory are used to program the ADV212 as well as receive or send compressed video data.

#### **Direct Registers**

The most commonly accessed resources on the ADV212 are available as Direct Registers, which are addressed using the 4-bit ADDR bus. This provides access to 16 locations. Other resources on the ADV212 can be accessed with the use of the Indirect Address (IADDR) and Indirect Data (IDATA) registers.

The IDATA, IADDR, and FIFO direct registers are 32 bits wide. The PLL\_HI and PLL\_LO registers are 8 bits wide. The remaining registers are 16 bits wide.

When accessing 8- and 16-bit registers in 32-bit host mode, the unused most significant bits should be ignored on the HDATA bus.

#### **Indirect Registers**

Since the ADV212 contains both 16- and 32-bit registers and its internal memory is mapped as 32-bit data, a mechanism has been provided to allow a 16-bit host interface to access these registers and memory locations. This is accomplished with the staging register (STAGE). The STAGE register is not used in 32-bit host mode.

The STAGE register is a direct register used by the host interface to set the indirect address register (IADDR) as well as for writing and reading data to that indirect memory location. Prior to writing to the desired location, the STAGE register must be written with the most significant 16-bit word of the address for that memory location. This is followed by writing the least significant 16-bit word of the address to the IADDR register. These two16-bit words are combined to create the full 32-bit address. Similarly, to write a 32-bit data value, STAGE is first written with the most significant 16-bit word, followed by writing the least significant 16-bit word to the IDATA register.

When a register is read, the upper [most significant] 16-bit word is returned immediately on HDATA and the lower 16-bit word can be retrieved by reading the STAGE register on a subsequent access.

Programming examples can be found in the ADV212 programming guide.

This does not apply to the PIXEL, CODE, and ATTR FIFOs. These channels are always accessed at the specified data width and do not require the use of the STAGE register.

#### **External DMA Interface**

The External DMA Interface is provided to enable high-bandwidth data I/O between an external DMA controller and the ADV212 data FIFOs. There are two independent DMA channels that can each be assigned to any one of the data stream FIFOs (PIXEL, CODE, or ATTR).

The controller supports asynchronous DMA using a DREQ/DACK (Data-Request/Data-Acknowledge) protocol in either single or burst access modes. Additional functionality is provided by Fly-By mode and Dedicated Chip Select (DCS) modes.

### **Video Input Formats**

The ADV212 supports a wide variety of formats for uncompressed video and still-image data. See "Video Input Formats" on page 69 for more information. The actual interface and bus modes selected for transferring uncompressed data determines the allowed size of the input data and the number of samples transferred with each access. The host interface can support 8-, 10-, 12-, 14-, and 16-bit data formats on the HDATA bus.

The pixel interface can support input and output video data or still-image data. All possible formats are listed in "System Registers" on page 26 of this user's guide. All formats can support less precision than provided by specifying the actual data width and precision. This can be set in the PMODE register or through a firmware parameter.

The maximum allowable data-input rate is dependent on the wavelet transform and the data-width (or precision) of the input samples.

Table 26 and Table 27 of the ADV212 datasheet list the maximum allowable data input rates.

# 3 VIDEO APPLICATIONS

This section describes typical video applications using the ADV212 JPEG2000 Video Processor.

## **Video Applications**

A single ADV212 can be in either Encode or Decode mode depending on what firmware the user has loaded into the device. An ADV212 can not change from Encode mode to Decode mode unless new firmware is loaded into the chip and the chip has gone through a reset and configuration process again.

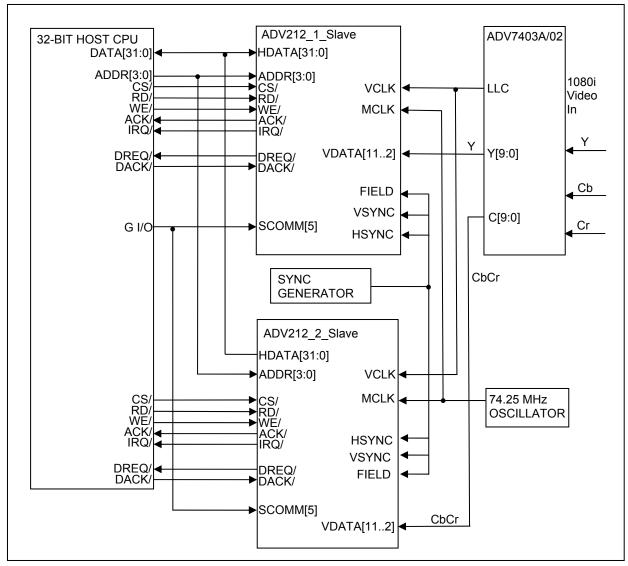

### **Encode in a Multi-chip Application**

Due to the pixel data rate limitation, an 1080i application requires at least 2 ADV212s to encode or decode full resolution 1080i or 720p video. In encode mode, the ADV212 accepts Y and CbCr data on separate buses. An encode example is shown in Figure 2 on page 18.

In decode mode, a master/slave configuration (as shown in Figure 3 on page 19) or a slave/slave configuration can be used in order to synchronize the outputs of the two ADV212s. See the application note "Using the ADV212 in a multi-chip application" for more details. This synchronization is necessary for glueless connection to standard video interface chips, such as the ADV7402.

Figure 2. Encode in a Slave/Slave Multi-chip Application

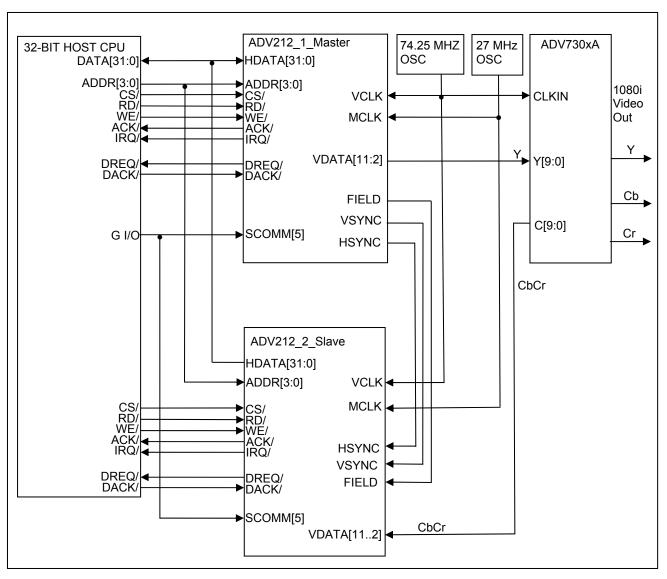

### **Decode in Multi-chip Applications**

In a master/slave configuration, it is expected that the master HVF outputs are connected to the slave HVF inputs and that each SCOMM[5] pin is connected to the same GPIO on the host.

In a slave/slave configuration the common HVF for both ADV212s is generated by an external sync generator and each SCOMM[5] is connected to the same GPIO output on the host.

SWIRQ1, Software Interrupt 1 in the EIRQIE register must be unmasked on both devices to enable multi-chip mode in order to synchronize video data at the VDATA outputs.

Figure 3. Decode in a Master/Slave Multi-chip Application

### **Digital Still Camera and Camcorder Applications**

Raw Video pixel mode can be used for still-image applications since there is no blanking or timing information and the pixel data only contains raw image data.

The ADV212 programming guide should be consulted for raw video pixel configuration and programming sequence when using this mode.

Figure 4. Digital Still Camera and Camcorder Applications

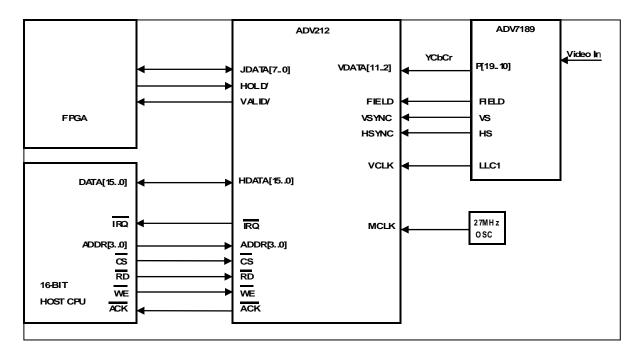

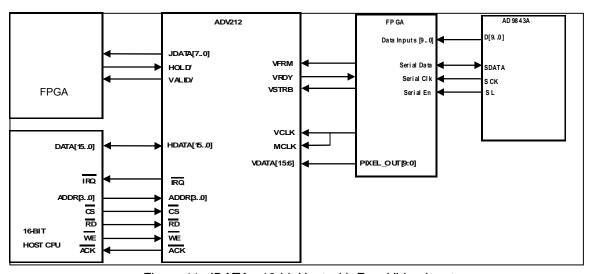

### **Encode and Decode SDTV Video Application**

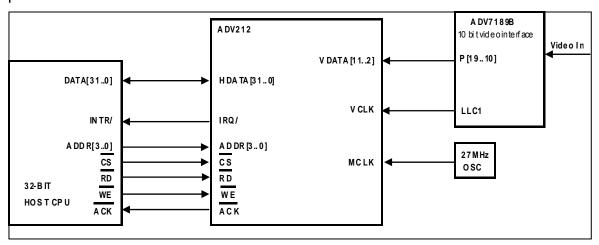

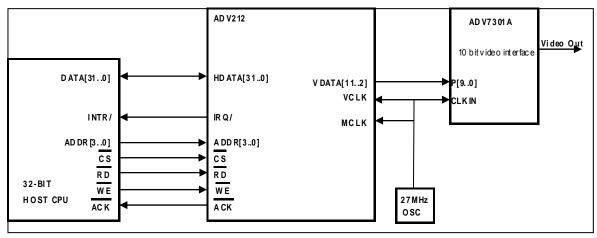

The figures below show a normal host mode SDTV application in 10-bit CCIR656 pixel interface mode.

Figure 5. Encode SDTV Video Application

Figure 6. Decode SDTV Video Application

### 32-bit Host/32-bit FPGA Application

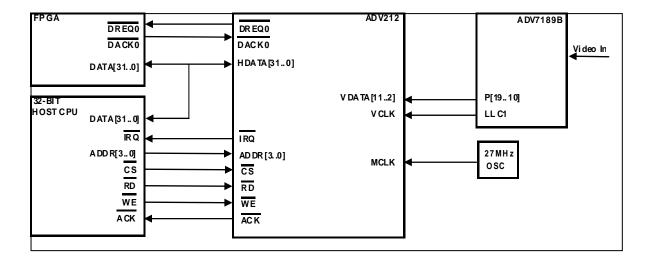

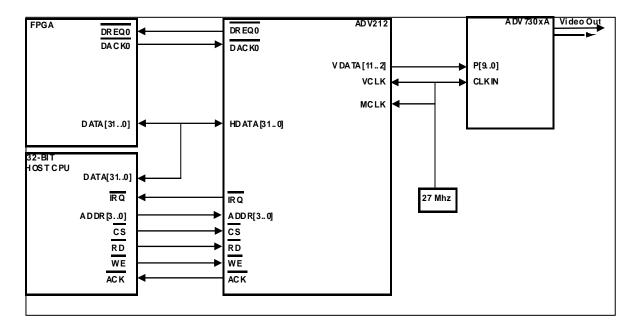

The figures below show encoding and decoding for a 10-bit CCIR656 FPGA application using DMA DREQ/DACK mode for compressed data transfer.

Figure 7. 32-bit Host/32-bit FPGA – Encode

Figure 8. 32-bit Host/32-bit FPGA - Decode

The figure above shows an SDTV application that uses external DMA channels, configured by the EDMOD registers, to transfer compressed data to and from the ADV212. The ADV212 programming guide should be consulted for configuration and programming sequence when using this configuration.

### HIPI (Host Interface Pixel Interface) Application

For more information about how to use the ADV212 in HIPI mode, the technical notes *ADV212 HIPI Mode* and *HIPI Mode Overview* at ftp://ftp.analog.com/pub/Digital\_Imaging/ADV212\_ApplicationNotes/ should be consulted.

Figure 9. HIPI Application Encode

### **JDATA Application**

### JDATA Mode in a CCIR656 Application

The figure below shows an example of using a 16-bit host for configuration and JDATA mode for compressed video output.

Figure 10. JDATA - 16-bit Host with Compressed Video Output

#### Raw Video Mode and JDATA Mode

On the ADV202, it was not possible to use JDATA Mode and Raw Video Mode simultaneously. This capability has been added in the ADV212.

To use Raw Video mode and JDATA mode on the ADV212 the following must be true:

- Uncompressed video data is interfaced over VDATA[15:0].

- Compressed video data is interfaced over JDATA[7:0].

- BUSMODE[6:4] must be set to 0x0003 for Raw Video Mode and JDATA Mode.

- EDMOD0[5:3] must be set to 0x0003.

Figure 11. JDATA - 16-bit Host with Raw Video Input

# **4 SYSTEM REGISTERS**

This section provides a functional description of the direct and indirect registers of the ADV212.

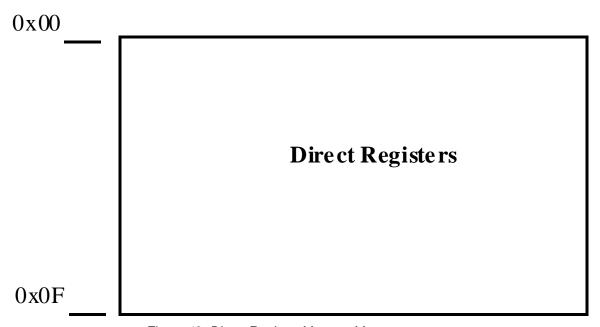

- There are 16 direct registers with a direct address range from 0x0 to 0xF.

The registers are accessed using the ADDR [3..0] pins for address and the HDATA bus for data. These registers are 8, 16 or 32 bits wide. See Table 1 on page 28 for a list of these registers.

- The Indirect register address range is from indirect addresses 0xFFFF0400 to 0xFFFF14FC. These registers are 16 bits wide and aligned on word (4-byte) boundaries. See Table 25 on page 41 for a list of indirect registers. Indirect address and data registers can be accessed by properly setting the IADDR and IDATA direct registers.

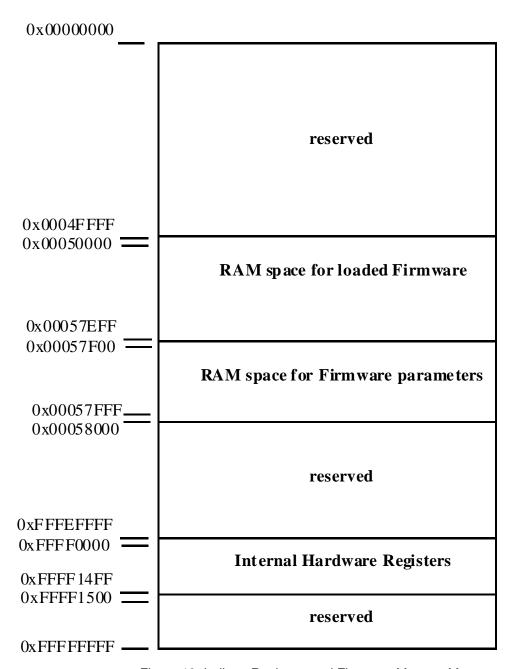

- The indirect memory locations are used for the storage of the firmware and firmware parameters. The 32KB encode or decode firmware is stored at starting address 0x00050000.

The firmware parameters are stored at starting address 0x00057F00.

These memory locations are 32 bits wide and are aligned on 4-byte boundaries. Indirect memory address and data registers can be accessed by properly setting the IADDR and IDATA direct registers.

Figure 12. Direct Register Memory Map

Figure 13. Indirect Registers and Firmware Memory Map

# **Direct Registers**

The ADV212 has 16 Direct Registers as shown in Table 1. The Direct Registers are accessed by the host interface using ADDR [3..0], HDATA[31..0], CS, RD,

$\overline{\text{WE}}$ , and  $\overline{\text{ACK}}$  pins.

The host must first initialize the Direct Registers before any application-specific operation can be implemented. The PLL\_HI and PLL\_LO registers are the only registers that can be read/write verified on bootup.

# DIRECT REGISTER MEMORY MAP Table 1.

| Address | Name     | Description                            | R/W | Length |

|---------|----------|----------------------------------------|-----|--------|

| 0x00    | PIXEL    | PIXEL FIFO Access Register             | R/W | [310]  |

| 0x01    | CODE     | Compressed Code-Stream Access Register | R/W | [310]  |

| 0x02    | ATTR     | ATTR FIFO Access Register              | R/W | [310]  |

| 0x03    | Reserved | Reserved                               | R/W | [310]  |

| 0x04    | Reserved | Reserved                               | R/W | [310]  |

| 0x05    | EIRQIE   | External Interrupt Enabled             | R/W | [150]  |

| 0x06    | EIRQFLG  | External interrupt Flags               | R/W | [150]  |

| 0x07    | SWFLAG   | Software Flag Register                 | R   | [150]  |

| 0x08    | BMODE    | Bus Mode Configuration Register        | R/W | [150]  |

| 0x09    | MMODE    | Miscellaneous Mode Register            | R/W | [150]  |

| 0x0A    | STAGE    | Staging Register                       | R/W | [150]  |

| 0x0B    | IADDR    | Indirect Address Register              | R/W | [310]  |

| 0x0C    | IDATA    | Indirect Data Register                 | R/W | [310]  |

| 0x0D    | BOOT     | Boot Mode Register                     | R/W | [150]  |

| 0x0E    | PLL_HI   | PLL Control Register - High Byte       | R/W | [150]  |

| 0x0F    | PLL_LO   | PLL Control Register - Low Byte        | R/W | [150]  |

# PIXEL FIFO ACCESS REGISTER Table 2.

|   | Address | Name  | Description                | R/W | Reset Value |

|---|---------|-------|----------------------------|-----|-------------|

| 1 | 0x00    | Pixel | PIXEL FIFO Access Register | R/W | Undefined   |

The 32-bit PIXEL register is used to access the PIXEL FIFO via normal addressed accesses and generally is used for pixel data input and output on the host interface (HIPI mode). The actual bus width when accessing this register depends on the host control data width selected [BUSMODE/HWIDTH].

- 16-bit mode will accept/return data on HDATA[15..0]

- 32-bit mode will accept/return data on HDATA[31..0]

In 16-bit mode, the upper unused bytes will be ignored on writes and return zeros on reads. The depth of the PIXEL FIFO is fixed to 256 x 32-bits.

# COMPRESSED CODE-STREAM ACCESS REGISTER Table 3.

| Address | Name | Description                            | R/W | Reset Value |

|---------|------|----------------------------------------|-----|-------------|

| 0x01    | CODE | Compressed Code-Stream Access Register | R/W | Undefined   |

The 32-bit CODE register is used to access the JPEG2000 compressed codestream FIFO via normal addressed accesses. It is also used for accessing raw code blocks when the ADV212 is in host interface pixel interface (HIPI) mode. The actual bus width when accessing this register depends on the host control data width selected [BUSMODE/HWIDTH].

In Encode mode, a host processor can read the compressed JPEG2000 stream using the CODE register in 16- or 32-bit mode. In Decode mode, it can write this compressed stream to the CODE register.

- 16-bit mode will accept/return data on HDATA[15..0]

- 32-bit mode will accept/return data on HDATA[31..0]

In 16-bit mode, the upper unused bytes will be ignored on writes and return zeros on reads.

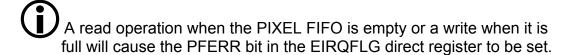

A read operation when the CODE FIFO is empty or a write when it is full, will cause the DFERR bit in the EIRQFLG direct register to be set.

#### ATTRIBUTE REGISTER

Table 4.

| Address | Name | Description      | R/W | Reset Value |

|---------|------|------------------|-----|-------------|

| 0x2     | ATTR | ATTR FIFO Access | R/W | Undefined   |

The 32-bit ATTR register is used to access the attribute FIFO via normal addressed accesses. The actual bus width when accessing this register depends on the host control data width selected [BUSMODE/HWIDTH].

- 16-bit mode will accept/return data on HDATA[15..0]

- 32-bit mode will accept/return data on HDATA[31..0]

- In 16-bit mode, the upper unused bytes will be ignored.

A read operation when the CODE FIFO is empty or a write when it is full, will cause the AFERR bit in the EIRQFLG direct register to be set.

# **EXTERNAL INTERRUPT ENABLE REGISTER** Table 5.

| Address | Name   | Description                | R/W | Reset Value                 |

|---------|--------|----------------------------|-----|-----------------------------|

| 0x05    | EIRQIE | External Interrupt Enables | R/W | See bit field descriptions. |

This 16-bit EIRQIE register is used to enable the interrconditions that causes an external interrupt to occur on the IRQ/ pin. See the ADV212 programming guide for more information.

# EIRQIE REGISTER BIT FIELDS Table 6.

| Bit | Name     | Description                                             | Reset Value |

|-----|----------|---------------------------------------------------------|-------------|

| 0   | PFTH     | PIXEL FIFO threshold condition exists (Level sensitive) | 0           |

| 1   | DFTH     | CODE FIFO threshold condition exists (Level sensitive)  | 0           |

| 2   | AFTH     | ATTR FIFO threshold condition exists (Level sensitive)  | 0           |

| 3   | Reserved | Reserved                                                | 0           |

| 4   | PFERR    | PIXEL FIFO has overflowed or underflowed                | 0           |

| 5   | DFERR    | Data FIFO has overflowed or underflowed.                | 0           |

| 6   | AFERR    | ATTR FIFO has overflowed or underflowed.                | 0           |

| 7   | Reserved | Reserved                                                | 0           |

| 8   | Reserved | Always write 0                                          | 0           |

| 9   | Reserved | Always write 0                                          | 0           |

| 10  | SWIRQ0   | Software interrupt 0                                    | 0           |

| 11  | SWIRQ1   | Software interrupt 1                                    | 0           |

| 12  | SWIRQ2   | Software interrupt 2 (reserved for future use)          | 0           |

| 13  | Reserved | Reserved                                                | 0           |

| 14  | Reserved | Reserved                                                | 0           |

| 15  | Reserved | Reserved                                                | 0           |

# **EXTERNAL INTERRUPT FLAG REGISTER** Table 7.

| Address | Name    | Description              | R/W | Reset Value                 |

|---------|---------|--------------------------|-----|-----------------------------|

| 0x6     | EIRQFLG | External Interrupt Flags | R/W | See bit field descriptions. |

The 16-bit EIRQFLG register indicates that external interrupt conditions are currently active. The bits in this register correspond directly to the bits in the external interrupt enable register (EIRQIE).

Individual interrupts are cleared by writing a '1' in the proper bit position of this register. A common mistake is trying to clear the interrupt flag before servicing the interrupt. For example, if you use the host processor to read JPEG2000 data out of the CODE FIFO after the DFTH interrupt is set (the CODE FIFO threshold condition is set). First the data must be read out of the FIFO, then the interrupt must be cleared by writing to the corresponding bit in the EIRQFLG register. Otherwise, if the interrupt flag is cleared before data is read out, the interrupt never gets cleared because the data count in the FIFO is still above the FIFO threshold.

# EIRQFLG REGISTER BIT FIELD DESCRIPTIONS Table 8.

| Bit | Name     | Description                                             | Reset Value |

|-----|----------|---------------------------------------------------------|-------------|

| 0   | PFTH     | PIXEL FIFO threshold condition exists (Level sensitive) | 1           |

| 1   | DFTH     | CODE FIFO threshold condition exists (Level sensitive)  | 1           |

| 2   | AFTH     | ATTR FIFO threshold condition exists (Level sensitive)  | 1           |

| 3   | Reserved | Reserved                                                | 1           |

| 4   | PFERR    | PIXEL FIFO has overflowed or underflowed                | 0           |

| 5   | DFERR    | Data FIFO has overflowed or underflowed.                | 0           |

| 6   | AFERR    | ATTR FIFO has overflowed or underflowed.                | 0           |

| 7   | Reserved | Reserved                                                | 0           |

| 8   | Reserved | Reserved                                                | 0           |

| 9   | Reserved | Reserved                                                | 0           |

| 10  | SWIRQ0   | Software interrupt 0                                    | 0           |

| 11  | SWIRQ1   | Software interrupt 1                                    | 0           |

| 12  | SWIRQ2   | Software interrupt 2                                    | 0           |

| 13  | Reserved | Reserved                                                | 0           |

| 14  | Reserved | Reserved                                                | 0           |

| 15  | Reserved | Reserved                                                | 0           |

#### **SWFLAG REGISTER**

Table 9.

| Address | Name   | Description    | R/W | Reset Value                 |

|---------|--------|----------------|-----|-----------------------------|

| 0x7     | SWFLAG | Application ID | R   | See bit field descriptions. |

The 16-bit SWFLAG register is used to read the Application ID after the ADV212 Encode or Decode firmware has been uploaded by the host processor. After the firmware has been uploaded and a soft reboot has been initiated, the embedded firmware takes control of this register and will write the Application ID into this register. Application IDs are different for Encode and Decode. This register is often used by the 16- or 32-bit host processor to ensure the firmware upload was successful.

#### **BUSMODE REGISTER**

Table 10.

| Address | Name    | Description            | R/W | Reset Value                 |

|---------|---------|------------------------|-----|-----------------------------|

| 0x8     | BUSMODE | Bus Mode Configuration | R/W | See bit field descriptions. |

The 16-bit BUSMODE register configures host control and data bus.

#### **BUSMODE REGISTER BIT FIELDS**

Table 11.

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reset Value |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 10  | HWIDTH   | Host control data width 00 = Invalid 01 =16-bits 10 = 32-bits 11 = Invalid                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '01'        |

| 32  | DWIDTH   | DMA data width 00 = 8 bits 01 =16 bits 10 = 32 bits 11 = Invalid                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '01'        |

| 64  | BCFG     | Bus configuration 000 = Normal. HDATA [310] are available for host or data transfers according to the settings of HWIDTH and DWIDTH. For normal read/write access HWIDTH and DWIDTH are set to 1 or 2. 001 = JDATA Mode. Enables JDATA[70]. HWIDTH must be set to 1 and DWIDTH must be set to 0. 010 = Raw Video Mode. HWIDTH should be set to 16-bit and DWIDTH should be set to 16- or 8-bit mode. 011 = Simultaneous JDATA and Raw Video modes. HWIDTH should be set to 16-bit mode and DWIDTH set to 8-bit mode. 111= Reserved | ,000,       |

| 7   | Reserved | Reserved for future use; always write 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0           |

| 158 | N/A      | Reserved for future use; always write 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | undefined   |

#### MMODE REGISTER

Table 12.

| Address | Name  | Description              | R/W | Reset Value                 |

|---------|-------|--------------------------|-----|-----------------------------|

| 0x9     | MMODE | Misc. Mode Configuration | R/W | See bit field descriptions. |

This 16-bit MMODE register configures miscellaneous functions for indirect access for 32-bit or 16-bit host interfaces.

Proper use and examples of this register can be found in "Host 32- and 16-bit Accesses to Direct/Indirect Registers and Indirect Memory" on page 60.

### **MMODE REGISTER BIT FIELDS**

Table 13.

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reset Value |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 10  | IWIDTH   | Indirect access widths 00 = Invalid 01 = 16-bits 10 = 32-bits 11 = Invalid                                                                                                                                                                                                                                                                                                                                                                               | '01'        |

| 32  | IAUTOSTP | IADDR increment/decrement size. IADDR can automatically increment/decrement the IADDR location. This would require only one write to the IADDR register/memory. It can also be disabled., in which case each indirect register/memory access requires a write to IADDR and IDATA.  00 = 8-bit increment/decrement 01 = 16-bit increment/decrement 10 = 32-bit increment/decrement 11 = Disable auto increment/decrement                                  | '01'        |

| 4   | IAUTOMOD | Indirect address auto increment/decrement 0 = increment 1 = decrement                                                                                                                                                                                                                                                                                                                                                                                    | 0           |

| 5   | CTLREGAM | Control register address mode. Enable full indirect address map. The control register address space is 0xFFFF0000 and above.  0 = Full address mode. Provides full access to the ADV212's internal address space  1 = Control register mode. The upper 16-bits of the internal address are forced to the beginning of the control register address map. This eliminates setting the upper 16-bits of the indirect address register prior to each access. | 0           |

| 156 | Reserved | Reserved for future use; always write 0.                                                                                                                                                                                                                                                                                                                                                                                                                 | Undefined   |

#### STAGE REGISTER

Table 14.

| Address | Name  | Description | R/W | Reset Value |

|---------|-------|-------------|-----|-------------|

| 0xA     | STAGE | Staging     | R/W | Undefined   |

The 16-bit STAGE register is used when accessing 32-bit registers in 16-bit host mode. It is not required for a 32-bit host. It is used to access 32-bit words in indirect memory, indirect registers, and 32-bit direct registers. The STAGE register acts as a holding or "staging" register. For example, when using a 16-bit host the STAGE register is used in conjunction with the IADDR register to configure the 32-bit address or the IDATA register.

Proper use and examples of this register can be found in "Host 32- and 16-bit Accesses to Direct/Indirect Registers and Indirect Memory" on page 60.

#### IADDR REGISTER

Table 15.

| Address | Name  | Description      | R/W | Reset Value |

|---------|-------|------------------|-----|-------------|

| 0xB     | IADDR | Indirect Address | R/W | Undefined   |

The 32-bit IADDR register is used to set the address for indirect register and indirect memory read/write accesses.

The indirect address may optionally be auto-incremented/decremented by setting the IAUTOMOD and IAUTOSTP fields in the MMODE register.

Proper use and examples of this register can be found in "Host 32- and 16-bit Accesses to Direct/Indirect Registers and Indirect Memory" on page 60.

#### **IADDR REGISTER**

Table 16.

| Address | Name  | Description   | R/W | Reset Value |

|---------|-------|---------------|-----|-------------|

| 0xC     | IDATA | Indirect Data | R/W | Undefined   |

The 32-bit IDATA direct register is used to read and write data to an indirect register or indirect memory. The data value written to the IDATA register is written to the address in the IADDR register..

The indirect address may optionally be auto-incremented by setting the IAUTOMOD and IAUTOSTP fields in the MMODE register.

Proper use and examples of this register can be found in "Host 32- and 16-bit Accesses to Direct/Indirect Registers and Indirect Memory" on page 60.

#### **BOOT REGISTER**

Table 17.

| Address | Name | Description | R/W | Reset Value                 |

|---------|------|-------------|-----|-----------------------------|

| 0xD     | BOOT | Boot Mode   | R/W | See bit field descriptions. |

The 16-bit BOOT register is used to configure the boot mode and initiate a soft or hard reset of the ADV212.

A hard reset, one made by using the reset pin or setting the HARDRST bit, causes bits [2..1] to be loaded from the configuration pins as specified below, all other bits in this register will be set as specified in the bit field table.

The bits in the BOOT register are used to select various boot modes of the ADV212 after reset and to load specific instruction sets into memory. The boot mode can be configured via hardware [over the CFG pins] or in writing to the Boot Mode register. In a hardware configuration after a hard reset, the boot mode will be set to the values on the configuration pins CFG[2..1]. These bits are not reset on a soft reset; see HARDRST and SOFTRST bit definitions below. The first boot mode after power-up is set by the CFG pins. Only boot mode 2 is available in hardware boot mode.

A soft reset, via setting the SOFTRST bit will only clear the SOFTRST bit, all other bits will remain unchanged. A soft reset affects all ADV212 internal registers except for the BOOT, PLL\_LO, or PLL\_HI registers. A hard reset, one made by using the reset pin or the BOOT register, resets all of the ADV212 internal registers.

## **BOOT REGISTER BIT FIELD DESCRIPTIONS**

Table 18.

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reset Value |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 20  | BOOTMODE | SOFTWARE BOOTMODE  000 Reserved. For internal use only. Do not use. 001 Reserved. For internal use only. Do not use. 010 No-boot host mode. TheADV212 does not boot but all internal registers and memory are accessible through normal host I/O operations. 011 Reserved. For internal use only. Do not use. 100 Reserved. 101 Co-processor boot Used in conjunction with the no-boot host mode and starts executing the loaded firmware. 110 Reserved. For internal use only. Do not use 111 Reserved. For internal use only. Do not use HARDWARE BOOTMODE 000 Reserved. For internal use only. Do not use. 001 Not Available 010 No-boot host mode, ADV212 does not boot but all internal registers and memory are accessible through normal host I/O operations. 101 Not Available 100 Reserved. 101 Not Available 110 Not Available 111 Not Available | 000         |

| 3   | Reserved | Reserved for future use; always write 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1           |

| 54  | Reserved | Reserved for future use; always write 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0           |

| 6   | HARDRST  | Setting this bit will cause the ADV212 to execute a hard reset. This is identical to asserting a reset on the RESET pin. The value in BOOT MODE will be ignored since it will be immediately reloaded from the configuration pins. This bit will override the SOFTRST bit if both bits are set concurrently. The PLL control register is reset to its reset value as well as the BOOT MODE [21] bits representing the values on the CFG [21] pins.                                                                                                                                                                                                                                                                                                                                                                                                         | 0           |

| 7   | SOFTRST  | Setting this bit will cause the ADV212 to execute a soft reset. This is similar to asserting the RESET/ pin except that the value in BOOT MODE will be used to determine how the ADV212 will boot instead of using the configuration pins. BOOT MODE [20] and the PLL control register will not be reset. This bit will be cleared after the soft reset, but all other bits in this register will remain unchanged.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0           |

| 158 | Reserved | Reserved for future use; always write 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Undefined   |

### **PLL HI REGISTER**

Table 19.

| Address | Name   | Description           | R/W | Reset Value                 |

|---------|--------|-----------------------|-----|-----------------------------|

| 0xE     | PLL_HI | PLL Control high byte | R/W | See bit field descriptions. |

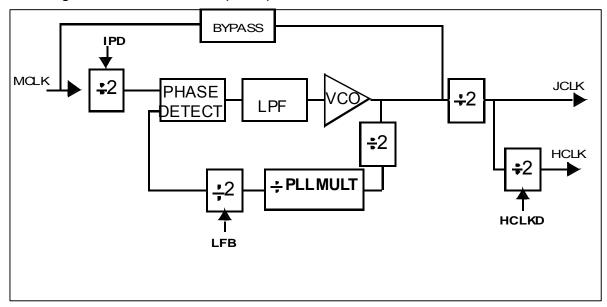

The 16-bit PLL\_HI register is used to configure the on-chip PLL. Internally, the ADV212 uses two clock domains that are generated by an on-chip PLL from the input clock MCLK.

JCLK is used to clock all of the JPEG2000 specific hardware blocks and HCLK is used to clock the embedded processor. A block diagram of the PLL and its control parameters are shown in Figure 14 on page 38.

Any time the PLL\_HI register is changed, the host must wait at least 20us before reading or writing any other register. If this delay is not implemented, erratic behavior may result.

# PLL\_HI REGISTER BIT FIELDS Table 20.

| Bit | Name     | Description                                                              | Reset<br>Value |

|-----|----------|--------------------------------------------------------------------------|----------------|

| 0   | PLLPDN   | Power down enable = 1                                                    | 0              |

| 1   | BYPASS   | Bypass enabled = 1                                                       | 0              |

| 2   | Reserved | Always write 0                                                           | 0              |

| 3   | HCLKD    | HCLK divider enabled = 1                                                 | 1              |

| 4   | ACK_FN   | 0 – ACK is actively driven 1 – ACK is configured as an open drain output | 0              |

| 65  | Reserved | ADI use only; always write 0                                             | Undefined      |

| 7   | Reserved | Reserved                                                                 | 1              |

| 158 | N/A      | Not Available                                                            | Undefined      |

### **PLL LO REGISTER**

Table 21.

| Address | Name   | Description          | R/W | Reset Value                 |

|---------|--------|----------------------|-----|-----------------------------|

| 0xF     | PLL_LO | PLL Control low byte | R/W | See bit field descriptions. |

This 16-bit PLL LO register is used to configure the on chip PLL.

Any time the PLL\_LO register is modified, the host must wait at least 20us before reading or writing any other register. If this delay is not implemented, erratic behavior may result.

# PLL\_LO REGISTER BIT FIELD DESCRIPTIONS Table 22.

| Bit | Name     | Description                      | Reset Value |

|-----|----------|----------------------------------|-------------|

| 40  | PLLMULT  | Multiplier [values from 0 to 31] | '00011'     |

| 5   | LFB      | Loop feedback divider enable = 1 | 0           |

| 6   | Reserved | Always write 0                   | 0           |

| 7   | IPD      | Input clock divider enable = 1   | 0           |

| 158 | N/A      | Not applicable                   | Undefined   |

In the figure below, the MCLK pin input is the external clock source.

Figure 14. PLL Architecture

# RECOMMENDED REGISTER SETTINGS FOR THE PLL REGISTERS Table 23.

| IPD | LFB | PLLMULT | HCLKD | HCLK         | JCLK         |

|-----|-----|---------|-------|--------------|--------------|

| 0   | 0   | N       | 0     | N * MCLK     | N * MCLK     |

| 0   | 0   | N       | 1     | N * MCLK / 2 | N * MCLK     |

| 0   | 1   | N       | 0     | 2 * N * MCLK | 2 * N * MCLK |

| 0   | 1   | N       | 1     | N * MCLK     | 2 * N * MCLK |

| 1   | 0   | N       | 0     | N * MCLK / 2 | N * MCLK / 2 |

| 1   | 0   | N       | 1     | N * MCLK / 4 | N * MCLK / 2 |

| 1   | 1   | N       | 0     | N * MCLK     | N * MCLK     |

| 1   | 1   | N       | 1     | N * MCLK / 2 | N * MCLK     |

## **PLL Rules For Various Speed Grades**

The ADV212 uses the PLL\_HI and PLL\_LO direct registers to configure the PLL. Any time the PLL\_LO register is modified, the host must wait at least 20 µs before reading or writing any other register. If this delay is not implemented, erratic behavior can result.

The PLL can be programmed to have any possible final multiplier value as long as the following are true:

- JCLK > 50 MHz and < 150 MHz (144-pin version)</li>

- JCLK > 50 MHz and < 115 MHz (121-pin version)</li>

- HCLK < 108 MHz (144-pin, 150MHz version)</li>

- HCLK < 81 MHz (121-pin version)</li>

- JCLK ≥ 2 × VCLK for single-component input

- JCLK ≥ 2 × VCLK for YCbCr [4:2:2] input

- In JDATA mode (JDATA), JCLK must be 4 × MCLK or higher.

- The maximum burst frequency for external DMA modes is ≤ 0.36 JCLK.

- For MCLK frequencies greater than 50 MHz, the input clock divider must be enabled, that is, IPD set to 1

- IPD cannot be enabled for MCLK frequencies below 20 MHz.

- De-Interlace modes require JCLK >= 4x MCLK

- It is not recommended to use an LLC output from a video decoder as a clock source for MCLK

For example, to achieve the lowest power consumption, an MCLK frequency of 27 MHz is recommended for a standard definition CCIR656 input. The PLL circuit is recommended to have a multiplier of 3. This sets JCLK and HCLK to 81 MHz.

# RECOMMENDED VALUES FOR PLL\_HI AND PLL\_LO REGISTERS Table 24.

| VIDEO STANDARD                                | CLKIN<br>FREQUENCY<br>ON MCLK | PLL_HI | PLL_LO | JCLK    |

|-----------------------------------------------|-------------------------------|--------|--------|---------|

| SMPTE125M or ITU-<br>R.BT656<br>[NTSC or PAL] | 27 MHz                        | 0x0008 | 0x0004 | 108 MHz |

| SMPTE293M [525p]                              | 27 MHz                        | 0x0008 | 0x0004 | 108 MHz |

| ITU-R.BT1358 [625p]                           | 27 MHz                        | 0x0008 | 0x0004 | 108 MHz |

| SMPTE274M [1080i]                             | 74.25 MHz                     | 0x0008 | 0x0084 | 149 MHz |

## **Internal Hardware Registers**

The indirect registers are accessed by the host processor through the IADDR and IDATA direct registers. If a 16-bit host is used, the STAGE direct register is also used. See Figure 13 on page 27. A common indirect access by the external host processor is to write indirect registers, such as the EDMOD and FIFO threshold registers.

In certain modes, such as Custom Specific or HIPI mode, indirect registers are accessed by the host. In standard modes, many of the indirect registers are controlled by the internal ADV212 processor. In these standard modes, the host processor simply needs to configure the indirect DMA or FIFO threshold registers.

Both 32-bit and 16-bit hosts can access the indirect registers. 32-bit access use the IADDR and IDATA registers while 16-bit hosts use IADDR, IDATA, and the STAGE register. Additional information on accessing and configuring these registers can be found in the *Getting Started with the ADV212* programming guide.

If the CTRLREGAM bit in the MMODE register is set (1), the user only needs to load the IADDR register with the lower 16 bits address [15..0]. The upper address bits default to 0xFFFF. The can be advantageous for 16-bit hosts. If the CTRLREGAM bit is cleared (0), a full 32-bit address must be written to the IADDR register.

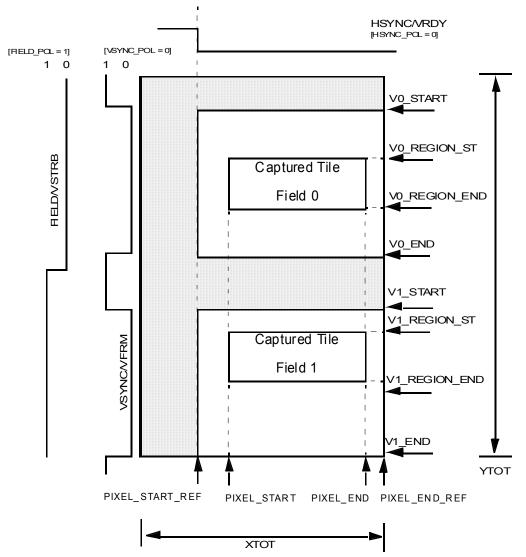

## **INTERNAL HARDWARE REGISTERS**

Table 25.

| INDIRECT<br>REGISTER<br>ADDRESS | NAME            | DESCRIPTION                              |  |

|---------------------------------|-----------------|------------------------------------------|--|

| 0xFFFF0400                      | PMODE1          | Pixel/Video Format                       |  |

| 0xFFFF0404                      | COMP_CNT_STATUS | Component count                          |  |

| 0xFFFF0408                      | LINE_CNT_STATUS | Line count                               |  |

| 0xFFFF040C                      | ХТОТ            | Total Samples per line                   |  |

| 0xFFFF0410                      | YTOT            | Total Lines per frame                    |  |

| 0xFFFF0414                      | F0_START        | Start Line of Field 0 [F0]               |  |

| 0xFFFF0418                      | F1_START        | Start Line of Field 1 [F1]               |  |

| 0xFFFF041C                      | V0_START        | Start of active video Field 0 [F0]       |  |

| 0xFFFF0420                      | V1_START        | Start of active video Field 1 [F1]       |  |

| 0xFFFF0424                      | V0_END          | End of active video Field 0 [F0]         |  |

| 0xFFFF0428                      | V1_END          | End of active video Field 1 [F1]         |  |

| 0xFFFF042C                      | PIXEL_START     | Horizontal start of active video         |  |

| 0xFFFF0430                      | PIXEL_END       | Horizontal end of active video           |  |

| 0xFFFF0440                      | MS_CNT_DEL      | Master/Slave Delay                       |  |

| 0xFFFF0444                      | Reserved        | Reserved                                 |  |

| 0xFFFF0448                      | PMODE2          | Pixel Mode 2                             |  |

| 0xFFFF044C                      | VMODE           | Video Mode                               |  |

| 0xFFFF0450                      | V0_REGION_ST    | Start of vertical cropped region Field 0 |  |

| 0xFFFF0454                      | V1_REGION_ST    | Start of vertical cropped region Field 1 |  |

| 0xFFFF0458                      | V0_REGION_END   | End of vertical cropped region Field 0   |  |

| 0xFFFF045C                      | V1_REGION_END   | End of vertical cropped region Field 1   |  |

| 0xFFFF0460                      | PIXEL_START_REF | Pixel start reference                    |  |

| 0xFFFF0464                      | PIXEL_END_REF   | Pixel end reference                      |  |

| 0xFFFF1408                      | EDMOD0          | External DMA mode register 0             |  |

| 0xFFFF140C                      | EDMOD1          | External DMA mode register 1             |  |

| 0xFFFF1410                      | FFTHRP          | FIFO Threshold for PIXEL FIFO            |  |

| 0xFFFF1414                      | Reserved        | Reserved                                 |  |

| 0xFFFF1418                      | Reserved        | Reserved                                 |  |

| 0xFFFF141C                      | FFTHRC          | FIFO Threshold for CODE FIFO             |  |

| 0xFFFF1420                      | FFTHRA          | FIFO Threshold for ATTR FIFO             |  |

## ADV212 JPEG2000 Video Processor User's Guide

| 0xFFFF1424                 | Reserved | Reserved                   |

|----------------------------|----------|----------------------------|

| 0xFFFF1428                 | Reserved | Reserved                   |

| 0xFFFF142C                 | Reserved | Reserved                   |

| 0xFFFF1430                 | Reserved | Reserved                   |

| 0xFFFF1434 -<br>0xFFFF14F3 | Reserved | Reserved                   |

| 0xFFFF14F4                 | HWREV    | Hardware Revision Register |

## **Indirect Registers: Configuration and Status**

These indirect configuration and status registers are typically controlled by the ADV212, except when in a custom specific video input mode or HIPI mode. In standard video input modes, they do not need to be programmed by the external host processor except for EDMOD and the FIFO threshold registers to configure compressed data transfer to/from the ADV212.

### PMODE1 REGISTER

Table 26.

| Address    | Name   | Description  | R/W | Reset Value                 |

|------------|--------|--------------|-----|-----------------------------|

| 0xFFFF0400 | PMODE1 | Pixel Mode 1 | R/W | See bit field descriptions. |

The PMODE1 register configures the VDATA or HDATA bus for a specific pixel format. See "Video Input Formats" on page 69 for a thorough explanation of the types of video formats used on the VDATA bus and HDATA bus.

# PMODE1 REGISTER BIT FIELD DESCRIPTIONS Table 27.

| Bit  | Name     | Description                                                                                                                                                                                                                                                                                                                           | Reset Value |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|