#### **MAX96793**

#### CSI-2 to GMSL3/2 Serializer

#### **General Description**

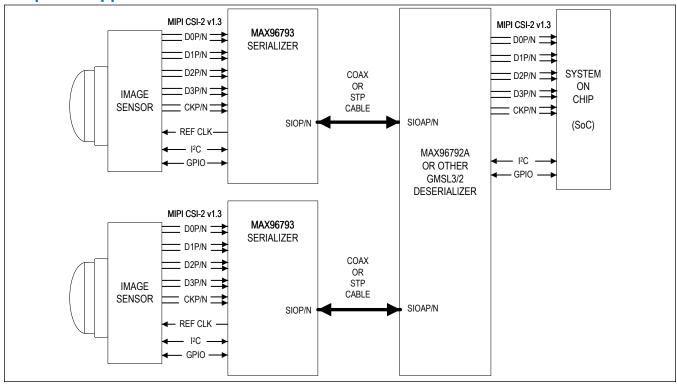

The MAX96793 GMSL<sup>™</sup> serializer receives video on a MIPI CSI-2 interface and outputs it to a GMSL2 or GMSL3 serial link transceiver. Simultaneously, it sends and receives bidirectional control channel data across the same GMSL link. GMSL2 or GMSL3 data can be transported over coaxial or shielded twisted pair (STP) cables. GMSL2 links operate at a fixed rate of 3Gbps or 6Gbps in the forward direction and 187.5Mbps in the reverse direction. GMSL3 links operate at a fixed rate of 12Gbps in the forward direction and 187.5Mbps in the reverse direction. The device is programmed through a local I<sup>2</sup>C/UART interface or across the link from a matching deserializer. The MAX96793 includes two I2C/UART pass-through channels, flexible GPIO, SPI tunnel, a built-in ADC, temperature sensor and an extensive set of diagnostics for functional safety. Operation is specified over the automotive temperature range of -40°C to +105°C and the device is AEC-Q100 grade 2 gualified.

Data can be transmitted over low-cost  $50\Omega$  coax or  $100\Omega$  STP cables that meet the GMSL3 or GMSL2 channel specification. Contact the factory for the GMSL3 or GM-SL2 Channel Specification.

Table 1. Typical Maximum Cable Length vs. Attenuation

|                                           | 3.2mm Ø<br>50Ω<br>Coax,<br>Foam<br>Dielectric | 2.7mm Ø<br>50Ω<br>Coax,<br>Solid<br>Dielectric | 100Ω<br>Shielded<br>Twisted<br>Pair,<br>AWG26 |  |

|-------------------------------------------|-----------------------------------------------|------------------------------------------------|-----------------------------------------------|--|

| Attenuation at 3GHz<br>(Typ, Room Temp)   | 0.9dB/m                                       | 1.6dB/m                                        | 1.8dB/m                                       |  |

| Attenuation at 3GHz<br>(Max, Aged, 105°C) | 1.1dB/m                                       | 2.0dB/m                                        | 2.2dB/m                                       |  |

| GMSL Fwd/Rev Data<br>Rate                 | Typical Maximum Cable Length at +105°C        |                                                |                                               |  |

| 3Gbps/187.5Mbps                           | 20m                                           | 10m                                            | 11m                                           |  |

| 6Gbps/187.5Mbps                           | 15m                                           | 9m                                             | 8m                                            |  |

| 12Gbps/187.5Mbps                          | 14m                                           | 8m                                             | 7m                                            |  |

#### **Applications**

- Advanced Driver Assistance Systems (ADAS)

- 8Mp 60fps Forward Vision Camera Systems (FVC)

- Forwarding of Aggregated Camera Data

- Systems with Multiple Synchronized Cameras

#### **Benefits and Features**

- · Automotive Grade High Speed Link

- -18db at 3GHz (12Gbps) Max Insertion Loss

- -21.0dB at 3GHz (6Gbps) Max Insertion Loss

- -19.5dB at 1.5GHz (3Gbps) Max Insertion Loss

- · Auto Adapt for Changes in Channel Conditions

- Operates at -40°C to +105°C Ambient

- MIPI CSI-2 v1.3 Input Port

- MIPI D-PHY v1.2 rated at 2.5Gbps/Lane (up to 4 Lanes)

- MIPI C-PHY v1.0 rated at 3.42Gbps/Lane (up to 2 Lanes)

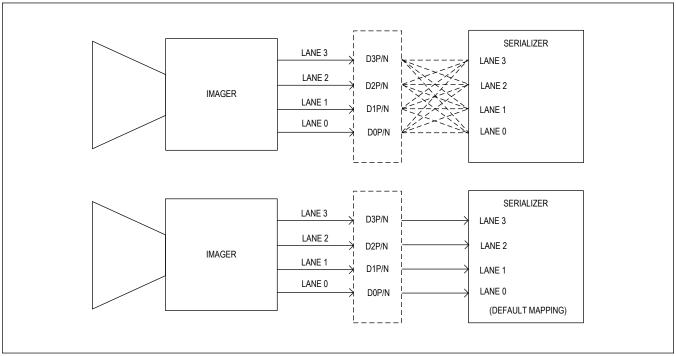

- Polarity Flip and Data Lane Reassignment

- Supports 16 Virtual Channels

- Single GMSL3 Output

- 12Gbps GMSL3 Forward Link Rate

- GMSL2 Backward Compatible 6Gbps / 3Gbps Link-Rates

- 187.5Mbps Reverse Link Rate

- Bidirectional Control-Channel Supports

- 11 Configurable GPIO

- 1 x I<sup>2</sup>C/UART Port up to 1MHz

- 2x Pass Through Ports

- Up to 2M Baud as UART

- Up to 1Mb/s as I<sup>2</sup>C

- 1x SPI Port, up to 25MHz

- Reduce BOM and Space Savings

- Tinv 5x5mm TQFN

- · RoR for Crystal-Free Operation on Serializers

- Industry's Smallest Power over Coax (PoC)

- Onboard Temperature Monitoring, ±2.5°C accuracy

- Safety Ready

- ASIL-B Compliant

- ASIL-D Decomposition Compliant

GMSL is a trademark of Analog Devices, Inc.

19-101163; Rev 3; 4/25

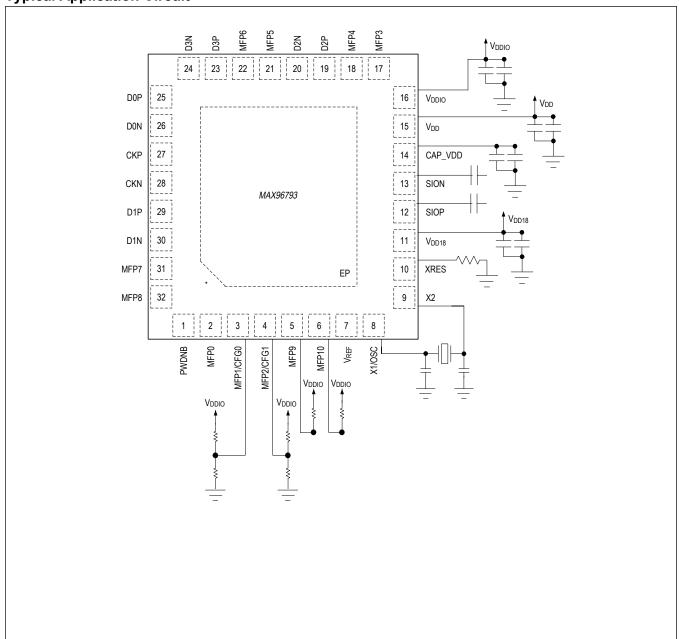

# **Simplified Application Circuit**

#### **TABLE OF CONTENTS**

| General Description                                                                  |    |

|--------------------------------------------------------------------------------------|----|

| Applications                                                                         | 1  |

| Benefits and Features                                                                | 1  |

| Simplified Application Circuit                                                       | 2  |

| Absolute Maximum Ratings                                                             | 10 |

| Package Information                                                                  | 10 |

| 32-Pin TQFN-SW (Side-Wettable)                                                       | 10 |

| Electrical Characteristics                                                           | 11 |

| Typical Operating Characteristics                                                    | 23 |

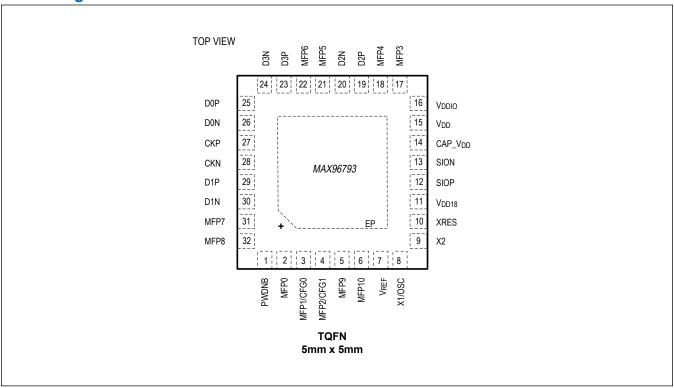

| Pin Configuration                                                                    | 24 |

| Pin Descriptions                                                                     | 24 |

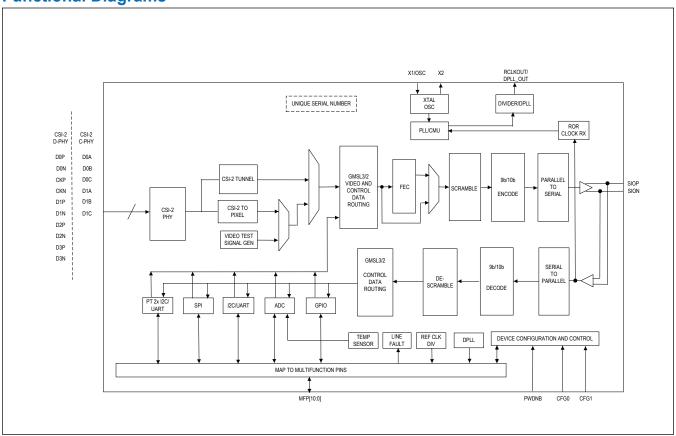

| Functional Diagrams                                                                  | 29 |

| Detailed Description                                                                 | 30 |

| Additional Documentation                                                             | 30 |

| Recommended Operating Conditions, External Component Requirements and ESD Protection | 30 |

| Functional Diagrams                                                                  | 32 |

| Introduction                                                                         | 39 |

| Product Overview                                                                     | 39 |

| Tunneling and Pixel Modes                                                            | 41 |

| Video Pipeline                                                                       | 42 |

| Video Pipes in Pixel Mode                                                            | 42 |

| RGB888 Video-Pattern Generator                                                       | 43 |

| Tx Crossbar                                                                          | 43 |

| GMSL3 Packet Protocol                                                                | 43 |

| Forward Error Correction                                                             | 43 |

| 9b10b Link Encoding                                                                  | 43 |

| GMSL3 Physical Interface                                                             | 44 |

| GMSL3 Mode                                                                           | 44 |

| GMSL2 Mode                                                                           | 44 |

| Cabling Options                                                                      | 44 |

| Adaptive Equalization (AEQ)                                                          | 45 |

| Echo Cancellation                                                                    | 45 |

| Spread-Spectrum                                                                      | 45 |

| Line Fault                                                                           | 45 |

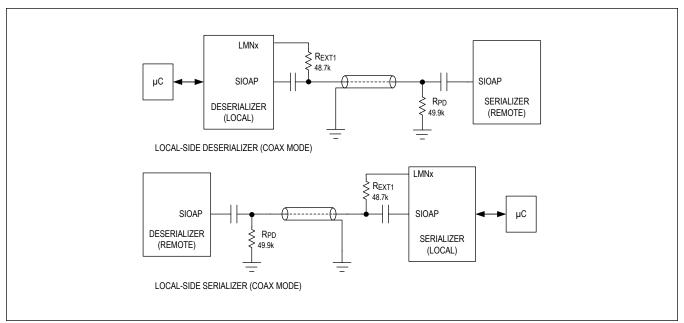

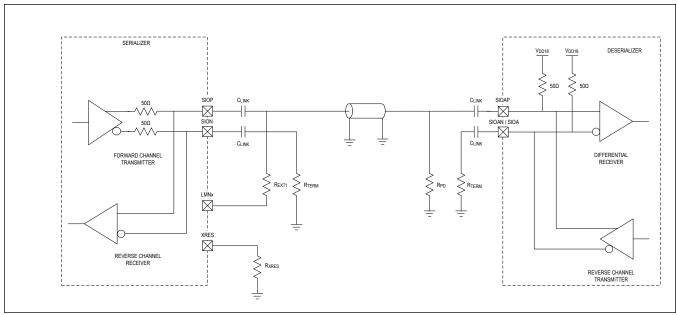

| Coax Mode                                                                            | 46 |

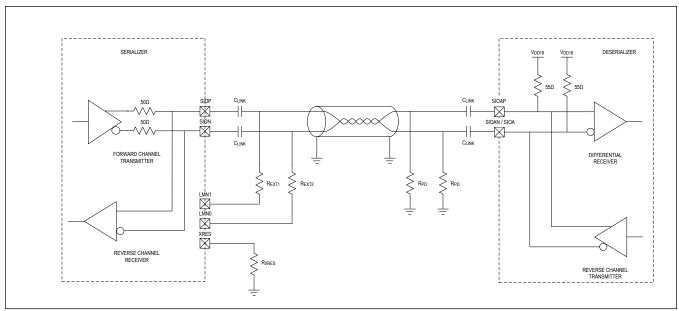

| STP Mode                                                                             | 47 |

| Link Lock                                                                            | 48 |

| GMSL3 Bandwidth Calculations                                                         | 49 |

| Control Channel and Side Channels                                                    | 51 |

## TABLE OF CONTENTS (CONTINUED)

| · · · · · · · · · · · · · · · · · · ·                      |      |

|------------------------------------------------------------|------|

| Main I <sup>2</sup> C/UART                                 | . 51 |

| I <sup>2</sup> C/UART CRC and Message Counter              | . 51 |

| I <sup>2</sup> C/UART CRC and Message Counter Options      | . 52 |

| Pass-Through I <sup>2</sup> C/UART                         | . 52 |

| Serial Peripheral Interface (SPI)                          | . 52 |

| General Purpose Input and Output (GPIO)                    | . 52 |

| Delay in Non-Compensated Mode                              | . 53 |

| Delay-Compensated Mode                                     | . 53 |

| Frame Sync                                                 | . 53 |

| Functional Safety Features                                 | . 53 |

| Analog-to-Digital Converter (ADC)                          | . 54 |

| ADC Features                                               | . 54 |

| ADC Architecture                                           | . 54 |

| ADC Operation                                              | . 55 |

| ADC Control Interface                                      | . 55 |

| ADC Power-Up and Power-Down Sequences                      | . 56 |

| ADC Overvoltage and Undervoltage Thresholds                | . 56 |

| ADC Round-Robin Sampling                                   | . 56 |

| ADC Application Diagrams for External Voltage Measurements | . 56 |

| Measuring External Voltages Lower than V <sub>DDIO</sub>   | . 56 |

| Measuring Voltages Higher than V <sub>DDIO</sub>           | . 57 |

| Junction Temperature Monitoring and Overtemperature Alarm  | . 57 |

| Eye-Opening Monitor                                        | . 58 |

| Sleep Mode                                                 | . 58 |

| Other Functions                                            | . 58 |

| Video PRBS                                                 | . 58 |

| MIPI CSI-2 Input Interface                                 | . 58 |

| Lane Configurations and Data Rates                         | . 59 |

| Clock Modes                                                | . 59 |

| Virtual Channel and Data Type Interleaving                 | . 59 |

| Lane Deskew                                                | . 59 |

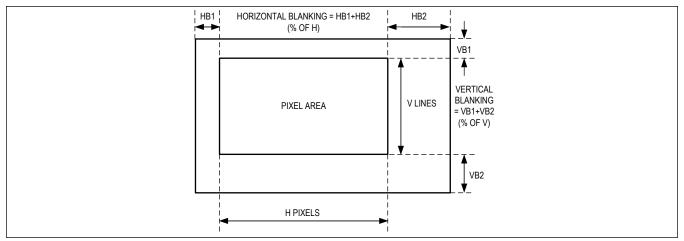

| Minimum Blanking                                           | . 60 |

| MIPI End-to-End Packet Spacing                             | . 60 |

| CFG Latch at Power-Up Pins                                 | . 60 |

| Multifunction Pin Assignments                              | . 62 |

| Control-Channel Link and Power-Up                          | . 63 |

| Device Reset                                               | . 63 |

| Clocking                                                   | . 63 |

| GMSL Reference Clock                                       | 64   |

## TABLE OF CONTENTS (CONTINUED)

| ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` `                                                  |    |

|------------------------------------------------------------------------------------------|----|

| Reference Clock Input Jitter                                                             | 64 |

| Remote Clocking (RoR Channel)                                                            | 64 |

| Reference Over Reverse Channel (RoR)                                                     | 64 |

| RoR Power-Up                                                                             | 64 |

| Reference Clock/DPLL Generation                                                          | 64 |

| Spread-Spectrum Clocking (SSC)                                                           | 64 |

| Error and Fault-Condition Monitoring                                                     | 65 |

| Power Supplies                                                                           | 65 |

| Supply Sequencing                                                                        | 65 |

| Overvoltage/Undervoltage                                                                 | 65 |

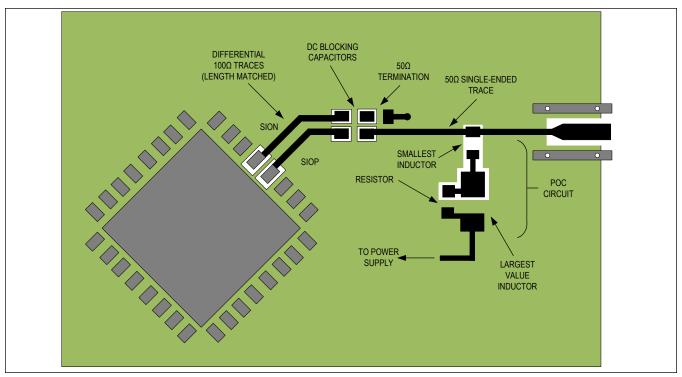

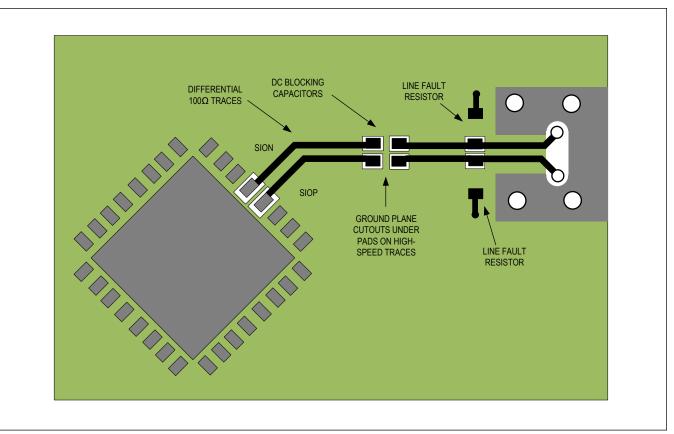

| PCB Layout Guidelines for GMSL                                                           | 66 |

| Ground Plane                                                                             | 66 |

| High-Speed GMSL Traces                                                                   | 66 |

| Power-over-Coax (PoC) Layout                                                             | 66 |

| Shielded-Twisted Pair Layout                                                             | 67 |

| Thermal Management                                                                       | 68 |

| Unique Serial Number                                                                     | 68 |

| Applications Information                                                                 | 69 |

| Software Programming Model                                                               | 69 |

| Programming Notes                                                                        | 69 |

| Control-Channel Programming                                                              | 69 |

| Conventional I <sup>2</sup> C/UART Control-Channel Programming                           | 69 |

| Host-to-Peripheral Main I <sup>2</sup> C and Pass-Through I <sup>2</sup> C Communication | 69 |

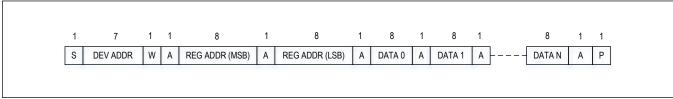

| I <sup>2</sup> C Write Packet Format                                                     | 70 |

| I <sup>2</sup> C Read Packet Format                                                      | 70 |

| Main I <sup>2</sup> C Host-to-GMSL2 Device Communication                                 | 70 |

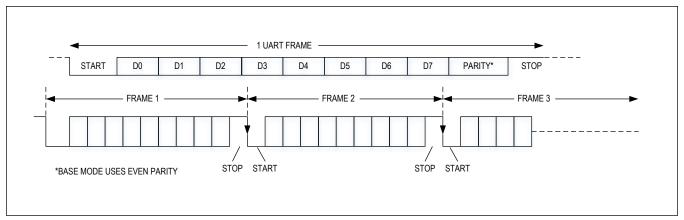

| Main UART                                                                                | 70 |

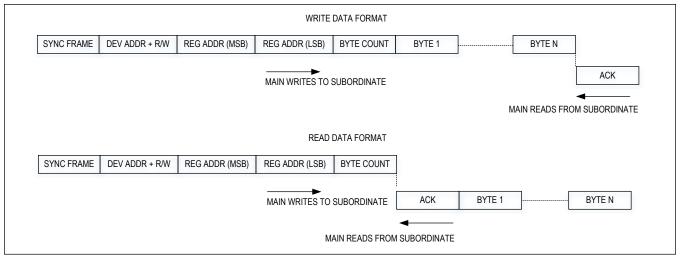

| UART Base Mode                                                                           | 70 |

| UART Bypass Mode                                                                         | 71 |

| Switching Between UART Base and Bypass Modes                                             | 71 |

| UART Frame Format                                                                        | 71 |

| Synchronization Frame                                                                    | 72 |

| Acknowledge Frame                                                                        | 72 |

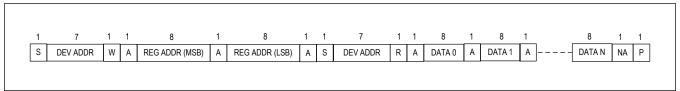

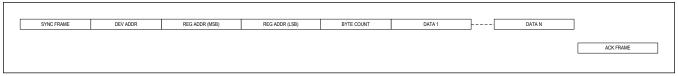

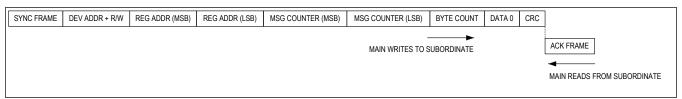

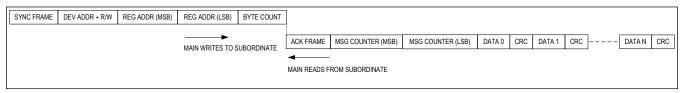

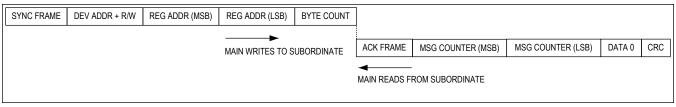

| Write Packet                                                                             | 72 |

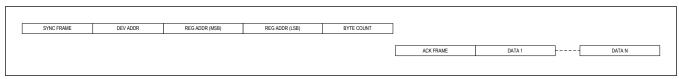

| Read Packet                                                                              | 73 |

| I <sup>2</sup> C/UART Control-Channel Programming with Optional CRC and Message Counter  | 73 |

| I <sup>2</sup> C/UART CRC and Message Counter Options                                    | 73 |

| I <sup>2</sup> C Writes with CRC                                                         | 73 |

| I <sup>2</sup> C Reads with CRC                                                          | 74 |

# TABLE OF CONTENTS (CONTINUED)

| Message Counter Writes       |     |

|------------------------------|-----|

| Message Counter Reads        | 74  |

| UART Writes with CRC         | 74  |

| UART Reads with CRC          | 75  |

| Typical Application Circuits | 77  |

| Typical Application Circuit  | 77  |

| Ordering Information         | 78  |

| Register Map                 | 79  |

| MAX96793                     | 79  |

| Register Details             | 97  |

| Revision History             | 248 |

#### LIST OF FIGURES

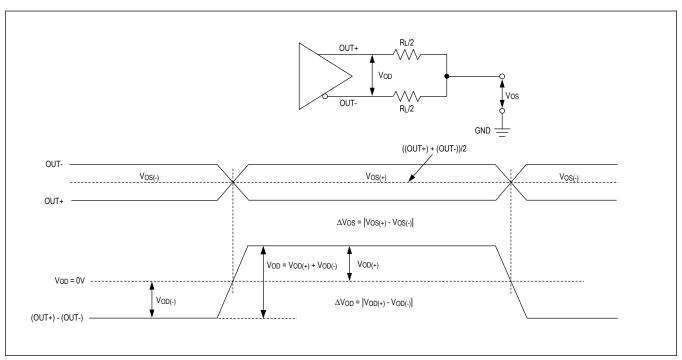

| Figure 1. Serial Output Parameters                                                                                | . 32 |

|-------------------------------------------------------------------------------------------------------------------|------|

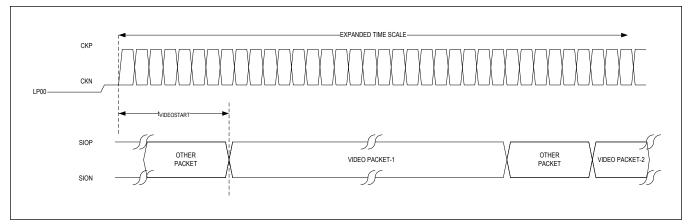

| Figure 2. GMSL3 Data Initialization Time                                                                          | . 33 |

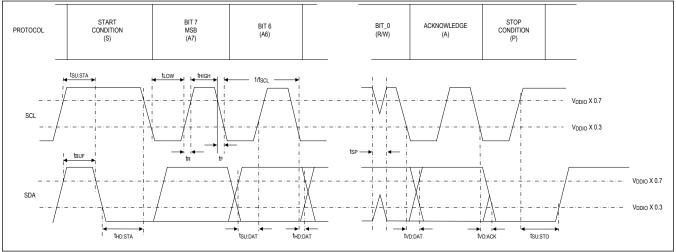

| Figure 3. I <sup>2</sup> C Timing Parameters                                                                      | . 33 |

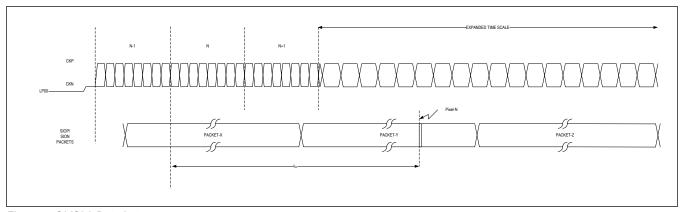

| Figure 4. GMSL3 Data Latency                                                                                      | . 33 |

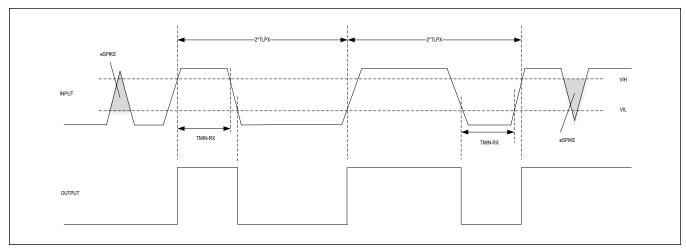

| Figure 5. D-PHY/C-PHY LP Receiver Pulse                                                                           | . 34 |

| Figure 6. D-PHY Data Clock Timing                                                                                 | . 34 |

| Figure 7. High-Speed Data Transmission in Bursts                                                                  | . 35 |

| Figure 8. D-PHY High-Speed Skew Calibration                                                                       | . 35 |

| Figure 9. Switching the Clock Lane Between Clock Transmission and Low-Power Mode                                  | . 36 |

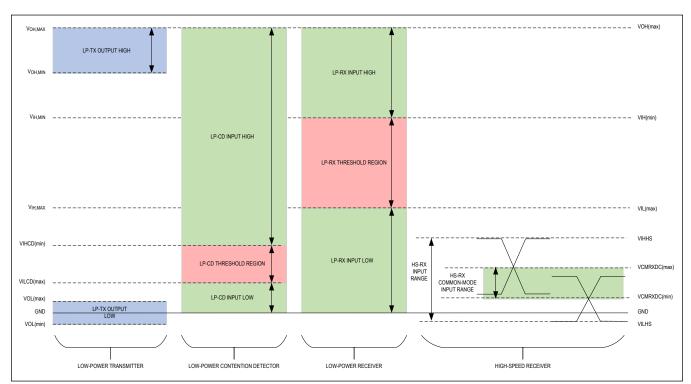

| Figure 10. Signaling and Contention Voltage Levels                                                                | . 36 |

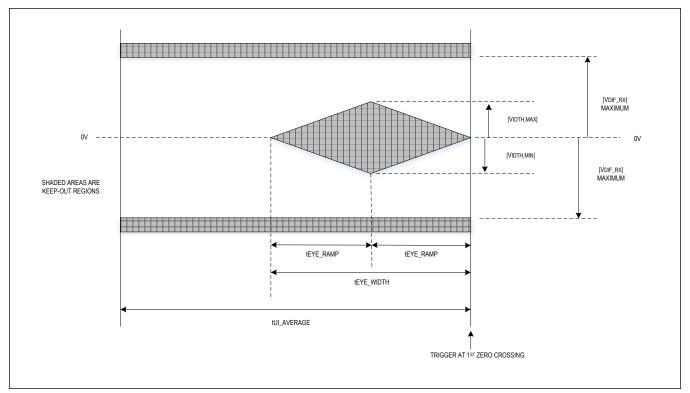

| Figure 11. C-PHY Receiver Eye Diagram                                                                             | . 37 |

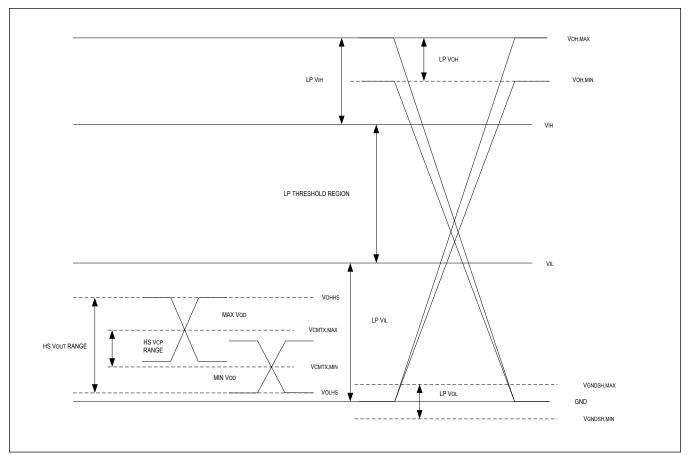

| Figure 12. C-PHY Signaling Levels                                                                                 | . 38 |

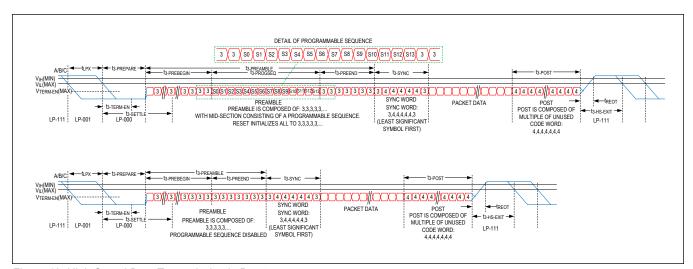

| Figure 13. High-Speed Data Transmission in Bursts                                                                 | . 38 |

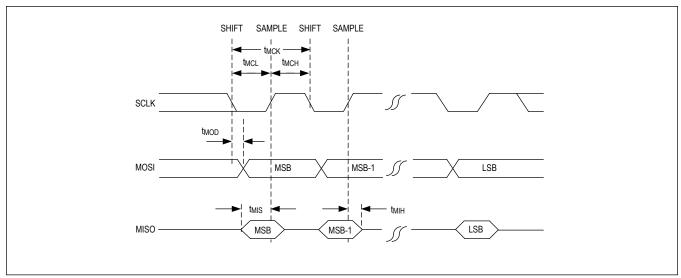

| Figure 14. SPI Main-Mode Timing Parameters                                                                        | . 39 |

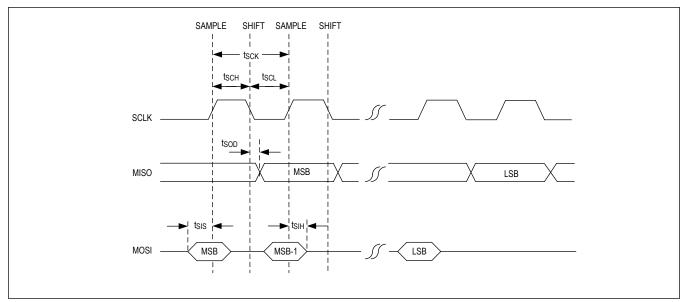

| Figure 15. SPI Subordinate-Mode Timing Parameters                                                                 | . 39 |

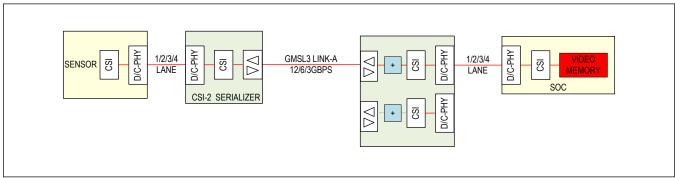

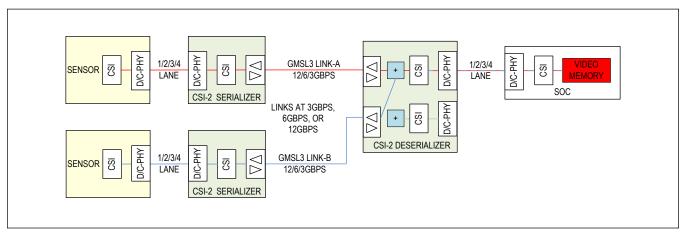

| Figure 16. Single Link                                                                                            | . 40 |

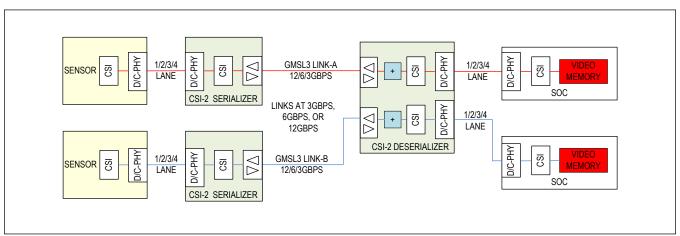

| Figure 17. Dual Link, Separate Data Type                                                                          | . 40 |

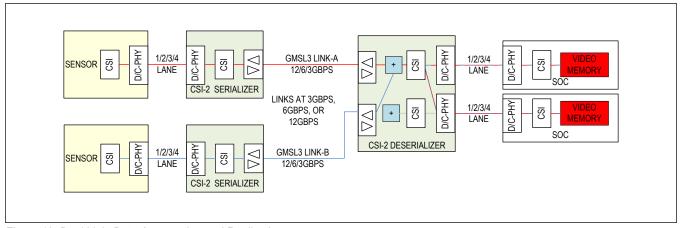

| Figure 18. Dual Link, Data Aggregation                                                                            | . 41 |

| Figure 19. Dual Link, Data Aggregation and Replication                                                            | . 41 |

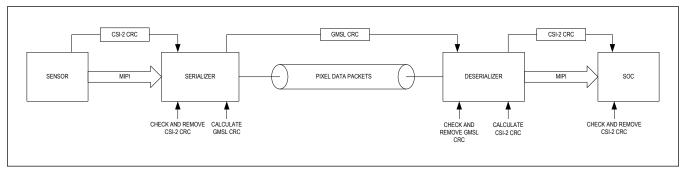

| Figure 20. Pixel Mode                                                                                             | . 42 |

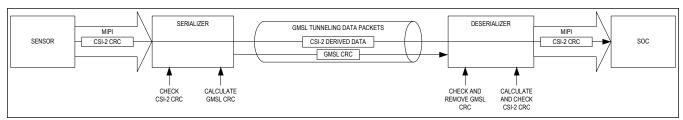

| Figure 21. Tunneling Mode                                                                                         | . 42 |

| Figure 22. Line Fault Detection Location Options                                                                  | . 46 |

| Figure 23. Typical GMSL Link Application Circuit for Coax Cable                                                   | . 47 |

| Figure 24. Typical GMSL Link Application Circuit for Twisted Pair (Line Fault Pair #1: LMN0 and LMN1, Option #2). | . 48 |

| Figure 25. GMSL2 Lock Time                                                                                        | . 48 |

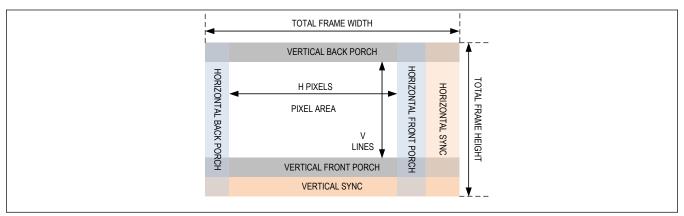

| Figure 26. Video Frame Format for Bandwidth Calculation                                                           | . 51 |

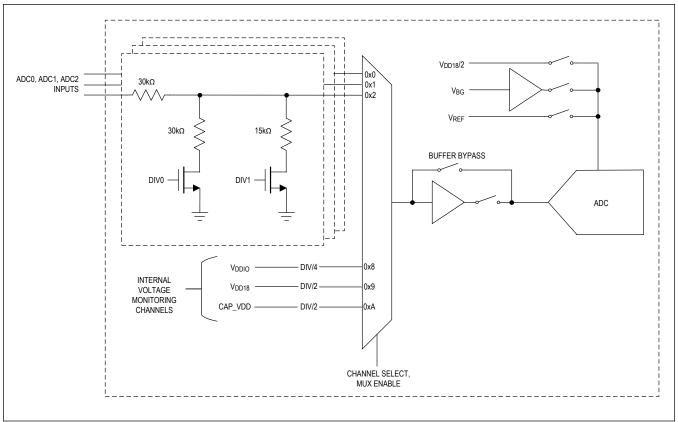

| Figure 27. ADC Block Diagram                                                                                      | . 55 |

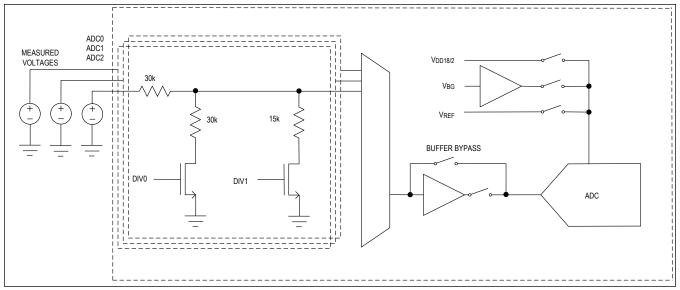

| Figure 28. Measuring External ADC Voltages < 3.6V                                                                 | . 57 |

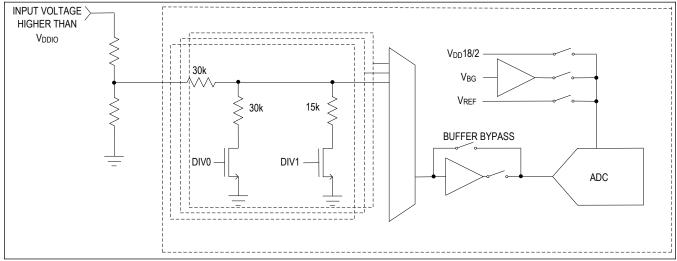

| Figure 29. Measuring External ADC Voltages Greater Than V <sub>DDIO</sub>                                         | . 57 |

| Figure 30. MIPI CSI-2 Lane Mapping Options and Default Settings                                                   | . 59 |

| Figure 31. Video Timing                                                                                           | . 60 |

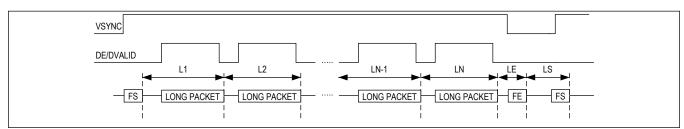

| Figure 32. End-to-End Packet Spacing                                                                              | . 60 |

| Figure 33. Coax PoC Layout Example                                                                                | . 67 |

| Figure 34. STP Layout Example                                                                                     | . 68 |

| Figure 35. I <sup>2</sup> C Write Packet Format                                                                   | . 70 |

| Figure 36. I <sup>2</sup> C Read Packet Format                                                                    | . 70 |

| Figure 37. UART Protocol for Base Mode                                                                            | . 71 |

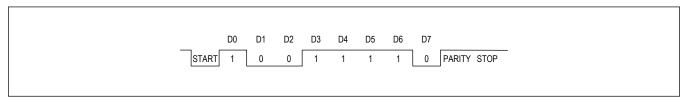

| Figure 38. UART Data Format for Base Mode                                                                         | . 72 |

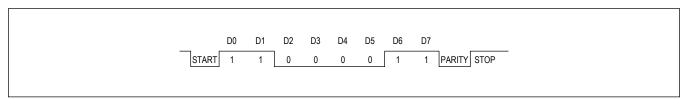

| Figure 39. UART Synchronization Frame                                                                             | . 72 |

# LIST OF FIGURES (CONTINUED)

| Figure 40. UART Acknowledge Frame                         | 72 |

|-----------------------------------------------------------|----|

| Figure 41. UART Write Packet Format                       |    |

| Figure 42. UART Read Packet Format                        |    |

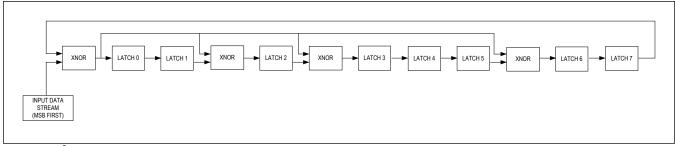

| Figure 43. I <sup>2</sup> C CRC Engine                    | 73 |

| Figure 44. I <sup>2</sup> C Multiple-Byte Write with CRC  | 74 |

| Figure 45. I <sup>2</sup> C Single-Byte Write with CRC    | 74 |

| Figure 46. I <sup>2</sup> C Multiple-Byte Read with CRC   | 74 |

| Figure 47. I <sup>2</sup> C Single-Byte Read with CRC     | 74 |

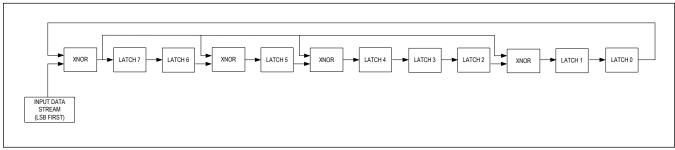

| Figure 48. UART CRC Engine                                | 75 |

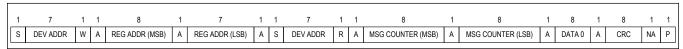

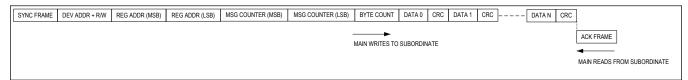

| Figure 49. UART Multiple-Byte Write Transactions with CRC |    |

| Figure 50. UART Single-Byte Write Transaction with CRC    | 75 |

| Figure 51. UART Multiple-Byte Read Transaction with CRC   | 75 |

| Figure 52. UART Single-Byte Read Transaction with CRC     | 76 |

#### **LIST OF TABLES**

| Table 1. Typical Maximum Cable Length vs. Attenuation                       | . 1 |

|-----------------------------------------------------------------------------|-----|

| Table 2. Recommended Operating Conditions                                   | 30  |

| Table 3. External Component Requirements                                    | 30  |

| Table 4. ESD Protection                                                     | 32  |

| Table 5. Coax Mode LINE Fault Configuration Options                         | 46  |

| Table 6. STP Mode Line Fault Configuration Options for LMN0/LMN1            | 47  |

| Table 7. Forward- and Reverse-Link Bandwidth Utilization                    | 50  |

| Table 8. SPI Latching Edge and Speed                                        | 52  |

| Table 9. Typical GPIO Delays for Forward-Link and Reverse-Link Transmission | 53  |

| Table 10. ADC Voltage Divider Settings                                      | 56  |

| Table 11. CFG0 Input Map                                                    | 61  |

| Table 12. CFG1 Input Map                                                    | 61  |

| Table 13. MFP Pin Function Map                                              | 62  |

| Table 14. Control- and Side-Channel Typical Rise and Fall Times             | 63  |

#### **Absolute Maximum Ratings**

| (All voltages with respect to ground)                        | D_P/N, CKP/N0.3V to +1.35V                                            |

|--------------------------------------------------------------|-----------------------------------------------------------------------|

| V <sub>DDIO</sub> 0.3V to +3.9V                              | XRES, X20.3V to (V <sub>DD18</sub> + 0.3V)                            |

| V <sub>DD18</sub> 0.3V to +2.0V                              | All Other Pins ( <u>Note B</u> )0.3V to (V <sub>DDIO</sub> + 0.3V)    |

| V <sub>DD</sub> 0.3V to +2.0V                                | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) TQFN & TQFN-SW, |

| CAP_VDD0.3V to +1.2V                                         | Multilayer board, derate 34.5mW/°C above +70°C1896mW                  |

| SIO_(Active State) ( <u>Note A</u> )0.3V to (CAP_VDD + 0.3V) | Storage Temperature Range40°C to +150°C                               |

| SIO_(Inactive State) (Note A)0.3V to (CAP_VDD + 0.3V)        | Soldering Temperature (reflow)+260°C                                  |

**Note A:** Active state means the device is powered-up and not in Sleep or Power-down modes. Inactive means the device is not powered-up or powered-up in Sleep or Power-down mode.

**Note B:** V<sub>DDIO</sub> = specified maximum voltage or 3.9V, whichever is lower.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### 32-Pin TQFN-SW (Side-Wettable)

| Package Code                           | T3255Y (Click on Land Pattern Number link below for additional details.) |

|----------------------------------------|--------------------------------------------------------------------------|

| Outline Number                         | <u>21-100156</u>                                                         |

| Land Pattern Number                    | <u>90-100067</u>                                                         |

| Thermal Resistance, Four-Layer Board   |                                                                          |

| Junction to Ambient (θ <sub>JA</sub> ) | 29°C/W                                                                   |

| Junction to Case (θ <sub>JC</sub> )    | 1.7°C/W                                                                  |

For the latest package outline information and land patterns (footprints), go to <a href="www.analog.com/packages">www.analog.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board in still air. For detailed information on package thermal considerations, refer to <a href="https://www.analog.com/thermal-tutorial">www.analog.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{DD18}$  = 1.7V to 1.9V,  $V_{DD}$  = 0.95V to 1.26V,  $V_{DDIO}$  = 1.7V to 3.6V,  $T_A$  = -40°C to +105°C, EP connected to PCB ground, typical values are at  $V_{DD18}$  =  $V_{DDIO}$  = 1.8V,  $V_{DD}$  = 1.0V,  $V_$

| COI                                                            | SYMBOL                                | CONDITIONS                                         | MIN        | TYP        | MAX       | UNITS |  |

|----------------------------------------------------------------|---------------------------------------|----------------------------------------------------|------------|------------|-----------|-------|--|

| /ARE                                                           | RACTERISTICS / G                      | DRWARD-CHANNEL SERIA                               | INPUTS/OUT | PUTS (SIOI | P, SION)— | SEE   |  |

| (VOH - VOL) for                                                |                                       |                                                    | 400        | 500        | 600       |       |  |

|                                                                |                                       |                                                    | 300        | 400        | 500       | mV    |  |

|                                                                | V <sub>ODT</sub>                      | DΩ ±1%,<br>Deak PAM4<br>al voltage                 | 800        | 1000       | 1200      | mV    |  |

|                                                                | VODI                                  | Ω ±1%,<br>peak NRZ<br>al voltage                   | 600        | 800        | 1000      | IIIV  |  |

| 1%, I                                                          | ΔV <sub>OD</sub>                      | )Ω ±1%, IV <sub>OD(H)</sub> - V <sub>OD(L)</sub> I |            |            | 25        | mV    |  |

| 1%, c                                                          | V <sub>OS</sub>                       | $\Omega$ ±1%, offset voltage in each ate           | 400        | 460        | 600       | mV    |  |

| $R_L = 100\Omega \pm 1\%$ , $I(V_{OS(H)} - V_{OS(L)})I$        |                                       |                                                    |            | 25         | mV        |       |  |

| Any pin to V <sub>DD18</sub>                                   |                                       | 45                                                 | 50         | 55         | Ω         |       |  |

| CEIV                                                           | ARACTERISTICS / D                     | RECEIVER                                           |            |            |           |       |  |

|                                                                | V <sub>CMRX(DC)</sub>                 |                                                    | 70         |            | 330       | mV    |  |

|                                                                | V <sub>IDTH</sub>                     |                                                    |            |            | 40        | mV    |  |

|                                                                | V <sub>IDTL</sub>                     |                                                    | -40        |            |           | mV    |  |

|                                                                | h V <sub>IHHS</sub>                   |                                                    |            |            | 460       | mV    |  |

|                                                                | V <sub>ILHS</sub>                     |                                                    | -40        |            |           | mV    |  |

|                                                                | d VTERM-EN                            |                                                    |            |            | 450       | mV    |  |

|                                                                | Z <sub>ID</sub>                       |                                                    | 80         | 100        | 125       | Ω     |  |

| DC ELECTRICAL CHARACTERISTICS / D-PHY LP RECEIVER—SEE Figure 5 |                                       |                                                    |            |            |           |       |  |

|                                                                |                                       | 740                                                |            |            | mV        |       |  |

|                                                                | V <sub>IL</sub>                       |                                                    |            |            | 550       | mV    |  |

|                                                                | V <sub>HYST</sub>                     |                                                    | 25         |            |           | mV    |  |

| 5V                                                             | I <sub>LEAK</sub>                     | 1.35V                                              | -10        |            | 10        | μA    |  |

|                                                                | V <sub>IH</sub> V <sub>IL</sub> VHYST |                                                    | 25         | _          |           |       |  |

$(V_{DD18}$  = 1.7V to 1.9V,  $V_{DD}$  = 0.95V to 1.26V,  $V_{DDIO}$  = 1.7V to 3.6V,  $T_A$  = -40°C to +105°C, EP connected to PCB ground, typical values are at  $V_{DD18}$  =  $V_{DDIO}$  = 1.8V,  $V_{DD}$  = 1.0V,  $V_$

| PARAMETER                                              | SYMBOL                | CONDITIONS                                                         | MIN                        | TYP | MAX                        | UNITS |

|--------------------------------------------------------|-----------------------|--------------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| DC ELECTRICAL CHARA                                    | ACTERISTICS /         | C-PHY HS RECEIVER—SEE Figure 11                                    | <u> </u>                   |     |                            |       |

| Common-Point Voltage<br>HS Receive Mode                | V <sub>CPRX(DC)</sub> | See Figure 12 (Note 8, Note 9)                                     | 95                         |     | 390                        | mV    |

| Differential Input High<br>Threshold                   | $V_{IDTH}$            |                                                                    |                            |     | 40                         | mV    |

| Differential Input Low<br>Threshold                    | $V_{IDTL}$            |                                                                    | -40                        |     |                            | mV    |

| Single-Ended Input High Voltage                        | V <sub>IHHS</sub>     | See Figure 10 (Note 8)                                             |                            |     | 535                        | mV    |

| Single-Ended Input Low Voltage                         | $V_{ILHS}$            | See Figure 10 (Note 8)                                             | -40                        |     |                            | mV    |

| Single-Ended Threshold<br>for HS Termination<br>Enable | V <sub>TERM-EN</sub>  | See <u>Figure 7</u>                                                |                            |     | 450                        | mV    |

| Differential Input<br>Impedance                        | Z <sub>ID</sub>       | Any two pins                                                       | 80                         | 100 | 120                        | Ω     |

| Differential Input<br>Impedance Mismatch               | ΔZ <sub>ID</sub>      | Between any two pin-pairs                                          |                            |     | 10                         | %     |

| DC ELECTRICAL CHARA                                    | ACTERISTICS /         | C-PHY LP RECEIVER                                                  |                            |     |                            | •     |

| Logic 1 Input Voltage                                  | V <sub>IH</sub>       | See Figure 12                                                      | 740                        |     |                            | mV    |

| Logic 0 Input Voltage,<br>Not in ULP State             | $V_{IL}$              | See <u>Figure 12</u>                                               |                            |     | 550                        | mV    |

| Input Hysteresis                                       | V <sub>HYST</sub>     |                                                                    | 25                         |     |                            | mV    |

| DC ELECTRICAL CHARA                                    | ACTERISTICS /         | I/O PINS (GPIO)                                                    |                            |     |                            |       |

| High-Level Input Voltage                               | $V_{IH}$              |                                                                    | 0.7 x<br>V <sub>DDIO</sub> |     |                            | V     |

| Low-Level Input Voltage                                | $V_{IL}$              |                                                                    |                            |     | 0.3 x<br>V <sub>DDIO</sub> | V     |

| High-Level Output<br>Voltage                           | V <sub>OH</sub>       | I <sub>OH</sub> = -4mA                                             | V <sub>DDIO</sub> -<br>0.4 |     |                            | V     |

| Low-Level Output<br>Voltage                            | V <sub>OL</sub>       | I <sub>OL</sub> = 4mA                                              |                            |     | 0.4                        | V     |

| Input Current                                          | I <sub>IN</sub>       | $V_{IN}$ = 0 to $V_{DDIO}$ . All pullup/pulldown devices disabled. |                            |     | 1                          | μA    |

| Input Capacitance                                      | C <sub>IN</sub>       | Each pin                                                           |                            | 5   |                            | pF    |

| Input Pullup/Pulldown                                  | R <sub>IN</sub>       | 40kΩ enabled                                                       |                            | 40  |                            | kΩ    |

| Resistance                                             |                       | 1MΩ enabled                                                        |                            | 1   |                            | ΜΩ    |

| DC ELECTRICAL CHARA                                    | ACTERISTICS /         | OPEN-DRAIN PINS                                                    |                            |     |                            |       |

| High-Level Input Voltage                               | $V_{IH}$              |                                                                    | 0.7 x<br>V <sub>DDIO</sub> |     |                            | V     |

| Low-Level Input Voltage                                | $V_{IL}$              |                                                                    |                            |     | 0.3 x<br>V <sub>DDIO</sub> | V     |

| Low-Level Open-Drain<br>Output Voltage                 | $V_{OL}$              | I <sub>OL</sub> = 4mA                                              |                            |     | 0.4                        | V     |

$(V_{DD18}$  = 1.7V to 1.9V,  $V_{DD}$  = 0.95V to 1.26V,  $V_{DDIO}$  = 1.7V to 3.6V,  $T_A$  = -40°C to +105°C, EP connected to PCB ground, typical values are at  $V_{DD18}$  =  $V_{DDIO}$  = 1.8V,  $V_{DD}$  = 1.0V,  $V_$

| PARAMETER                        | SYMBOL             | CONDITIONS                                                                       | MIN                        | TYP    | MAX                        | UNITS |

|----------------------------------|--------------------|----------------------------------------------------------------------------------|----------------------------|--------|----------------------------|-------|

| Input Current                    | I <sub>IN</sub>    | V <sub>IN</sub> = 0 to V <sub>DDIO</sub> . All pullup/pulldown devices disabled. |                            |        | 1                          | μA    |

| Input Capacitance                | C <sub>IN</sub>    | Each pin                                                                         |                            | 3      |                            | pF    |

| Internal Dulling Decistor        | В                  | 40kΩ enabled                                                                     |                            | 40     |                            | kΩ    |

| Internal Pullup Resistor         | $R_{PU}$           | 1MΩ enabled                                                                      |                            | 1      |                            | МΩ    |

| DC ELECTRICAL CHARA              | ACTERISTICS /      | PWDNB INPUT                                                                      | •                          |        |                            |       |

| High-Level Input Voltage         | $V_{IH}$           |                                                                                  | 0.7 x<br>V <sub>DDIO</sub> |        |                            | V     |

| Low-Level Input Voltage          | $V_{IL}$           |                                                                                  |                            |        | 0.3 x<br>V <sub>DDIO</sub> | V     |

| Input Current                    | I <sub>IN</sub>    | $V_{IN} = 0$ to $V_{DDIO}$                                                       |                            |        | 6                          | μΑ    |

| Input Capacitance                | C <sub>IN</sub>    |                                                                                  |                            | 3      |                            | pF    |

| Internal Pulldown<br>Resistor    | $R_{PD}$           |                                                                                  |                            | 1      |                            | МΩ    |

| DC ELECTRICAL CHARA              | ACTERISTICS /      | PUSH-PULL OUTPUTS (GPIO)                                                         | •                          |        |                            |       |

| High-Level Output<br>Voltage     | V <sub>OH</sub>    | I <sub>OH</sub> = -4mA                                                           | V <sub>DDIO</sub> - 0.4    |        |                            | ٧     |

| Low-Level Output<br>Voltage      | $V_{OL}$           | I <sub>OL</sub> = 4mA                                                            |                            |        | 0.4                        | V     |

| DC ELECTRICAL CHARA              | ACTERISTICS /      | LINE FAULT DETECTION INPUT (LMN0,                                                | LMN1)                      |        |                            |       |

| Open-Pin Voltage                 | V <sub>O0</sub>    | LMN0                                                                             |                            | 1.25   |                            | V     |

|                                  | V <sub>O1</sub>    | LMN1                                                                             |                            | 0.75   |                            |       |

| DC ELECTRICAL CHARA              | ACTERISTICS /      | REFERENCE CLOCK INPUT (CRYSTAL)                                                  | (X1/OSC, X2)               |        |                            |       |

| X1/OSC Input<br>Capacitance      | C <sub>IN_X1</sub> |                                                                                  |                            | 3      |                            | pF    |

| X2 Input Capacitance             | C <sub>IN_X2</sub> |                                                                                  |                            | 1      |                            | pF    |

| Internal X2 Limit<br>Resistor    | $R_{LIM}$          |                                                                                  |                            | 1.2    |                            | kΩ    |

| Internal Feedback<br>Resistor    | $R_{FB}$           |                                                                                  |                            | 10     |                            | kΩ    |

| Transconductance                 | 9m                 |                                                                                  |                            | 28     |                            | mA/V  |

| DC ELECTRICAL CHARA<br>FLOATING) | ACTERISTICS /      | REFERENCE CLOCK REQUIREMENTS (I                                                  | EXTERNAL IN                | PUT ON | X1/OSC, X2                 |       |

| High-Level Input Voltage         | V <sub>IH</sub>    |                                                                                  | 0.9                        |        |                            | V     |

| Low-Level Input Voltage          | V <sub>IL</sub>    |                                                                                  |                            |        | 0.4                        | V     |

| Input Resistance                 | R <sub>IN</sub>    |                                                                                  |                            | 10     |                            | kΩ    |

| X1 Input Capacitance             | C <sub>IN_X1</sub> |                                                                                  |                            | 3      |                            | pF    |

| DC ELECTRICAL CHARA              | ACTERISTICS /      | MONITOR ADC                                                                      |                            |        |                            |       |

| Resolution                       |                    |                                                                                  |                            | 10     |                            | bits  |

$(V_{DD18}$  = 1.7V to 1.9V,  $V_{DD}$  = 0.95V to 1.26V,  $V_{DDIO}$  = 1.7V to 3.6V,  $T_A$  = -40°C to +105°C, EP connected to PCB ground, typical values are at  $V_{DD18}$  =  $V_{DDIO}$  = 1.8V,  $V_{DD}$  = 1.0V,  $V_$

| PARAMETER           | SYMBOL          | СО                                        | NDITIONS                                         | MIN | TYP                                                                      | MAX | UNITS  |  |

|---------------------|-----------------|-------------------------------------------|--------------------------------------------------|-----|--------------------------------------------------------------------------|-----|--------|--|

|                     |                 | Using internal reference internal buffer. | erence, no divider, no                           |     | 0.0 to<br>V <sub>REF</sub>                                               |     |        |  |

| Input-Voltage Range |                 |                                           | erence, 2:1 divider, no<br>DC0, ADC1, ADC2 pins. |     | 0.0 to<br>lower of<br>(2 x<br>V <sub>REF</sub> ) or<br>V <sub>DDIO</sub> |     | V V    |  |

|                     | V <sub>IN</sub> |                                           | erence, 3:1 divider, no<br>OC0, ADC1, ADC2 pins. |     | 0.0 to<br>lower of<br>(3 x<br>V <sub>REF</sub> ) or<br>V <sub>DDIO</sub> |     |        |  |

|                     |                 |                                           | erence, 4:1 divider, no<br>DC0, ADC1, ADC2 pins. |     | 0.0 to<br>V <sub>DDIO</sub>                                              |     |        |  |

|                     |                 | No divider, buffer                        | ed input                                         |     | 0.1 to<br>V <sub>REF</sub>                                               |     |        |  |

|                     |                 | Input configured f                        | or 2:1 voltage division                          |     | 60                                                                       |     | kΩ     |  |

| Invest Decistores   |                 | Input configured f                        | or 3:1 voltage division                          |     | 45                                                                       |     | kΩ     |  |

| Input Resistance    | R <sub>IN</sub> | Input configured f                        | or 4:1 voltage division                          |     | 40                                                                       |     | 1      |  |

|                     |                 | No divider, buffer                        | ed input                                         |     | > 5                                                                      |     | МΩ     |  |

|                     |                 |                                           | GPIO /1 (no<br>divider)                          |     | 1                                                                        |     |        |  |

|                     |                 |                                           | GPIO /2                                          |     | 2                                                                        |     | kΩ     |  |

|                     |                 |                                           | GPIO /3                                          |     | 3                                                                        |     | ] ,,,, |  |

| Divider Ratio       | DR              | Divider Ratio                             | GPIO /4                                          |     | 4                                                                        |     | ] V/V  |  |

|                     |                 |                                           | V <sub>DDIO</sub> /4 Input                       |     | 4.017                                                                    |     |        |  |

|                     |                 |                                           | V <sub>DD18</sub> /2 Input                       |     | 2.009                                                                    |     |        |  |

|                     |                 |                                           | CAP_VDD/2 Input                                  |     | 2.009                                                                    |     |        |  |

$(V_{DD18}$  = 1.7V to 1.9V,  $V_{DD}$  = 0.95V to 1.26V,  $V_{DDIO}$  = 1.7V to 3.6V,  $T_A$  = -40°C to +105°C, EP connected to PCB ground, typical values are at  $V_{DD18}$  =  $V_{DDIO}$  = 1.8V,  $V_{DD}$  = 1.0V,  $V_$

| PARAMETER                                             | SYMBOL               | COND                                                                           | ITIONS                                 | MIN  | TYP | MAX  | UNITS       |

|-------------------------------------------------------|----------------------|--------------------------------------------------------------------------------|----------------------------------------|------|-----|------|-------------|

|                                                       |                      |                                                                                | External ADC (0-2)<br>voltage = 0.1V   | -10  |     | +10  |             |

|                                                       |                      | External V <sub>REF</sub> = 1.25V, no divider, buffered input                  | External ADC (0-2)<br>voltage = 0.625V | -12  |     | +12  |             |

|                                                       |                      | bullered input                                                                 | External ADC (0-2)<br>voltage = 1.2V   | -15  |     | +15  |             |

|                                                       |                      | Internal Reference                                                             | External ADC (0-2)<br>voltage = 0.1V   | -10  |     | +10  |             |

|                                                       |                      | (V <sub>REF</sub> = 1.25V), no divider, buffered                               | External ADC (0-2)<br>voltage = 0.625V | -12  |     | +12  |             |

| Total Unadjusted Error                                |                      | input                                                                          | External ADC (0-2)<br>voltage = 1.2V   | -15  |     | +15  |             |

|                                                       | TUE                  | Internal Reference<br>(V <sub>REF</sub> = 1.25V),<br>GPIO/2, buffered<br>input | External ADC (0-2)                     | -15  |     | +15  | mV          |

|                                                       |                      | Internal Reference<br>(V <sub>REF</sub> = 1.25V),<br>GPIO/3, buffered<br>input | External ADC (0-2)                     | -30  |     | +30  | mV °C °C °C |

|                                                       |                      | Internal Reference<br>(V <sub>REF</sub> = 1.25V),<br>GPIO/4, buffered<br>input | External ADC (0-2)                     | -42  |     | +42  |             |

|                                                       |                      | Internal Reference                                                             | V <sub>DDIO</sub> /4 Input             | -40  |     | +40  | _           |

|                                                       |                      | $(V_{REF} = 1.25V),$                                                           | V <sub>DD18</sub> /2 Input             | -15  |     | +15  |             |

|                                                       |                      | buffered input                                                                 | CAP_VDD/2 Input                        | -15  |     | +15  | -           |

| Reference-Voltage<br>Tolerance for 1% ADC<br>Accuracy | V <sub>REF_TOL</sub> | External V <sub>REF</sub> = 1.29 buffered input                                | 5V, no divider,                        |      | ±1  |      | mV          |

| DC ELECTRICAL CHAR                                    | ACTERISTICS /        | TEMPERATURE MON                                                                | NITOR ( <u>Note 2</u> )                |      |     |      |             |

| Measurable Range                                      | T1                   |                                                                                |                                        | -40  |     | +105 | °C          |

| Accuracy                                              | ERROR <sub>T1</sub>  | -40°C to +105°C                                                                |                                        |      | ±3  |      | °C          |

| Measurable Range                                      | T2                   |                                                                                |                                        | +105 |     | 125  | °C          |

| Accuracy                                              | ERROR <sub>T2</sub>  | +105°C to +125°C                                                               |                                        | -2.5 |     | +2.5 | °C          |

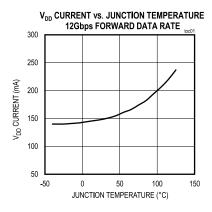

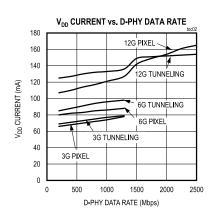

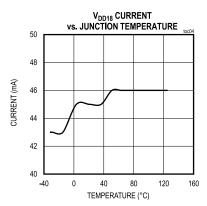

| DC ELECTRICAL CHAR                                    | ACTERISTICS /        | POWER SUPPLY CU                                                                | RRENTS (GMSL3 MO                       | DE)  |     |      |             |

| Supply Current (Note 3)                               | I <sub>DD</sub>      | RGB888, 12Gbps,<br>4-Lane CSI-2<br>DPHY input,<br>2.5Gbps per lane             |                                        |      | 46  | 53   | mA          |

| Supply Current (Note 3)                               | I <sub>DD</sub>      | RGB888, 12Gbps, 4-Lane CSI-2 DPHY input, 2.5Gbps per lane                      |                                        | 340  | mA  |      |             |

$(V_{DD18}$  = 1.7V to 1.9V,  $V_{DD}$  = 0.95V to 1.26V,  $V_{DDIO}$  = 1.7V to 3.6V,  $T_A$  = -40°C to +105°C, EP connected to PCB ground, typical values are at  $V_{DD18}$  =  $V_{DDIO}$  = 1.8V,  $V_{DD}$  = 1.0V,  $V_$

| PARAMETER                                                     | SYMBOL            | COND                                                                      | ITIONS                                               | MIN        | TYP                                | MAX | UNITS                                               |

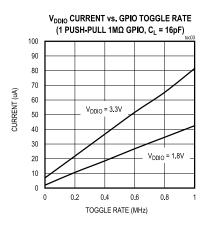

|---------------------------------------------------------------|-------------------|---------------------------------------------------------------------------|------------------------------------------------------|------------|------------------------------------|-----|-----------------------------------------------------|

| Maximum V <sub>DDIO</sub> Supply<br>Current ( <i>Note 4</i> ) | I <sub>DDIO</sub> | Per toggling GPIO,<br>C <sub>L</sub> = 20pF                               | V <sub>DDIO</sub> = 1.9V                             |            | 44                                 |     | μA/MHz                                              |

| Maximum V <sub>DDIO</sub> Supply Current ( <i>Note 4</i> )    | I <sub>DDIO</sub> | Per toggling GPIO,<br>C <sub>L</sub> = 20pF                               | V <sub>DDIO</sub> = 3.6V                             |            | 81                                 |     | µA/MHz                                              |

| DC ELECTRICAL CHAR                                            | ACTERISTICS / I   | POWER-DOWN CUR                                                            | RENT                                                 | •          |                                    |     | '                                                   |

|                                                               |                   | -+ 2 0 /                                                                  | T <sub>A</sub> = +25°C                               |            | 6.4                                |     | μΑ/MHz μΑ/MHz μΑ μΑ  μΑ  μΑ  μΑ  μΑ  μΑ  μΑ  μΑ  μΑ |

|                                                               |                   | V <sub>DDIO</sub> at 3.6V                                                 | T <sub>A</sub> = +105°C                              |            | 6.1                                |     | 1                                                   |

| Maximum Power-Down                                            | I                 | \/ at 1 0\/                                                               | T <sub>A</sub> = +25°C                               |            | 0.5                                |     | μΑ/MHz μΑ/MHz μΑ/MHz μΑ μΑ ps ps                    |

| Current                                                       | I <sub>DD</sub>   | V <sub>DD18</sub> at 1.9V                                                 | T <sub>A</sub> = +105°C                              |            | 1.9                                |     |                                                     |

|                                                               |                   | V at 1.26V                                                                | T <sub>A</sub> = +25°C                               |            | 3                                  |     |                                                     |

|                                                               |                   | V <sub>DD</sub> at 1.26V                                                  | T <sub>A</sub> = +105°C                              |            | 48                                 |     |                                                     |

| DC ELECTRICAL CHAR                                            | ACTERISTICS /     | SLEEP CURRENT                                                             |                                                      | •          |                                    |     |                                                     |

| Maximum Sleep Current                                         |                   | \/ at 2.6\/                                                               | T <sub>A</sub> = +25°C                               |            | 7.7                                |     |                                                     |

|                                                               |                   | V <sub>DDIO</sub> at 3.6V                                                 | T <sub>A</sub> = +105°C                              |            | 7.4                                |     |                                                     |

|                                                               | I                 | \/ ot 1 0\/                                                               | T <sub>A</sub> = +25°C                               |            | 0.5                                |     | ]                                                   |

|                                                               | I <sub>DD</sub>   | V <sub>DD18</sub> at 1.9V                                                 | T <sub>A</sub> = +105°C                              |            | 5                                  |     | ] μΑ                                                |

|                                                               |                   | V at 1.26V                                                                | T <sub>A</sub> = +25°C                               |            | 6.2                                |     |                                                     |

|                                                               |                   | V <sub>DD</sub> at 1.26V                                                  | T <sub>A</sub> = +105°C                              |            | 49                                 |     |                                                     |

| AC ELECTRICAL CHAR                                            | ACTERISTICS / I   | FORWARD CHANNE                                                            | L SWITCHING CHAR                                     | ACTERISTIC | s                                  |     |                                                     |

| Serial-Output Rise Time                                       | t <sub>R</sub>    | 20% to 80%, V <sub>OD</sub> = R <sub>L</sub> = 100Ω, 500mV s $50Ω$        |                                                      |            | 50                                 |     | ps                                                  |

| Serial-Output Fall Time                                       | t <sub>F</sub>    | $80\%$ to 20%, $V_{OD}$ = $R_L$ = 100Ω, 400mV s $50Ω$                     | 800mV differential,<br>single-ended R <sub>L</sub> = |            | 50                                 |     | ps                                                  |

| Total Serial-Output Jitter                                    | t <sub>TSOJ</sub> | PRBS7, single-ende                                                        | d or differential                                    |            | 0.15                               |     | UI (p-p)                                            |

| Deterministic Serial-<br>Output Jitter                        | t <sub>DSOJ</sub> | PRBS7, single-ende                                                        | d or differential                                    |            | 0.10                               |     | UI (p-p)                                            |

| Lock Time                                                     | <sup>t</sup> LOCK | Time from deassertion LOCK = '1'. See Figu                                |                                                      |            | 45                                 |     | ms                                                  |

|                                                               |                   |                                                                           | Pixel mode                                           |            | 120 x<br>t <sub>PCLK</sub>         |     |                                                     |

| Maximum Video Latency                                         | t <sub>VL</sub>   | Time from CSI-2<br>input to SIO±<br>output in GMSL2<br>packet. See Figure | Tunneling mode<br>6G                                 |            | 30 x<br>tPCLK +<br>1µs             |     | s                                                   |

|                                                               |                   | 4.                                                                        | Tunneling mode<br>3G                                 |            | 30 x<br>t <sub>PCLK</sub> +<br>2µs |     |                                                     |

| PWDNB Hold Time                                               | tHOLD_PWDNB       | The minimum duration PWDNB must be held LOW to reset the device.          |                                                      |            | 1                                  |     | ms                                                  |

$(V_{DD18}$  = 1.7V to 1.9V,  $V_{DD}$  = 0.95V to 1.26V,  $V_{DDIO}$  = 1.7V to 3.6V,  $T_A$  = -40°C to +105°C, EP connected to PCB ground, typical values are at  $V_{DD18}$  =  $V_{DDIO}$  = 1.8V,  $V_{DD}$  = 1.0V,  $V_$

| PARAMETER                                            | SYMBOL                                                       | CON                       | DITIONS                            | MIN                   | TYP   | MAX  | UNITS              |  |

|------------------------------------------------------|--------------------------------------------------------------|---------------------------|------------------------------------|-----------------------|-------|------|--------------------|--|

| Data Initialization Time                             | t <sub>PU</sub>                                              | CSI-2 until it appea      |                                    |                       | 2     |      | ms                 |  |

| GPI-to-GPO Delay                                     | t <sub>GPD1</sub>                                            | Delay compensate          | d mode.                            |                       | 10    |      | μs                 |  |

| or rio or o Belay                                    | t <sub>GPD2</sub>                                            | Non-delay compen          | Non-delay compensated mode.        |                       | 3     |      | μο                 |  |

| GPI-GPO Skew<br>Reverse Path                         | tskew                                                        | Delay compensate          | Delay compensated mode.            |                       | 7     |      | ns                 |  |

| AC ELECTRICAL CHARA                                  | ACTERISTICS /                                                | D-PHY HS RECEIVE          | ER                                 |                       |       |      |                    |  |

| Common-Mode<br>Interference Beyond<br>450MHz         | ΔV <sub>CMRX(HF)</sub>                                       | Note 2, Note 5,<br>Note 8 | Data rate > 1.5Gbps                |                       |       | 50   | mV                 |  |

| Common-Mode<br>Interference<br>50MHz–450MHz          | ΔV <sub>CMRX(LF)</sub>                                       | Note 2, Note 5,<br>Note 6 | Data rate > 1.5Gbps                | -25                   |       | 25   | mV                 |  |

| Common-Mode<br>Reflection Coefficient                | Scc <sub>RX</sub>                                            | 450MHz < f < 1.87         | 450MHz < f < 1.875GHz              |                       | -5    |      | dB                 |  |

| D:"                                                  |                                                              | f < 20MHz                 |                                    |                       | -22.5 |      |                    |  |

| Differential-Mode Reflection Coefficient             | Sdd <sub>RX</sub>                                            | f = 1.25GHz               |                                    |                       | -12   |      | dB                 |  |

|                                                      |                                                              | f = 1.875GHz              |                                    |                       | -9.7  |      | V*ps               |  |

| AC ELECTRICAL CHARA                                  | ACTERISTICS /                                                | D-PHY LP RECEIVE          | R—SEE <u>Figure 5</u> ( <u>Not</u> | <u>e 2</u> )          |       |      |                    |  |

| Input Pulse Rejection                                | e <sub>SPIKE</sub>                                           | See Figure 5              |                                    |                       |       | 300  | V∗ps               |  |

| Minimum Pulse Width Response                         | T <sub>MIN-RX</sub>                                          | See Figure 5              |                                    | 20                    |       |      | ns                 |  |

| Peak Interference<br>Amplitude                       | V <sub>INT</sub>                                             |                           |                                    |                       |       | 200  | mV                 |  |

| Interference Frequency                               | f <sub>INT</sub>                                             |                           |                                    | 450                   |       |      | MHz                |  |

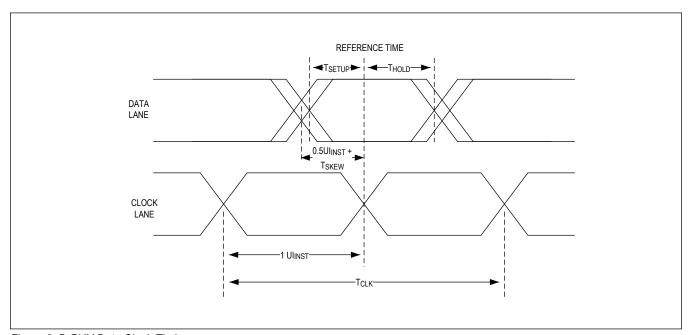

| AC ELECTRICAL CHARA                                  | ACTERISTICS /                                                | D-PHY DATA CLOC           | K TIMING—SEE <u>Figur</u>          | e 6 ( <u>Note 2</u> ) |       |      |                    |  |

| UI Instantaneous                                     | UI <sub>INST</sub>                                           |                           |                                    | 0.4                   |       | 12.5 | ns                 |  |

| UI Variation                                         | ΔUΙ                                                          | UI ≥ 1ns, within a s      | single burst                       | -10%                  |       | +10% | UI                 |  |

| Of Variation                                         | ДОГ                                                          | 0.667ns < UI < 1ns        | s, within a single burst           | -5%                   |       | 5%   | 01                 |  |

| Data to Clock Setup                                  | toczupiow                                                    | < 1.0Gbps                 |                                    | 0.15                  |       |      | UI <sub>INST</sub> |  |

| Time                                                 | tsetup[RX]                                                   | > 1.0Gbps                 |                                    | 0.2                   |       |      | OINST              |  |

| Data to Clock Hold Time                              | tuoi prpys                                                   | < 1.0Gbps                 |                                    | 0.15                  |       |      | UI <sub>INST</sub> |  |

| Data to clock field fillie                           | thold[RX]                                                    | > 1.0Gbps                 |                                    | 0.2                   |       |      | O'INST             |  |

| Static Data to Clock<br>Skew                         | T <sub>SKEW[RX]</sub><br>static                              | > 1.5Gbps                 |                                    | -0.2                  |       | 0.2  | UI <sub>INST</sub> |  |

| Dynamic Data to Clock<br>Skew Window Rx<br>Tolerance | T <sub>SETUP[RX]</sub> +<br>T <sub>HOLD[RX]</sub><br>Dynamic | > 1.5Gbps                 | > 1.5Gbps                          |                       |       |      | UI <sub>INST</sub> |  |

$(V_{DD18}$  = 1.7V to 1.9V,  $V_{DD}$  = 0.95V to 1.26V,  $V_{DDIO}$  = 1.7V to 3.6V,  $T_A$  = -40°C to +105°C, EP connected to PCB ground, typical values are at  $V_{DD18}$  =  $V_{DDIO}$  = 1.8V,  $V_{DD}$  = 1.0V,  $V_$

| PARAMETER                                                                                                                                             | SYMBOL                   | CONDITIONS                   | MIN                                                    | TYP MAX        | UNITS |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------|--------------------------------------------------------|----------------|-------|

| AC ELECTRICAL CHAR                                                                                                                                    | ACTERISTICS / I          | D-PHY GLOBAL OPERATION TIM   | ING ( <u>Note 2</u> )                                  |                |       |

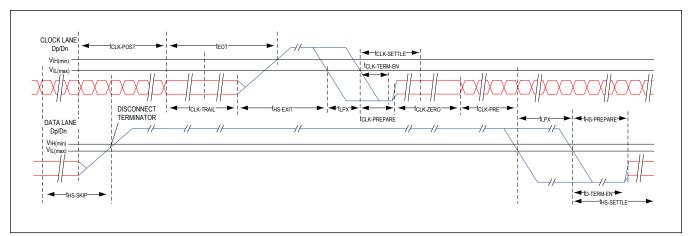

| Time Interval When the HS Receiver Ignores Any Clock Lane HS Transitions, Starting from the Beginning of TCLK-PREPARE-                                | tclk-settle              | See Figure 9                 | 95                                                     | 300            | ns    |

| Time for the Clock Lane<br>Receiver to Enable the<br>HS Line Termination,<br>Starting from the Time<br>Point When Dn Crosses<br>V <sub>IL,MAX</sub> . | t <sub>CLK-TERM-EN</sub> | See Figure 9                 | Time for Dn to reach VTERM-EN                          | 38             | ns    |

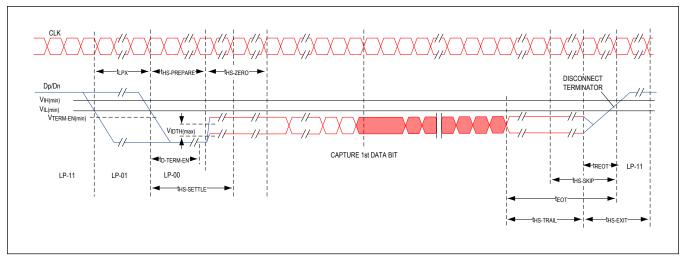

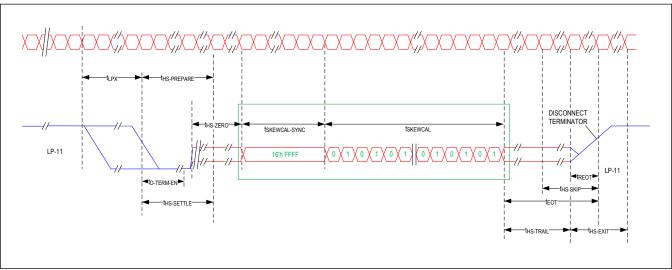

| Time for the Data Lane<br>Receiver to Enable the<br>HS Line Termination,<br>Starting from the Time<br>Point When Dn Crosses<br>V <sub>IL,MAX</sub> .  | <sup>t</sup> D-TERM-EN   | See Figure 7 and Figure 8    | Time for<br>Dn to<br>reach<br>VTERM-<br>EN             | 35ns +<br>4*UI | ns    |

| Time Interval When the HS Receiver Ignores Any Data Lane HS Transitions, Starting from the Beginning of THS-PREPARE                                   | t <sub>HS-SETTLE</sub>   | See Figure 7 and Figure 8    | 85 +<br>6*UI                                           | 145 +<br>10*Ul | ns    |

| AC ELECTRICAL CHAR                                                                                                                                    | ACTERISTICS /            | C-PHY HS RECEIVER            |                                                        |                |       |

| Common-Point<br>Interference Beyond<br>450MHz                                                                                                         | ΔV <sub>CPRX(HF)</sub>   | ( <u>Note 8</u> )            |                                                        | 50             | mV    |

| Common-Point<br>Interference<br>50MHz-450MHz                                                                                                          | ΔV <sub>CPRX(LF)</sub>   | ( <u>Note 5, Note 6</u> )    | -25                                                    | 25             | mV    |

| AC ELECTRICAL CHAR                                                                                                                                    | ACTERISTICS /            | C-PHY LP RECEIVER—SEE Figure | e 5 ( <u>Note 2</u> )                                  |                |       |

| Input Pulse Rejection                                                                                                                                 | e <sub>SPIKE</sub>       |                              |                                                        | 300            | V∗ps  |

| Minimum Pulse Width Response                                                                                                                          | T <sub>MIN-RX</sub>      |                              | 20                                                     |                | ns    |

| Peak Interference<br>Amplitude                                                                                                                        | V <sub>INT</sub>         |                              |                                                        | 200            | mV    |

| Interference Frequency                                                                                                                                | f <sub>INT</sub>         |                              | 450                                                    |                | MHz   |

| AC ELECTRICAL CHAR                                                                                                                                    | ACTERISTICS /            | CSI-2 C-PHY GLOBAL OPERATIO  | N TIMING                                               |                |       |

| Time for the Subordinate to Enable the HS Line Termination, Starting from the Time Point When the A, B and C Wire Cross V <sub>IL_MAX</sub>           | T <sub>3-TERM-EN</sub>   | See Figure 7                 | >Time<br>for lines<br>to fall<br>below<br>VTERM-<br>EN | 38             | ns    |