## IO-Link Device Transceiver with Integrated Cortex-M0 and Analog Front End

**MAX22522**

### Product Highlights

- Enable Smallest Sensors and Actuators

- Cortex-M0 with 64kB RAM and SWD

- IO-Link State Machine

- High Performance IO-Link Transceiver

- High Speed Comparator

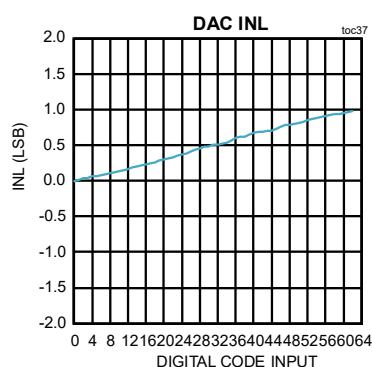

- 6-bit DAC

- Three 256-Tap 10kΩ Variable Resistors

- 60kΩ 64-Tap Variable Resistor

- 13-Bit ADC

- 10 GPIOs Configurable as I<sup>2</sup>C, SPI, SWD

- Integrated Temperature Sensor

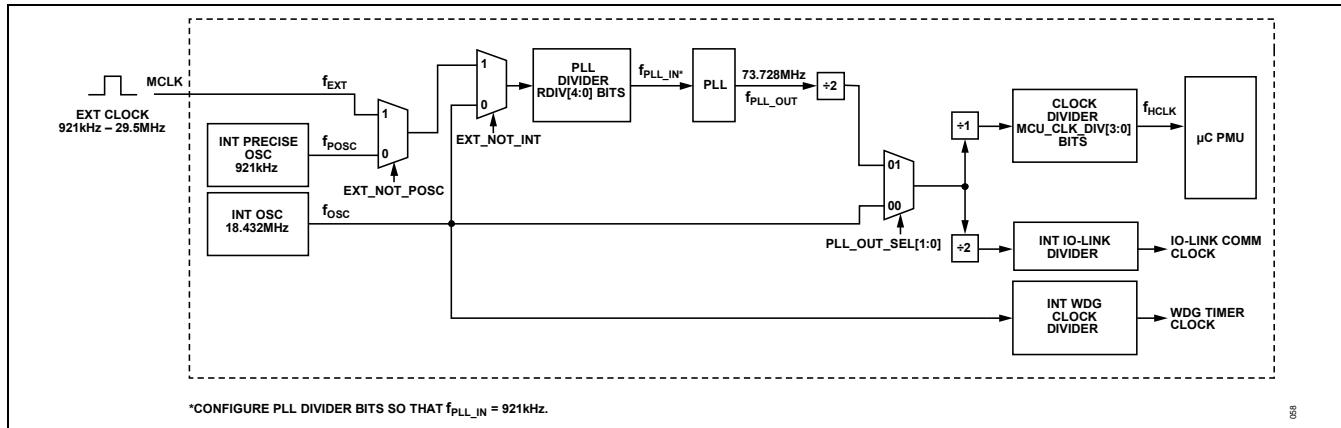

- Integrated Oscillator with PLL for IO-Link

- Highly Flexible and Configurable

- 7V to 36V Supply

- COM1, COM2, and COM3 Data Rates

- Programmable 50mA to 250mA C/Q Current Limit Threshold

- 5V and 1.8V Linear Regulators with Controller

- WLP Package (4.42mm × 2.64mm)

- Robust 24V IO Interface

- Reverse Polarity and Overvoltage Protection

- Internal Monitoring Enables Enhanced Diagnostics

- Fast Demag of 200mA/1.2H Inductive Loads

- ±4kV IEC 61000-4-2 Contact ESD Protection

- ±6kV IEC 61000-4-2 Air-Gap ESD Protection

- ±1.2kV/500Ω Surge Protection on C/Q and V<sub>24</sub>

### General Description

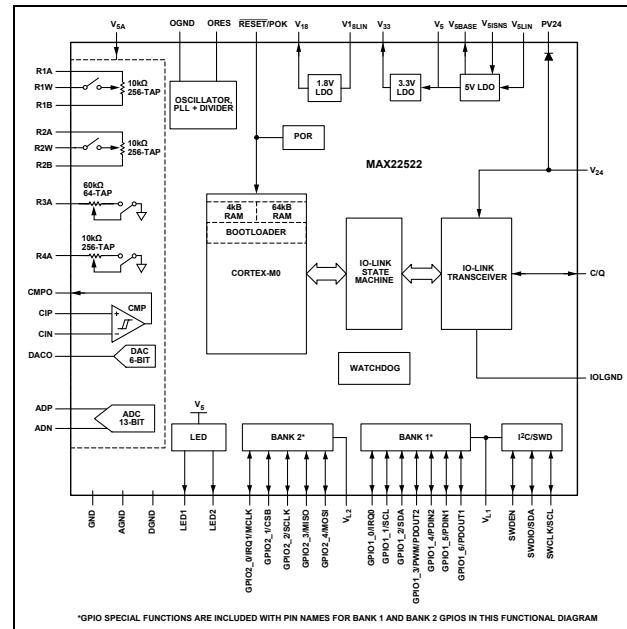

The MAX22522 is a mixed signal IO-Link device transceiver incorporating an ARM® Cortex-M0 with an IO-Link data link state machine. This state machine autonomously manages all time critical tasks for IO-Link communication at the COM1, COM2, and COM3 data rates. The integrated state machine manages all IO-Link M-sequence types, as well as full ISDU transfers.

The MAX22522 integrates programmable analog components including a 13-bit ADC, an integrated comparator, and four programmable resistors, which allow the MAX22522 to be used for signal generation and conditioning for end-of-line calibration for sensors and actuators.

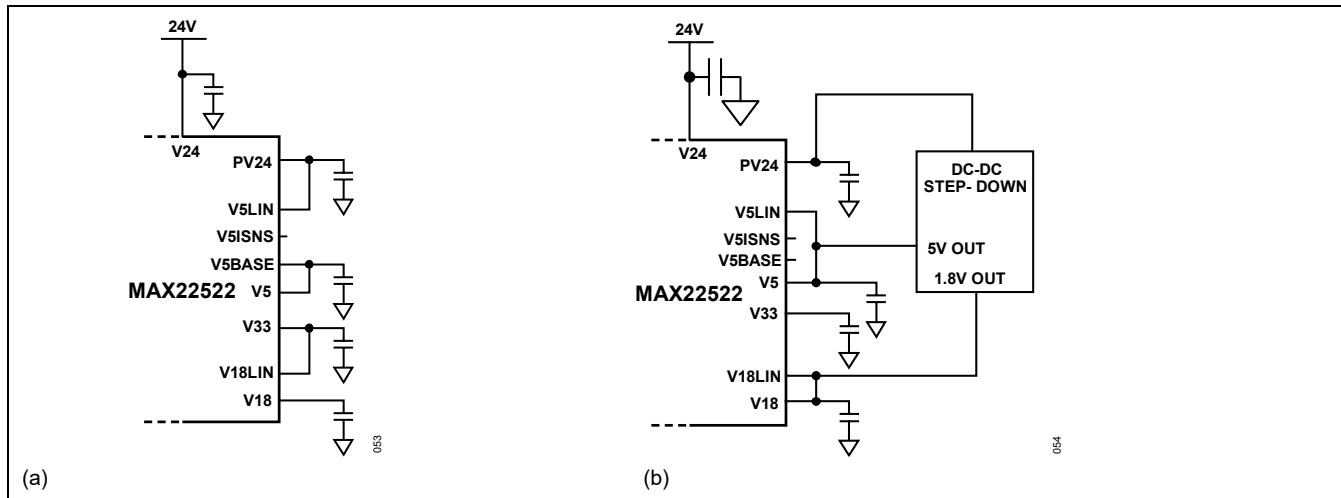

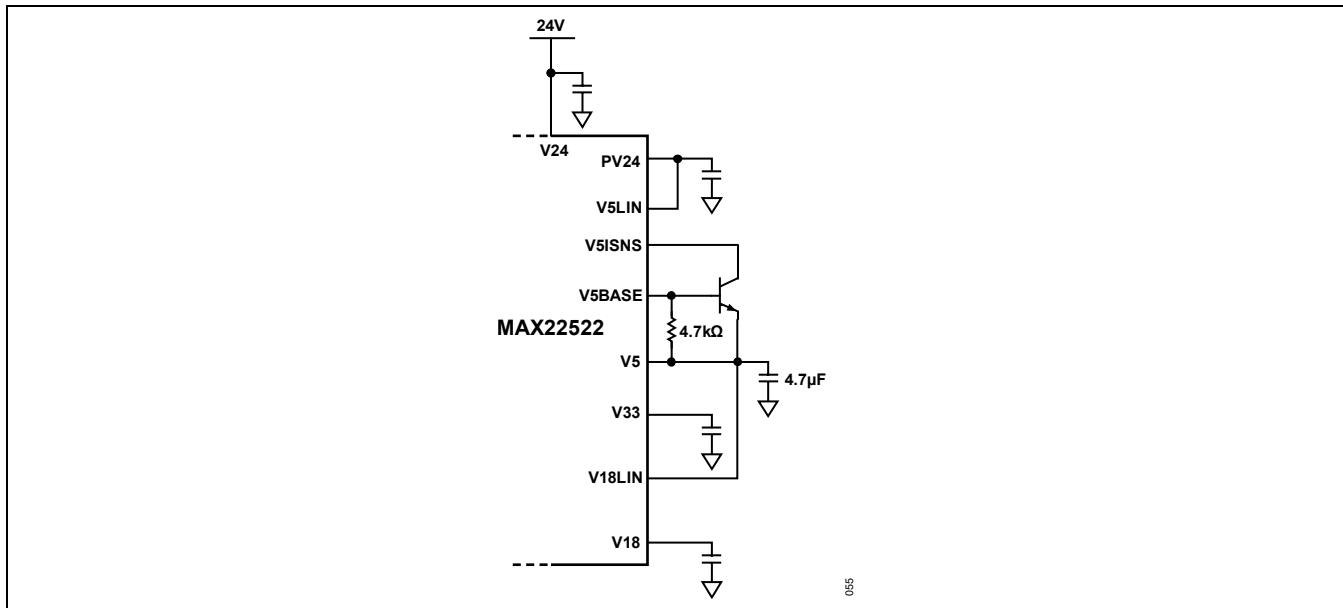

Low-noise 5V, 3.3V, and 1.8V linear regulators provide low-noise supplies for analog signal sensing. Optionally, an external NPN transistor may also be used to shunt regulator heat off-chip.

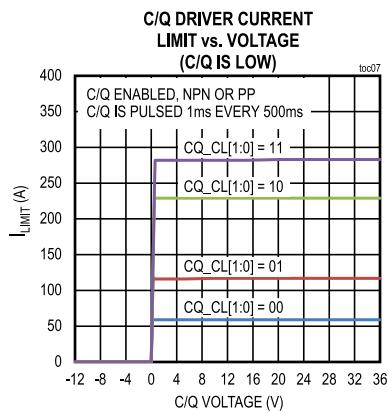

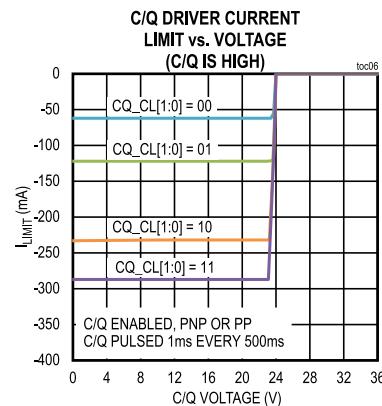

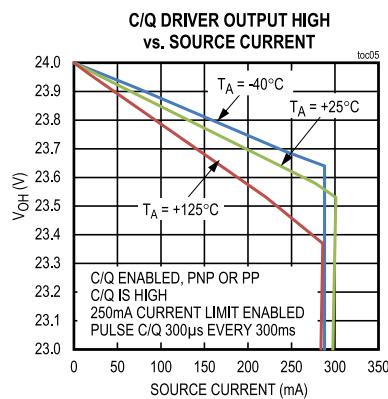

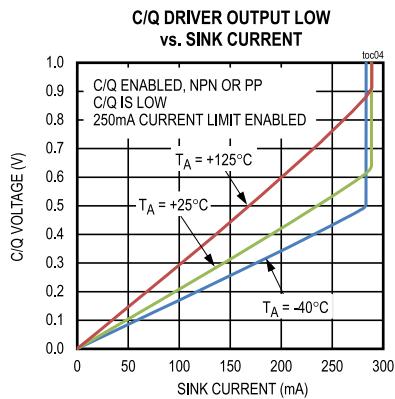

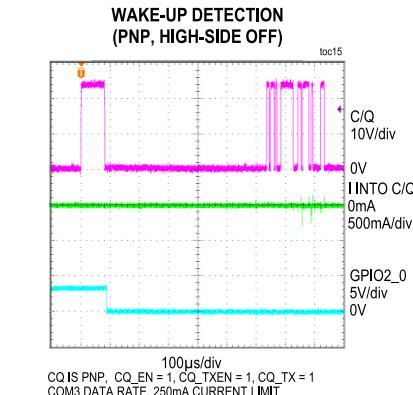

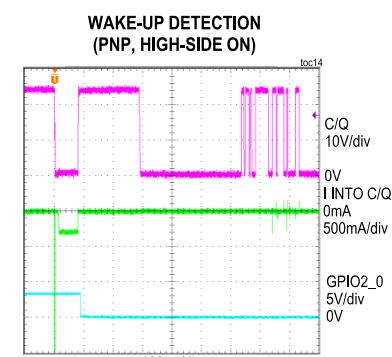

The 24V C/Q driver can be configured to operate in high-side (PNP), low-side (NPN), or push-pull (PP) modes. The C/Q current limit threshold is programmable from 50mA to 250mA.

An integrated comparator, a 6-bit DAC, a 13-bit ADC, and high-resolution variable resistors are included for signal conditioning for analog sensing circuitry.

The MAX22522 is available in a 60-bump WLP package (4.42mm × 2.64mm) and operates over the -40°C to +125°C temperature range.

### Simplified Functional Diagram

[Ordering Information](#) appears at end of data sheet.

---

**TABLE OF CONTENTS**

---

|                                                         |    |

|---------------------------------------------------------|----|

| Product Highlights .....                                | 1  |

| General Description .....                               | 1  |

| Simplified Functional Diagram .....                     | 1  |

| Absolute Maximum Ratings .....                          | 4  |

| Package Information .....                               | 4  |

| Electrical Characteristics .....                        | 5  |

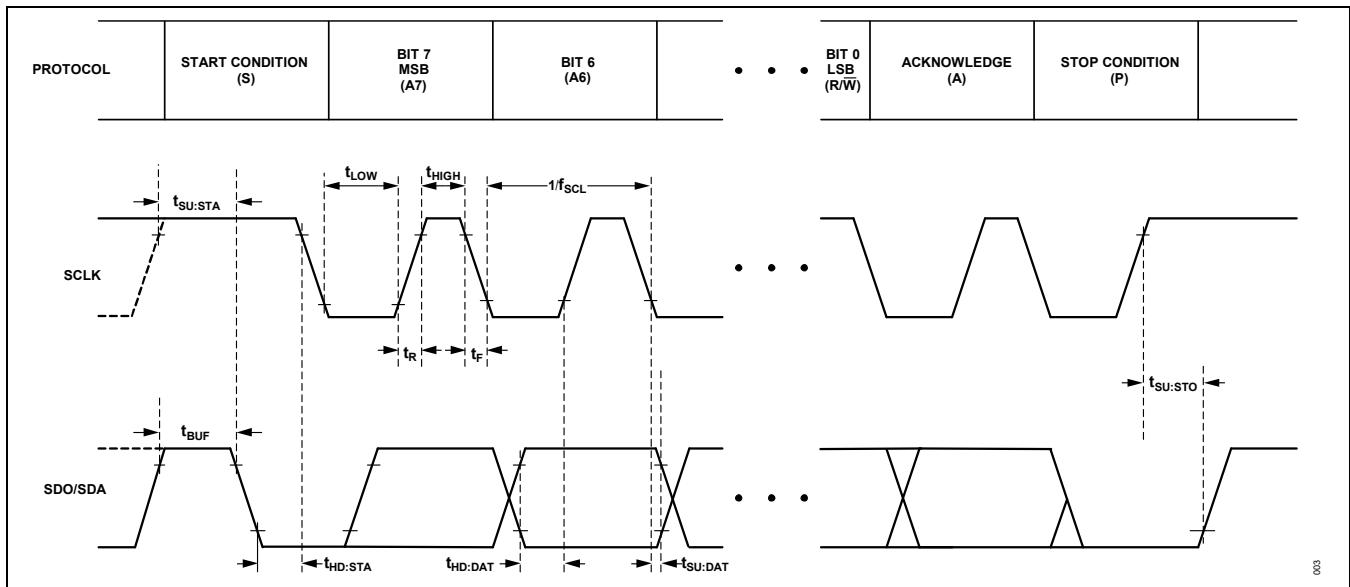

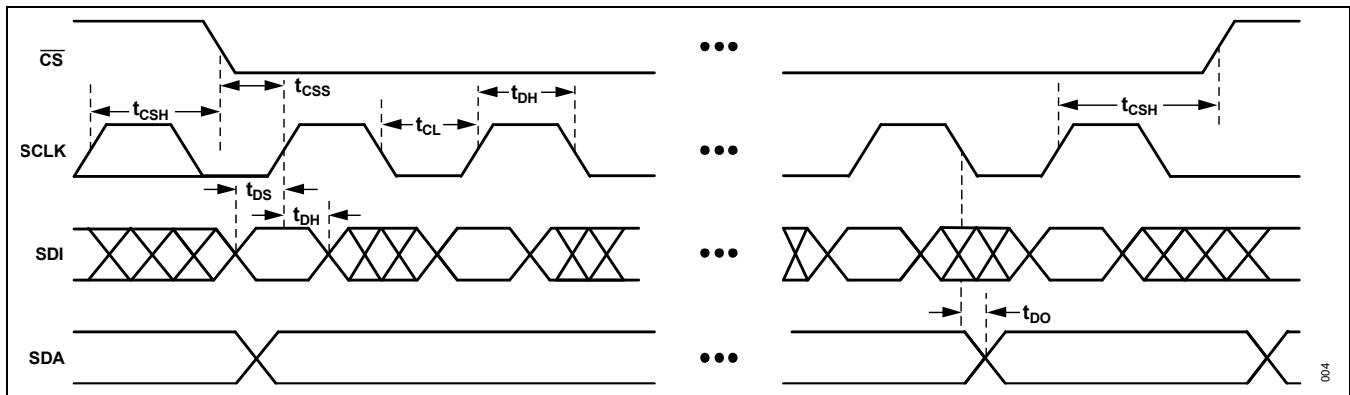

| Timing Diagrams .....                                   | 17 |

| Typical Operating Characteristics .....                 | 18 |

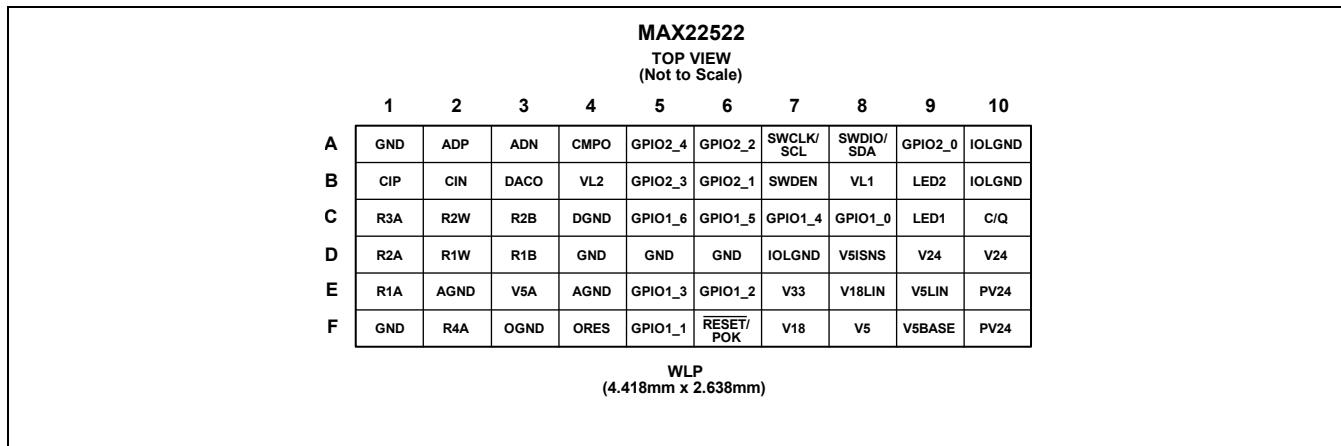

| Pin Configurations .....                                | 24 |

| Pin Descriptions .....                                  | 24 |

| Detailed Description .....                              | 27 |

| Power .....                                             | 27 |

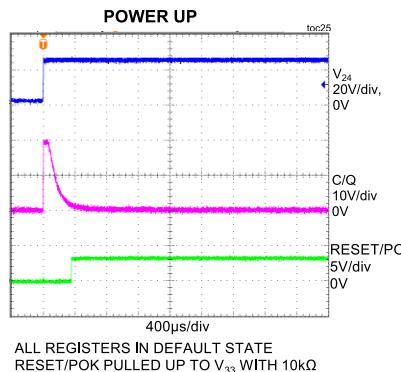

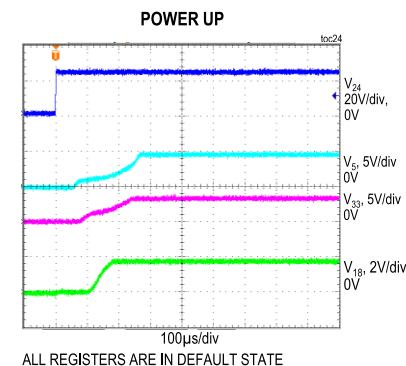

| Power-Up Sequencing .....                               | 27 |

| PV24 Protected Supply .....                             | 27 |

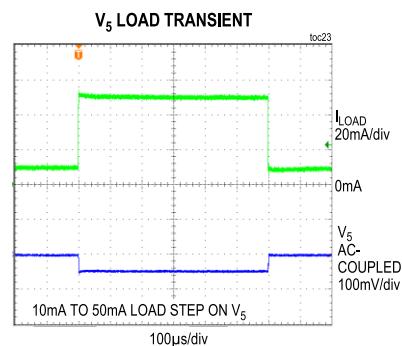

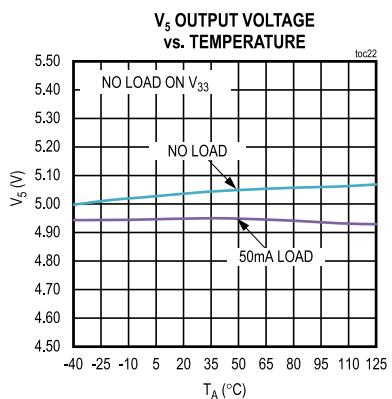

| V <sub>5</sub> Linear Regulator .....                   | 27 |

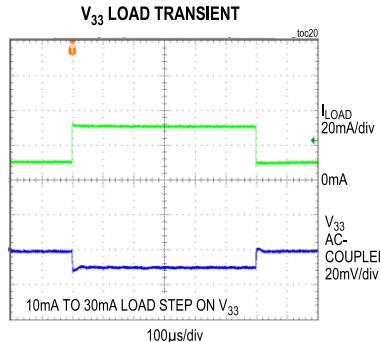

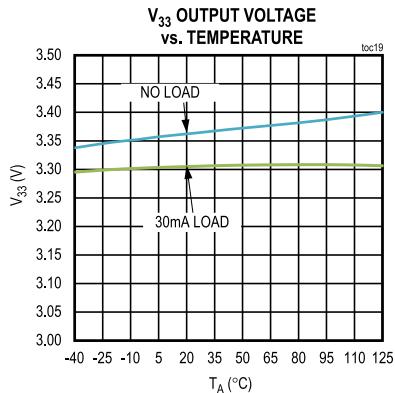

| V <sub>33</sub> Linear Regulator .....                  | 28 |

| V <sub>18</sub> Linear Regulator .....                  | 28 |

| 24V Interface (V <sub>24</sub> , C/Q, IOLGND) .....     | 28 |

| Variable Resistors (R1, R2) .....                       | 28 |

| Variable Resistors (R3, R4) .....                       | 28 |

| General-Purpose Inputs/Outputs (GPIO1_x, GPIO2_x) ..... | 29 |

| GPIO Alternate Functions .....                          | 29 |

| High Speed Comparator and DAC (CMP, DAC) .....          | 30 |

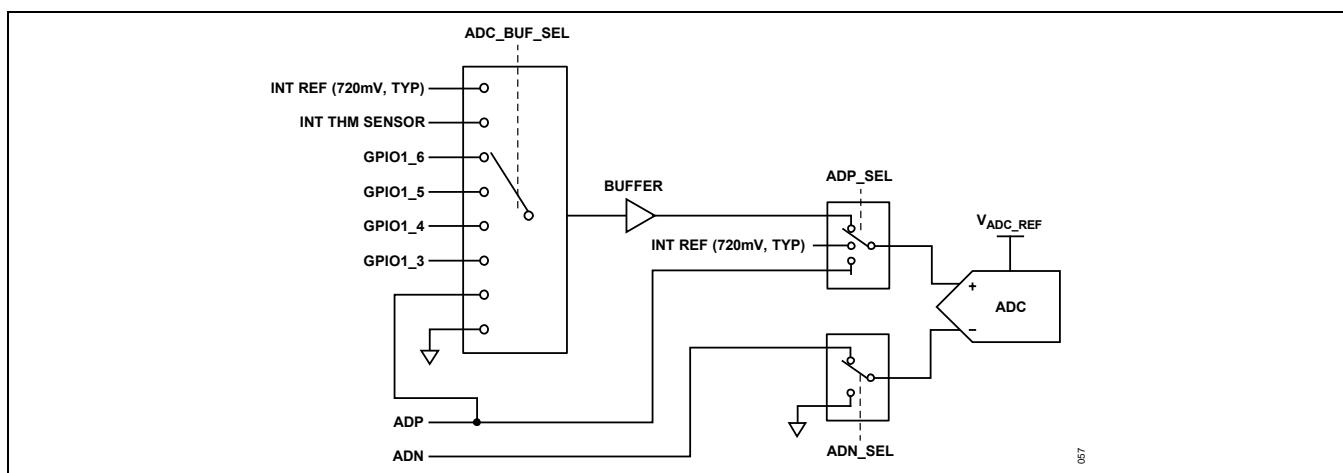

| Analog-to-Digital Converter (ADC) .....                 | 30 |

| Clock Control .....                                     | 31 |

| Timers and System Watchdog .....                        | 31 |

| SysTick Timer .....                                     | 31 |

| IO-Link Data Link Layer .....                           | 31 |

| SIO Mode .....                                          | 31 |

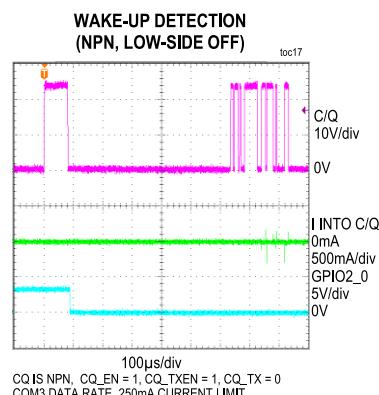

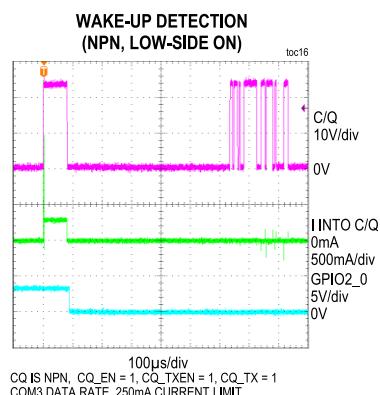

| Wake-Up and Establish COM .....                         | 31 |

| Process Data Transfers .....                            | 31 |

| Process Data Output (PDOut) .....                       | 31 |

| Process Data Input (PDIn) .....                         | 32 |

| ISDU Transmission .....                                 | 32 |

| LED1, LED2: Status and Diagnostic Indicators .....      | 32 |

| Applications Information .....                          | 33 |

| Power Dissipation and Thermal Considerations .....      | 33 |

---

|                            |    |

|----------------------------|----|

| EMC Protection .....       | 33 |

| Layout and Grounding ..... | 34 |

| Ordering Information ..... | 34 |

| Chip Information.....      | 34 |

| Revision History .....     | 35 |

## Absolute Maximum Ratings

|                                                                                                        |                                                |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------|

| (All voltages referenced to GND unless otherwise noted.).....                                          |                                                |

| V <sub>24</sub> (Continuous).....                                                                      | -36V to +36V                                   |

| V <sub>24</sub> (Peak, 100μs).....                                                                     | -52V to +60V                                   |

| PV <sub>24</sub> (Continuous).....                                                                     | -0.3V to +36V                                  |

| PV <sub>24</sub> (Peak, 100μs) MAX (-0.3V, V <sub>24</sub> - 52V) to MIN (+52V, V <sub>24</sub> + 52V) |                                                |

| V <sub>24</sub> to PV <sub>24</sub> .....                                                              | -48V to +48V                                   |

| C/Q (Continuous) MAX (-36V, V <sub>24</sub> - 36V) to MIN (+36V, V <sub>24</sub> + 36V)                |                                                |

| C/Q (Peak, 100μs) MAX (-52V, V <sub>24</sub> - 60V) to MIN (+52V, V <sub>24</sub> + 60V)               |                                                |

| GND, AGND, DGND, IOLGND .....                                                                          | -0.3V to +0.3V                                 |

| V <sub>5LIN</sub> (Continuous) .....                                                                   | MAX (-0.3V, V <sub>5BASE</sub> - 0.3V) to +36V |

| V <sub>5LIN</sub> (Peak, 100μs) .....                                                                  | MAX (-0.3V, V <sub>5BASE</sub> - 0.3V) to +52V |

| V <sub>5ISNS</sub> .....                                                                               | MAX (-0.3V, V <sub>5LIN</sub> - 2V) to +36V    |

| V <sub>5BASE</sub> .....                                                                               | -0.3V to MIN (+18V, V <sub>5LIN</sub> + 0.3V)  |

| V <sub>5</sub> , V <sub>5A</sub> .....                                                                 | -0.3V to +6V                                   |

| V <sub>33</sub> .....                                                                                  | -0.3V to (V <sub>5</sub> + 0.3V)               |

| V <sub>18LIN</sub> .....                                                                               | MAX (-0.3V, V <sub>18</sub> - 0.3V) to +6V     |

| V <sub>18</sub> .....                                                                                  | -0.3V to +2V                                   |

| V <sub>L1</sub> , V <sub>L2</sub> .....                                                                | -0.3V to +6V                                   |

|                                                                                                |                                   |

|------------------------------------------------------------------------------------------------|-----------------------------------|

| RESET/POK .....                                                                                | -0.3V to +6V                      |

| ORES .....                                                                                     | -0.3V to (V <sub>18</sub> + 0.3V) |

| R1A, R1B, R1W, R2A, R2B, R2W, R3A, R4A ( <a href="#">Note 1</a> ) ..                           | -0.3V to (V <sub>5A</sub> + 0.3V) |

| CMPO .....                                                                                     | -0.3V to (V <sub>5</sub> + 0.3V)  |

| CIP, CIN, DACY .....                                                                           | -0.3V to (V <sub>5A</sub> + 0.3V) |

| ADP, ADN .....                                                                                 | -0.3V to (V <sub>18</sub> + 0.3V) |

| LED1, LED2 .....                                                                               | -0.3V to +6V                      |

| GPIO1_x .....                                                                                  | -0.3V to (V <sub>L1</sub> + 0.3V) |

| GPIO2_x .....                                                                                  | -0.3V to (V <sub>L2</sub> + 0.3V) |

| SWDEN, SWDIO/SDA, SWCLK/SCL .....                                                              | -0.3V to (V <sub>L1</sub> + 0.3V) |

| Continuous Current into V <sub>24</sub> , C/Q, IOLGND .....                                    | ±0.5A                             |

| Continuous Current into Variable Resistor, Rx .....                                            | ±2.5mA                            |

| Continuous Current into Any Other Pin .....                                                    | ±50mA                             |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C, derates at 25.46mW/°C above +70°C) ..... | 2037mW                            |

| Operating Temperature Range .....                                                              | -40°C to +125°C                   |

| Maximum Junction Temperature .....                                                             | +150°C                            |

| Storage Temperature Range .....                                                                | -40°C to +150°C                   |

| Bump Reflow Temperature .....                                                                  | +260°C                            |

**Note 1:** Ensure that sink/source current does not exceed the maximum rating at any voltage.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Package Information

|                                                        |                                                                                                      |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Package Code                                           | W602B4+1                                                                                             |

| Outline Number                                         | <a href="#">21-100691</a>                                                                            |

| Land Pattern Number                                    | Refer to the <a href="#">Application Note 1891: Wafer-Level Packaging (WLP) and Its Applications</a> |

| <b>Thermal Resistance, 4-Layer Board:</b>              |                                                                                                      |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 39.27°C/W                                                                                            |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                                                                                                  |

For the latest package outline information and land patterns (footprints), go to [www.analog.com/en/resources/packaging-quality-symbols-footprints/package-index](http://www.analog.com/en/resources/packaging-quality-symbols-footprints/package-index). Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layer board. For detailed information on package thermal considerations, refer to [www.analog.com/en/resources/technical-articles/thermal-characterization-of-ic-packages](http://www.analog.com/en/resources/technical-articles/thermal-characterization-of-ic-packages).

## Electrical Characteristics

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ , GND = DGND = OGND = AGND = IOLGND =  $0V$ , and  $T_A = -40^\circ C$  to  $+125^\circ C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_x, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND.  $\overline{RESET}/POK$  pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^\circ C$  (See [Note 2](#)))

| PARAMETER                                                | SYMBOL              | CONDITIONS                                                                                                               | MIN                                                                                                  | TYP  | MAX   | UNITS   |

|----------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|-------|---------|

| <b>V<sub>24</sub> SUPPLY</b>                             |                     |                                                                                                                          |                                                                                                      |      |       |         |

| V <sub>24</sub> Supply Voltage                           | $V_{24}$            |                                                                                                                          | 7                                                                                                    | 36   |       | V       |

| V <sub>24</sub> Undervoltage Error Threshold             | $V_{24\_ERR\_R}$    | $V_{24}$ rising (See <a href="#">Note 3</a> , <a href="#">Note 4</a> )                                                   | 6.6                                                                                                  | 6.9  |       | V       |

| V <sub>24</sub> Undervoltage Error Threshold             | $V_{24\_ERR\_F}$    | $V_{24}$ falling (See <a href="#">Note 3</a> , <a href="#">Note 4</a> )                                                  | 6.1                                                                                                  | 6.5  |       | V       |

| V <sub>24</sub> Undervoltage Warning Threshold           | $V_{24\_WRN\_R}$    | $V_{24}$ rising ( <a href="#">Note 4</a> )                                                                               | 16                                                                                                   | 16.9 | 18    | V       |

|                                                          | $V_{24\_WRN\_F}$    | $V_{24}$ falling ( <a href="#">Note 4</a> )                                                                              | 15.5                                                                                                 | 16.5 | 17.5  |         |

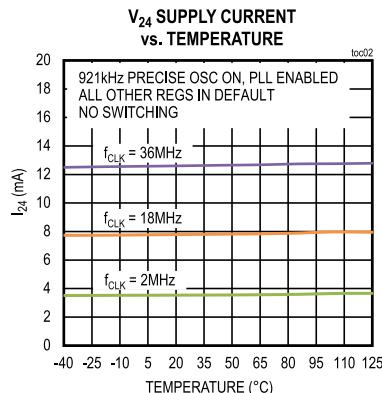

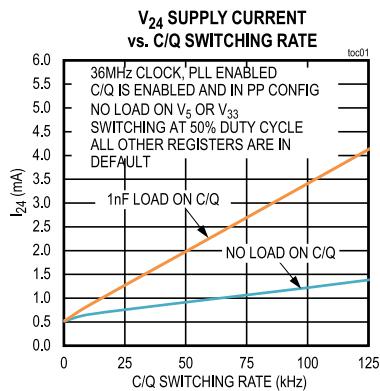

| V <sub>24</sub> Supply Current                           | $I_{24\_DIS}$       | No load on C/Q, $V_5$ , and $V_{18}$ powered externally, and the microcontroller is halted (See <a href="#">Note 5</a> ) | Registers in a default state, C/Q disabled, PLL off, and 921kHz precise oscillator off               | 0.03 | 0.11  | mA      |

|                                                          | $I_{24\_ACT\_H}$    | No load on C/Q, $V_5$ , and $V_{18}$ powered externally, and the microcontroller is halted (See <a href="#">Note 5</a> ) | Registers in a default state except: C/Q in push-pull and high, PLL on, 921kHz precise oscillator on | 0.3  | 0.437 | 0.7     |

|                                                          | $I_{24\_ACT\_L}$    | No load on C/Q, $V_5$ , and $V_{18}$ powered externally, and the microcontroller is halted (See <a href="#">Note 5</a> ) | Registers in a default state except: C/Q in push-pull and low, PLL on, 921kHz precise oscillator on  | 0.3  | 0.419 | 0.7     |

| V <sub>24</sub> Clamp Voltage                            | $V_{24\_CLAMP}$     | ( $V_{24} - GND$ ), $I_{LOAD} = 1mA$                                                                                     | 42                                                                                                   | 48.2 | 53    | V       |

| <b>LOGIC SUPPLY (V<sub>L1</sub>, V<sub>L2</sub>)</b>     |                     |                                                                                                                          |                                                                                                      |      |       |         |

| V <sub>L1</sub> Supply Voltage                           | $V_{L1}$            |                                                                                                                          | 2.5                                                                                                  | 5.5  |       | V       |

| V <sub>L2</sub> Supply Voltage                           | $V_{L2}$            | ( <a href="#">Note 6</a> )                                                                                               | 1.62                                                                                                 | 5.5  |       | V       |

| V <sub>L1</sub> Supply Current                           | $I_{L1}$            | All logic inputs are at GND or $V_{L1}$ , no load on any logic outputs                                                   |                                                                                                      | 60   |       | $\mu A$ |

| V <sub>L2</sub> Supply Current                           | $I_{L2}$            | All logic inputs are at GND or $V_{L2}$ , no load on any logic outputs                                                   |                                                                                                      | 70   |       | $\mu A$ |

| <b>5V SUPPLY (V<sub>5</sub>)</b>                         |                     |                                                                                                                          |                                                                                                      |      |       |         |

| V <sub>5</sub> Supply Voltage                            | $V_5$               | $V_5$ externally supplied, $V_{5LIN} = V_5$                                                                              | 4.5                                                                                                  | 5.5  |       | V       |

| V <sub>5</sub> Undervoltage Lockout Threshold            | $V_{5\_UVLO\_R}$    | $V_5$ rising (See <a href="#">Note 4</a> )                                                                               | 3.5                                                                                                  | 4.5  |       | V       |

|                                                          | $V_{5\_UVLO\_F}$    | $V_5$ falling (See <a href="#">Note 4</a> )                                                                              | 3.5                                                                                                  | 4.5  |       |         |

| V <sub>5</sub> Undervoltage Lockout Threshold Hysteresis | $V_{5\_UVLO\_HYST}$ |                                                                                                                          |                                                                                                      | 140  |       | $mV$    |

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ ,  $GND = DGND = OGND = AGND = IOLGND = 0V$ , and  $T_A = -40^\circ C$  to  $+125^\circ C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_X, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND. RESET/POK pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^\circ C$  (See [Note 2](#)))

| PARAMETER                                                 | SYMBOL                 | CONDITIONS                                                                                                                             |                                                                                                    | MIN  | TYP  | MAX | UNITS |

|-----------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|------|-----|-------|

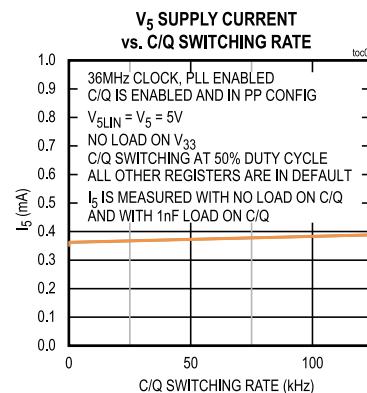

| V <sub>5</sub> Supply Current                             | I <sub>5_DIS</sub>     | No load on C/Q, V <sub>5</sub> , and V <sub>18</sub> powered externally, and the microcontroller halted (See <a href="#">Note 5</a> )  | Registers in default state, C/Q disabled, PLL off, and IO-Link oscillator off                      | 0.1  | 0.27 |     | mA    |

|                                                           | I <sub>5_ACT_H</sub>   | No load on C/Q, V <sub>5</sub> , and V <sub>18</sub> powered externally, and the microcontroller halted (See <a href="#">Note 5</a> )  | Registers in default state except: C/Q in push-pull and high, PLL on, 921kHz precise oscillator on | 0.25 | 0.57 |     |       |

|                                                           | I <sub>5_ACT_L</sub>   | No load on C/Q, V <sub>5</sub> , and V <sub>18</sub> powered externally, and the microcontroller halted (See <a href="#">Note 5</a> )  | Registers in default state except: C/Q in push-pull and low, PLL on, 921kHz precise oscillator on  | 0.25 | 0.57 |     |       |

| <b>1.8V SUPPLY (V<sub>18</sub>)</b>                       |                        |                                                                                                                                        |                                                                                                    |      |      |     |       |

| V <sub>18</sub> Supply Voltage                            | V <sub>18</sub>        | V <sub>18LIN</sub> = V <sub>18</sub> , V <sub>18</sub> externally supplied                                                             |                                                                                                    | 1.71 | 1.89 |     | V     |

| V <sub>18</sub> Undervoltage Lockout Threshold            | V <sub>18_UVLO_R</sub> | V <sub>18</sub> rising (See <a href="#">Note 4</a> )                                                                                   |                                                                                                    | 1.66 | 1.76 |     | V     |

|                                                           | V <sub>18_UVLO_F</sub> | V <sub>18</sub> falling (See <a href="#">Note 4</a> )                                                                                  |                                                                                                    | 1.62 | 1.72 |     |       |

| V <sub>18</sub> Undervoltage Lockout Threshold Hysteresis |                        |                                                                                                                                        |                                                                                                    | 35   |      |     | mV    |

| V <sub>18</sub> Supply Current                            | I <sub>18_SLEEP</sub>  | V <sub>5</sub> and V <sub>18</sub> powered externally, f <sub>HCLK</sub> = 18MHz, sleep mode                                           | PLL off                                                                                            | 0.9  |      |     | mA    |

|                                                           |                        |                                                                                                                                        | PLL on                                                                                             | 2.1  |      |     |       |

|                                                           | I <sub>18_DIS</sub>    | V <sub>5</sub> and V <sub>18</sub> powered externally, f <sub>HCLK</sub> = 18MHz, microcontroller halted (See <a href="#">Note 5</a> ) | Registers in a default state, PLL off, and 921kHz precise oscillator off                           | 2.8  | 4.6  |     |       |

|                                                           | I <sub>18_ACT</sub>    | V <sub>5</sub> and V <sub>18</sub> powered externally, f <sub>HCLK</sub> = 36MHz, microcontroller halted (See <a href="#">Note 5</a> ) | Registers in a default state, PLL on, and 921kHz precise oscillator on                             | 4.5  | 6.7  | 9   |       |

|                                                           |                        |                                                                                                                                        | PLL off                                                                                            | 5.4  |      |     |       |

| <b>V<sub>5A</sub> SUPPLY (V<sub>5A</sub>)</b>             |                        |                                                                                                                                        |                                                                                                    |      |      |     |       |

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ , GND = DGND = OGND = AGND = IOLGND =  $0V$ , and  $T_A = -40^\circ C$  to  $+125^\circ C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_X, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND. RESET/POK pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^\circ C$  (See [Note 2](#)))

| PARAMETER                                                                                                            | SYMBOL                 | CONDITIONS                                                                                               | MIN  | TYP  | MAX  | UNITS    |

|----------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|----------|

| $V_{5A}$ Supply Voltage                                                                                              | $V_{5A}$               |                                                                                                          | 4.5  | 5.5  |      | V        |

| $V_{5A}$ Supply Current                                                                                              | $I_{5A\_DIS}$          | Digipots, comparators, and DACs disabled                                                                 |      | 4.5  |      | $\mu A$  |

|                                                                                                                      | $I_{5A\_ACT}$          | Digipots, comparators, and DACs enabled, Digipots and DAC set at mid-code, comparators fast mode enabled |      | 60   |      |          |

| <b>ACTIVE DIODE (PV24)</b>                                                                                           |                        |                                                                                                          |      |      |      |          |

| Active Diode On-Resistance                                                                                           | $R_{ACT}$              | $I_{LOAD} = 10mA$                                                                                        |      | 3.1  | 7    | $\Omega$ |

| Active Diode Current Limit                                                                                           | $I_{ACTMAX}$           | $I_{LOSS} < 1\%$                                                                                         | 110  | 430  |      | mA       |

| <b>5V LINEAR REGULATOR (<math>V_5</math>, <math>V_{5LIN}</math>, <math>V_{5BASE}</math>, <math>V_{5ISNS}</math>)</b> |                        |                                                                                                          |      |      |      |          |

| $V_{5LIN}$ Input Supply Voltage                                                                                      | $V_{5LIN}$             |                                                                                                          | 6    | 36   |      | V        |

| $V_{5LIN}$ Supply Current                                                                                            | $I_{5LIN\_DIS}$        | $V_5 = V_{5LIN}$ , $V_5$ regulator is disabled                                                           | 10   | 60   |      | $\mu A$  |

|                                                                                                                      | $I_{5LIN\_ACT}$        | $V_5 = 36V$ , no load                                                                                    | 50   | 350  |      |          |

| $V_5$ Output Voltage                                                                                                 | $V_{5\_OUT}$           | $7V \leq V_{5LIN} \leq 36V$                                                                              | 4.8  | 5.2  |      | V        |

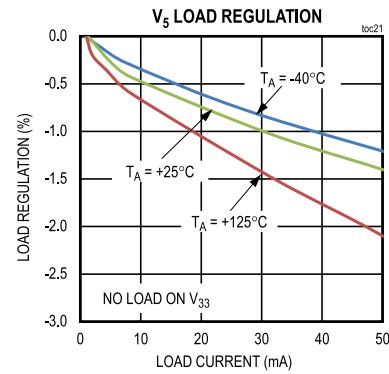

| $V_5$ Load Regulation                                                                                                | $\Delta V_{5\_LDR}$    | $V_{5LIN} = 24V$ , $1mA \leq I_{LOAD} \leq 50mA$                                                         | 2    | 5    |      | %        |

| $V_5$ Line Regulation                                                                                                | $\Delta V_{5\_LNR}$    | $6V \leq V_{5LIN} \leq 36V$ , $I_{LOAD} = 1mA$                                                           | -0.2 | +0.2 |      | mV/V     |

| $V_5$ Current limit                                                                                                  | $I_{5\_SHORT}$         |                                                                                                          | 52   | 250  |      | mA       |

| $V_{5LIN}$ to $V_5$ Enable Voltage Threshold                                                                         | $V_{THR\_V5LIN\_R}$    | $(V_{5LIN} - V_5)$ rising                                                                                | 0.2  | 0.43 | 0.7  | V        |

|                                                                                                                      | $V_{THR\_V5LIN\_F}$    | $(V_{5LIN} - V_5)$ falling                                                                               | 0.17 | 0.41 | 0.67 |          |

| $V_{5LIN}$ to $V_5$ Enable Voltage Threshold Hysteresis                                                              | $V_{THR\_V5LIN\_HYST}$ |                                                                                                          |      | 20   |      | mV       |

| $V_{5LIN}$ to $V_5$ Enable Voltage Threshold                                                                         | $V_{THR\_V5LIN\_F}$    | $(V_{5LIN} - V_5)$ falling                                                                               | 2.2  |      |      | $\mu F$  |

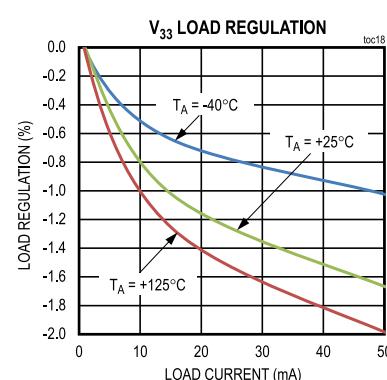

| <b>3.3V LINEAR REGULATOR (<math>V_{33}</math>)</b>                                                                   |                        |                                                                                                          |      |      |      |          |

| $V_{33}$ Output Voltage                                                                                              | $V_{33}$               |                                                                                                          | 3.2  | 3.45 |      | V        |

| $V_{33}$ Load Regulation                                                                                             | $\Delta V_{33\_LDR}$   | $V_5 = 5V$ , $1mA \leq I_{LOAD} \leq 50mA$                                                               | 0    | 1.0  | 5    | %        |

| $V_{33}$ Line Regulation                                                                                             | $\Delta V_{33\_LNR}$   | $4.5V \leq V_5 \leq 5.5V$ , $I_{LOAD} = 1mA$                                                             | -1   | +1   |      | mV/V     |

| $V_{33}$ Current Limit                                                                                               | $I_{33\_SHORT}$        |                                                                                                          | 68   | 208  |      | mA       |

| $V_{33}$ Load Capacitance                                                                                            | $C_{33}$               | Required capacitance for stability, $\pm 20\%$ tolerance allowed                                         | 2.2  |      |      | $\mu F$  |

| <b>1.8V LINEAR REGULATOR (<math>V_{18}</math>)</b>                                                                   |                        |                                                                                                          |      |      |      |          |

| $V_{18LIN}$ Input Supply Voltage                                                                                     | $V_{18LIN}$            |                                                                                                          | 2.7  | 5.5  |      | V        |

| $V_{18}$ Output Voltage                                                                                              | $V_{18\_OUT}$          | $2.7V \leq V_{18LIN} \leq 5.5V$                                                                          | 1.74 | 1.86 |      | V        |

| $V_{18}$ Load Regulation                                                                                             | $\Delta V_{18\_LDR}$   | $V_{18LIN} = 5V$ , $1mA \leq I_{LOAD} \leq 50mA$                                                         | 1    | 4    |      | %        |

| $V_{18}$ Line Regulation                                                                                             | $\Delta V_{18\_LNR}$   | $2.7V \leq V_{18LIN} \leq 5.5V$ , $I_{LOAD} = 1mA$                                                       | -0.6 | +0.6 |      | mV/V     |

| $V_{18}$ Current Limit                                                                                               | $I_{V18\_SHORT}$       |                                                                                                          | 68   | 208  |      | mA       |

| $V_{18LIN}$ to $V_{18}$ Enable Voltage Threshold                                                                     | $V_{THR\_V18LIN\_R}$   | $(V_{18LIN} - V_{18})$ rising                                                                            | 0.15 | 0.7  |      | V        |

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ , GND = DGND = OGND = AGND = IOLGND =  $0V$ , and  $T_A = -40^\circ C$  to  $+125^\circ C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_X, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND. RESET/POK pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^\circ C$  (See [Note 2](#)))

| PARAMETER                                    | SYMBOL            | CONDITIONS                                                                               | MIN                                     | TYP    | MAX    | UNITS     |

|----------------------------------------------|-------------------|------------------------------------------------------------------------------------------|-----------------------------------------|--------|--------|-----------|

| <b>18MHz RAW OSCILLATOR</b>                  |                   |                                                                                          |                                         |        |        |           |

| Raw Oscillator Frequency                     | $f_{CLK\_INT}$    | (See <a href="#">Note 7</a> )                                                            | 17.51                                   | 18.432 | 19.35  | MHz       |

| <b>921kHz PRECISION REFERENCE OSCILLATOR</b> |                   |                                                                                          |                                         |        |        |           |

| Reference Oscillator Supply Current          | $I_{POSC\_REF}$   |                                                                                          | 230                                     | 550    |        | $\mu A$   |

| Internal Reference Oscillator Frequency      | $f_{POSC\_REF}$   | $10k\Omega \pm 0.1\%$ resistance between ORES and OGND                                   | 912.5                                   | 921.6  | 931.0  | kHz       |

| Internal Reference Oscillator Precision      | $PRE_{POSC\_REF}$ | $10k\Omega \pm 0.1\%$ resistance between ORES and OGND                                   | -1.00                                   |        | +1.00  | %         |

| External Oscillator Required Resistance      | $R_{ORES}$        | $\pm 0.1\%$ tolerance                                                                    |                                         | 10     |        | $k\Omega$ |

| <b>PHASE-LOCKED LOOP (PLL)</b>               |                   |                                                                                          |                                         |        |        |           |

| PLL Supply Current                           | $I_{PLL}$         | $PLL_{MULT} = 80$ , PLL current sourced from $V_{18}$                                    | 0.8                                     | 1.6    |        | mA        |

| PLL Multiplying factor                       | $PLL_{MULT}$      |                                                                                          | 80                                      |        |        |           |

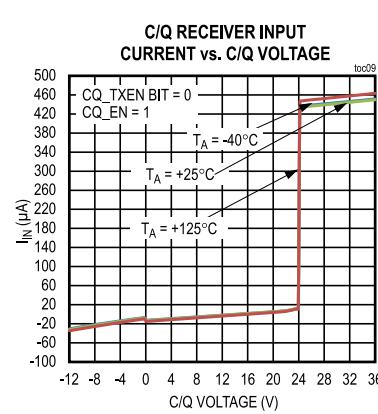

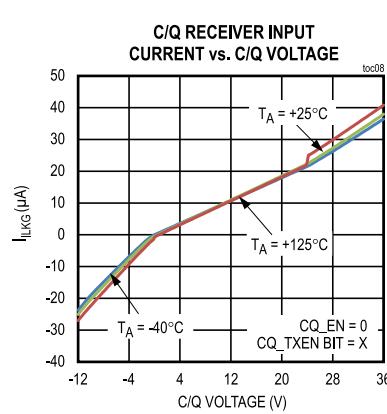

| <b>C/Q DRIVER</b>                            |                   |                                                                                          |                                         |        |        |           |

| C/Q Driver High-Side On-Resistance           | $R_{CQOH}$        | High-side enabled, $CQ\_CL = 11$ , $I_{LOAD} = 150mA$ (See <a href="#">Note 8</a> )      | 0.97                                    | 2      |        | $\Omega$  |

| C/Q Driver Low-Side On-Resistance            | $R_{CQOL}$        | Low-side enabled, $CQ\_CL = 11$ , $I_{SINK} = 150mA$ (See <a href="#">Note 8</a> )       | 1.7                                     | 3.4    |        | $\Omega$  |

| C/Q Driver Current Limit                     | $I_{CQ\_CL}$      | $V_{CQ} = (V_{24} - 3V)$ or $3V$                                                         | $CQ\_CL[1:0] = 00$                      | 53     | 60     | 65        |

|                                              |                   |                                                                                          | $CQ\_CL[1:0] = 01$                      | 106    | 120    | 130       |

|                                              |                   |                                                                                          | $CQ\_CL[1:0] = 10$                      | 209    | 240    | 255       |

|                                              |                   |                                                                                          | $CQ\_CL[1:0] = 11$                      | 259    | 287    | 317       |

| C/Q Driver Short Circuit Protection          | $I_{CQ\_FAULT}$   | Relative to the typical programmed current limit                                         |                                         | 25     |        | %         |

| C/Q Reverse Current                          | $I_{REV\_CQ\_H}$  | $V_{24} = 24V$ , C/Q enabled, and high impedance or pull-up enabled                      | $V_{CQ} = V_{24} + 5V$                  | 0.25   | 0.7    | mA        |

|                                              | $I_{REV\_CQ\_L}$  | $V_{24} = 24V$ , C/Q enabled, and high impedance or pull-down enabled                    | $V_{CQ} = -5V$                          | -0.025 | -0.005 |           |

| C/Q Input Current (High Impedance)           | $I_{CQ\_HZ}$      | $V_{24} = 24V$ , C/Q enabled, push-pull, high impedance, no pull-up or pull-down enabled | $0.1V \leq V_{CQ} \leq (V_{24} - 0.1V)$ | -19    | +19    | $\mu A$   |

| C/Q Leakage Current                          | $I_{CQ\_LKG}$     | $V_{24} = 24V$ , C/Q disabled, no pull-up or pull-down enabled                           | $(V_{24} - 36V) \leq V_{CQ} \leq 36V$   | -44    | +55    | $\mu A$   |

| C/Q Clamp Voltage                            | $V_{CQ\_CLAMP}$   | $V_{24} - V_{CQ}$ , $I_{LOAD} = -1mA$                                                    |                                         | 42     | 48.2   | 53        |

|                                              |                   | $V_{CQ} - GND$ , $I_{LOAD} = 1mA$                                                        |                                         | 42     | 48.2   | 53        |

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ , GND = DGND = OGND = AGND = IOLGND =  $0V$ , and  $T_A = -40^\circ C$  to  $+125^\circ C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_X, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND. RESET/POK pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^\circ C$  (See [Note 2](#)))

| PARAMETER                      | SYMBOL          | CONDITIONS                                                 | MIN                      | TYP   | MAX   | UNITS      |

|--------------------------------|-----------------|------------------------------------------------------------|--------------------------|-------|-------|------------|

| C/Q Rise Time                  | $t_{CQ\_RISE}$  | Push-pull or PNP mode, $V_{24} = 30V$ , $CQ\_CL[1:0] = 11$ | CQ_SLEW[1:0] = 00        | 0.11  | 0.23  | $\mu s$    |

|                                |                 |                                                            | CQ_SLEW[1:0] = 01        | 0.24  | 0.48  |            |

|                                |                 |                                                            | CQ_SLEW[1:0] = 10        | 0.36  | 0.75  |            |

|                                |                 |                                                            | CQ_SLEW[1:0] = 11        | 2.5   | 6.3   |            |

| C/Q Fall Time                  | $t_{CQ\_FALL}$  | Push-pull or NPN mode, $V_{24} = 30V$ , $CQ\_CL[1:0] = 11$ | CQ_SLEW[1:0] = 00        | 0.13  | 0.27  | $\mu s$    |

|                                |                 |                                                            | CQ_SLEW[1:0] = 01        | 0.26  | 0.52  |            |

|                                |                 |                                                            | CQ_SLEW[1:0] = 10        | 0.38  | 0.79  |            |

|                                |                 |                                                            | CQ_SLEW[1:0] = 11        | 1.8   | 5     |            |

| C/Q Driver Propagation Delay   | $t_{CQ\_PLH}$   | Push-pull, $V_{24} = 30V$ , $CQ\_CL[1:0] = 11$             | CQ_SLEW[1:0] = 00        | 0.15  | 0.70  | $\mu s$    |

|                                | $t_{CQ\_PHL}$   | Push-pull, $V_{24} = 30V$ , $CQ\_CL[1:0] = 11$             | CQ_SLEW[1:0] = 00        | 0.15  | 0.90  |            |

| C/Q Skew                       | $t_{CQ\_SKEW}$  | Push-pull, $V_{24} = 30V$ , $CQ\_CL[1:0] = 11$             | CQ_SLEW[1:0] = 00        | -0.50 | +0.50 | $\mu s$    |

| <b>C/Q PULL-UP/PULL-DOWN</b>   |                 |                                                            |                          |       |       |            |

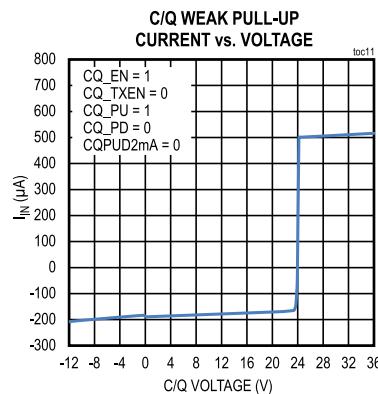

| C/Q Weak Pull-Up               | $I_{CQPUW}$     | C/Q disabled, weak pull-up enabled                         | $V_{CQ} = 5V$            | -200  | -130  | $\mu A$    |

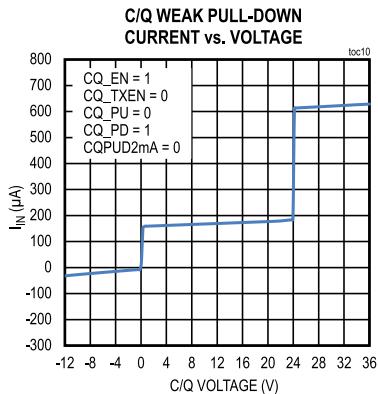

| C/Q Weak Pull-Down             | $I_{CQPDW}$     | C/Q disabled, weak pull-down enabled                       | $V_{CQ} = (V_{24} - 5V)$ | +150  | +200  | $\mu A$    |

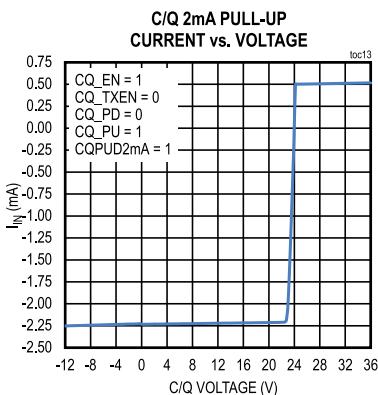

| C/Q 2mA Pull-Up                | $I_{CQPU2}$     | C/Q disabled, 2mA pull-up enabled                          | $V_{CQ} = 5V$            | -2.4  | -1.9  | $mA$       |

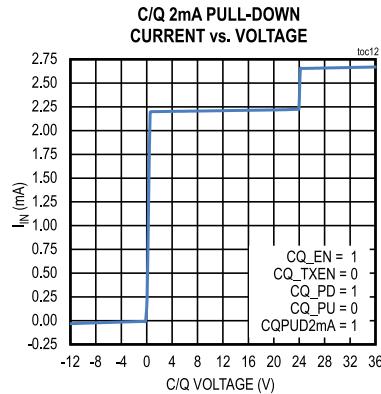

| C/Q 2mA Pull-Down              | $I_{CQPD2}$     | C/Q disabled, 2mA pull-down enabled                        | $V_{CQ} = (V_{24} - 5V)$ | 1.9   | 2.4   | $mA$       |

| <b>C/Q RECEIVER</b>            |                 |                                                            |                          |       |       |            |

| C/Q Input Voltage Range        | $V_{CQ\_IN}$    | For valid C/Q reception                                    | $V_{24} - 36V$           | 36    |       | V          |

| C/Q Input Threshold High       | $V_{CQ\_TH}$    | $V_{24} \geq 18V$                                          | 11.3                     | 12.2  |       | V          |

|                                |                 | $V_{24} < 18V$                                             | 62                       | 68    |       | $\%V_{24}$ |

| C/Q Input Threshold Low        | $V_{CQ\_TL}$    | $V_{24} \geq 18V$                                          | 9.4                      | 10.3  |       | V          |

|                                |                 | $V_{24} < 18V$                                             | 52                       | 58    |       | $\%V_{24}$ |

| C/Q Input Capacitance          | $C_{IN\_CQ}$    |                                                            |                          | 72    |       | $pF$       |

| C/Q Receiver Propagation Delay | $t_{CQIN\_PLH}$ | $RX\_FILTER = 0$                                           | 0.16                     | 0.58  |       | $\mu s$    |

|                                |                 | $RX\_FILTER = 1$                                           | 0.5                      | 1.8   |       |            |

|                                | $t_{CQIN\_PHL}$ | $RX\_FILTER = 0$                                           | 0.21                     | 0.66  |       |            |

|                                |                 | $RX\_FILTER = 1$                                           | 0.5                      | 1.8   |       |            |

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ , GND = DGND = OGND = AGND = IOLGND =  $0V$ , and  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_X, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND. RESET/POK pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^{\circ}C$  (See [Note 2](#)))

| PARAMETER                                                                                                                  | SYMBOL                              | CONDITIONS                                               | MIN                              | TYP             | MAX             | UNITS            |   |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------|----------------------------------|-----------------|-----------------|------------------|---|

| C/Q Receiver Skew                                                                                                          | tCQIN_SKew                          | RX_FILTER = 0                                            | -0.3                             | +0.3            | +1              | μs               |   |

|                                                                                                                            |                                     | RX_FILTER = 1                                            | -1                               | +1              | +1              |                  |   |

| <b>ANALOG-TO-DIGITAL CONVERTER (ADC)</b>                                                                                   |                                     |                                                          |                                  |                 |                 |                  |   |

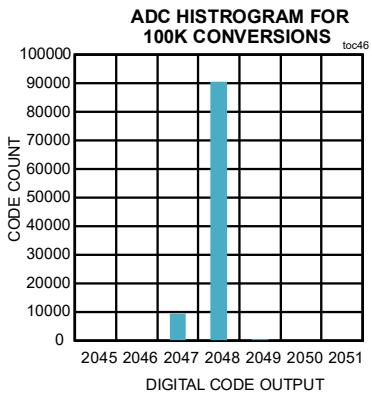

| ADC Resolution                                                                                                             | N <sub>BIT_ADC</sub>                |                                                          |                                  | 12 + sign       | bit             |                  |   |

| ADC Input Voltage Range                                                                                                    | V <sub>ADC</sub>                    | (V <sub>ADP</sub> – V <sub>ADN</sub> )                   | -1.27                            | +1.27           | +1.27           | V                |   |

|                                                                                                                            |                                     | V <sub>ADP</sub> , V <sub>ADN</sub> to ground            | 0                                | V <sub>18</sub> | V <sub>18</sub> |                  |   |

| ADC Internal Reference                                                                                                     | V <sub>ADC_REF</sub>                |                                                          |                                  | 1.235           | 1.25            | 1.27             | V |

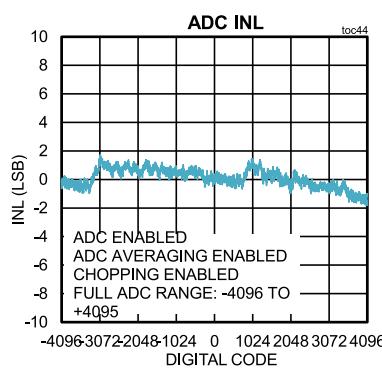

| ADC INL                                                                                                                    | INL <sub>ADC</sub>                  | f <sub>CONV</sub> = 500ksps                              | -10                              | +10             | +10             | LSB              |   |

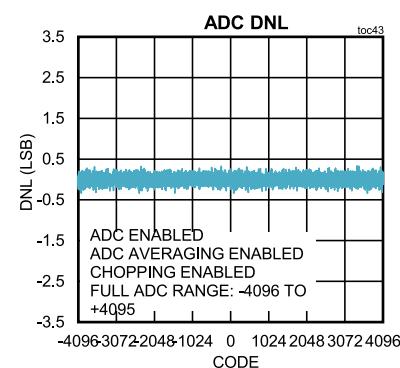

| ADC DNL                                                                                                                    | DNL <sub>ADC</sub>                  | f <sub>CONV</sub> = 500ksps                              | -3.5                             | +3.5            | +3.5            | LSB              |   |

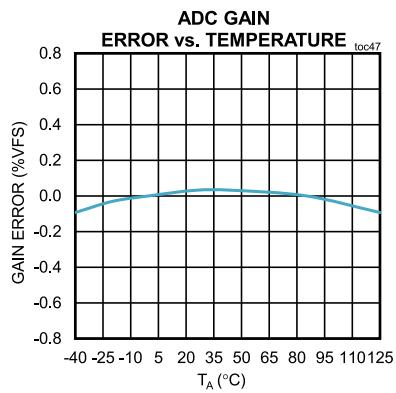

| ADC Gain Error                                                                                                             |                                     | V <sub>FS</sub> = 2.5V                                   | -0.8                             | +0.8            | +0.8            | %V <sub>FS</sub> |   |

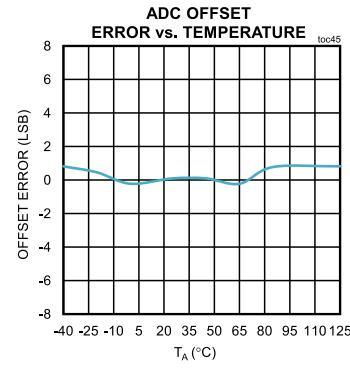

| ADC Offset Error                                                                                                           |                                     | ADC output with V <sub>ADP</sub> = V <sub>ADN</sub> = 0V | -8                               | +8              | +8              | LSB              |   |

| Conversion Time                                                                                                            | t <sub>ADC</sub>                    | ADC clock is HCLK                                        | 33                               |                 | Clock cycles    |                  |   |

| ADP, ADN Input Leakage                                                                                                     | I <sub>ADP</sub> , I <sub>ADN</sub> | V <sub>ADP</sub> , ADN = 1.8V                            | -1                               | +1              | +1              | μA               |   |

| <b>ADC INPUT MUX AND BUFFER</b>                                                                                            |                                     |                                                          |                                  |                 |                 |                  |   |

| ADC Buffer Input Range                                                                                                     | V <sub>BUFIN</sub>                  | GPIO1_3 – GPIO1_6, when configured as ADC inputs         | 0                                | V <sub>5A</sub> | V <sub>5A</sub> | V                |   |

| ADC Buffer Output Range                                                                                                    | V <sub>BUFOUT</sub>                 |                                                          |                                  | 0.01            | 1.4             | V                |   |

| ADC Buffer Offset                                                                                                          | V <sub>BUF_OS</sub>                 | Buffer input = 0.01V to 1.5V                             | -4                               | +4              | +4              | mV               |   |

| ADC -3dB Buffer Bandwidth                                                                                                  | V <sub>BUF_BW</sub>                 |                                                          |                                  | 1.5             |                 | MHz              |   |

| ADC Buffer Internal Voltage Reference                                                                                      | V <sub>BUF_REF</sub>                |                                                          |                                  | 712             | 725             | mV               |   |

| <b>ANALOG COMPARATORS AND DIGITAL-TO-ANALOG CONVERTERs (DACS) (CIP, CIN, CMPO, DACY) (CMP_IN_HIGH = 1, CMP_IN_LOW = 1)</b> |                                     |                                                          |                                  |                 |                 |                  |   |

| Comparator Common Mode Range                                                                                               | V <sub>CM_CMP</sub>                 |                                                          |                                  | 0               | V <sub>5A</sub> | V                |   |

| Comparator Offset                                                                                                          | V <sub>OS_CMP</sub>                 | CIP_rising                                               | Input = 0V                       | -20             | 0               | +15              |   |

|                                                                                                                            |                                     |                                                          | Input = V <sub>5A</sub>          | -15             | 0               | +15              |   |

|                                                                                                                            |                                     |                                                          | Input = V <sub>5A</sub> / 2      | -12             | 0               | +12              |   |

| Comparator Hysteresis                                                                                                      | V <sub>OS_CMP_HYST</sub>            | Input = 0V to V <sub>5A</sub>                            | 25                               |                 | mV              |                  |   |

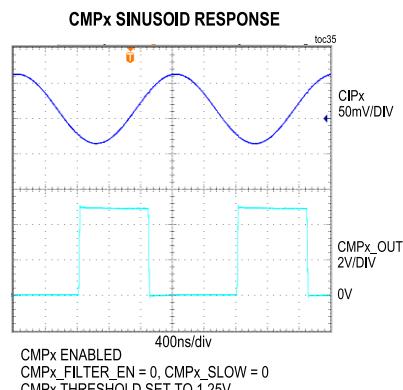

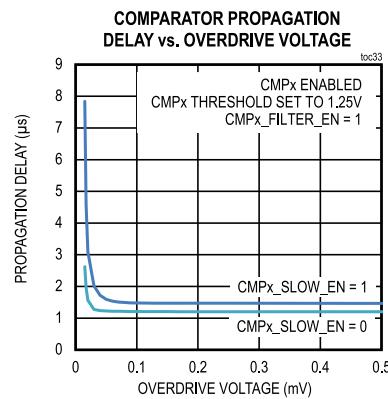

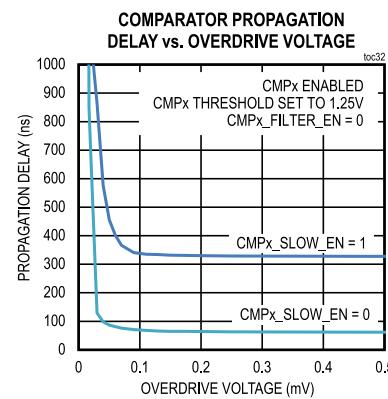

| Comparator Response Time                                                                                                   | t <sub>CMP</sub>                    | CIP_Threshold = 2.5V, CIP_from 2.4V to 2.6V              | CMP_FILT_EN = 0, CMP_SLOW_EN = 0 | 30              | 120             | ns               |   |

|                                                                                                                            |                                     |                                                          | CMP_FILT_EN = 0, CMP_SLOW_EN = 1 | 120             | 810             |                  |   |

|                                                                                                                            |                                     |                                                          | CMP_FILT_EN = 1, CMP_SLOW_EN = 0 | 0.75            | 1.65            | μs               |   |

|                                                                                                                            |                                     |                                                          | CMP_FILT_EN = 1, CMP_SLOW_EN = 1 | 0.9             | 2.2             |                  |   |

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ , GND = DGND = OGND = AGND = IOLGND =  $0V$ , and  $T_A = -40^\circ C$  to  $+125^\circ C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_X, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND. RESET/POK pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^\circ C$  (See [Note 2](#)))

| PARAMETER                                                               | SYMBOL                         | CONDITIONS                                                                                                                                           | MIN                                                           | TYP      | MAX      | UNITS      |

|-------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|----------|------------|

| Comparator Input Leakage                                                | $I_{CMP\_LKG}$                 | $V_{CIP}, C_{IN} = 0V$ to $5.5V$                                                                                                                     | -1                                                            | +1       |          | $\mu A$    |

| Comparator Output High                                                  | $V_{CMPO\_H}$                  | $I_{LOAD} = 5mA$                                                                                                                                     | $V_{5A} - 0.15$                                               | $V_{5A}$ |          | V          |

| Comparator Output Low                                                   | $V_{CMPO\_L}$                  | $I_{LOAD} = -5mA$                                                                                                                                    |                                                               | 0.1      |          | V          |

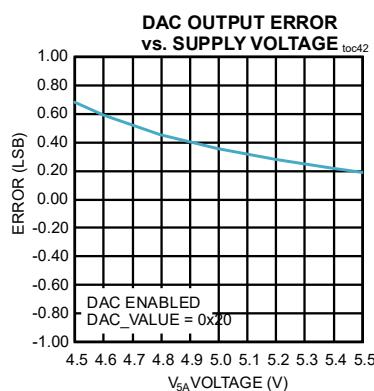

| DAC Full Scale                                                          | $V_{DAC\_}$                    |                                                                                                                                                      | 100                                                           |          |          | $\%V_{5A}$ |

| DAC Resolution                                                          | $N_{DAC}$                      |                                                                                                                                                      | 6                                                             |          |          | BIT        |

| DAC INL                                                                 | $INL_{DAC}$                    |                                                                                                                                                      | -0.35                                                         | +0.35    |          | LSB        |

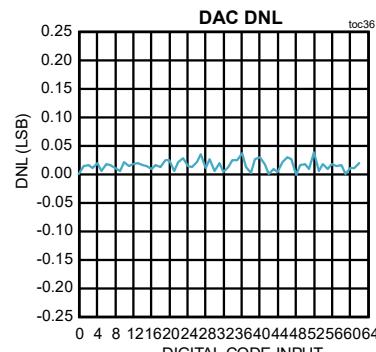

| DAC DNL                                                                 |                                |                                                                                                                                                      | -0.2                                                          | +0.2     |          | LSB        |

| DAC Monotonicity                                                        |                                | Guaranteed by DNL test                                                                                                                               |                                                               |          |          |            |

| DAC Output Resistance                                                   | $R_{DAC}$                      |                                                                                                                                                      | 273                                                           |          |          | $k\Omega$  |

| <b>VARIABLE RESISTORS (R1, R2, R3, R4) (See <a href="#">Note 9</a>)</b> |                                |                                                                                                                                                      |                                                               |          |          |            |

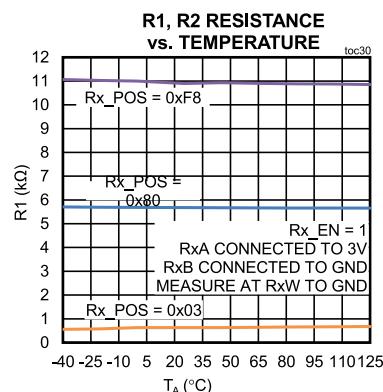

| R1, R2 Resistor Value                                                   | $R_{R1}, R_{R2}$               |                                                                                                                                                      | 8.2                                                           | 10.9     | 13.6     | $k\Omega$  |

| R1W, R2W Wiper Resistance                                               | $R_{R1W}, R_{R2W}$             | $0V < V_{R1W}, V_{R2W} \leq V_{5A}$ , $I_{TEST} = 200\mu A$                                                                                          | $T_A = 25^\circ C$<br>$-40^\circ C \leq T_A \leq 125^\circ C$ | 35<br>15 | 52<br>55 | 65<br>120  |

| R1, R2 Off-Current                                                      | $I_{OFF\_R1\_}, I_{OFF\_R2\_}$ | R1, R2 disabled,<br>$0V \leq V_{R1\_}, V_{R2\_} \leq V_{5A}$                                                                                         |                                                               | -1       | +1       | $\mu A$    |

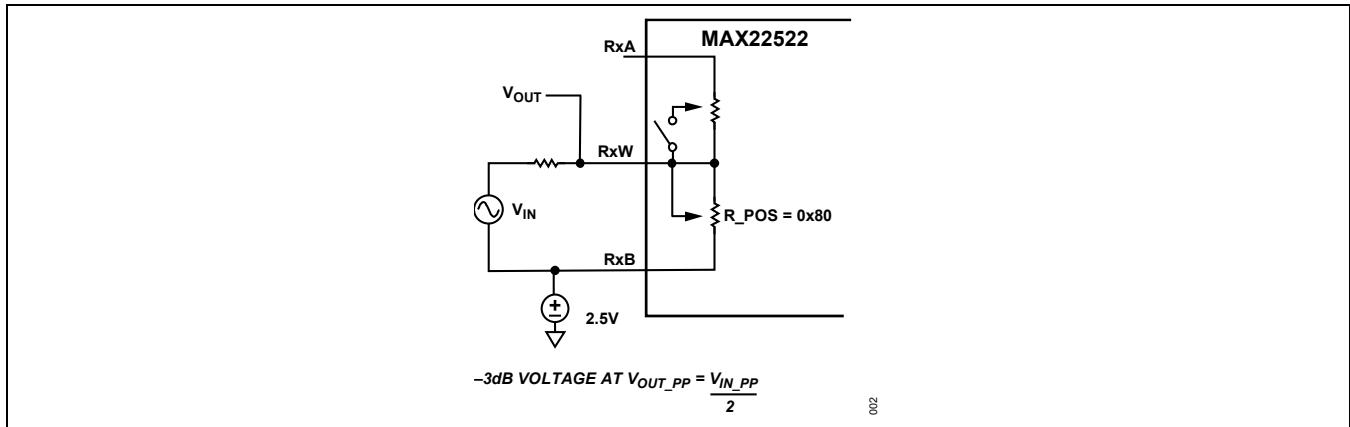

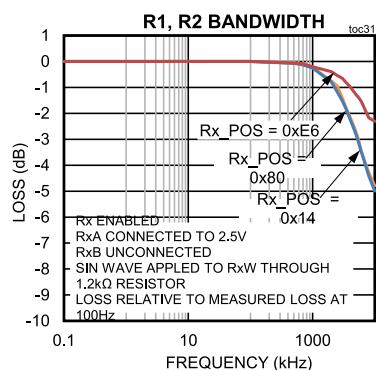

| R1, R2 Bandwidth                                                        | $BW_{R1}, BW_{R2}$             | R1A/R2A connected to $2.5V_{DC}$ , drive R1W/R2W with a $1.2k\Omega$ resistor, R1B/R2B is unconnected, Rx_POS = 0x80 (See <a href="#">Figure 1</a> ) |                                                               |          | 0.866    | MHz        |

| R1, R2 INL                                                              | $INL_{R1, R2}$                 |                                                                                                                                                      | -3.5                                                          | +1       |          | LSB        |

| R1, R2 DNL                                                              | $DNL_{R1}, DNL_{R2}$           |                                                                                                                                                      | -1.2                                                          | +1.2     |          | LSB        |

| R1A, R1B, R2A, R2B Capacitance                                          | $C_{R1\_}, C_{R2\_}$           | R1/R2 disabled,<br>$V_{RxA} = V_{RxB} = V_{RxW} = 0V$                                                                                                |                                                               | 14       |          | pF         |

| R1W, R2W Off-Capacitance                                                | $C_{R1W}, C_{R2W}$             | R1/R2 disabled,<br>$V_{RxA} = V_{RxB} = V_{RxW} = 0V$                                                                                                |                                                               | 10       |          | pF         |

| R1A, R1B, R2A, R2B On-Capacitance                                       | $C_{R1\_ON}, C_{R2\_ON}$       | R1, R2 enabled, set to minimum resistance, $V_{RxW} = 0V$                                                                                            |                                                               | 14       |          | pF         |

| R3 Resistor Value                                                       | $R_{R3}$                       | $I_{TEST} = 100\mu A$ or $V_{TEST} = 0.5V$                                                                                                           | 47                                                            | 63       | 79       | $k\Omega$  |

| R3 Steps                                                                | $N_{R3}$                       |                                                                                                                                                      | 63                                                            |          |          |            |

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ , GND = DGND = OGND = AGND = IOLGND =  $0V$ , and  $T_A = -40^\circ C$  to  $+125^\circ C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_X, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND.  $\overline{RESET}/POK$  pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^\circ C$  (See [Note 2](#)))

| PARAMETER                                            | SYMBOL          | CONDITIONS                                  |                  | MIN                  | TYP                  | MAX  | UNITS     |

|------------------------------------------------------|-----------------|---------------------------------------------|------------------|----------------------|----------------------|------|-----------|

| R3 Maximum Current                                   | $I_{R3}$        | (See <a href="#">Note 8</a> )               |                  | 2                    |                      |      | mA        |

| R3 Leakage Current                                   | $I_{OFFR3}$     | R3 disabled, $V_{R3} = 0V$ to $V_{5A}$      |                  | -1                   | +1                   |      | $\mu A$   |

| R3 INL                                               | $INL_{R3}$      | From 0 to 63                                |                  | -0.25                | +0.25                |      | LSB       |

| R3 DNL                                               |                 |                                             |                  | -0.08                | +0.08                |      | LSB       |

| R3 Capacitance                                       | $C_{R3}$        | R3 disabled, $V_{R3} = 0V$                  |                  | 7                    |                      |      | $pF$      |

| R4 Resistor Value                                    | $R_{R4\_0}$     | $V_{TEST} = 0.5V$                           | $R4\_POS = 0x00$ | 8.5                  | 11.1                 | 14.5 | $k\Omega$ |

|                                                      | $R_{R4\_8}$     | $V_{TEST} = 0.5V$                           | $R4\_POS = 0x08$ | 8                    | 10.7                 | 14   |           |

|                                                      | $R_{R4\_255}$   | $V_{TEST} = 0.5V$                           | $R4\_POS = 0xFF$ | 0.07                 | 0.11                 | 0.16 |           |

| R4 Steps                                             |                 |                                             |                  | 256                  |                      |      |           |

| R4A Off-Current                                      | $I_{OFF\_R4A}$  | $R4$ disabled, $0V$ to $V_{5A}$             |                  | -1                   | +1                   |      | $\mu A$   |

| R4 INL                                               | $INL_{R4}$      |                                             |                  | -0.8                 | +0.8                 |      | LSB       |

| R4 DNL                                               |                 |                                             |                  | -0.5                 | +0.5                 |      | LSB       |

| R4A Capacitance                                      | $C_{R4A}$       | $R4$ disabled, $V_{R4A} = 0V$               |                  | 21                   |                      |      | $pF$      |

| <b>LED OUTPUT (LED1, LED2)</b>                       |                 |                                             |                  |                      |                      |      |           |

| LED_ Output Voltage Low                              | $V_{LED\_OL}$   | $I_{LOAD} = -5mA$                           |                  |                      | 0.2                  |      | V         |

| LED_ High Impedance Leakage Current                  | $I_{LED\_OL}$   | $0V \leq V_{LEDx} \leq 5.5V$                |                  | -1                   | +1                   |      | $\mu A$   |

| <b>RESET/POK</b>                                     |                 |                                             |                  |                      |                      |      |           |

| RESET/POK Input Voltage High                         | $V_{RST\_IH}$   |                                             |                  | 1.7                  |                      |      | V         |

| RESET/POK Input Voltage Low                          | $V_{RST\_IL}$   |                                             |                  |                      | 1.3                  |      | V         |

| RESET/POK Output Voltage Low                         | $V_{POK\_LOW}$  | $I_{LOAD} = -5mA$                           |                  |                      | 0.1                  |      | V         |

| RESET/POK High Impedance Leakage Current             | $I_{RST\_OD}$   | $0V \leq V_{RESET\_POK} \leq 5.5V$          |                  | -1                   | +1                   |      | $\mu A$   |

| <b>BANK 1 GPIOs (GPIO1_0 – GPIO1_6)</b>              |                 |                                             |                  |                      |                      |      |           |

| GPIO1_x Input Voltage High                           | $V_{GPIO1IH}$   | Not in I <sup>2</sup> C mode                |                  | $0.70 \times V_{L1}$ |                      |      | V         |

| GPIO1_x Input Voltage Low                            | $V_{GPIO1IL}$   | Not in I <sup>2</sup> C mode                |                  |                      | $0.28 \times V_{L1}$ |      | V         |

| GPIO1_2 I <sup>2</sup> C Mode SDA Input Voltage High | $V_{SDA\_IH}$   | GPIO1_2 configured in I <sup>2</sup> C mode |                  | 1.8                  |                      |      | V         |

| GPIO1_2 I <sup>2</sup> C Mode SDA Input Voltage Low  | $V_{SDA\_IL}$   | GPIO1_2 configured in I <sup>2</sup> C mode |                  |                      | 1                    |      | V         |

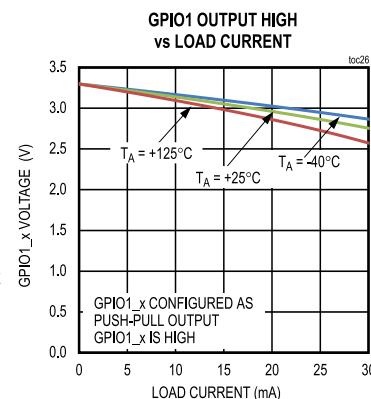

| GPIO1_x Output Voltage High                          | $V_{GPIO1\_OH}$ | $I_{LOAD} = 5mA$                            |                  | $V_{L1} - 0.26$      |                      |      | V         |

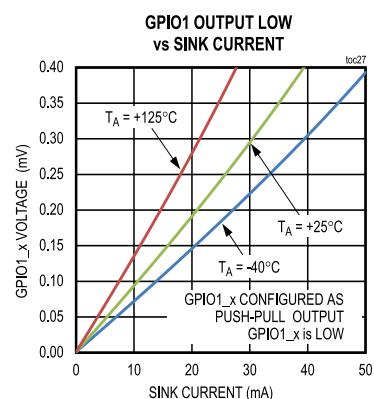

| GPIO1_x Output Voltage Low                           | $V_{GPIO1\_OL}$ | $I_{LOAD} = -5mA$                           |                  |                      | 0.2                  |      | V         |

| GPIO1_x Pull-Up Resistance                           | $R_{GPIO1\_PU}$ | $V_{GPIO1\_x} = 0V$ , pull-up enabled       |                  | 230                  | 470                  |      | $k\Omega$ |

( $V_{24} = 7V$  to  $36V$ ,  $V_{5LIN} = V_5$  to  $36V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_{18LIN} = V_{18}$  to  $5.5V$ ,  $V_{18} = 1.71V$  to  $1.89V$ ,  $V_{L1} = 2.5V$  to  $5.5V$ ,  $V_{L2} = 1.62V$  to  $5.5V$ , GND = DGND = OGND = AGND = IOLGND =  $0V$ , and  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , ORES connected to  $10k\Omega$  to GND. GPIO1\_X, SWDEN at  $V_{L1}$  or GND. GPIO2\_x at  $V_{L2}$  or GND. RESET/POK pull-up to  $3.3V$ . Typical values are at  $V_{24} = 24V$ ,  $V_{L1} = V_{L2} = 3.3V$ ,  $V_{5LIN} = V_5 = V_{5A} = 5V$ ,  $V_{18LIN} = V_{18} = 1.8V$ , and  $T_A = +25^{\circ}C$  (See [Note 2](#)))

| PARAMETER                                                              | SYMBOL            | CONDITIONS                                                 | MIN                  | TYP                  | MAX | UNITS     |

|------------------------------------------------------------------------|-------------------|------------------------------------------------------------|----------------------|----------------------|-----|-----------|