## 15V<sub>IN</sub>, Single 15A Step-Down μModule Regulator with PMBus

### FEATURES

- ▶ Complete Solution in <1cm<sup>2</sup> (Single-Sided PCB) or 0.5cm<sup>2</sup> (Dual-Sided PCB)

- ▶ PMBus Telemetry of Output Current, Output Voltage, Input Voltage, and Junction Temperature

- ▶ Pin-to-Pin Compatible with [LTM4739](#)

- ▶ Input Voltage Range: 3V to 15V

- ▶ Output Voltage Range: 0.4V to 5.5V

- ▶ Adjustable Reference Voltage: 0.4V to 0.8V (Default 0.5V)

- ▶ 90% Full-Load Efficiency from 12V<sub>IN</sub> to 1.5V<sub>OUT</sub> at 15A

- ▶ ±1% Maximum DC Output Error Over Temperature

- ▶ Wide Frequency Range: 500kHz to 2MHz

- ▶ Internal Compensation

- ▶ Power Good Indicator

- ▶ Constant Frequency Peak Current Mode Control

- ▶ Differential Remote Sense

- ▶ Single-Phase Point-of-Load Operation

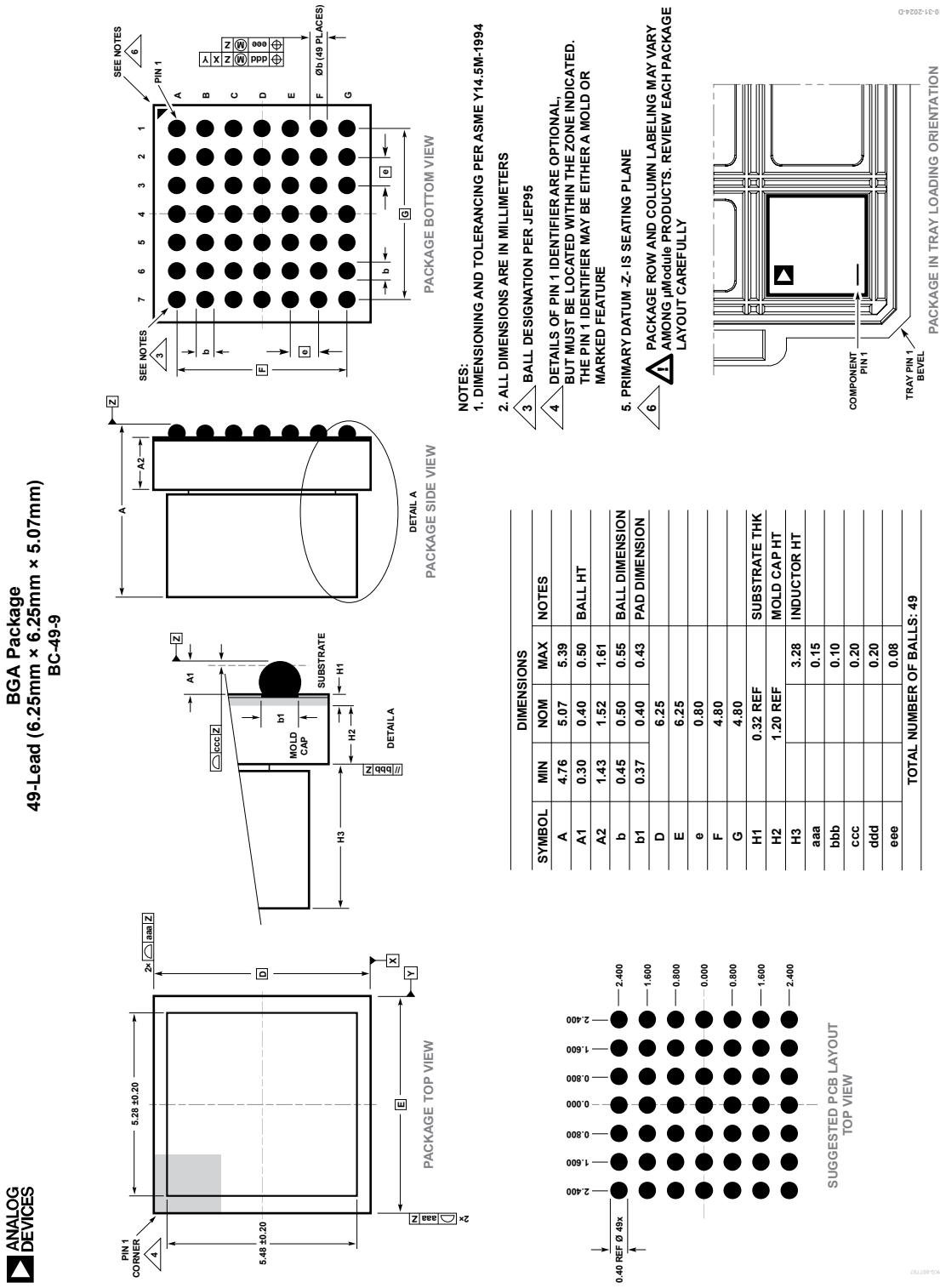

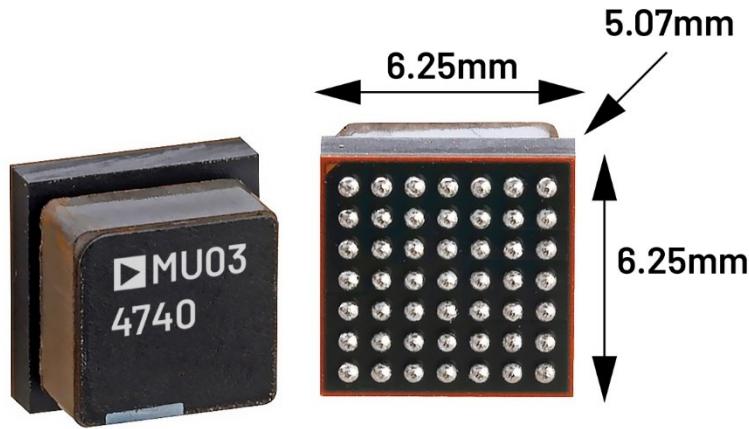

- ▶ [49-Lead 6.25mm × 6.25mm × 5.07mm](#) BGA Package

### APPLICATIONS

- ▶ Data Center Power, Servers, and Storage

- ▶ Telecom, Networking, and Industrial Equipment

- ▶ Point-of-Load (POL) Voltage Regulators

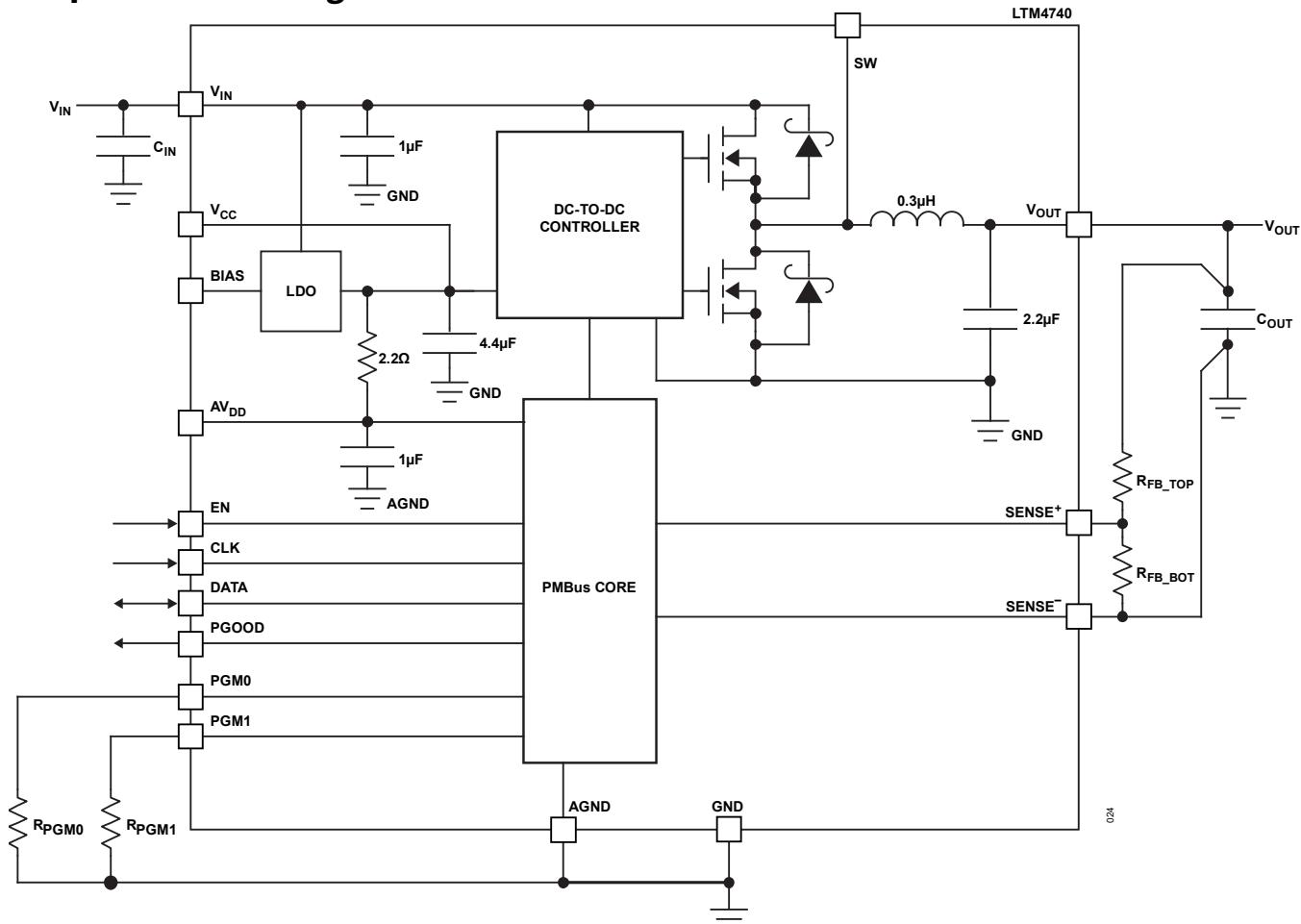

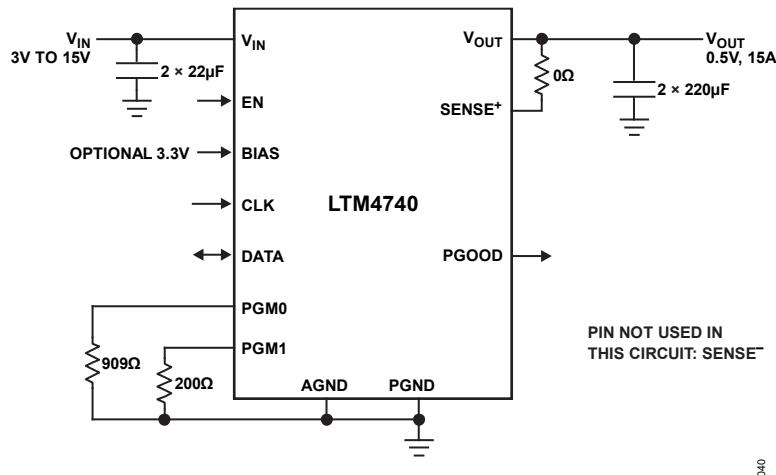

### TYPICAL APPLICATION

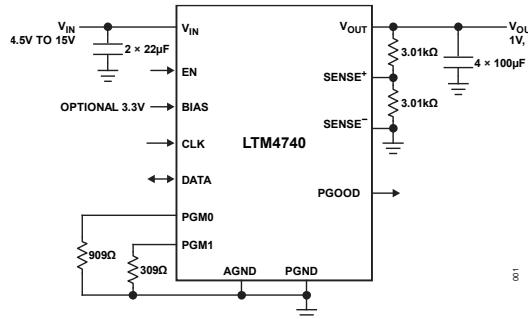

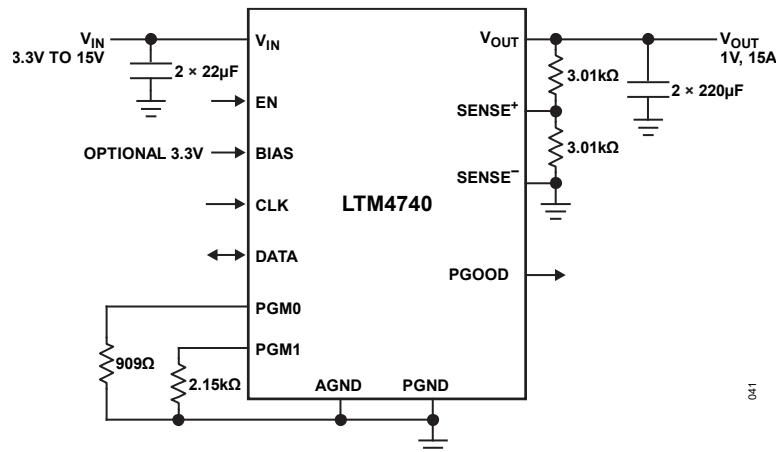

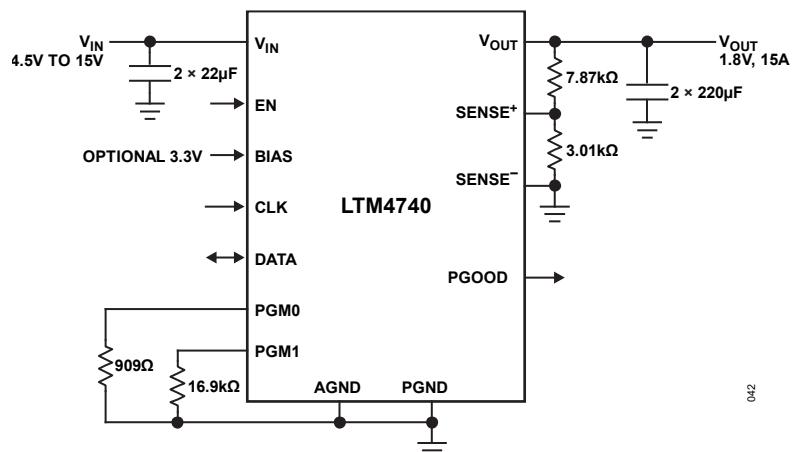

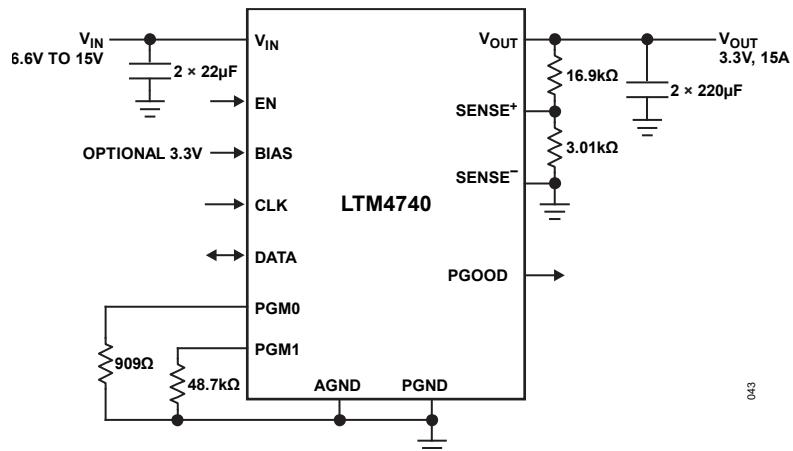

Figure 1. 4.5V to 15V Input to 1V, 15A Output

### GENERAL DESCRIPTION

The [LTM4740](#) is a complete 15A step-down switching-mode power μModule® (micromodule) regulator with a PMBus interface in a tiny 6.25mm × 6.25mm × 5.07mm Ball Grid Array (BGA) package. The package includes the switching controller, the power MOSFETs, an inductor, and the supporting components. Operating over an input voltage range of 3V to 15V, the LTM4740 supports an output voltage range of 0.4V to 5.5V. Its high-efficiency design delivers up to 15A of continuous output current. Only bulk input and output capacitors are needed. The switching frequency of the LTM4740 can be configured from 500kHz to 2MHz to provide the capability of optimizing the design in terms of size and performance. Pin-compatible with LTM4739, which is a 10A μModule regulator with PMBus. Therefore, one layout could fit different power-level requests with flexibility. The LTM4740 has an optional BIAS input pin, allowing connection from a 2.8V to 5.5V bias input supply for optimized efficiency. Operation settings and configurable features can be selected by connecting two pin-strap resistors from the PGMin pins to ground and then adjusted using PMBus commands. The LTM4740 has multiple protections, including positive and negative overcurrent (POC/NOC), output overvoltage (OV), and overtemperature (OT) to ensure a robust design. It is available with a RoHS-compliant terminal finish.

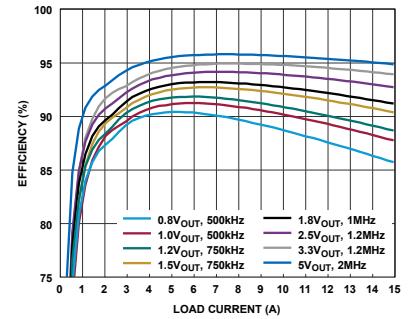

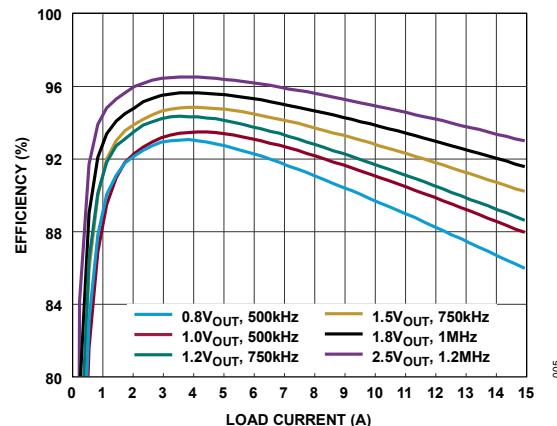

Figure 2. Efficiency, V<sub>IN</sub> = 12V, V<sub>BIA</sub>S = 3.3V

## TABLE OF CONTENTS

|                                                                   |    |

|-------------------------------------------------------------------|----|

| Features.....                                                     | 1  |

| Applications .....                                                | 1  |

| General Description .....                                         | 1  |

| Typical Application .....                                         | 1  |

| Revision History .....                                            | 3  |

| Specifications.....                                               | 4  |

| Absolute Maximum Ratings .....                                    | 7  |

| Thermal Resistance .....                                          | 8  |

| Electrostatic Discharge (ESD) .....                               | 8  |

| ESD Ratings .....                                                 | 8  |

| ESD Caution.....                                                  | 8  |

| Pin Configurations and Function Descriptions .....                | 9  |

| Pin Descriptions.....                                             | 9  |

| Typical Performance Characteristics .....                         | 11 |

| Theory of Operation.....                                          | 15 |

| LTM4740 Overview.....                                             | 15 |

| LTM4740 Major Features .....                                      | 15 |

| Simplified Block Diagram.....                                     | 16 |

| Decoupling Requirements .....                                     | 16 |

| Applications Information.....                                     | 17 |

| Capacitor Selection Considerations .....                          | 17 |

| Pin-Strap Programmability .....                                   | 18 |

| PMBus Interface.....                                              | 20 |

| LTpowerPlay: An Interactive GUI for Digital Power Management..... | 22 |

| Frequency Selection .....                                         | 23 |

| Advanced Modulation Scheme .....                                  | 23 |

| Output Voltage Sensing.....                                       | 23 |

| Operating Frequency Trade-Offs.....                               | 24 |

| Maximum Load .....                                                | 25 |

| Voltage Loop Gain.....                                            | 25 |

| Minimum Input Voltage .....                                       | 25 |

| Prebiased Output .....                                            | 25 |

| Discontinuous-Conduction Mode Operation.....                      | 25 |

| Shorted Input Protection .....                                    | 25 |

|                                                         |    |

|---------------------------------------------------------|----|

| Fault Handling .....                                    | 26 |

| Input Undervoltage Lockout.....                         | 26 |

| Output Overvoltage Protection .....                     | 26 |

| Positive Overcurrent Protection .....                   | 26 |

| Negative Overcurrent Protection.....                    | 27 |

| Overtemperature Protection .....                        | 27 |

| Hot-Plugging Safely .....                               | 27 |

| Safety Consideration .....                              | 27 |

| Thermal Considerations and Output Current Derating..... | 27 |

| Thermal Derating Curves .....                           | 30 |

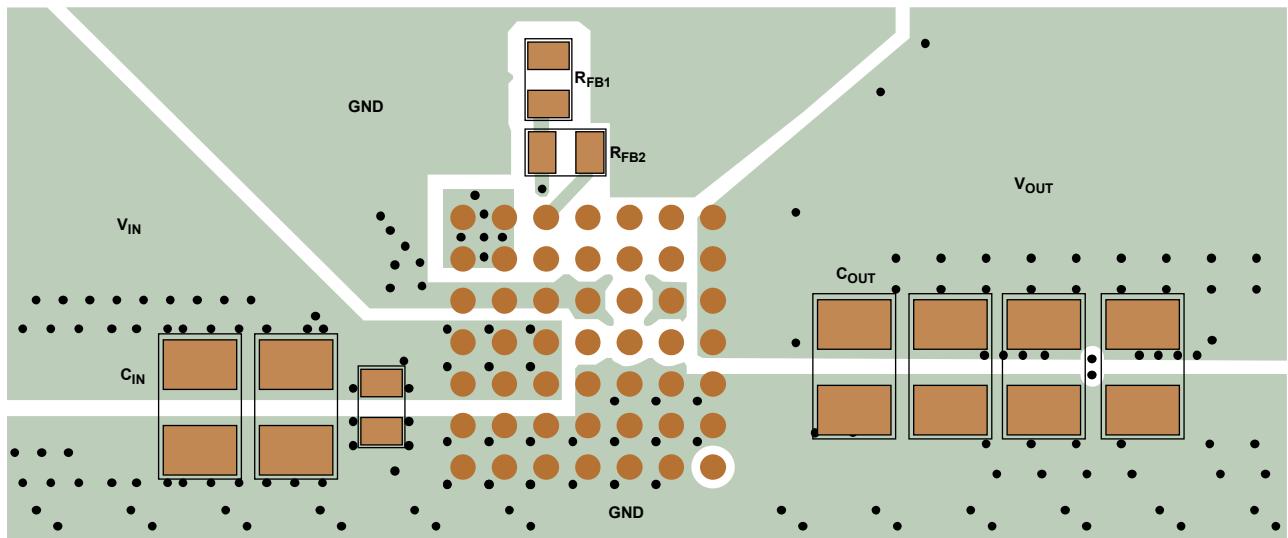

| PCB Layout Recommendations .....                        | 33 |

| Typical Applications .....                              | 34 |

| Related Parts.....                                      | 36 |

| Outline Dimensions.....                                 | 37 |

| Ordering Guide.....                                     | 38 |

| Selector Guide.....                                     | 39 |

| Package Photos .....                                    | 39 |

| Design Resources.....                                   | 39 |

## REVISION HISTORY

| REVISION NUMBER | REVISION DATE | DESCRIPTION     | PAGE NUMBER |

|-----------------|---------------|-----------------|-------------|

| 0               | 1/26          | Initial release | —           |

## SPECIFICATIONS

Table 1. Electrical Characteristics

(T<sub>A</sub> = 25°C, V<sub>IN</sub> = 12V)

| PARAMETER                                          | SYMBOL                                  | CONDITIONS                                                                                                                  | COMMENTS                       | MIN  | TYP   | MAX  | UNITS |

|----------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|-------|------|-------|

| Input DC voltage                                   | V <sub>IN</sub>                         |                                                                                                                             | -40°C ≤ T <sub>J</sub> ≤ 125°C | 3    |       | 15   | V     |

| Optional BIAS input voltage range                  | V <sub>BIAS</sub>                       |                                                                                                                             | -40°C ≤ T <sub>J</sub> ≤ 125°C | 2.8  |       | 5.5  | V     |

| Output voltage range                               | V <sub>OUT(RANGE)</sub>                 |                                                                                                                             | -40°C ≤ T <sub>J</sub> ≤ 125°C | 0.4  |       | 5.5  | V     |

| Output voltage, total variation with line and load | V <sub>OUT(DC)</sub>                    | C <sub>IN</sub> = 22µF,<br>C <sub>OUT</sub> = 400µF ceramic<br>V <sub>IN</sub> = 3V to 15V,<br>I <sub>OUT</sub> = 0A to 15A | -40°C ≤ T <sub>J</sub> ≤ 125°C | 0.99 | 1     | 1.01 | V     |

| Input supply current (shutdown)                    | I <sub>S(VIN)</sub>                     | Shutdown, EN = 0,<br>V <sub>IN</sub> = 12V, BIAS = 3.3V                                                                     |                                | 90   | 120   | 150  | µA    |

| BIAS pin input current                             | I <sub>BIAS</sub>                       | Shutdown, EN = 0,<br>BIAS = 3.3V                                                                                            |                                |      | 1     | 10   | µA    |

| Input supply quiescent current                     | I <sub>Q(VIN)</sub>                     | V <sub>IN</sub> = 12V, EN = 1V,<br>V <sub>OUT</sub> = 1V, forced<br>continuous mode<br>(FCM), BIAS is open                  |                                | 40   | 47    | 55   | mA    |

|                                                    |                                         | V <sub>IN</sub> = 12V, EN = 1V,<br>V <sub>OUT</sub> = 1V,<br>discontinuous-<br>conduction mode<br>(DCM), BIAS is open       |                                | 8    | 10    | 12   | mA    |

| Start-up time                                      | t <sub>START</sub>                      | C <sub>OUT</sub> = 400µF ceramic,<br>no load, V <sub>IN</sub> = 12V,<br>V <sub>OUT</sub> = 1V                               |                                |      | 1.3   |      | ms    |

| Soft-start slew rate                               | SS                                      | SENSE <sup>+</sup> – SENSE <sup>-</sup>                                                                                     |                                |      | 0.5   |      | V/ms  |

| EN pin rising threshold                            | V <sub>EN(RISE)</sub>                   | EN rising                                                                                                                   | -40°C ≤ T <sub>J</sub> ≤ 125°C | 0.8  | 0.85  |      | V     |

| EN pin falling threshold                           | V <sub>EN(FALL)</sub>                   | EN falling                                                                                                                  | -40°C ≤ T <sub>J</sub> ≤ 125°C |      | 0.66  | 0.7  | V     |

| Output continuous current range                    | I <sub>OUT(DC)</sub>                    | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1V <sup>4</sup>                                                                   |                                |      |       | 15   | A     |

| Line regulation accuracy                           | ΔV <sub>OUT(LINE)/V<sub>OUT</sub></sub> | V <sub>OUT</sub> = 1V, V <sub>IN</sub> = 3V to 15V, I <sub>OUT</sub> = 0A                                                   | -40°C ≤ T <sub>J</sub> ≤ 125°C |      | 0.001 | 0.02 | %/V   |

| Load regulation accuracy                           | ΔV <sub>OUT(LOAD)/V<sub>OUT</sub></sub> | V <sub>OUT</sub> = 1V,<br>I <sub>OUT</sub> = 0A to 15A                                                                      | -40°C ≤ T <sub>J</sub> ≤ 125°C |      | 0.2   | 0.6  | %     |

$(T_A = 25^\circ\text{C}, V_{IN} = 12\text{V})$

| PARAMETER                                                          | SYMBOL              | CONDITIONS                                                                                                   | COMMENTS                                            | MIN   | TYP | MAX   | UNITS         |

|--------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------|-----|-------|---------------|

| Output ripple voltage <sup>4</sup>                                 | $V_{OUT(AC)}$       | $I_{OUT} = 0\text{A}, C_{OUT} = 400\mu\text{F}$<br>ceramic, $V_{IN} = 12\text{V}$ ,<br>$V_{OUT} = 1\text{V}$ |                                                     | 16.5  | 5   | 20.5  | mV            |

| Output current limit                                               | $I_{OUTPK}$         | $V_{IN} = 12, V_{OUT} = 1\text{V}$                                                                           |                                                     | 16    | 18  | 20    | A             |

| Positive overcurrent (POC) protection threshold <sup>5</sup>       | $I_{POC}$           | Inductor peak current, POC = 20A                                                                             |                                                     | 18    | 20  | 22    | A             |

| Fast positive overcurrent (FPOC) protection threshold <sup>5</sup> | $I_{FPOC}$          | Inductor peak current, FPOC = 25A, will shut down the $\mu$ Module                                           |                                                     | 23    | 25  | 29    | A             |

| Minimum on-time                                                    | $t_{ON(MIN)}$       |                                                                                                              |                                                     | 50    | 60  |       | ns            |

| PGOOD output low                                                   | $V_{PGOODL}$        | $I_{PGOOD} = 4\text{mA}$                                                                                     |                                                     |       |     | 0.4   | V             |

| PGOOD trip level<br>$V_{REF} = 0.5\text{V}$                        | $V_{PGOOD}$         | Output undervoltage threshold                                                                                |                                                     | -16   | -13 | -10   | %             |

|                                                                    |                     | Output OV protection threshold                                                                               |                                                     | 10    | 13  | 16    | %             |

| PGOOD leakage                                                      | $I_{PGOOD}$         |                                                                                                              |                                                     |       | 0.1 |       | $\mu\text{A}$ |

| PGOOD pull-down resistance                                         | $R_{PGOOD}$         |                                                                                                              |                                                     | 68    |     |       | $\Omega$      |

| Oscillator frequency                                               | $f_{OSC}$           | $R_{PGM1} = 309\Omega$                                                                                       |                                                     | 500   |     |       | kHz           |

|                                                                    |                     | $R_{PGM1} = 21.5\text{k}\Omega$                                                                              |                                                     | 1     |     |       | MHz           |

|                                                                    |                     | $R_{PGM1} = 115\text{k}\Omega$                                                                               |                                                     | 2     |     |       | MHz           |

| Internal low dropout (LDO)-regulated output to power gate drives   | $V_{CC}$            | $V_{IN} = 3\text{V to } 15\text{V}$                                                                          |                                                     | 1.7   | 1.8 | 1.9   | V             |

| Analog AV <sub>DD</sub> voltage to power internal circuitry        | $V_{AVDD}$          | $V_{IN} = 3\text{V to } 15\text{V}$                                                                          |                                                     |       | 1.8 |       | V             |

| $V_{IN}$ undervoltage lockout                                      | $V_{IN\_UVLO}$      | Rising                                                                                                       |                                                     | 2.4   | 2.5 | 2.6   | V             |

|                                                                    |                     | Hysteresis                                                                                                   |                                                     | 100   |     |       | mV            |

| Feedback voltage accuracy                                          | $SENSE^+ / SENSE^-$ | $SENSE^+$ and $SENSE^-$ , overline and load range                                                            | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ | 0.495 | 0.5 | 0.505 | V             |

| Feedback voltage range                                             | $SENSE^+ / SENSE^-$ | Set by PMBus command, 1.95mV resolution                                                                      |                                                     | 0.4   |     | 0.8   | V             |

| Negative voltage sense input range                                 | $V_{SENSE^-}$       |                                                                                                              |                                                     | -0.1  |     | 0.1   | V             |

| Positive voltage sense current                                     | $I_{SENSE^+}$       |                                                                                                              |                                                     | -1    |     | 1     | $\mu\text{A}$ |

$(T_A = 25^\circ\text{C}, V_{IN} = 12\text{V})$

| PARAMETER                      | SYMBOL        | CONDITIONS | COMMENTS | MIN | TYP | MAX | UNITS         |

|--------------------------------|---------------|------------|----------|-----|-----|-----|---------------|

| Negative voltage sense current | $I_{SENSE^-}$ |            |          |     | 300 |     | $\mu\text{A}$ |

**Power Management Bus (PMBus) Interface**

|                                    |           |             |  |      |     |     |               |

|------------------------------------|-----------|-------------|--|------|-----|-----|---------------|

| CLK, DATA input logic low voltage  |           |             |  |      | 0.8 | V   |               |

| CLK, DATA input logic high voltage |           |             |  | 1.45 |     | V   |               |

| CLK, DATA input leakage current    |           |             |  | -1   |     | 1   | $\mu\text{A}$ |

| DATA output logic low              |           | Sinking 4mA |  |      | 0.4 | V   |               |

| PMBus operating frequency          | $f_{CLK}$ |             |  |      | 1   | MHz |               |

**PMBus Telemetry**

|                                        |  |                                          |  |      |         |     |                  |

|----------------------------------------|--|------------------------------------------|--|------|---------|-----|------------------|

| Reading update rate <sup>4</sup>       |  | READ_IOUT,<br>READ_VOUT, and<br>READ_VIN |  |      | 1.47    |     | ms               |

|                                        |  | READ_TEMPERATURE                         |  |      | 2.86    |     | ms               |

| READ_IOUT range                        |  |                                          |  |      |         | 15  | A                |

| READ_IOUT accuracy                     |  | $I_{OUT} = 0\text{A}$                    |  | -1   |         | 1   | A                |

|                                        |  | $0\text{A} < I_{OUT}$                    |  | -1.5 |         | 1.5 | A                |

| READ_VOUT range                        |  |                                          |  | 400  |         | 800 | mV               |

| READ_VOUT accuracy                     |  |                                          |  | -1   |         | 1   | %                |

| READ_VIN range                         |  |                                          |  | 3    |         | 15  | V                |

| READ_VIN accuracy                      |  |                                          |  | -350 |         | 350 | mV               |

| READ_TEMPERATURE range                 |  |                                          |  | -40  |         | 125 | $^\circ\text{C}$ |

| READ_TEMPERATURE accuracy <sup>4</sup> |  |                                          |  |      | $\pm 4$ |     | $^\circ\text{C}$ |

The LTM4740 is tested under pulsed-load conditions such that  $T_J \approx T_A$ . The LTM4740E is guaranteed to meet performance specifications over the  $0^\circ\text{C}$  to  $125^\circ\text{C}$  internal operating temperature range. Specifications over the full  $-40^\circ\text{C}$  to  $125^\circ\text{C}$  internal operating temperature range are assured by design, characterization, and

<sup>1</sup> correlation with statistical process controls. The LTM4740I is guaranteed to meet specifications over the full  $-40^\circ\text{C}$  to  $125^\circ\text{C}$  internal operating temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by the specific operating conditions in conjunction with board layout, the rated package thermal resistance, and other environmental factors.

<sup>2</sup> The minimum on-time is tested at wafer sort.

<sup>3</sup> See output current derating curves, [Figure 30](#) through [Figure 38](#), for different  $V_{IN}$ ,  $V_{OUT}$ , and  $T_A$  conditions.

<sup>4</sup> Guaranteed by design.

<sup>5</sup> 100% tested at the wafer level.

## ABSOLUTE MAXIMUM RATINGS

$T_A = 25^\circ\text{C}$  unless otherwise specified.

**Table 2. Absolute Maximum Ratings**

| PARAMETER                                               | RATING                                     |

|---------------------------------------------------------|--------------------------------------------|

| $V_{IN}$ , SW                                           | 18V                                        |

| $V_{OUT}$ , BIAS                                        | 6V                                         |

| PGOOD, DATA, CLK, EN                                    | 4V                                         |

| $AV_{DD}$ , $V_{CC}$                                    | 2.5V                                       |

| SENSE <sup>+</sup> , PGM0, PGM1                         | $AV_{DD}$                                  |

| SENSE <sup>-</sup>                                      | 0.3V                                       |

| Internal operating temperature range (E-grade, I-grade) | $-40^\circ\text{C}$ to $125^\circ\text{C}$ |

| Storage temperature range                               | $-55^\circ\text{C}$ to $150^\circ\text{C}$ |

| Peak solder reflow body temperature                     | 250°C                                      |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## Thermal Resistance

Thermal performance is directly linked to PCB design and operating environment. Close attention to printed circuit board (PCB) thermal design is required.

## Electrostatic Discharge (ESD)

The following ESD information is provided for handling of ESD-sensitive devices in an ESD-protected area only. Human body model (HBM) per ANSI/ESDA/JEDEC JS-001, Field induced charged device model (FICDM), and charged device model (CDM) per ANSI/ESDA/JEDEC JS-002. International Electrotechnical Commission (IEC) electromagnetic compatibility: Part 4-2 (IEC) per IEC 61000-4-2. Machine model (MM) per ANSI/ESD STM5.2. MM voltage values are for characterization only.

### ESD Ratings

**Table 3. LTM4740 ESD Ratings**

| ESD MODEL | WITHSTAND THRESHOLD (V) | CLASS |

|-----------|-------------------------|-------|

| HBM       | ±4000                   | 3A    |

| CDM       | ±1250                   | C3    |

### ESD Caution

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

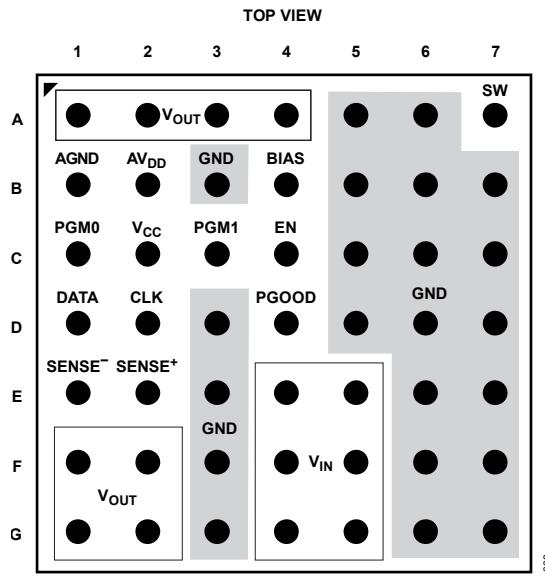

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

003

**BGA PACKAGE**

49-LEAD (6.25mm x 6.25mm x 5.07mm)

$T_{JMAX} = 125^\circ\text{C}$ ,  $\theta_{JA} = 17.5^\circ\text{C/W}$ ,  $\theta_{JCTop} = 9.7^\circ\text{C/W}$ ,

$\theta_{JCbot} = 6.6^\circ\text{C/W}$

WEIGHT = 0.701g

$\theta$  VALUES ARE DETERMINED BY SIMULATION PER JESD51

CONDITIONS.

$\theta_{JA}$  VALUE IS OBTAINED WITH DEMO BOARD.

FOR LAB MEASURED DERATING CURVES, SEE APPLICATIONS

INFORMATION SECTION.

Figure 3. Pin Configuration

PACKAGE ROW AND COLUMN LABELING MAY VARY

AMONG  $\mu$ Module PRODUCTS. REVIEW EACH PACKAGE

LAYOUT CAREFULLY.

## Pin Descriptions

Table 4. Pin Descriptions

| PIN                                                                                   | NAME      | DESCRIPTION                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CFG 1</b>                                                                          |           |                                                                                                                                                                                                                                  |

| A1, A2, A3, A4,<br>F1, F2, G1, G2                                                     | $V_{OUT}$ | Power Output Pins. Apply output load between these pins and GND pins. Recommend placing the output decoupling capacitor directly between these pins and GND pins. See the <i>Decoupling Requirements</i> table for more details. |

| A5, A6, B3, B5-<br>B7, C5-C7, D5-<br>D7, E6, E7, F6,<br>F7, G6, G7, D3,<br>E3, F3, G3 | GND       | Power Ground Pins for Both Input and Output Returns.                                                                                                                                                                             |

| PIN                    | NAME               | DESCRIPTION                                                                                                                                                                                                                                                                                           |

|------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CFG 1</b>           |                    |                                                                                                                                                                                                                                                                                                       |

| A7                     | SW                 | Switching node of LTM4740. This pin is for test purposes only. Do not load the SW pin with external circuitry.                                                                                                                                                                                        |

| B1                     | AGND               | Analog Ground. Single point connecting this pin to GND plane.                                                                                                                                                                                                                                         |

| B2                     | AV <sub>DD</sub>   | 1.8V Supply for Analog Circuitry. There is an internal 1 $\mu$ F ceramic capacitor from AV <sub>DD</sub> to AGND. The AV <sub>DD</sub> pin could be left open.                                                                                                                                        |

| B4                     | BIAS               | Optional 2.8V to 5.5V LDO Input Supply. External BIAS helps to improve efficiency. A 2.2 $\mu$ F external bias capacitor is required. Leave the BIAS pin floating if unused.                                                                                                                          |

| C1                     | PGM0               | Program Input. Connect the PGM0 pin to ground through a programming resistor. The PGM0 sets overcurrent (OC) protection and the PMBus address.                                                                                                                                                        |

| C2                     | V <sub>CC</sub>    | Internal 1.8V Regulator Bypass Pin. The internal power drivers and control circuits are powered from this voltage. There is an internal 4.4 $\mu$ F capacitor from V <sub>CC</sub> to GND. Do not load the V <sub>CC</sub> pin with external circuitry. The V <sub>CC</sub> pin should be floated.    |

| C3                     | PGM1               | Program Input. Connect the PGM1 pin to ground through a programming resistor. The PGM1 sets the frequency and the control loop gain.                                                                                                                                                                  |

| C4                     | EN                 | EN control input of each switching mode regulator channel. Enables device operation by connecting EN above 1V. Connecting this pin to GND shuts down the device.                                                                                                                                      |

| D1                     | DATA               | PMBus Data.                                                                                                                                                                                                                                                                                           |

| D2                     | CLK                | PMBus Clock.                                                                                                                                                                                                                                                                                          |

| D4                     | PGOOD              | Output Power Good Indicator. The PGOOD pin is the open-drain output of an internal comparator. The PGOOD pin remains low until the V <sub>SENSE</sub> <sup>+</sup> – V <sub>SENSE</sub> <sup>-</sup> voltage is within $\pm 13\%$ of the final regulation voltage, and there are no fault conditions. |

| E1                     | SENSE <sup>-</sup> | Output Voltage Remote Sense Negative Input Pin.                                                                                                                                                                                                                                                       |

| E2                     | SENSE <sup>+</sup> | Output Voltage Remote Sense Positive Input Pin. Connect V <sub>SENSE</sub> <sup>+</sup> to the output voltage at the load. A resistive voltage divider can be inserted between the output and V <sub>SENSE</sub> <sup>+</sup> to regulate the output above the reference voltage.                     |

| E4, E5, F4, F5, G4, G5 | V <sub>IN</sub>    | Power Input Pins. Apply input voltage between the V <sub>IN</sub> pins and GND pins. Recommend placing input decoupling capacitors directly between V <sub>IN</sub> pins and GND pins.                                                                                                                |

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25^\circ\text{C}$ , unless otherwise noted.

Figure 4. Efficiency,  $V_{IN} = 12\text{V}$ ,  $V_{BIAS} = 3.3\text{V}$

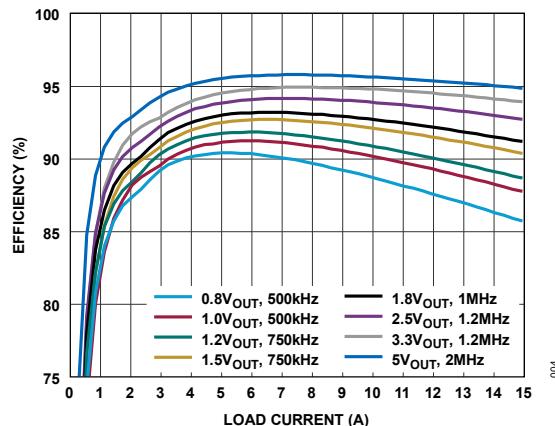

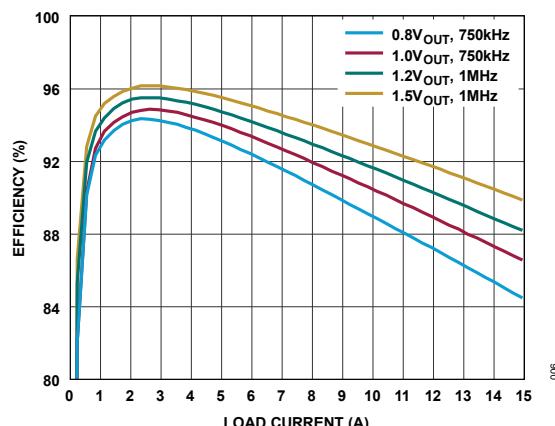

Figure 5. Efficiency,  $V_{IN} = 5\text{V}$ ,  $V_{BIAS} = 3.3\text{V}$

Figure 6. Efficiency,  $V_{IN} = 3.3\text{V}$ ,  $V_{BIAS} = 3.3\text{V}$

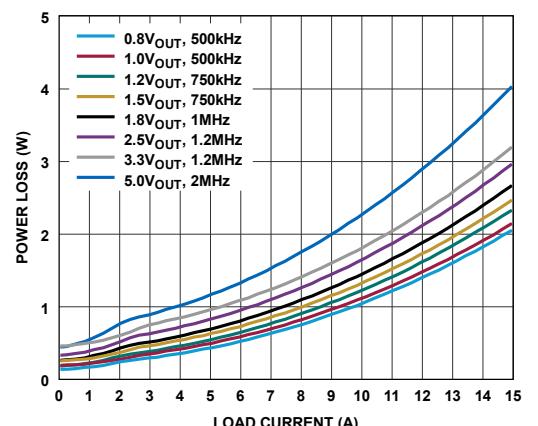

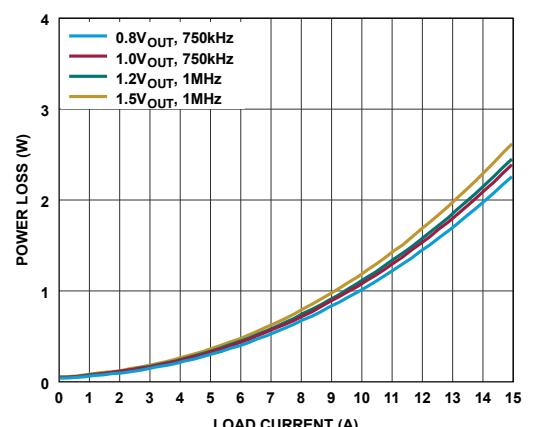

Figure 7. Power Loss,  $V_{IN} = 12\text{V}$ ,  $V_{BIAS} = 3.3\text{V}$

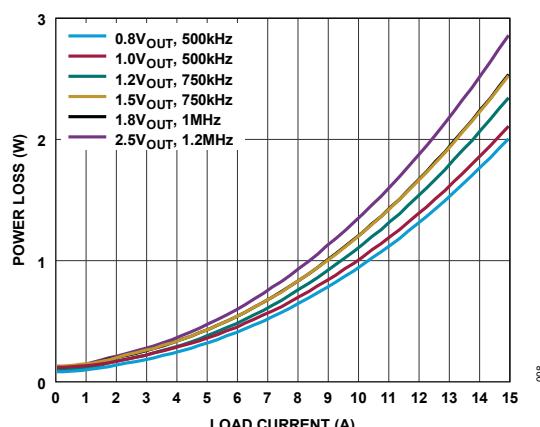

Figure 8. Power Loss,  $V_{IN} = 5\text{V}$ ,  $V_{BIAS} = 3.3\text{V}$

Figure 9. Power Loss,  $V_{IN} = 3.3\text{V}$ ,  $V_{BIAS} = 3.3\text{V}$

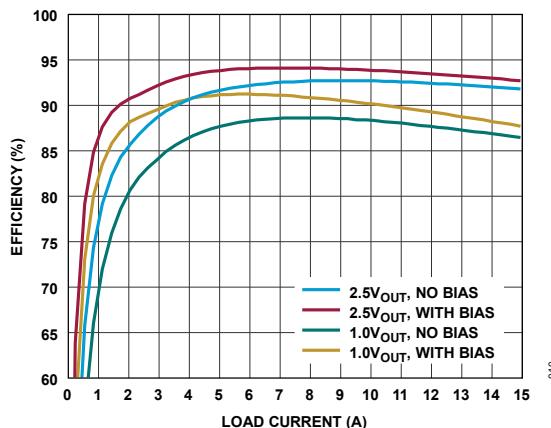

**Figure 10. Efficiency vs. Load,  $V_{IN} = 12V$ , with and without External Bias**

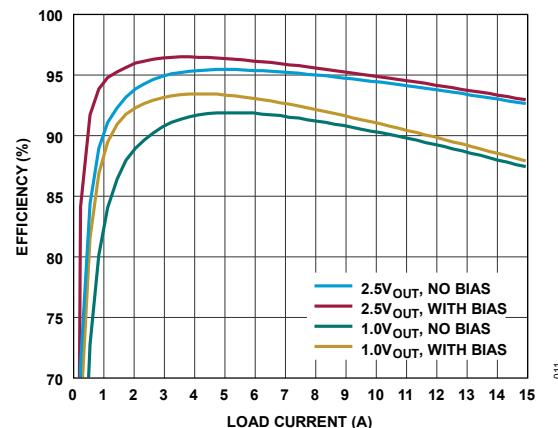

**Figure 11. Efficiency vs. Load,  $V_{IN} = 5V$ , with and without External Bias**

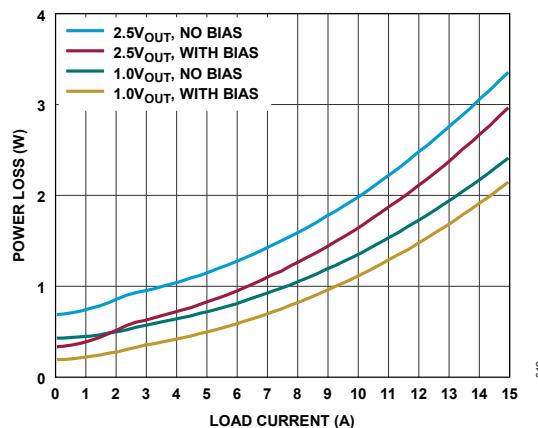

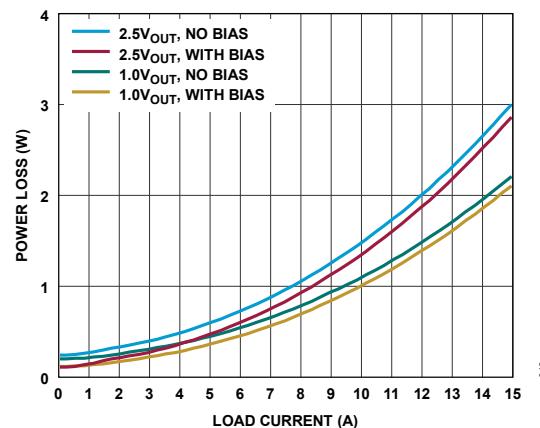

**Figure 12. Power Loss vs. Load,  $V_{IN} = 12V$ , with and without External Bias**

**Figure 13. Power Loss vs. Load,  $V_{IN} = 5V$ , with and without External Bias**

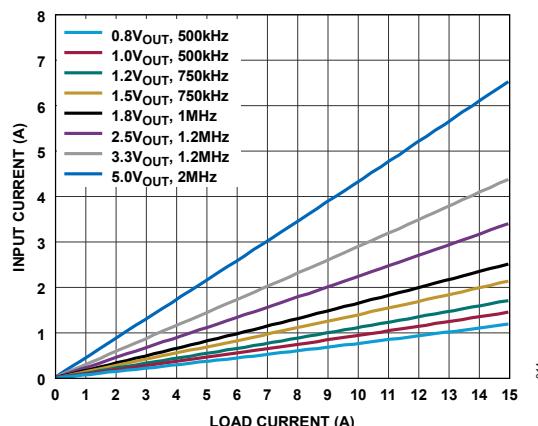

**Figure 14. Input Current,  $V_{IN} = 12V$ ,  $V_{BIAS} = 3.3V$**

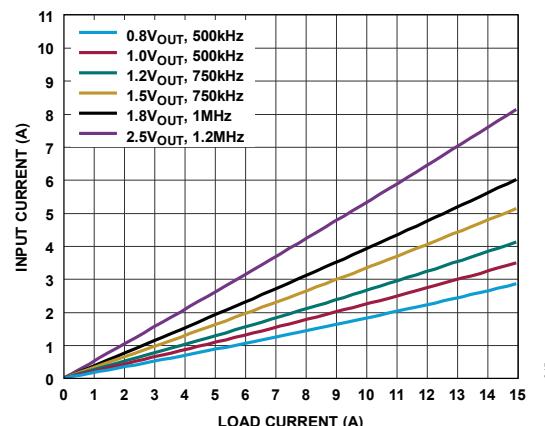

**Figure 15. Input Current,  $V_{IN} = 5V$ ,  $V_{BIAS} = 3.3V$**

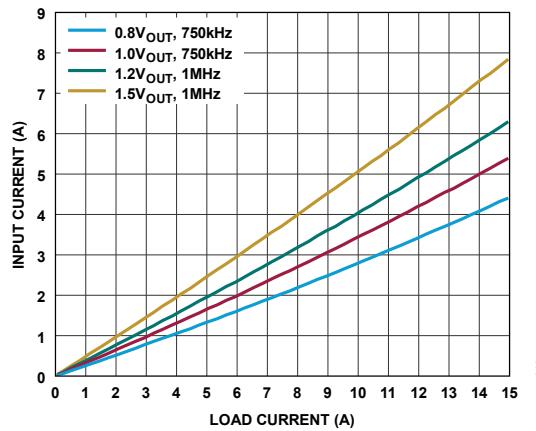

Figure 16. Input Current,  $V_{IN} = 3.3V$ ,  $V_{BIAS} = 3.3V$

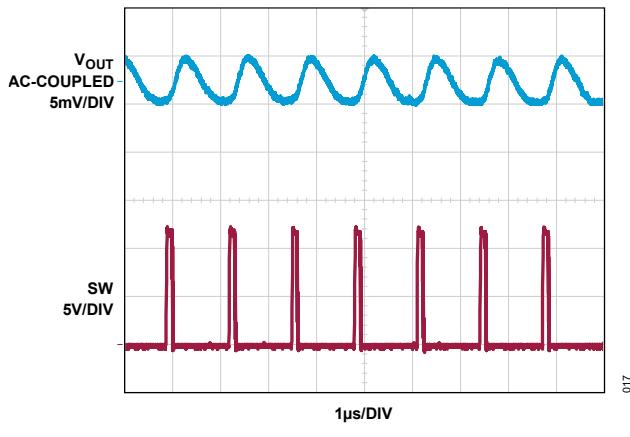

Figure 17. Output Voltage Ripple (FCM)

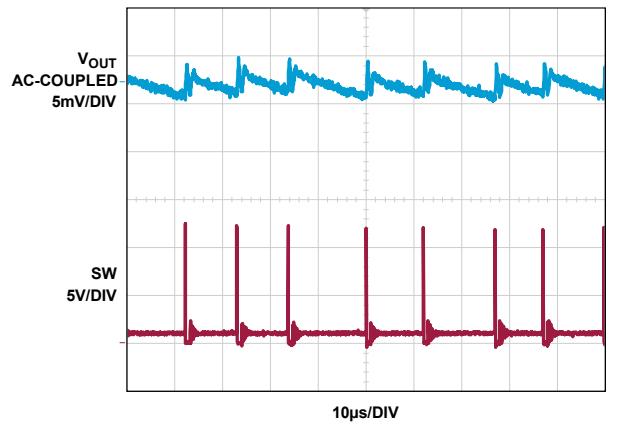

Figure 18. Output Voltage Ripple (DCM)

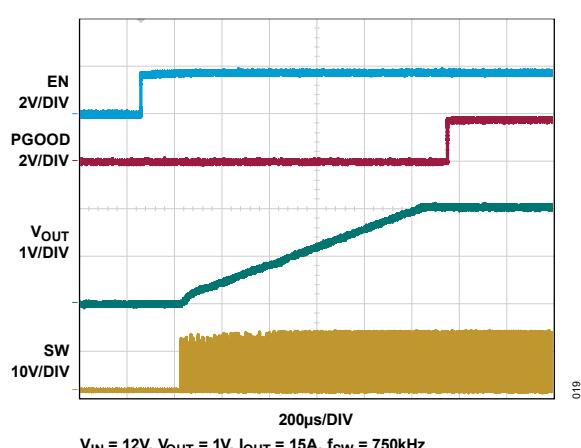

Figure 19. Startup without Pre-Bias

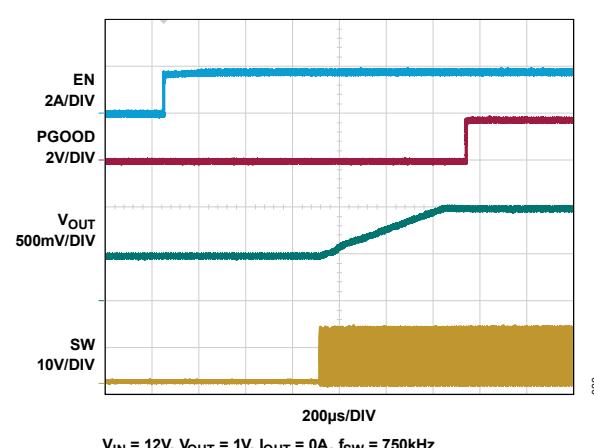

Figure 20. Startup with Pre-Bias, 0.5V

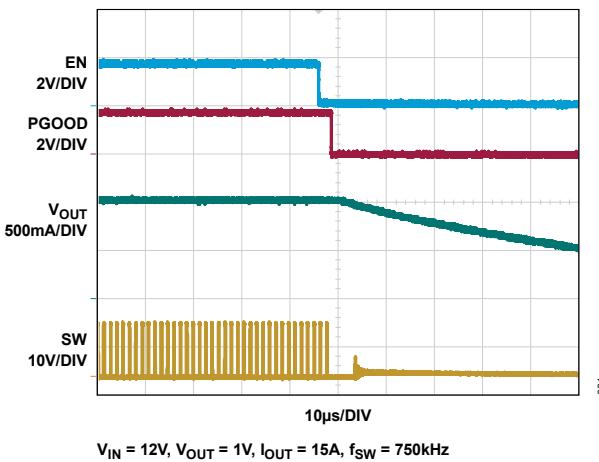

Figure 21. Shutdown

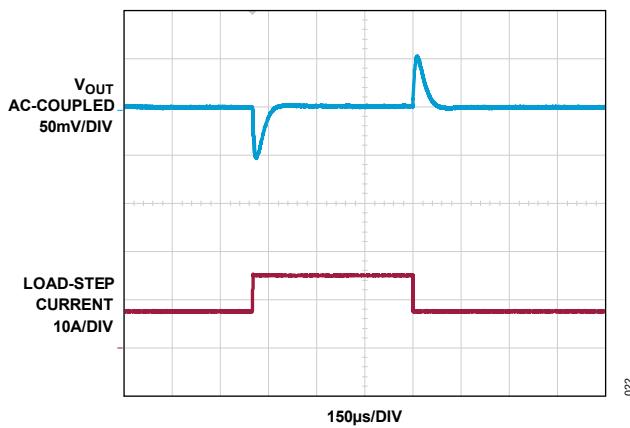

Figure 22. Output Transient Response, 1V

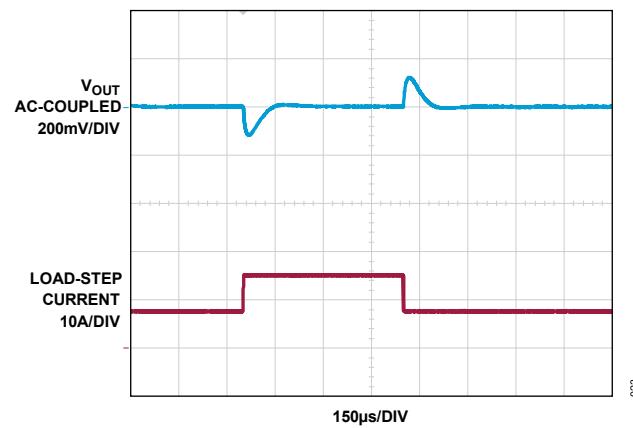

Figure 23. Output Transient Response, 5V

## THEORY OF OPERATION

### LTM4740 Overview

The LTM4740 is a single-phase point-of-load (POL) buck regulator with PMBus that can deliver up to 15A. The continuous current is determined by the internal operating temperature. It provides a precisely regulated output voltage, programmable through two external resistors from 0.4V to 5.5V. The input voltage range is 3V to 15V. Given that the LTM4740 is a step-down converter, make sure that the input voltage is high enough to support the desired output voltage and load current. See the simplified Block Diagram (*Figure 24*). The Analog Devices *LTpowerPlay*® graphical user interface (GUI), the *DC1613A* USB-to-PMBus adapter, and the *EVAL-LTM4740-AZ* evaluation board are available.

The LTM4740 contains a current mode controller, power switching elements, a power inductor, and a modest amount of input and output capacitance. The LTM4740 is a fixed-frequency pulse-width modulation (PWM) regulator. The switching frequency is set by simply connecting the appropriate resistor value from the PGM1 pin to GND. The LTM4740 features a selectable advanced modulation scheme (AMS) to provide improved performance during fast-load transients. Operation settings and configurable features can be selected by connecting pin-strap resistors from the PGMin pins to ground or using PMBus commands. See the *Applications Information* section for more details. An internal regulator provides power to control circuitry. To improve efficiency across all loads, supply current to the control circuitry can be sourced from an external 3.3V<sub>BIAS</sub>, instead of leaving BIAS floating. The EN pin is used to place the LTM4740 in operation or in shutdown. The LTM4740 can operate in forced continuous mode (FCM) for fast transient response and full-frequency operation across a wide load range. In FCM, the oscillator operates continuously, and positive SW transitions are aligned to the clock. Negative inductor current is allowed. The LTM4740 can sink current from the output and return this charge to the input in this mode, improving load-step transient response. To enhance efficiency at light load, the LTM4740 can operate in discontinuous-conduction mode (DCM) under light-load situations. The DCM is disabled by default; it can be enabled with PMBus commands. See the *Applications Information* section for more details.

The LTM4740 contains a power good comparator which trips when the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins voltage is within  $\pm 10\%$  of the typical value (for example: 0.5V, the PGOOD range is 0.45V to 0.55V). The PGOOD output is an open-drain transistor that is off when the output is regulated, allowing an external resistor to pull the PGOOD pin high. The LTM4740 is equipped with a thermal shutdown that inhibits power switching at high junction temperatures. The activation threshold of this function is above 125°C to avoid interfering with normal operation, so prolonged or repetitive operation under a condition in which the thermal shutdown activates may damage or impair the device's reliability. The LTM4740 does not support the parallel operation to produce higher currents.

### LTM4740 Major Features

- ▶ Forced continuous mode (FCM) and discontinuous-conduction mode (DCM) operation.

- ▶ Fixed frequency control loop.

- ▶ Configurable and programmable frequency from 500kHz to 2MHz.

- ▶ Selectable advanced modulation scheme (AMS) to improve transient response.

- ▶ High efficiency with an optional external bias input supply.

- ▶ Pin-strap programmability.

- ▶ PMBus telemetry of output current, output/input voltage, and junction temperature.

- ▶ PMBus adaptive voltage scaling (AVS) of 0.4V to 0.8V reference range.

- ▶ PMBus fault or warning monitoring for input/output undervoltage, overvoltage, overcurrent, overpower, and communication, memory, or logic (CML) faults.

## Simplified Block Diagram

Figure 24. LTM4740 Simplified Block Diagram

## Decoupling Requirements

Table 5. Decoupling Requirements

| SYMBOL    | PARAMETER                                                                      | CONDITIONS      | MIN | TYP | MAX | UNITS |

|-----------|--------------------------------------------------------------------------------|-----------------|-----|-----|-----|-------|

| $C_{IN}$  | External input capacitor requirement<br>( $V_{IN} = 12V$ , $V_{OUT} = 1.5V$ )  | $I_{OUT} = 15A$ | 10  | 22  |     | μF    |

| $C_{OUT}$ | External output capacitor requirement<br>( $V_{IN} = 12V$ , $V_{OUT} = 1.5V$ ) | $I_{OUT} = 15A$ | 200 | 300 |     | μF    |

## APPLICATIONS INFORMATION

For most applications, the design process is straightforward and is summarized below.

1. See [Table 6](#) and find the row that has the desired input range and output voltage.

2. Apply the recommended  $C_{IN}$  and  $C_{OUT}$  resistor values.

While these component combinations have been tested for proper operation, it is the user's responsibility to verify proper operation over the intended system's line, load, and environmental conditions. Remember that the maximum output current is limited by the junction temperature, the relationship between the input and output voltage magnitudes, the polarity, and other factors. See the graphs in the [Typical Performance Characteristics](#) section for guidance.

The recommended frequency (and the  $R_{PGM1}$  value) for optimal efficiency over the given input condition is shown in [Table 6](#).

**Table 6. Recommended Component Values and Configuration ( $T_A = 25^\circ\text{C}$ )**

| $V_{IN}$ (V) | $V_{OUT}$ (V) | $R_{FB1}$ (k $\Omega$ ) | $R_{FB2}$ (k $\Omega$ ) | $C_{IN}$ ( $\mu\text{F}$ ) | $C_{OUT}$ ( $\mu\text{F}$ ) | $f_{SW}$ (Hz) | $R_{PGM1}$ ( $\Omega$ ) |

|--------------|---------------|-------------------------|-------------------------|----------------------------|-----------------------------|---------------|-------------------------|

| 4.5 to 15    | 0.8           | 1.82                    | 3.01                    | 2 $\times$ 22 (25V)        | 4 $\times$ 100              | 500k          | 309                     |

| 4.5 to 15    | 1             | 3.01                    | 3.01                    | 2 $\times$ 22 (25V)        | 4 $\times$ 100              | 500k          | 309                     |

| 4.5 to 15    | 1.2           | 4.22                    | 3.01                    | 2 $\times$ 22 (25V)        | 4 $\times$ 100              | 750k          | 2.15k                   |

| 4.5 to 15    | 1.5           | 6.02                    | 3.01                    | 2 $\times$ 22 (25V)        | 4 $\times$ 100              | 750k          | 2.15k                   |

| 4.5 to 15    | 1.8           | 7.87                    | 3.01                    | 2 $\times$ 22 (25V)        | 4 $\times$ 100              | 1M            | 21.5k                   |

| 5 to 15      | 2.5           | 12.01                   | 3.01                    | 2 $\times$ 22 (25V)        | 4 $\times$ 100              | 1.2M          | 56.2k                   |

| 6.6 to 15    | 3.3           | 16.9                    | 3.01                    | 2 $\times$ 22 (25V)        | 4 $\times$ 100              | 1.2M          | 56.2k                   |

| 10.5 to 15   | 5             | 22.6                    | 2.49                    | 2 $\times$ 22 (25V)        | 4 $\times$ 100              | 2M            | 115k                    |

## Capacitor Selection Considerations

The  $C_{IN}$  and  $C_{OUT}$  capacitor values in [Table 6](#) are the minimum recommended values for the associated operating conditions. Applying capacitor values below those indicated in [Table 6](#) is not recommended and may result in undesirable operation. Using larger values is generally acceptable and can yield improved dynamic response if necessary. Again, the user is responsible for verifying the proper operation conditions over the intended system's line, load, and environmental conditions.

Ceramic capacitors are small, robust, and have very low ESR. However, not all ceramic capacitors are suitable. The X5R and X7R types are stable over temperature and applied voltage, and provide dependable service. Other types, including Y5V and Z5U, have very large temperature and voltage-coefficients of capacitance. In an application circuit, they may have only a small fraction of their nominal capacitance, resulting in much higher output voltage ripple than expected. Ceramic capacitors are also piezoelectric. In DCM operation, the LTM4740's switching frequency depends on the load current, and can stimulate a ceramic capacitor at audio frequencies, generating audible noise. Only if DCM is enabled, the LTM4740 may skip pulses during light load conditions. If this occurs, the effective switching frequency could be lowered enough to operate in the audible frequency range. During this scenario, the LTM4740 operates with a lower current limit, which helps suppress audible noise. If this audible noise is unacceptable, use a high-performance electrolytic capacitor at the output. It may also be a parallel combination of a ceramic capacitor and a low-cost electrolytic capacitor. A final precaution regarding ceramic capacitors concerns the maximum input voltage rating of the LTM4740. A ceramic input capacitor combined with trace or cable inductance forms a high-Q (underdamped) tank circuit. If the LTM4740 circuit is plugged into a live supply,

the input voltage can ring to twice its nominal value, possibly exceeding the device's rating. This situation can be easily avoided; see the [Hot-Plugging Safely](#) subsection for more details.

## Pin-Strap Programmability

The LTM4740 has two program pins (PGM0 and PGM1) that set some of the key device configurations (see [Table 7](#) and [Table 8](#) for more details). The PGMn pin values are read during startup initialization. Each PGM0 and PGM1 pin has 32 detection levels. A pin-strap resistor is connected from the PGMn pin to AGND to select one of the 32 codes. The PGM0 is used to select the POC level and PMBus address. The PGM1 pin selects the switching frequency and a predefined scenario, which corresponds to the voltage loop gain and the advanced modulation scheme (AMS) selection. Predefined scenarios are summarized in [Table 9](#).

**Table 7. PGM0, POC, and PMBus Address Selection**

| CODES | $R_{PGM0}$ ( $\Omega$ ) | POC (A) | PMBus ADDRESS |

|-------|-------------------------|---------|---------------|

| 0     | 95.3                    | 20      | 0x38h         |

| 1     | 200                     |         | 0x39h         |

| 2     | 309                     |         | 0x3Ah         |

| 3     | 422                     |         | 0x3Bh         |

| 4     | 536                     |         | 0x3Ch         |

| 5     | 649                     |         | 0x3Dh         |

| 6     | 768                     |         | 0x3Eh         |

| 7     | 909                     |         | 0x3Fh         |

| 8     | 1.05k                   | 17.3    | 0x38h         |

| 9     | 1.21k                   |         | 0x39h         |

| 10    | 1.4k                    |         | 0x3Ah         |

| 11    | 1.62k                   |         | 0x3Bh         |

| 12    | 1.87k                   |         | 0x3Ch         |

| 13    | 2.15k                   |         | 0x3Dh         |

| 14    | 2.49k                   |         | 0x3Eh         |

| 15    | 2.87k                   |         | 0x3Fh         |

| 16    | 3.74k                   | 14.6    | 0x38h         |

| 17    | 8.06k                   |         | 0x39h         |

| 18    | 12.4k                   |         | 0x3Ah         |

| 19    | 16.9k                   |         | 0x3Bh         |

| 20    | 21.5k                   |         | 0x3Ch         |

| 21    | 26.1k                   |         | 0x3Dh         |

| 22    | 30.9k                   |         | 0x3Eh         |

| 23    | 36.5k                   |         | 0x3Fh         |

| 24    | 42.2k                   | 12      | 0x38h         |

| 25    | 48.7k                   |         | 0x39h         |

| 26    | 56.2k                   |         | 0x3Ah         |

| 27    | 64.9k                   |         | 0x3Bh         |

| 28    | 75k                     |         | 0x3Ch         |

| 29    | 86.6k                   |         | 0x3Dh         |

| 30    | 100k                    |         | 0x3Eh         |

| 31    | 115k                    |         | 0x3Fh         |

**Table 8. PGM1 Switching Frequency and Scenario Selection**

| CODES | R <sub>PGM1</sub> (Ω) | SWITCHING FREQUENCY (Hz) | SCENARIO # |

|-------|-----------------------|--------------------------|------------|

| 0     | 95.3                  | 500k                     | A          |

| 1     | 200                   |                          | B          |

| 2     | 309                   |                          | C          |

| 3     | 422                   |                          | D          |

| 4     | 536                   |                          | E          |

| 5     | 649                   |                          | F          |

| 6     | 768                   | 600k                     | A          |

| 7     | 909                   |                          | B          |

| 8     | 1.05k                 |                          | C          |

| 9     | 1.21k                 |                          | D          |

| 10    | 1.4k                  |                          | E          |

| 11    | 1.62k                 |                          | F          |

| 12    | 1.87k                 | 750k                     | A          |

| 13    | 2.15k                 |                          | B          |

| 14    | 2.49k                 |                          | C          |

| 15    | 2.87k                 |                          | D          |

| 16    | 3.74k                 |                          | E          |

| 17    | 8.06k                 |                          | F          |

| 18    | 12.4k                 | 1M                       | A          |

| 19    | 16.9k                 |                          | B          |

| 20    | 21.5k                 |                          | C          |

| 21    | 26.1k                 |                          | D          |

| 22    | 30.9k                 |                          | E          |

| 23    | 36.5k                 |                          | F          |

| 24    | 42.2k                 | 1.2M                     | A          |

| 25    | 48.7k                 |                          | B          |

| 26    | 56.2k                 |                          | C          |

| 27    | 64.9k                 |                          | D          |

| 28    | 75k                   |                          | E          |

| 29    | 86.6k                 |                          | F          |

| 30    | 100k                  | 2M                       | A          |

| 31    | 115k                  |                          | B          |

The LTM4740 has six predefined scenarios as summarized in [Table 9](#), which can be selected by a pin-strap resistor connected from the PGM1 pin to AGND. See the [Voltage Loop Gain](#) section for information on selecting the voltage loop gain resistance ( $R_{VGA}$ ) to optimize the control loop performance. For each scenario, the advanced modulation scheme (AMS) option can also be selected.

**Table 9. Predefined Scenarios**

| SCENARIO # | $R_{VGA}$ (kΩ) | AMS OPTION |

|------------|----------------|------------|

| A          | 15.7           | Disabled   |

| B          | 22.7           | Disabled   |

| C          | 15.7           | Enabled    |

| D          | 22.7           | Enabled    |

| E          | 31.3           | Enabled    |

| F          | 44.8           | Enabled    |

## PMBus Interface

The PMBus is an industry standard that defines a means of communication with power conversion devices. It is comprised of an industry-standard SMBus serial interface and the PMBus command language. The LTM4740 supports the PMBus interface to communicate with a host (controller) device. The device PMBus address is selected by a pin-strap resistor connected from the PGM0 pin to AGND (see the [Pin-Strap Programmability](#) subsection for more details). [Table 10](#) shows the supported PMBus commands. Refer to the [User Reference Manual](#) for complete details.

**Table 10. Supported PMBus Commands**

| COMMAND CODE | COMMAND NAME  | DESCRIPTION                                                                 | TYPE      | DATA FORMAT | FACTORY VALUE |

|--------------|---------------|-----------------------------------------------------------------------------|-----------|-------------|---------------|

| 0x01         | OPERATION     | Output enable/disable.                                                      | R/W byte  | Bit field   | 0x80          |

| 0x02         | ON_OFF_CONFIG | EN pin and PMBus operation command setting.                                 | R/W byte  | Bit field   | 0x1F          |

| 0x03         | CLEAR_FAULTS  | Clear any fault bits that have been set.                                    | Send byte |             | N/A           |

| 0x10         | WRITE_PROTECT | Level of protection provided by the device against accidental changes.      | R/W byte  | Bit field   | 0x20          |

| 0x19         | CAPABILITY    | Summary of PMBus optional communication protocols supported by the LTM4740. | R byte    | Bit field   | 0xA0          |

| 0x20         | VOUT_MODE     | Output voltage data format and mantissa exponent.                           | R byte    | Bit field   | 0x17          |

| 0x21         | VOUT_COMMAND  | Feedback reference voltage setpoint.                                        | R/W word  | ULINEAR16   | 0x0100        |

| COMMAND CODE | COMMAND NAME        | DESCRIPTION                                           | TYPE     | DATA FORMAT | FACTORY VALUE       |

|--------------|---------------------|-------------------------------------------------------|----------|-------------|---------------------|

| 0x24         | VOUT_MAX            | Upper limit of reference voltage setpoint.            | R/W word | ULINEAR16   | 0x019A              |

| 0x78         | STATUS_BYTE         | One-byte summary of the unit's fault condition.       | R byte   | Bit field   | N/A                 |

| 0x79         | STATUS_WORD         | A two-byte summary of the unit's fault condition.     | R word   | Bit field   | N/A                 |

| 0x7A         | STATUS_VOUT         | Output voltage fault and warning status.              | R byte   | Bit field   | N/A                 |

| 0x7B         | STATUS_IOUT         | Output current fault and warning status.              | R byte   | Bit field   | N/A                 |

| 0x7C         | STATUS_INPUT        | Input voltage fault and warning status.               | R byte   | Bit field   | N/A                 |

| 0x7D         | STATUS_TEMPERATURE  | Device junction temperature fault and warning status. | R byte   | Bit field   | N/A                 |

| 0x7E         | STATUS_CML          | Communication fault and warning status.               | R byte   | Bit field   | N/A                 |

| 0x80         | STATUS_MFR_SPECIFIC | Manufacturing specific faults and warning status.     | R byte   | Bit field   | N/A                 |

| 0x88         | READ_VIN            | Input voltage telemetry.                              | R word   | LINEAR11    | N/A                 |

| 0x8B         | READ_VOUT           | Feedback voltage telemetry.                           | R word   | ULINEAR16   | N/A                 |

| 0x8C         | READ_IOUT           | Output current telemetry.                             | R word   | LINEAR11    | N/A                 |

| 0x8D         | READ_TEMPERATURE_1  | Device junction temperature telemetry.                | R word   | LINEAR11    | N/A                 |

| 0xAD         | IC_DEVICE_ID        | Device root part number.                              | R block  | ASCII       | "LTM4740"           |

| 0xAE         | IC_DEVICE_REV       | Device revision code.                                 | R block  | ASCII       | N/A                 |

| 0xD0         | MFR_PINSTRAP        | Manufacture specific device operating configurations. | R/W byte | Bit field   | PGM0/PGM1 dependent |

| 0xD1         | MFR_SCENARIO_0      | Manufacture specific device operating configurations. | R/W byte | Bit field   | PGM1 dependent      |

| 0xD2         | MFR_SCENARIO_1      | Manufacture specific device operating configurations. | R/W byte | Bit field   | PGM1 dependent      |

| 0xD3         | MFR_SCENARIO_2      | Manufacture specific device operating configurations. | R/W byte | Bit field   | N/A                 |

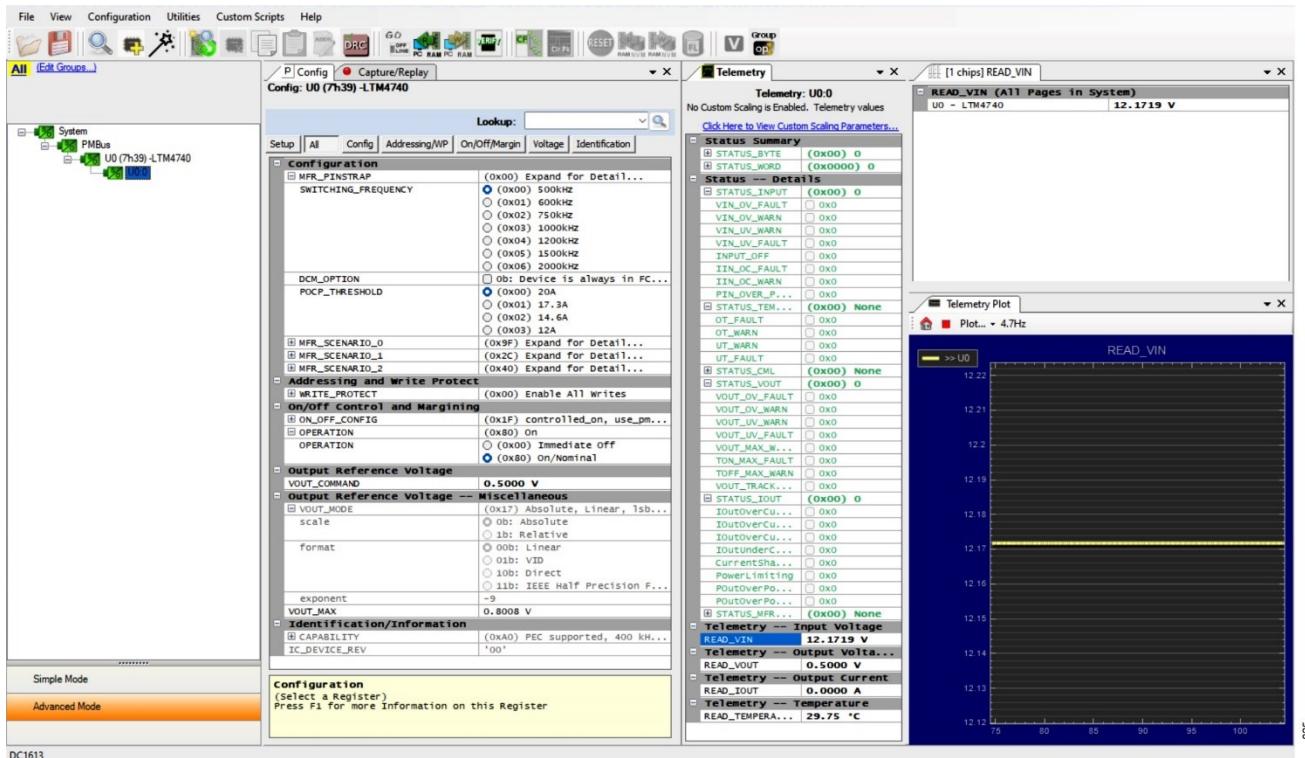

## LTPowerPlay: An Interactive GUI for Digital Power Management

The LTPowerPlay® is a powerful Windows-based development environment that supports Analog Devices digital power system management (PSM) devices, including the LTM4740. See [Figure 25](#) for the LTPowerPlay main interface.

The LTPowerPlay can be used to evaluate Analog Devices ICs by connecting to an evaluation board or to the user application. The LTPowerPlay design software supports a variety of tasks. It can also be used in offline mode (with no hardware present) to build multiple device configuration files that can be saved and reloaded later. The LTPowerPlay provides unprecedented diagnostic and debugging features. It becomes a valuable diagnostic tool during board bring-up to program or tweak the power system, or to diagnose power issues during rail bring-up. The LTPowerPlay utilizes the Analog Devices USB-to-I<sup>2</sup>C/SMBus/PMBus [DC1613A](#) adapter to communicate with one of the many potential targets, including the Analog Devices [EVAL-LTM4740-AZ](#) evaluation board. The software also provides an automatic update feature to keep revisions up to date with the latest set of device drivers and documentation. A great deal of context-sensitive help is available with LTPowerPlay, along with several tutorial demos. Refer to the Analog Devices [LTPowerPlay](#) web page for complete information.

Figure 25. LTPowerPlay Main Interface

## Frequency Selection

The LTM4740 uses a constant frequency pulse-width modulation (PWM) architecture that can be programmed to switch from 500kHz to 2MHz by using a resistor connected from the PGM1 pin to ground. For more details, see [Table 8](#).

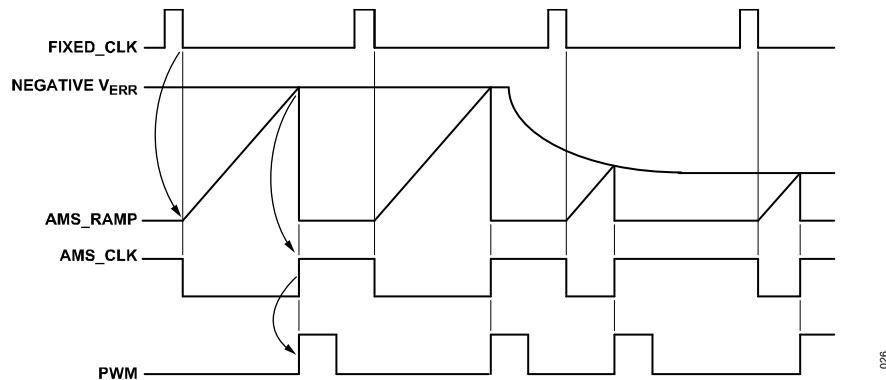

## Advanced Modulation Scheme

The LTM4740 offers a selectable advanced modulation scheme (AMS) to provide improved transient response. The AMS provides a significant advantage over conventional fixed-frequency PWM schemes. Enabling the AMS feature allows for modulation at both the leading and trailing edges, resulting in a temporary increase or decrease of the switching frequency during large load transients. [Figure 26](#) shows the scheme to include leading-edge modulation to the traditional trailing-edge modulation when AMS is enabled in the LTM4740.

The modulation scheme allows the turn on and off with minimal delay. Since the total inductor current increases quickly, satisfying the load demand, the current drawn from the output capacitors is reduced. With AMS enabled, the system's closed-loop bandwidth can be extended without a phase-margin penalty. As a result, the output capacitance can be minimized.

**Figure 26. Advanced Modulation Scheme Operation**

## Output Voltage Sensing

The LTM4740 has a default 0.5V reference voltage. The reference voltage can be adjusted by the PMBus VOUT\_COMMAND from 0.4V to 0.8V with a 1.95mV resolution. When the desired output voltage is higher than  $V_{REF}$ , it is required to use a resistor divider,  $R_{FB1}$  and  $R_{FB2}$ , to sense the output voltage. It is recommended that the value  $R_{FB2}$  does not exceed 5k $\Omega$ . The resistor-divider ratio is given by Equation 1.

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_{FB1}}{R_{FB2}}\right) \quad (1)$$

Where:

$V_{OUT}$  is the output voltage.

$V_{REF}$  is the reference voltage.

$R_{FB1}$  is the top divider resistor.

$R_{FB2}$  is the bottom divider resistor.

## Operating Frequency Trade-Offs

It is recommended that the user apply the optimal  $R_{PGM1}$  value as shown in [Table 6](#) for the input and output operating conditions. System-level or other considerations, however, may necessitate another operating frequency. While the LTM4740 is flexible enough to accommodate a wide range of operating frequencies, a haphazardly chosen one may result in undesirable operation under certain operating or fault conditions. A frequency that is too high can reduce efficiency, generate excessive heat, or even damage the LTM4740 if the output is overloaded or short-circuited. A frequency that is too low can result in a final design with too much output ripple or too large of an output capacitor.

The LTM4740 internally has a slope compensation applied to the current loop during on-time to guarantee stability and improve noise immunity. To avoid the slope compensation saturating the current loop, it is required that the maximum on-time be limited using [Equation 2](#).

$$t_{ON(MAX)} = \frac{5pF \left[ 800mV - \left( I_{OUT(MAX)} + \frac{I_{RIPPLE}}{2} \right) \times \frac{1.6\Omega}{62.5} \right]}{I_{SLOPE}} \quad (2)$$

where:

$t_{ON(MAX)}$  is the maximum on-time of the high-side MOSFET.

$I_{OUT(MAX)}$  is the maximum load current.

$I_{RIPPLE}$  is the inductor current ripple peak-to-peak value.

$I_{SLOPE}$  is the internal slope compensation amplitude. The default value is  $3.78\mu A$ , and the value can be adjusted by the PMBus MFR\_SCENARIO\_0 command.

The minimum recommended switching frequency is calculated with [Equation 3](#).

$$f_{SW(MIN)} = \frac{V_{OUT}}{t_{ON(MAX)} \times V_{IN(MIN)}} \quad (3)$$

where:

$f_{SW(MIN)}$  is the minimum selectable switching frequency.

Because of system noise injection, even at steady-state operation, typically the SW rising and falling edges would have some random jittering noise. The selection of the switching frequency ( $f_{SW}$ ) should take into consideration the jittering and be higher than  $f_{SW(MIN)}$  and lower than  $f_{SW(MAX)}$ . To improve the SW jittering, it is recommended to use smaller inductor values and lower voltage loop gain to minimize the noise sensitivity.

It is required that the frequency be selected so that the minimum controllable on-time and minimum controllable off-time are not violated. The maximum recommended switching frequency is calculated by [Equation 4](#).

$$f_{SW(MAX)} = \text{MIN} \left\{ \frac{V_{OUT}}{t_{ON(MIN)} \times V_{IN(MAX)}}, \frac{V_{IN(MIN)} - V_{OUT}}{t_{OFF(MIN)} \times V_{IN(MIN)}} \right\} \quad (4)$$

where:

$f_{SW(MAX)}$  is the maximum selectable switching frequency.

$V_{IN(MAX)}$  is the maximum input voltage.

$V_{IN(MIN)}$  is the minimum input voltage.

$t_{ON(MIN)}$  is the minimum controllable on-time.

$t_{OFF(MIN)}$  is the minimum controllable off-time.

## Maximum Load

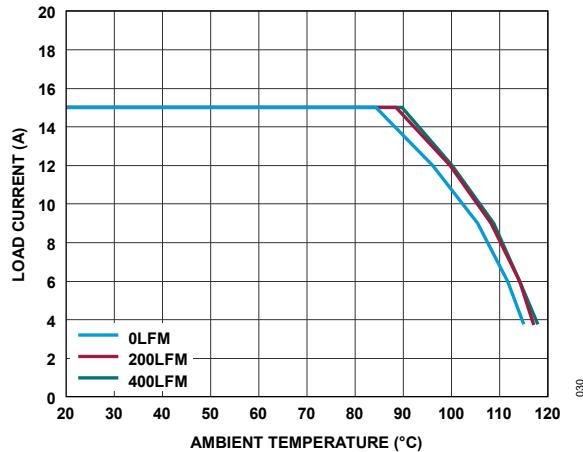

The maximum practical continuous load that the LTM4740 can drive, while rated at 15A, depends upon both the internal current limit and the internal temperature. The internal current limit is designed to prevent damage to the LTM4740 in the case of an overload or a short circuit. The internal temperature of the LTM4740 depends upon operating conditions, such as the ambient temperature, the power delivered, and the heat-sinking capability of the system. For example, if the LTM4740 is configured to regulate at 1V, it may continuously deliver 15A from 12V<sub>IN</sub> if the ambient temperature is controlled to less than 60°C. See [Figure 30](#) and [Figure 31](#), derating curves, for the V<sub>OUT</sub> = 1V condition. Similarly, if the output voltage is 5V and the ambient temperature is 85°C, the LTM4740 will deliver at most 8.5A from 12V<sub>IN</sub>, which is less than the 15A continuous rating, as shown in [Figure 38](#) derating curve.

## Voltage Loop Gain

For stability purposes, it is recommended that the voltage loop bandwidth (BW) be lower than 1/5 of the switching frequency. Consider the case of using multi-layer ceramic capacitor (MLCC) output capacitors, which have nearly ideal impedance characteristics in the frequency range of interest, with negligible ESR and Equivalent Series Inductance (ESL). The voltage loop BW can be estimated with the Equation 5.

$$BW = \frac{\frac{R_{FB2}}{R_{FB2} + R_{FB1}} \times \frac{R_{VGA}}{10k\Omega}}{2\pi \times 8m\Omega \times C_{OUT}} \quad (5)$$

where:

R<sub>VGA</sub> = The voltage loop gain resistance, which is set by the scenario selected (see [Table 9](#)).

## Minimum Input Voltage

The LTM4740 is a step-down converter, so a minimum amount of headroom is required to keep the output in regulation. Keep V<sub>IN</sub> above 3V to ensure proper operation.

## Prebiased Output

The LTM4740 regulates the output to the SENSE<sup>+</sup> and SENSE<sup>-</sup> voltage. If the LTM4740 output is higher than the target output voltage, the LTM4740 will attempt to regulate the output to the target voltage by returning a small amount of energy back to the input supply. If there is nothing loading the input supply, its voltage may rise. Take care that it does not rise so high that the input voltage exceeds the absolute maximum rating of the LTM4740.

## Discontinuous-Conduction Mode Operation

The discontinuous-conduction mode (DCM) operation is an optional feature that improves light-load efficiency. The device has a DCM current-detection comparator to monitor the inductor valley current while operating in forced continuos mode (FCM). At light load, if the inductor valley current is below the DCM comparator threshold for 56 consecutive cycles, the LTM4740 transitions seamlessly to DCM. Once in DCM, the switching frequency decreases as the load decreases. The device transitions back to FCM operation as soon as the inductor valley current is higher than 0A. For LTM4740, the DCM is by default disabled; it can be enabled with PMBus commands.

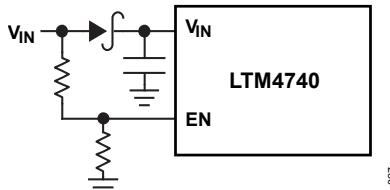

## Shorted Input Protection

Care needs to be taken in systems where the output is held high when the power input to the LTM4740 is absent. This may occur in battery charging applications or in battery backup systems where a battery or some other supply is diode OR-ed with the LTM4740's output. If the V<sub>IN</sub> pin is allowed to float and the EN pin is held high (either by a logic signal or because it is connected to V<sub>IN</sub>), then the LTM4740's internal circuitry pulls its quiescent current through its internal power switch. This is fine if your system can tolerate a few millamps in this state. If you ground the EN pin, the internal current drops to essentially zero. However, if the V<sub>IN</sub> pin is grounded while the output is held

high, parasitic diodes inside the LTM4740 can pull large currents from the output through the  $V_{IN}$  pin. [Figure 27](#) shows a circuit that runs only when the input voltage is present, and that protects against a shorted or reversed input. The input diode prevents a shorted input from discharging a backup battery connected to the output. It also protects the circuit from a reversed input. The LTM4740 runs only when the input is present.

027

**Figure 27. Shorted Input Protection from a Reversed Input**

## Fault Handling

The LTM4740 features comprehensive fault detection and handling mechanisms to protect both the device and the load. The LTM4740 monitors conditions such as overcurrent (OC), overvoltage (OV), undervoltage (UV), overtemperature (OT), and short-circuit faults. Upon detecting a fault, the device can respond by shutting down or entering safe mode, depending on the configuration. Fault status is communicated via the PMBus, allowing the host (controller) to identify and take corrective action.

### Input Undervoltage Lockout

The LTM4740 internally monitors the  $V_{IN}$  voltage level. When the input supply voltage is below the undervoltage lockout (UVLO) threshold, the device stops switching and drives the PGOOD pin low. The device restarts after 20ms if the UVLO status is cleared.

### Output Overvoltage Protection

The feedback voltage on  $V_{SENSE}^+$  and  $V_{SENSE}^-$  is monitored for the output overvoltage once the soft start ramp is complete. If the feedback voltage is above the overvoltage (OV) protection threshold beyond the OV deglitch filtering delay, the device stops switching and drives PGOOD pin low. The device restarts after 20ms if the OV status is cleared.

### Positive Overcurrent Protection

The LTM4740's peak current mode control architecture provides inherent current limiting and short-circuit protection. The inductor current is continuously monitored while switching. The inductor peak current is limited on a cycle-by-cycle basis. In each switching cycle, once the sensed inductor current exceeds the overcurrent (OC) protection threshold, the device turns off the high-side MOSFET and turns on the low-side MOSFET to allow the inductor current to be discharged by the output voltage. An up-down counter accumulates the number of consecutive OC events in each switching cycle. If the counter exceeds 1024, the device stops switching and drives the PGOOD pin low. The OC is a hiccup protection, and the device restarts after 20ms.

The LTM4740 offers four OC thresholds (20A, 17.3A, 14.6A, and 12A), which can be selected by the PGM0 pin (see the [Pin-Strap Programmability](#)). Because of the OC deglitch delay, for a specific application use case, the actual OC threshold should be higher.

Besides the current limiting OC protection, the device also features a fast positive overcurrent (FPOC) protection, which is intended to protect extreme overcurrent conditions, including inductor short or saturation. The FPOC has a threshold of 25A. Once the sensed inductor current exceeds the FPOC threshold, the device stops switching, drives the PGOOD pin low, and latches the device. It requires cycling power to clear the latched FPOC fault and resume operation.

## Negative Overcurrent Protection

The device also has negative overcurrent (NOC) protection against inductor valley current. The NOC threshold is –83% of the POC threshold. In each switching cycle, once the sensed inductor current exceeds the NOC threshold, the device turns off the low-side MOSFET and turns on the high-side MOSFET for a fixed 180ns time to allow the inductor current to be charged by the input voltage. Same as the POC, an up-down counter is used to accumulate the number of consecutive NOC events. If the counter exceeds 1024, the device stops switching, and drives the PGOOD pin low. The NOC is a hiccup protection and the device restarts after 20ms.

## Overtemperature Protection

The overtemperature (OT) protection threshold is 155°C with 20°C hysteresis. If the junction temperature reaches OT threshold during operation, the device stops switching and drives the PGOOD pin low. The device restarts after 20ms if the OT status is cleared.

## Hot-Plugging Safely

The small size, robustness, and low impedance of ceramic capacitors make them an attractive option for the input bypass capacitor of LTM4740. However, these capacitors can cause problems if the LTM4740 is plugged into a live supply (Refer to the Analog Devices [Application Note 88](#) for a complete discussion). The low-loss ceramic capacitor, combined with stray inductance in series with the power source, forms an underdamped tank circuit, and the voltage at the  $V_{IN}$  pins of the LTM4740 can ring to more than twice the nominal input voltage, possibly exceeding the LTM4740's rating and damaging the part. If the input supply is poorly controlled or the LTM4740 is hot-plugged into an energized supply, the input network should be designed to prevent this overshoot. This can be accomplished by installing a small resistor in series to  $V_{IN}$ , but the most popular method of controlling input voltage overshoot is adding an electrolytic bulk cap to the  $V_{IN}$  net. This capacitor's relatively high equivalent series resistance damps the circuit and eliminates the voltage overshoot. The extra capacitor improves low-frequency ripple filtering and can slightly improve the efficiency of the circuit, though it is likely to be the largest component in the circuit.

## Safety Consideration

The LTM4740 modules do not provide galvanic isolation from  $V_{IN}$  to  $V_{OUT}$ . There is no internal fuse. If required, a slow-blow fuse with a rating twice the maximum input current needs to be provided to protect each unit from catastrophic failure. The device does support thermal shutdown and overcurrent protection.

## Thermal Considerations and Output Current Derating

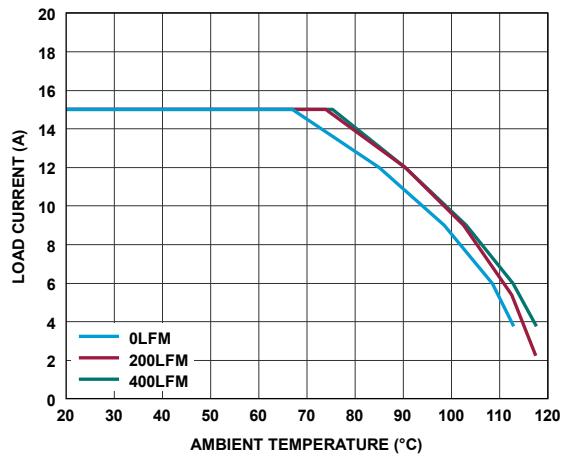

The LTM4740 output current may need to be derated if it is required to operate in a high ambient temperature. The amount of current derating depends on the input voltage, output power, and ambient temperature. The derating curves, [Figure 30](#) through [Figure 38](#), can be used as a guide. These curves were generated by the LTM4740 mounted to a 58cm<sup>2</sup> 4-layer FR4 printed circuit board. Boards of different sizes and layer count can exhibit different thermal behavior, so it is incumbent upon the user to verify proper operation over the intended system's line, load, and environmental operating conditions.

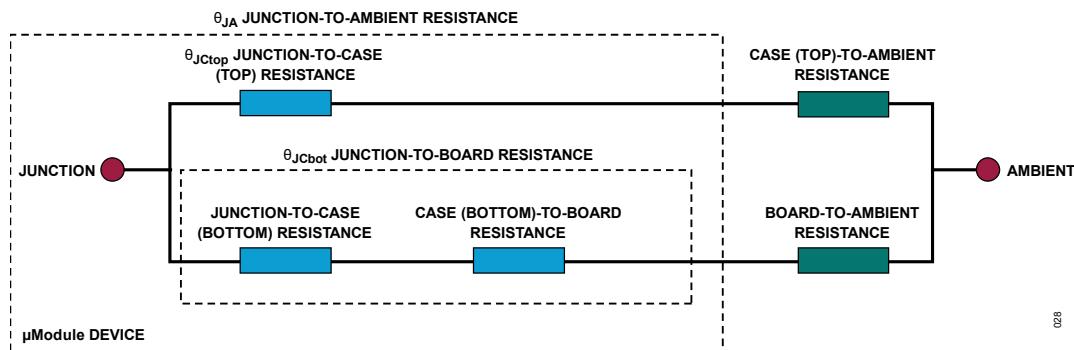

For increased accuracy and fidelity to the actual application, many designers use thermal simulation software to predict thermal performance. The [Pin Configurations and Function Descriptions](#) section typically gives the following four thermal coefficients.

1.  $\theta_{JA}$  – Thermal resistance from junction to ambient through the bottom of the package case to the board, see [Figure 28](#).

2.  $\theta_{JCbot}$  – Thermal resistance from junction.

3.  $\theta_{JCtop}$  – Thermal resistance from junction to top of the package case.

While the meaning of each of these coefficients may seem intuitive, JEDEC has defined them to avoid confusion and inconsistency. The following definitions are taken from JESD5112 and are presented in quoted or paraphrased form.

1.  $\theta_{JA}$  is the natural convection junction-to-ambient air thermal resistance measured in a one cubic foot sealed enclosure. This environment is sometimes referred to as still air, although natural convection causes the air to move. This value is determined with the part mounted to a JESD519-defined test board, which does not reflect an actual application or a viable operating condition.

2.  $\theta_{JCbot}$  is the junction-to-board thermal resistance with all the component power dissipation flowing through the bottom of the package. In a typical  $\mu$ Module regulator, the bulk of the heat flows out of the bottom of the package, but there is always heat flow out into the ambient environment. As a result, this thermal resistance value may be useful for comparing packages, but the test conditions don't generally match the user's application.

3.  $\theta_{JCtop}$  is determined with nearly all the component power dissipation flowing through the top of the package. As the electrical connections of the typical  $\mu$ Module regulator are on the bottom of the package, it is rare for an application to operate in which most of the heat flows from the junction to the top of the part. As in the case of  $\theta_{JCbot}$ , this value may be useful for comparing packages, but the test conditions don't generally match the user's application.

Given these definitions, it should now be apparent that none of these thermal coefficients reflects an actual physical operating condition of a  $\mu$ Module regulator. Thus, none of them can be used individually to accurately predict the product's thermal performance. Likewise, it would be inappropriate to attempt to use any one coefficient to correlate with the junction temperature vs load graphs given in the product's data sheet. The only appropriate way to use the coefficients is when running a detailed thermal analysis, such as finite element analysis (FEA), which considers all the thermal resistances simultaneously.

A graphical representation of these thermal resistances is given in *Figure 28*. The blue resistances are contained within the  $\mu$ Module regulator, and the green are outside.

*Figure 28. Graphical Representation of the Thermal Resistance between the Device Junction and Ambient, Including JESD5112 Terms*

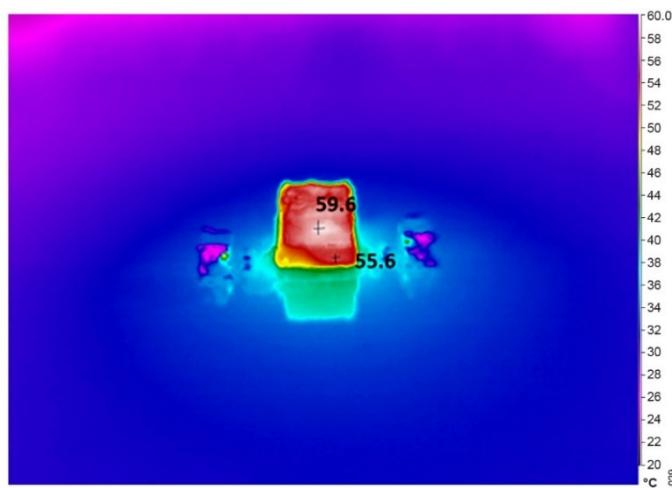

*Figure 29* shows a temperature plot of the LTM4740 with 12V input, 500kHz, 1V output at 15A without heat sink and a no airflow condition.

Figure 29. Thermal Image at  $12V_{IN}$ , 1V, 15A Output, No Airflow and Heat Sink,  $T_A = 25^\circ C$ .

The die temperature of the LTM4740 must be lower than the maximum rating of  $125^\circ C$ , so care should be taken in the layout of the circuit to ensure good heat sinking of the LTM4740. The bulk of the heat from the LTM4740 flows out through the bottom of the package and the pads into the PCB. Consequently, a poorly designed printed circuit board can cause excessive heating, resulting in impaired performance or reliability. See the [PCB Layout Recommendations](#) section for PCB design suggestions.

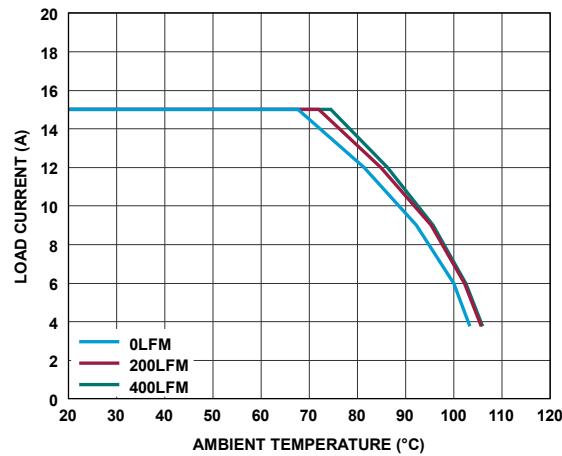

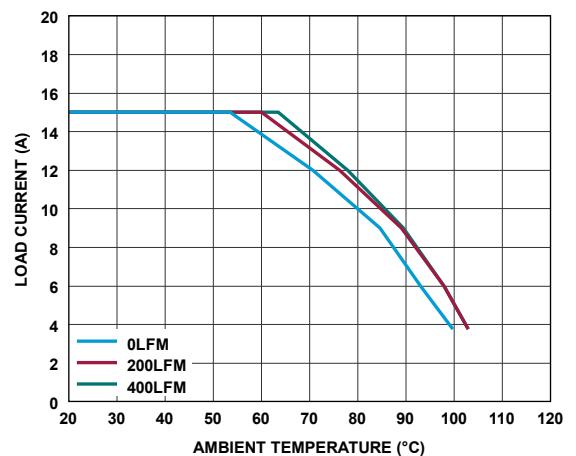

## Thermal Derating Curves

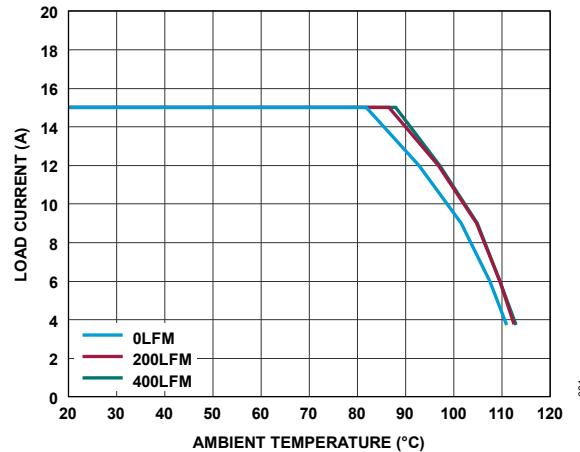

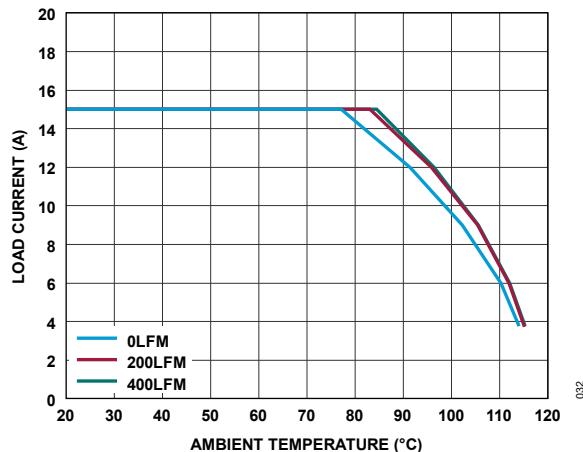

The thermal derating curves in *Figure 30* through *Figure 38* can be used to calculate approximate values of  $\theta_{JA}$  thermal resistance with various airflow conditions.

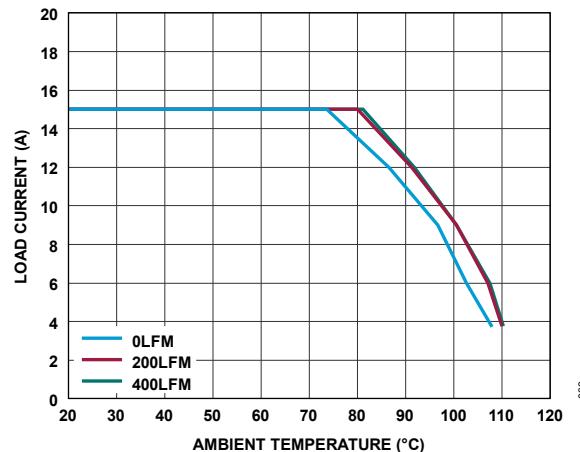

**Figure 30. Derating Curve, No Heat Sink,**

$V_{IN} = 5V$ ,  $V_{OUT} = 1V$ ,  $f_{SW} = 500kHz$

**Figure 31. Derating Curve, No Heat Sink,**

$V_{IN} = 12V$ ,  $V_{OUT} = 1V$ ,  $f_{SW} = 500kHz$

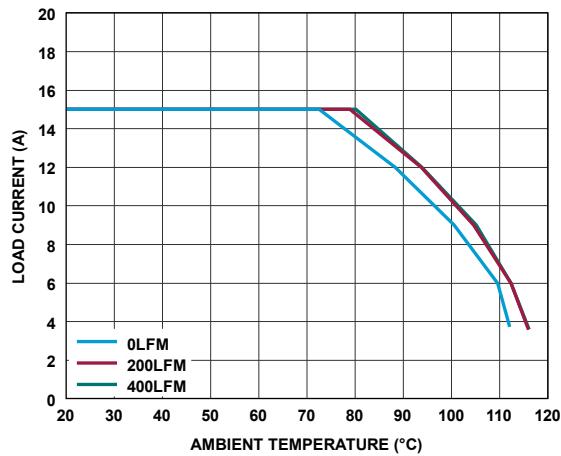

**Figure 32. Derating Curve, No Heat Sink,**

$V_{IN} = 5V$ ,  $V_{OUT} = 1.8V$ ,  $f_{SW} = 1MHz$

**Figure 33. Derating Curve, No Heat Sink,**

$V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$ ,  $f_{SW} = 1MHz$

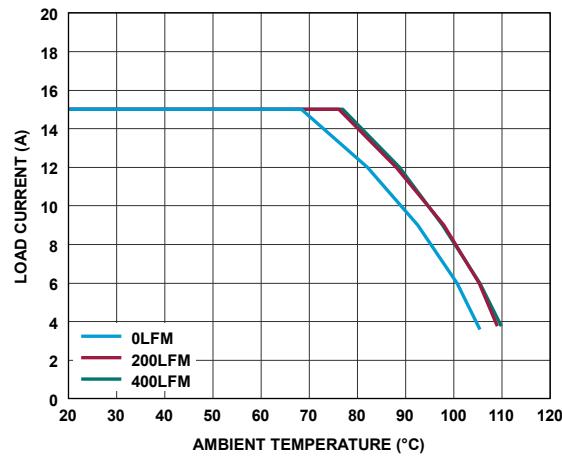

**Figure 34. Derating Curve, No Heat Sink,**

$V_{IN} = 5V$ ,  $V_{OUT} = 2.5V$ ,  $f_{SW} = 1.2MHz$

**Figure 35. Derating Curve, No Heat Sink,**

$V_{IN} = 12V$ ,  $V_{OUT} = 2.5V$ ,  $f_{SW} = 1.2MHz$