## 5V<sub>IN</sub>, 33A High-Density Step-Down DC-to-DC μModule Regulator with I<sup>2</sup>C and Integrated Capacitors

### FEATURES

- ▶ Highest Output Current to Total Solution Footprint (1A/mm<sup>2</sup>), Integrates all C<sub>INS</sub>, C<sub>OUTS</sub>, and Inductors

- ▶ Fast Transient Response

- ▶ V<sub>IN</sub> Range: 2.9V to 5.5V

- ▶ V<sub>OUT</sub> Range: 0.3V to 1V

- ▶ Remote Differential Output Sense Pins

- ▶ V<sub>OUT</sub><sup>+</sup> DC accuracy:  $\pm 1\%$

- ▶ I<sup>2</sup>C Serial Interface—Telemetry Readback Includes V<sub>OUT</sub>, I<sub>OUT</sub>, V<sub>IN</sub>, and Die Temperature

- ▶ Analog IMON pin for Output Current Monitoring

- ▶ Fixed Clock Frequency of 5MHz, External SYNC from 4.5MHz to 5.5MHz

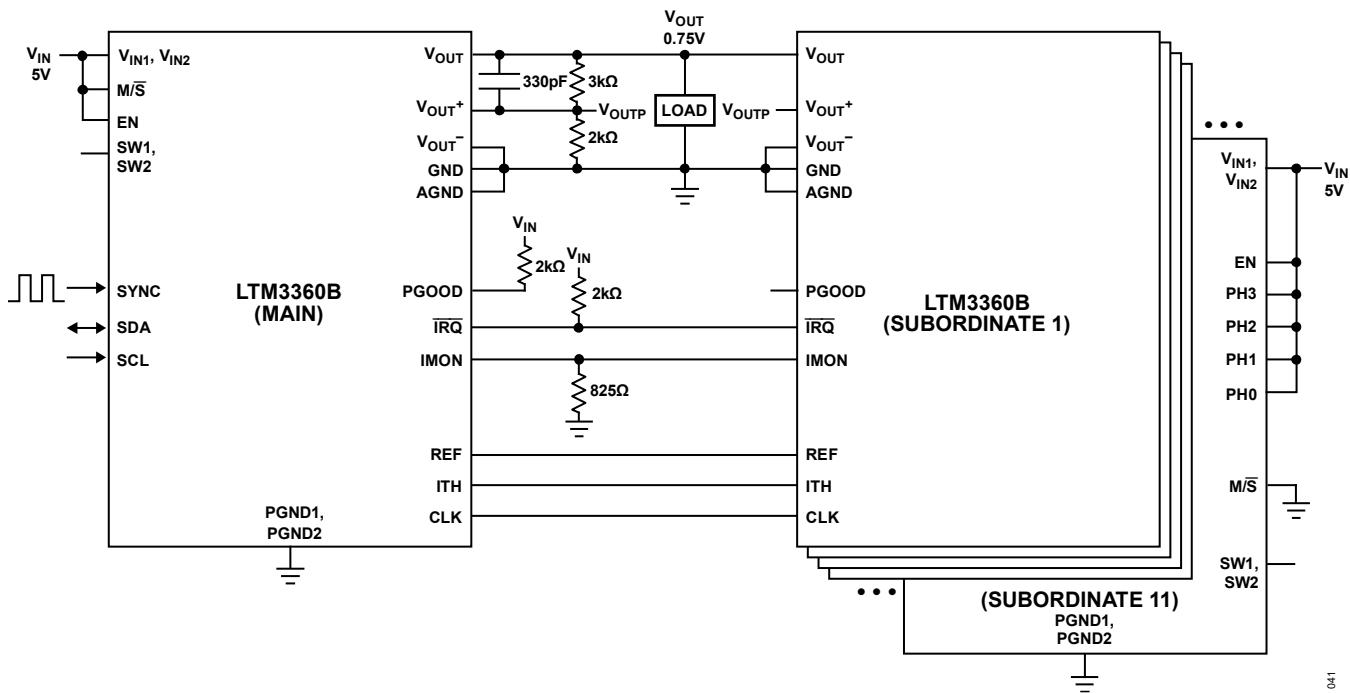

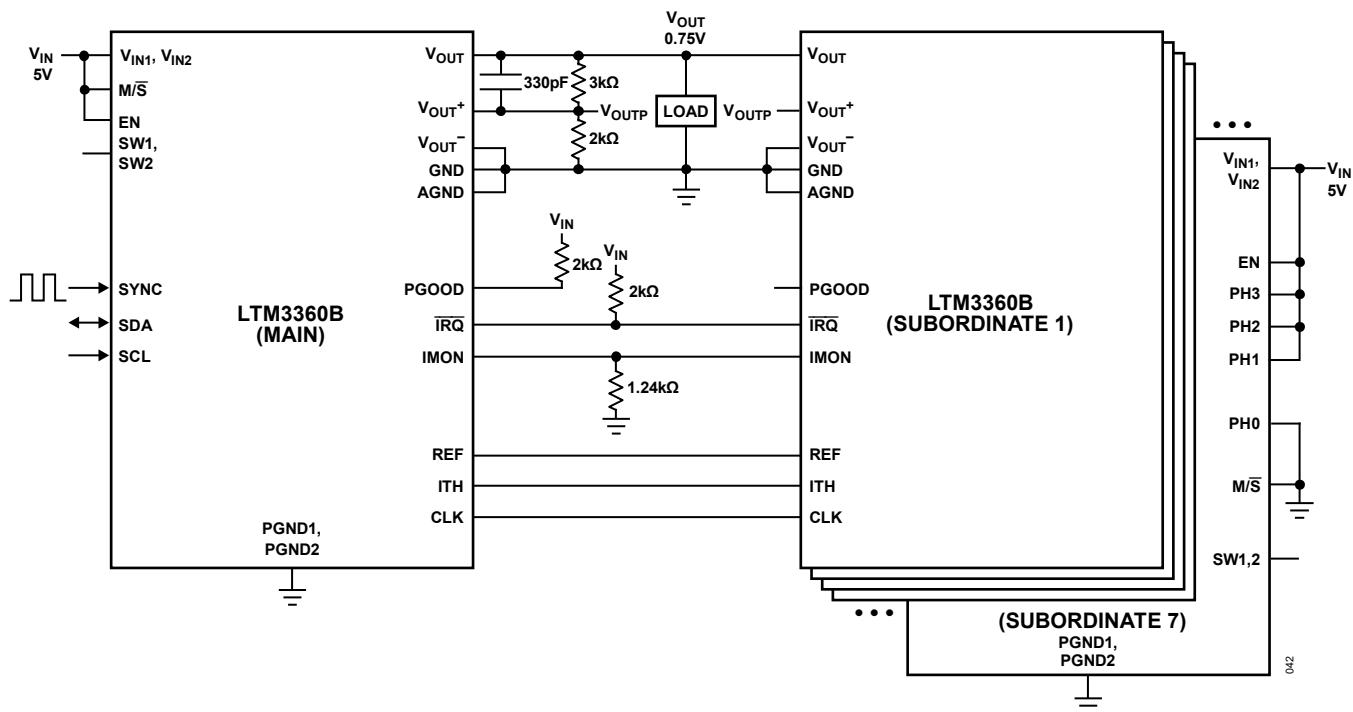

- ▶ Parallel Operation: Multiphase up to 12 phases and Stackable to > 1000A

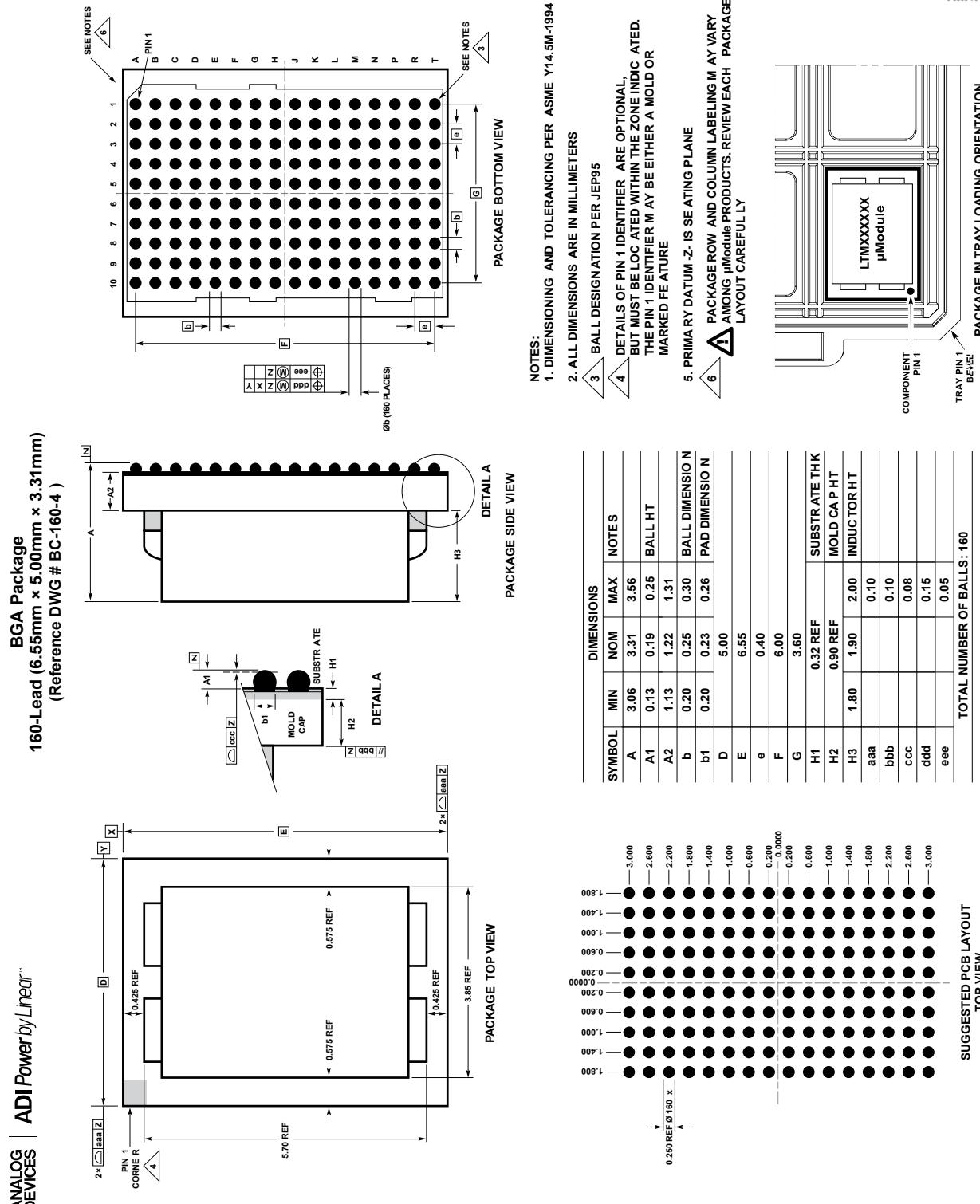

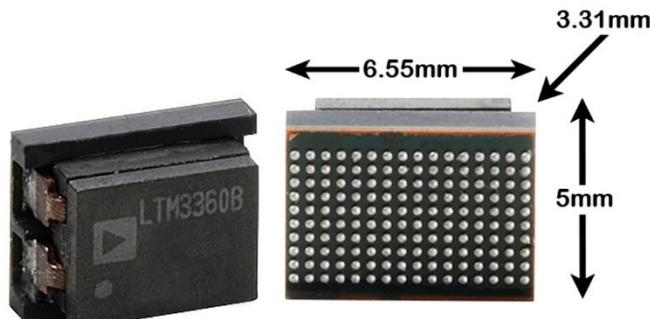

- ▶ Advanced Thermally Enhanced [160-Lead, 6.55mm × 5mm × 3.31mm, BGA](#) Package

### APPLICATIONS

- ▶ Data Centers xPU Core, Application-Specific Integrated Circuit (ASIC), Field-Programmable Gate Array (FPGA) Supplies

- ▶ Optical Modules

- ▶ Industrial and Communications

- ▶ Distributed DC Point-of-Load (POL) Power Systems

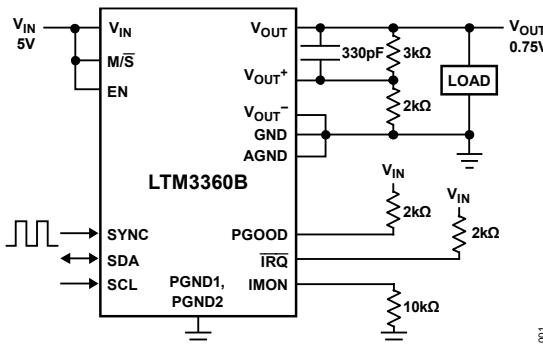

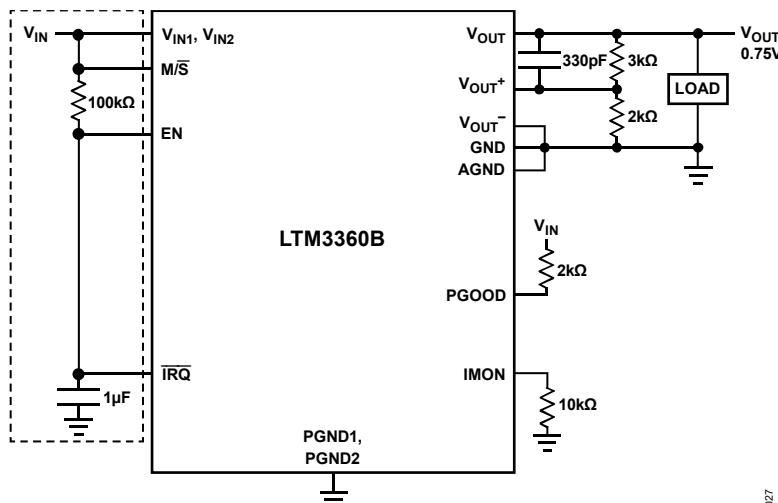

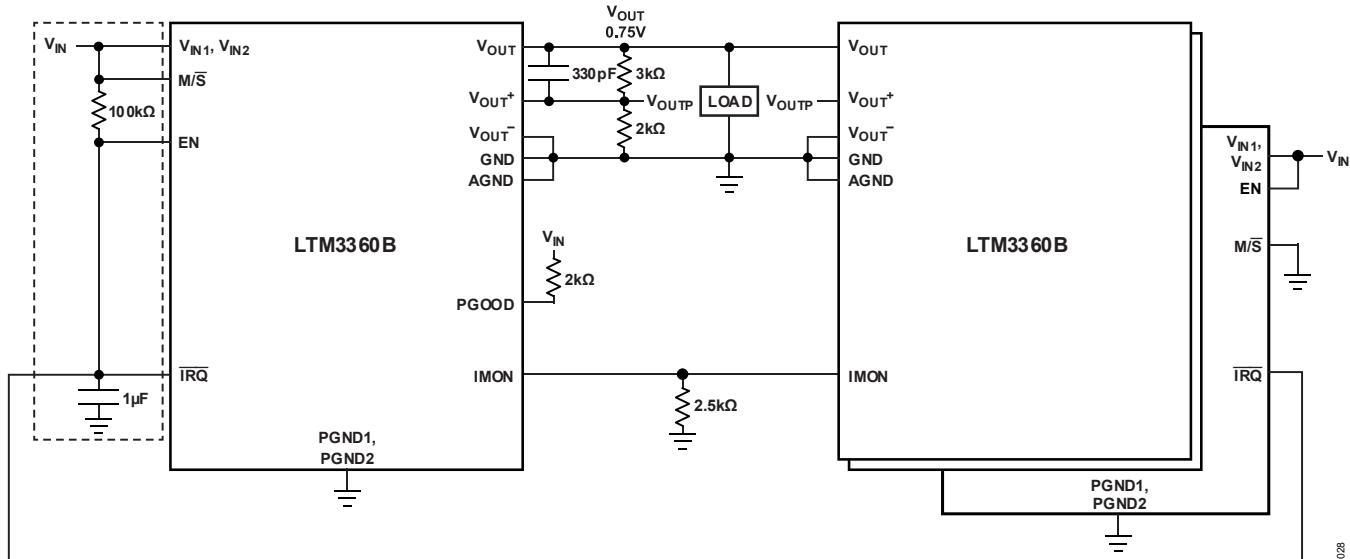

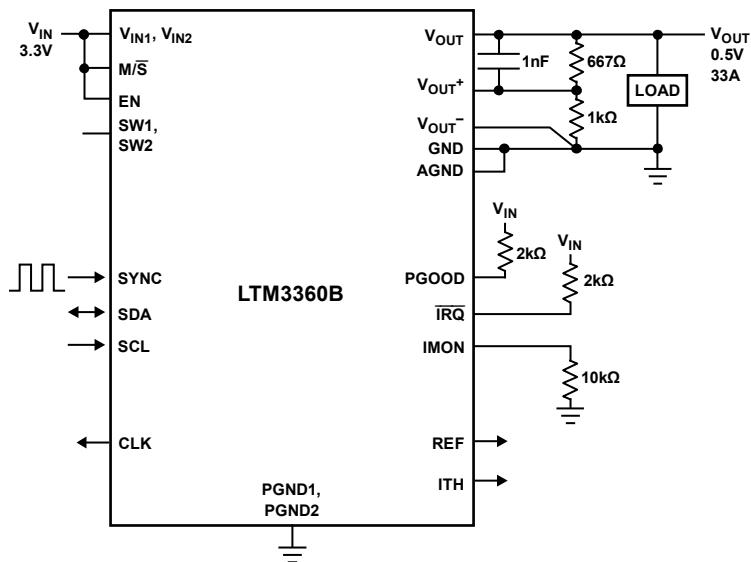

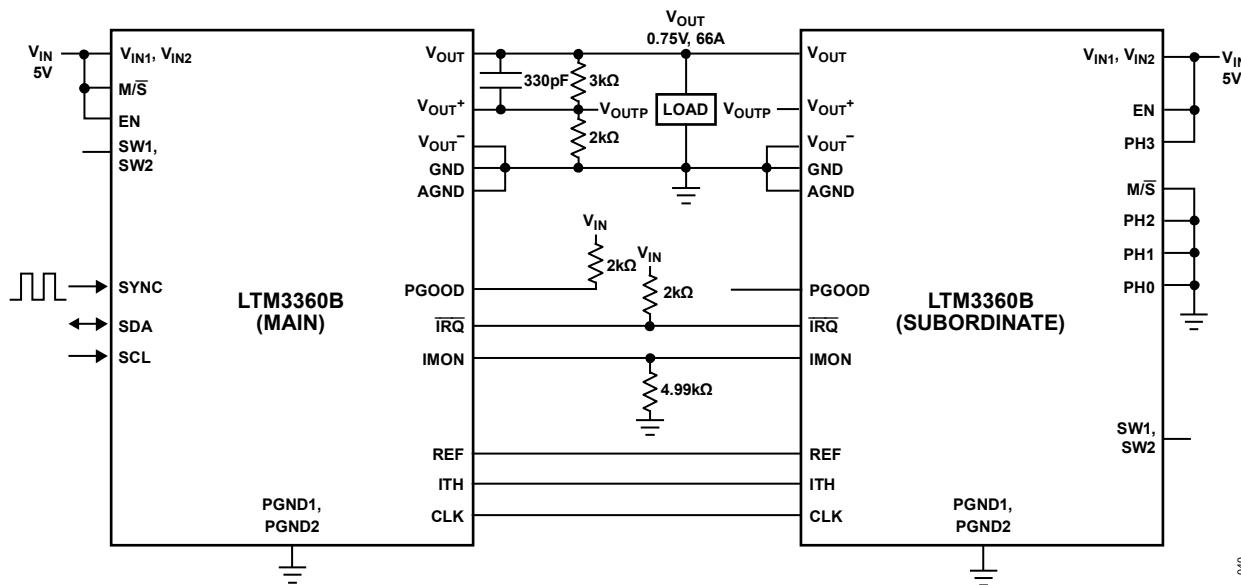

### TYPICAL APPLICATION

Figure 1. 5V to 0.75V at 33A, No Additional Capacitors

### GENERAL DESCRIPTION

The **LTM<sup>®</sup>3360B** is a high-current, high-density, low-voltage buck power μModule® (micromodule) regulator optimized for high-output current applications. The 2.9V to 5.5V input voltage range accommodates an intermediate bus voltage (IBV) of 5V  $\pm 10\%$  or 3.3V  $\pm 10\%$ . The current output capability of 33A can be paralleled to provide >1000A in a multiphase, stacked from a main-to-subordinate device configuration. Regulated output voltages down to 0.3V are achieved using a current mode architecture, which is capable of small on-time at very high frequencies. Select an appropriate feedback resistor divider to configure the output voltage. The 0.3V (default) feedback voltage is 8-bit adjustable through an I<sup>2</sup>C for margining or dynamic voltage scaling. Keep the feedback voltage close to 0.3V for the best phase-margin voltage regulation loop. The high fixed clock frequency of 5MHz which is double the switching frequency of 2.5MHz each phase permits integration of input and output capacitors and a power inductor, resulting in the highest density of output current-to-board footprint achievable in the industry today with minimal external components required. The LTM3360B is offered in a ball grid array (BGA) package, 0.4mm ball pitch, with excellent thermal performance and integrated inductors, input, and output capacitors. The LTM3360B is lead(Pb)-free and RoHS-compliant.

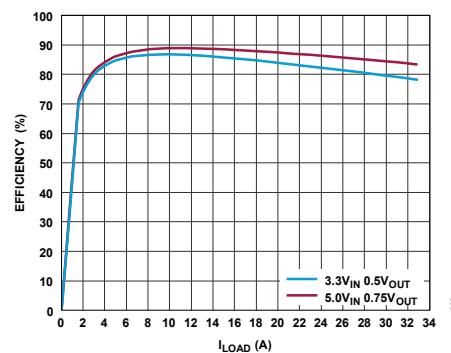

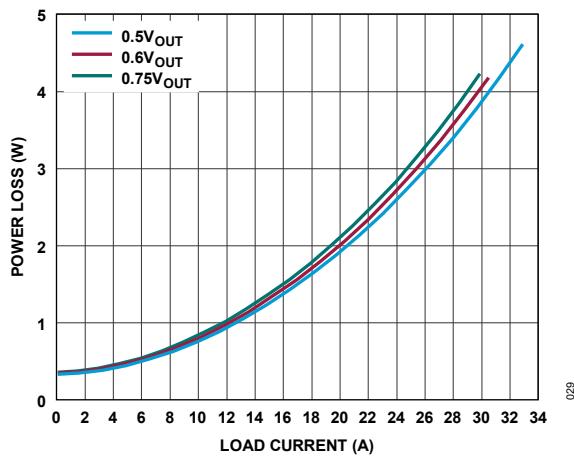

Figure 2. Efficiency vs. Current

## TABLE OF CONTENTS

|                                                    |    |

|----------------------------------------------------|----|

| Features.....                                      | 1  |

| Applications .....                                 | 1  |

| General Description .....                          | 1  |

| Typical Application .....                          | 1  |

| Revision History .....                             | 4  |

| Specifications.....                                | 5  |

| I <sup>2</sup> C Digital Interface .....           | 10 |

| Absolute Maximum Ratings.....                      | 10 |

| Thermal Resistance .....                           | 11 |

| Thermal Coefficients Definition .....              | 11 |

| Electrostatic Discharge (ESD) .....                | 11 |

| ESD Ratings .....                                  | 11 |

| ESD Caution.....                                   | 11 |

| Pin Configurations and Function Descriptions ..... | 12 |

| Pin Descriptions.....                              | 13 |

| Typical Performance Characteristics .....          | 16 |

| I <sup>2</sup> C Communication .....               | 18 |

| Overview .....                                     | 18 |

| Register Summary: LTM3360B Register Map .....      | 18 |

| Enable and IMON Control Register .....             | 18 |

| V <sub>OUT</sub> + Setting Register .....          | 19 |

| ADC Input Selection Register .....                 | 19 |

| ADC Setup Register.....                            | 20 |

| ADC Output Register.....                           | 20 |

| Theory of Operation.....                           | 21 |

| LTM3360B Overview .....                            | 21 |

| Simplified Block Diagram.....                      | 21 |

| Power-On .....                                     | 22 |

| Voltage Regulation .....                           | 22 |

| Forced Continuous Mode Operation.....              | 22 |

| Soft Start and Output Power Good .....             | 22 |

| Output Dynamic Voltage Scaling (DVS) Rate .....    | 23 |

| Power-Down .....                                   | 23 |

| Overtemperature Protection.....                    | 24 |

---

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| Overcurrent Warning .....                                                   | 24 |

| Output Short-Circuit Operation .....                                        | 24 |

| Synchronization.....                                                        | 25 |

| Applications Information.....                                               | 26 |

| Output Voltage Programming/Sensing .....                                    | 26 |

| Setting the Output Overcurrent Warning Threshold .....                      | 27 |

| Reverse Output Current Limit .....                                          | 27 |

| Output Pull-Down.....                                                       | 27 |

| Synchronization.....                                                        | 27 |

| Analog-to-Digital Converter (ADC) .....                                     | 28 |

| Transient Response and Loop Compensation.....                               | 29 |

| $V_{OUT}$ Overvoltage/Undervoltage Monitoring.....                          | 29 |

| Additional Input Capacitors .....                                           | 30 |

| Additional Output Capacitor, Output Ripple, and Transient Response.....     | 30 |

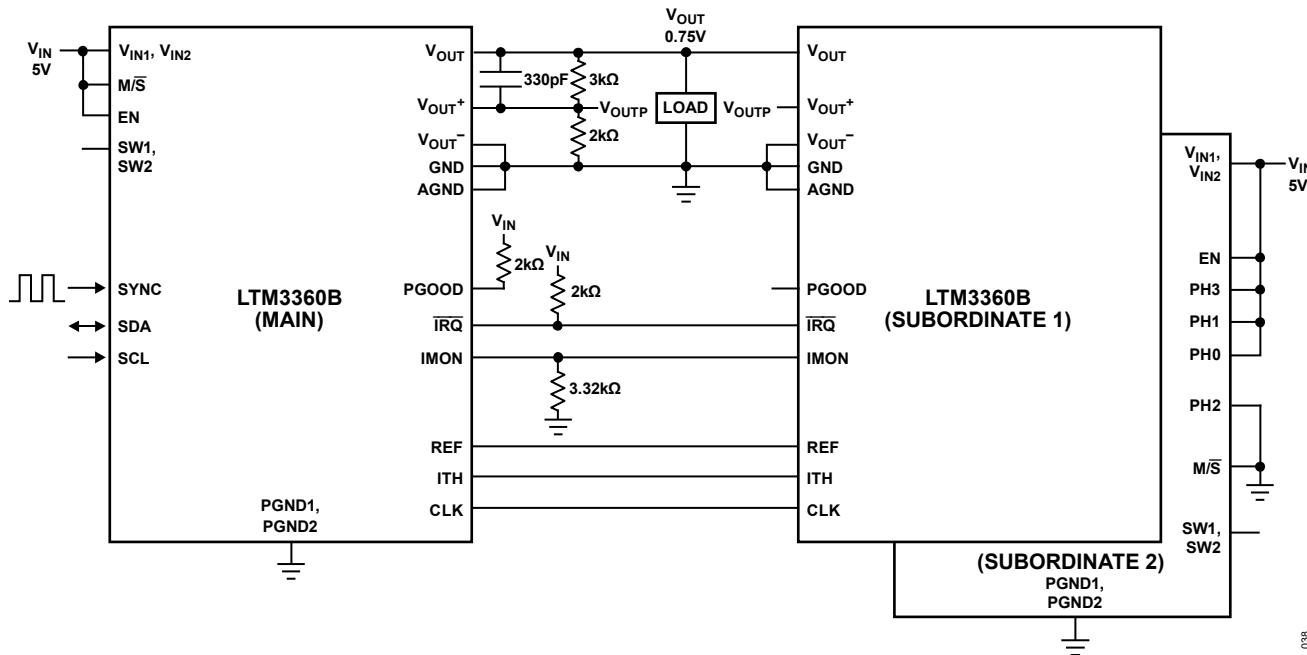

| Multiphase Operation.....                                                   | 30 |

| Enabling and Disabling Subordinates in a Multiphase Operation .....         | 32 |

| Low Supply Operation.....                                                   | 32 |

| Thermal Consideration for Output Short-Circuit and Overload Condition ..... | 32 |

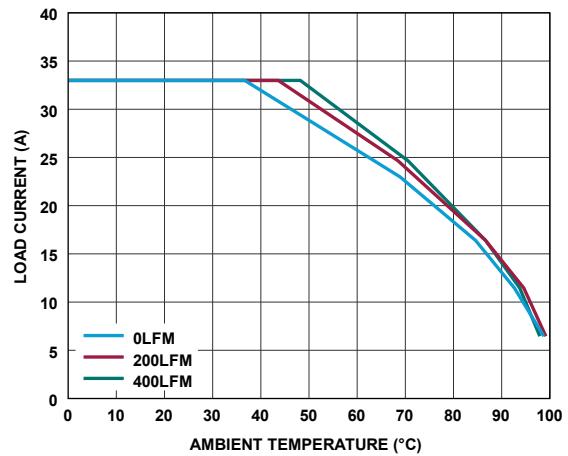

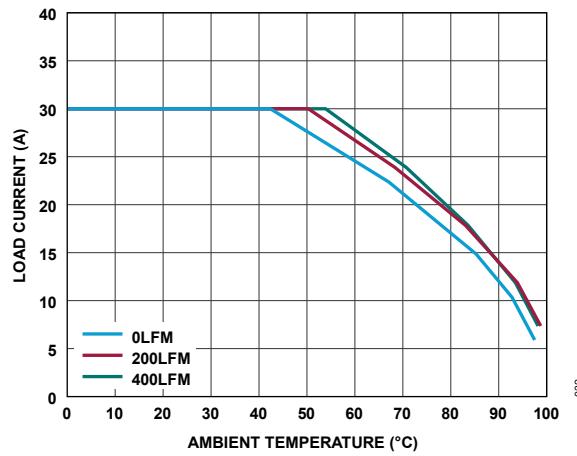

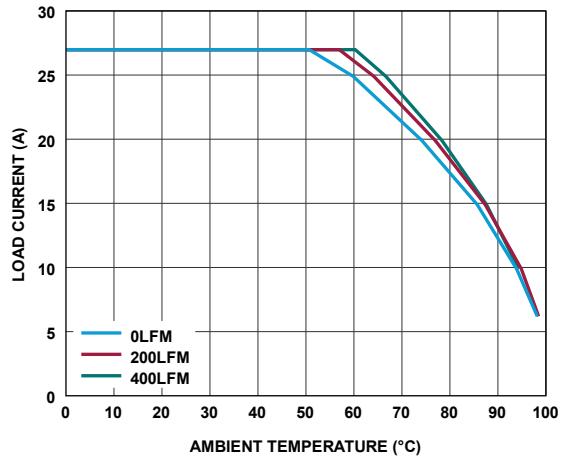

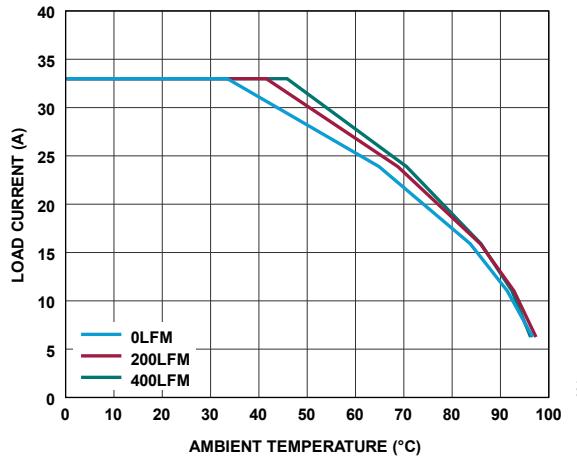

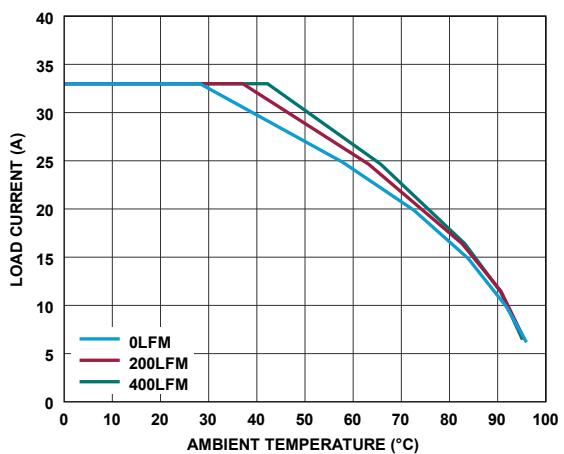

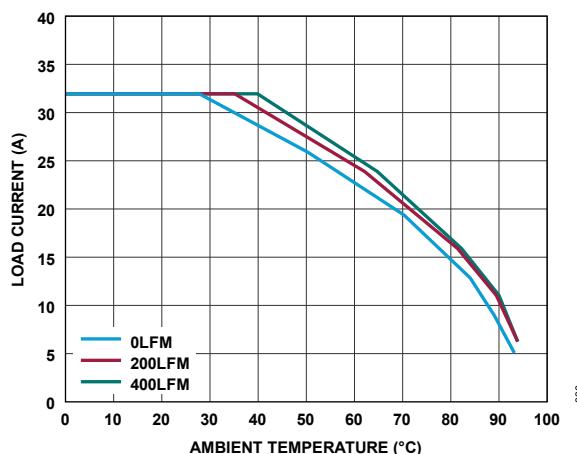

| Thermal Derating Curves .....                                               | 33 |

| PC Board Layout Considerations .....                                        | 35 |

| Typical Applications .....                                                  | 36 |

| Related Parts.....                                                          | 40 |

| Outline Dimensions.....                                                     | 41 |

| Ordering Guide.....                                                         | 42 |

| Selector Guide.....                                                         | 43 |

| Package Photos .....                                                        | 43 |

| Design Resources.....                                                       | 43 |

## REVISION HISTORY

| REVISION NUMBER | REVISION DATE | DESCRIPTION      | PAGE NUMBER |

|-----------------|---------------|------------------|-------------|

| 0               | 11/25         | Initial Release. | —           |

**SPECIFICATIONS****Table 1. Electrical Characteristics**(V<sub>IN</sub> = 5V and -40°C ≤ T<sub>J</sub> ≤ 105°C unless otherwise noted. [1,2](#))

| PARAMETER                                           | CONDITIONS                                                                                                                                | MIN   | TYP  | MAX   | UNITS |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| <b>Input Supply</b>                                 |                                                                                                                                           |       |      |       |       |

| Operating supply voltage (V <sub>IN</sub> )         |                                                                                                                                           | 2.9   |      | 5.5   | V     |

| V <sub>IN</sub> undervoltage lockout                | V <sub>IN</sub> rising                                                                                                                    | 2.70  | 2.75 | 2.80  | V     |

| V <sub>IN</sub> hysteresis                          | T <sub>A</sub> = 25°C                                                                                                                     |       | 110  |       | mV    |

| V <sub>IN</sub> quiescent current                   | Shutdown (not switching, V <sub>EN</sub> = 0V), T <sub>A</sub> = 25°C                                                                     |       | 5    |       | mA    |

| EN threshold                                        | V <sub>EN</sub> rising                                                                                                                    | 1.0   | 1.2  | 1.4   | V     |

| EN hysteresis                                       | T <sub>A</sub> = 25°C                                                                                                                     |       | 250  |       | mV    |

| EN pin leakage current                              | 0V ≤ V <sub>EN</sub> ≤ 5.5V, T <sub>A</sub> = 25°C                                                                                        |       |      | ±6    | µA    |

| <b>Output Voltage Regulation</b>                    |                                                                                                                                           |       |      |       |       |

| Regulated output feedback voltage                   | V <sub>OUT</sub> <sup>+</sup> = 0.3V, V <sub>OUT</sub> <sup>-</sup> = 0V, I <sub>OUT</sub> = 0A, T <sub>A</sub> = 25°C                    | 0.297 | 0.3  | 0.303 | V     |

| Output voltage range                                |                                                                                                                                           | 0.3   |      | 1     | V     |

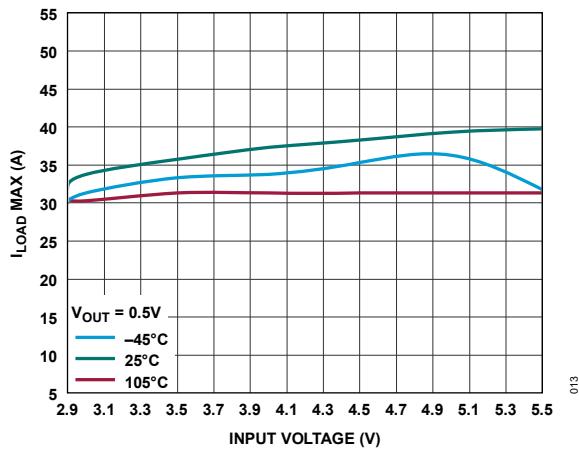

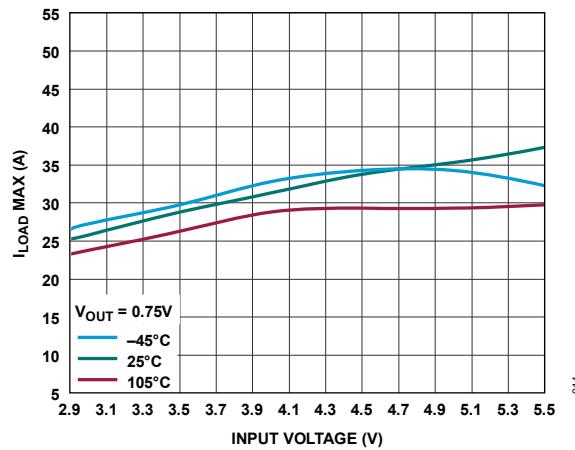

| Continuous output current range                     | V <sub>OUT</sub> = 0.75V, T <sub>A</sub> = 25°C                                                                                           |       |      | 33    | A     |

|                                                     | V <sub>IN</sub> = 3.3V, V <sub>OUT</sub> = 0.5V, T <sub>A</sub> = 25°C. See <a href="#">Figure 13</a> for different T <sub>A</sub> values |       |      | 33    | A     |

| Output current limit, peak high range               | V <sub>OUT</sub> = 0.75V, T <sub>A</sub> = 25°C, average load current                                                                     |       | 46   |       | A     |

| Turn-on startup time                                | From EN high to PGOOD high, V <sub>OUT</sub> = 0.75V                                                                                      |       | 800  |       | µs    |

| V <sub>OUT</sub> <sup>+</sup> pin input current     | V <sub>OUT</sub> = 0.75V, T <sub>A</sub> = 25°C                                                                                           |       |      | ±100  | nA    |

| V <sub>OUT</sub> <sup>-</sup> pin input current     | V <sub>OUT</sub> <sup>-</sup> = 0V, T <sub>A</sub> = 25°C                                                                                 | -300  | -150 |       | µA    |

| <b>Feedback Voltage Programmability</b>             |                                                                                                                                           |       |      |       |       |

| Feedback voltage digital-to-analog (DAC) resolution | T <sub>A</sub> = 25°C                                                                                                                     |       | 8    |       | bits  |

| LSB step size                                       | T <sub>A</sub> = 25°C                                                                                                                     |       | 4    |       | mV    |

| Default startup feedback voltage                    | OPT_VOUT = 0x4b, T <sub>A</sub> = 25°C, I <sub>OUT</sub> = 0A                                                                             |       | 300  |       | mV    |

| Feedback voltage programmability range              | T <sub>A</sub> = 25°C                                                                                                                     | 300   |      | 1000  | mV    |

| Output programmability differential nonlinearity    | Monotonicity guaranteed                                                                                                                   | -0.2  |      | 0.2   | LSB   |

( $V_{IN} = 5V$  and  $-40^{\circ}C \leq T_J \leq 105^{\circ}C$  unless otherwise noted. [1-2](#))

| PARAMETER                                                  | CONDITIONS                                                                      | MIN            | TYP | MAX       | UNITS   |

|------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|-----|-----------|---------|

| Input supply voltage rejection                             | $V_{IN} = 2.9V$ to $5.5V$ , $V_{OUT} = 0.75V$ , $I_{OUT} = 0A$                  | -4             |     | 4         | mV      |

| <b>Oscillator</b>                                          |                                                                                 |                |     |           |         |

| Default clock frequency                                    |                                                                                 | 4.5            | 5   | 5.5       | MHz     |

| Minimum synchronization frequency                          | Through the SYNC pin                                                            |                | 4.5 |           | MHz     |

| Maximum synchronization frequency                          | Through the SYNC pin                                                            |                | 5.5 |           | MHz     |

| SYNC input level<br>(main device only)                     | $V_{SYNC}$ high                                                                 | 1.5            |     |           | V       |

|                                                            | $V_{SYNC}$ low                                                                  |                |     | 0.6       | V       |

| Minimum SYNC input pulse width                             | $T_A = 25^{\circ}C$                                                             | 20             |     |           | ns      |

| SYNC input leakage current to GND                          | $V_{SYNC} = 6V$ , $T_A = 25^{\circ}C$                                           |                |     | $\pm 1$   | $\mu A$ |

| CLK out rise/fall time<br>(main device only)               | $C_{CLK} = 50pF$ , rising: 10% to 90%, falling: 90% to 10%, $T_A = 25^{\circ}C$ |                |     | 16        | ns      |

| CLK low output voltage<br>(main device only)               | $I_{CLK} = 1mA$ , $T_A = 25^{\circ}C$                                           |                |     | 0.2       | V       |

| CLK high output voltage<br>(main device only)              | $I_{CLK} = -1mA$ , $T_A = 25^{\circ}C$                                          | $V_{IN} - 0.2$ |     |           | V       |

| CLK out duty cycle<br>(main device only)                   | $T_A = 25^{\circ}C$                                                             |                | 50  |           | %       |

| CLK input level<br>(subordinate device only)               | $V_{CLK}$ high                                                                  | 1.5            |     |           | V       |

|                                                            | $V_{CLK}$ low                                                                   |                |     | 0.6       | V       |

| Minimum CLK input pulse width<br>(subordinate device only) | $T_A = 25^{\circ}C$                                                             | 20             |     |           | ns      |

| CLK input leakage current to GND                           | $V_{CLK} = 6V$ , $T_A = 25^{\circ}C$                                            |                |     | $\pm 1$   | $\mu A$ |

| <b>Main/Subordinate Device Communication Pins: ITH</b>     |                                                                                 |                |     |           |         |

| ITH pull-up current<br>(main device only)                  | $V_{OUT}$ at -10% out of regulation, $V_{ITH} = 1.2V$ , $T_A = 25^{\circ}C$     |                | -10 |           | mA      |

| ITH pull-down current<br>(main device only)                | $V_{OUT}$ at +10% out of regulation, $V_{ITH} = 1.2V$ , $T_A = 25^{\circ}C$     |                | 10  |           | mA      |

| ITH input leakage current<br>(subordinate device only)     | $V_{ITH} = 2.0V$ , $T_A = 25^{\circ}C$                                          |                |     | $\pm 100$ | nA      |

( $V_{IN} = 5V$  and  $-40^\circ C \leq T_J \leq 105^\circ C$  unless otherwise noted. [1.2](#))

| PARAMETER                                                 | CONDITIONS                                                                                                                             | MIN  | TYP    | MAX       | UNITS     |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|--------|-----------|-----------|

| <b>Current Monitor</b>                                    |                                                                                                                                        |      |        |           |           |

| IMON voltage at 33A                                       | $R_{IMON} = 10k\Omega$ , $V_{OUT} = 0.75V$ , $T_A = 25^\circ C$                                                                        | 0.91 | 0.96   | 1.01      | V         |

| IMON voltage at no load                                   | $R_{IMON} = 10k\Omega$ , $V_{OUT} = 0.75V$ , $T_A = 25^\circ C$                                                                        |      | 0      |           | V         |

| IMON gain                                                 | $I_{IMON}/I_{OUT}$ , $V_{IMON} = 0.96V$ , $T_A = 25^\circ C$                                                                           |      | 2.91   |           | $\mu A/A$ |

| Output current error                                      | $V_{IMON} = 0V$ to $0.96V$ , $R_{IMON} = 10k\Omega$ , $T_A = 25^\circ C$                                                               |      |        | $\pm 5$   | $\mu A$   |

| <b>IMON Over Current Alert Through IRQ</b>                |                                                                                                                                        |      |        |           |           |

| IMON rising threshold overvoltage                         | OPT_IMON_TH bits 00 to 103% ( $I_{OUT} = 34A$ )                                                                                        | 0.96 | 0.99   | 1.02      | V         |

|                                                           | OPT_IMON_TH bits 01 to 93% ( $I_{OUT} = 30.6A$ )                                                                                       | 0.86 | 0.89   | 0.92      | V         |

| IMON rising threshold overvoltage                         | OPT_IMON_TH bits 10 to 82% ( $I_{OUT} = 27.1A$ )                                                                                       | 0.76 | 0.79   | 0.82      | V         |

|                                                           | OPT_IMON_TH bits 11 to 72% ( $I_{OUT} = 23.7A$ )                                                                                       | 0.66 | 0.69   | 0.72      | V         |

| Hysteresis                                                |                                                                                                                                        | 40   | 50     | 60        | mV        |

| IMON overvoltage to IRQ delay                             | $V_{IMON}$ rising edge = 0.90V to 1.04V, OPT_IMON_TH = 00, $2k\Omega$ to $V_{IN}$ and 10pF on $\overline{IRQ}$ pin, $T_A = 25^\circ C$ |      | 1      | 2         | $\mu s$   |

| <b>REF Pin</b>                                            |                                                                                                                                        |      |        |           |           |

| REF voltage (main device only)                            | $I_{OUT} = 0A$                                                                                                                         |      | 300    |           | mV        |

| REF input leakage current (subordinate device only)       | $T_A = 25^\circ C$                                                                                                                     |      |        | $\pm 100$ | nA        |

| <b>PGOOD (Main Device Only), IRQ Pins, and Soft Start</b> |                                                                                                                                        |      |        |           |           |

| PGOOD UV (undervoltage) rising threshold                  |                                                                                                                                        | -30  | -18.75 | -7.5      | mV        |

| Hysteresis                                                |                                                                                                                                        | 1.88 | 3.75   | 5.63      | mV        |

| PGOOD OV (overvoltage) rising threshold                   |                                                                                                                                        | 7.5  | 18.75  | 30        | mV        |

| Hysteresis                                                |                                                                                                                                        | 1.88 | 3.75   | 5.63      | mV        |

| PGOOD delay/deglitch time                                 | $V_{OUT}$ : 110% to 100% or 90% to 100% to PGOOD rising edge, $2k\Omega$ pull-up to $V_{IN}$ , $T_A = 25^\circ C$                      |      | 20     |           | $\mu s$   |

( $V_{IN} = 5V$  and  $-40^{\circ}C \leq T_J \leq 105^{\circ}C$  unless otherwise noted. [1,2](#))

| PARAMETER                                 | CONDITIONS                          | MIN | TYP | MAX     | UNITS      |

|-------------------------------------------|-------------------------------------|-----|-----|---------|------------|

| PGOOD, $\overline{IRQ}$ leakage current   | $V_{PIN} = 5V, T_A = 25^{\circ}C$   |     |     | $\pm 1$ | $\mu A$    |

| PGOOD, $\overline{IRQ}$ pull-down current | $V_{PIN} = 0.4V, T_A = 25^{\circ}C$ | 5   | 15  |         | mA         |

| Soft start slew rate                      | $T_A = 25^{\circ}C$                 |     | 2   |         | $mV/\mu s$ |

#### M/ $\overline{S}$ , I<sup>2</sup>C, PH[3:0] (Digital/Programming Pins)

|                                                                                                         |                                                                                   |     |    |         |         |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|----|---------|---------|

| Input level for pins M/ $\overline{S}$ SDA, SCL (main device only)<br>PH[3:0] (subordinate device only) | $V_{PIN}$ high                                                                    | 1.4 |    |         | V       |

|                                                                                                         | $V_{PIN}$ low                                                                     |     |    | 0.6     | V       |

| Input leakage current to GND                                                                            | For pins M/ $\overline{S}$ , SDA, SCL, PH[3:0], $V_{PIN} = 5V, T_A = 25^{\circ}C$ |     |    | $\pm 1$ | $\mu A$ |

| SDA pull-down current                                                                                   | $V_{PIN} = 0.4V, T_A = 25^{\circ}C$                                               | 5   | 20 |         | mA      |

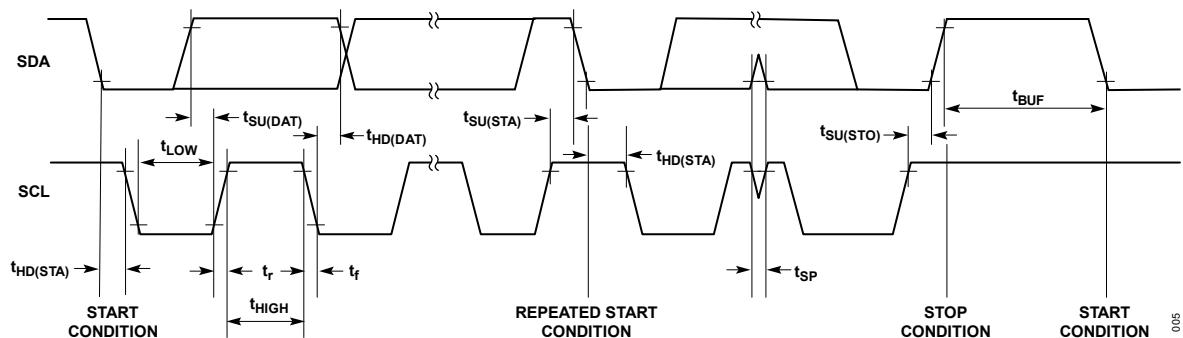

#### I<sup>2</sup>C Timing Characteristics

|                                     |               |     |            |     |         |

|-------------------------------------|---------------|-----|------------|-----|---------|

| I <sup>2</sup> C address            |               |     | 7'b1101001 |     |         |

| SCL clock frequency                 | $f_{SCL}$     |     |            | 400 | kHz     |

| SCL pulse width low                 |               | 1.3 |            |     | $\mu s$ |

| SCL pulse width high                |               | 0.6 |            |     | $\mu s$ |

| Bus free time start to stop         | $t_{BUF}$     | 1.3 |            |     | $\mu s$ |

| Hold time after repeated start      | $t_{HD(STA)}$ | 0.6 |            |     | $\mu s$ |

| Setup time after repeated start     | $t_{SU(STA)}$ | 0.6 |            |     | $\mu s$ |

| Stop the setup time                 | $t_{SU(STO)}$ | 0.6 |            |     | $\mu s$ |

| Data hold time                      | $t_{HD(DAT)}$ | 0   |            | 900 | ns      |

| Data setup time                     | $t_{SU(DAT)}$ | 100 |            |     | ns      |

| Input spike suppression pulse width | $t_{SP}$      |     |            | 50  | ns      |

#### IMON-Average Current Readback Through I<sup>2</sup>C

|                                                            |                                                                               |    |      |   |      |

|------------------------------------------------------------|-------------------------------------------------------------------------------|----|------|---|------|

| Output current resolution                                  | $T_A = 25^{\circ}C$                                                           |    | 8    |   | bits |

| LSB                                                        | $I_{MON}$ to LSB, $T_A = 25^{\circ}C$                                         |    | 4.7  |   | mV   |

| Analog-to-digital converter (ADC) full-scale input voltage | $T_A = 25^{\circ}C$                                                           |    | 1.2  |   | V    |

| Full-scale $I_{MON}$ output code                           | $I_{MON}$ voltage = 1V, $T_A = 25^{\circ}C$                                   |    | 0xd5 |   |      |

| Total unadjusted readback error <sup>3</sup>               | $I_{MON}$ voltage = 1V, output valid $25^{\circ}C \leq T_J \leq 105^{\circ}C$ | -1 |      | 1 | %    |

| Conversion time                                            | $T_A = 25^{\circ}C$                                                           |    | 3.3  |   | ms   |

( $V_{IN} = 5V$  and  $-40^\circ C \leq T_J \leq 105^\circ C$  unless otherwise noted. <sup>1,2</sup>)

| PARAMETER                                                         | CONDITIONS                                          | MIN  | TYP      | MAX | UNITS |

|-------------------------------------------------------------------|-----------------------------------------------------|------|----------|-----|-------|

| <b>Temperature Monitor Readback<sup>4</sup></b>                   |                                                     |      |          |     |       |

| Temperature least-significant bit (LSB)                           | $T_A = 25^\circ C$                                  |      | 2.6      |     | °C    |

| Monitor code (room temperature)                                   | $T_A = 25^\circ C$                                  | -3   | 01010101 | 3   | LSB   |

| Total unadjusted readback error <sup>3</sup>                      | $T_A = 25^\circ C$                                  | -7.8 |          | 7.8 | °C    |

| Conversion time                                                   | $T_A = 25^\circ C$                                  |      | 3.3      |     | ms    |

| <b>Input Voltage Monitor Readback<sup>4</sup></b>                 |                                                     |      |          |     |       |

| LSB                                                               | $T_A = 25^\circ C$                                  |      | 23       |     | mV    |

| $V_{IN}$ output code                                              | $V_{IN} = 3.3V, T_A = 25^\circ C$                   |      | 10001101 |     |       |

| Total unadjusted readback error <sup>3</sup>                      | Output valid $25^\circ C \leq T_J \leq 105^\circ C$ | -5   |          | 5   | %     |

| <b>Differential Feedback Voltage Monitor Readback<sup>4</sup></b> |                                                     |      |          |     |       |

| LSB                                                               | $T_A = 25^\circ C$                                  |      | 4.7      |     | mV    |

| $V_{OUT}^+$ output code                                           | $T_A = 25^\circ C, V_{OUT}^+ = 0.3V$                |      | 01001011 |     |       |

| $V_{OUT}^-$ output code                                           | $T_A = 25^\circ C, V_{OUT}^- = 0V$                  |      | 00000000 |     |       |

| Total unadjusted $V_{OUT}^\pm$ readback error <sup>3</sup>        | Output valid $25^\circ C \leq T_J \leq 105^\circ C$ | -2   |          | 2   | LSB   |

The LTM3360B is tested under conditions such that  $T_J \approx T_A$ . The LTM3360B is guaranteed to meet specifications from  $-40^\circ C$  to  $105^\circ C$  junction temperature. Note that the maximum ambient temperature consistent with these specifications is determined by

<sup>1</sup> specific operating conditions in conjunction with board layout, the rated package thermal impedance, and other environmental factors. The junction temperature ( $T_J$ , in °C) is calculated from the ambient temperature ( $T_A$ , in °C) and power dissipation ( $P_D$ , in Watts) according to the following formula:  $T_J = T_A + (P_D \times \theta_{JA})$ , where  $\theta_{JA}$  (in °C/W) is the package thermal impedance.

<sup>2</sup> All currents into pins are positive; all voltages are referenced to GND unless otherwise noted.

<sup>3</sup> Total unadjusted error includes gain, integral nonlinearity (INL), differential nonlinearity (DNL), as well as offset.

<sup>4</sup> The ADC output is valid for  $25^\circ C \leq T_J \leq 105^\circ C$  and is ADC tested with pulse-width modulation (PWM) disabled. Comparable capability demonstrated by the in-circuit evaluations.

<sup>5</sup> This module includes overtemperature protection that is intended to protect the switching device during momentary overload conditions. Junction temperature exceeds  $105^\circ C$  when overtemperature protection is active. Continuous operation above the specified maximum junction temperature may impair device reliability or permanently damage the device.

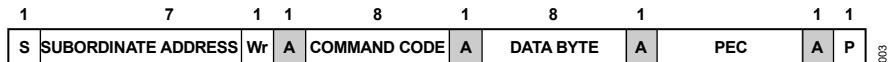

**I<sup>2</sup>C Digital Interface**

Figure 3. Write Byte Protocol

Figure 4. Read Byte Protocol

Figure 5. I<sup>2</sup>C Timing Diagram**ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^\circ\text{C}$  unless otherwise specified.

Table 2. Absolute Maximum Ratings<sup>1</sup>

| PARAMETER                             | RATING                        |

|---------------------------------------|-------------------------------|

| $V_{IN1,2}$ voltage                   | -0.3V to 6V                   |

| SDA, SCL, $\overline{IRQ}$ voltage    | -0.3V to Min ( $V_{IN}$ , 6V) |

| EN, M/S, SYNC, PGOOD voltage          | -0.3V to Min ( $V_{IN}$ , 6V) |

| PH[3:0] voltage                       | -0.3V to Min ( $V_{IN}$ , 6V) |

| IMON, REF voltage                     | -0.3V to 1.5V                 |

| $V_{OUT^+}$ , $V_{OUT^-}$ voltage     | -0.3V to 1.5V                 |

| Operating junction temperature range  | -40°C to 105°C                |

| Storage temperature range             | -55°C to 125°C                |

| Max reflow (package body) temperature | 250°C                         |

<sup>1</sup> The LTM3360B is tested under conditions such that  $T_J \approx T_A$ . The LTM3360B is guaranteed to meet specifications from  $-40^\circ\text{C}$  to  $105^\circ\text{C}$  junction temperature.

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## Thermal Resistance

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to the PCB thermal design is required. Using enhanced heat removal like the PCB, heat sink, and airflow techniques improve the thermal resistance values.

### Thermal Coefficients Definition

1.  $\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure.

2.  $\theta_{JCTop}$  is the junction-to-case top thermal resistance.

3.  $\theta_{JCbottom}$  is the junction-to-case bottom thermal resistance.

**Table 3. Thermal Resistance for LTM3360B Evaluation Board in “Still Air”**

| $\theta_{JA}$ | $\theta_{JCTop}$ | $\theta_{JCbottom}$ | UNIT |

|---------------|------------------|---------------------|------|

| 15.5          | 12.7             | 4.2                 | °C/W |

## Electrostatic Discharge (ESD)

The following ESD information is provided for handling of ESD-sensitive devices in an ESD-protected area only. Human body model (HBM) per ANSI/ESDA/JEDEC JS-001. Field-induced charged device model (FICDM) and charged device model (CDM) per ANSI/ESDA/JEDEC JS-002. International Electrotechnical Commission (IEC) electromagnetic compatibility: Part 4-2 (IEC) per IEC 61000-4-2. Machine model (MM) per ANSI/ESD STM5.2. MM voltage values are for characterization only.

### ESD Ratings

**Table 4. LTM3360B ESD Ratings**

| ESD MODEL | WITHSTAND THRESHOLD (V) | CLASS |

|-----------|-------------------------|-------|

| HBM       | ±4000                   | 3A    |

| CDM       | ±1250                   | C3    |

### ESD Caution

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

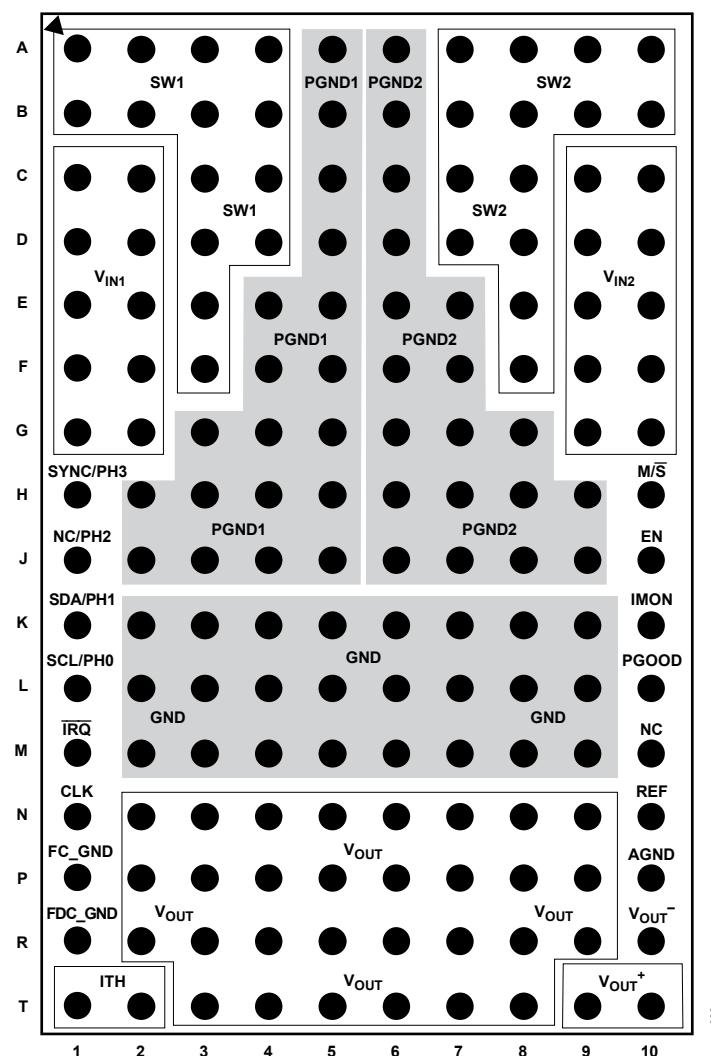

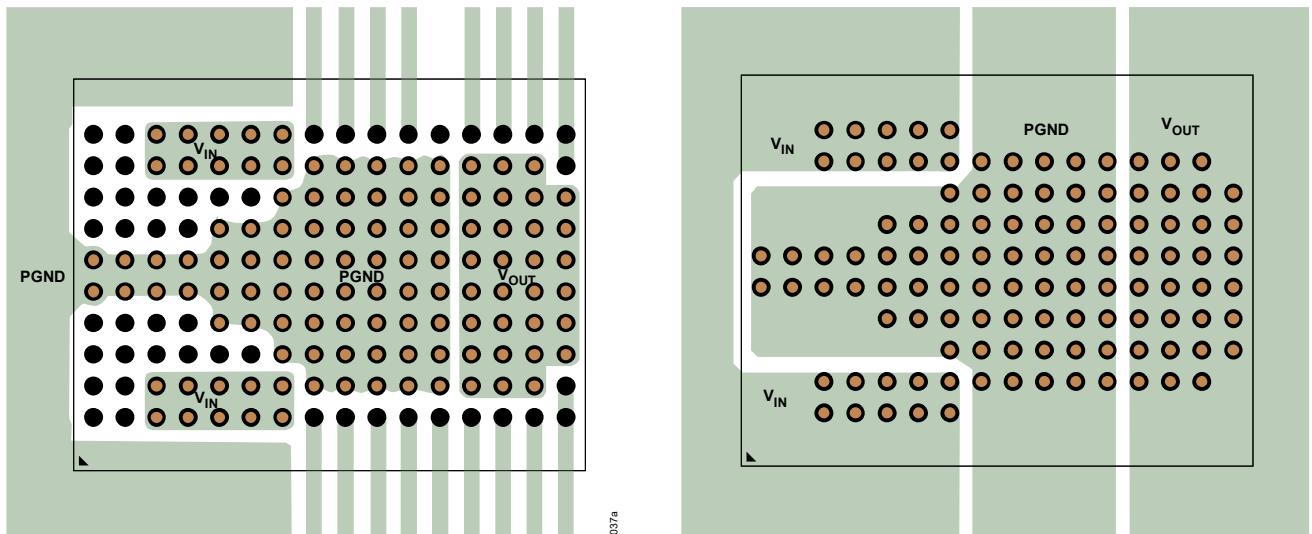

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

TOP VIEW

## BGA PACKAGE

160-PIN (6.55mm x 5mm x 3.31mm)

TJMAX = 105°C,  $\theta_{JA}$  = 15.5°C/W, 0.4mm BALL PITCH $\theta_{JCTop}$  = 12.7°C/W,  $\theta_{JCbottom}$  = 4.2°C/W

WEIGHT = 0.31g

$\theta$  VALUES DETERMINED PER JESD5112

Figure 6. Pin Configuration

PACKAGE ROW AND COLUMN LABELING MAY VARY

AMONG  $\mu$ Module PRODUCTS. REVIEW EACH PACKAGE

LAYOUT CAREFULLY.

## Pin Descriptions

Table 5. Pin Descriptions

| PIN                                                               | NAME                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1-B1, A2-B2,<br>A3-F3, A4-D4;<br>A7-D7, A8-F8,<br>A9-B9, A10-B10 | SW1, SW2              | Switch Pins. These pins are the switching outputs of the internal power switches connected to the internal power inductors. High $dV/dt$ waveforms are present in these pins. Leave these pins open to minimize electromagnetic interference (EMI).                                                                                                                                                                                                            |

| A5-J5, E4-J4,<br>G3-J3, H2-J2                                     | PGND1                 | Power Ground 1. PGND1 pins are the return path of the internal bottom-side power switch 1 (SW1). Connect the negative terminal of any additional input capacitors as close to the PGND1 pins as possible (half between $V_{IN1}$ and PGND1, and the other half between $V_{IN2}$ and PGND2). The PGND1 node is one of the primary thermal highways at the bottom of the package and should be connected to a large PCB ground plane with several thermal vias. |

| A6-J6, E7-J7,<br>G8-J8, H9-J9                                     | PGND2                 | Power Ground 2. PGND2 pins are the return path of the internal bottom-side power switch 2 (SW2). Connect the negative terminal of any additional input capacitors as close to the PGND2 pins as possible (half between $V_{IN1}$ and PGND1, and the other half between $V_{IN2}$ and PGND2). The PGND2 node is one of the primary thermal highways at the bottom of the package and should be connected to a large PCB ground plane with several thermal vias. |

| C1-G1, C2-G2;<br>C9-G9, C10-G10                                   | $V_{IN1}$ , $V_{IN2}$ | Input Voltage Supply. The $V_{IN1}$ and $V_{IN2}$ pins supply current to the internal circuitry and top-side power switches. The $V_{IN1}$ and $V_{IN2}$ pins must be connected to the same power source potential. Internally connected to bypass capacitors to GND.                                                                                                                                                                                          |

| H1 <sup>2</sup>                                                   | SYNC                  | Synchronization Input Pin. The SYNC pin allows the power switches to synchronize to an external clock between 4.5MHz and 5.5MHz.                                                                                                                                                                                                                                                                                                                               |

| H1, J1, K1, L1 <sup>3</sup>                                       | PH3, PH2,<br>PH1, PH0 | Phase Setting Pins. For each subordinate device, one of 16-phase delays (in degrees) is selectable, allowing for the implementation of an evenly spaced 1-, 2-, 3-, 4-, 6-, 8-, or 12-phase system. For the main device, the phase is set to 0°. On the main device, these pins' functions are replaced by SYNC, NC, SDA, and SCL pins, respectively. See the <i>Applications Information</i> section for more details.                                        |

| H10                                                               | M/S                   | Main/Subordinate Select Input Pin. Connect this pin to $V_{IN}$ to set the LTM3360B to the main mode. Similarly, connect this pin to GND to set the LTM3360B to the subordinate mode.                                                                                                                                                                                                                                                                          |

| J1 <sup>2</sup>                                                   | NC                    | No Connect Pin. Leave the NC pin open in the main configuration.                                                                                                                                                                                                                                                                                                                                                                                               |

| J10                                                               | EN                    | Enable Input Pin. Pull the EN pin above its rising threshold to enable the switching converter. If this pin is not used, directly connect the pin to $V_{IN}$ to automatically enable the switching converter as $V_{IN}$ rises. Connecting this pin to GND ensures that the switching converter remains disabled with no power                                                                                                                                |

| PIN                        | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |           | delivered to $V_{OUT}$ as $V_{IN}$ rises. When connected in the main configuration, use the I <sup>2</sup> C ports to overwrite this pin, allowing the enable/disable of the switching converter independent of the state of this pin. When connected as a subordinate, connect the EN pin to the main EN pin. See the <i>Applications Information</i> section for details on subordinate operation in a multiphase system when the main is disabled through I <sup>2</sup> C. |

| K1 <sup>2,5</sup>          | SDA       | I <sup>2</sup> C Data Pin. When writing data to the LTM3360B, the SDA pin is a high impedance input pin. When reading data from the LTM3360B, the SDA pin is an open-drain, active-low pin. Connect a 2k $\Omega$ pull-up resistor to the I <sup>2</sup> C supply or $V_{IN}$ . See the <i>I<sup>2</sup>C Communication</i> section for more details.                                                                                                                          |

| K2-K9, L2-L9, M2-M9        | GND       | Power Ground. The GND pins are the return path of the internal output bulk capacitors. Connect the negative terminal of any additional output capacitors between $V_{OUT}$ and GND. The GND node is one of the primary thermal highways at the bottom of the package and should be connected to a large PCB ground plane with several thermal vias.                                                                                                                            |

| K10                        | IMON      | Current Monitor Pin. The IMON pin outputs a current proportional to the output current. Connect an appropriate resistor to ground to convert IMON current to an equivalent voltage. At 34A load current at $V_{OUT}$ , the IMON pin outputs 100 $\mu$ A (typical) of current.                                                                                                                                                                                                  |

| L1 <sup>2,5</sup>          | SCL       | I <sup>2</sup> C Clock Input Pin. The SCL pin is a high impedance input pin. See the <i>I<sup>2</sup>C Communication</i> section for more details.                                                                                                                                                                                                                                                                                                                             |

| L10 <sup>2</sup>           | PGOOD     | Power Good Output. Open-drain active low output. This pin is driven low when the regulated output voltage falls below its PGOOD threshold or rises above its overvoltage threshold. Connect a 2k $\Omega$ pull-up resistor to $V_{IN}$ in a typical application.                                                                                                                                                                                                               |

| M1                         | IRQ       | Interrupt Request Output. Open-drain active low output. This pin pulls low when there is an overcurrent event (IMON pin goes above the overcurrent alert threshold) or an overtemperature event.                                                                                                                                                                                                                                                                               |

| M10                        | NC        | Do Not Connect Pin. Leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| N1 <sup>4</sup>            | CLK       | Clock Pin. In the main, this is the clock reference output for the multiphase operation. On a subordinate, it is an input. Connect the main and subordinate CLK pins in a multiphase operation. When connected as a subordinate, the converter is disabled when there is no edge on the CLK pin.                                                                                                                                                                               |

| N2-N9, P2-P9, R2-R9, T3-T8 | $V_{OUT}$ | Output Voltage Pins. Connect the appropriate feedback resistor divider to $V_{OUT}^+$ and $V_{OUT}^-$ to set the desired output voltage. The $V_{OUT}$ pins deliver the inductor output current up to a maximum of 33A in steady state. Ensure that short, wide traces or several thermal vias (in a vertical construction) with sufficient current density ratings connect these pins to the point-of-load. Internally connected to bypass capacitors to GND.                 |

| N10 <sup>4</sup>           | REF       | Reference Pin. The REF pin from the main drives all the subordinate REF pins to ensure a common reference voltage for proper operation. The buffer driving the main REF pin has a 100 $\Omega$ (typical) output impedance. Ensure that only the                                                                                                                                                                                                                                |

| PIN                      | NAME                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                           | subordinate REF pins are connected to the main REF pin. Do not connect this pin to other circuits that source or sink current, or near any noise source.                                                                                                                                                                                                                     |

| P1                       | FC_GND                    | Test purpose only. Suggested to be connected to ground.                                                                                                                                                                                                                                                                                                                      |

| P10                      | AGND                      | Analog Ground. The AGND pin is the return path for all the internal sensitive analog circuits. Connect the AGND pin directly to any of the GND pins (K2-K9, L2-L9, M2-M9) for a kelvin connection to the negative terminal of the internal bypass $V_{OUT}$ capacitors.                                                                                                      |

| R1                       | FDC_GND                   | Test purpose only. Suggested to be connected to ground.                                                                                                                                                                                                                                                                                                                      |

| R10, T9-T10 <sup>2</sup> | $V_{OUT}^+$ , $V_{OUT}^-$ | Output Voltage Differential Remote Sense Pins. Voltage across these pins is regulated to 0.3V by default. Connect an appropriate feedback resistor divider from $V_{OUT}$ to $V_{OUT}^+$ and from $V_{OUT}^+$ to $V_{OUT}^-$ to set the desired output voltage at $V_{OUT}$ . See the <i>Applications Information</i> section for details on selecting the feedback network. |

| T1-T2 <sup>4</sup>       | ITH                       | Current Threshold Control Pin. On the main, this is an output. On a subordinate, it is an input. Connect the main and subordinate ITH pins in a multiphase operation. When connected in the main, the ITH pin is driven to 0V when the device is disabled (through the EN pin or I <sup>2</sup> C).                                                                          |

<sup>1</sup> See *Figure 38* in the *Applications Information* section for the main and the subordinate devices' pin configurations.

<sup>2</sup> Main device only.

<sup>3</sup> Subordinate devices only.

<sup>4</sup> Output for main device, input for subordinate devices.

The LTM3360B's method of implementing ESD protection on these pins is I<sup>2</sup>C-compliant but not SMBus-compliant. The  $V_{IN}$  power should not be removed from the device when the I<sup>2</sup>C bus is active to avoid loading the I<sup>2</sup>C bus lines through the internal ESD protection diodes.

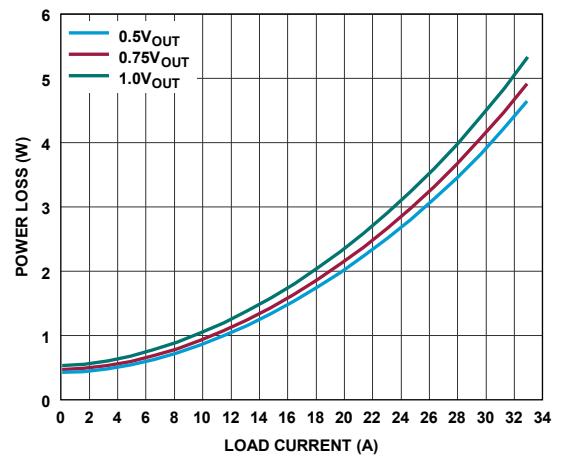

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25^\circ\text{C}$ , unless otherwise noted.

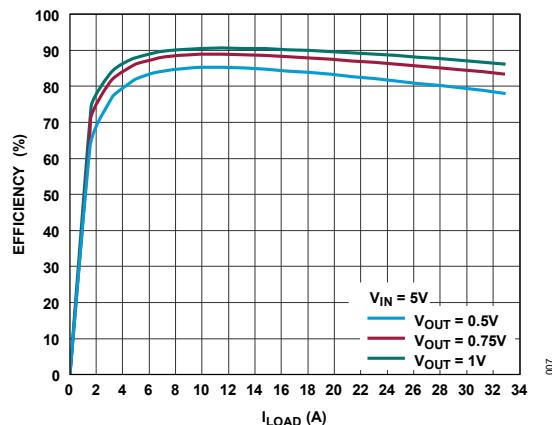

Figure 7. Efficiency vs.  $I_{LOAD}$  at Different  $V_{OUT}$

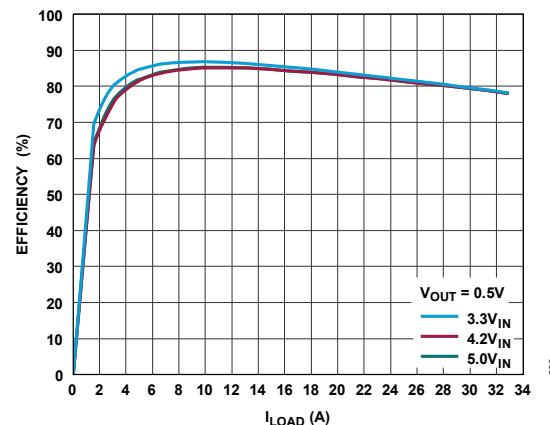

Figure 8. Efficiency vs.  $I_{LOAD}$  at Different  $V_{IN}$

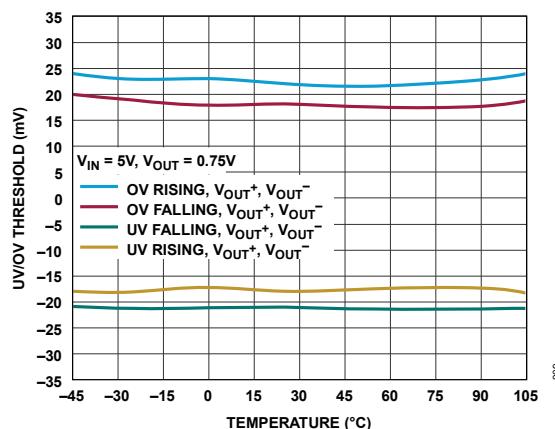

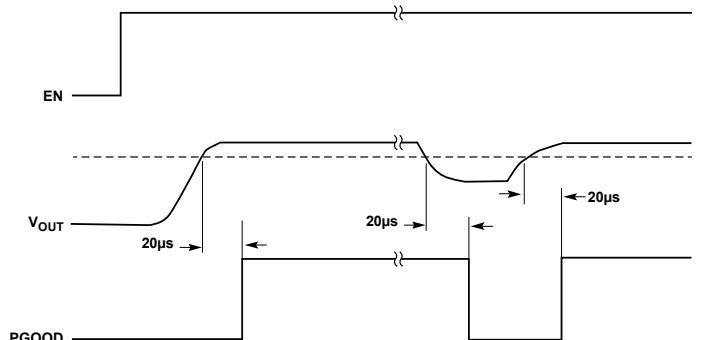

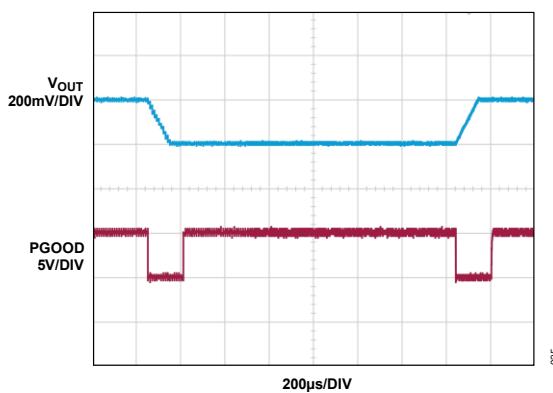

Figure 9. PGOOD UV/OV Rise and Fall

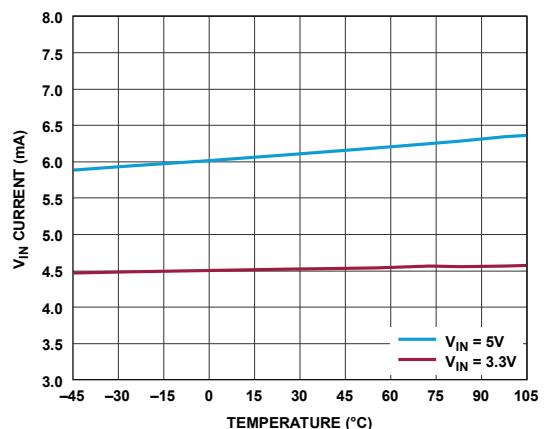

Figure 10.  $V_{IN}$  Shutdown Current vs. Temperature

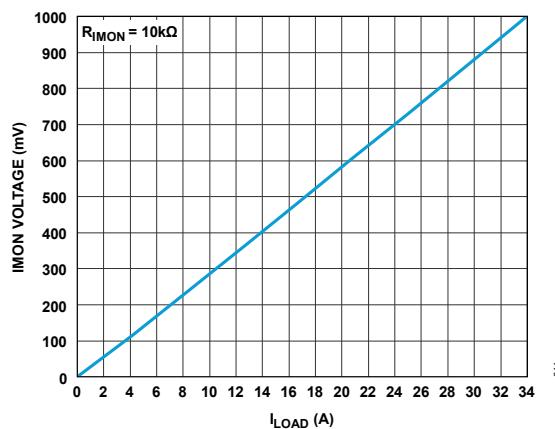

Figure 11. IMON Voltage vs.  $I_{LOAD}$

Figure 12. IMON Sensing Gain vs. Temperature

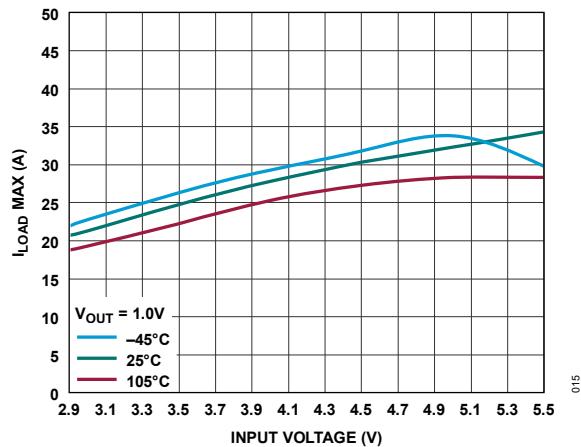

Figure 13. Maximum  $I_{LOAD}$  vs.  $V_{IN}$ Figure 14. Maximum  $I_{LOAD}$  vs.  $V_{IN}$ Figure 15. Maximum  $I_{LOAD}$  vs.  $V_{IN}$

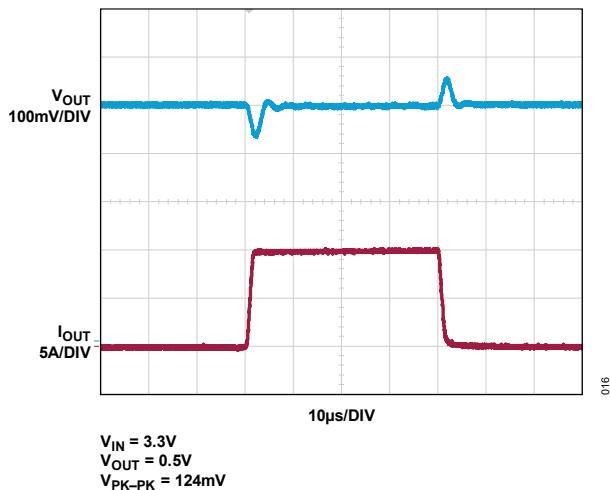

Figure 16. Load Step Up/Down Waveforms

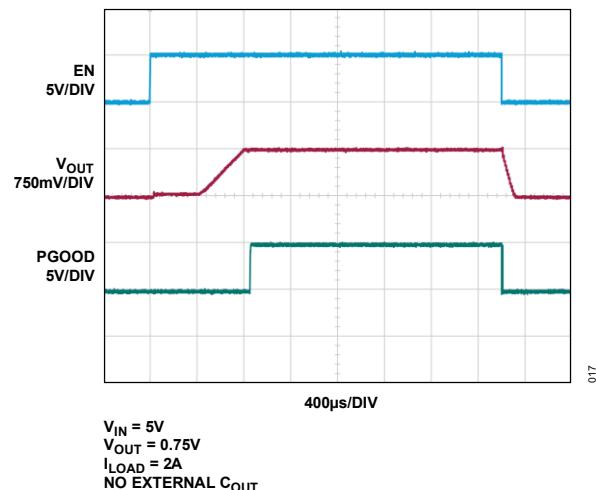

Figure 17. Startup and Shutdown Waveforms

## I<sup>2</sup>C COMMUNICATION

### Overview

When connected as the main device, the LTM3360B's I<sup>2</sup>C port allows communication with the LTM3360B for configuration and readback telemetry data. The communication protocol is compatible with the SMBus read-byte and write-byte protocols. The input thresholds for the ports are fixed at 1.1V (typical).

The registers, accessible through this port, are organized on an 8-bit address bus, and each register is 8 bits wide. The "command code" (or subordinate address) of the SMBus read/write word formats is the 8-bit address of each of these registers. The address of the LTM3360B is 7'b1101001(Wr), where Wr is 1 for write and 0 for read.

See the [Register Summary: LTM3360B Register Map](#) section for more details on the registers accessible through this interface. For the I<sup>2</sup>C main devices unable to create the repeated start needed for the read and write word protocols, a stop followed by a start may be substituted.

The serial clock line (SCL) has no output driver and does not stretch clock cycles.

The I<sup>2</sup>C port is disabled in subordinate mode.

### Register Summary: LTM3360B Register Map

Table 6. LTM3360B Register Summary

| ADDRESS | NAME          | DESCRIPTION              | RESET | ACCESS |

|---------|---------------|--------------------------|-------|--------|

| 0x1     | EN_IMON_CTRL  | Enable and IMON control  | 0x00  | R/W    |

| 0x3     | VOUT+_SETTING | Feedback voltage setting | 0x4b  | R/W    |

| 0x4     | ADC_SELECT    | ADC input selection      | 0x00  | R/W    |

| 0x5     | ADC_CTRL      | ADC setup                | 0x00  | R/W    |

| 0x6     | ADC_OUTPUT    | ADC output               | 0x00  | R      |

### Enable and IMON Control Register

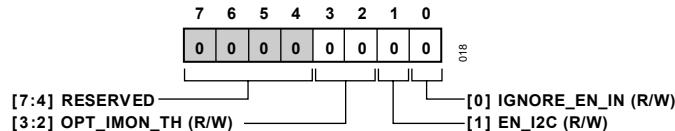

Figure 18. Address: 0x1, Reset: 0x00, Name: EN\_IMON\_CTRL

Table 7. Bit Descriptions for EN\_IMON\_CTRL

| BITS  | BIT NAME     | DESCRIPTION                                                                         | RESET | ACCESS |

|-------|--------------|-------------------------------------------------------------------------------------|-------|--------|

| [7:4] | RESERVED     | Reserved                                                                            | 0x0   | R      |

| [3:2] | OPT_IMON_TH  | IMON threshold setting:<br>00 to 99%<br>01 to 89%<br>10 to 79%<br>11 to 69%         | 0x0   | R/W    |

| 1     | EN_I2C       | Writing this bit high enables the device regardless of the state of the enable pin. | 0x0   | R/W    |

| 0     | IGNORE_EN_IN | Writing this bit high ignores the enable pin.                                       | 0x0   | R/W    |

**V<sub>OUT</sub>+ Setting Register***Figure 19. Address: 0x3, Reset: 0x4b, Name: VOUT+\_SETTING***Table 8. Bit Descriptions for VOUT\_SETTING**

| BITS  | BIT NAME | DESCRIPTION                                                                                                                                                                                                                           | RESET | ACCESS |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [7:0] | OPT_VOUT | Feedback Voltage setting – range 300mV to 1000mV, LSB ~ 4mV:<br>11111111 (0xff – 255): 1000mV<br>10111011 (0x4b – 75): 300mV (factory program default at power-up)<br>01000111 (0x4a – 74): 297mV (minimum allowable programmed code) | 0x4b  | R/W    |

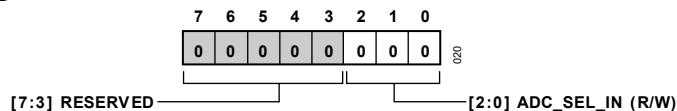

**ADC Input Selection Register***Figure 20. Address: 0x4, Reset: 0x00, Name: ADC\_SELECT***Table 9. Bit Descriptions for ADC\_SELECT**

| BITS  | BIT NAME   | DESCRIPTION                                                                                                                                                                                                                                                         | RESET | ACCESS |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [7:3] | RESERVED   | Reserved                                                                                                                                                                                                                                                            | 0x0   | R      |

| [2:0] | ADC_SEL_IN | 3-bit input select for ADC. Write to this register to initiate a new conversion cycle.<br>000: IMON<br>001: Temperature monitor<br>010: V <sub>OUTP</sub> monitor<br>011: V <sub>OUTN</sub> monitor<br>100: V <sub>IN</sub> monitor<br>101 to 111: IMON (redundant) | 0x0   | R/W    |

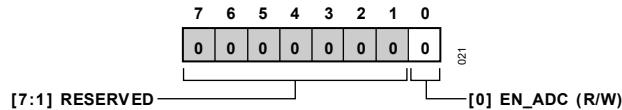

**ADC Setup Register***Figure 21. Address: 0x5, Reset: 0x00, Name: ADC\_CTRL***Table 10. Bit Descriptions for ADC\_CTRL**

| BITS  | BIT NAME | DESCRIPTION                            | RESET | ACCESS |

|-------|----------|----------------------------------------|-------|--------|

| [7:1] | RESERVED | Reserved                               | 0x0   | R      |

| 0     | EN_ADC   | Writing this bit high enables the ADC. | 0x0   | R/W    |

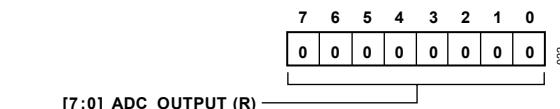

**ADC Output Register***Figure 22. Address: 0x6, Reset: 0x00, Name: ADC\_OUTPUT***Table 11. Bit Descriptions for ADC\_OUTPUT**

| BITS  | BIT NAME   | DESCRIPTION | RESET | ACCESS |

|-------|------------|-------------|-------|--------|

| [7:0] | ADC_OUTPUT | ADC output. | 0x0   | R      |

## THEORY OF OPERATION

### LTM3360B Overview

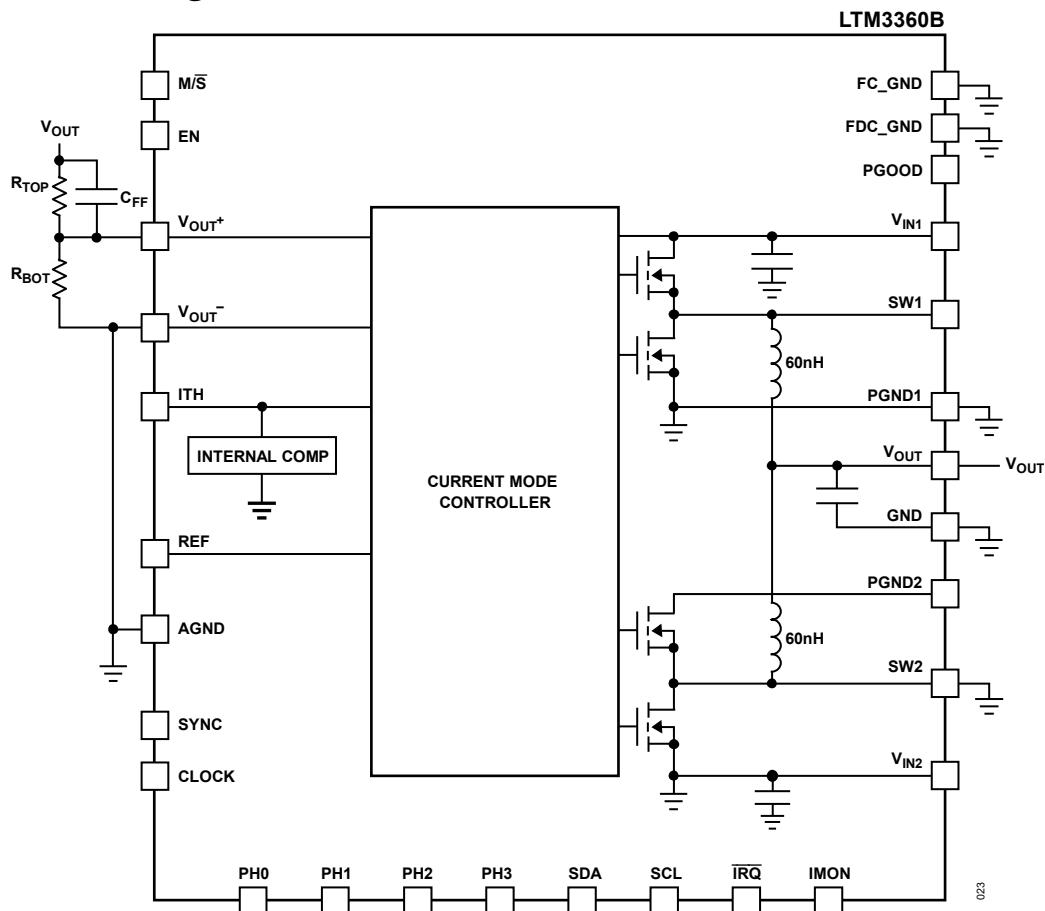

The LTM3360B is a power  $\mu$ Module DC-to-DC regulator with high-current, high-density, constant-frequency, and current-mode architecture, which is capable of efficiently delivering 33A at output voltages as low as 300mV. The I<sup>2</sup>C interface allows for programmability of various features as well as readback of output current. The high-fixed switching frequency of 5MHz permits the integration of not only the input and the output capacitors, but also the integration of the power inductor, resulting in the highest density of output current to total board footprint achievable in the industry, with minimal external components required. The high-density and small footprint, with the ability to synchronize the switching frequency to an external clock, enable systems using the LTM3360B to easily maintain a low-noise/EMI profile. Some of the features of the LTM3360B include internal compensation to optimize transient response, soft start to manage inrush current, an output power good function to report when  $V_{OUT}$  is within regulation, and an  $\overline{IRQ}$  pin to signal status change. For higher current applications, multiple LTM3360Bs are easily paralleled with the clock (CLK) and current threshold control (ITH) pins, along with the REF pins. In multi-device applications, one device acts as the main controller, and the other devices operate as subordinate devices. The devices are subordinate if the M/S pin is connected to GND.

### Simplified Block Diagram

Figure 23. LTM3360B Simplified Block Diagram

## Power-On

The LTM3360B uses the EN pin and the EN\_I2C bit in the EN\_IMON\_CTRL register to enable and disable the device. The device can only be enabled if the input supply at  $V_{INn}$  is above the UVLO rising threshold.

Setting the EN\_I2C bit high enables the device regardless of the state of the EN pin. And if the IGNORE\_EN\_IN bit in the same EN\_IMON\_CTRL register is low, once the EN pin exceeds the input threshold, the device is enabled.

To disable the device, both the EN\_I2C bit and the EN pin must be low if the IGNORE\_EN\_IN bit is low. However, if the IGNORE\_EN\_IN bit is high, setting the EN\_I2C bit disables the device regardless of the state of the EN pin.

The LOGIC Equation 1 determines the state of the internal enable signal (INT\_EN).

$$INT_{EN} = [\overline{IGNORE\_EN\_IN} \times EN\_PIN] + ENI^2C \quad (1)$$

When the internal enable signal is high, the device is enabled and starts switching after 100 $\mu$ s (typical). On the other hand, when the internal enable signal is low, the device powers down, and all the internal logic states are reset to their default values.

## Voltage Regulation

The internal bottom power switch is turned on at the beginning of each clock cycle. Current in the inductor then decreases until the inductor current comparator trips and turns off the bottom power switch. The valley inductor current at which the bottom switch turns off is controlled by the voltage on the internal ITH node. The error amplifier servos this ITH node by comparing the differential voltage on the  $V_{OUT}$  sense pins ( $V_{OUT}^+$ ,  $V_{OUT}^-$ ) with a factory-programmed reference of 0.3V.

When the load current increases, it causes a reduction in the  $V_{OUT}$  sense pins voltage relative to the reference voltage, leading the error amplifier to raise the ITH voltage until the average inductor current matches the new load current. When the bottom power switch turns off, the synchronous top power switch turns on until the next clock cycle begins or inductor current rises to the top switch current limit.

If overload conditions result in excessive current flowing through the bottom switch, the next clock cycle is delayed (pulse-skipped) until the switch current returns to a safe level.

## Forced Continuous Mode Operation

The LTM3360B operates in forced continuous mode (FCM). In FCM, the oscillator operates continuously. The bottom switch turns on every cycle, and regulation is maintained by allowing the inductor current to reverse at light load. This mode allows the buck regulator to run at a fixed frequency with minimal output ripple. With this FCM of operation, if the inductor current reaches the negative current limit (into the SW pin), the bottom switch turns off for the remainder of the cycle to limit the reverse current.

## Soft Start and Output Power Good

Soft-starting the output during startup prevents a current surge on the input supply and/or output voltage overshoot. During the soft start, the output voltage proportionally tracks the internal reference voltage ramp. The soft start rate is set to a default (typ 2mV/ $\mu$ s) on feedback in the internal one-time programmable (OTP) memory and cannot be changed through I<sup>2</sup>C. Consult with the factory for startup rates other than the programmed default.

In the case of a fault condition, the soft start voltage is reset to 0V. The ramp restarts when the fault is cleared, and the output returns to its default value. Fault conditions that initiate the soft start ramp include disabling the device,  $V_{INn}$  is undervoltage, or thermal shutdown.

When operating as a main device, the power good status is indicated on the PGOOD pin. If the output voltage is within the specified power good voltage window, the output is considered good, and the open-drain PGOOD pin becomes high impedance. The PGOOD output is typically pulled high with an external resistor (2k $\Omega$  recommended).

If the output voltage is outside the specified power good voltage window, the output is considered NOT good, and the internal pull-down device pulls the PGOOD pin low. The PGOOD pin is also pulled low under the following conditions: the device is disabled,  $V_{IN}$  is undervoltage, or thermal shutdown is active. To filter noise and short-duration output voltage transients, the threshold has built-in hysteresis and a 20 $\mu$ s time delay to report PGOOD. *Figure 24* shows the timing relationship between EN,  $V_{OUT}$ , and PGOOD. If a device is acting as a subordinate (M/S = 0V), the PGOOD function is disabled since only the main device power good comparators are enabled to detect if regulation is within the power good window.

*Figure 24. Output Power Good (PGOOD) Timing*

## Output Dynamic Voltage Scaling (DVS) Rate

When the output voltage regulation target is changed through the OPT\_VOUT bits in the VOUT\_SETTING register, the dynamic voltage scaling (DVS) rate is similarly set to a default (typical 2mV/ $\mu$ s) in the internal OTP memory and cannot be changed through I<sup>2</sup>C. Consult with the factory for DVS rates other than the programmed default. The PGOOD pin is driven LOW before the DVS starts and then released HIGH after the DVS process completes. *Figure 25* shows the timing relationship between  $V_{OUT}$  and PGOOD. The PGOOD DVS function can be disabled by I<sup>2</sup>C communication by setting the register at address 0x7 from x0 to x1.

*Figure 25. Output Dynamic Voltage Scaling (DVS)*

## Power-Down

When the device is disabled (INT\_EN = 0), the inductor current returns to zero, and the output discharge resistor (typical 1k $\Omega$ ) is turned on. Much of the internal circuitry is disabled when the internal enable signal (INT\_EN) is set

low to reduce shutdown current. Disabling the internal circuitry also results in all the registers being reset to their default programmed values in preparation for the next restart.

## Overtemperature Protection

To prevent thermal damage to the LTM3360B, the device incorporates an overtemperature (OT) function. When the die temperature reaches 150°C (typical, not tested), the switcher is shut down and remains in shutdown until the die temperature falls below 140°C (typical, not tested).

When an OT event occurs, the  $\overline{\text{IRQ}}$  pin pulls low to indicate an overtemperature fault condition. Note that multiple devices can assert the  $\overline{\text{IRQ}}$  pin.

For systems with subordinate devices, if the  $\overline{\text{IRQ}}$  pins of the subordinate devices are connected to the main device  $\overline{\text{IRQ}}$  pin, then all the  $\overline{\text{IRQ}}$  pins are low anytime one or more of the devices are above the over temperature threshold (typical 160°C, not tested).

## Overcurrent Warning

The average current of the inductor is represented as a pull-up current at the IMON pin. The average inductor current to the IMON output current gain is set to typically 1/340,000, with 100 $\mu$ A IMON output current representing 34A average inductor current. When a resistor is connected to this IMON pin, the average inductor current is then translated to a voltage.

The voltage on the IMON pin is monitored by an overcurrent warning comparator. By default (at power-up), this comparator threshold is set to 0.99V. However, this threshold is adjustable through I<sup>2</sup>C from 0.69V to 0.99V in 0.1V increments.

When the IMON voltage exceeds this overcurrent warning threshold, the  $\overline{\text{IRQ}}$  pin pulls low.

For systems with subordinate devices, typically, the IMON pins of the subordinate devices are connected to the main device IMON pin. Then all the pull-up currents of the devices are summed together. Each of the device IMON output current gain to its own output current is typically 1/340,000. Therefore, by scaling the resistor value connected to this common IMON node, the real-time total average inductor current of all the LTM3360B (main and subordinates included) is translated to a single voltage on this common IMON node.

If the  $\overline{\text{IRQ}}$  pins of the subordinate devices are also connected to the main device  $\overline{\text{IRQ}}$  pin, then all the  $\overline{\text{IRQ}}$  pins are low any time the total system current exceeds the overcurrent warning threshold set in the main LTM3360B.

## Output Short-Circuit Operation

As described in the *Voltage Regulation* subsection, the valley inductor current at which the bottom switch turns off (and therefore turning on the top switch) is controlled by the voltage on the internal ITH node.

If the output current increases, the error amplifier raises the ITH pin voltage (allowing the top switch to turn on earlier in the clock cycle and therefore for a longer period) until the average inductor current matches the load current. The LTM3360B clamps the maximum ITH pin voltage, thereby limiting the maximum valley inductor current. This clamp point is set to the bottom switch's maximum valley current limit.

To ensure safe operations of the top switch under all conditions, the current through the top switch is monitored whenever it is turned on. The maximum current through the top switch is set to the top switch's maximum peak current limit.

When the output is shorted to ground, the inductor current decays very slowly during a single switching cycle because the voltage across the inductor is low. If the inductor current measured through the bottom power switch

is greater than the bottom switch's max valley current limit, then the bottom switch is held on and the top power switch is held off. Subsequent switching cycles are skipped until the inductor current is reduced below the bottom switch's max valley current limit.

## Synchronization

When operating as the main, the LTM3360B internal oscillator is synchronized through an internal phase-locked loop (PLL) circuit to an external frequency by applying a square wave clock signal to the SYNC pin. When synchronized, the bottom power switch's turn-on is locked to the rising edge of the external frequency source.

The slope compensation is automatically adapted to the external clock frequency. After detecting an external clock on the first rising edge of the SYNC pin, the internal PLL gradually adjusts its operating frequency to match the frequency and phase of the signal on the SYNC pin.

When the external clock is abruptly removed, the LTM3360B detects the absence of the external clock within approximately 10 $\mu$ s (typical). During this detection time, the PLL continues to provide clock cycles at a gradually decreasing frequency to a minimum of 4.5MHz (typical). Once the external clock removal has been detected, the oscillator gradually adjusts its operating frequency back to the default frequency of 5MHz (typical).

When operating as subordinates, the main LTM3360B provides a reference clock through its CLK pin. This is to ensure that any external synchronization source only needs to drive the main's SYNC pin without worrying about the capacitive loading of multiple subordinates. To ensure correct phasing and synchronization of the subordinates, their CLK pins need to be connected to each other and to the main CLK pin.

Identical to the main synchronization of its internal clock to the SYNC pin, the subordinates' internal PLL synchronizes its internal clock to the CLK pin.

## APPLICATIONS INFORMATION

The LTM3360B is designed to be a highly integrated complete step-down DC-to-DC converter solution maximizing output current density per unit board surface area. See [Figure 23](#) (LTM3360B Simplified Block Diagram) as a reference for the following sections.

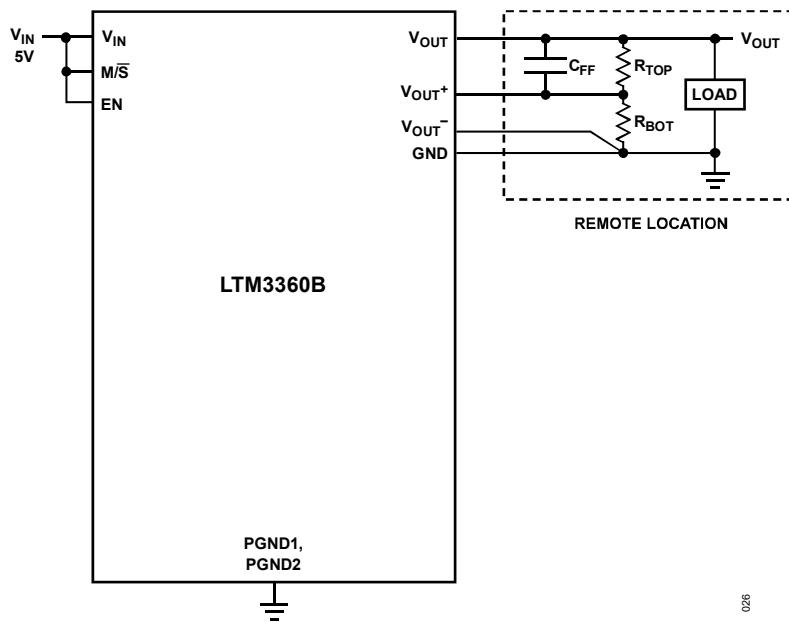

### Output Voltage Programming/Sensing

The LTM3360B has an internal reference voltage of 0.3V. When operating as the main device, the internal error amplifier (EA) compares the output sense voltage ( $V_{OUT}^+$  and  $V_{OUT}^-$ ) to the internal reference voltage. A buffered version of this internal reference voltage is accessible on the REF pin.

The output voltage level of the LTM3360B can be changed by selecting the appropriate resistor dividers,  $R_{TOP}$  and  $R_{BOT}$ , between  $V_{OUT}$ ,  $V_{OUT}^+$ , and  $V_{OUT}^-$  as shown in [Figure 26](#). Use values of less than  $2k\Omega$  (0.1% tolerance) for  $R_{BOT}$ .

Calculate  $R_{TOP}$  based on the desired output voltage using Equation 2. See [Table 13](#) for the recommended values for  $R_{TOP}$  and  $R_{BOT}$ .

$$V_{OUT} = \left(1 + \frac{R_{TOP}}{R_{BOT}}\right) \times 300mV \quad (2)$$

026

**Figure 26. Resistor Divider for Setting the Output Voltage**

Place the resistor dividers,  $R_{TOP}$  and  $R_{BOT}$ , as close to the load where the voltage needs to be sensed. The  $V_{OUT}^+$  and  $V_{OUT}^-$  should always be connected directly across  $R_{BOT}$ , near the desired sense location. Minimize impedance between the  $V_{OUT}$  and GND pins of the device, and sense locations for maximum accuracy. Thought should be given to inaccuracies that occur due to large currents in the output ground (GND) plane when selecting the  $V_{OUT}$  location.

The LTM3360B AGND pin is the ground reference for the internal analog circuitry. For proper functioning of the device, connect the AGND pin to the GND pins as close to the device as possible. All the signal components, such as the IMON resistor, should be referenced to the AGND node. The AGND node carries very little current and can therefore be a minimal-size trace. See the [PC Board Layout Considerations](#) section for more information.

## Setting the Output Overcurrent Warning Threshold

The IMON pin sources a current that is proportional to the average output current. At 34A of load current at  $V_{OUT}$ , the IMON pin outputs 100 $\mu$ A (typical) of current. By connecting a resistor on this pin, a voltage representing the average output current is obtained according to Equation 3.

$$V_{IMON} = \frac{I_{OUT}(A) \times R_{IMON}}{340,000} \quad (3)$$

For example, with a 10k $\Omega$  resistor connected between IMON and GND, the IMON voltage gain to the output voltage is 29.1mV/A with a voltage of 0.99V for a 34A output current.

As discussed in the *Theory of Operation* section, the voltage on the IMON pin is monitored by an overcurrent warning comparator. The output overcurrent warning threshold has four different thresholds, whose default is programmed at the factory. Beyond the default value, this threshold can be programmed over through I<sup>2</sup>C. This threshold can be changed by setting the OPT\_IMON\_TH bit field, as shown in *Table 12*.

**Table 12. OPT\_IMON\_TH Bit Field Settings**

| OPT_IMON_TH<br>(BITS) | PERCENTAGE OVER 33A<br>(%) | VOLTAGE<br>(V) |

|-----------------------|----------------------------|----------------|

| 00 (default)          | 103                        | 0.99           |

| 01                    | 93                         | 0.89           |

| 10                    | 82                         | 0.79           |

| 11                    | 72                         | 0.69           |

By default (at power-up), this comparator threshold is set to 0.99V. However, this threshold is adjustable through I<sup>2</sup>C from 0.69V to 0.99V in 0.1V increments.

When the IMON pin voltage goes above the overcurrent alert threshold, the  $\overline{IRQ}$  pin pulls low.

## Reverse Output Current Limit

The LTM3360B operates in forced continuous mode, allowing the current in the inductor to go negative. To prevent damage to the device, the reverse inductor current is limited by internal circuitry. The limit is set to -7A (typical).

## Output Pull-Down

When the LTM3360B is disabled, a resistive pull-down is connected between  $V_{OUT}$  and GND (typical 1k $\Omega$ ).

## Synchronization

The switching regulator clock source may be switched from the internal oscillator to a clock on the SYNC pin. The LTM3360B can sync to an externally applied clock in the range of 4.5MHz to 5.5MHz at the appropriate logic levels.

As discussed in the *Theory of Operation* section, when operating as the main, the LTM3360B has an edge detector on the SYNC pin. When detecting an external clock on the first rising edge of the SYNC pin, the internal PLL gradually adjusts its operating frequency to match the frequency and phase of the signal on the SYNC pin.