Dual Channel 9A, 16V PolyPhase Step-Down Silent Switcher 2 with Digital Power System Management

### **FEATURES**

- Silent Switcher® 2 Architecture: Enables Compact. Efficient, Low EMI Solution

- ► PMBus/I<sup>2</sup>C Serial Interface

- ► Telemetry Read Back Includes: V<sub>OUT</sub>, I<sub>OUT</sub>, V<sub>IN</sub>, Die Temperature, Faults

- ► Programmable Voltage, Current Limit, Digital Soft-Start/Stop, Sequencing, UV/OV, Phase, Frequency (up to 4MHz), Loop Compensation

- ► Integrated EEPROM with Fault Event Log

- ► Set Key Parameters with Configuration Resistors for **Operation without Programming**

- ±0.25% Output Voltage Accuracy over Temperature from 0.6V to 1.375V

- PolyPhase® Load Sharing for up to Eight Phases

- Wide V<sub>IN</sub> Range: Down to 2.9V, or 1.5V with EXTV<sub>CC</sub> up to 16V

- Over 94% Peak Efficiency at 1MHz, 12V<sub>IN</sub> to 3.3V<sub>OUT</sub>

- $V_{OUT}$  Range: 0.4V to 5.5V (up to 85% x  $V_{IN}$ )

- Differential Remote V<sub>OUT</sub> Sense

- **External Frequency Synchronization**

- 36-Lead (4mm x 5mm) LQFN Package

#### **APPLICATIONS**

- ► Communications, Storage, and Industrial Systems

- ▶ Data Center and Solid-State Drive Power Supplies

#### DESCRIPTION

The LT7184S is a dual-output monolithic PolyPhase DC/DC synchronous step-down regulator that delivers up to 7A of continuous current from both channels simultaneously and supports loads from -8A to +9A in either channel. The LT7184S features second-Silent Switcher® generation architecture integrated V<sub>IN</sub> bypass capacitors for fast, clean, lowovershoot switching edges to deliver high efficiency at switching frequencies and minimize Electromagnetic interference (EMI) emissions. The I<sup>2</sup>Cbased PMBus 1.3-compliant serial interface enables control of device functions and provides telemetry information for system monitoring. The LT7184S is supported by the LTpowerPlay® graphical user interface tool. The output voltage, frequency, phase, and device address can be configured using resistors for operation without programming. Settings can also be written via the serial interface and/or stored in EEPROM. The controlled on-time valley current mode control architecture with 25ns (typical) minimum on-time enables high switching frequency at low output voltage with excellent transient response in a small overall solution size.

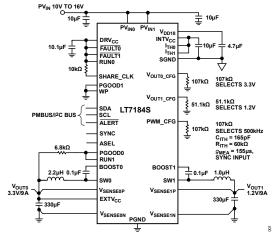

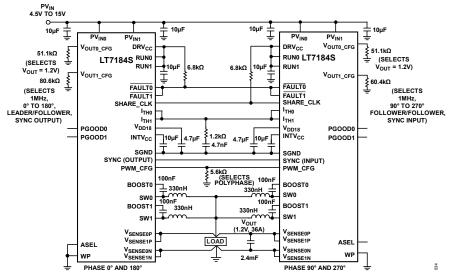

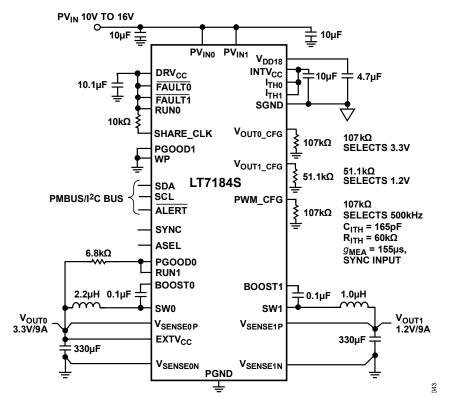

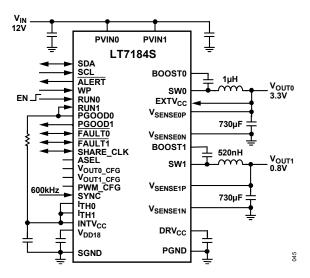

### TYPICAL APPLICATION

Figure 1. Typical Application for the LT7184S

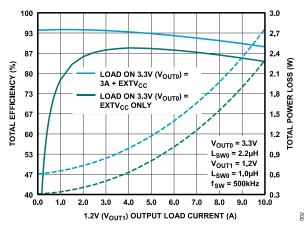

Figure 2. LT7184S 12V<sub>IN</sub> Typical Application Efficiency

# **TABLE OF CONTENTS**

| Features                                            | 1  |

|-----------------------------------------------------|----|

| Applications                                        | 1  |

| Description                                         | 1  |

| Typical Application                                 | 1  |

| Revision History                                    | 3  |

| Absolute Maximum Ratings                            | 4  |

| Thermal Resistance                                  | 5  |

| ESD Caution                                         | 5  |

| Specifications                                      | 6  |

| Pin Configurations and Function Descriptions        | 12 |

| Typical Performance Characteristics                 | 16 |

| Block Diagram                                       | 21 |

| Theory of Operation                                 | 22 |

| Overview                                            | 22 |

| Switching Regulator Control Loop                    | 23 |

| Soft-Start                                          | 23 |

| EEPROM                                              | 23 |

| Power-up and Initialization                         | 24 |

| Shutdown                                            | 24 |

| Warning and Fault Handling                          | 25 |

| FAULT PINS                                          | 26 |

| PGOOD PINS                                          | 26 |

| ALERT PIN                                           | 26 |

| FAULT Event Logging                                 | 26 |

| Applications Information                            | 28 |

| Using Resistor Configuration Pins                   | 28 |

| Setting Output Voltage                              | 28 |

| Switching Frequency and Phase                       | 29 |

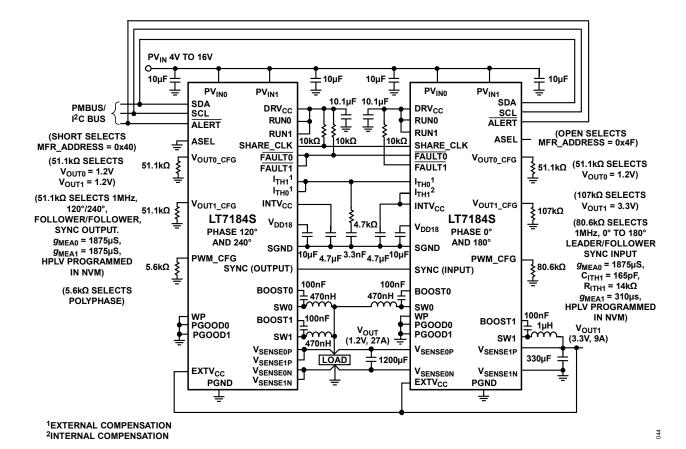

| PolyPhase Load Sharing                              | 31 |

| Configuring Device Address with ASEL Pin            | 33 |

| Operating Frequency Trade-Offs                      | 33 |

| Minimum On-Time and Minimum Off-Time Considerations | 34 |

| PROGRAMMABLE CURRENT LIMIT                          | 34 |

| Inductor Selection                                  | 35 |

|                | Input and Output Capacitors                     | 36 |

|----------------|-------------------------------------------------|----|

|                | Programmable PWM Control Loop Compensation      | 36 |

|                | Control Loop Model                              | 37 |

|                | Software-Configurable Sequencing                | 39 |

|                | Event-Based Sequencing                          | 39 |

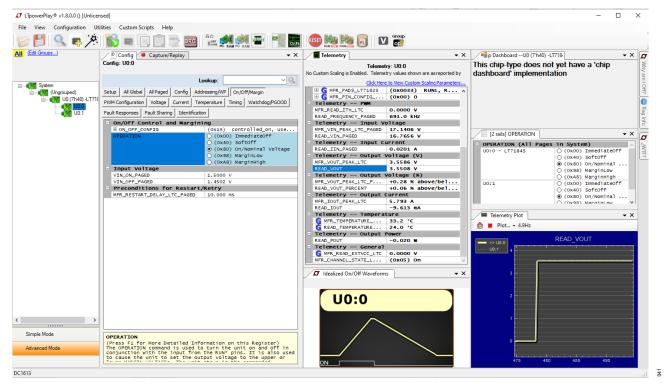

|                | LTPowerPlay GUI                                 | 39 |

|                | Board Layout Considerations                     | 40 |

|                | Thermal Considerations                          | 41 |

| T <sub>2</sub> | pical Applications                              | 42 |

| P              | Mbus Command Summary                            | 44 |

|                | PMbus/I <sup>2</sup> C Serial Interface Summary | 44 |

|                | utline Dimensions                               |    |

| $\sim$         | rdering Guide                                   | 51 |

# **REVISION HISTORY**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION       | UNITS |

|--------------------|------------------|-------------------|-------|

| 0                  | 10/24            | Initial release   | l     |

| А                  | 8/25             | Updated Figure 16 | 18    |

2

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise specified.

**Table 1. Absolute Maximum Ratings**

| PARAMETER                                                                                                                                          | RATING          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| $PV_{IN0}$ , $PV_{IN1}$                                                                                                                            | -0.3V to +20V   |

| Average PV <sub>IN</sub> Input Supply Current <sup>2</sup>                                                                                         | 3A              |

| EXTV <sub>CC</sub>                                                                                                                                 | -0.3V to +6V    |

| V <sub>SENSEOP</sub> , V <sub>SENSE1P</sub>                                                                                                        | -0.3V to +6V    |

| V <sub>SENSEON</sub> , V <sub>SENSE1N</sub>                                                                                                        | -0.3V to +0.3V  |

| I <sub>TH0</sub> , I <sub>TH1</sub>                                                                                                                | -0.3V to +6V    |

| SYNC, PWM_CFG, WP, SHARE_CLK, ALERT, SDA, SCL, FAULTO, FAULT1, RUNO, RUN1, PGOODO, PGOOD1, ASEL, V <sub>OUT0_CFG</sub> , and V <sub>OUT1_CFG</sub> | -0.3V to +6V    |

| BOOST0 with respect to SW0                                                                                                                         | -0.3V to +6V    |

| BOOST1 with respect to SW1                                                                                                                         | -0.3V to +6V    |

| Operating Junction Temperature 3, 4, 5                                                                                                             | -40°C to +150°C |

| T <sub>J</sub>                                                                                                                                     | 150°C           |

| Storage Temperature Range                                                                                                                          | -65°C to +150°C |

| Maximum Peak Re-flow (Package Body) Temperature                                                                                                    | 260°C           |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

The average input current to each PV<sub>IN</sub> pin on the LT7184S is a function of the PV<sub>IN</sub> input voltage, the programmed output voltage that channels load current, and the efficiency as:

$$I_{PVIN} = \frac{V_{OUT} \times I_{OUT}}{PV_{IN} \times Efficiency}$$

The output voltage and current can be programmed so that the  $PV_{IN}$  input current exceeds the maximum average current rating for the LT7184S. Exceeding the maximum average input current rating for the LT7184S can affect device reliability and lifetime.

The LT7184S is specified over the -40°C to +150°C operating junction temperature range. High junction temperatures degrade operating lifetimes: operating lifetime is derated for junction temperatures greater than 125°C. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance, and other environmental factors.

The LT7184S includes overtemperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature is exceeded when this protection is active. Continuous operation above the specified maximum operating junction temperature will reduce the device's lifetime.

analog.com Rev 1 | 4 of 52

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability and lifetime.

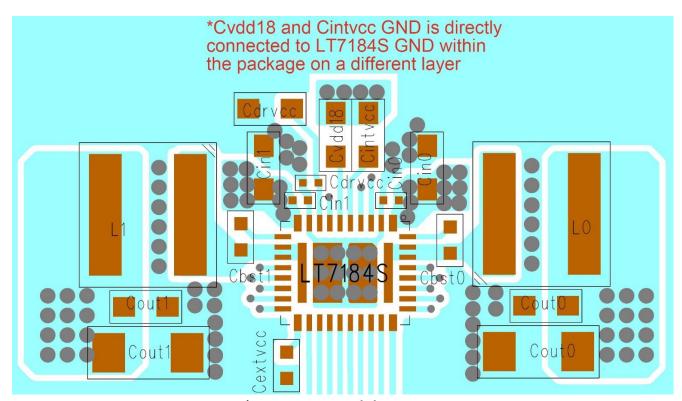

#### Thermal Resistance

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

**Table 2. Thermal Resistance**

| PACKAGE TYPE      | $\theta_{JA}^3$ | $oldsymbol{	heta}_{	extsf{JC-TOP}}^4$ | $oldsymbol{	heta}_{JC-BOTTOM}^4$ | UNIT      |

|-------------------|-----------------|---------------------------------------|----------------------------------|-----------|

| LQFN <sup>1</sup> | 31.0            | 29.2                                  | 2.6                              | (°C/Watt) |

| LQFN <sup>2</sup> | 19.9            | 29.2                                  | 2.6                              | (°C/Watt) |

<sup>&</sup>lt;sup>1</sup> Test Condition 1: Thermal impedance simulated values based upon use of 2S2P JEDEC FR-4 PCB 114mm x 76mm, 1.6mm thick in a one cubic foot sealed enclosure.

#### **ESD Caution**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev 1 | 5 of 52

<sup>&</sup>lt;sup>2</sup> Test Condition 2: Thermal impedance simulated values based upon the demonstration board in still air.

$<sup>^{3}</sup>$   $\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance.

$<sup>^4</sup>$   $\theta_{\text{JC-TOP}}$  and  $\theta_{\text{JC-BOTTOM}}$  are the natural conduction junction-to-case thermal resistances.

# **SPECIFICATIONS**

### **Table 3. Electrical Characteristics**

$(T_A = 25^{\circ}C \text{ for typical values. For minimum and maximum values, specifications apply over the full operating temperature range unless otherwise noted.)$

| PARAMETER                                                                                                   | CONDITIONS                                                                                                                      | MIN   | TYP  | MAX                        | UNITS |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|------|----------------------------|-------|

| INPUT SUPPLY                                                                                                |                                                                                                                                 |       |      |                            |       |

| Channel 0 Input Supply<br>Range                                                                             | EXTV <sub>CC</sub> < 3.0                                                                                                        | 2.9   |      | 16                         | V     |

| Channel 0 Input Supply<br>Range with EXTV <sub>CC</sub>                                                     | $3V \le EXTV_{CC} \le 5.5V$                                                                                                     | 1.5   |      | 16                         | V     |

| Channel 1 Input Supply<br>Range                                                                             | $PV_{IN0} \ge 2.9V \text{ or } 3V \le EXTV_{CC} \le 5.5V$                                                                       | 1.5   |      | 16                         | V     |

| Optional EXTV <sub>cc</sub> Input<br>Supply Range                                                           |                                                                                                                                 | 3     |      | 5.5                        | V     |

| EXTV <sub>CC</sub> + PV <sub>IN0</sub> + PV <sub>IN1</sub><br>Quiescent Current, both<br>Channels Switching | EXTV <sub>CC</sub> = 4V, f <sub>SW</sub> = 1MHz,<br>PV <sub>IN0</sub> = PV <sub>IN1</sub> = 12V, No Load, T <sub>A</sub> = 25°C |       | 44   |                            | mA    |

| EXTV <sub>CC</sub> + PV <sub>INO</sub> Current,<br>Shutdown                                                 | Shutdown, T <sub>A</sub> = 25°C                                                                                                 |       | 7.4  |                            |       |

| Initialization Time <sup>1</sup>                                                                            | With CFG Pins Enabled (Default),<br>T <sub>A</sub> = 25°C                                                                       |       | 13   |                            | ms    |

|                                                                                                             | CFG Pins Ignored, T <sub>A</sub> = 25°C                                                                                         |       | 10   |                            | ms    |

| SWITCHING REGULATORS                                                                                        |                                                                                                                                 | T     | 1    |                            | _     |

|                                                                                                             | $PV_{IN} \ge 6.5V$                                                                                                              | 0.4   |      | 5.5                        | V     |

| V <sub>OUT</sub> Range                                                                                      | PV <sub>IN</sub> < 6.5V                                                                                                         | 0.4   |      | 0.85 x<br>PV <sub>IN</sub> | V     |

| V <sub>OUT</sub> Set-Point Accuracy                                                                         | High-Performance, Low V <sub>OUT</sub> Mode,<br>0.6V ≤ V <sub>OUT</sub> ≤ 1.375V                                                | -0.25 |      | 0.25                       | %     |

|                                                                                                             | $0.4V \le V_{OUT} \le 5.5V$                                                                                                     | -0.5  |      | 0.5                        | %     |

| V <sub>OUT</sub> Set-Point Resolution                                                                       |                                                                                                                                 |       | 1    |                            | mV    |

| V <sub>SENSEOP</sub> , V <sub>SENSE1P</sub> Input<br>Resistance                                             | Switcher (SWR0 or SWR1) Enabled, or 250Ω Pull-Down Disabled, T <sub>A</sub> = 25°C                                              |       | 30   |                            | kΩ    |

| Error Amplifier<br>Transconductance<br>Programming Resolution                                               |                                                                                                                                 |       | 3    |                            | bits  |

| Error Amplifier<br>Transconductance<br>(g <sub>m(MAX)</sub> )                                               | Full V <sub>OUT</sub> Range Mode,<br>0.4V ≤ V <sub>OUT</sub> ≤ 5.5V,<br>Includes Internal V <sub>OUT</sub> Feedback Divider     |       | 1240 |                            | μS    |

| Error Amplifier<br>Transconductance<br>(g <sub>m(MIN)</sub> )                                               | Full V <sub>OUT</sub> Range Mode,<br>0.4V ≤ V <sub>OUT</sub> ≤ 5.5V,<br>Includes Internal V <sub>OUT</sub> Feedback Divider     |       | 155  |                            | μS    |

| Error Amplifier<br>Transconductance<br>(gm step size)                                                       | Full V <sub>OUT</sub> Range Mode,<br>0.4V ≤ V <sub>OUT</sub> ≤ 5.5V,<br>Includes Internal V <sub>OUT</sub> Feedback Divider     |       | 155  |                            | μS    |

analog.com Rev 1 | 6 of 52

$(T_A = 25^{\circ}\text{C for typical values.}$  For minimum and maximum values, specifications apply over the full operating temperature range unless otherwise noted.)

| PARAMETER                                           | CONDITIONS                                                               | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------|--------------------------------------------------------------------------|------|------|------|-------|

| Error Amplifier                                     | High-Performance, Low V <sub>OUT</sub> Mode,                             |      | İ    |      |       |

| Transconductance                                    | $0.6V \le V_{OUT} \le 1.375V$ ,                                          |      | 5000 |      | μS    |

| $(g_{m(MAX)})$                                      | Includes Internal V <sub>OUT</sub> Feedback Divider                      |      |      |      |       |

| Error Amplifier                                     | High-Performance, Low V <sub>OUT</sub> Mode,                             |      |      |      |       |

| Transconductance                                    | $0.6V \le V_{OUT} \le 1.375V$ ,                                          |      | 625  |      | μS    |

| $(g_{m(MIN)})$                                      | Includes Internal V <sub>OUT</sub> Feedback Divider                      |      |      |      |       |

| Error Amplifier                                     | High-Performance, Low V <sub>OUT</sub> Mode,                             |      |      |      |       |

| Transconductance                                    | $0.6V \le V_{OUT} \le 1.375V$ ,                                          |      | 625  |      | μS    |

| (g <sub>m</sub> step size)                          | Includes Internal V <sub>OUT</sub> Feedback Divider                      |      |      |      |       |

| Internal Compensation                               | Internal Compensation                                                    |      |      |      |       |

| <b>Resistor Programming</b>                         | (I <sub>TH</sub> connected to INTV <sub>CC</sub> )                       |      | 3    |      | Bits  |

| Resolution                                          | (I <sub>TH</sub> connected to INTV <sub>CC</sub> )                       |      |      |      |       |

| Internal Compensation                               | Internal Compensation                                                    |      |      |      |       |

| Capacitor Programming                               | (I <sub>TH</sub> connected to INTV <sub>CC</sub> )                       |      | 3    |      | Bits  |

| Resolution                                          | (I <sub>TH</sub> connected to INTV <sub>CC</sub> )                       |      |      |      |       |

| Positive Inductor Valley                            | I <sub>LIM</sub> Range 0                                                 | 3.4  | 4    | 4.5  | Α     |

| Current Limit: (I <sub>LIM-POS</sub> ) <sup>2</sup> | I <sub>LIM</sub> Range 1                                                 | 6.0  | 7    | 7.5  | Α     |

| (Sourcing Output                                    | I <sub>LIM</sub> Range 2                                                 | 7.8  | 9    | 10   | Α     |

| Current)                                            | I <sub>LIM</sub> Range 3                                                 | 7.8  | 9    | 10   | А     |

| N. C. L. L. W. H.                                   | I <sub>LIM</sub> Range 0                                                 | -4   | -3.5 | -3.0 | А     |

| Negative Inductor Valley                            | I <sub>LIM</sub> Range 1                                                 | -6.5 | -6   | -5.5 | А     |

| Current Limit (I <sub>LIM-NEG</sub> ) <sup>2</sup>  | I <sub>LIM</sub> range 2                                                 | -8.5 | -7.5 | -6.5 | Α     |

| (Sinking Output Current)                            | I <sub>LIM</sub> Range 3                                                 | -10  | -9   | -8   | Α     |

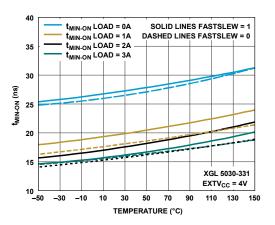

| Minimum On-Time                                     |                                                                          |      | 0.5  | 40   |       |

| (t <sub>MIN-ON</sub> )                              | I <sub>LOAD</sub> = +1A, FASTSLEW = 1                                    |      | 25   | 40   | ns    |

| Minimum Off-Time                                    |                                                                          |      | 0.5  | 405  |       |

| (t <sub>MIN-OFF</sub> )                             |                                                                          |      | 85   | 125  | ns    |

| POWER FETs                                          | •                                                                        |      | •    |      | •     |

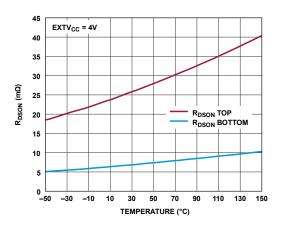

| 0. 5. : 1. (5. )                                    | Top Switch                                                               |      | 25   |      | mΩ    |

| On-Resistance (R <sub>DS-ON</sub> )                 | Bottom Switch                                                            |      | 7    |      | mΩ    |

| SW Leakage                                          | PV <sub>IN</sub> = 16V, V <sub>SW</sub> = 0V, 16V, T <sub>A</sub> = 25°C | -20  |      | 20   | μΑ    |

| OUTPUT VOLTAGE SUPERV                               |                                                                          | l .  | 1    |      |       |

| V <sub>OUT</sub> Undervoltage (UV)                  |                                                                          |      |      |      |       |

| Fault/Warning                                       | T <sub>A</sub> = 25°C                                                    | 0.36 |      | 5.5  | V     |

| Programming Range                                   | "                                                                        |      |      |      |       |

| V <sub>OUT</sub> Overvoltage (OV)                   |                                                                          |      |      |      |       |

| Fault/Warning                                       | T <sub>A</sub> = 25°C                                                    | 0.4  |      | 6    | V     |

| Programming Range                                   |                                                                          |      |      |      |       |

| V <sub>OUT</sub> UV/OV Fault/Warning                | V <sub>OUT</sub> UV/OV Threshold < 0.6V                                  | -12  |      | 12   | mV    |

| Threshold Accuracy                                  | V <sub>OUT</sub> UV/OV Threshold ≥ 0.6V                                  | -2   |      | 2    | %     |

| V <sub>OUT</sub> UV/OV Fault/Warning                | ,                                                                        |      |      |      |       |

| Programming Step-Size                               |                                                                          |      | 4    |      | mV    |

analog.com Rev 1 7 of 52

$(T_A = 25^{\circ}C \text{ for typical values. For minimum and maximum values, specifications apply over the full operating temperature range unless otherwise noted.)$

| PARAMETER                                           | CONDITIONS                                      | MIN   | TYP  | MAX   | UNITS |

|-----------------------------------------------------|-------------------------------------------------|-------|------|-------|-------|

| V <sub>OUT</sub> UV/OV Fault/Warning<br>Time        | V <sub>OUT</sub> = 10mV Beyond Threshold        |       |      | 25    | μs    |

| INPUT VOLTAGE SUPERVIS                              | ORS                                             |       |      |       | 1     |

| ON Threshold                                        | P.V., rising T. = 25°C                          | 1.4   |      | 16    | V     |

| Programming Range                                   | $PV_{IN}$ rising, $T_A = 25^{\circ}C$           | 1,4   |      | 10    | V     |

| OFF Threshold                                       | PV <sub>IN</sub> falling, T <sub>A</sub> = 25°C | 1.35  |      | 16    | V     |

| Programming Range                                   | I VIN Iditing, 14 25 C                          | 1.55  |      | 10    | •     |

| ON/OFF Threshold                                    |                                                 |       |      |       |       |

| Programming                                         |                                                 |       | 25   |       | mV    |

| Step Size                                           |                                                 |       |      |       |       |

| ON/OFF Threshold                                    | $V_{IN\_ON/OFF} \le 5V$                         | -100  |      | 100   | mV    |

| Set Point Accuracy                                  | $5V \le V_{IN\_ON/OFF} \le 20V$                 | -2    |      | 2     | %     |

| PV <sub>IN</sub> Overvoltage Lockout                | PV <sub>IN0</sub> or PV <sub>IN1</sub> Rising   | 17.26 | 17.6 | 17.94 | V     |

| Threshold                                           | PV <sub>IN0</sub> or PV <sub>IN1</sub> Falling  | 16.26 | 16.7 | 17.14 | V     |

| OSCILLATOR AND PHASE-L                              | OCKED LOOP                                      | ı     | T    |       | T     |

| SYNC Input Frequency                                |                                                 | 500   |      | 4000  | kHz   |

| Range                                               |                                                 |       |      |       |       |

| Switching Frequency                                 | T <sub>A</sub> = 25°C                           | 500   |      | 4000  | kHz   |

| Programmable Range                                  |                                                 |       |      |       | 1     |

| Switching Frequency Set                             |                                                 | -7.5  |      | 7.5   | %     |

| Point Accuracy                                      |                                                 |       |      |       |       |

| Switching Phase                                     |                                                 | 0     |      | 345   | deg   |

| Programming Range                                   |                                                 |       |      |       | -     |

| Switching Phase                                     |                                                 |       | 4.5  |       |       |

| Programmable                                        |                                                 |       | 15   |       | deg   |

| Resolution                                          |                                                 |       |      |       |       |

| TELEMETRY READBACK                                  | T                                               |       | 1    |       | 1     |

| Telemetry Measurement                               | Charadand Talanashan Mada                       |       | C F  |       |       |

| Period, All Except Die                              | Standard Telemetry Mode                         |       | 6.5  |       | ms    |

| Temperature Telemetry Measurement                   |                                                 |       |      |       |       |

| Telemetry Measurement                               | Low Fragues av Talamatav                        |       | 110  |       |       |

| Period, All except Die                              | Low-Frequency Telemetry                         |       | 110  |       | ms    |

| Temperature Telemetry Measurement                   |                                                 |       |      |       |       |

| Period, Die Temperature                             |                                                 |       | 26   |       | ms    |

| OUTPUT VOLTAGE READBA                               | CV                                              |       |      |       | 1     |

| OOTPOT VOLTAGE READBA                               |                                                 |       |      |       |       |

| DEAD VOLLE Accourage                                | High-Performance Low-V <sub>OUT</sub> Mode,     | -0.2  |      | 0.2   | %     |

| READ_VOUT Accuracy                                  | $0.6V \le V_{OUT} \le 1.375V$                   |       | -    | 0.1   | 6.4   |

|                                                     | 0.4V < V <sub>OUT</sub> < 5.5V                  | -0.4  |      | 0.4   | %     |

| PV <sub>INO</sub> , PV <sub>IN1</sub> INPUT VOLTAGE |                                                 |       | 1    |       | 1     |

| READ_VIN Accuracy                                   | $1.5V \le PV_{IN} \le 3.0V$                     | -30   |      | 30    | mV    |

|                                                     | $3.0V \le PV_{IN} \le 16V$                      | -1    |      | 1     | %     |

analog.com Rev 1 | 8 of 52

$(T_A = 25^{\circ}C \text{ for typical values. For minimum and maximum values, specifications apply over the full operating temperature range unless otherwise noted.)$

| PARAMETER                               | CONDITIONS                                              | MIN         | TYP    | MAX    | UNITS  |

|-----------------------------------------|---------------------------------------------------------|-------------|--------|--------|--------|

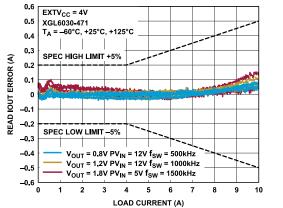

| OUTPUT CURRENT READBA                   | CK                                                      | '           |        |        |        |

|                                         | $I_{OUT} = 0A \text{ to } 4A, V_{OUT}/V_{IN} \le 0.25,$ | -350        |        | 350    | mA     |

|                                         | $500kHz \le f_{SW} \le 2MHz$                            | -330        |        | 330    | IIIA   |

| READ_IOUT Accuracy <sup>3</sup>         | $I_{OUT} = 4A \text{ to } 8A, V_{OUT}/V_{IN} \le 0.25,$ | -5          |        | 5      | %      |

| NEAD_1001 Accuracy                      | $500kHz \le f_{SW} \le 2MHz$                            | 3           |        | ,      | 70     |

|                                         | $I_{OUT} = 0A \text{ to } 4A, V_{OUT}/V_{IN} > 0.25$    | -600        |        | 600    | mA     |

|                                         | All other conditions $4 \le I_{OUT} \le 8A$             | -15         |        | 15     | %      |

| FREQUENCY READBACK                      | T                                                       |             | T      |        |        |

| READ_FREQUENCY                          | $f_{SW}$ < 600kHz, $T_A$ = 25°C                         | -30         |        | 30     | kHz    |

| Accuracy                                | $f_{SW} \ge 600 \text{kHz}, T_A = 25^{\circ}\text{C}$   | -5          |        | 5      | %      |

| ELECTRICALLY ERASABLE P                 | ROGRAMMABLE READ-ONLY MEMORY (EEF                       | PROM) CHARA | CTERIS | STICS4 |        |

| Retention                               |                                                         | 10          |        |        | years  |

| Endurance                               |                                                         | 10,000      |        |        | writes |

| Mass Write Time                         |                                                         |             | 250    | 500    | ms     |

| (STORE_USER_ALL)                        |                                                         |             | 230    | 300    | 1113   |

|                                         | NULTN, PGOODN, SHARE_CLK, SCL, SDA, A                   | LERT, WP    | T      |        | Т      |

| Input High Threshold (V <sub>IH</sub> ) |                                                         |             | 1.1    | 1.35   | V      |

| Input Low Threshold (V <sub>IL</sub> )  |                                                         | 0.8         | 0.9    |        | V      |

| Hysteresis (V <sub>HYS</sub> )          |                                                         |             | 200    |        | mV     |

| Leakage Current                         | Applied Voltage = 0V, 5.5V, T <sub>A</sub> = 25°C       |             |        | ±10    | μΑ     |

| Input Capacitance⁵                      | $T_A = 25$ °C                                           |             |        | 10     | pF     |

| DIGITAL CLOCK INPUT: SYN                | IC                                                      |             |        |        |        |

| Peak-To-Peak Input<br>Voltage Swing     | Sync Input Mode                                         | 1.4         |        | 5.5    | V      |

| Rise Time                               | Sync Input Mode                                         |             |        | 25     | ns     |

| Duty Cycle                              | Sync Input Mode                                         | 30          |        | 70     | %      |

| DIGITAL CLOCK OUTPUT: S                 | YNC                                                     |             |        |        |        |

| Output High Voltage (V <sub>OH</sub> )  | SYNC Output Mode                                        | 1.6         | 1.88   | 1.98   | V      |

| Output Low Voltage (V <sub>OL</sub> )   | SYNC Output Mode                                        |             |        | 0.2    | V      |

| Output Impedance                        | SYNC Output Mode                                        |             | 60     |        | Ω      |

| CURRENT-LIMITED OPEN-D                  | RAIN OUTPUTS: RUNN, FAULTN                              |             |        |        |        |

| Pull-Down Current                       | Applied Voltage = 0.4V to 5.5V                          | 1           | 1.5    | 2      | mA     |

| <b>OPEN-DRAIN OUTPUTS: PG</b>           | OODN, SHARE_CLK                                         |             |        |        |        |

| Output Low Voltage                      | I = 6mA                                                 |             |        | 0.4    | V      |

| DIGITAL I/O: SCL, SDA, ALE              | RT                                                      |             |        |        |        |

|                                         | Data Output Hold-Time                                   | 0           |        | 450    | ns     |

Delay from RESTORE\_USER\_ALL, MFR\_RESET, or Application of  $PV_{IN0}$  or EXTV<sub>CC</sub> until the TON\_DELAY timer can begin.

analog.com Rev 1 9 of 52

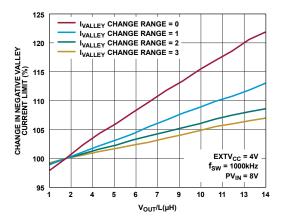

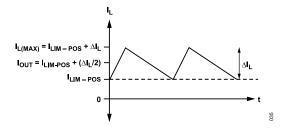

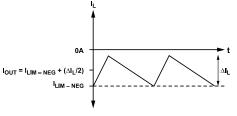

The LT7184S switching regulators use valley current mode control, so the current limits specified correspond to the valley of the inductor current waveform. Valley current limit moves with  $V_{OUT}/L$  and with

FREQUENCY\_SWITCH and is guaranteed for duty cycles < 50%; current limits are specified at  $V_{OUT}/L = 2V/\mu H$  and FREQUENCY\_SWITCH = 1000. Maximum load current is higher with positive loads and equals the valley current plus one-half of the inductor ripple current. Maximum load current is lower with negative loads and equals the valley current minus one-half of the inductor ripple current. See the *Applications Information* section and *Typical Performance Characteristics* for more details.

- READ\_IOUT is tested in a production test mode at full rated current where I<sub>SW</sub> flows through the synchronous switch at 100% duty cycle. In applications, READ\_IOUT is calculated from sampled current measurements across the synchronous switch.

- EEPROM endurance is guaranteed by design, characterization, and correlation with statistical process controls. Data retention is production tested via a high-temperature bake at the wafer level. The minimum retention specification applies for devices whose EEPROM has been cycled less than the minimum endurance specification.

- <sup>5</sup> Guaranteed by design, characterization, and correlation with statistical process controls.

analog.com Rev 1 | 10 of 52

LT7184S

Table 4. I<sup>2</sup>C/PMBus Timing

| PARAMETER                                | SYMBOL               | MIN | MAX   | UNITS |

|------------------------------------------|----------------------|-----|-------|-------|

| Serial Bus Operating Frequency           | f <sub>SCL</sub>     | 10  | 1000  | kHz   |

| Bus Free Time Between Stop and Start     | t <sub>BUF</sub>     | 500 |       | ns    |

| Hold Time After Repeated Start Condition | t <sub>HD-STA</sub>  | 260 |       | ns    |

| Repeated Start Condition Setup Time      | t <sub>su-sta</sub>  | 260 |       | ns    |

| Stop Condition Setup Time                | t <sub>su-sto</sub>  | 260 |       | ns    |

| Data Input Setup Time                    | t <sub>su-dat</sub>  | 50  |       | ns    |

| Data Input Hold Time                     | t <sub>HD-DAT</sub>  | 0   |       | ns    |

| Data Output Hold Time                    |                      | 0   | 450   | ns    |

| Bus Timeout                              | t <sub>TIMEOUT</sub> | 25  | 35    | ms    |

| Serial Clock Low Period                  | t <sub>LOW</sub>     | 0.5 | 10000 | μs    |

| Serial Clock High Period                 | t <sub>HIGH</sub>    | 260 |       | ns    |

analog.com Rev 1 | 11 of 52

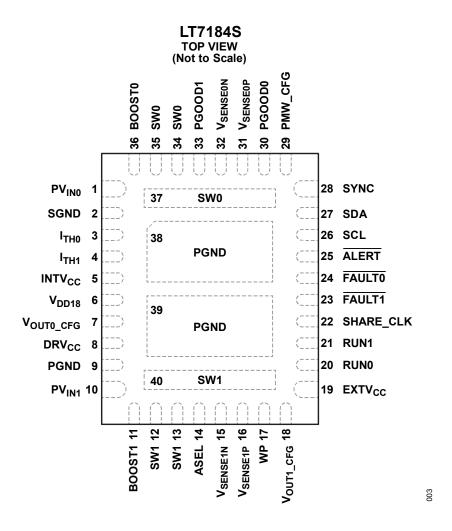

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

#### **Table 5. Pin Descriptions**

|                                                                                                                                                                                                                                          | -                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN                                                                                                                                                                                                                                      | Name              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 1                                                                                                                                                                                                                                        | PV <sub>INO</sub> | Power Supply Input for Channel 0 and Internal LDO Regulators. This pin must be bypassed to SGND as close as possible to the LT7184S, with a low ESR capacitor of value $4.7\mu F$ or more using the top PCB layer. If EXTV <sub>CC</sub> < 3V, then the internal LDO regulators (for DRV <sub>CC</sub> , INTV <sub>CC</sub> , and V <sub>DD18</sub> ) pull power from PV <sub>INO</sub> .                                                                                                                                                     |  |  |  |  |

| and V <sub>DD18</sub> supply pins should be connected to an isolate close as possible to the SGND pin. This pin is connected package. Do not connect the SGND isolated ground retulocation in the application PCB. In PolyPhase applicat |                   | Signal Ground. The return for the $I_{THO}$ and $I_{THI}$ compensation networks and the INTV <sub>CC</sub> and $V_{DD18}$ supply pins should be connected to an isolated ground return connected as close as possible to the SGND pin. This pin is connected to PGND within the LT7184S package. Do not connect the SGND isolated ground return to PGND in more than one location in the application PCB. In PolyPhase applications the SGND and $I_{THN}$ nodes should be symmetrically connected to each IC in the PolyPhase configuration. |  |  |  |  |

analog.com Rev 1 | 12 of 52

| PIN                             | Name               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                               | I <sub>THO</sub>   | Error amplifier output and switching regulator compensation for Channel 0. Connect the appropriate external components between $I_{THO}$ and SGND to compensate the regulator loop frequency response for Channel 0 or connect to $INTV_{CC}$ to select internal compensation for Channel 0.                                                                                                                                                                                                                                                        |

| 4                               | I <sub>TH1</sub>   | Error amplifier output and switching regulator compensation for channel 1. Connect the appropriate external components between $I_{TH1}$ and SGND to compensate the regulator loop frequency response for Channel 1, or connect to $INTV_{CC}$ to select internal compensation for Channel 1.                                                                                                                                                                                                                                                       |

| 5                               | INTV <sub>cc</sub> | Internal 3V LDO regulator bypass. This LDO regulator output provides a supply current for internal circuitry. This pin must be bypassed to SGND with a $10\mu F$ or greater, low ESR ceramic capacitor as close as possible to the IC on the top Printed Circuit Board (PCB) layer. Do not load the INTV <sub>CC</sub> pin with external circuitry.                                                                                                                                                                                                 |

| 6                               | $V_{DD18}$         | Internal 1.8V regulator bypass. This pin must be bypassed to SGND with a $4.7\mu F$ or greater low ESR ceramic capacitor as close as possible to the LT7184S on the top PCB layer. Do not load the $V_{DD18}$ pin with external circuitry.                                                                                                                                                                                                                                                                                                          |

| 7                               | $V_{OUTO\_CFG}$    | Output voltage configuration for channel 0. Connect a 1% resistor from $V_{OUT0\_CFG}$ to GND (SGND or PGND) according to <i>Table 7</i> in the <i>Applications Information</i> section to select one of sixteen output voltage set points. If left floating or connected to $V_{DD18}$ , the LT7184S uses the value of VOUT_COMMAND programmed in EEPROM to set the output voltage set point. The $V_{OUT0\_CFG}$ pin is only read at the start-up.                                                                                                |

| 8                               | DRV <sub>cc</sub>  | Internal 3.5V LDO regulator bypass. The DRV <sub>CC</sub> regulator provides the supply current for the power FET drivers. This pin must be bypassed to PGND with a 100nF or greater low Equivalent series resistance (ESR) ceramic capacitor as close as possible to the LT7184S using the top PCB layer, and a bulk 10 $\mu$ F low ESR ceramic capacitor. Do not load the DRV <sub>CC</sub> pin with external circuitry with the optional exceptions of the pull-up resistor for the SHARE_CLK pin and/or the RUN0, RUN1, FAULT0, or FAULT1 pins. |

| 9,<br>Exposed<br>pads 38,<br>39 | PGND               | Power ground. The (-) terminal of the $PV_{IN1}$ input bypass capacitors and the (-) terminal of the output capacitors ( $C_{OUT0}$ and $C_{OUT1}$ ) should be connected to these pins with low-impedance connections. The PCB must be designed to provide low electrical and thermal impedance to PGND.                                                                                                                                                                                                                                            |

| 10                              | $PV_{IN1}$         | Power supply input for Channel 1. This pin must be bypassed to PGND as close as possible to the LT7184S with a low ESR capacitor of value 4.7µF or more using the top PCB layer.                                                                                                                                                                                                                                                                                                                                                                    |

| 11                              | BOOST1             | Boosted floating driver supply for Channel 1. Connect a $0.1\mu F$ boost capacitor from BOOST1 to SW1 as close as possible to the LT7184S using only the top PCB layer. The normal operation voltage swing on this pin is from DRV <sub>CC</sub> to PV <sub>IN1</sub> + DRV <sub>CC</sub> .                                                                                                                                                                                                                                                         |

| 12, 13,<br>Exposed<br>pad 40    | SW1                | The output of the Channel 1 internal power switches. Connect these pins together and connect the Channel 1 inductor and BOOST1 capacitor. This node should be sized to support the maximum load current for Channel 1 and be spaced away from all other PCB metal.                                                                                                                                                                                                                                                                                  |

| 14                              | ASEL               | Serial bus address configuration pin. Connect a 1% resistor from ASEL to ground (SGND or PGND) to select one of sixteen serial bus interface addresses. The ASEL pin is read at start-up. If the ASEL pin is left floating, the factory default 7-Bit device address is 0x4F. If the ASEL pin is grounded, the factory default device address is 0x40.                                                                                                                                                                                              |

analog.com Rev 1 | 13 of 52

| PIN | Name                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | V <sub>SENSE1N</sub>  | Output voltage negative sense input. Connect to the Channel 1 output voltage sense ground point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16  | V <sub>SENSE1P</sub>  | Output voltage positive sense input. Connect to the Channel 1 output voltage sense point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 17  | WP                    | Write protect pin. When this pin is high, only the PAGE, OPERATION, MFR_EE_UNLOCK, and CLEAR_FAULTS commands are write-able. Clear individual fault bits by writing a 1 to the respective bits in the STATUS commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18  | V <sub>OUT1_CFG</sub> | Output voltage configuration for Channel 1 or poly phase configuration. If the PWM_CFG pin is NOT configured for PolyPhase, the 1% resistor from $V_{OUT1\_CFG}$ to the ground (either SGND or PGND) will be selected as the voltage set point according to <i>Table 7</i> in the <i>Applications Information</i> section. If the PWM_CFG pin is configured for poly phase operation, then the Channel 1 output is set to the same value as Channel 0 based on $V_{OUT0\_CFG}$ , and a 1% resistor from $V_{OUT1\_CFG}$ to ground selects a PolyPhase configuration according to <i>Table 10</i> in the <i>Applications Information</i> section. The $V_{OUT1\_CFG}$ pin is read at LT7184S start-up.   |

| 19  | EXTV <sub>cc</sub>    | Optional Power Supply input. If connected to 3V to 5.5V, this pin is used to derive the DRV <sub>CC</sub> , INTV <sub>CC</sub> , and V <sub>DD18</sub> supplies. If one of the regulator outputs is set to output 3V or greater, that output may be connected to EXTV <sub>CC</sub> to reduce power loss. If this pin is not connected to a regulator output, apply a $0.1\mu F$ or greater local bypass capacitor on this pin to GND as close as possible to the LT7184S.                                                                                                                                                                                                                              |

| 20  | RUN0                  | Channel 0 Regulator Enable Input. Logic high enables the Channel 0 regulator. The RUN0 pin is pulled down with 1.5mA (typical) during POR and reset to facilitate sequencing with other regulators but may be over-driven high by a digital output of another device. This pin may be connected directly to DRV <sub>CC</sub> to enable the regulator when input power is present.                                                                                                                                                                                                                                                                                                                      |

| 21  | RUN1                  | Channel 1 Regulator Enable Input. Logic high enables the Channel 1 regulator. The RUNO pin is pulled down with 1.5mA (typical) during POR and reset to facilitate sequencing with other regulators but may be over-driven high by a digital output of another device. This pin may be tied directly to DRV <sub>CC</sub> to enable the regulator when input power is present.                                                                                                                                                                                                                                                                                                                           |

| 22  | SHARE_CLK             | Bidirectional Open-Drain Sequence Time Base Share Clock. Nominally 100kHz. Used to align start-up and shutdown of regulator outputs among multiple Analog Devices' products when PolyPhase or time-based sequencing is employed. A pull-up resistor to 1.6V to 5.5V is required if SHARE_CLK is connected between multiple devices to synchronize sequencing. If time-based sequencing is not used, leave the SHARE_CLK pin floating. It is pulled up to $V_{DD18}$ inside the chip through a diode and a $100k\Omega$ resistor.                                                                                                                                                                        |

| 23  | FAULT1                | Input/Open-Drain Output. The LT7184S pulls the $\overline{FAULT1}$ pin down with 1.5mA (typical) when an unmasked fault occurs on the Channel 1 regulator. If another device pulls down the $\overline{FAULT1}$ pin, the LT7184 Channel 1 regulator turns off immediately. If PolyPhase configuration is used, tie together the $\overline{FAULTN}$ pins of all PolyPhase channels. If the PolyPhase configuration is used, or if $\overline{FAULTN}$ pin reporting or sharing is required, a pull-up resistor of 6.8k $\Omega$ or greater to 1.6V to 5.5V is required. $\overline{FAULT1}$ pin may be connected directly to DRV <sub>CC</sub> if the $\overline{FAULT1}$ pin function is not required. |

| 24  | FAULT0                | FAULTO Input/Open-Drain Output. The LT7184S pulls the FAULTO pin down with 1.5mA (typical) when an unmasked fault occurs on the Channel 0 regulator. If another device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

**analog.com** Rev 1 | 14 of 52

| PIN                          | Name                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                      | pulls down the FAULTO pin, the LT7184 channel 0 regulator turns off immediately. If PolyPhase configuration is used, tie together the $\overline{\text{FAULTN}}$ pins of all PolyPhase channels. If the PolyPhase configuration is used, or if the Fault pin reporting or sharing is required, a pull-up resistor of $6.8\text{k}\Omega$ or greater to $1.6\text{V}$ to $5.5\text{V}$ is required. $\overline{\text{FAULTO}}$ pin may be tied directly to DRV <sub>CC</sub> if the $\overline{\text{FAULTO}}$ pin function is not required. |

| 25                           | ALERT                | Open-Drain Alert Output. If the ALERT pin function is used, a pull-up resistor of 1.6V to 5.5V is required. If the ALERT pin function is not used, the pin may be connected to the ground.                                                                                                                                                                                                                                                                                                                                                  |

| 26                           | SCL                  | Serial Bus Clock Input and Output. The LT7184S may hold SCL low if clock stretching is enabled (PMBus speeds 400kHz - 1MHz only). A pull-up resistor of 1.6V to 5.5V is required for PMBus/I <sup>2</sup> C operation. If serial bus operation is not required, SCL may be connected to the ground.                                                                                                                                                                                                                                         |

| 27                           | SDA                  | Serial Bus Data Input and Output. A pull-up resistor of 1.6V to 5.5V is required for PMBus/I <sup>2</sup> C operation. If serial bus operation is not required, the SDA may be connected to the ground.                                                                                                                                                                                                                                                                                                                                     |

| 28                           | SYNC                 | External Clock Synchronization Input/Output. When driven with an external clock, an internal phase-locked loop synchronizes the switching regulator output with the rising edge of the external clock. If configured as an output (MFR_SYNC_CONFIG_LT7184 bit 0 is set to 1), the LT7184S drives the SYNC pin output at the switching clock frequency set by the FREQUENCY_SWITCH command with a voltage swing of 0V to V <sub>DD18</sub> .                                                                                                 |

| 29                           | PWM_CFG              | PWM Configuration Resistor Pin. Connect a 1% resistor from PWM_CFG to the ground (SGND or PGND) according to <i>Table 9</i> in the <i>Applications Information</i> section to select frequency, phase, and mode configurations. The PWM_CFG pin is read at LT7184S start-up. See <i>Applications Information</i> for more details.                                                                                                                                                                                                          |

| 30                           | PGOOD0               | Power Good Indicator Output for channel 0. PGOOD0 is pulled low when the channel 0 regulator output is outside of the OV/UV fault thresholds when Channel 0 is disabled, and during on/off sequencing. The PGOOD0 output is deglitched by an internal configurable timer. If the PGOOD0 pin function is not used, it may be connected to the ground.                                                                                                                                                                                        |

| 31                           | $V_{SENSEOP}$        | Output voltage positive sense input. Connect to the Channel 0 output voltage sense point.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 32                           | V <sub>SENSEON</sub> | Output voltage negative sense input. Connect to the Channel 0 output voltage sense ground point.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 33                           | PGOOD1               | Power Good Indicator Output for Channel 1. PGOOD1 is pulled low when the Channel 0 regulator output is outside of the OV/UV fault thresholds when Channel 1 is disabled and during on/off sequencing. The PGOOD1 output is deglitched by an internal configurable timer. If the PGOOD1 pin function is not used, it may be connected to the ground.                                                                                                                                                                                         |

| 34, 35,<br>Exposed<br>pad 37 | SW0                  | Output of the Channel 0 internal power switches. Connect these pins together and connect the Channel 0 inductor and BOOST0 capacitor. This node should be sized to support the maximum load current for Channel 0 and be spaced away from all other PCB metal.                                                                                                                                                                                                                                                                              |

| 36                           | BOOST0               | Boosted floating driver supply for Channel 0. Connect a $0.1\mu F$ boost capacitor from BOOST0 to SW0 as close as possible to the LT7184S using only the top PCB layer. The normal operation voltage swing on this pin is from DRV <sub>CC</sub> to PV <sub>IN0</sub> + DRV <sub>CC</sub> .                                                                                                                                                                                                                                                 |

analog.com Rev 1 | 15 of 52

LT7184S

### TYPICAL PERFORMANCE CHARACTERISTICS

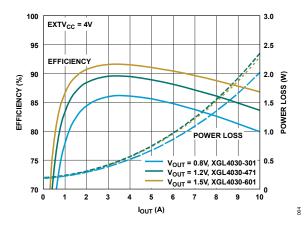

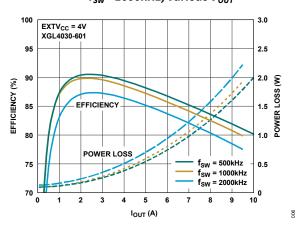

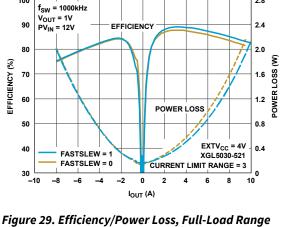

Figure 4. 12V PV<sub>IN</sub> Efficiency/Power Loss at  $f_{SW}$  = 1000kHz, various  $V_{OUT}$

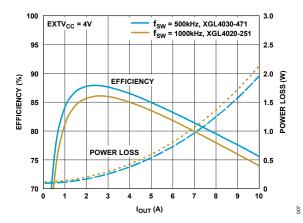

Figure 6. 5V PV<sub>IN</sub> to 0.8V  $V_{OUT}$  Efficiency/ Power Loss various  $f_{SW}$

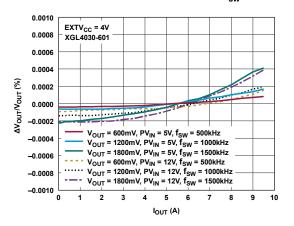

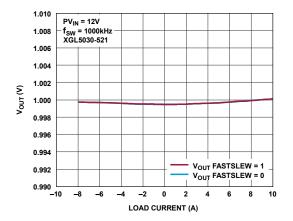

Figure 8. Load Regulation

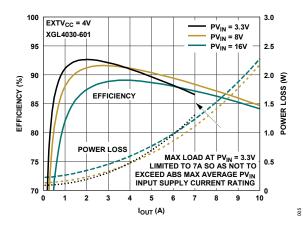

Figure 5.  $V_{OUT}$  = 1.2V,  $f_{SW}$  = 1000kHz Efficiency/ Power Loss, various P $V_{IN}$

Figure 7. 5V PV<sub>IN</sub> to 0.6V V<sub>OUT</sub> Efficiency at various  $f_{SW}$

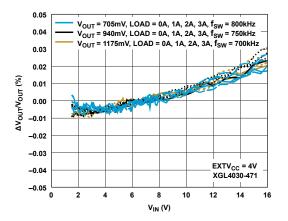

Figure 9. Line Regulation

600

analog.com Rev 1 | 16 of 52

800

010

012

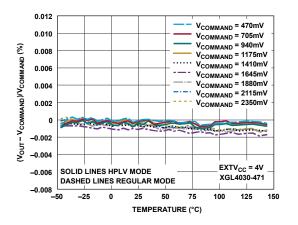

Figure 10. Temperature Regulation:  $(V_{OUT} - V_{COMMAND})/V_{COMMAND}$  (%) vs Temperature

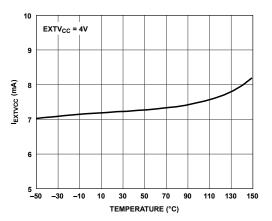

Figure 12.  $I_{EXTVCC}$  vs Temperature Shutdown

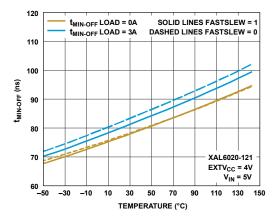

Figure 14.  $t_{MIN-OFF}$  vs Temperature

Figure 11. ON Resistance vs Temperature

011

013

015

Figure 13. t<sub>MIN-ON</sub> vs Temperature

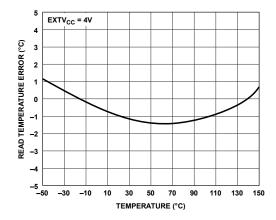

Figure 15. READ\_TEMPERATURE Error vs Temperature

analog.com Rev 1 | 17 of 52

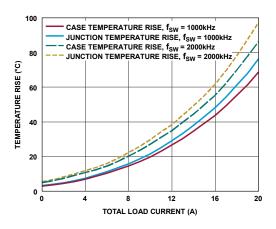

MAX LOAD AT T\_A = 125°C LIMITED TO SO AS NOT TO EXCEED ABS MAX T\_J RATING.  $\mbox{\ensuremath{\Xi}}$

Figure 16. READ\_IOUT Error vs Iout

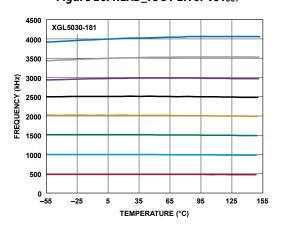

Figure 18. f<sub>SW</sub> vs Temperature

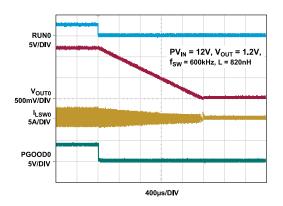

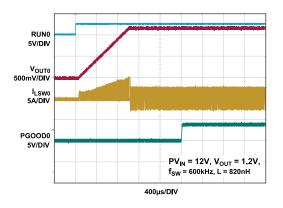

Figure 20. Soft-Stop no Load

Figure 17. Temperature Rise vs Total Load Current

017

019

021

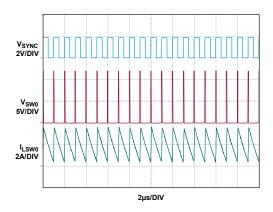

Figure 19. Soft-Start no Load

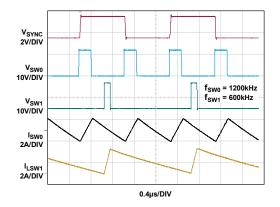

Figure 21. SYNC Waveforms Figure 45 Application, EXTV<sub>CC</sub> = V<sub>OUTO</sub>, V<sub>OUT1</sub> = 0.8V, I<sub>OUT1</sub> = 1A

analog.com Rev 1 | 18 of 52

0.18

022

024

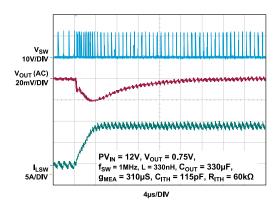

Figure 22. Continuous Conduction,  $PV_{IN} = 12V$ ,  $V_{OUT} = 0.75V$ ,  $L_{SW} = XGL4020-251$ , 2A load

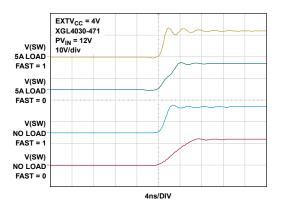

Figure 24. SW Rise Waveforms, V<sub>OUT</sub> = 1.2V

Figure 26. Negative Valley Current Limit Change with  $V_{\text{OUT}}/L$

Figure 23. 9A Load Step, Default Internal Compensation,  $V_{OUT} = 0.75V$

023

025

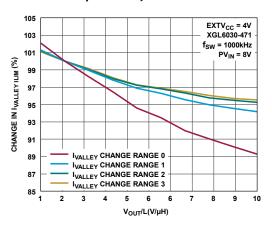

Figure 25. Positive Valley Current Limit Change with  $V_{\text{OUT}}/L$

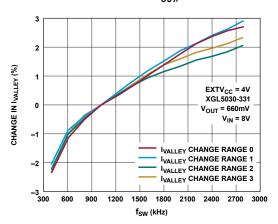

Figure 27. Valley Current Limit Change with fsw

analog.com Rev 1 | 19 of 52

LT7184S **Data Sheet**

028

100

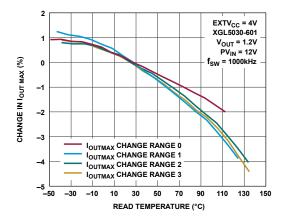

Figure 28. Maximum Output Current Change with **Temperature**

2.8

029

031

Figure 30. Load Regulation  $V_{OUT} = 1V$ , Full-Load Range

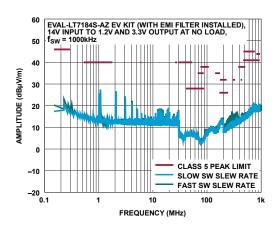

Figure 31. Radiated EMI Performance No-Load (CISPR25 Radiated Emission Test with Class 5 **Peak Limits**)

032

030

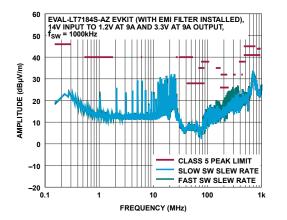

Figure 32. Radiated EMI Performance Full-Load (CISPR25 Radiated Emission Test with Class 5 Peak Limits)

Rev 1 20 of 52 analog.com

LT7184S

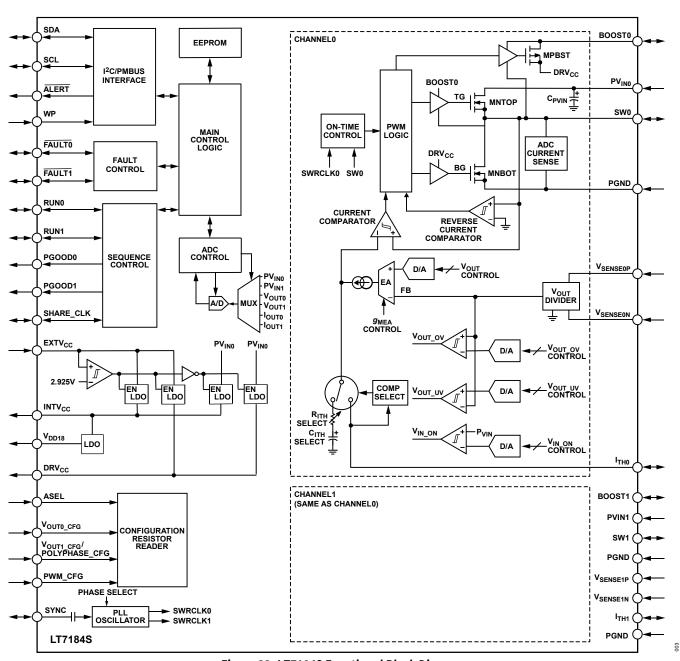

# **BLOCK DIAGRAM**

Figure 33. LT7184S Functional Block Diagram

analog.com Rev 1 | 21 of 52

#### THEORY OF OPERATION

### **Overview**

The LT7184S is a dual-output monolithic PolyPhase DC/DC synchronous step-down regulator. The S in the LT7184S refers to the second-generation Silent Switcher® technology, which provides fast and clean switching edges, reduces overall solution size, improves efficiency, and minimizes EMI emissions. The I<sup>2</sup>C-based serial interface is compatible with PMBus 1.3, which supports bus speeds up to 1MHz.

#### Major features include:

- ► Programmable Output Voltage.

- ► Programmable Current Limit.

- ► Programmable Switching Frequency.

- ▶ Programmable Output Overvoltage and Undervoltage Fault and Warning Thresholds.

- ► Programmable On and Off Delay Times.

- ► Programmable Output Rise/Fall Times.

- ▶ Programmable Control Loop Compensation.

- ► Programmable Input Undervoltage Threshold.

- ▶ Dedicated Power Good Output Pin for Each Channel.

- ▶ Phase-Locked Loop (PLL) for Synchronous, PolyPhase Operation (2, 3, 4, 6, or 8 Phases).

- ▶ Input and Output Voltage, Output Current, and Die Temperature Telemetry.

- ► Fully Differential Remote V<sub>OUT</sub> Sense.

- ▶ Nonvolatile Configuration Memory (NVM) with Error Correcting Code (ECC).

- ► Nonvolatile Event-Based Fault Log.

- Optional External Configuration Resistors for Key Operating Parameters.

- ▶ Optional Time-Based Interconnect for Synchronization Between Multiple Devices.

- ▶ WP Pin to Write-Protect Internal Configuration.

- Standalone Operation using Configuration Resistors or NVM.

A variety of mechanisms for fault and warning handling are available. Fault and warning detection capabilities include:

- Output Undervoltage/Overvoltage Fault and Warning.

- ► Internal Overtemperature Fault and Warning.

- ► Communication, Memory, or Logic (CML) Fault.

- ► Input Overvoltage Fault and Undervoltage Warning.

- Output Overcurrent Fault and Warning.

- ► Internal Reference Fault.

- ► External Fault Detection via the Bidirectional FAULT Pins.

A dedicated ALERT pin is provided to indicate that faults or warnings have occurred.

Individual status commands enable fault and warning reporting to identify the specific event.

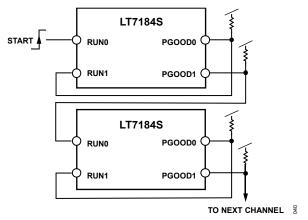

The LT7184S's FAULT pins enable fault sharing between channels and with other Analog Devices' power system management products, including the LTC3880, LTC2974, LTC2978, LTC4676 μModule®, etc. Fault reporting and shutdown behavior are fully configurable using the FAULT pins and the MFR\_FAULT\_PROPAGATE\_LT7184S command. Faults can be individually masked, and the fault responses can be programmed to retry (unlatched) or latch off the regulator output.

analog.com Rev 1 | 22 of 52

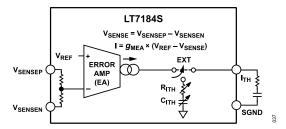

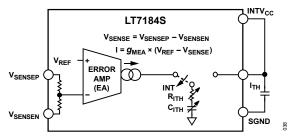

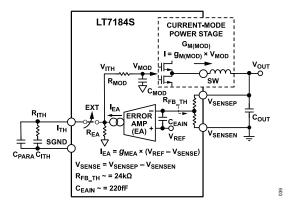

## **Switching Regulator Control Loop**

The LT7184S employs a controlled, on-time, valley current mode architecture. In normal operation, the internal top power Metal-oxide-semiconductor FET (MOSFET) is turned on for an interval determined by an on-time control circuit. When the top power MOSFET turns off, the bottom power MOSFET turns on until the valley current comparator trips, restarting the on-time control circuit and initiating the next cycle. The inductor current is determined by sensing the voltage drop across the bottom power MOSFET when it is on. The voltage on the  $I_{THN}$  pin sets the comparator threshold corresponding to the inductor valley current. The error amplifier (EA) adjusts the  $I_{TH}$  voltage by comparing the output voltage with an internal reference Digital-to-analog Converter (DAC) output. If the load current increases, the output voltage drops relative to the internal reference, which causes the  $I_{TH}$  voltage to rise until the average inductor current matches that of the load current.

An internal phase-locked loop synchronizes the oscillator frequency to an external clock signal if one is present on the SYNC pin. If no external clock is applied, the switching frequency is set by the FREQUENCY\_SWITCH command, which may be initialized using configuration resistors (see the *Applications Information* section for more details).

### **Soft-Start**

The LT7184S has two Pulse Width Modulation (PWM) modes of operation: Pulse-skip mode (PSM) and Forced continuous mode (FCM). Pulse-skip mode is only used during soft-start while the output voltage rises to the programmed regulation voltage. During PSM or discontinuous operation, the inductor current cannot be reversed. The reverse current comparator turns off the bottom switch when the inductor current reaches zero, preventing the inductor current from going negative and discharging the output. During discontinuous operation, the power MOSFETs remain off while the output capacitor supplies the load current. The LT7184S switches again when the  $I_{TH}$  voltage rises above the zero current level to initiate the next cycle as either the internal reference voltage rises above the  $V_{SENSE}$  voltage with the soft-start ramp, or the load discharges the  $V_{SENSE}$  voltage.

When all conditions required for startup have been met, and a channel is enabled with an OPERATION command or when the RUN pin is raised, a soft-start ramp begins. The soft-start ramp time is set by the TON\_RISE command, which is 1ms by default. The soft start ramp begins after a programmable delay (TON\_DELAY, default 0ms). Once the output voltage reaches the programmed regulation voltage (VOUT\_COMMAND), the PGOOD flag is set, and the operating mode automatically switches to the FCM mode of operation.