# Narrow-Band and Wideband RF Transceiver with Integrated Application Processor

#### **FEATURES**

- ▶ Integrated 1 Tx × 2 Rx RF transceiver

- Operating frequency range of 70 MHz to 6000 MHz

- Transmitter and wideband receiver signal bandwidth from 12 kHz to 40 MHz

- ▶ Narrowband receiver signal bandwidth from 12 kHz to 2 MHz

- ▶ 2 fully integrated, fractional-N, RF synthesizers

- ▶ 2 fully integrated, fractional-N, RF PLLs to control external VCO banks

- Supports external LO

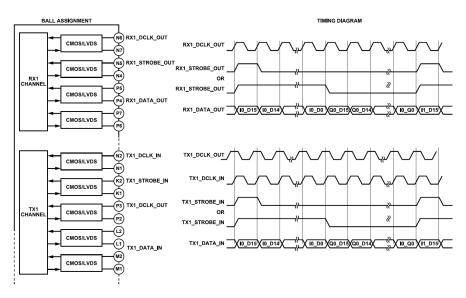

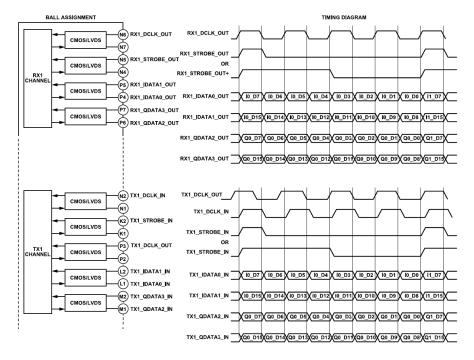

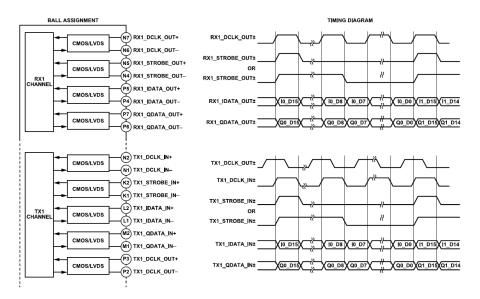

- ▶ LVDS and CMOS synchronous serial data interface options

- ▶ Low power monitor and sleep modes

- Fully integrated DPD for TDD narrowband waveforms

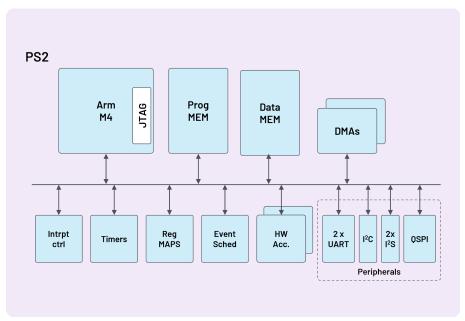

- ▶ User-programmable ARM core with 928 kB memory

- ▶ Interfaces include 2× UART, 2× I<sup>2</sup>S, I<sup>2</sup>C, QSPI, SPI-M, JTAG

- Library of hardware accelerators

- Fully programmable via a 4-wire SPI

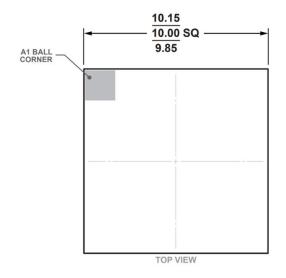

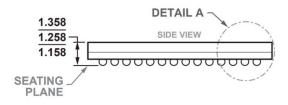

- ▶ Package: 196-ball, 10 mm × 10 mm, CSP\_BGA

#### **APPLICATIONS**

- ▶ Land Mobile Radios

- Mobile Satellite and Satellite IoT

- ▶ Wireless microphones

- Mission critical communications systems

- Smart Meters

- ▶ Factory Automation

#### **GENERAL DESCRIPTION**

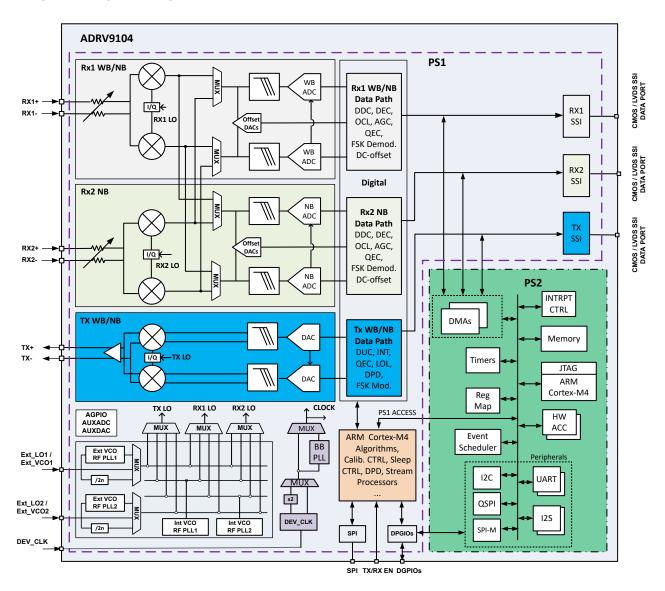

The ADRV9104 is a highly integrated RF transceiver with an integrated application processor that has a single transmitter, dual receivers, integrated synthesizers, and digital signal processing functions. Its a high performance, highly linear, high dynamic range transceiver designed for the lowest power consumption to support portable, and battery powered equipment. The ADRV9104 operates from 70 MHz to 6000 MHz and covers the VHF (from 70MHz),UHF, industrial, scientific, and medical (ISM) bands, and cellular frequency bands in narrow-band (kHz) and wideband operation up to 40 MHz. The ADRV9104 is capable of both TDD and uncalibrated FDD operation.

The transceiver has three direct conversion signal paths (1Tx and 2Rx) with state-of-the-art noise figure and linearity. The dedicated Narrow Band Receiver path can support up to 2MHz of RF signal BW. The dedicated wide band Receiver path can support up to 40MHz of RF signal BW. Each receiver and transmitter subsystem includes quadrature error correction (QEC), programmable digital

filters, DC offset correction on the Rx paths and LO leakage suppression on the Tx path. In addition, functions such as analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and general-purpose inputs/outputs (GPIOs), are integrated to provide additional monitoring and control capability.

The transmitter has internal modulator functions that can support for typical Land Mobile Radio (LMR) standards, such as Analog FM, Digital Mobile Radio (DMR), P25. The modulator integrates the symbol mapping, interpolation and pulse shaping functions which allow the basedband processor to send 2bit symbols to ADRV9014.

The fully integrated phase-locked loops (PLLs) provide high performance, low power, fractional-N frequency synthesis for the transmitter, receiver, and clock sections. Careful design and layout techniques provide the isolation required in high performance personal radio applications.

All voltage-controlled oscillator (VCO) and loop filter components are integrated to minimize the external component count. The internal PLLs provide local oscillators (LOs) and have flexible configuration options and include fast lock modes. The fully integrated PLLs also have the option of operating with one or more external VCOs to provide ultra low noise LOs for the transmitter and receivers.

The transceiver includes low power sleep and monitor modes to save power and extend the battery life of portable devices while monitoring communications, it has the capability to monitor the DMR and Analog FM signal simultaneously with the narrow-band receiver channel when monitor mode is enabled. For some modes, ADRV9104 can operate form DEV\_CLK only with the internal Clock PLL powered down.

The fully integrated, low power digital predistortion (DPD) is optimized for narrow-band TDD signals and enables linearization of high efficiency power amplifiers.

The ADRV9104 hosts a second processor, Processor Subsystem 2 (PS2), for users application specific programming. The ARM M4 has 928kB of useable memory, hardware accelerators, peripheral interfaces and runs up to 200MHz. This application processor can be used to implement modem like features on the transceiver customized to individual use cases.

The ADRV9104 core can be powered directly from 1.0 V and 1.8 V regulators and is controlled via a standard 4-wire serial port. High data rate and low data rate interfaces are supported using configurable CMOS or low voltage differential signaling (LVDS) serial synchronous interface (SSI) choice. The ADRV9104 is packaged in a 10 mm × 10 mm, 0.65 pitch 196-ball chip scale package ball grid array (CSP\_BGA).

Rev. PrC

# **TABLE OF CONTENTS**

| Features                                    | 1    |

|---------------------------------------------|------|

| Applications                                | 1    |

| General Description                         |      |

| Functional Block Diagram                    |      |

| Specifications                              | 4    |

| Transmitter Specifications                  | 4    |

| Receiver Specifications                     | 5    |

| Internal LO, External LO, and Device Clock  | 7    |

| External VCO Charge Pump                    | 8    |

| Digital Interfaces and Auxiliary Converters | 8    |

| Power Supply Specifications                 | 10   |

| Power Consumption Estimates (Typical        |      |

| Values)                                     | . 10 |

| Pin Configuration and Function Descriptions | . 12 |

| Theory of Operation         | 17 |

|-----------------------------|----|

| Transmitter                 | 17 |

| Receiver                    | 17 |

| Clock Input                 | 17 |

| Synthesizers                | 17 |

| RF PLL                      | 18 |

| Baseband PLL                |    |

| GPIO Pins                   | 18 |

| Auxiliary Converters        | 18 |

| SPI                         | 18 |

| Processor Subsystem 2 (PS2) | 19 |

| Digital Data Interface      | 20 |

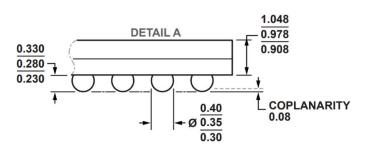

| Outline Dimensions          | 23 |

|                             |    |

analog.com Rev. PrC | 2 of 23

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

analog.com Rev. PrC | 3 of 23

Electrical characteristics are at the operating ambient temperature range, VDDA\_1P0 = 1.0 V, VDDA\_1P8 = 1.8 V, VDD\_1P0 = 1.0 V, VDD\_1P0 = 1.0 V, VDD\_1P0 = 1.8 V. The following values are not de-embedded. The specification tables below are populated with preliminary measurement results, taken at 25°C averaged across multiple parts, and are subject to change as characterization on the device continues and more qualified data is obtained.

## TRANSMITTER SPECIFICATIONS

All values in the transmitter specification table have been measured while the part was in NB mode only.

Table 1. Transmitter

| Parameter                                              | Symbol | Min | Тур  | Max  | Unit   | Test Conditions/Comments                                                              |

|--------------------------------------------------------|--------|-----|------|------|--------|---------------------------------------------------------------------------------------|

| CENTER FREQUENCY                                       |        | 70  |      | 6000 | MHz    |                                                                                       |

| BANDWIDTH FLATNESS                                     |        |     | 0.1  |      | dB     |                                                                                       |

| DEVIATION FROM LINEAR PHASE                            |        |     | 1    |      | Degree |                                                                                       |

| POWER CONTROL RANGE                                    |        |     |      |      |        |                                                                                       |

| IQ Mode                                                |        |     | 42   |      | dB     | LO of 900MHz                                                                          |

| Direct Modulation Mode                                 |        |     | 12   |      | dB     | LO of 900MHz. Only through internal PLL                                               |

| POWER CONTROL RESOLUTION                               |        |     |      |      |        |                                                                                       |

| IQ Mode                                                |        |     | 0.05 |      | dB     |                                                                                       |

| IN BAND NOISE FLOOR                                    |        |     |      |      |        |                                                                                       |

| 100kHz                                                 |        |     | -135 |      | dBm/Hz | 0dB Attenuation                                                                       |

| 1MHz                                                   |        |     | -138 |      | dBm/Hz | 0dB Attenuation                                                                       |

| OUT OF BAND NOISE FLOOR                                |        |     |      |      |        |                                                                                       |

| 10MHz                                                  |        |     | -146 |      | dBm/Hz | 0dB Attenuation                                                                       |

| 100MHz                                                 |        |     | -148 |      | dBm/Hz | 0dB Attenuation                                                                       |

| IMAGE REJECTION WITH                                   |        |     |      |      |        | Internal LO, 0 dB transmitter Attenuation, -6dBFs, 4.1Khz offset                      |

| INITIALIZATION CALIBRATION                             |        |     |      |      |        | continuous wave Signal output                                                         |

| Narrow-Band                                            |        |     |      |      |        |                                                                                       |

| 70 MHz                                                 |        |     | 76   |      | dBc    |                                                                                       |

| 136 MHz                                                |        |     | 84   |      | dBc    |                                                                                       |

| 380 MHz                                                |        |     | 87   |      | dBc    |                                                                                       |

| 520 MHz                                                |        |     | 83   |      | dBc    |                                                                                       |

| 941 MHz                                                |        |     | 74   |      | dBc    |                                                                                       |

| CONTINUOUS WAVE FULL-SCALE OUTPUT POWER                |        |     |      |      |        | Full scale CW output and 0 dB transmitter attenuation. Backoff of 0.2dB               |

| 70MHz                                                  |        |     | 7.9  |      | dBm    |                                                                                       |

| 136MHz                                                 |        |     | 8.3  |      | dBm    |                                                                                       |

| 380MHz                                                 |        |     | 8.3  |      | dBm    |                                                                                       |

| 520MHz                                                 |        |     | 8.3  |      | dBm    |                                                                                       |

| 941MHz                                                 |        |     | 8.2  |      | dBm    |                                                                                       |

| OUTPUT IMPEDANCE                                       | ZOUT   |     | 50   |      | Ω      | Differential                                                                          |

| MAXIMUM OUTPUT LOAD VOLTAGE STANDING WAVE RATIO (VSWR) |        |     | TBD  |      | Ω      | Use the maximum value to ensure adequate calibration.                                 |

| OUTPUT RETURN LOSS                                     |        |     |      |      |        | Unmatched differential port return loss. From simulation, no trace or balun included. |

| 70 MHz                                                 |        |     | 29   |      | dB     |                                                                                       |

| 136 MHz                                                |        |     | 29   |      | dB     |                                                                                       |

| 380 MHz                                                |        |     | 26   |      | dB     |                                                                                       |

| 520 MHz                                                |        |     | 24   |      | dB     |                                                                                       |

| 941 MHz                                                |        |     | 20   |      | dB     |                                                                                       |

analog.com Rev. PrC | 4 of 23

Table 1. Transmitter (Continued)

| Parameter                                       | Symbol | Min | Тур   | Max | Unit | Test Conditions/Comments                                                                               |

|-------------------------------------------------|--------|-----|-------|-----|------|--------------------------------------------------------------------------------------------------------|

| OUTPUT THIRD-ORDER INTERCEPT POINT              | OIP3   |     |       |     |      | Internal LO, 0 dB transmitter attenuation. Continuous wave tones at 4.1 kHz and 5.1 kHz, -7 dBFS/tone. |

| 70MHz                                           |        |     | 30.8  |     | dBm  |                                                                                                        |

| 136MHz                                          |        |     | 31.8  |     | dBm  |                                                                                                        |

| 380MHz                                          |        |     | 32.5  |     | dBm  |                                                                                                        |

| 520 MHz                                         |        |     | 32.3  |     | dBm  |                                                                                                        |

| 941MHz                                          |        |     | 33.9  |     | dBm  |                                                                                                        |

| CARRIER LEAKAGE WITH INITIALIZATION CALIBRATION |        |     |       |     |      | Internal LO, 0 dB transmitter Attenuation, -6dBFs, 4.1Khz offset continuous wave Signal output         |

| Narrow-Band                                     |        |     |       |     |      |                                                                                                        |

| 70 MHz                                          |        |     | -74.9 |     | dBm  |                                                                                                        |

| 136 MHz                                         |        |     | -71.7 |     | dBm  |                                                                                                        |

| 380 MHz                                         |        |     | -71.7 |     | dBm  |                                                                                                        |

| 520 MHz                                         |        |     | -74.1 |     | dBm  |                                                                                                        |

| 941 MHz                                         |        |     | -68.2 |     | dBm  |                                                                                                        |

# **RECEIVER SPECIFICATIONS**

### Table 2. Receiver (Rx2)

| Parameter                                 | Symbol | Min | Тур   | Max  | Unit | Test Conditions/Comments                                                                                                                                                                                          |

|-------------------------------------------|--------|-----|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CENTER FREQUENCY                          |        | 70  |       | 6000 | MHz  |                                                                                                                                                                                                                   |

| MAXIMUM GAIN                              |        |     |       |      |      |                                                                                                                                                                                                                   |

| 70 MHz                                    |        |     | 22.2  |      | dB   |                                                                                                                                                                                                                   |

| 136 MHz                                   |        |     | 22.3  |      | dB   |                                                                                                                                                                                                                   |

| 380 MHz                                   |        |     | 22.6  |      | dB   |                                                                                                                                                                                                                   |

| 520 MHz                                   |        |     | 22.3  |      | dB   |                                                                                                                                                                                                                   |

| 941 MHz                                   |        |     | 22.6  |      | dB   |                                                                                                                                                                                                                   |

| ATTENUATION RANGE FROM<br>MAXIMUM GAIN    |        |     | 34    |      | dB   |                                                                                                                                                                                                                   |

| Attenuation Accuracy                      |        |     |       |      |      |                                                                                                                                                                                                                   |

| Gain Step                                 |        |     | 0.5   |      | dB   | Attenuator steps from 0 dB to 30 dB.                                                                                                                                                                              |

|                                           |        |     | 1     |      | dB   | Attenuator steps from 30 dB to 34 dB.                                                                                                                                                                             |

| Gain Step Error                           |        |     | 0.1   |      | dB   | Attenuator steps from 0 dB to 30 dB.                                                                                                                                                                              |

|                                           |        |     | TBD   |      |      | Attenuator steps from 30 dB to 34 dB.                                                                                                                                                                             |

| FREQUENCY RESPONSE                        |        |     |       |      |      |                                                                                                                                                                                                                   |

| Peak-to-Peak Gain Deviation               |        |     | 1     |      | dB   |                                                                                                                                                                                                                   |

| RECEIVER BANDWIDTH                        |        | 12  |       | 2000 | kHz  |                                                                                                                                                                                                                   |

| RECEIVER ALIAS BAND REJECTION             |        | 80  |       |      | dB   | This performance is achieved because of the digital filters                                                                                                                                                       |

| CONTINUOUS WAVE FULL-SCALE<br>INPUT POWER | FSIP   |     |       |      |      | This continuous wave signal level corresponds to the input power at maximum gain that produces 0 dBFS at the ADC output, this level increases dB for dB with attenuation, backoff by at least -1 dBFS is required |

| 70 MHz                                    |        |     | -11.8 |      | dBm  |                                                                                                                                                                                                                   |

| 136 MHz                                   |        |     | -12.5 |      | dBm  |                                                                                                                                                                                                                   |

| 380 MHz                                   |        |     | -12.2 |      | dBm  |                                                                                                                                                                                                                   |

| 520.MHz                                   |        |     | -12.5 |      | dBm  |                                                                                                                                                                                                                   |

| 941 MHz                                   |        |     | -12.3 |      | dBm  |                                                                                                                                                                                                                   |

| INPUT IMPEDANCE                           |        |     | 100   |      | Ω    | Differential                                                                                                                                                                                                      |

| INPUT PORT RETURN LOSS                    |        |     |       |      |      | Values from simulation, without board trace or balun                                                                                                                                                              |

| 70 MHz                                    |        |     | 29    |      | dB   |                                                                                                                                                                                                                   |

analog.com Rev. PrC | 5 of 23

Table 2. Receiver (Rx2) (Continued)

| Parameter                                             | Symbol   | Min | Тур              | Max | Unit | Test Conditions/Comments                                                                                                                        |

|-------------------------------------------------------|----------|-----|------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 136 MHz                                               |          |     | 28               |     | dB   |                                                                                                                                                 |

| 380 MHz                                               |          |     | 26               |     | dB   |                                                                                                                                                 |

| 520 MHz                                               |          |     | 26               |     | dB   |                                                                                                                                                 |

| 941 MHz                                               |          |     | 26               |     | dB   |                                                                                                                                                 |

| NOISE FIGURE                                          | NF       |     |                  |     |      | Measured at max gain vs LO                                                                                                                      |

| 70 MHz                                                |          |     | 14               |     | dB   |                                                                                                                                                 |

| 136 MHz                                               |          |     | 13               |     | dB   |                                                                                                                                                 |

| 380 MHz                                               |          |     | 13               |     | dB   |                                                                                                                                                 |

| 520 MHz                                               |          |     | 13               |     | dB   |                                                                                                                                                 |

| 941 MHz                                               |          |     | 12               |     | dB   |                                                                                                                                                 |

| SECOND-ORDER INPUT<br>INTERMODULATION INTERCEPT POINT |          |     |                  |     |      | Max Receiver Gain, One tone at 50Khz carrier frequency offset, second tone at 492Khz carrier frequency offset, tone output power is -9dBFs/tone |

| Rx2 Narrow-Band                                       | IIP2LB   |     |                  |     |      |                                                                                                                                                 |

| 70 MHz                                                |          |     | 97.0             |     | dBm  |                                                                                                                                                 |

| 136 MHz                                               |          |     | 97.3             |     | dBm  |                                                                                                                                                 |

| 380 MHz                                               |          |     | 88.6             |     | dBm  |                                                                                                                                                 |

| 520 MHz                                               |          |     | 85.5             |     | dBm  |                                                                                                                                                 |

| 941 MHz                                               |          |     | 80.8             |     | dBm  |                                                                                                                                                 |

| THIRD-ORDER INPUT                                     |          |     |                  |     |      | Max Receiver Gain, Two tone at 50Khz/100Khz carrier frequency offset                                                                            |

| INTERMODULATION INTERCEPT POINT, DIFFERENCE PRODUCT   |          |     |                  |     |      | respectively, tone output power is -9 dBFs/tone                                                                                                 |

| Rx2 Narrow-Band                                       | LB -     |     |                  |     |      |                                                                                                                                                 |

|                                                       | IIP3DIFF |     |                  |     |      |                                                                                                                                                 |

| 70 MHz                                                |          |     | 28.9             |     | dBm  |                                                                                                                                                 |

| 136 MHz                                               |          |     | 26.8             |     | dBm  |                                                                                                                                                 |

| 380 MHz                                               |          |     | 25.6             |     | dBm  |                                                                                                                                                 |

| 520 MHz                                               |          |     | 24.4             |     | dBm  |                                                                                                                                                 |

| 941 MHz                                               |          |     | 23.1             |     | dBm  |                                                                                                                                                 |

| THIRD-ORDER HARMONIC DISTORTION                       |          |     |                  |     |      | Max Receiver Gain, Input continuous wave signal at Carrier frequency + 294KHz (2/3 IF), tone output power is -1dBFS                             |

| Rx2 Narrow-Band                                       | HD3LB    |     |                  |     |      |                                                                                                                                                 |

| 70 MHz                                                |          |     | 122.7            |     | dBc  |                                                                                                                                                 |

| 136 MHz                                               |          |     | 126.3            |     | dBc  |                                                                                                                                                 |

| 380 MHz                                               |          |     | 109.8            |     | dBc  |                                                                                                                                                 |

| 520 MHz                                               |          |     | 108.7            |     | dBc  |                                                                                                                                                 |

| 941 MHz                                               |          |     | 105.4            |     | dBc  |                                                                                                                                                 |

| SECOND-ORDER HARMONIC DISTORTION                      |          |     |                  |     |      | Max Receiver Gain, Input continuous wave signal at Carrier frequency + 221KHz (1/2 IF), tone output power is -1dBFS                             |

| Rx2 Narrow-Band                                       | HD2LB    |     |                  |     |      |                                                                                                                                                 |

| 70 MHz                                                |          |     | 103.5            |     | dBc  |                                                                                                                                                 |

| 136 MHz                                               |          |     | 102.5            |     | dBc  |                                                                                                                                                 |

| 380 MHz                                               |          |     | 96.9             |     | dBc  |                                                                                                                                                 |

| 520 MHz                                               |          |     | 94.9             |     | dBc  |                                                                                                                                                 |

| 941 MHz                                               |          |     | 95.4             |     | dBc  |                                                                                                                                                 |

| IMAGE REJECTION                                       |          |     | JJ. <del>4</del> |     | uDC  | Ext LO. Gain sweep from index 255 to 195. Tone is input at 3k, amplitude                                                                        |

|                                                       |          |     |                  |     |      | adjusted to measure –10dB on data capture.                                                                                                      |

| Narrow-Band                                           |          |     |                  |     |      |                                                                                                                                                 |

| 70 MHz                                                |          |     | 105              |     | dBc  |                                                                                                                                                 |

| 136 MHz                                               |          |     | 103              |     | dBc  |                                                                                                                                                 |

analog.com Rev. PrC | 6 of 23

Table 2. Receiver (Rx2) (Continued)

| Parameter                                 | Symbol | Min | Тур | Max | Unit | Test Conditions/Comments |

|-------------------------------------------|--------|-----|-----|-----|------|--------------------------|

| 380 MHz                                   |        |     | 103 |     | dBc  |                          |

| 520 MHz                                   |        |     | 101 |     | dBc  |                          |

| 941 MHz                                   |        |     | 103 |     | dBc  |                          |

| RECEIVER INPUT LO LEAKAGE AT MAXIMUM GAIN |        |     |     |     |      |                          |

| 70 MHz                                    |        |     | TBD |     | dBm  |                          |

| 136 MHz                                   |        |     | TBD |     | dBm  |                          |

| 380 MHz                                   |        |     | TBD |     | dBm  |                          |

| 520 MHz                                   |        |     | TBD |     | dBm  |                          |

| 941 MHz                                   |        |     | TBD |     | dbm  |                          |

| SIGNAL ISOLATION                          |        |     |     |     |      |                          |

| Tx to Rx2 Isolation                       |        |     |     |     |      |                          |

| 70 MHz                                    |        |     | TBD |     | dB   |                          |

| 136 MHz                                   |        |     | TBD |     | dB   |                          |

| 380 MHz                                   |        |     | TBD |     | dB   |                          |

| 520 MHz                                   |        |     | TBD |     | dB   |                          |

| 941 MHz                                   |        |     | TBD |     | dB   |                          |

# INTERNAL LO, EXTERNAL LO, AND DEVICE CLOCK

### Table 3.

| Parameter                                      | Symbol | Min | Тур | Max   | Unit    | Test Conditions/Comments                                                                                   |

|------------------------------------------------|--------|-----|-----|-------|---------|------------------------------------------------------------------------------------------------------------|

| LOCAL OSCILLATOR                               |        |     |     |       |         |                                                                                                            |

| LO Frequency Step                              |        |     |     | 2.2   | Hz      | For 38.4 MHz DEV_CLK, use the equation DEV_CLK/((223 - 15) × 2) to calculate, assuming the LO divider is 2 |

| LO Reference Spurs                             |        |     | -80 |       | dBc     | LO < 1 GHz, PLL bandwidth = 300 kHz                                                                        |

| LOCAL OSCILLATOR WITH HIGH<br>PERFORMANCE MODE |        |     |     |       |         |                                                                                                            |

| Integrated Phase Noise                         |        |     |     |       |         |                                                                                                            |

| 136 MHz LO                                     |        |     | TBD |       | °rms    |                                                                                                            |

| 520 MHz LO                                     |        |     | TBD |       | °rms    |                                                                                                            |

| 941 MHz LO                                     |        |     | TBD |       | °rms    |                                                                                                            |

| Phase Noise                                    |        |     |     |       |         |                                                                                                            |

| 136 MHz LO                                     |        |     | TBD |       |         |                                                                                                            |

| 520 MHz LO                                     |        |     | TBD |       |         |                                                                                                            |

| 941 MHz LO                                     |        |     | TBD |       |         |                                                                                                            |

| LO PHASE SYNCHRONIZATION                       |        |     |     |       |         |                                                                                                            |

| Initial Phase Synchronization Accuracy         |        |     | TBD |       | ps      |                                                                                                            |

| EXTERNAL LO INPUT                              |        |     |     |       |         |                                                                                                            |

| Input Frequency                                |        |     |     |       |         |                                                                                                            |

| 2x VCO/LO Input                                |        | 140 |     | 12000 | MHz     |                                                                                                            |

| 1x VCO/LO Input                                |        | 250 |     | 1000  | MHz     |                                                                                                            |

| Input Signal Power                             |        | -6  | 0   |       | dBm     | 100 Ω matching at the device differential input. Divider set to 4 by default.                              |

| Input Signal Differential Phase Balance        |        |     |     | 20    | Degrees | Do not exceed 20 degrees to ensure adequate quadrature error correction.                                   |

| Input Signal Differential Amplitude Balance    |        |     |     | 1     | dB      |                                                                                                            |

analog.com Rev. PrC | 7 of 23

Table 3. (Continued)

| Parameter                           | Symbol | Min | Тур | Max   | Unit  | Test Conditions/Comments                                                                                                                                  |

|-------------------------------------|--------|-----|-----|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Signal Duty Cycle Error       |        |     |     | 2.5   | %     |                                                                                                                                                           |

| Input Impedance                     |        |     | 100 |       | Ω     | Differential                                                                                                                                              |

| REFERENCE CLOCK (DEV_CLK_IN SIGNAL) |        |     |     |       |       |                                                                                                                                                           |

| Differential mode                   |        |     |     |       |       |                                                                                                                                                           |

| Frequency Range                     |        | 10  |     | 307.2 | MHz   |                                                                                                                                                           |

| Signal Level                        |        | 0.2 |     | 0.4   | V p-p | AC-coupled, for optimal spurious performance and to meet the specified PLL performance parameters, use a 400 mV p-p (800 mV p-p differential) input clock |

| Single-Ended Mode                   |        |     |     |       |       |                                                                                                                                                           |

| Frequency Range                     |        | 10  |     | 80    | MHz   |                                                                                                                                                           |

| Signal Level                        |        | 0.2 |     | 1     | V p-p | AC-coupled, for optimal spurious performance and to meet the specified PLL performance parameters, use a 1V p-p input clock.                              |

| REFERENCE CLOCK (XTAL)              |        |     |     |       |       |                                                                                                                                                           |

| Frequency Range                     |        | 20  |     | 80    | MHz   |                                                                                                                                                           |

| CLOCK OUTPUT (DEV_CLK_OUT SIGNAL)   |        |     |     |       |       |                                                                                                                                                           |

| Frequency Range                     |        | 10  |     | 80    | MHz   |                                                                                                                                                           |

# **EXTERNAL VCO CHARGE PUMP**

| Parameter                        | Symbol | Min | Тур | Max | Unit | Test Conditions/Comments |

|----------------------------------|--------|-----|-----|-----|------|--------------------------|

| CHARGE PUMP(CP)                  |        |     |     |     |      |                          |

| CP Current Sink and Source       |        |     |     |     |      |                          |

| High Value                       |        |     | 6.4 |     | mA   |                          |

| Low Value                        |        |     | 0.1 |     | mA   |                          |

| Absolute Accuracy                |        |     | TBD |     | %    |                          |

| ICP Three-State Leakage          |        |     | TBD |     | nA   |                          |

| Sink and Source Current Matching |        |     | TBD |     | %    |                          |

| ICP vs. VCP                      |        |     | TBD |     | %    |                          |

| ICP vs. Temperature              |        |     | TBD |     | %    |                          |

# **DIGITAL INTERFACES AND AUXILIARY CONVERTERS**

Table 4.

| Parameter                | Min | Тур        | Max | Unit | Test Conditions/Comments |

|--------------------------|-----|------------|-----|------|--------------------------|

| AUXILIARY ADC CONVERTERS |     |            |     |      |                          |

| Resolution               |     | 10         |     | Bits |                          |

| Input Voltage            |     |            |     |      |                          |

| Minimum                  |     | 0.05       |     | V    |                          |

| Maximum                  |     | 0.95       |     | V    |                          |

| AUXILIARY DAC CONVERTERS |     |            |     |      |                          |

| Resolution               |     | 12         |     | Bits |                          |

| Output Voltage           |     |            |     |      |                          |

| Minimum                  |     | 0.05       |     | V    |                          |

| Maximum                  |     | VDDA_1P8 - |     | V    |                          |

|                          |     | 0.05       |     |      |                          |

| Drive Capability         |     | 10         |     | mA   |                          |

analog.com Rev. PrC | 8 of 23

Table 4. (Continued)

| Parameter                                     | Min             | Тур      | Max             | Unit | Test Conditions/Comments |

|-----------------------------------------------|-----------------|----------|-----------------|------|--------------------------|

| DIGITAL SPECIFICATIONS (CMOSSISIGNALS)        |                 | <u> </u> |                 |      |                          |

| Logic Inputs                                  |                 |          |                 |      |                          |

| Input Voltage                                 |                 |          |                 |      |                          |

| High Level                                    | VDIG_1P8 × 0.65 |          | VDIG_1P8 + 0.18 | V    |                          |

| Low Level                                     | -0.30           |          | VDIG_1P8 × 0.35 | V    |                          |

| Logic Outputs Voltage                         |                 |          | _               |      |                          |

| Output Voltage                                |                 |          |                 |      |                          |

| High Level                                    | VDIG_1P8 - 0.45 |          |                 | V    |                          |

| Low Level                                     | _               |          | 0.45            | V    |                          |

| Drive Capability                              |                 | 10       |                 | mA   |                          |

| DIGITAL SPECIFICATIONS (DIGITAL GPIO SIGNALS) |                 |          |                 |      |                          |

| Logic Inputs                                  |                 |          |                 |      |                          |

| Input Voltage                                 |                 |          |                 |      |                          |

| High Level                                    | VDIG_1P8 × 0.65 |          | VDIG_1P8 + 0.18 | V    |                          |

| Low Level                                     | -0.30           |          | VDIG_1P8 × 0.35 | V    |                          |

| Logic Outputs                                 |                 |          | _               |      |                          |

| Output Voltage                                |                 |          |                 |      |                          |

| High Level                                    | VDIG_1P8 - 0.45 |          |                 | V    |                          |

| Low Level                                     |                 |          | 0.45            | V    |                          |

| Drive Capability                              |                 | 10       |                 | mA   |                          |

| DATAPORT SPECIFICATIONS (LVDS SSI, MCS+/MCS-) |                 |          |                 |      |                          |

| Logic Inputs                                  |                 |          |                 |      |                          |

| Input Voltage Range                           | 825             |          | 1675            | mV   |                          |

| Input Differential Voltage<br>Threshold       | -100            |          | +100            | mV   |                          |

| Receiver Differential Input Impedance         |                 | 100      |                 | Ω    |                          |

| Logic Outputs                                 |                 |          |                 |      |                          |

| Output Voltage                                |                 |          |                 |      |                          |

| High                                          |                 |          | 1390            | mV   |                          |

| Low                                           | 1000            |          |                 | mV   |                          |

| Differential                                  |                 | 300      |                 | mV   |                          |

| Offset                                        |                 | 1200     |                 | mV   |                          |

| Output Current                                |                 |          | 4.1             | mA   |                          |

| Clock Signal Duty Cycle                       | 45              | 50       | 55              | %    |                          |

| Output Rise/Fall Time                         |                 | 0.371    |                 | ns   |                          |

| DIGITAL SPECIFICATIONS (ANALOG GPIO SIGNALS)  |                 |          |                 |      |                          |

| Logic Inputs                                  |                 |          |                 |      |                          |

| Input Voltage                                 |                 |          |                 |      |                          |

| High Level                                    | VDDA_1P8 × 0.65 |          | VDDA_1P8 + 0.18 |      |                          |

| Low Level                                     | -0.30           |          | VDDA_1P8 × 0.35 | V    |                          |

| Logic Outputs                                 |                 |          |                 |      |                          |

| Output Voltage                                |                 |          |                 |      |                          |

| High Level                                    | VDDA_1P8 - 0.45 |          |                 | V    |                          |

| Low Level                                     |                 |          | 0.45            | V    |                          |

analog.com Rev. PrC | 9 of 23

#### Table 4. (Continued)

| Parameter        | Min | Тур | Max | Unit | Test Conditions/Comments |

|------------------|-----|-----|-----|------|--------------------------|

| Drive Capability |     | 10  |     | mA   |                          |

#### POWER SUPPLY SPECIFICATIONS

#### Table 5.

| Parameter                             | Min | Тур | Max | Unit |

|---------------------------------------|-----|-----|-----|------|

| SUPPLY CHARACTERISTICS                |     |     |     |      |

| VDDA_1P0 <sup>1</sup> Analog Supplies |     | 1.0 |     | V    |

| VDD_1P0 <sup>2</sup> Digital Supply   |     | 1.0 |     | V    |

| VDDA_1P8 <sup>3</sup> Analog Supplies |     | 1.8 |     | V    |

| VDD_1P8 <sup>4</sup> Digital Supply   |     | 1.8 |     | V    |

<sup>1</sup> VDDA\_1P0 refers to all analog 1.0 V supplies, including VANA1\_1P0, VANA2\_1P0 , VRFSYN1\_1P0, VRFSYN2\_1P0, VCLKSYN\_1P0, VRFLO1\_1P0, VRFLO2\_1P0, VCONV1\_1P0, VCONV2\_1P0, VAGPIO\_1P0, VRX1LO\_1P0, VRX1LO\_1P0, VCLKVCO\_1P0, VTXLO\_1P0, VDEVCLK\_1P0, VEXTLO1\_1P0, VEXTLO2\_1P0.

# **POWER CONSUMPTION ESTIMATES (TYPICAL VALUES)**

The values in Table 6 are based on the following configuration: DEV\_CLK: 38.4Mhz, Input Sample Rate: 24KSPS, DAC Sample Rate: 38.4Mhz, 4X EXT LO Mode with Tx channel power on only.

Table 6. Tx Power Consumption

| Conditions                                             | VDDA_1P0 Analog<br>Supplies | VDD_1P0 Digital<br>Supply | VDDA_1P8 Analog<br>Supplies | VDD_1P8 Digital<br>Supply | Total Average Power (mW) |

|--------------------------------------------------------|-----------------------------|---------------------------|-----------------------------|---------------------------|--------------------------|

| Tx Attenuation: 0 dB<br>RF PLL is Enabled for EXT VCO  | 170                         | 22                        | 141                         | 1.9                       | 450                      |

| Tx Attenuation: 10 dB<br>RF PLL is Enabled for EXT VCO | 170                         | 22                        | 67.2                        | 1.9                       | 316                      |

The values in Table 7 are based on the following configuration: DEV\_CLK: 38.4Mhz, with Tx channel power on only.

Table 7. Tx Power Consumption with Internal LO

| Conditions                                                                                                 | VDDA_1P0 Analog<br>Supplies | VDD_1P0 Digital<br>Supply | VDDA_1P8 Analog<br>Supplies | VDD_1P8 Digital<br>Supply | Total Average Power (mW) |

|------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|-----------------------------|---------------------------|--------------------------|

| Tx Attenuation: 0 dB Input Sample Rate: 2.4MSPS, DAC Sample Rate: 38.4Mhz, Internal LO Mode at 450MHz      | 204.6                       | 24.7                      | 193.5                       | 5.4                       | 588                      |

| Tx Attenuation: 10 dB Input Sample Rate: 2.4MSPS, DAC Sample Rate: 38.4Mhz, Internal LO Mode at 450MHz     | 204.2                       | 24.6                      | 114.3                       | 5.2                       | 444                      |

| Tx Attenuation: 0 dB Input Sample Rate: 30.72MSPS, DAC Sample Rate: 552.96Mhz, Internal LO Mode at 450MHz  | 302.8                       | 215.5                     | 231.9                       | 34.1                      | 997                      |

| Tx Attenuation: 10 dB Input Sample Rate: 30.72MSPS, DAC Sample Rate: 552.96Mhz, Internal LO Mode at 450MHz | 302.8                       | 215.7                     | 155.9                       | 33.6                      | 859.6                    |

analog.com Rev. PrC | 10 of 23

<sup>&</sup>lt;sup>2</sup> VDD\_1P0 refers to all digital 1.0 V supplies including VDIG\_1P0.

<sup>&</sup>lt;sup>3</sup> VDD\_1P8 refers to all analog 1.8 V supplies including VAGPIO\_1P8, VCONV1\_1P8, VCONV2\_1P8, VANA1\_1P8, VANA2\_1P8, VRFVCO1\_1P8, VRFVCO2\_1P8.

<sup>&</sup>lt;sup>4</sup> VDD\_1P8 refers to all digital 1.8 V supplies including VDIG\_1P8.

The values in Table 8 are based on the following configuration: DEV\_CLK: 38.4Mhz, ADC Sample Rate: 38.4Mhz, Output Sample Rate: 24Khz, 4X EXT LO Mod, with Rx channel power on only.

Table 8. Rx Power Consumption

| Conditions                    | VDDA_1P0 Analog<br>Supplies | VDD_1P0 Digital<br>Supply | VDDA_1P8 Analog<br>Supplies | VDD_1P8 Digital<br>Supply | Total Average Power (mW) |

|-------------------------------|-----------------------------|---------------------------|-----------------------------|---------------------------|--------------------------|

| RF PLL is Enabled for EXT VCO | 45.2                        | 22.5                      | 19                          | 1.5                       | 105                      |

The values in Table 9 are based on the following configuration: DEV\_CLK: 38.4Mhz, with Rx channel power on only.

Table 9. Rx Power Consumption with Internal LO

| Conditions                                                                                            | VDDA_1P0 Analog<br>Supplies | VDD_1P0 Digital<br>Supply | VDDA_1P8 Analog<br>Supplies | VDD_1P8 Digital<br>Supply | Total Average Power (mW) |

|-------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|-----------------------------|---------------------------|--------------------------|

| Rx2 NB enabled, Sample Rate: 2.4MSPS,<br>ADC Sample Rate: 38.4Mhz, Internal LO<br>Mode at 450MHz      | 55                          | 27.6                      | 51.8                        | 4.2                       | 183.4                    |

| Rx1 WB enabled, Sample Rate: 30.72MSPS,<br>ADC Sample Rate: 1105.92Mhz, Internal LO<br>Mode at 450MHz | 134.5                       | 190.4                     | 97.7                        | 20                        | 536.8                    |

analog.com Rev. PrC | 11 of 23

|   | 1                 | 2             | 3                | 4                   | 5                   | 6                  | 7                  | 8                  | 9                  | 10                  | 11                  | 12              | 13                | 14              |

|---|-------------------|---------------|------------------|---------------------|---------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|-----------------|-------------------|-----------------|

| A | VSSA              | VSSA          | VSSA             | VANA1_1P<br>0       | VSSA                | VSSA               | RX1-               | RX1+               | VSSA               | VSSA                | VSSA                | VANA2_1P<br>8   | VSSA              | VSSA            |

| В | TX+               | VANA1_1P8     | VTXLO_1P<br>0    | VSSA                | VRX1LO_1<br>P0      | VSSA               | VSSA               | VSSA               | VSSA               | VRX2LO_1<br>P0      | VSSA                | VANA2_1P<br>0   | VSSA              | RX2+            |

| c | тх-               | VSSA          | VSSA             | VSSA                | AGPIO_0             | AGPIO_1            | AUXADC_<br>0       | AUXADC_<br>1       | AGPIO_8            | AGPIO_9             | MODEA               | RBIAS           | VSSA              | RX2-            |

| D | VSSA              | VSSA          | VCO2_VC          | VSSA                | VRFLO2_1<br>P0      | VSSA               | VRFSYN2_<br>1P0    | VRFSYN1_<br>1P0    | VSSA               | VRFLO1_1<br>P0      | VSSA                | vco1_vc         | VSSA              | VSSA            |

| E | VCO2_VC_<br>INT   | VCO2_VF_SENSE | VCO2_VF          | VSSA                | AGPIO_2             | AGPIO_3            | VSSA               | VSSA               | VSSA               | AGPIO_10            | VSSA                | VCO1_VF         | VCO1_VF_<br>SENSE | VCO1_VC_<br>INT |

| F | VEXTLO2_<br>1P0   | VSSA          | VSSA             | VRFVCO2_<br>CAP     | AGPIO_4             | AGPIO_5            | VCONV1_1<br>P8     | VAGPIO_1<br>P8     | VCONV2_1<br>P8     | AGPIO_11            | VRFVCO1_<br>CAP     | VSSA            | VSSA              | VEXTLO1_<br>1P0 |

| G | EXT_LO2+          | EXT_LO2-      | VSSA             | VRFVCO2_<br>1P8     | AGPIO_6             | AGPIO_7            | VCONV1_1<br>P0     | VAGPIO_1<br>P0     | VCONV2_1<br>P0     | AGPIO_12            | VRFVCO1_<br>1P8     | VSSA            | EXT_LO1-          | EXT_LO1+        |

| н | VSSA              | VSSA          | VSSA             | VSSA                | VSSA                | VSSA               | VSSA               | VSSA               | VSSA               | VSSA/TES<br>T+      | VSSA                | VSSA            | VSSA              | VSSA            |

| j | DGPIO_0           | DGPIO_1       | DGPIO_2          | DGPIO_5             | DGPIO_8             | DGPIO_12           | DGPIO_13           | DGPIO_14           | DGPIO_18           | VSSA/TES<br>T-      | VCLKVCO_<br>CAP     | VCLKVCO_<br>1P0 | AGPIO_13          | VCLKSYN_<br>1P0 |

| K | TX_STROB<br>E_IN- | TX_STROBE_IN+ | DGPIO_3          | DGPIO_6             | DGPIO_9             | VDIG_1P0           | VDIG_1P0           | DGPIO_15           | DGPIO_19           | VSSA                | VSSA                | VSSA            | VSSA              | VSSA            |

| ι | TX_IDATA<br>_IN-  | TX_IDATA_IN+  | DGPIO_4          | DGPIO_7             | DGPIO_10            | VSSD               | VSSD               | DGPIO_16           | SPI_EN             | SPI_CLK             | GP_INT              | MCS-            | VDEVCLK_<br>1P0   | DEV_CLK_<br>IN+ |

| м | TX_QDAT<br>A_IN-  | TX_QDATA_IN+  | TX_EN            | TX_EN_OP<br>T       | DGPIO_11            | VDIG_1P8           | VDIG_CAP           | DGPIO_17           | SPI_DO             | SPI_DIO             | DEV_CLK_<br>OUT     | VSSA            | MCS+              | DEV_CLK_<br>IN- |

| N | TX_DCLK_<br>IN-   | TX_DCLK_IN+   | MODE             | RX1_STRO<br>BE_OUT- | RX1_STRO<br>BE_OUT+ | RX1_DCLK<br>_OUT-  | RX1_DCLK<br>_OUT+  | RX2_QDA<br>TA_OUT+ | RX2_QDA<br>TA_OUT- | RX2_STRO<br>BE_OUT+ | RX2_STRO<br>BE_OUT- | RESETB          | VSSA              | VSSA            |

| P | VSSD              | TX_DCLK_OUT-  | TX_DCLK_<br>OUT+ | RX1_IDAT<br>A_OUT-  | RX1_IDAT<br>A_OUT+  | RX1_QDA<br>TA_OUT- | RX1_QDA<br>TA_OUT+ | RX2_DCLK<br>_OUT+  | RX2_DCLK<br>_OUT-  | RX2_IDAT<br>A_OUT+  | RX2_IDAT<br>A_OUT-  | RX1_EN          | RX2_EN            | VSSD            |

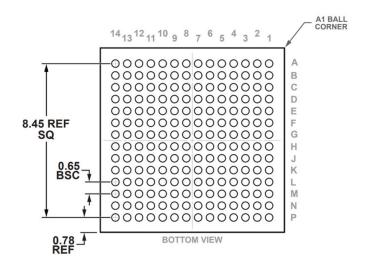

Figure 2. Pin Configuration

## Table 10. Pin Function Descriptions

| Pin No.                                                                                                                                                                                                                                      | Туре   | Mnemonic   | Description                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|-------------------------------------------------------------------------------------------------------------------|

| A1, A2, A3, A5, A6, A9, A10,<br>A11, A13, A14, B4, B6 to B9,<br>B11, B13, C2, C3, C4, C13,<br>D1, D2, D4, D6, D9, D11,<br>D13, D14, E4, E7, E8, E9,<br>E11, F2, F3, F12, F13, G3,<br>G12, H1 to H9, H11 to H14,<br>K10 to K14, M12, N13, N14 | Input  | VSSA       | Analog Ground                                                                                                     |

| A4                                                                                                                                                                                                                                           | Input  | VANA1_1P0  | 1.0 V Analog Supply for RX1 TIA, TX Baseband Filter.                                                              |

| A7, A8                                                                                                                                                                                                                                       | Input  | RX1-, RX1+ | Differential Input for Receiver Channel 1 (Wide Band).  If unused, connect RX1- and RX1+ to VSSA via a capacitor. |

| A12                                                                                                                                                                                                                                          | Input  | VANA2_1P8  | 1.8 V Analog Supply for RX2 Mixer, RX2 TIA, and Internal References.                                              |

| B1, C1                                                                                                                                                                                                                                       | Output | TX+, TX-   | Differential Output for Transmitter Channel.  If unused, do not connect TX+ and TX                                |

| B2                                                                                                                                                                                                                                           | Input  | VANA1_1P8  | 1.8 V Analog Supply for RX1 Mixer, RX1 TIA, TX Mixer, TX Baseband Filter.                                         |

analog.com Rev. PrC | 12 of 23

Table 10. Pin Function Descriptions (Continued)

| Pin No.                     | Type   | Mnemonic           | Description                                                                                              |

|-----------------------------|--------|--------------------|----------------------------------------------------------------------------------------------------------|

| B3                          | Input  | VTXLO_1P0          | 1.0 V Analog Supply for TX LO Distribution and TX Upconverter.                                           |

| B5                          | Input  | VRX1LO_1P0         | 1.0 V Analog Supply for RX1 LO Distribution, RX1 Mixer.                                                  |

| B10                         | Input  | VRX2LO_1P0         | 1.0 V Analog Supply for RX2 LO Distribution, RX2 Mixer.                                                  |

| B12                         | Input  | VANA2_1P0          | 1.0 V Analog Supply for RX2 TIA                                                                          |

| B14, C14                    | Input  | RX2+, RX2-         | Differential Input for Receiver Channel 2 (Narrow Band).                                                 |

| , -                         | '      | ,                  | If unused, connect RX2- and RX2+ to VSSA via a capacitor.                                                |

| C5, C6, E5, E6, F5, F6, G5, | Input/ | AGPIO xx           | GPIOs Signals Referenced to VAGPIO_1P8 1.8 V Supply, AGPIO_0 to AGPIO_3 pins can also                    |

| G6, C9, C10, E10, F10, G10, | Output | 1                  | function as auxiliary DAC outputs.                                                                       |

| J13                         |        |                    | If unused, do not connect AGPIO_xx.                                                                      |

| C7                          | Input  | AUXADC_0           | Input to Auxiliary ADC0.                                                                                 |

|                             |        | 1317.2.2           | If unused, do not connect AUXADC_0.                                                                      |

| C8                          | Input  | AUXADC_1           | Input to Auxiliary ADC1.                                                                                 |

| 00                          | liiput | 7.070.00_1         | If unused, do not connect AUXADC 1.                                                                      |

| C11                         | Input  | MODEA              | Use MODEA to configure the boot up option for the DEV_CLK_IN± inputs and the DEV_CLK_OUT                 |

| OII                         | IIIput | WODEA              | output. Connect MODEA to VSSA to enable the differential clock receiver at the DEV_CLK_IN± pins.         |

|                             |        |                    | Connect MODEA to 1.8V supply to enable single ended clock at DEV_CLK_IN+. Connect MODEA to               |

|                             |        |                    | voltage level higher than any VSSA (level TBD) to enable the crystal oscillator resonator at both of the |

|                             |        |                    | DEV_CLK_IN± pins.                                                                                        |

| C12                         | Input  | RBIAS              | Bias Resistor Connection. RBIAS generates an internal current based on an external 1% resistor.          |

| <b>D</b> 0                  |        | 1,000 1,0          | Connect a 4.99 kΩ resistor between RBIAS and VSSA (analog ground).                                       |

| D3                          | Output | VCO2_VC            | External VCO2 Coarse tuning Voltage output                                                               |

| D5                          | Input  | VRFLO2_1P0         | 1.0 V Analog Supply for RF LO2 Generation                                                                |

| D7                          | Input  | VRFSYN2_1P0        | 1.0 V Analog Supply for RF PLL2                                                                          |

| D8                          | Input  | VRFSYN1_1P0        | 1.0 V Analog Supply for RF PLL1                                                                          |

| D10                         | Input  | VRFLO1_1P0         | 1.0 V Analog Supply for RF LO1 Generation                                                                |

| D12                         | Output | VCO1_VC            | External VCO1 Coarse tuning Voltage output                                                               |

| E1                          | Output | VCO2_VC_INT        | External VCO2 Coarse tuning Voltage Integration                                                          |

| E2                          | Input  | VCO2_VF_SENSE      | External VCO2 Fine tuning Voltage Sense input                                                            |

| E3                          | Output | VCO2_VF            | External VCO2 Fine tuning Voltage output                                                                 |

| E12                         | Output | VCO1_VF            | External VCO1 Fine tuning Voltage output                                                                 |

| E13                         | Input  | VCO1_VF_SENSE      | External VCO1 Fine tuning Voltage Sense input                                                            |

| E14                         | Output | VCO1_VC_INT        | External VCO1 Coarse tuning Voltage Integration                                                          |

| F1                          | Input  | VEXTLO2_1P0        | 1.0 V Analog Supply for External LO2                                                                     |

| F4                          | Output | VRFVCO2_CAP        | 1.6 V Internal Supply Node for RF PLL2 Circuitry. Bypass VRFVCO2_CAP with a 4.7 μF capacitor.            |

| F7                          | Input  | VCONV1_1P8         | 1.8 V Analog Supply for TX DAC, RX1 ADC.                                                                 |

| F8                          | Input  | VAGPIO_1P8         | 1.8 V Analog Supply for DEV_CLK, MCS, Auxiliary DACs, Auxiliary ADCs, and AGPIO Signals.                 |

| F9                          | Input  | VCONV2_1P8         | 1.8 V Analog Supply for RX2 ADC.                                                                         |

| F11                         | Output | VRFVCO1_CAP        | 1.6 V Internal Supply Node for RF PLL1 Circuitry. Bypass VRFVCO1_CAP with a 4.7 μF capacitor.            |

| F14                         | Input  | VEXTLO1_1P0        | 1.0 V Analog Supply for External LO1                                                                     |

| G1, G2                      | Input  | EXT_LO2+, EXT_LO2- | External LO/External VCO Input port 2 (LO2).                                                             |

|                             |        |                    | In differential mode, the input frequency could be 2x or higher than the desired carrier frequency. For  |

|                             |        |                    | the carrier frequency range of 250 MHz (TBD) to 1 GHz, 1x multiplier is available.                       |

|                             |        |                    | In single ended mode, the input frequency must be 2x or higher than the desired carrier frequency,       |