# 8-channel 16-bit Configurable IDAC/VDAC with On-Chip Reference

#### **FEATURES**

- Octal channel, configurable as any combination of VDAC or IDAC

- ▶ Guaranteed monotonicity : ±1 LSB<sub>16</sub> Max DNL

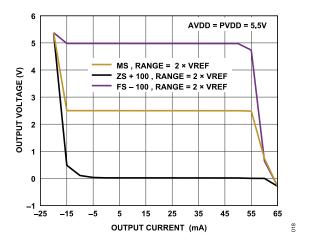

- ▶ 50mA output current drive for IDAC and VDAC modes

- ▶ 70mV max headroom for VDAC mode

- ▶ 0.25V max headroom for IDAC mode

- ▶ 2.5V internal voltage reference, 3ppm/°C typical

- ▶ Device addressable SPI interface

- ▶ Output supply range: +1.71V to +5.5V

- ▶ Diagnostic monitoring for output voltage, output current, and die temperature

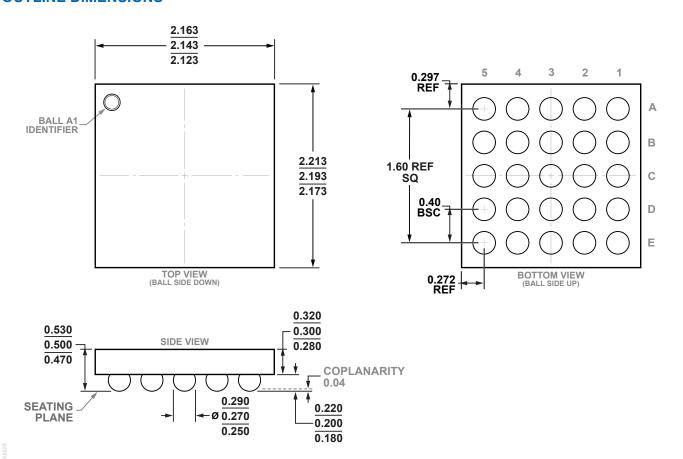

- ▶ Ultra small form factor: 2.1mm × 2.2mm, 25-ball WLCSP

- ▶ Operating temperature range: -40 °C to +125 °C

#### **APPLICATIONS**

- Optical networking

- ▶ Instrumentation

- Data acquisition

- Automatic test equipment

- Process control and industrial automation

#### **GENERAL DESCRIPTION**

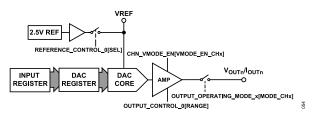

The AD5710R features eight DAC channels that can be independently configured as either a current output digital-to-analog converter (IDAC) or a voltage output digital-to-analog converter (VDAC). The AD5710R includes an integrated 2.5V, 3ppm/°C reference.

When the AD5710R outputs are configured as an IDAC, the output current range is 0mA to 50mA. When configured as a VDAC, the output voltage range is 0V to VREF or 0V to 2 × VREF.

The AD5710R is available in a 25-ball wafer level chip scale packaging (WLCSP) and is specified over the -40°C to +125°C temperature range.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    | 1  |

| Electrical Characteristics                  | 3  |

| DC Specifications                           | 3  |

| AC Specifications                           | 5  |

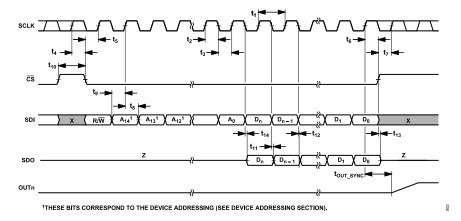

| Digital Interface Timing                    | 7  |

| Absolute Maximum Ratings                    | 9  |

| Thermal Resistance                          | 9  |

| ESD Caution                                 | 9  |

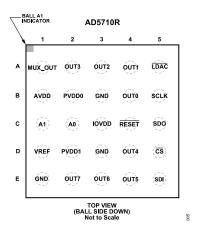

| Pin Configuration and Function Descriptions | 10 |

| Typical Performance Characteristics         | 11 |

| Terminology                                 |    |

| Theory of Operation                         | 21 |

| Digital-to-Analog Converter                 | 21 |

| Voltage Reference                           | 22 |

| Integrated Multiplexer                      | 22 |

| DAC Core Functions                          | 24 |

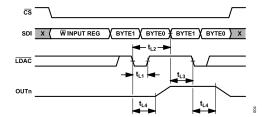

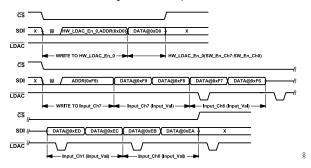

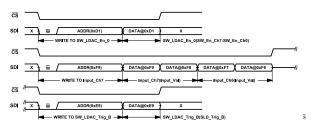

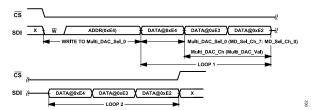

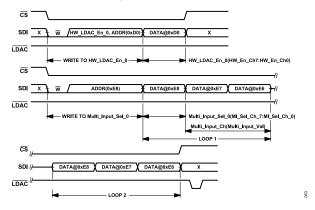

| LDAC Function                               | 24 |

| DAC Update                                  | 24 |

| Digital Interface                           | 28 |

|                                             |    |

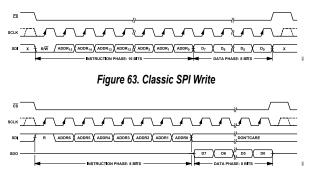

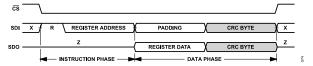

| SPI Frame Synchronization                 | .28  |

|-------------------------------------------|------|

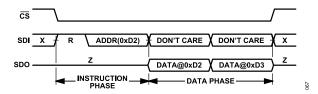

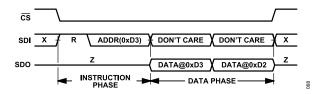

| Instruction Phase                         | .28  |

| Data Phase                                | .28  |

| Multibyte Registers                       | .28  |

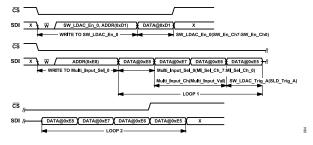

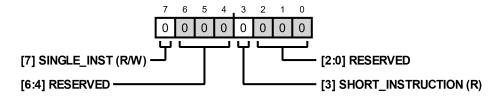

| Single Instruction Mode                   | .29  |

| Streaming Mode                            | .30  |

| Device Addressing                         | 31   |

| Device Status Errors                      | 32   |

| Cyclic Redundancy Check (CRC) Error       |      |

| Detection                                 | 32   |

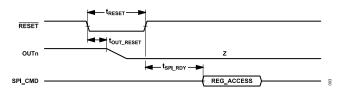

| Device Reset                              |      |

| Applications Information                  | 34   |

| Power Supply Recommendations              | 34   |

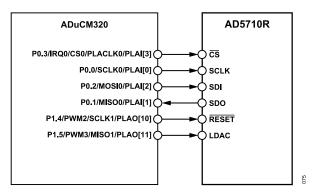

| Microprocessor Interfacing                | . 34 |

| Layout Guidelines and Assembly Guidelines | .34  |

| Thermal Considerations                    | 34   |

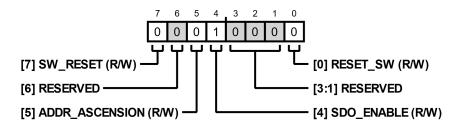

| Registers                                 | 36   |

| Register Summary                          | .36  |

| Register Details                          | . 38 |

| Outline Dimensions                        | 56   |

| Ordering Guide                            | .56  |

# **REVISION HISTORY**

10/2025—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 56

## **ELECTRICAL CHARACTERISTICS**

#### **DC SPECIFICATIONS**

AVDD = 2.7V to 5.5V, PVDDx = 2.7V to AVDD for VDAC channels, PVDDx = 1.71V to AVDD for IDAC channels, IOVDD = 1.08V to 1.98V, VREF = 2.5V (internal or external), all specifications are at  $T_J$  = -40°C to +125°C. Typical specifications at  $T_A$  = 25°C, unless otherwise noted.  $R_L$  = 2k $\Omega$ ,  $C_L$  = 200pF for VDAC channels.  $R_L$  = 50 $\Omega$  for IDAC channels. No capacitor on VREF.

Table 1. DC Specifications

| Parameter                                    | Min   | Тур   | Max      | Unit                                  | Test Conditions/Comments                                                                                  |

|----------------------------------------------|-------|-------|----------|---------------------------------------|-----------------------------------------------------------------------------------------------------------|

| VDAC STATIC PERFORMANCE                      |       |       |          |                                       |                                                                                                           |

| Resolution                                   | 16    |       |          | Bits                                  |                                                                                                           |

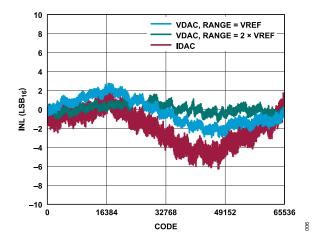

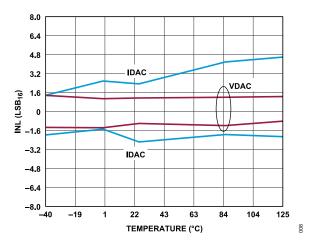

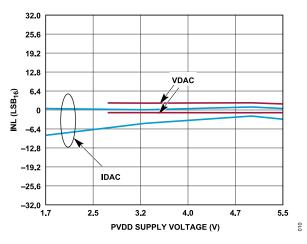

| Integral Nonlinearity (INL) <sup>1</sup>     | -10   |       | +10      | LSB <sub>16</sub>                     |                                                                                                           |

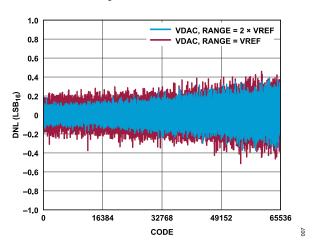

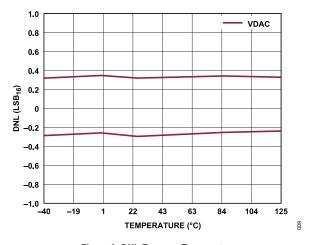

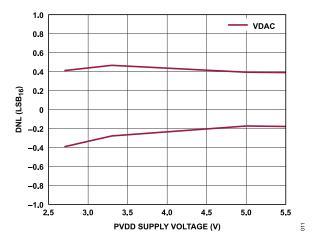

| Differential Nonlinearity (DNL) <sup>1</sup> | -1    |       | +1       | LSB <sub>16</sub>                     | Guaranteed monotonic                                                                                      |

| Zero-Code Error                              | -4.6  | 1.5   | +4.6     | mV                                    |                                                                                                           |

| Offset Error <sup>2</sup>                    | -5.2  | 1.4   | +5.2     | mV                                    |                                                                                                           |

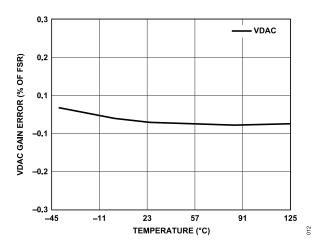

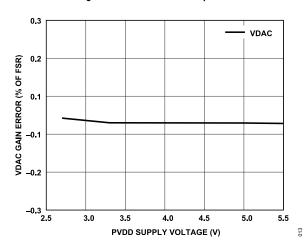

| Gain Error                                   | -0.3  | 0.02  | +0.3     | % of FSR                              | Range = 0 to VREF                                                                                         |

|                                              |       | 0.04  |          | % of FSR                              | Range = 0 to 2 × VREF                                                                                     |

| Total Unadjusted Error (TUE)                 | -0.34 | ±0.08 | +0.34    | % of FSR                              | Range = 0 to VREF                                                                                         |

|                                              | -0.16 | ±0.04 | 0.16     | % of FSR                              | Range = 0 to 2 × VREF                                                                                     |

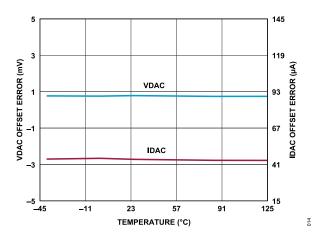

| Offset Error Drift                           |       | 1.5   |          | μV/°C                                 | Range = 0 to VREF                                                                                         |

|                                              |       | 2.5   |          | μV/°C                                 | Range = 0 to 2 × VREF                                                                                     |

| Gain Error Drift                             |       | 18    |          | ppm/°C                                | Range = 0 to VREF                                                                                         |

|                                              |       | 25    |          | ppm/°C                                | Range = 0 to 2 × VREF                                                                                     |

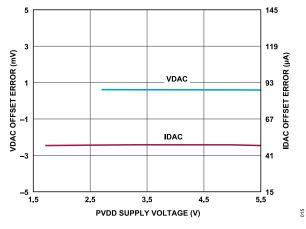

| DC Power Supply Rejection Ratio (PSRR)       |       |       |          |                                       |                                                                                                           |

| AVDD                                         |       | 33    |          | μV/V                                  | DAC code = midscale, AVDD = 5V ± 10%                                                                      |

| PVDD                                         |       | 16    |          | μV/V                                  | DAC code = midscale, PVDD = 5V ± 10%                                                                      |

| DC Crosstalk                                 |       |       |          |                                       |                                                                                                           |

| VDAC to VDAC                                 |       | 4.5   |          | μV                                    | Due to single channel, full-scale output change, internal reference, and range = 0 to VREF                |

|                                              |       | 35    |          | μV/mA                                 | Due to single channel, from -10mA to +10mA load current change, internal reference, and range = 0 to VREF |

|                                              |       | 14    |          | μV                                    | Due to powering down (per channel), internal reference, and range = 0 to VREF                             |

| IDAC to VDAC                                 |       | 168   |          | μV                                    | Due to single channel, full-scale output change, internal reference, and range = 0 to VREF                |

|                                              |       | 298   |          | μV                                    | Due to powering down (per channel), internal reference, and range = 0 to VREF                             |

| VDAC OUTPUT CHARACTERISTICS                  |       |       |          |                                       | •                                                                                                         |

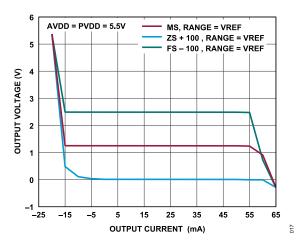

| Output Voltage Range                         | 0     |       | VREF     | V                                     | Range = 0 to VREF                                                                                         |

|                                              | 0     |       | 2 × VREF | V                                     | Range = 0 to 2 × VREF                                                                                     |

| Short Circuit Current                        |       | 50    |          | mA                                    | Sourcing                                                                                                  |

|                                              |       | 10    |          | mA                                    | Sinking                                                                                                   |

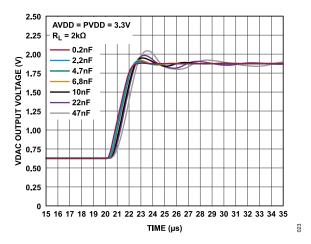

| Capacitive Load Stability                    |       | 2     |          | nF                                    | R <sub>L</sub> = ∞                                                                                        |

|                                              |       | 10    |          | nF                                    | $R_L \le 2k\Omega$                                                                                        |

|                                              |       |       |          |                                       | PVDD = 5V ± 10%, DAC code = midscale, −30mA ≤ I <sub>OUT</sub> ≤                                          |

| Load Regulation                              |       | 200   |          | μV/mA                                 | +30mA                                                                                                     |

|                                              |       | 222   |          | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | PVDD = 3V ± 10%, DAC code = midscale, −20mA ≤ I <sub>OUT</sub> ≤                                          |

|                                              | 70    | 200   |          | μV/mA                                 | +20mA                                                                                                     |

| Headroom                                     | 70    | 50    |          | mV                                    | Source current = 20mA                                                                                     |

| Footroom                                     | 250   | 120   |          | mV                                    | Sink current = 10mA                                                                                       |

| Output Impedance                             |       | 10    |          | Ω                                     | Output close to VDD or GND                                                                                |

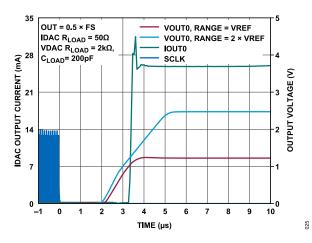

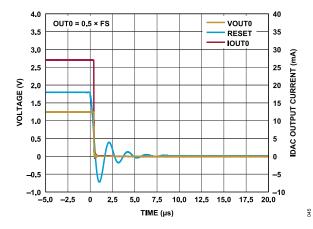

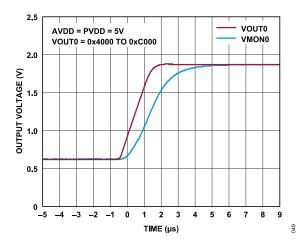

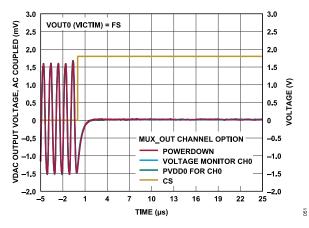

| Power-Up Time                                |       | 4.5   |          | μs                                    | Exiting power-down mode, AVDD = PVDD = 5V                                                                 |

analog.com Rev. 0 | 3 of 56

# **ELECTRICAL CHARACTERISTICS**

Table 1. DC Specifications (Continued)

| Parameter (Continued)          | Min    | Тур  | Max    | Unit              | Test Conditions/Comments                                      |

|--------------------------------|--------|------|--------|-------------------|---------------------------------------------------------------|

| IDAC STATIC PERFORMANCE        |        |      |        |                   |                                                               |

| Resolution                     | 16     |      |        | Bits              |                                                               |

| INL <sup>1</sup>               | 10     | ±8   |        | LSB <sub>16</sub> |                                                               |

| DNL <sup>1</sup>               | -1     | 10   | +1     | LSB <sub>16</sub> | Guaranteed monotonic                                          |

|                                | -      |      | ΤI     |                   | Guaranteed monotonic                                          |

| Offset Error <sup>2</sup>      |        | 82   |        | μA                |                                                               |

| Gain Error                     |        | 0.1  |        | % of FSR          |                                                               |

| Offset Error Drift             |        | 0.14 |        | μΑ/°C             |                                                               |

| Gain Error Drift               |        | 20   |        | ppm/°C            |                                                               |

| DC PSRR                        |        |      |        |                   |                                                               |

| AVDD                           |        | 1.2  |        | μA/V              | DAC code = midscale, AVDD = 5V ± 10%                          |

|                                |        | 1.5  |        | μA/V              | DAC code = midscale, AVDD = 3.3V ± 10%                        |

| PVDD                           |        | 23   |        | μA/V              | DAC code = midscale, PVDD = 5V ± 10%                          |

|                                |        | 12.5 |        | μA/V              | DAC code = midscale, PVDD = 1.8V ± 10%                        |

| DC Crosstalk                   |        |      |        | '                 | ,                                                             |

|                                |        |      |        |                   | Due to single channel, full-scale output change, and internal |

| IDAC to IDAC                   |        | 3    |        | μA                | reference                                                     |

|                                |        | 5    |        | μA                | Due to powering down (per channel), and internal reference    |

|                                |        | -    |        | Fin -             | Due to single channel, full-scale output change, and internal |

| VDAC to IDAC                   |        | 0.1  |        | μA                | reference                                                     |

|                                |        |      |        | '                 | Due to powering down (per channel), internal reference, and   |

|                                |        | 0.5  |        | μA                | VDAC range = 0 to VREF                                        |

| IDAC OUTPUT CHARACTERISTICS    |        |      |        |                   |                                                               |

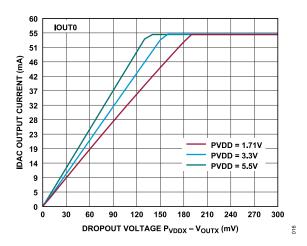

| Output Current Range           | 0      |      | >50    | mA                |                                                               |

| Dropout Voltage                |        |      | 250    | mV                | Output current = FS                                           |

| Power-Up Time                  |        | 4    | 200    | μs                | Exiting power-down mode, AVDD = PVDD = 5V                     |

| REFERENCE INPUT                |        |      |        | μο                | Exiting power-down mode, AVDD = 1 VDD = 5V                    |

|                                |        | 207  |        |                   | \\DEF = F F\\                                                 |

| Reference Input Current        |        | 387  |        | μA                | VREF = 5.5V                                                   |

|                                |        | 682  |        | μA                | VREF = 5.5V and VDAC range = 0 to 2 × VREF                    |

| Reference Input Voltage        |        | 2.5  |        | V                 |                                                               |

| Reference Input Impedance      |        | 14.3 |        | kΩ                |                                                               |

|                                |        | 8.1  |        | kΩ                | VDAC range = 0 to 2 × VREF                                    |

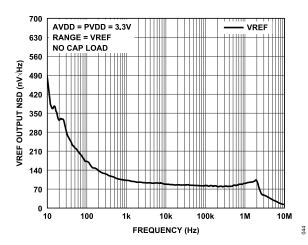

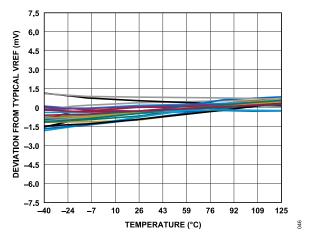

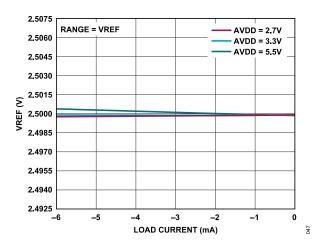

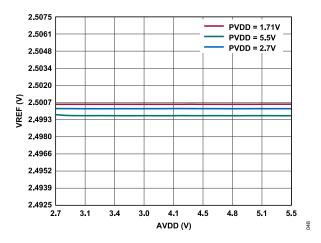

| REFERENCE OUTPUT               |        |      |        |                   |                                                               |

| VREF Output                    | 2.4925 | 2.5  | 2.5075 | V                 |                                                               |

| Voltage Reference Temperature  |        |      |        |                   |                                                               |

| Coefficient (TC)               |        | 3    |        | ppm/°C            |                                                               |

| Output Impedance               |        | 0.04 |        | Ω                 |                                                               |

| Load Regulation Sourcing       |        | 40   |        | μV/mA             | At ambient temperature                                        |

| Output Current Load Capability |        | +7   |        | mA                | Sourcing, AVDD ≥ 3V                                           |

|                                |        | 400  |        | μA                | Sinking                                                       |

| Line Regulation                |        | 13.4 |        | μV/V              | At ambient temperature                                        |

| Thermal Hysteresis             |        | 2.6  |        | ppm               | First cycle                                                   |

| ,                              |        | 2.7  |        | ppm               | Additional cycles                                             |

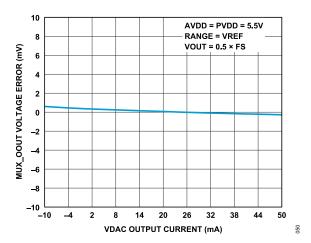

| INTEGRATED MULTIPLEXER         |        |      |        | 11                | ,                                                             |

| Output Voltage Range           | 0      |      | PVDD   | V                 |                                                               |

| Output Current                 | J      | ±9   | יסטע ו |                   |                                                               |

| -                              |        |      |        | mA<br>O           |                                                               |

| Output Impedance               |        | 0.54 |        | Ω                 |                                                               |

| Offset Error                   |        | 50   |        | mV                |                                                               |

| Maximum Capacitive Load        |        | 10   |        | nF                |                                                               |

analog.com Rev. 0 | 4 of 56

#### **ELECTRICAL CHARACTERISTICS**

Table 1. DC Specifications (Continued)

| Parameter                               | Min         | Тур  | Max         | Unit | Test Conditions/Comments                                      |

|-----------------------------------------|-------------|------|-------------|------|---------------------------------------------------------------|

| LOGIC INPUTS                            |             |      |             |      |                                                               |

| Input Current                           |             |      | 1           | μA   | Per pin, leakage current                                      |

| Input Low Voltage (V <sub>IL</sub> )    |             |      | 0.3 × IOVDD | V    |                                                               |

| Input High Voltage (V <sub>IH</sub> )   | 0.7 × IOVDD |      |             | V    |                                                               |

| Pin Capacitance                         |             | 1.3  |             | pF   |                                                               |

| LOGIC OUTPUTS SERIAL DATA OUT (SDO)     |             |      |             |      |                                                               |

| Output Low Voltage (V <sub>OL</sub> )   |             |      | 0.4         | V    | I <sub>SINK</sub> = 1μA                                       |

| Output High Voltage (V <sub>OH</sub> )  | IOVDD - 0.4 |      |             | V    | I <sub>SOURCE</sub> = 1µA                                     |

| Floating State Output Capacitance       |             | 1.2  |             | pF   |                                                               |

| POWER REQUIREMENTS                      |             |      |             |      |                                                               |

| IOVDD                                   | 1.08        |      | 1.98        | V    |                                                               |

| I <sub>LOGIC</sub>                      |             | 16   |             | μA   | Static Inputs, V <sub>IH</sub> = IOVDD, V <sub>IL</sub> = GND |

| AVDD                                    | 2.7         |      | 5.5         | V    |                                                               |

| PVDDx                                   | 1.71        |      | AVDD        | V    |                                                               |

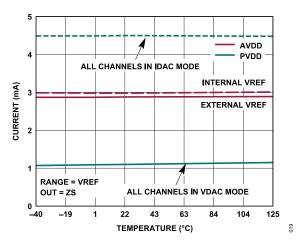

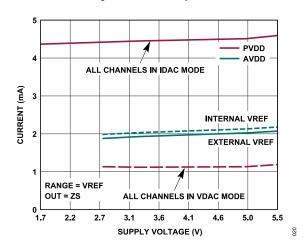

| I <sub>AVDD</sub>                       |             |      |             |      |                                                               |

| Normal Mode                             |             | 1.75 |             | mA   | External reference = 2.5V                                     |

|                                         |             | 2.64 | 2.76        | mA   | Internal reference                                            |

| Power-Down                              |             | 1.05 | 1.8         | mA   | Internal reference                                            |

|                                         |             | 690  |             | μA   | External reference = 2.5V                                     |

| I <sub>PVDD0</sub> , I <sub>PVDD1</sub> |             | 2.3  |             | mA   | IDAC output at zero scale                                     |

|                                         |             | 0.8  |             | μA   | IDAC output = high-Z                                          |

|                                         |             | 0.55 |             | mA   | VDAC output at zero scale                                     |

|                                         |             | 0.35 |             | μA   | VDAC output = 15kΩ to GND                                     |

<sup>&</sup>lt;sup>1</sup> Linearity is defined from code 256 to code 65535 for VDAC and IDAC channels.

# **AC SPECIFICATIONS**

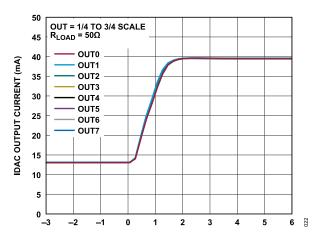

AVDD = 2.7V to 5.5 V, PVDDx = 2.7V to AVDD for VDAC channels, PVDDx = 1.71V to AVDD for IDAC channels, 1.08V  $\leq$  IOVDD  $\leq$  1.98V, VREF = 2.5V (internal or external), and all specifications are at  $T_J$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C. Typical at  $T_A$  = 25 $^{\circ}$ C, unless otherwise noted.  $R_L$  =  $2k\Omega$  to GND,  $C_L$  = 200pF to GND for VDAC channels.  $R_L$  = 50 $\Omega$  to GND for IDAC channels. No capacitor on VREF.

Table 2. AC Specifications

| Parameter                                          | Min | Тур  | Max | Unit   | Test Conditions/Comments                                                              |

|----------------------------------------------------|-----|------|-----|--------|---------------------------------------------------------------------------------------|

| VDAC SPECIFICATIONS                                |     |      |     |        |                                                                                       |

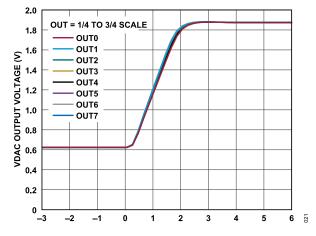

| Output Voltage Settling Time                       |     | 7    |     | μs     | 1/4 to 3/4 scale and vice versa with settling to ±2 LSB <sub>16</sub>                 |

| Slew Rate                                          |     | 0.7  |     | V/µs   | 10% FSR to 90% FSR and vice versa                                                     |

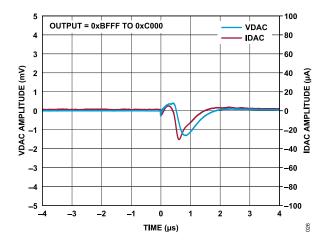

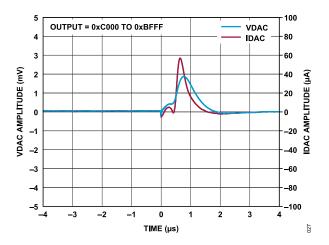

| Digital-to-Analog Glitch Impulse                   |     | 1    |     | nV-sec | 1 LSB <sub>16</sub> change around major carry (internal reference, range = 0 to VREF) |

| Digital-to-Analog Glitch Peak                      |     | 1.5  |     | mV     |                                                                                       |

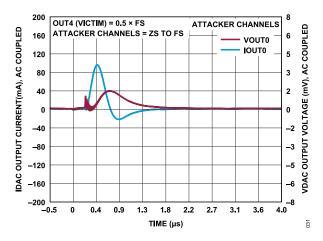

| Digital Feedthrough (Voltage Peak)                 |     |      |     |        | Internal reference and range = 0 to VREF                                              |

|                                                    |     | 0.04 |     | mV     | OUT1, OUT2, OUT3, OUT5, OUT6, and OUT7 as victim channels                             |

|                                                    |     | 0.7  |     | mV     | OUT0 and OUT4 as victim channels                                                      |

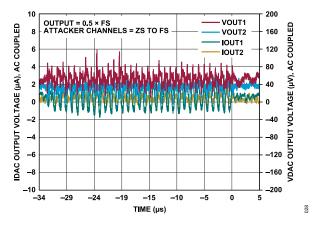

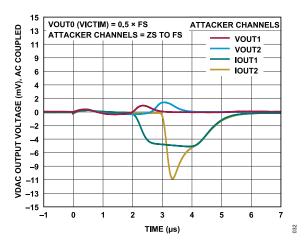

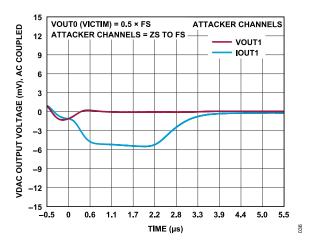

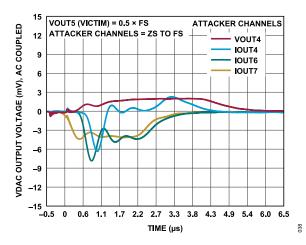

| VDAC-to-VDAC Crosstalk (Voltage Peak) <sup>1</sup> |     |      |     |        | Internal reference and range = 0 to VREF                                              |

| Digital                                            |     | 0.05 |     | mV     | OUT1, OUT2, OUT3, OUT5, OUT6, and OUT7 as victim channels                             |

|                                                    |     | 0.7  |     | mV     | OUT0 and OUT4 as victim channels                                                      |

| Analog                                             |     | 1.1  |     | mV     | Adjacent channels <sup>2</sup>                                                        |

|                                                    |     | 0.2  |     | mV     | Non adjacent channels <sup>2</sup>                                                    |

analog.com Rev. 0 | 5 of 56

<sup>&</sup>lt;sup>2</sup> Offset error is measured at code 6503 for VDAC channels and code 255 for IDAC channels.

# **ELECTRICAL CHARACTERISTICS**

Table 2. AC Specifications (Continued)

| Parameter                                          | Min Typ Ma | ax Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

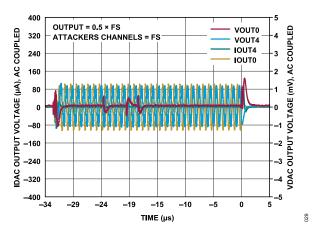

| DAC-to-DAC                                         | 1.1        | mV      | OUT1 and OUT5 as victim channels, with OUT0 and OUT4 as attackers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                    |            |         | respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                    | 0.3        | mV      | OUT0, OUT2, OUT3, OUT4, OUT6, and OUT7 as victim channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

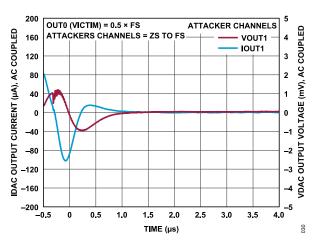

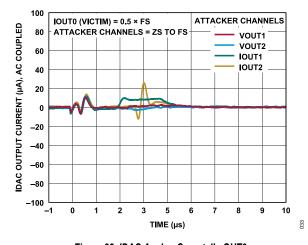

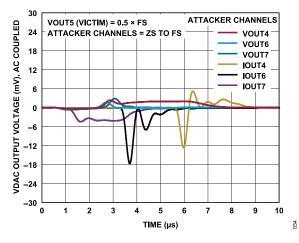

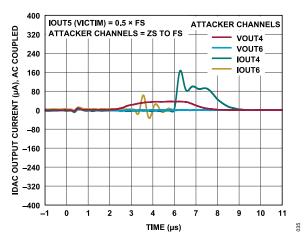

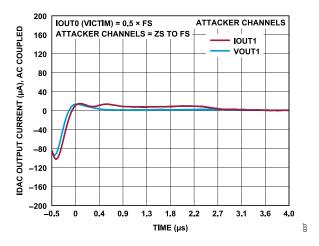

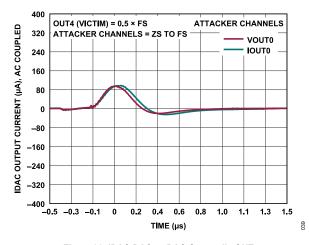

| IDAC-to-VDAC Crosstalk (Voltage Peak) <sup>3</sup> |            |         | Internal reference and range = 0 to VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Analog                                             | 5          | mV      | Adjacent channels <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                    | 0.2        | mV      | Non adjacent channels <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DAC-to-DAC                                         | 3          | mV      | Adjacent channels <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                    | 0.2        | mV      | Non adjacent channels <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Mux-to-VDAC Crosstalk <sup>4</sup>                 | 0.09       | mV      | OUT1, OUT2, OUT3, OUT4, OUT5, and OUT7 as victim channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                    | 1.3        | mV      | OUT0 and OUT4 as victim channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

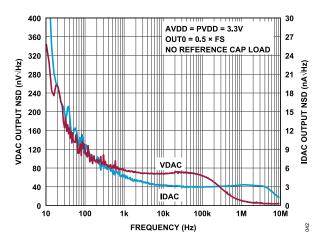

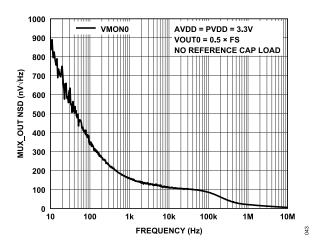

| Output Noise Spectral Density                      |            |         | DAC code = midscale, 10kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                    | 68         | nV/√Hz  | Range = 0 to VREF and external reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                    | 84         | nV/√Hz  | Range = 0 to 2 × VREF and external reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                    | 107        | nV/√Hz  | Range = 0 to VREF and internal reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                    | 131        | nV/√Hz  | Range = 0 to 2 × VREF and ixternal reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

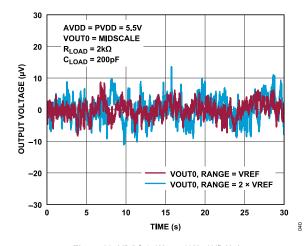

| Output Noise                                       | 15         | μV p-p  | 0.1Hz to 10Hz, range = 0 to VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| •                                                  | 25         | μV p-p  | 0.1Hz to 10Hz, range = 0 to 2 × VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

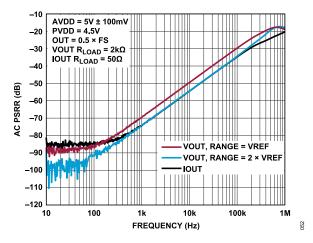

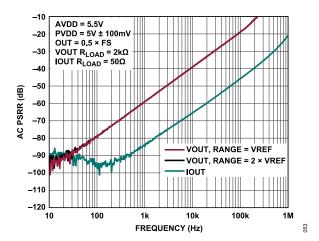

| PVDDx AC PSRR                                      | -93        | dB      | 10Hz, range = 0 to VREF or range = 0 to 2 × VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                    | -79        | dB      | 100Hz, range = 0 to VREF or range = 0 to 2 × VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                    | -59        | dB      | 1kHz, range = 0 to VREF or range = 0 to 2 × VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

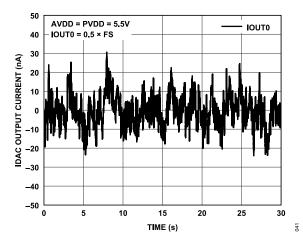

| DAC SPECIFICATIONS                                 |            | 12      | in a go o to the original of the contract of t |

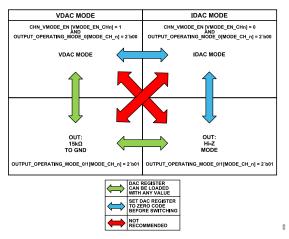

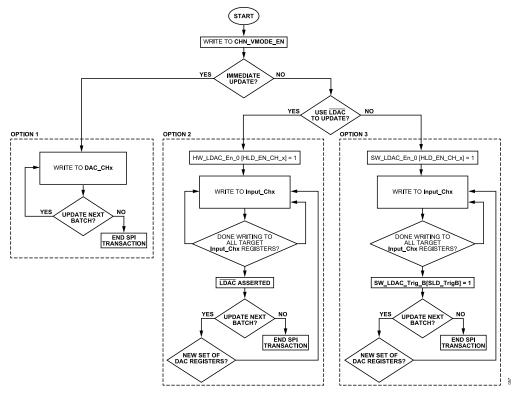

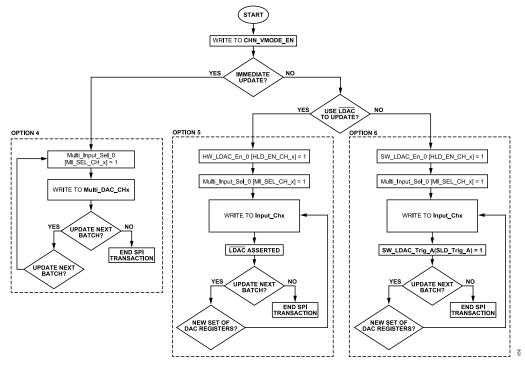

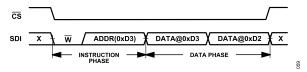

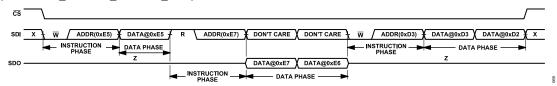

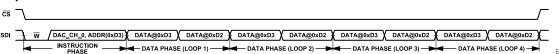

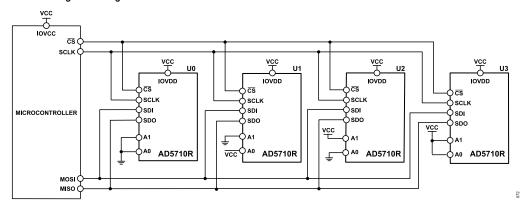

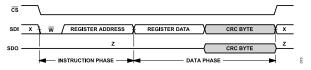

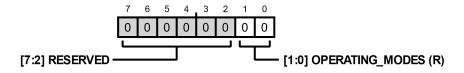

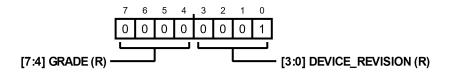

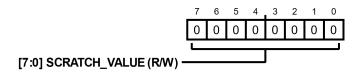

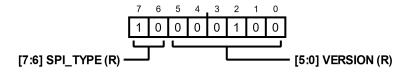

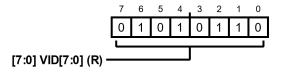

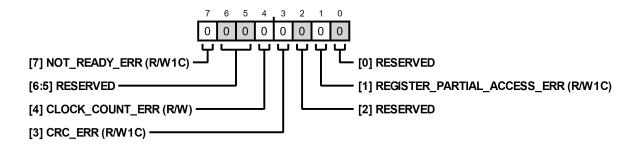

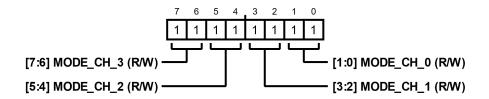

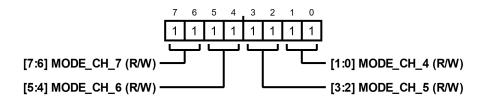

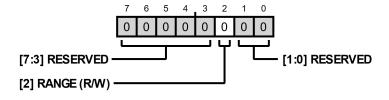

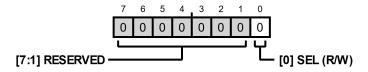

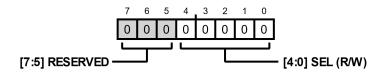

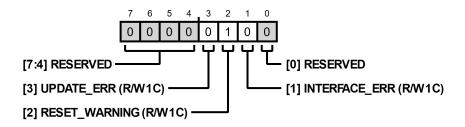

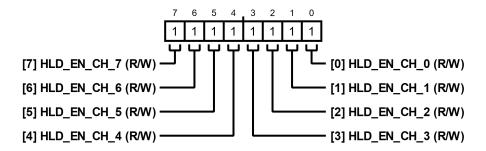

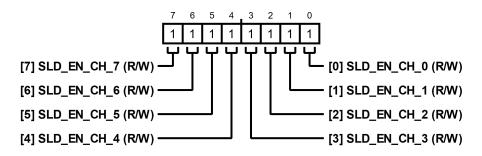

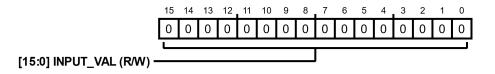

|                                                    | 17.5       |         | 1/ to 3/ goods with pottling to 12 LCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |