## 4-Channel, 16-Bit, Current Output DAC with On-Chip Reference and SPI

### FEATURES

- ▶ 4-channel, 16-bit, current output DAC

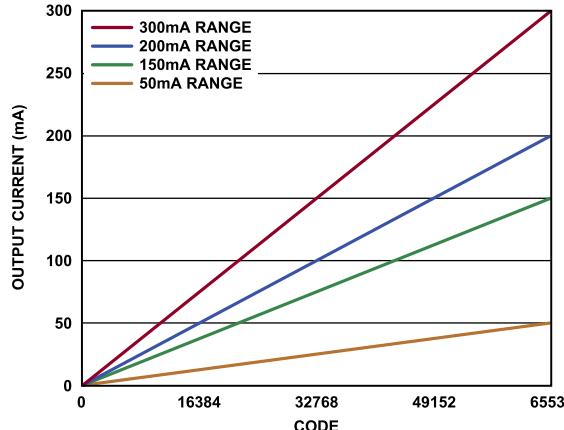

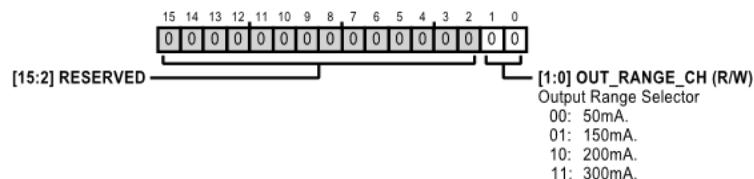

- ▶ Programmable output current ranges per channel

- ▶ 50mA, 150mA, 200mA, and 300mA

- ▶ Flexible 1.65V to 3.6V output supply voltages

- ▶ Separate voltage supply per output channel

- ▶ 0.3V maximum dropout voltage per channel

- ▶ Internal switches to ground on IOUT pins

- ▶ 2.5V on-chip voltage reference

- ▶ 50MHz SPI interface

- ▶ Load DAC, A/B toggle, and dither functions

- ▶ Integrated analog diagnostic monitoring

- ▶ Integrated thermal warning alert

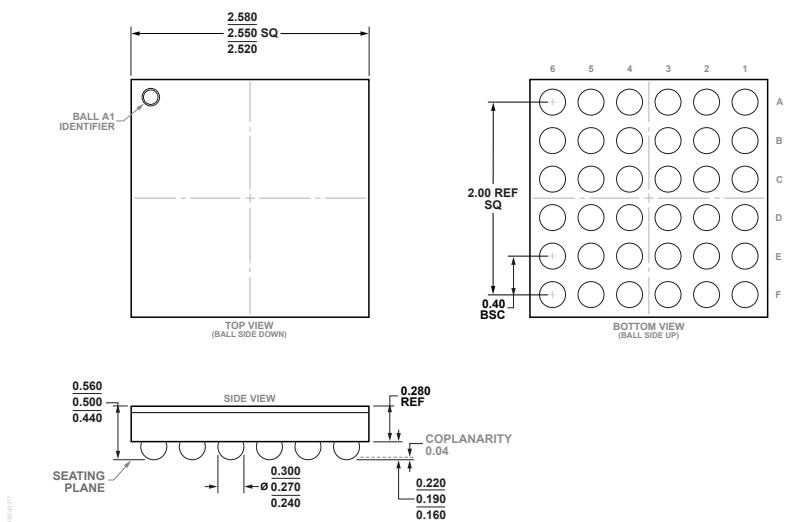

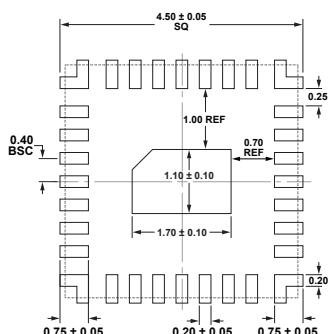

- ▶ **36-ball 2.55mm × 2.55mm WLCSP**

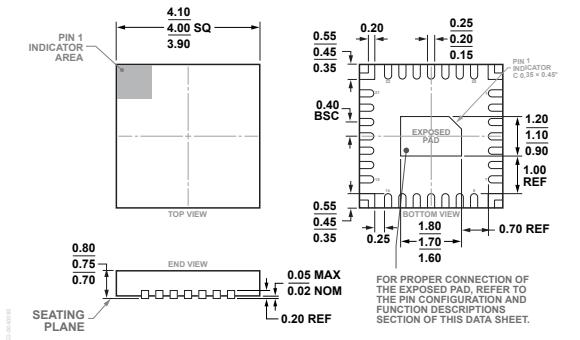

- ▶ **28-pin 4mm × 4mm LFCSP**

- ▶ Operating temperature:  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

### APPLICATIONS

- ▶ Photonics control

- ▶ Optical communications

- ▶ LED driver programmable current source

- ▶ Current-mode biasing

### GENERAL DESCRIPTION

The AD5706R is a 4-channel, 16-bit resolution, low noise programmable current output, digital-to-analog converter (DAC). The device is ideal for applications such as photonics control and current-mode biasing.

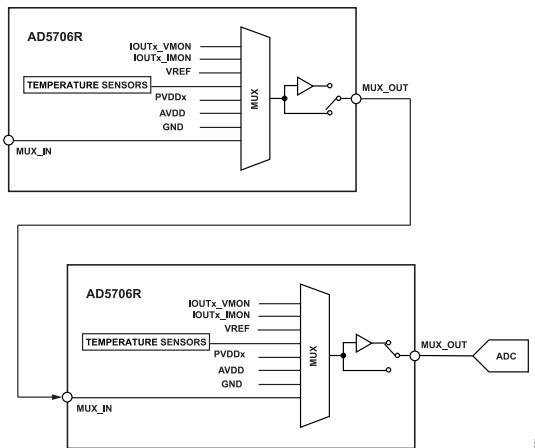

The device features an integrated 2.5V voltage reference, along with load DAC, A/B toggle, and dither functions. An onboard multiplexer allows for monitoring of supply and output voltages, output currents, and the internal die temperature.

The AD5706R supports several programmable output current ranges, with a maximum of 300mA. With addressable pins, up to four devices can share a single SPI bus for communication.

Each DAC channel operates independently with its own positive power supply rail (PVDDx) that can range from 1.65V to 3.6V, optimizing both power efficiency and thermal performance. The device requires a 2.9V to 3.6V AVDD supply and is rated for operation across a wide temperature range from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

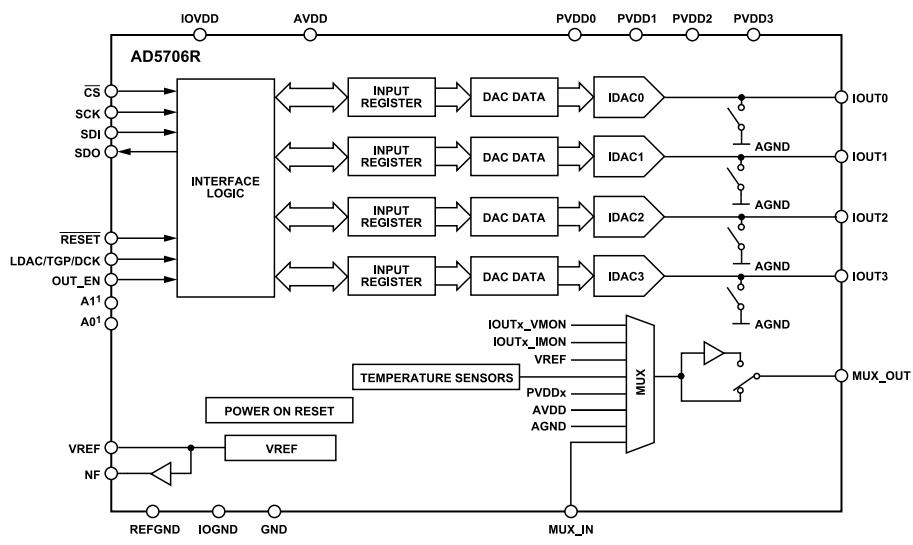

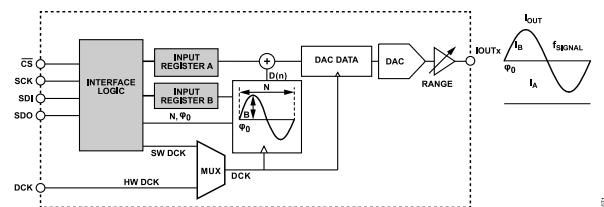

### FUNCTIONAL BLOCK DIAGRAM

<sup>1</sup>AVAILABLE IN WLCSP PACKAGE ONLY.

101

Figure 1. Functional Block Diagram

**TABLE OF CONTENTS**

|                                                  |    |                                                    |    |

|--------------------------------------------------|----|----------------------------------------------------|----|

| Features.....                                    | 1  | Device Addressing.....                             | 32 |

| Applications.....                                | 1  | Error Detection.....                               | 33 |

| General Description.....                         | 1  | Cyclic Redundancy Check (CRC) Error Detection..... | 34 |

| Functional Block Diagram .....                   | 1  | Overtemperature Warning Alert.....                 | 36 |

| Specifications.....                              | 3  | Device Reset.....                                  | 36 |

| DC Specifications.....                           | 3  | Scratchpad and User Spare Registers.....           | 36 |

| AC Specifications.....                           | 5  | Device Identification.....                         | 36 |

| Timing Specifications.....                       | 6  | DAC Operations.....                                | 37 |

| Absolute Maximum Ratings.....                    | 11 | DAC Registers (Data and Input).....                | 37 |

| Thermal Performance.....                         | 11 | IOUT Output Stages.....                            | 37 |

| Thermal Resistance.....                          | 11 | DAC Update Modes.....                              | 38 |

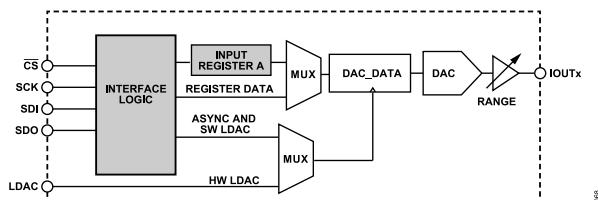

| ESD Caution.....                                 | 11 | Load DAC Function.....                             | 39 |

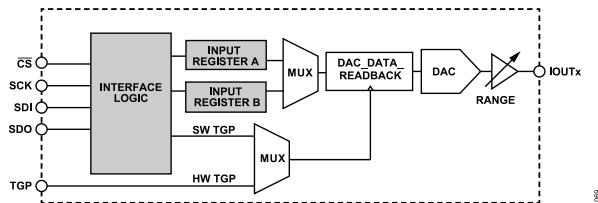

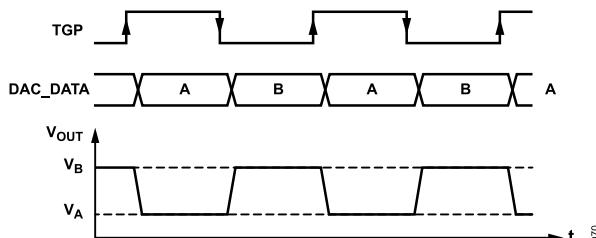

| Pin Configuration and Function Descriptions..... | 12 | Toggle DAC Function.....                           | 40 |

| Typical Performance Characteristics.....         | 14 | Dither Function.....                               | 41 |

| DC Performance.....                              | 14 | Multi-DAC Function.....                            | 46 |

| AC Performance.....                              | 16 | Summary of DAC Modes.....                          | 47 |

| Miscellaneous.....                               | 19 | Applications Information.....                      | 48 |

| Terminology.....                                 | 21 | Recommended External Components.....               | 48 |

| Theory of Operation.....                         | 24 | Power Supply Initialization.....                   | 48 |

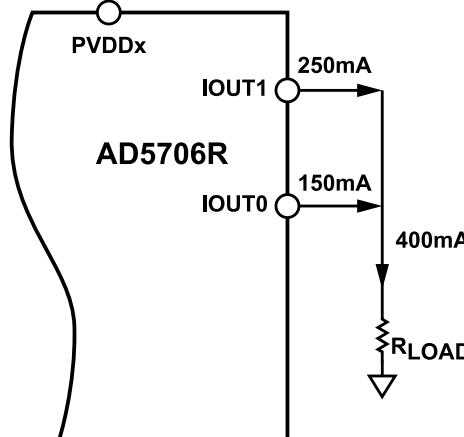

| Device Information.....                          | 24 | Combining Channels to Increase Current Range ..... | 48 |

| Precision Reference.....                         | 24 | Combining Channels to Reduce Output Noise.....     | 48 |

| Analog Multiplexer and Diagnostic                |    | Microprocessor Interfacing.....                    | 48 |

| Monitoring.....                                  | 24 | Layout and Assembly Guidelines.....                | 49 |

| Multiplexer Input and Daisy Chaining.....        | 26 | Thermal Considerations.....                        | 49 |

| Power Supplies.....                              | 26 | Registers.....                                     | 51 |

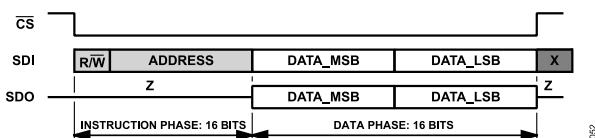

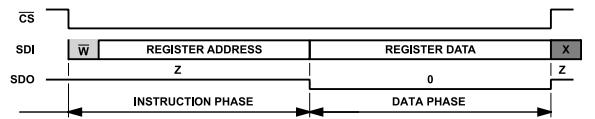

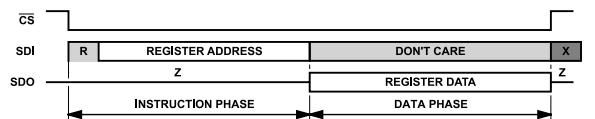

| Digital Interface.....                           | 27 | Register Summary.....                              | 51 |

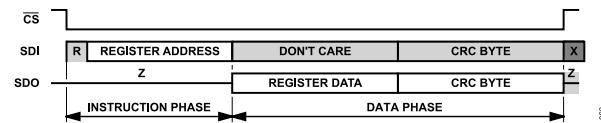

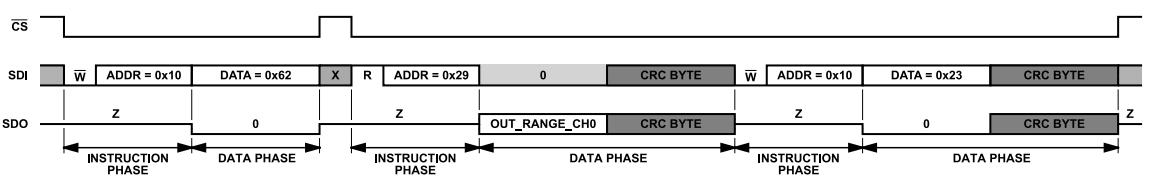

| Instruction Phase.....                           | 27 | Register Bitwise Summary.....                      | 52 |

| Data Phase.....                                  | 27 | Register Details.....                              | 55 |

| SPI Frame Synchronization.....                   | 27 | Outline Dimensions.....                            | 74 |

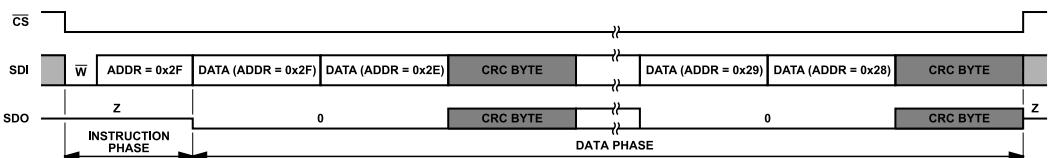

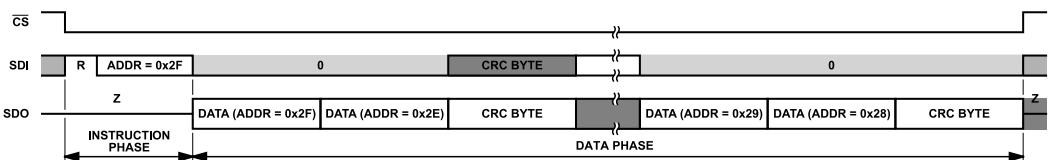

| Multibyte Registers.....                         | 28 | Ordering Guide.....                                | 75 |

| Register Map Address Direction.....              | 29 |                                                    |    |

| Streaming Mode.....                              | 29 |                                                    |    |

| Single Instruction Mode.....                     | 31 |                                                    |    |

**REVISION HISTORY****1/2026—Revision 0: Initial Version**

**SPECIFICATIONS**

AVDD = 2.9V to 3.6V, PVDDx = 1.65V to AVDD, IOVDD = 1.14V to 1.89V, VREF = 2.5V (internal or external), operating temperature range =  $-40^{\circ}\text{C}$  ( $T_A$ ) to  $+125^{\circ}\text{C}$  ( $T_J$ ), and external passive components  $C_{\text{REF}} = 1\mu\text{F}$ ,  $C_{\text{NF}} = 0.1\mu\text{F}$ , unless otherwise noted. Typical values specified at  $T_A = 25^{\circ}\text{C}$  with nominal supply conditions AVDD = 3.3V, PVDDx = 3.3V, and IOVDD = 1.8V.

**DC SPECIFICATIONS****Table 1. DC Specifications**

| Parameter <sup>1</sup>                                  | Min   | Typ        | Max         | Unit                           | Test Conditions/Comments                                                                                          |

|---------------------------------------------------------|-------|------------|-------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|

| OPERATING TEMPERATURE RANGE                             | -40   |            | 125         | °C                             | Minimum operating ambient temperature ( $T_{A\_MIN}$ )<br>Maximum operating junction temperature ( $T_{J\_MAX}$ ) |

| DAC STATIC PERFORMANCE                                  |       |            |             |                                |                                                                                                                   |

| Resolution                                              | 16    |            |             | Bits                           | All output current ranges                                                                                         |

| Integral Nonlinearity (INL) <sup>2</sup>                | -32   |            | +32         | LSB <sub>16</sub> <sup>3</sup> |                                                                                                                   |

| Differential Nonlinearity (DNL) <sup>2</sup>            | -1    | $\pm 0.25$ | +1          | LSB <sub>16</sub>              | Per channel, guaranteed monotonic                                                                                 |

| Total Unadjusted Error (TUE)                            | -1    |            | +1          | %FSR                           |                                                                                                                   |

| Offset Error <sup>2</sup>                               | -0.4  |            | +0.4        | %FSR                           |                                                                                                                   |

| Offset Error Drift                                      |       | 5          |             | ppm/°C                         |                                                                                                                   |

| Gain Error <sup>2</sup>                                 | -0.9  |            | +0.9        | %FSR                           |                                                                                                                   |

| Gain Error Drift                                        |       | 10         |             | ppm/°C                         |                                                                                                                   |

| DC Crosstalk <sup>4</sup>                               |       | 110        |             | μA                             | Result of a 638mW change in dissipated power, with internal reference                                             |

| DC Power Supply Rejection Ratio (PSRR)                  |       |            |             |                                | 50mA range, DAC code = 3/4 full scale                                                                             |

| AVDD                                                    |       | 5          |             | μA/V                           | AVDD = 3.3V $\pm 10\%$                                                                                            |

| PVDDx                                                   |       | 3          |             | μA/V                           | PVDD = 3.3V $\pm 10\%$                                                                                            |

| DAC OUTPUT CHARACTERISTICS                              |       |            |             |                                |                                                                                                                   |

| Output Current ( $I_{\text{OUT}}$ ) Ranges <sup>5</sup> | 0     |            | +50         | mA                             |                                                                                                                   |

|                                                         | 0     |            | +150        | mA                             |                                                                                                                   |

|                                                         | 0     |            | +200        | mA                             |                                                                                                                   |

|                                                         | 0     |            | +300        | mA                             |                                                                                                                   |

| Output Compliance Voltage <sup>6</sup>                  | 0     |            | PVDDx - 0.3 | V                              |                                                                                                                   |

| Ground Switch Resistance                                |       | 10         |             | Ω                              | Sinking 100mA from $I_{\text{OUT}}$ to GND                                                                        |

| INTERNAL REFERENCE OUTPUT                               |       |            |             |                                |                                                                                                                   |

| Voltage ( $V_{\text{REF}}$ )                            | 2.49  | 2.5        | 2.51        | V                              | Internal reference enabled, decoupling 1μF                                                                        |

| Temperature Coefficient                                 |       | 15         |             | ppm/°C                         | $T_A = 25^{\circ}\text{C}$<br>Across operating temperature range                                                  |

| Output Current Load Capability                          |       | +5         |             | mA                             | Across operating temperature range                                                                                |

| Line Regulation                                         |       | 2          |             | μV/V                           | Due to change in AVDD                                                                                             |

| Load Regulation, Sourcing                               |       | 2          |             | ppm/mA                         | $\Delta V_{\text{OUT}}/\Delta I_{\text{LOAD}}$                                                                    |

| EXTERNAL REFERENCE INPUT                                |       |            |             |                                |                                                                                                                   |

| Input Voltage                                           | 2.495 | 2.5        | 2.505       | V                              | Internal reference disabled (default)                                                                             |

| Input Impedance                                         |       | 16         |             | kΩ                             | $T_A = 25^{\circ}\text{C}$                                                                                        |

| TEMPERATURE SENSING DIODE                               |       |            |             |                                |                                                                                                                   |

| Accuracy                                                |       | 5          |             | °C                             |                                                                                                                   |

| Reading                                                 |       | 1.395      |             | V                              | MUX_OUT reading at $T_A = 25^{\circ}\text{C}$                                                                     |

| Temperature Coefficient                                 |       | -3.8       |             | mV/°C                          |                                                                                                                   |

| Range                                                   | -40   |            | 125         | °C                             | $T_A$<br>$T_J$                                                                                                    |

## SPECIFICATIONS

Table 1. DC Specifications (Continued)

| Parameter <sup>1</sup>                 | Min         | Typ  | Max         | Unit | Test Conditions/Comments                                                                        |

|----------------------------------------|-------------|------|-------------|------|-------------------------------------------------------------------------------------------------|

| THERMAL ALARMS                         |             |      |             |      |                                                                                                 |

| Overheat Warning Temperature           |             | 125  |             | °C   | T <sub>J</sub>                                                                                  |

| Overheat Warning Hysteresis            |             | 5    |             | °C   | T <sub>J</sub>                                                                                  |

| MUX OUTPUT (MUX_OUT)                   |             |      |             |      |                                                                                                 |

| DC Output Impedance                    |             | 1    |             | Ω    | Buffered, output drive = ±1mA                                                                   |

|                                        |             | 7    |             | kΩ   | Nonbuffered, output drive = ±1μA                                                                |

| Leakage Current                        |             | 1    |             | nA   | Nonbuffered, T <sub>A</sub> = 125°C                                                             |

| Output Voltage Offset                  | -10         |      | +10         | mV   | Buffered                                                                                        |

| Output Drive Current                   |             | ±5   |             | mA   | Buffered                                                                                        |

| MUX INPUT (MUX_IN)                     |             |      |             |      |                                                                                                 |

| Input Voltage Range                    | 0           |      | VREF        | V    |                                                                                                 |

| Input Leakage Current                  |             | 10   |             | nA   |                                                                                                 |

| Input Impedance                        |             | 2    |             | kΩ   | Nonbuffered MUX signal path                                                                     |

| LOGIC INPUTS <sup>7</sup>              |             |      |             |      |                                                                                                 |

| Input Current                          | -1          |      | +1          | μA   | Per pin                                                                                         |

| Input Low Voltage (V <sub>IL</sub> )   | 0           |      | 0.3 × IOVDD | V    |                                                                                                 |

| Input High Voltage (V <sub>IH</sub> )  | 0.7 × IOVDD |      | IOVDD       | V    |                                                                                                 |

| Pin Capacitance                        |             | 5    |             | pF   | Per pin                                                                                         |

| LOGIC OUTPUTS                          |             |      |             |      |                                                                                                 |

| Output Low Voltage (V <sub>OL</sub> )  |             |      | 0.4         | V    | I <sub>SINK</sub> = 100μA                                                                       |

| Output High Voltage (V <sub>OH</sub> ) | IOVDD - 0.4 |      |             | V    | I <sub>SOURCE</sub> = 100μA                                                                     |

| Floating State Output Capacitance      |             | 5    |             | pF   |                                                                                                 |

| POWER SUPPLIES                         |             |      |             |      |                                                                                                 |

| AVDD                                   | 2.9         | 3.3  | 3.6         | V    |                                                                                                 |

| PVDDx <sup>8</sup>                     | 1.65        | 3.3  | AVDD        | V    |                                                                                                 |

| IOVDD                                  | 1.14        | 1.8  | 1.89        | V    |                                                                                                 |

| POWER PERFORMANCE                      |             |      |             |      |                                                                                                 |

| AVDD Supply Current                    |             | 29.7 | 37          | mA   | Internal reference, all IOUTx outputs enabled, and at zero scale or in high-Z state             |

|                                        |             | 29.4 |             | mA   | External reference, all IOUTx outputs enabled, and at zero scale or in high-Z state             |

| PVDDx Supply Current                   |             | 0.27 | 1.7         | mA   | Per PVDD pin, all IOUTx outputs enabled, and at zero scale or in high-Z state                   |

| IOVDD Supply Current                   |             | 0.05 | 30          | μA   | Digital Inputs = 0V or IOVDD                                                                    |

| Quiescent Power Dissipation            |             | 100  |             | mW   | AVDD = 3.3V, internal reference, all IOUTx output enabled, and at zero scale or in high-Z state |

<sup>1</sup> See the Terminology section.<sup>2</sup> Linearity is defined from Code 384 to Code 65535. Offset Error is computed at Code 384.<sup>3</sup> LSB size varies with current output range.<sup>4</sup> Crosstalk is measured with a step change from 0mA to 300mA on all aggressor channels, with PVDD = 3.3V and R<sub>LOAD</sub> = 3.9Ω. Total power dissipation change is 638mW. The monitored channel is held at midscale on 300mA range, with AVDD = 3.5V, PVDD = 3.3V, and R<sub>LOAD</sub> = 8.33Ω.<sup>5</sup> See Table 15.<sup>6</sup> When sourcing current, the output compliance voltage is the maximum voltage at the IOUTx pin, for which the output current is within 0.1% of the measured full-scale range.<sup>7</sup> See the Timing Specifications section for more details.<sup>8</sup> PVDD must either be tied to AVDD or sourced to a lower level than AVDD.

## SPECIFICATIONS

## AC SPECIFICATIONS

Table 2. AC Specifications

| Parameter <sup>1</sup>               | Min  | Typ | Max | Unit                         | Test Conditions/Comments                                                                                            |

|--------------------------------------|------|-----|-----|------------------------------|---------------------------------------------------------------------------------------------------------------------|

| DAC DYNAMIC PERFORMANCE              |      |     |     |                              |                                                                                                                     |

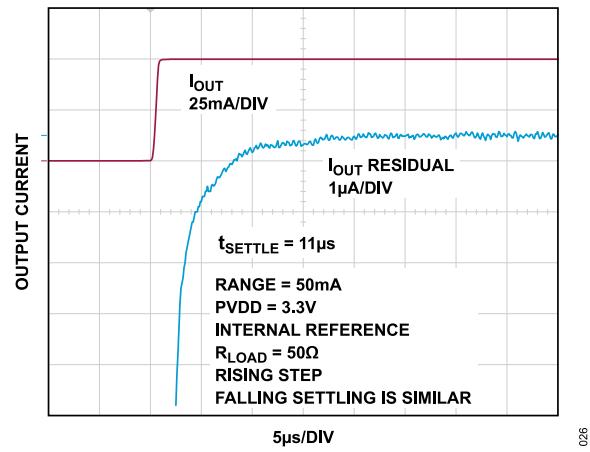

| Output Current Settling Time         |      |     |     |                              | DAC code changed from zero scale to full scale and vice-versa, with settling to $\pm 4\text{LSB}_{16}$ <sup>2</sup> |

|                                      | 9    |     |     | $\mu\text{s}$                | 0mA to +200mA range                                                                                                 |

|                                      | 11   |     |     | $\mu\text{s}$                | 0mA to +50mA range                                                                                                  |

| Slew Rate                            |      |     |     |                              | $I_{\text{OUT}} = 10\%$ to 90% of FSR and vice-versa                                                                |

|                                      | 285  |     |     | $\text{mA}/\mu\text{s}$      | 0mA to +200mA range                                                                                                 |

|                                      | 67   |     |     | $\text{mA}/\mu\text{s}$      | 0mA to +50mA range                                                                                                  |

| Digital-to-Analog Glitch Energy      | 6    |     |     | $\text{pA}\cdot\text{sec}$   |                                                                                                                     |

| Digital Feedthrough (Current Area)   | 0.03 |     |     | $\text{nA}\cdot\text{sec}$   |                                                                                                                     |

| Digital Crosstalk                    | 0.03 |     |     | $\text{nA}\cdot\text{sec}$   |                                                                                                                     |

| DAC to DAC Crosstalk (Current Area)  |      |     |     |                              | For 200mA range on adjacent DAC channel                                                                             |

|                                      | 40   |     |     | $\text{pA}\cdot\text{sec}$   | DAC code change from 1/4 scale to 3/4 scale in a step change and vice-versa                                         |

|                                      | 70   |     |     | $\text{pA}\cdot\text{sec}$   | DAC code changed from zero scale to full scale in a step change and vice-versa                                      |

| MUX to DAC Crosstalk (Current Area)  |      |     |     |                              | DAC code = midscale                                                                                                 |

|                                      | 0.03 |     |     | $\text{nA}\cdot\text{sec}$   | 0mA to +300mA range                                                                                                 |

| AC PSRR                              |      |     |     |                              |                                                                                                                     |

| PVDDx                                | -72  |     |     | $\text{dB}$                  | $f = 100\text{kHz}$ , 0mA to +300mA range                                                                           |

|                                      | -80  |     |     | $\text{dB}$                  | $f = 100\text{kHz}$ , 0mA to +50mA range                                                                            |

| AVDD                                 | -82  |     |     | $\text{dB}$                  | $f = 10\text{kHz}$                                                                                                  |

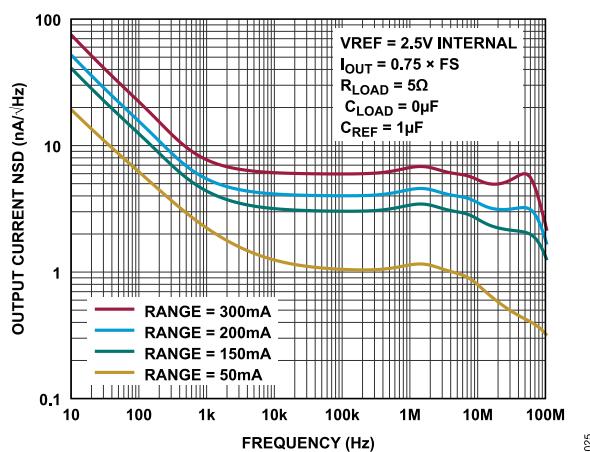

| Output Noise Spectral Density (NSD)  |      |     |     |                              | DAC code = 3/4 full scale, no external filter                                                                       |

|                                      | 7.7  |     |     | $\text{nA}/\sqrt{\text{Hz}}$ | 1 kHz, 0mA to +300mA range                                                                                          |

|                                      | 6    |     |     | $\text{nA}/\sqrt{\text{Hz}}$ | 10 kHz, 0mA to +300mA range                                                                                         |

|                                      | 5.3  |     |     | $\text{nA}/\sqrt{\text{Hz}}$ | 1 kHz, 0mA to +200mA range                                                                                          |

|                                      | 4.1  |     |     | $\text{nA}/\sqrt{\text{Hz}}$ | 10 kHz, 0mA to +200mA range                                                                                         |

|                                      | 4.2  |     |     | $\text{nA}/\sqrt{\text{Hz}}$ | 1 kHz, 0mA to +150mA range                                                                                          |

|                                      | 3.2  |     |     | $\text{nA}/\sqrt{\text{Hz}}$ | 10 kHz, 0mA to +150mA range                                                                                         |

|                                      | 2.2  |     |     | $\text{nA}/\sqrt{\text{Hz}}$ | 1 kHz, 0mA to +50mA range                                                                                           |

|                                      | 1.2  |     |     | $\text{nA}/\sqrt{\text{Hz}}$ | 10 kHz, 0mA to +50mA range                                                                                          |

| Output Noise (0.1Hz to 10Hz)         |      |     |     |                              | DAC code = 3/4 full scale, no external filter                                                                       |

|                                      | 620  |     |     | $\text{nA rms}$              | 0mA to +300mA range                                                                                                 |

|                                      | 425  |     |     | $\text{nA rms}$              | 0mA to +200mA range                                                                                                 |

|                                      | 332  |     |     | $\text{nA rms}$              | 0mA to +150mA range                                                                                                 |

|                                      | 148  |     |     | $\text{nA rms}$              | 0mA to +50mA range                                                                                                  |

| REFERENCE OUTPUT                     |      |     |     |                              |                                                                                                                     |

| Output Voltage Noise (0.1Hz to 10Hz) | 4    |     |     | $\mu\text{V rms}$            | Internal reference enabled, decoupling 1 $\mu\text{F}$                                                              |

| Output Voltage Noise Density         | 112  |     |     | $\text{nV}/\sqrt{\text{Hz}}$ | $f = 1\text{kHz}$                                                                                                   |

| Turn On Settling Time                | 500  |     |     | $\mu\text{s}$                | Decoupling 1 $\mu\text{F}$ , settling to $\pm 0.1\%$                                                                |

| MUX OUTPUT CHARACTERISTICS           |      |     |     |                              |                                                                                                                     |

| -3dB Input Bandwidth                 | 2.2  |     |     | $\text{MHz}$                 | Buffered, $C_{\text{LOAD}} = 3\text{pF}$                                                                            |

|                                      | 1.4  |     |     | $\text{MHz}$                 | Nonbuffered, standalone, $C_{\text{LOAD}} = 3\text{pF}$                                                             |

| Maximum Output Capacitive Load       | 100  |     |     | $\text{pF}$                  | Buffered                                                                                                            |

<sup>1</sup> See the Terminology section.<sup>2</sup> LSB size varies with current output range.

## SPECIFICATIONS

### TIMING SPECIFICATIONS

AVDD = 2.9V to 3.6V, PVDDx = 1.65V to AVDD, IOVDD = 1.14V to 1.89V, and operating temperature range =  $-40^{\circ}\text{C}$  ( $T_A$ ) to  $+125^{\circ}\text{C}$  ( $T_J$ ), unless otherwise noted. All timing values are specified for a standalone device.

All digital input signals are specified with rise time ( $t_R$ ) = fall time ( $t_F$ ) = 1ns/V (10% to 90% of IOVDD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

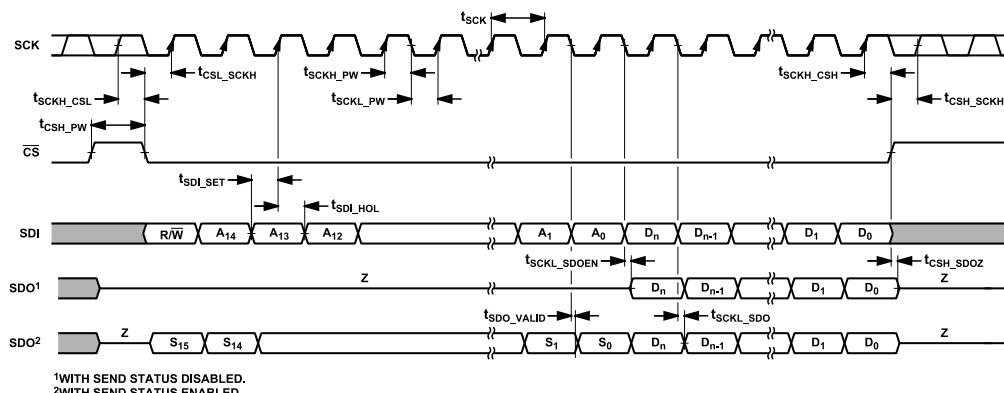

### Serial Interface Timing

See [Figure 2](#) to [Figure 5](#) for related timing diagrams.

**Table 3. Digital Interface Timing Specifications**

| Parameter                       | Description                                                                                                                                | Min | Typ  | Max | Unit |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| $t_{SCK}$                       | SCK cycle time, write operation. <sup>1</sup>                                                                                              | 20  |      |     | ns   |

|                                 | SCK cycle time, write and read operations. <sup>2</sup>                                                                                    | 40  |      |     | ns   |

| $f_{SCK}$                       | SCK frequency, write operation. <sup>1</sup>                                                                                               |     | 50   |     | MHz  |

|                                 | SCK frequency, write and read operations. <sup>2</sup>                                                                                     |     | 25   |     | MHz  |

| $t_{SCKH\_PW}$                  | SCK high time.                                                                                                                             | 8   |      |     | ns   |

| $t_{SCKL\_PW}$                  | SCK low time.                                                                                                                              | 8   |      |     | ns   |

| $t_{CSL\_SCKH}$                 | $\overline{CS}$ falling edge to SCK rising edge setup time                                                                                 | 6   |      |     | ns   |

| $t_{CSH\_SCKH}$                 | $\overline{CS}$ rising edge to SCK rising edge setup time.                                                                                 | 10  |      |     | ns   |

| $t_{SCKH\_CSH}$                 | Rising edge of SCK <sup>3</sup> to rising edge of $\overline{CS}$ .                                                                        | 10  |      |     | ns   |

| $t_{SCKH\_CSL}$                 | Rising edge of SCK to falling edge of $\overline{CS}$ .                                                                                    | 10  |      |     | ns   |

| $t_{SDI\_SET}$                  | SDI data setup time.                                                                                                                       | 5   |      |     | ns   |

| $t_{SDI\_HOL}$                  | SDI data hold time.                                                                                                                        | 5   |      |     | ns   |

| $t_{CSH\_PW}$                   | $\overline{CS}$ pulse width high.                                                                                                          | 10  |      |     | ns   |

| $t_{SCKL\_SDO}$                 | SCK falling edge to SDO data available delay.                                                                                              |     | 15   |     | ns   |

| $t_{SDO\_VALID}$                | SCK falling Edge to SDO data remains valid.                                                                                                |     | 12   |     | ns   |

| $t_{CSH\_SDOZ}$                 | $\overline{CS}$ rising edge to SDO disabled.                                                                                               |     | 14   |     | ns   |

| $t_{SCKL\_SDOEN}$               | SCK falling edge to SDO enabled.                                                                                                           |     | 14   |     | ns   |

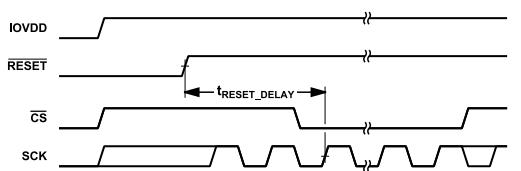

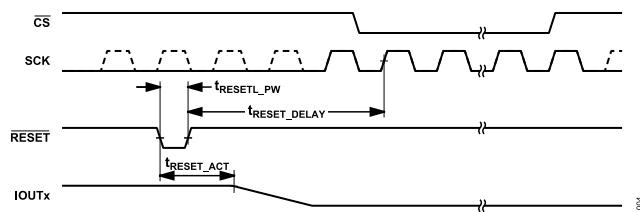

| $t_{RESETL\_PW}$                | RESET pulse width low.                                                                                                                     | 20  |      |     | ns   |

| $t_{RESET\_ACT}$ <sup>4</sup>   | RESET assertion (low level triggered) to channel output getting reset, or rising edge of SCK <sup>3</sup> to channel output getting reset. |     | <100 |     | ns   |

| $t_{RESET\_DELAY}$ <sup>5</sup> | RESET pulse delay upon power-on reset.                                                                                                     |     |      | 200 | μs   |

<sup>1</sup> With send status and CRC disabled.

<sup>2</sup> With send status and CRC enabled.

<sup>3</sup> The 8th or 16th SCK, whichever shifts in the final bit of register data in the data phase.

<sup>4</sup> Channel output settling behaviour not taken into consideration.

<sup>5</sup> Guaranteed by design; not production tested.

## SPECIFICATIONS

Figure 2. Register Read/Write Timing Diagram (C<sub>POL</sub> = 0 and C<sub>PHA</sub> = 0)

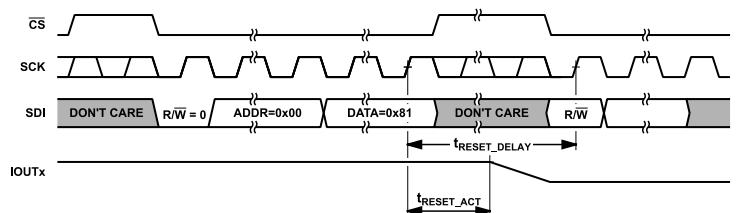

Figure 3. Power On Reset (POR) Timing Diagram

Figure 4. Hardware Reset Timing Diagram

Figure 5. Software Reset Timing Diagram

## SPECIFICATIONS

## DAC Output Update Timing

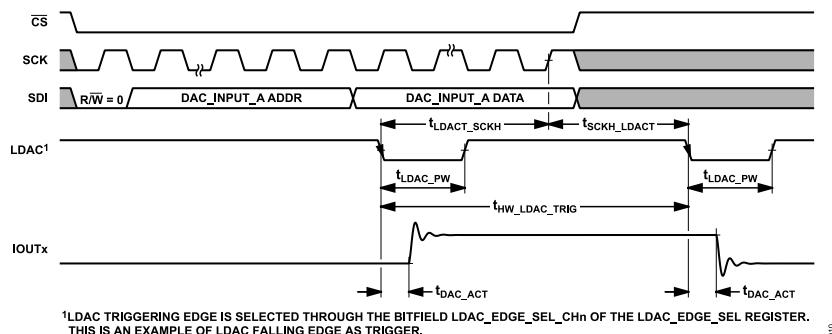

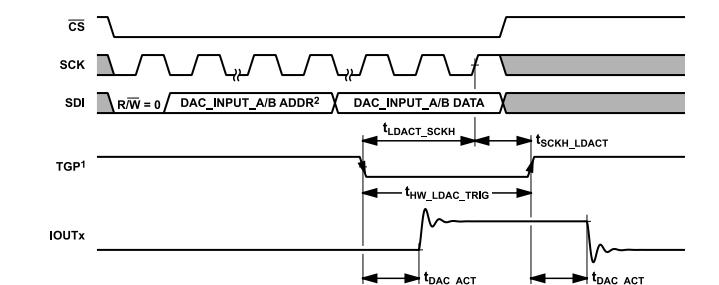

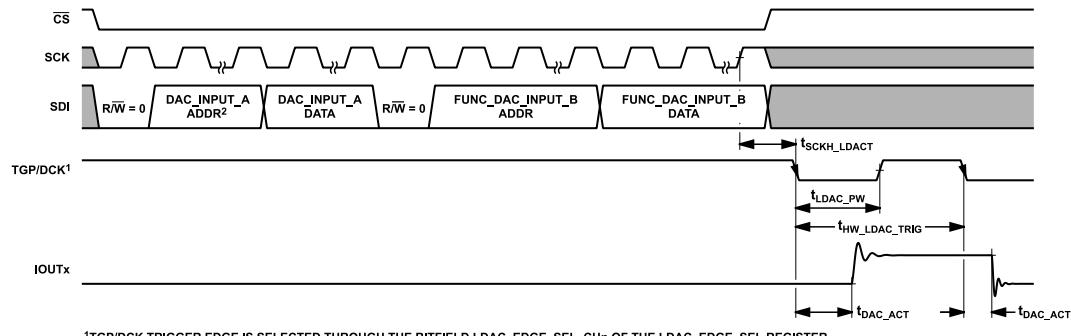

See [Figure 6](#) to [Figure 15](#) for related timing diagrams.

**Table 4. DAC Output Update Timing Specifications**

| Parameter <sup>1</sup> | Description                                                                                                                                                                        | Min               | Typ | Max | Unit |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|------|

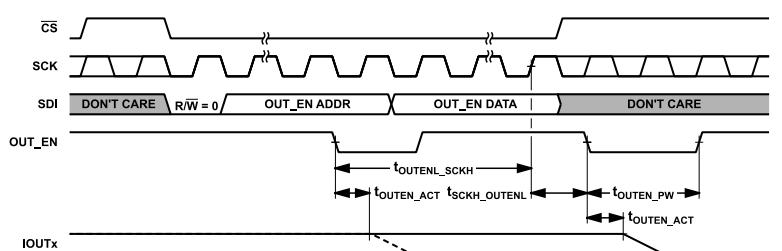

| $t_{OUTEN\_ACT}^2$     | Delay from OUT_EN low level trigger to DAC channel in high-Z state (measured on 200mA range)                                                                                       |                   | 350 |     | ns   |

| $t_{OUTENL\_SCKH}^3$   | Delay from the OUT_EN low level trigger to the rising edge of SCK <sup>4</sup> for transition of IOUTx from high-Z state to normal operation                                       | 0                 |     |     | ns   |

| $t_{SCKH\_OUTENL}^3$   | Delay from the rising edge of SCK <sup>4</sup> to OUT_EN low for transition of IOUTx to high-Z state                                                                               | 5                 |     |     | ns   |

| $t_{OUTEN\_PW}^3$      | OUT_EN pulse width low                                                                                                                                                             | 6                 |     |     | μs   |

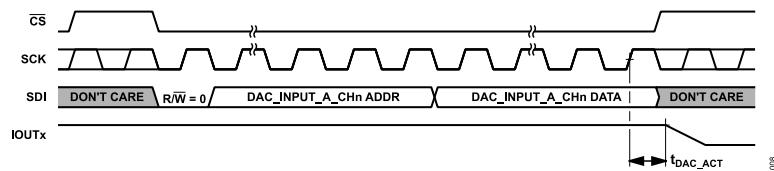

| $t_{DAC\_ACT}^2$       | Direct DAC update activation time (measured on 200mA range)                                                                                                                        |                   | 230 |     | ns   |

| $t_{LDAC\_PW}$         | LDAC/TGP/DCK pulse width (low or high)                                                                                                                                             | 20                |     |     | ns   |

| $t_{LDACT\_SCKH}$      | Delay from the active edge of LDAC/TGP/DCK to the rising edge of SCK <sup>4</sup> in a SPI write transaction during hardware trigger modes                                         | 5                 |     |     | ns   |

| $t_{SCKH\_LDACT}$      | Delay from the rising edge of SCK <sup>4</sup> to the following active edge of LDAC/TGP/DCK in a SPI write transaction during hardware trigger modes                               | 5                 |     |     | ns   |

| $t_{HW\_LDAC\_TRIG}$   | Time between the two consecutive active trigger edges of LDAC/TGP/DCK during hardware trigger modes                                                                                | 80                |     |     | ns   |

| $t_{SW\_LDAC\_TRIG}$   | Delay from one rising edge of SCK <sup>4</sup> to another rising edge of SCK <sup>4</sup> (in the consecutive data phase) in a SPI write transaction during software trigger modes | 16 ×<br>$t_{SCK}$ |     |     |      |

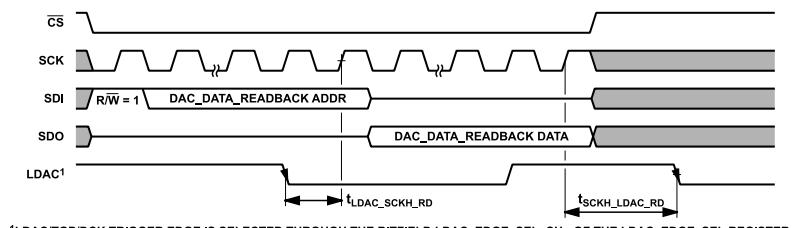

| $t_{LDACT\_SCKH\_RD}$  | Delay from active edge of LDAC/TGP/DCK to the rising edge of SCK <sup>4</sup> in a SPI read transaction during hardware trigger modes                                              | 5                 |     |     | ns   |

| $t_{SCKH\_LDACT\_RD}$  | Delay from the rising edge of SCK <sup>4</sup> to the next active edge of LDAC/TGP/DCK in a SPI read transaction during hardware trigger modes                                     | 5                 |     |     | ns   |

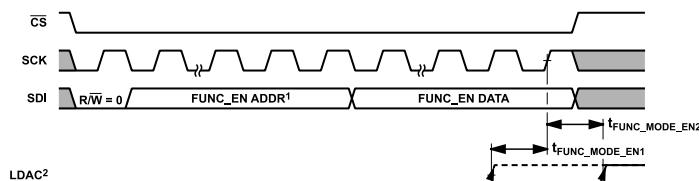

| $t_{FUNC\_MODE\_EN1}$  | Delay from the active trigger edge of LDAC/TGP/DCK to the rising edge of SCK <sup>4</sup> for change in DAC function modes                                                         | 5                 |     |     | ns   |

| $t_{FUNC\_MODE\_EN2}$  | Delay from the rising edge of SCK <sup>4</sup> to the active trigger edge of LDAC/TGP/DCK for change in DAC function modes                                                         | 5                 |     |     | ns   |

<sup>1</sup> See the [DAC Operations](#) section for a list of DAC update modes.

<sup>2</sup> The timing does not include the analog IOUT settling time.

<sup>3</sup> Guaranteed by design; not production tested.

<sup>4</sup> The 8th or 16th SCK, whichever shifts in the final bit of register data in the data phase.

**Figure 6. IOUTx Enable/Disable Timing Diagram Using OUT\_EN Pin**

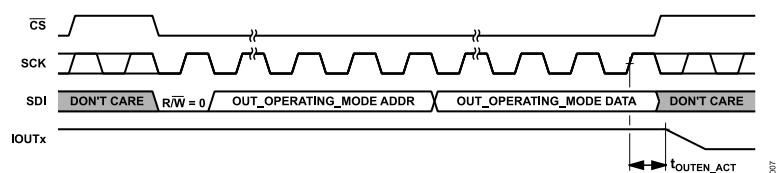

**Figure 7. IOUTx Enable/Disable Timing Diagram Using SPI Write**

## SPECIFICATIONS

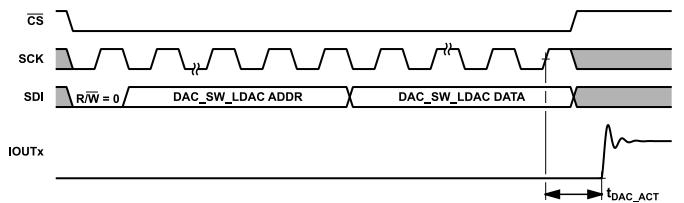

Figure 8. Asynchronous DAC Update Timing Diagram

Figure 9. Software LDAC Timing Diagram

Figure 10. Hardware LDAC Timing Diagram

Figure 11. Software DAC Update Timing Diagram in Streaming Mode

Figure 12. Hardware Toggle Timing Diagram

## SPECIFICATIONS

Figure 13. Hardware Toggle and Dither Timing Diagram in Single Instruction Mode

Figure 14. DAC Mode Function Enable Timing Diagram

Figure 15. DAC Data Read Back Timing Diagram

## ABSOLUTE MAXIMUM RATINGS

$T_A = 25^\circ\text{C}$ , unless otherwise noted

Table 5. Absolute Maximum Ratings

| Parameter                            | Rating                                    |

|--------------------------------------|-------------------------------------------|

| AVDD to AGND                         | −0.3 V to +3.96 V                         |

| PVDD <sup>1</sup> to GND             | −0.3 V to minimum (AVDD + 0.3 V, +3.96 V) |

| IOUT <sub>x</sub> to GND             | −0.3 V to minimum (AVDD + 0.3 V, +4.26 V) |

| VREF <sup>2</sup> , NF to REFGND     | −0.3 V to minimum (AVDD + 0.3 V, +4.26 V) |

| MUX_IN, MUX_OUT to GND               | −0.3 V to minimum (AVDD + 0.3 V, +4.26 V) |

| IOVDD to IOGND <sup>3</sup>          | −0.3 V to +2.1 V                          |

| Digital Inputs <sup>4</sup> to IOGND | −0.3 V to minimum (IOVDD + 0.3 V, +2.4 V) |

| Digital Outputs to IOGND             | −0.3 V to minimum (IOVDD + 0.3 V, +2.4 V) |

| Temperature                          |                                           |

| Operating Range                      | −40°C ( $T_A$ ) to +125°C ( $T_J$ )       |

| Storage Range                        | −60°C to +150°C                           |

| Junction                             | 150°C                                     |

| Lead, Soldering Reflow               | 260°C, as per JEDEC J-STD-020             |

<sup>1</sup> PVDD<sub>x</sub> refers to the PVDD0, PVDD1, PVDD2, and PVDD3 pins. IOUT<sub>x</sub> refers to the IOUT0, IOUT1, IOUT2, and IOUT3 pins.

<sup>2</sup> when in External Reference mode

<sup>3</sup> In LFCSP package, IOGND is same as GND.

<sup>4</sup> See the [Pin Configuration and Function Descriptions](#) section for a list of the digital input and digital output pins.

Stresses at or above those listed under absolute maximum ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in combination.

## THERMAL PERFORMANCE

The AD5706R can be damaged when the junction temperature ( $T_J$ ) limits are exceeded. See [Table 1](#) for the maximum operating junction temperature specification ( $T_{J\text{ MAX}}$ ). Monitoring ambient temperature does not guarantee that  $T_J$  is within the specified maximum temperature limits. In applications with high power dissipation and poor thermal resistance,  $T_J$  must be monitored using the internal temperature sensor.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required, in particular for applications where high maximum power dissipation exists.

Thermal resistance values specified in [Table 6](#) are calculated based on JEDEC specifications and must be used in compliance with JESD51-12. The worst-case junction temperature is reported.

Table 6. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}$ | $\theta_{JB}$ | $\Psi_{JB}$ | $\Psi_{JT}$ | $\Psi_{JC\text{-TOP}}$ | Unit |

|---------------------------|---------------|---------------|-------------|-------------|------------------------|------|

| WLCSP                     | 42.26         | 7.9           | 8.1         | 0.06        | 0.16                   | °C/W |

| LFCSP                     | 39.02         | 7.88          | 10.28       | 0.56        | 23.32                  | °C/W |

<sup>1</sup> The values in [Table 6](#) are calculated based on the standard JEDEC 2S2P thermal test board with 4 thermal vias. See JEDEC JESD51 series

$\theta_{JA}$  and  $\theta_{JB}$  are mainly used to compare thermal performance of the package of the device with other semiconductor packages when all test conditions listed are similar.  $\theta_{JA}$  and  $\theta_{JB}$  can be used for first-order approximation of the junction temperature in the system environment.

For WLCSP devices, using  $\Psi_{JB}$  or  $\Psi_{JT}$  is a more appropriate way to estimate the worst case junction temperature of the device in the system environment if an accurate thermal measurement of the board temperature near the device under test (DUT) or directly on the package top surface operating in the system environment is available.

Using the parameters listed in [Table 6](#) in accordance with JEDEC standards in the JESD51 series is recommended.

## ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

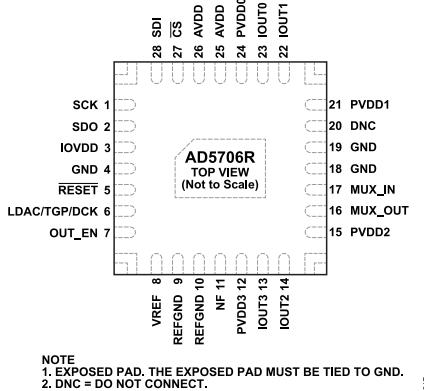

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

| AD5706R<br>TOP VIEW<br>(Not to Scale) |                    |                 |        |       |         |       |

|---------------------------------------|--------------------|-----------------|--------|-------|---------|-------|

|                                       | 1                  | 2               | 3      | 4     | 5       | 6     |

| A                                     | SDI                | $\overline{CS}$ | PVDD0  | IOUT0 | IOUT1   | PVDD1 |

| B                                     | SDO                | SCK             | PVDD0  | IOUT0 | IOUT1   | PVDD1 |

| C                                     | IOVDD              | A0              | IOGND  | GND   | MUX_IN  | DNC   |

| D                                     | $\overline{RESET}$ | A1              | REFGND | GND   | MUX_OUT | AVDD  |

| E                                     | LDAC/TGP/DCK       | OUT_EN          | PVDD3  | IOUT3 | IOUT2   | PVDD2 |

| F                                     | VREF               | NF              | PVDD3  | IOUT3 | IOUT2   | PVDD2 |

NOTE

1. DNC = DO NOT CONNECT.

016

Figure 16. WLCSP Pin Configuration

017

Figure 17. LFCSP Pin Configuration

Table 7. AD5706R Pin Function Descriptions

| Pin No. | WLCSP     | LFCSP | Mnemonic           | Type <sup>1</sup> | Description                                                                                                                                            |

|---------|-----------|-------|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| D5      | 16        |       | MUX_OUT            | AO                | Analog Output with Internal Buffer. An external analog-to-digital converter (ADC) reads voltages on this pin for diagnostic purposes.                  |

| C5      | 17        |       | MUX_IN             | AI                | Analog Input. An external input within 0 to VREF range can be fed from another AD5706R MUX_OUT or any other analog output for daisy chaining purposes. |

| A4, B4  | 23        |       | IOUT0              | AO                | Current Output of IDAC0 Channel.                                                                                                                       |

| A5, B5  | 22        |       | IOUT1              | AO                | Current Output of IDAC1 Channel.                                                                                                                       |

| E5, F5  | 14        |       | IOUT2              | AO                | Current Output of IDAC2 Channel.                                                                                                                       |

| E4, F4  | 13        |       | IOUT3              | AO                | Current Output of IDAC3 Channel.                                                                                                                       |

| A3, B3  | 24        |       | PVDD0              | S                 | Power Supply for IDAC0 Channel.                                                                                                                        |

| A6, B6  | 21        |       | PVDD1              | S                 | Power Supply for IDAC1 Channel.                                                                                                                        |

| E6, F6  | 15        |       | PVDD2              | S                 | Power Supply for IDAC2 Channel.                                                                                                                        |

| E3, F3  | 12        |       | PVDD3              | S                 | Power Supply for IDAC3 Channel.                                                                                                                        |

| D6      | 25, 26    |       | AVDD               | S                 | Analog Power Supply.                                                                                                                                   |

| C1      | 3         |       | IOVDD              | S                 | Logic Power Supply. IOVDD must be between 1.14V and 1.89V. This pin supplies power to the serial interface circuit blocks on the device.               |

| C4, D4  | 4, 18, 19 |       | GND                | S                 | Analog Supply Ground Pin.                                                                                                                              |

| C3      | -         |       | IOGND <sup>2</sup> | S                 | Digital Supply Ground Pin.                                                                                                                             |

| D3      | 9, 10     |       | REFGND             | S                 | Analog Ground for DAC Core(s) and Internal Reference. REFEND and GND must be tied together at 0V using a low impedance connection.                     |

| F1      | 8         |       | VREF               | AI/O              | 2.5V Voltage Reference Input/Output. Connect a 1 $\mu$ F capacitor between this pin and REFEND.                                                        |

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 7. AD5706R Pin Function Descriptions (Continued)

| Pin No. |       |                  |                   |                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLCSP   | LFCSP | Mnemonic         | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                       |

| F2      | 11    | NF               | AI/O              | Filter Capacitor for internal regulator. A 0.1 $\mu$ F capacitor connected from the NF pin to REFGND is recommended to achieve the specified performance from the AD5706R.                                                                                                                                                                                        |

| D1      | 5     | RESET            | DI                | Active Low Device Reset. Tie this pin high for normal operation. Asserting this pin low will reset the device to its default configuration.                                                                                                                                                                                                                       |

| A2      | 27    | CS               | DI                | Active Low Chip Select Input. This input is used to frame data during an SPI transaction.                                                                                                                                                                                                                                                                         |

| B2      | 1     | SCK              | DI                | Serial Clock Input. Data can be transferred at rates of up to 50MHz when writing to the device.                                                                                                                                                                                                                                                                   |

| A1      | 28    | SDI              | DI                | Serial Data Input. Data to be written to the device is provided on this input and is clocked into the register on the rising edge of SCK.                                                                                                                                                                                                                         |

| B1      | 2     | SDO              | DO                | Serial Data Output. A read back operation provides data on this output pin as a serial data stream. Data is clocked out on the falling edge of SCK and is valid on the rising edge of SCK.                                                                                                                                                                        |

| E1      | 6     | LDAC/<br>TGP/DCK | DI                | LDAC: Load DAC pin.<br>TGP: Toggle DAC pin.<br>DCK: Dither Clock Pin.<br>Pulsing this pin low or high based on trigger edge settings allows all selected DAC registers to be updated if the corresponding input registers have new data, allowing all selected DAC outputs to update synchronously. Alternatively, this pin can be tied to either IOVDD or IOGND. |

| E2      | 7     | OUT_EN           | DI                | Output Enable/Disable. OUT_EN pin is low level triggered for setting the current outputs to high-Z state or to GND. This pin can be tied high to IOVDD if not used.                                                                                                                                                                                               |

| D2      | -     | A1               | DI                | Logic Input: Programmable Address Bit 1. This pin must be tied to either IOVDD or IOGND.                                                                                                                                                                                                                                                                          |

| C2      | -     | A0               | DI                | Logic Input: Programmable Address Bit 0. This pin must be tied to either IOVDD or IOGND.                                                                                                                                                                                                                                                                          |

| C6      | 20    | DNC              | DNC               | Do Not Connect.                                                                                                                                                                                                                                                                                                                                                   |

<sup>1</sup> AO is analog output, S is supply, AI is analog input, AI/O is analog input or output, DI is digital input, DO is digital output, DI/O is digital input or output, and DNC is do not connect.

<sup>2</sup> IOGND and GND are tied internally in LFCSP package.

## TYPICAL PERFORMANCE CHARACTERISTICS

AVDD = 3.3V, PVDDx = 3.0V, IOVDD = 1.8V, internal reference, and temperature = 25 °C (T<sub>A</sub>), unless otherwise noted.

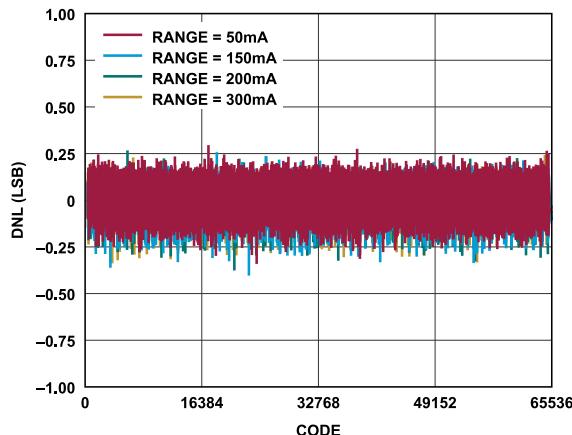

## DC PERFORMANCE

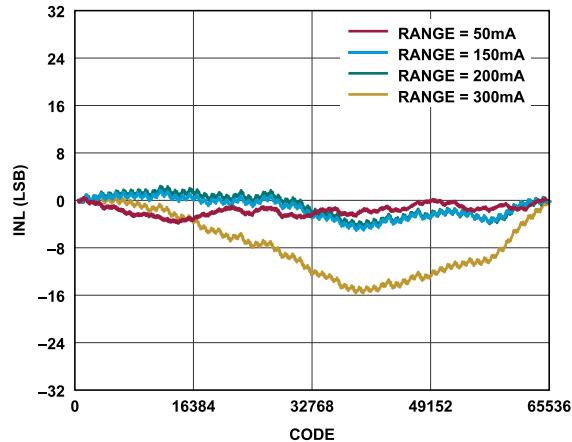

Figure 18. DAC DNL Error vs. DAC Code

Figure 19. DAC INL Error vs. DAC Code

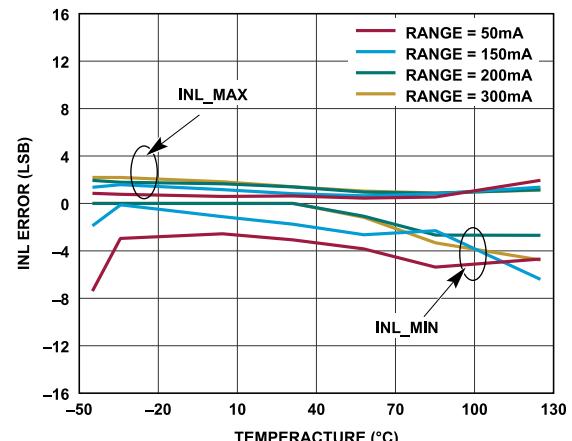

Figure 20. DAC INL Error vs. Temperature

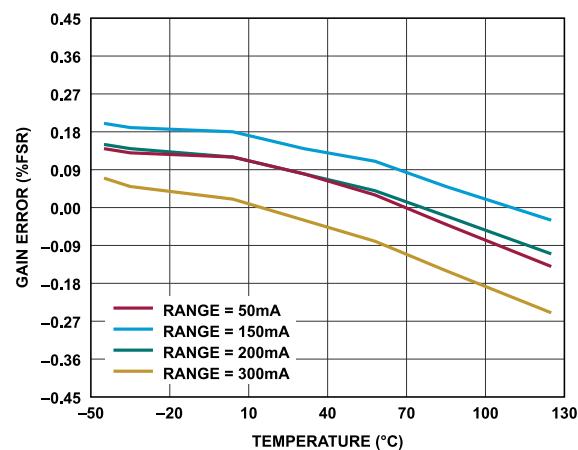

Figure 21. DAC Gain Error vs. Temperature

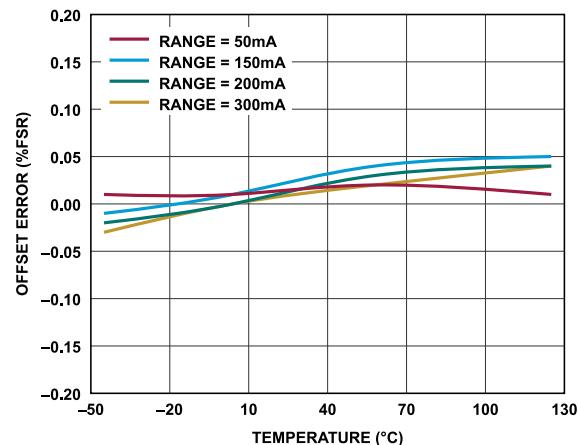

Figure 22. DAC Offset Error vs. Temperature

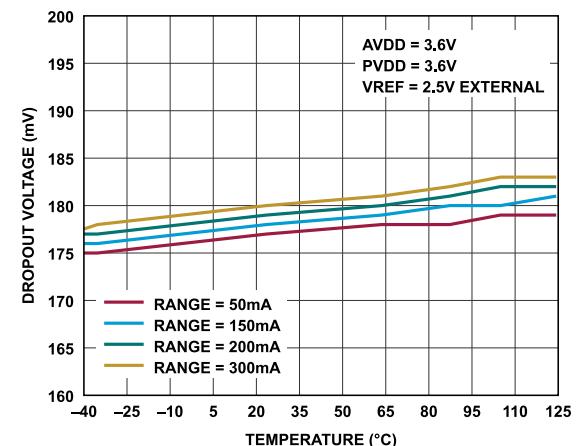

Figure 23. PVDD Dropout Voltage vs. Temperature at PVDD = 3.6V

## TYPICAL PERFORMANCE CHARACTERISTICS

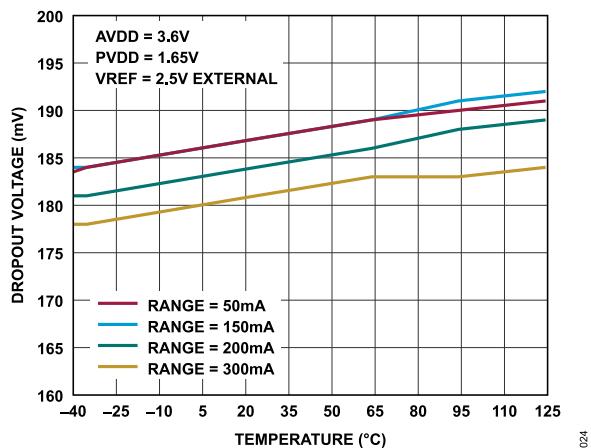

Figure 24. PVDD Dropout Voltage vs. Temperature at PVDD = 1.65V

## TYPICAL PERFORMANCE CHARACTERISTICS

## AC PERFORMANCE

Figure 25. DAC Output Noise Spectral Density vs. Frequency

Figure 26. DAC Output Settling Time, 50mA Range

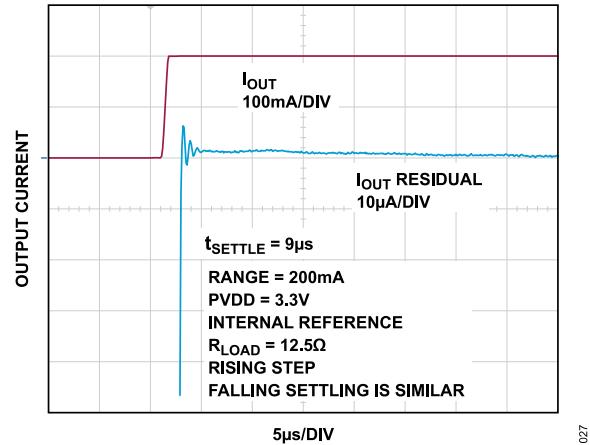

Figure 27. DAC Output Settling Time, 200mA Range

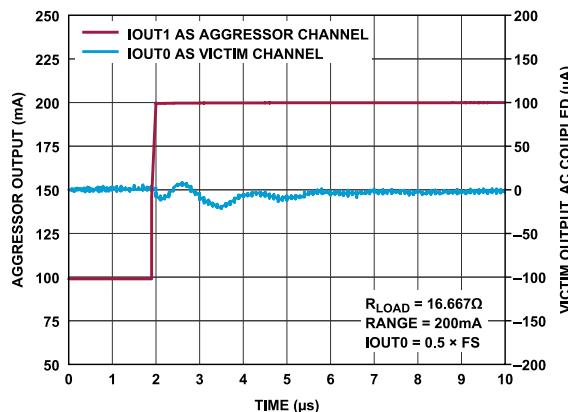

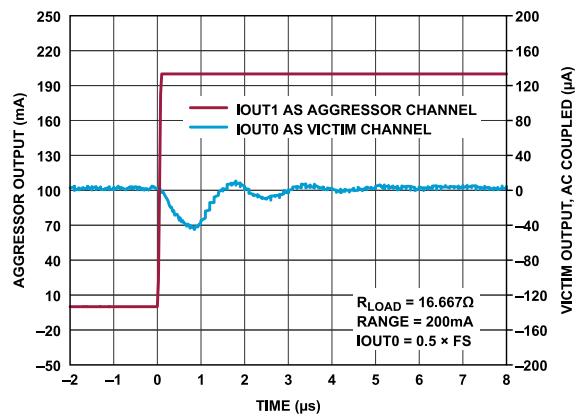

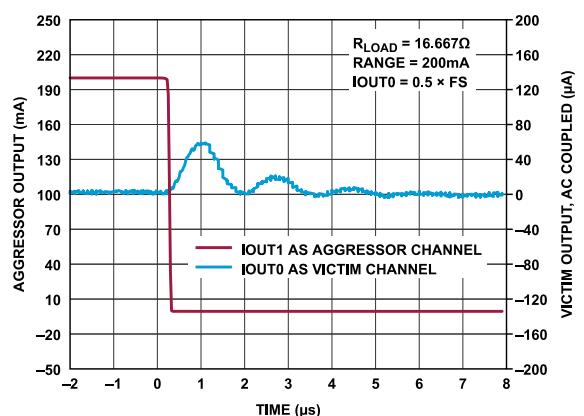

Figure 28. DAC Channel-to-Channel Crosstalk, Positive Output Transition

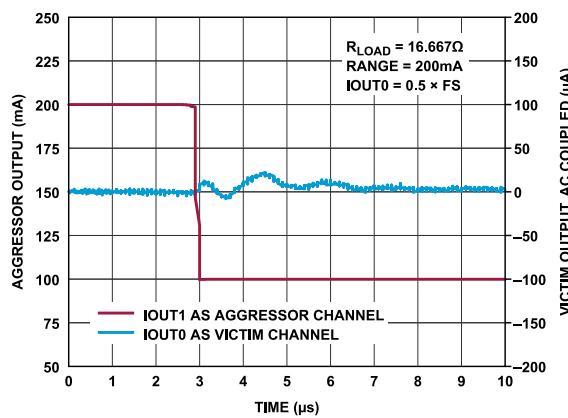

Figure 29. DAC Channel-to-Channel Crosstalk, Negative Output Transition

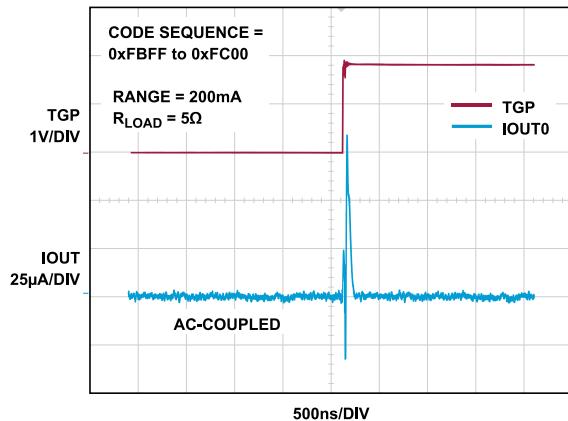

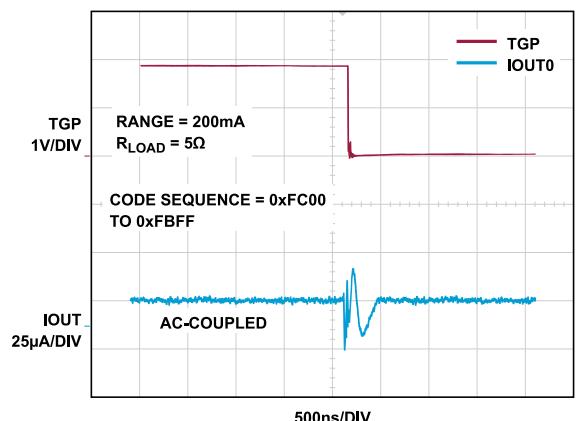

Figure 30. DAC Glitch on Positive Output Transition

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 31. DAC Glitch on Negative Output Transition

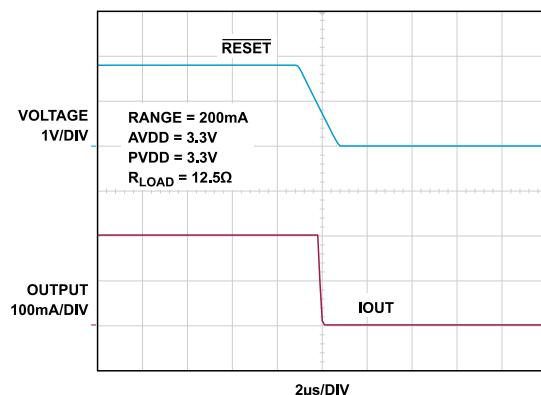

Figure 34. DAC Response Time on Device Reset

Figure 32. Analog Crosstalk, Positive Output Transition

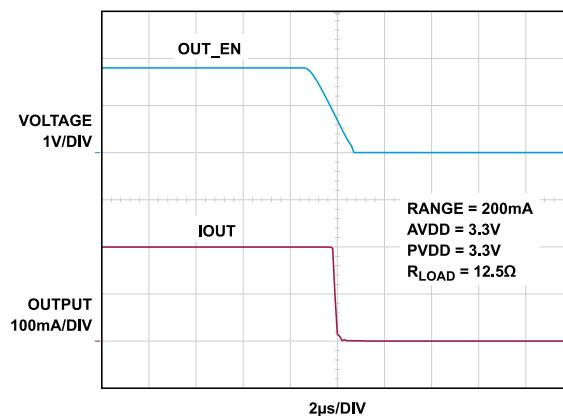

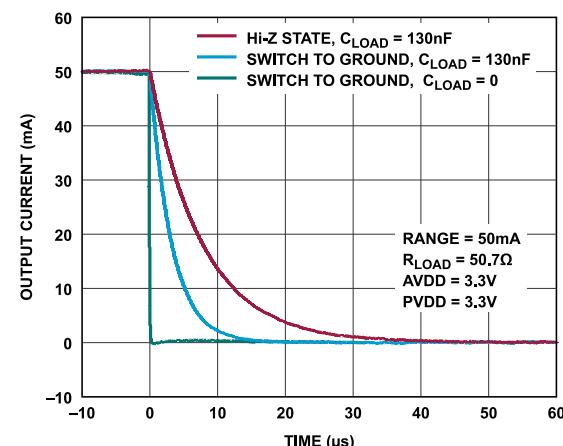

Figure 35. DAC Response Time on Output Disable

Figure 33. Analog Crosstalk, Negative Output Transition

Figure 36. DAC Response on Output Disable over Time

## TYPICAL PERFORMANCE CHARACTERISTICS

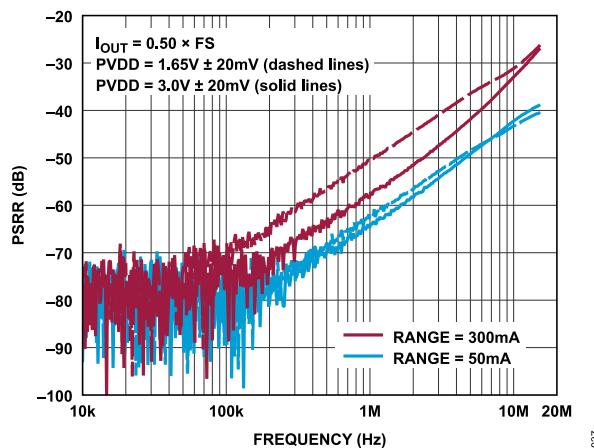

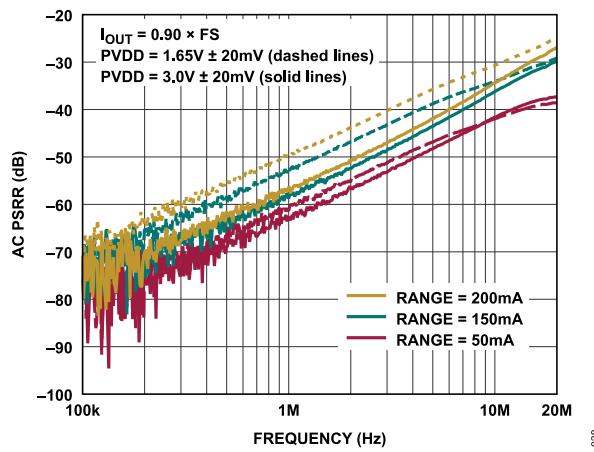

Figure 37. DAC AC PSRR vs. Frequency at DAC Output =  $0.50 \times \text{FS}$

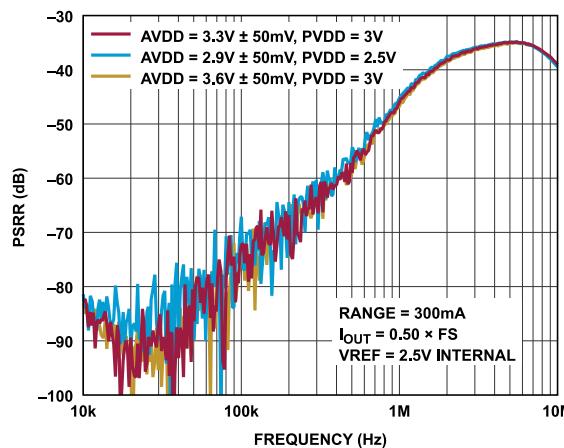

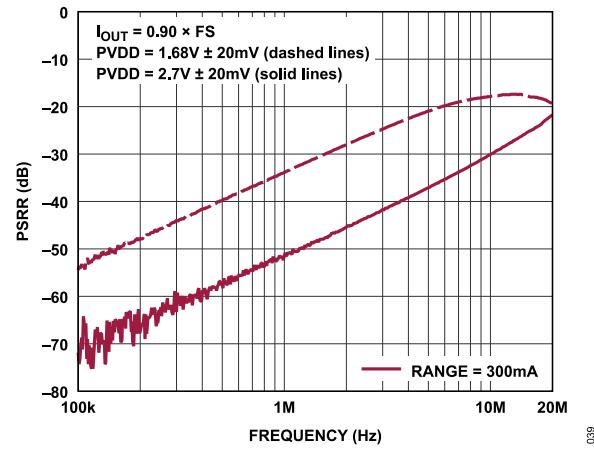

Figure 40. DAC AC PSRR vs. Frequency Across AVDD Supply

Figure 38. DAC AC PSRR vs. Frequency at DAC Output =  $0.90 \times \text{FS}$ Figure 39. DAC AC PSRR vs. Frequency at DAC Output =  $0.90 \times \text{FS}$  of 300mA Range

## TYPICAL PERFORMANCE CHARACTERISTICS

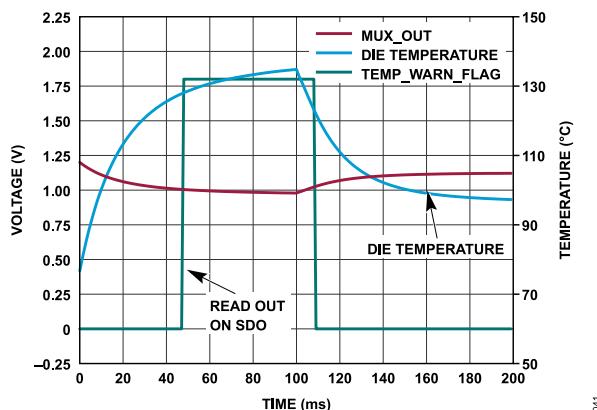

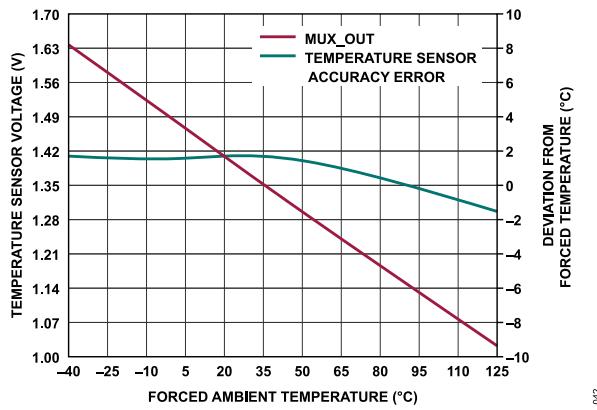

## MISCELLANEOUS

Figure 41. Temperature Sensor Response over Time

Figure 42. Temperature Sensor Voltage vs. Forced Ambient Temperature

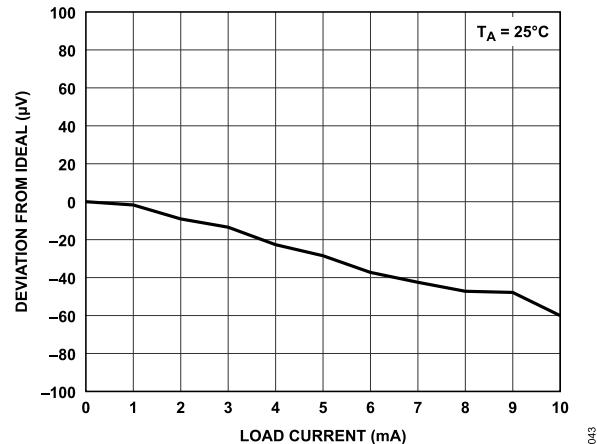

Figure 43. VREF Accuracy Error vs. Load Current

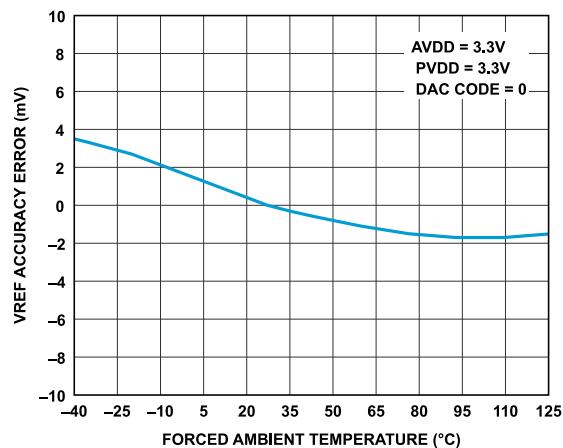

Figure 44. VREF Accuracy Error vs. Forced Ambient Temperature

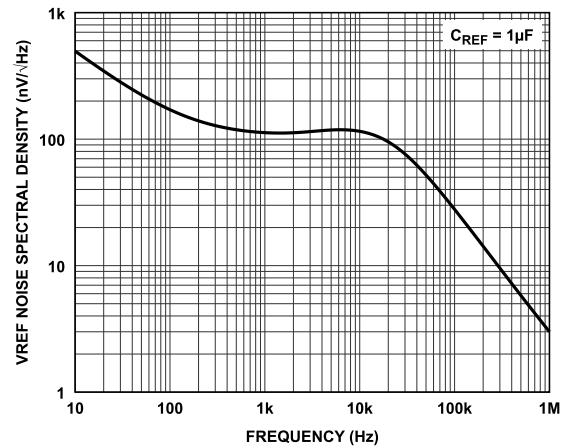

Figure 45. VREF Noise Spectral Density vs. Frequency

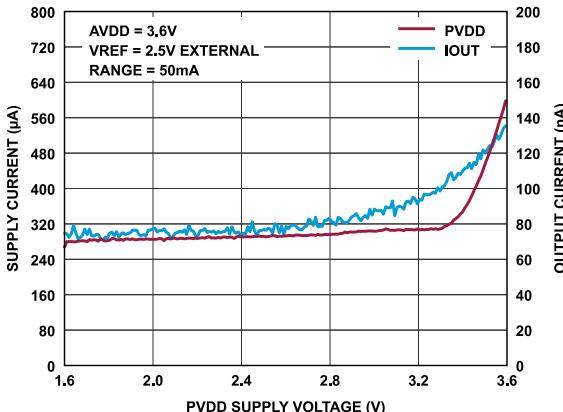

Figure 46. PVDD and IOUT Response in High-Z vs. PVDD Supply Voltage

## TYPICAL PERFORMANCE CHARACTERISTICS

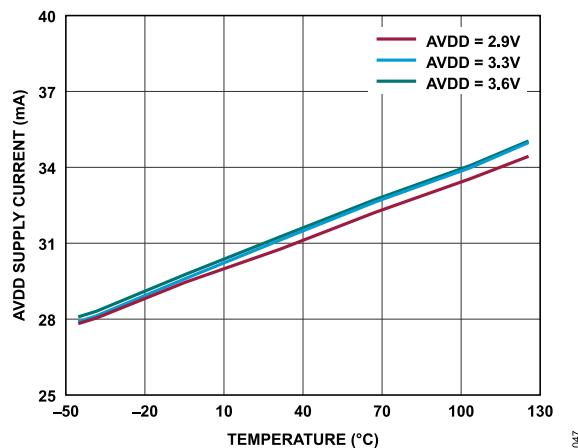

Figure 47. AVDD Supply Current vs. Temperature

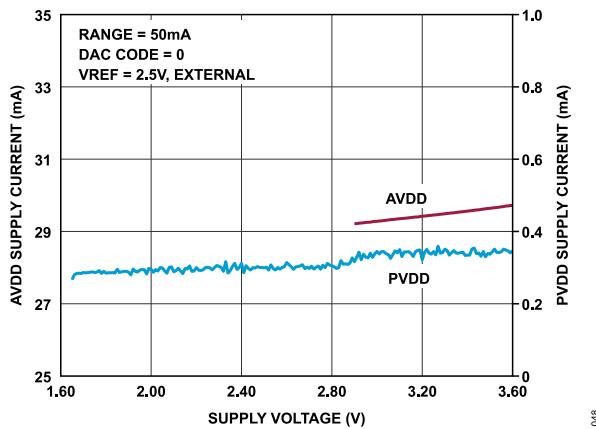

Figure 48. AVDD Supply Current vs. Supply Voltage

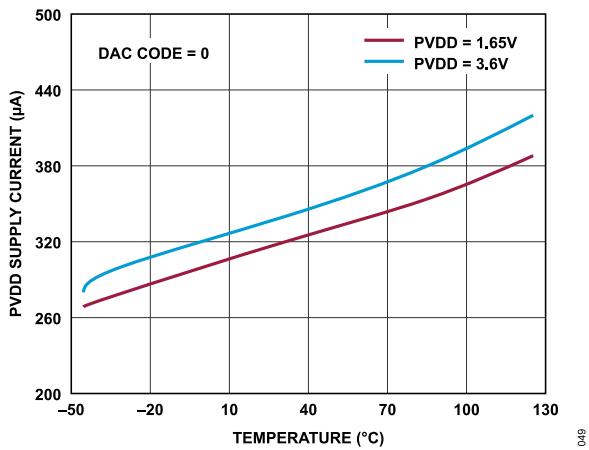

Figure 49. PVDD Supply Current vs. Temperature

## TERMINOLOGY

### DAC

#### Full-Scale Range (FSR)

FSR is the maximum output of the DAC when the full-scale code (0xFFFF for a 16-bit DAC) is loaded to the DAC register.

#### Total Unadjusted Error (TUE)

TUE is a measure of the output error taking all the various errors into account, namely INL error, offset error, gain error, and output drift over supplies, temperature, and time. TUE is expressed as a percentage of full-scale range (% FSR).

#### Relative Accuracy or Integral Nonlinearity (INL)

INL is a measurement of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function.

#### Differential Nonlinearity (DNL)

DNL is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity. This DAC is guaranteed monotonic by design.

#### Gain Error

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal expressed as %FSR.

#### Gain Error Drift

Gain error drift is a measurement of the change in gain error with changes in temperature. It is expressed in ppm of FSR/°C.

#### Offset Error

Offset error is a measurement of the difference between the actual and ideal current output of IOUTx, IOUTx (actual) and IOUTx (ideal), expressed in  $\mu$ A, in the linear region of the transfer function. Offset error can be negative or positive and for a current output DAC, it's expressed in  $\mu$ A.

#### Offset Error Drift

Offset error drift is a measurement of the change in offset error with a change in temperature. For a current output DAC, the offset error drift is expressed in  $\mu$ A/°C.

#### DC Power Supply Rejection Ratio (PSRR)

PSRR indicates how the output of the DAC is affected by DC changes in the supply voltage. For a current output DAC, PSRR

is the ratio of the change in IOUTx to a change in AVDDx for a full-scale output of the DAC and it's measured in  $\mu$ A/V.

#### AC Power Supply Rejection Ratio (PSRR)

AC PSRR is a measure of the rejection of the DAC output to AC changes in the power supplies applied to the DAC. AC PSRR is measured for a given amplitude and frequency change in power supply voltage, using the minimum recommended decoupling, and for a current output DAC is expressed in decibels or  $\mu$ A/V.

#### Output Settling Time

Output settling time is the amount of time it takes for the output of a DAC channel to settle to a specified level for a specified input change and is measured from the falling or rising edge of LDAC.

#### Digital-to-Analog Glitch Energy

Digital-to-analog glitch energy is the energy of the impulse injected into the analog output when the input code in the DAC register changes state. For a current output DAC, the energy is normally specified as the area of the current output glitch in nA-sec and is measured when the digital input code is changed by 1 LSB at the major carry transition (such as 0x7FFF to 0x8000 for a 16-bit DAC).

#### Digital Feedthrough

Digital feedthrough is a measure of the energy of the impulse injected into the analog output of the DAC from the digital inputs of the DAC but is measured when the DAC output is not updated. For a current output DAC, digital feedthrough is specified as the area of the current output glitch in nA-sec and measured with a full-scale code change on the data bus, that is, from all 0s to all 1s and vice-versa.

#### DC Crosstalk

DC crosstalk is the DC change in the output level of one DAC in response to a change in the output of another DAC. For a current output DAC, DC crosstalk is specified as the current output change in  $\mu$ A and is measured with a full-scale output change on one DAC while monitoring another DAC maintained at midscale.

#### Digital Crosstalk

Digital crosstalk is the energy of the glitch impulse transferred to the output of one DAC at midscale in response to a full-scale code change (all 0s to all 1s and vice-versa) in the input register of another DAC. For a current output DAC, digital crosstalk is specified as the area of the current output glitch in nA-sec and measured on one DAC channel at a time.

#### DAC to DAC Crosstalk

DAC to DAC crosstalk is the energy of the glitch impulse transferred to the output of one DAC due to a digital code change and

## TERMINOLOGY

subsequent analog output change of another DAC. For a current output DAC, DAC to DAC crosstalk is specified as the area of the current output glitch in nA-sec and measured with a full-scale change on one DAC output, writing directly to the DAC register while monitoring the other DAC output kept at midscale.

### Analog Crosstalk

Analog crosstalk is the glitch impulse transferred to the output of one DAC due to a change in the output of another DAC. It is measured by loading one of the input registers with a full-scale code change (all 0s to all 1s and vice-versa), then executing a software LDAC command and monitoring the output of the DAC whose digital code was not changed. The energy of the glitch is expressed in nA-sec for a current output DAC.

### Output Noise Spectral Density (NSD)

Output NSD is a measurement of the internally generated random noise. Random noise is characterized as a spectral density. NSD is measured by loading the DAC to midscale and measuring noise at the output. For a current output DAC, NSD is expressed in nA/ $\sqrt{\text{Hz}}$ .

### Multiplexer to DAC Crosstalk

The multiplexer to DAC crosstalk is a measure of the impulse injected into the analog output of the DAC channel when the monitor MUX is changed to the DAC channel from a different channel and vice-versa. This parameter is specified as the area of the current output glitch on the DAC channel and is expressed in nA-sec.

## TERMINOLOGY

### REFERENCE

#### Line Regulation

Line regulation refers to the change in output voltage in response to a given change in supply voltage and is expressed in  $\mu\text{V}/\text{V}$ .

#### Load Regulation

Load regulation refers to the change in output voltage in response to a given change in load current and is expressed in  $\text{ppm}/\text{mA}$ .

#### Voltage Reference ( $V_{\text{REF}}$ ) Temperature Coefficient (TC)

$V_{\text{REF}} \text{ TC}$  is a measure of the change in the reference output voltage with a change in the ambient temperature of the device, normalized by the output voltage at 25°C.  $V_{\text{REF}} \text{ TC}$  is specified using the box method that defines TC as the maximum change in the reference output over a given temperature range expressed in  $\text{ppm}/^{\circ}\text{C}$ , as follows:

$$V_{\text{REF}TC} = \left( \frac{V_{\text{REF}, \text{MAX}} - V_{\text{REF}, \text{MIN}}}{V_{\text{REF}, \text{NOM}} \times \text{TEMP\_RANGE}} \right) \times 10^6 \text{ ppm}/^{\circ}\text{C} \quad (1)$$

where:

$V_{\text{REF}, \text{MAX}}$  is the maximum reference voltage output measured over the full temperature range.

$V_{\text{REF}, \text{MIN}}$  is the minimum reference voltage output measured over the full temperature range.

$V_{\text{REF}, \text{NOM}}$  is the nominal reference voltage output at ambient temperature (25°C).

$\text{TEMP\_RANGE}$  is the difference between the maximum and minimum operating temperature of the reference.

#### Voltage Reference ( $V_{\text{REF}}$ ) Noise Spectral Density (NSD)

$V_{\text{REF}} \text{ NSD}$  is a measurement of the internally generated random noise characterized as a spectral density  $\text{nV}/\sqrt{\text{Hz}}$ .

## THEORY OF OPERATION

### DEVICE INFORMATION

The AD5706R is a 4-channel, 16-bit current output digital-to-analog converter (DAC) with an SPI interface. The device is optimized for sourcing programmable, low-noise output currents with high power efficiency. Integrated features include a 2.5V on-chip voltage reference, load DAC, A/B toggle functionality, and sinusoidal dither. An internal analog multiplexer enables monitoring of key internal nodes, including supply and output voltages, output currents, and die temperature.

### PRECISION REFERENCE

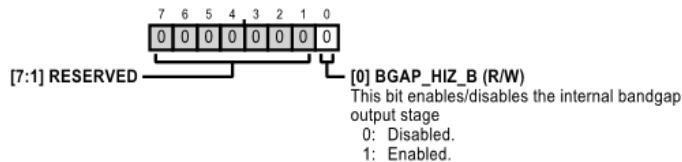

The AD5706R integrates a low-noise, on-chip 2.5V voltage reference with a typical temperature coefficient of 15ppm/°C. By default, this internal reference is powered down and can be enabled by setting the BGAP\_HIZ\_B bit in the BANDGAP\_CONTROL register. When enabled, the buffered 2.5V reference is available at the VREF pin for external system use.

Alternatively, the device supports the use of an external 2.5V reference applied to the VREF pin, which is the default configuration at power-up. For proper operation, it is recommended that the external reference shares the same supply as the AD5706R to ensure that  $VREF \leq AVDD$  during power-up.

To achieve optimal noise performance, consider the following:

- ▶ A 0.1 $\mu$ F capacitor should be connected between the NF pin and REFGND, regardless of the reference source.

- ▶ When using the internal reference, an additional 1 $\mu$ F capacitor is recommended between VREF and REFGND.

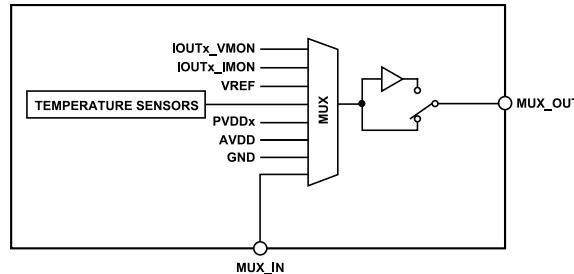

### ANALOG MULTIPLEXER AND DIAGNOSTIC MONITORING

The device includes an integrated diagnostic feature that enables real-time monitoring of key internal and external parameters via the MUX\_OUT pin. The following signals can be routed to the MUX\_OUT output:

- ▶ IOUTx load voltages

- ▶ IOUTx output currents

- ▶ Supply rail voltages

- ▶ VREF (reference voltage)

- ▶ Internal die temperature

All monitored signals are represented as unipolar voltages ranging from 0V to VREF. This allows for straightforward interfacing with external ADCs or monitoring systems.

Figure 50. Analog Multiplexer

At power-up, the diagnostic monitoring function is disabled, and the MUX\_OUT pin is placed in a high-impedance (high-Z) state to prevent unintended signal output.

Complete the following to enable diagnostic monitoring:

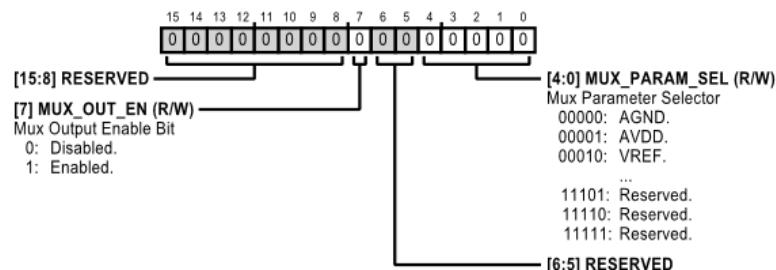

- ▶ Set the MUX\_OUT\_EN field in the MUX\_OUT\_SEL register.

- ▶ Use the MUX\_PARAM\_SEL register to select which internal signal or channel is routed to the MUX\_OUT pin.

By default, the GND channel is selected in the MUX block. The available channel selections and their corresponding register field values are listed in Table 8.

Table 8. Multiplexer Channels

| MUX_PARAM_SEL Field | MUX_OUT Channel                  |

|---------------------|----------------------------------|

| 0                   | GND (default)                    |

| 1                   | AVDD supply voltage monitor      |

| 2                   | VREF voltage monitor             |

| 3                   | GND                              |

| 4                   | IOUT0 load voltage monitor       |

| 5                   | IOUT1 load voltage monitor       |

| 6                   | IOUT2 load voltage monitor       |

| 7                   | IOUT3 load voltage monitor       |

| 8                   | IOUT0 output current monitor     |

| 9                   | IOUT1 output current monitor     |

| 10                  | IOUT2 output current monitor     |

| 11                  | IOUT3 output current monitor     |

| 12                  | PVDD0 supply voltage monitor     |

| 13                  | PVDD1 supply voltage monitor     |

| 14                  | PVDD2 supply voltage monitor     |

| 15                  | PVDD3 supply voltage monitor     |

| 16                  | IOUT0 temperature sensor monitor |

| 17                  | IOUT1 temperature sensor monitor |

| 18                  | IOUT2 temperature sensor monitor |

| 19                  | IOUT3 temperature sensor monitor |

| 20 to 23            | MUX_IN                           |

| 24 to 31            | Reserved                         |

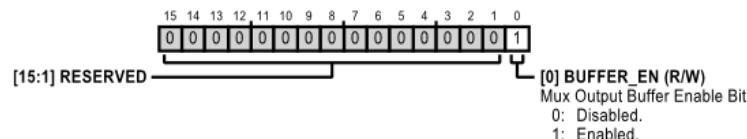

The MUX\_OUT pin is internally buffered to support direct interfacing with external ADCs. This buffer can be bypassed by clearing the BUFFER\_EN bit (that is, setting it to 0). The internal buffer can be bypassed by setting the BUFFER\_EN bit to 0. Note that when

## THEORY OF OPERATION

the internal buffer is disabled, the MUX switch impedance can vary between  $1\text{k}\Omega$  and  $20\text{k}\Omega$ . In this configuration, the MUX\_OUT pin should only be connected to high-impedance inputs to ensure signal integrity. The available MUX\_OUT configurations are summarized in [Table 9](#), and the corresponding full-scale output voltages for each monitored channel are provided in [Table 10](#).

**Table 9. MUX\_OUT Configuration**

| MUX_OUT_EN Bit | BUFFER_EN Bit | MUX_OUT Status               |

|----------------|---------------|------------------------------|

| 1'b0           | X             | High-Z                       |

| 1'b1           | 1'b0          | Buffer disabled and bypassed |

| 1'b1           | 1'b1          | Buffer enabled               |

**Table 10. Full Scale Output Voltages**

| MUX_OUT Channel             | Nominal Full Scale Output (V) |

|-----------------------------|-------------------------------|

| Current Monitor Channels    | 1.2                           |

| Temperature Sensor Channels | 1.6                           |

| Other Channels              | 2.5                           |

## IOUT Output Current Monitoring

When the appropriate MUX channel is selected via the MUX\_PAR-AM\_SEL register, the current at the IOUTx pin is represented as a voltage on the MUX\_OUT pin. The output voltage range for this representation is 0V to 1.25V.

The output current can be calculated using the following formula:

$$I_{OUT} = \frac{300mA \times V_{MUX\_OUT}}{1.25V} \quad (2)$$

where:

$I_{OUT}$  is the output current at the IOUTx pin.

$V_{MUX\_OUT}$  is the voltage at the MUX\_OUT pin.

Note that the above equation is valid only when the IOUTx pin is properly loaded and operating within compliance voltage limits. It is not valid if the output is open or dropping out.

The voltage output at MUX\_OUT maintains the same optimal linearity as the current outputs. However, due to potential slope error (up to  $\pm 20\%$  of full-scale range), calibration is recommended for accurate current measurement.

## Two-Point Calibration

For improved accuracy (up to  $\pm 1\%$  FSR), a two-point calibration method can be applied, assuming the current output is reasonably linear over the measurement range. The calibrated output current is calculated as:

$$I_{OUT,X} = \frac{I_{OUT,A} - I_{OUT,B}}{DAC\_CODE_A - DAC\_CODE_B} \times (DAC\_CODE_X - DAC\_CODE_B) + I_{OUT,B} \quad (3)$$

where:

$I_{OUT,A}$ ,  $I_{OUT,B}$  = Measured output currents at respective DAC codes  $DAC\_CODE_A$  and  $DAC\_CODE_B$ .

$I_{OUT,X}$  = Expected output currents at DAC code  $DAC\_CODE_X$ .

## IOUT Output Voltage Monitoring

By selecting the appropriate MUX channel in the MUX\_PAR-AM\_SEL register, a scaled-down representation of the IOUTx pin voltage can be routed to the MUX\_OUT pin. The output voltage range for this representation is 0V to VREF, with a typical accuracy of  $\pm 10\text{mV}$ .

The conversion from MUX\_OUT voltage to the actual IOUTx pin voltage follows the equation:

$$V_{OUT} = \frac{2}{3} \times V_{MUX\_OUT} \quad (4)$$

where:

$V_{OUT}$  is the actual voltage at the IOUTx pin.

$V_{MUX\_OUT}$  is the voltage measured at the MUX\_OUT pin.

The preceding equation is valid only when the IOUTx pin is properly loaded and operating within its compliance voltage range. It is not valid if the output is open or dropping out.

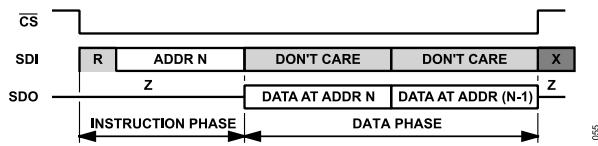

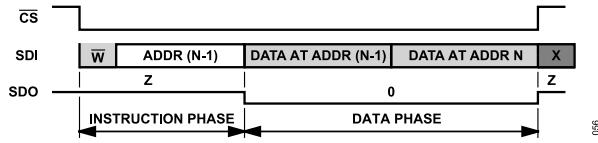

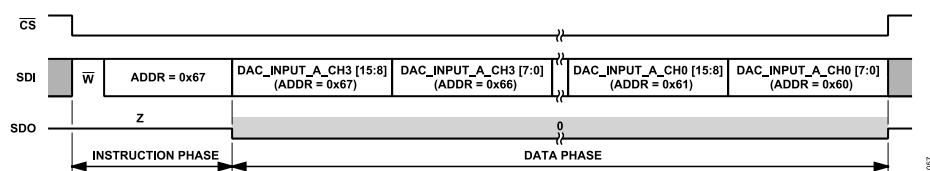

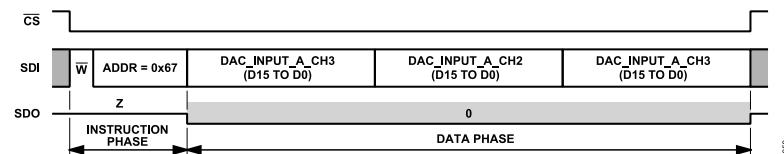

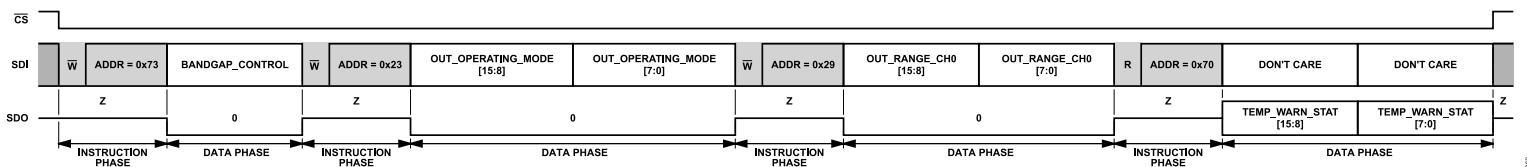

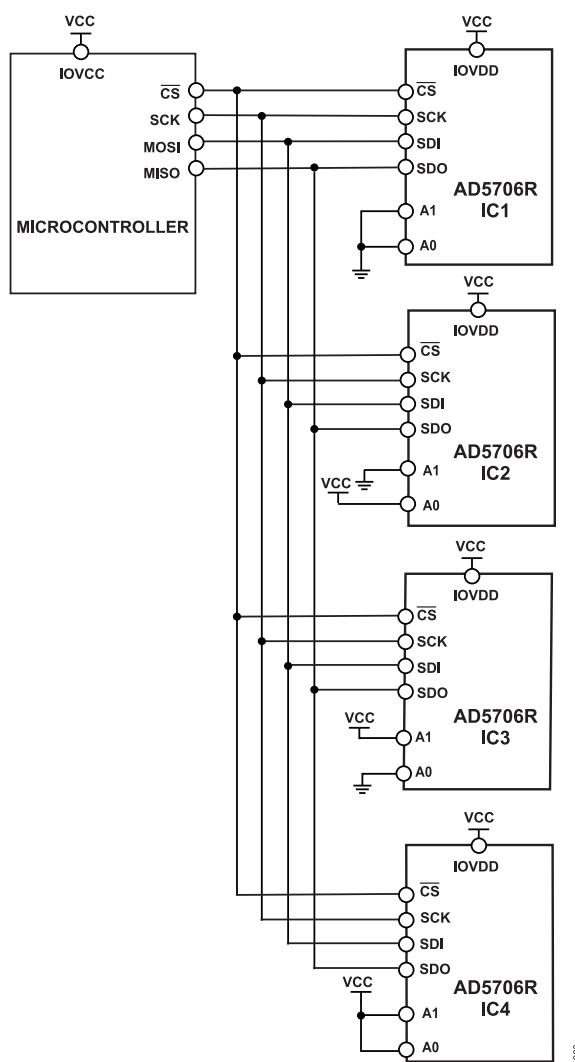

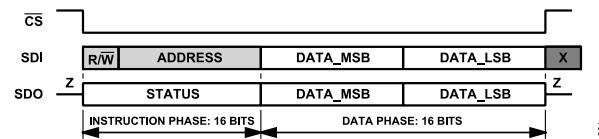

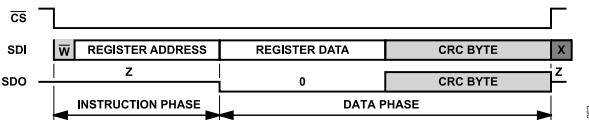

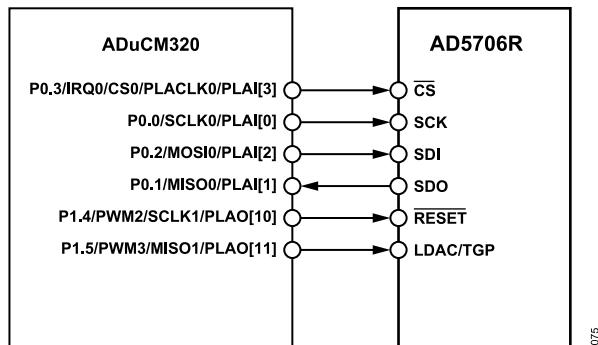

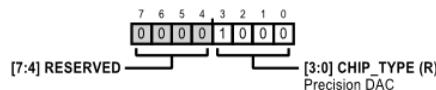

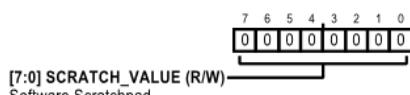

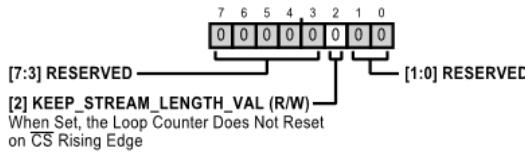

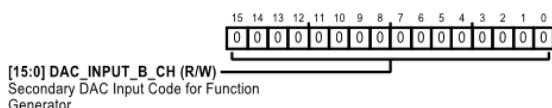

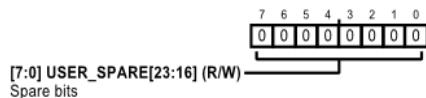

## Internal Die Temperature Monitoring