## 14-Bit, 20 MSPS, Low Noise, Low Power SAR ADC

### FEATURES

- ▶ 14-bit resolution, no missing codes

- ▶ Throughput: 20MSPS, 82.14ns conversion latency

- ▶ Noise spectral density: 35.61nV/ $\sqrt{\text{Hz}}$ , 158.5dBFS/Hz

- ▶ Low 1/f, low frequency noise (0.1Hz to 10Hz): 383nV rms

- ▶ Low Power: 68mW typical at 20MSPS

- ▶ INL:  $\pm 12\text{ppm}$  (typ),  $\pm 16\text{ppm}$  (max)

- ▶ Dynamic range: 85.5dBFS

- ▶ SNR/THD

- ▶ 85.39dB (typ)/-114.8dB (typ) at  $f_{\text{IN}} = 1\text{kHz}$

- ▶ 85.27dB (typ)/-101.35dB (typ) at  $f_{\text{IN}} = 1\text{MHz}$

- ▶ Easy Drive

- ▶ 6V p-p differential input range

- ▶ Continuous signal acquisition

- ▶ Linearized, 5 $\mu\text{A}$ /MSPS input current

- ▶ Integrated, low-drift reference buffer and decoupling

- ▶ Integrated  $V_{\text{CM}}$  generation

- ▶ Digital features and data interface

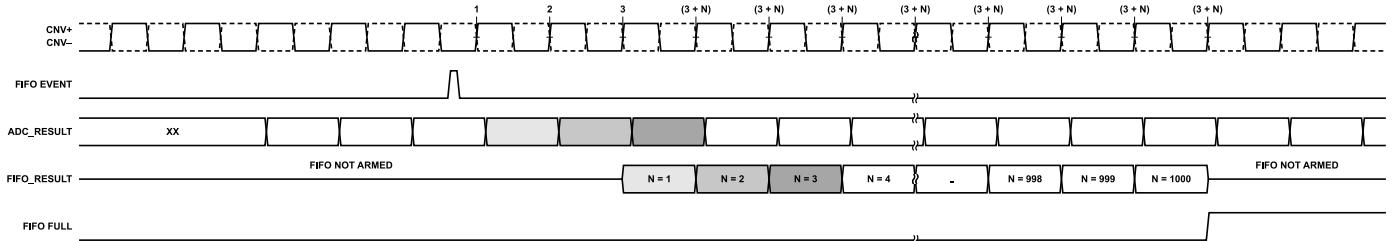

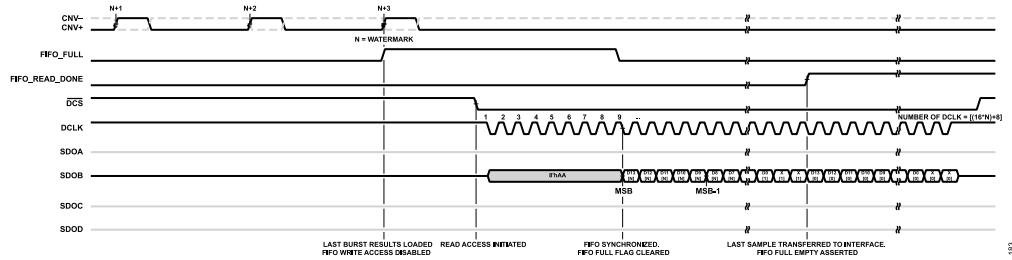

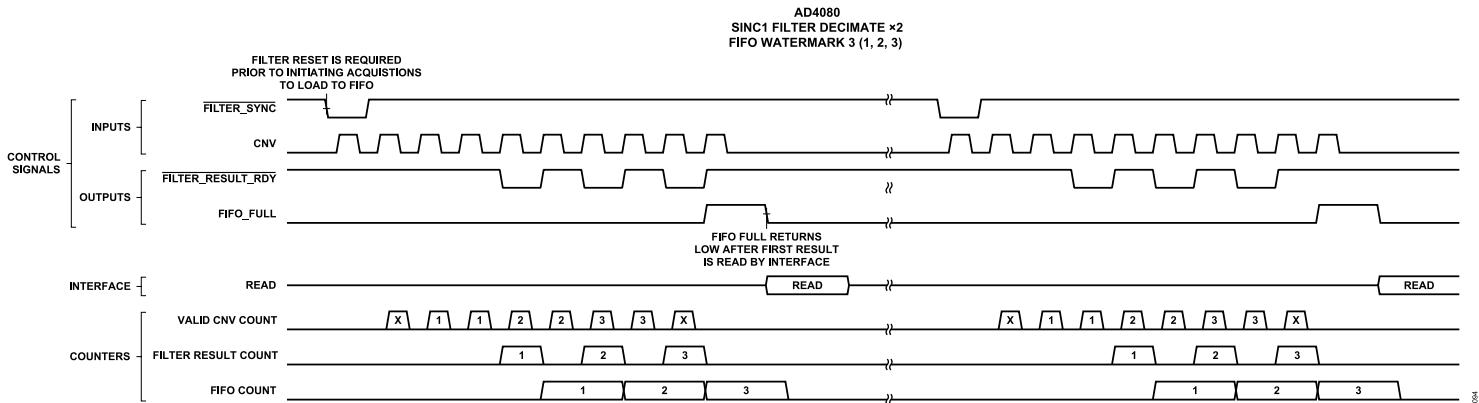

- ▶ Conversion result FIFO, 16K sample depth

- ▶ Digital averaging filter with up to  $2^{10}$  decimation

- ▶ SPI configuration

- ▶ Configurable data interface

- ▶ Single lane, DDR, serial LVDS, 280Mbps per lane

- ▶ Dual lane, DDR, serial LVDS, 140Mbps per lane

- ▶ Single/quad lane SPI data interface

- ▶ Package

- ▶ 49-ball, 5mm  $\times$  5mm CSP\_BGA, 0.65mm pitch

- ▶ Integrated supply decoupling capacitors

- ▶ Operating temperature range: -40°C to +85°C

### APPLICATIONS

- ▶ Digital imaging

- ▶ Cell analysis

- ▶ Spectroscopy

- ▶ Automated test equipment

- ▶ High speed data acquisition

- ▶ Digital control loops, hardware in the loop

- ▶ Power quality analysis

- ▶ Source measurement units

- ▶ Electron and X-ray microscopy

- ▶ Radar level measurement

- ▶ Nondestructive test

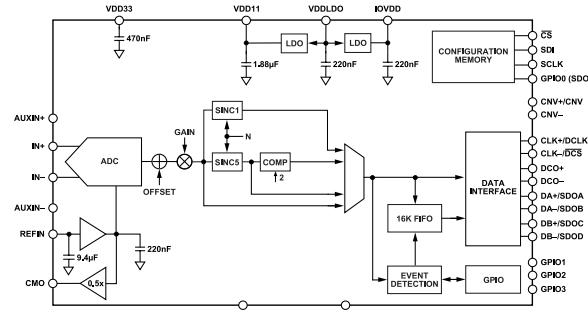

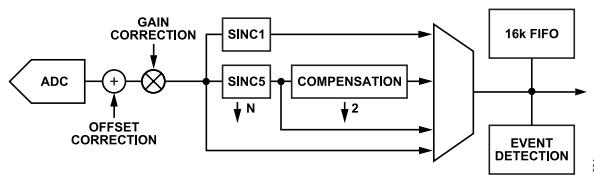

### FUNCTIONAL BLOCK DIAGRAM

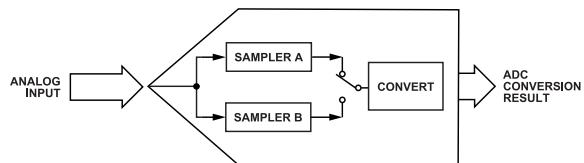

Figure 1. AD4087 Functional Block Diagram

### GENERAL DESCRIPTION

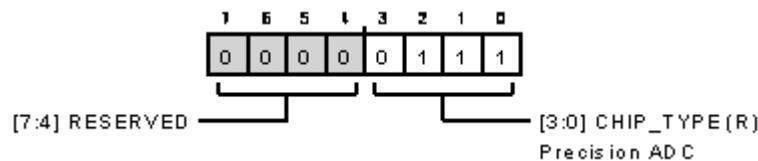

The AD4087 is a high speed, low noise, low distortion, 14-bit, Easy Drive, successive approximation register (SAR) analog-to-digital converter (ADC). Maintaining high performance (signal-to-noise and distortion (SINAD) ratio  $> 90\text{dBFS}$ ) at signal frequencies in excess of 1MHz enables the AD4087 to service a wide variety of precision, wide bandwidth data acquisition applications. Simplification of the input anti-alias filter design can be accomplished by applying over-sampling along with the integrated digital filtering and decimation to reduce noise and lower the output data rate for applications that do not require the lowest latency of the AD4087.

The AD4087 Easy Drive features reduce both signal chain complexity and power consumption while enabling greater channel density and flexibility in companion component selection. The product input structure was designed to minimize any input dependent signal currents, therefore reducing any converter induced settling artifacts. The continuous acquisition architecture allows settling across the entire conversion cycle, easing ADC driver settling and bandwidth requirements as compared to other high-speed data converters.

The AD4087 includes several elements that simplify data converter integration: a low drift reference buffer, low dropout (LDO) regulators to generate ADC core and digital interface supply rails, and a 16K result data first-in first out (FIFO) that can greatly reduce the load on the digital host. Additionally, critical supply and reference decoupling capacitors are integrated in the package to ensure optimum performance, simplify printed circuit board (PCB) layout, and reduce the overall solution footprint.

**TABLE OF CONTENTS**

|                                                  |    |                                           |    |

|--------------------------------------------------|----|-------------------------------------------|----|

| Features.....                                    | 1  | Software Reset.....                       | 26 |

| Applications.....                                | 1  | Applications Information.....             | 27 |

| Functional Block Diagram.....                    | 1  | Typical Applications Diagrams.....        | 27 |

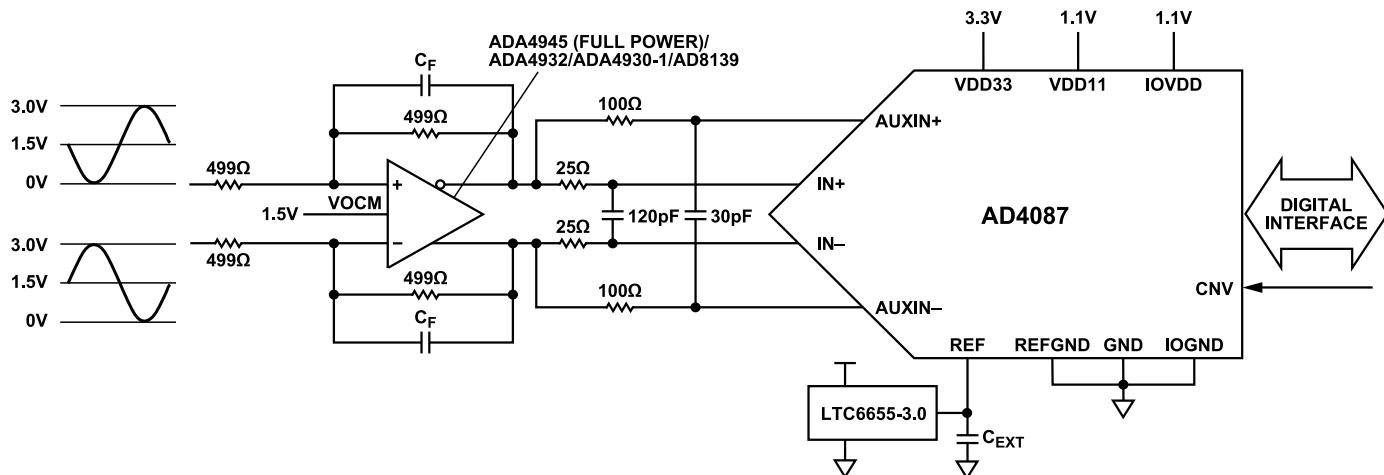

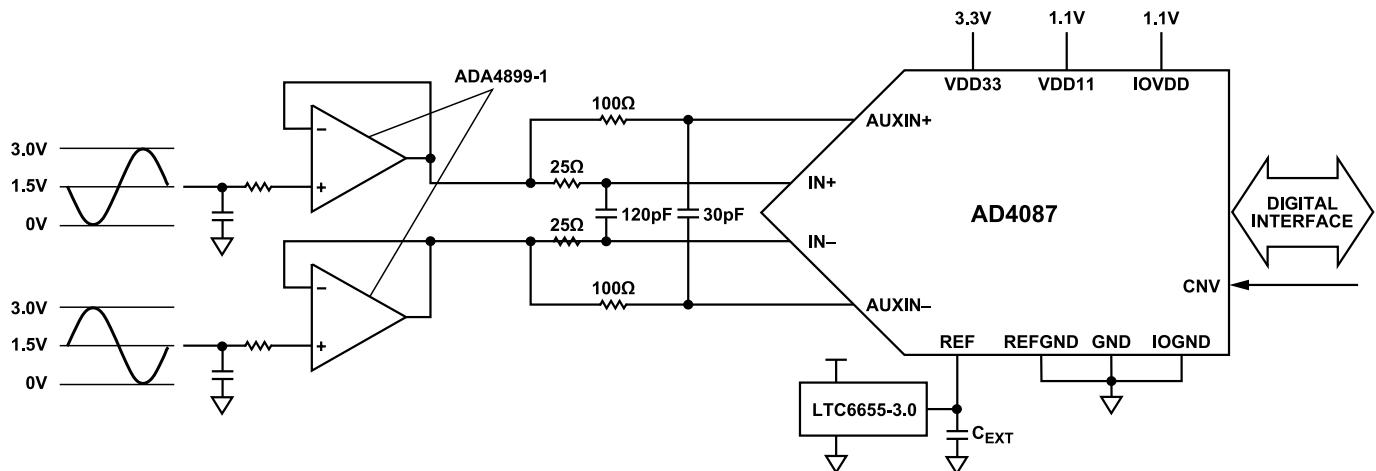

| General Description.....                         | 1  | Analog Front End Design.....              | 28 |

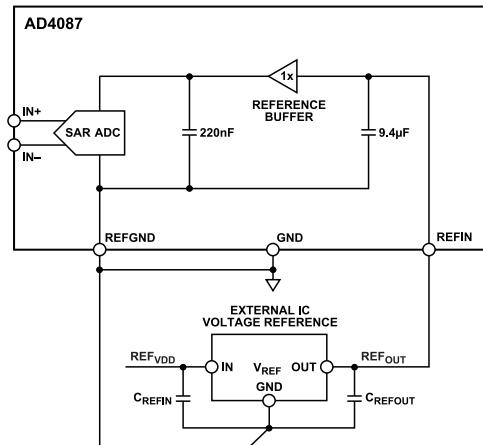

| Specifications.....                              | 3  | Reference Circuitry Design.....           | 29 |

| Timing Specifications.....                       | 6  | Data Interface Clocking Solution.....     | 29 |

| Absolute Maximum Ratings.....                    | 8  | Power Solution.....                       | 30 |

| Thermal Resistance.....                          | 8  | Digital Interface.....                    | 31 |

| Electrostatic Discharge (ESD) Ratings.....       | 8  | Overview.....                             | 31 |

| ESD Caution.....                                 | 8  | SPI Configuration Interface.....          | 31 |

| Pin Configuration and Function Descriptions..... | 9  | LVDS Data Interface.....                  | 43 |

| Typical Performance Characteristics.....         | 12 | SPI Data Interface.....                   | 49 |

| Terminology.....                                 | 17 | GPIO Pins.....                            | 50 |

| Theory of Operation.....                         | 18 | Digital Features.....                     | 52 |

| Product Overview.....                            | 18 | Overview.....                             | 52 |

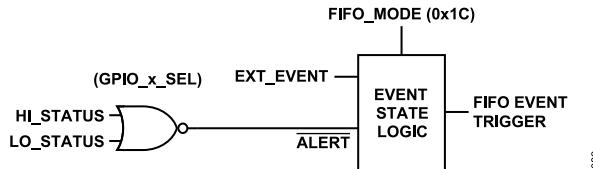

| Converter Operation.....                         | 18 | Event Detection.....                      | 52 |

| Transfer Function.....                           | 19 | Result FIFO.....                          | 54 |

| Easy Drive Analog Inputs .....                   | 19 | Digital Filter.....                       | 61 |

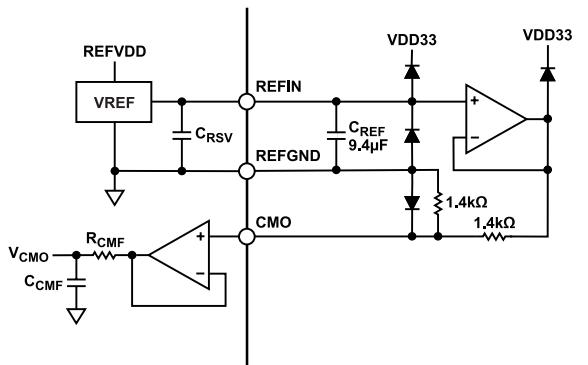

| Reference Buffer and Common-Mode Output..        | 21 | System Error Correction Coefficients..... | 68 |

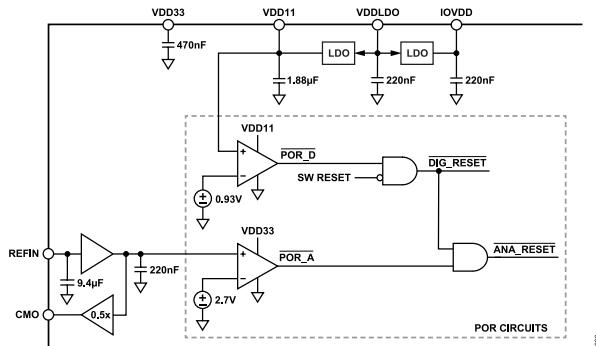

| Power Supplies.....                              | 21 | Layout Guidelines.....                    | 69 |

| Internally Regulated Supply Configuration.....   | 22 | Configuration Registers.....              | 70 |

| Externally Generated Supply Configuration....    | 22 | Register Details.....                     | 72 |

| Power-On Reset (POR) Monitor.....                | 22 | Outline Dimensions.....                   | 92 |

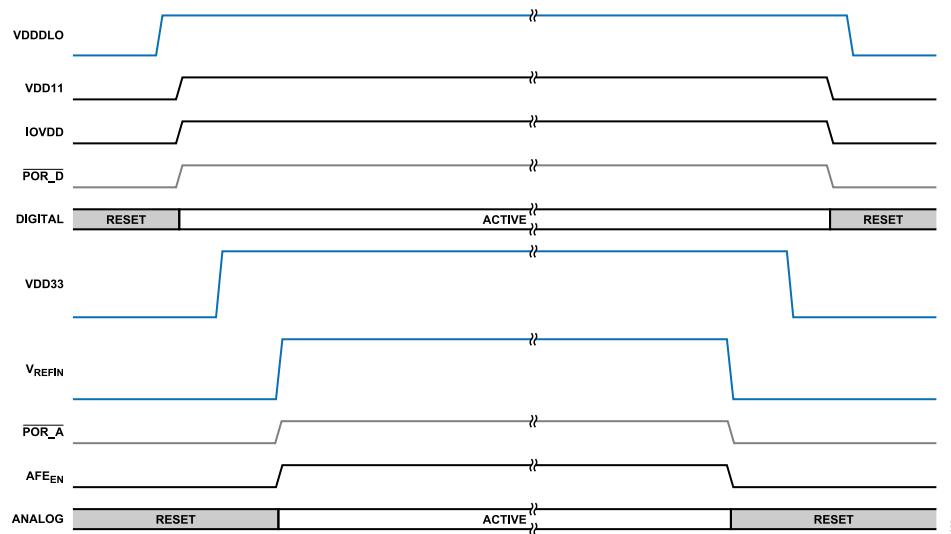

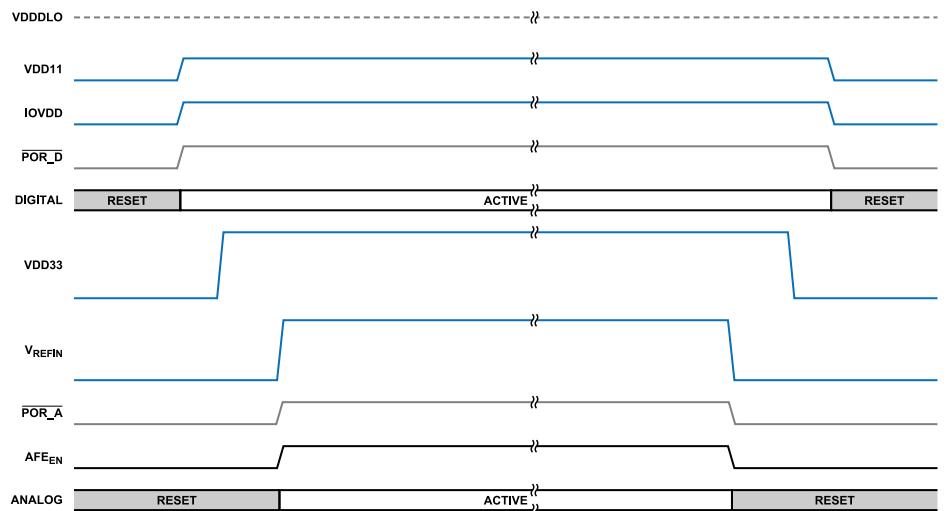

| Power Supply Sequence.....                       | 23 | Ordering Guide.....                       | 92 |

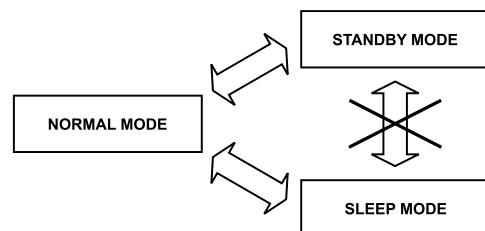

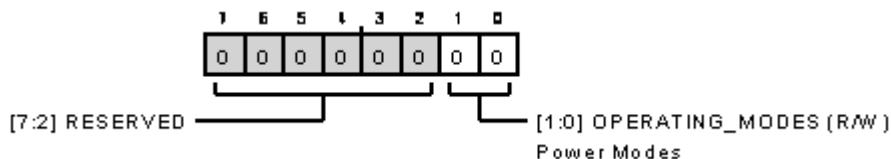

| Power Saving Operating Modes.....                | 24 |                                           |    |

**REVISION HISTORY****1/2026—Revision 0: Initial Version**

## SPECIFICATIONS

VDD33 = 3.3V  $\pm$  5%, VDDLDO = 1.5V to 2.7V, VDD11 = 1.1V  $\pm$  5%, IOVDD = 1.1V – 5% to 1.2V + 5%, voltage reference input ( $V_{REFIN}$ ) = 3.0V, sampling frequency ( $f_S$ ) = 20MHz, and  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 1. Specifications

| Parameter                              | Test Conditions/Comments                                                                         | Min                  | Typ           | Max                  | Unit                      |

|----------------------------------------|--------------------------------------------------------------------------------------------------|----------------------|---------------|----------------------|---------------------------|

| RESOLUTION                             |                                                                                                  | 14                   |               |                      | Bits                      |

| ANALOG INPUT                           |                                                                                                  |                      |               |                      |                           |

| Absolute Operating Input Voltage       | Voltage at input, referred to GND                                                                | -0.1                 |               | VDD33 + 0.1          | V                         |

| Differential Input Voltage Range       | IN+ voltage – IN- voltage                                                                        | $-V_{REFIN}$         |               | $+V_{REFIN}$         | V                         |

| Common-Mode Input Range                |                                                                                                  | $V_{REFIN}/2 - 0.05$ | $V_{REFIN}/2$ | $V_{REFIN}/2 + 0.05$ | V                         |

| DC PERFORMANCE                         |                                                                                                  |                      |               |                      |                           |

| No Missing Codes                       |                                                                                                  | 14                   |               |                      | Bits                      |

| Differential Nonlinearity (DNL)        |                                                                                                  |                      | $\pm 0.061$   | $\pm 0.16$           | LSB                       |

| Integral Nonlinearity (INL)            |                                                                                                  |                      | $\pm 12$      | $\pm 16$             | ppm                       |

| Transition Noise                       |                                                                                                  |                      | 0.31          |                      | LSB rms                   |

| Gain Error                             | $T_A = 25^\circ\text{C}$                                                                         |                      | 0.0037        | $\pm 0.05$           | %FS                       |

| Gain Error Drift                       | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$                                                 |                      | 0.27          |                      | ppm/ $^\circ\text{C}$     |

| Zero Error                             | $T_A = 25^\circ\text{C}$                                                                         |                      | -361          |                      | $\mu\text{V}$             |

| Zero-Error Drift                       | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$                                                 |                      | 0.03          |                      | ppm/ $^\circ\text{C}$     |

| Power Supply Rejection                 | VDD33 = 3.3V $\pm$ 5%                                                                            |                      | -89           |                      | dB                        |

|                                        | VDD11 = 1.1V $\pm$ 5%                                                                            |                      | -68           |                      | dB                        |

| Low Frequency Noise                    | Bandwidth = 0.1Hz to 10Hz                                                                        |                      | 383           |                      | nV rms                    |

| AC PERFORMANCE                         |                                                                                                  |                      |               |                      |                           |

| Dynamic Range                          |                                                                                                  |                      | 85.5          |                      | dB                        |

| Noise Spectral Density (NSD)           |                                                                                                  |                      | 158.5         |                      | dBFS/Hz                   |

| Total RMS Noise                        | Bandwidth = 10MHz                                                                                |                      | 112.62        |                      | $\mu\text{V rms}$         |

| Signal-to-Noise Ratio (SNR)            | Voltage magnitude ( $V_{MAG}$ ) = -0.5dBFS, input frequency ( $f_{IN}$ ) = 1kHz                  | 85                   | 85.39         |                      | dB                        |

|                                        | $V_{MAG} = -1\text{dBFS}$ , $f_{IN} = 1\text{MHz}$                                               |                      | 85.27         |                      | dB                        |

|                                        | Sinc5 + compensation filter, decimate by 8, $V_{MAG} = -0.5\text{dBFS}$ , $f_{IN} = 1\text{kHz}$ | 95.5                 | 96.7          |                      | dB                        |

| Total Harmonic Distortion (THD)        | $V_{MAG} = -0.5\text{dBFS}$ , $f_{IN} = 1\text{kHz}$                                             |                      | -114.8        | -108.5               | dB                        |

|                                        | $V_{MAG} = -1\text{dBFS}$ , $f_{IN} = 1\text{MHz}$                                               |                      | -101.35       |                      | dB                        |

| Signal-to-Noise-and-Distortion (SINAD) | $V_{MAG} = -0.5\text{dBFS}$ , $f_{IN} = 1\text{kHz}$                                             |                      | 85.38         |                      | dB                        |

|                                        | $V_{MAG} = -0.5\text{dBFS}$ , $f_{IN} = 1\text{MHz}$                                             |                      | 85.21         |                      | dB                        |

| Spurious-Free Dynamic Range            | $V_{MAG} = -0.5\text{dBFS}$ , $f_{IN} = 1\text{kHz}$                                             |                      | 118.1         |                      | dB                        |

|                                        | $V_{MAG} = -0.5\text{dBFS}$ , $f_{IN} = 1\text{MHz}$                                             |                      | 108.2         |                      | dB                        |

| -3dB Bandwidth                         | Input at IN+ and IN-, no external filter                                                         |                      | 272           |                      | MHz                       |

| Intermodulation Distortion (IMD)       | Frequency A ( $f_A$ ) = 1.0MHz, Frequency B ( $f_B$ ) = 800kHz                                   |                      |               |                      |                           |

|                                        |                                                                                                  |                      | -94.2         |                      | dB                        |

|                                        |                                                                                                  |                      | -100.7        |                      | dB                        |

| Second-Order IMD (IMD2)                |                                                                                                  |                      |               |                      |                           |

| Third-Order IMD (IMD3)                 |                                                                                                  |                      |               |                      |                           |

| Power Supply Rejection                 | Ripple voltage = 50mV p-p, $f = 1\text{kHz}$                                                     |                      |               |                      |                           |

| VDD33                                  |                                                                                                  |                      | -92.5         |                      | dB                        |

| VDD11                                  |                                                                                                  |                      | -81.2         |                      | dB                        |

| REFERENCE INPUT                        |                                                                                                  |                      |               |                      |                           |

| $V_{REFIN}$ Range                      |                                                                                                  | 2.995                | 3.0           | 3.005                | V                         |

| $V_{REFIN}$ Current                    |                                                                                                  | -1                   |               | 1                    | $\mu\text{A}/\text{MSPS}$ |

|                                        | $T_A = 25^\circ\text{C}$                                                                         | -14                  |               | 14                   | $\mu\text{A}$             |

| $V_{REFIN}$ Leakage Current            | Converter Idle                                                                                   | -2                   |               | 2                    | $\mu\text{A}$             |

## SPECIFICATIONS

Table 1. Specifications (Continued)

| Parameter                                                            | Test Conditions/Comments                                                                        | Min  | Typ           | Max                 | Unit           |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|---------------|---------------------|----------------|

| COMMON-MODE OUTPUT (CMO)                                             |                                                                                                 |      |               |                     |                |

| Absolute Output Voltage                                              | $V_{REFIN} = 3.0V$                                                                              | 1.48 |               | 1.51                | V              |

| Noise                                                                | Bandwidth = 7.4MHz                                                                              |      | 71            |                     | $\mu V$ rms    |

| Noise Spectral Density                                               |                                                                                                 |      | 26.1          |                     | $nV/\sqrt{Hz}$ |

| LOW DROPOUT REGULATORS (VDD11, IOVDD)                                |                                                                                                 |      |               |                     |                |

| Input Voltage Range (VDDLDO)                                         |                                                                                                 | 1.4  |               | 2.7                 | V              |

| Output Voltage                                                       | $T_A = 25^\circ C, VDDLDO = 1.8V$                                                               |      | 1.1           |                     | V              |

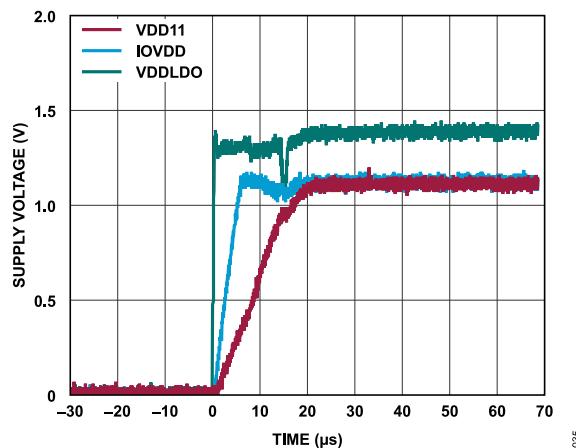

| Start-Up Time                                                        |                                                                                                 |      | 10            |                     | $\mu s$        |

| LOW VOLTAGE DIFFERENTIAL SIGNALING (LVDS) INPUT AND OUTPUT (EIA-644) |                                                                                                 |      |               |                     |                |

| Data Format                                                          | Serial LVDS data output                                                                         |      |               | Twos complement     |                |

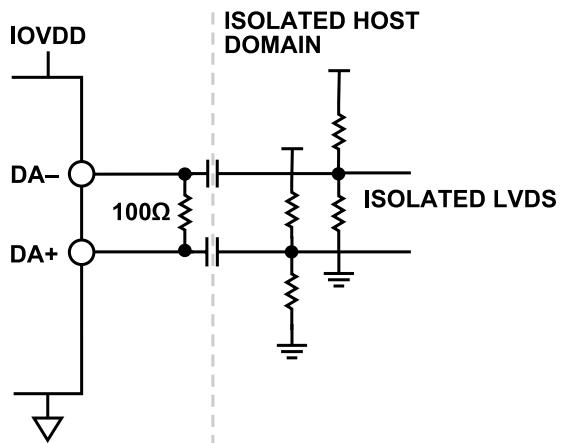

| LVDS Inputs (CLK $\pm$ and CNV $\pm$ )                               | IOVDD supply domain inputs                                                                      |      |               |                     |                |

| Common-Mode Input Voltage ( $V_{ICM}$ )                              | Default setting                                                                                 | 700  |               | 1400                | mV             |

| Differential Input Voltage ( $V_{IDIFF}$ )                           | Default setting                                                                                 | 100  |               | 600                 | mV             |

| LVDS Outputs (DCO $\pm$ , DA $\pm$ , and DB $\pm$ )                  | IOVDD supply domain outputs, differential termination, load resistance ( $R_L$ ) = 100 $\Omega$ |      |               |                     |                |

| Common-Mode Output Voltage ( $V_{OCM}$ )                             | LVDS_VOD = 001b                                                                                 | 915  | 927           | 935                 | mV             |

| LVDS_VOD = 010b (default)                                            |                                                                                                 | 840  | 851           | 860                 | mV             |

| LVDS_VOD = 100b                                                      |                                                                                                 | 695  | 706           | 715                 | mV             |

| Differential Output Voltage ( $V_{ODIFF}$ )                          | LVDS_VOD = 001b                                                                                 | 370  | 382           | 430                 | mV             |

| LVDS_VOD = 010b (default)                                            |                                                                                                 | 500  | 510           | 570                 | mV             |

| LVDS_VOD = 100b                                                      |                                                                                                 | 735  | 745           | 840                 | mV             |

| DIGITAL INPUTS (CNV, CS, SCLK, and SDI)                              | VDD11 supply domain inputs                                                                      |      |               |                     |                |

| Input Voltage Tolerance                                              |                                                                                                 | 0    |               | 2.5                 |                |

| Logic Levels                                                         |                                                                                                 |      |               |                     |                |

| Input Low Voltage ( $V_{IL}$ )                                       |                                                                                                 | 0    |               | 0.36 $\times$ VDD11 |                |

| Input High Voltage ( $V_{IH}$ )                                      |                                                                                                 | 0.92 |               | 2.5                 |                |

| DIGITAL INPUTS (GPIOx, DCS, and DCLK)                                | IOVDD supply domain inputs                                                                      |      |               |                     |                |

| Input Voltage Tolerance                                              |                                                                                                 | 0    |               | 1.26                | V              |

| Logic Levels                                                         |                                                                                                 |      |               |                     |                |

| $V_{IL}$                                                             |                                                                                                 | 0    |               | 0.36 $\times$ IOVDD | V              |

| $V_{IH}$                                                             |                                                                                                 | 0.92 |               | IOVDD               | V              |

| Input Current                                                        |                                                                                                 |      |               |                     |                |

| Input Low Current ( $I_{IL}$ )                                       |                                                                                                 | -1   |               | +1                  | $\mu A$        |

| Input High Current ( $I_{IH}$ )                                      |                                                                                                 | -1   |               | +1                  | $\mu A$        |

| Input Pin Capacitance                                                |                                                                                                 |      | 4.5           |                     | pF             |

| DIGITAL OUTPUTS (GPIOx)                                              | IOVDD supply domain outputs                                                                     |      |               |                     |                |

| Logic Levels                                                         |                                                                                                 |      |               |                     |                |

| Output Low Voltage ( $V_{OL}$ )                                      | Sink current ( $I_{SINK}$ ) = 500 $\mu A$                                                       | 0    |               | 0.15                | V              |

| Output High Voltage ( $V_{OH}$ )                                     | Source current ( $I_{SOURCE}$ ) = 500 $\mu A$                                                   |      | IOVDD - 0.115 | IOVDD               | V              |

| DIGITAL OUTPUTS (SDOx)                                               | IOVDD supply domain outputs. Configured as serial data output                                   |      |               | Twos complement     |                |

| Data Format                                                          |                                                                                                 |      |               |                     |                |

| Logic Levels                                                         |                                                                                                 |      |               |                     |                |

| $V_{OL}$                                                             | $I_{SINK} = 500\mu A$                                                                           | 0    |               | 0.15                | V              |

| $V_{OH}$                                                             | $I_{SOURCE} = 500\mu A$                                                                         |      | IOVDD - 0.115 | IOVDD               | V              |

## SPECIFICATIONS

Table 1. Specifications (Continued)

| Parameter             | Test Conditions/Comments                    | Min   | Typ  | Max   | Unit |

|-----------------------|---------------------------------------------|-------|------|-------|------|

| POWER SUPPLIES        |                                             |       |      |       |      |

| VDD33                 |                                             | 3.135 | 3.30 | 3.465 | V    |

| VDDLDO                |                                             | 1.4   |      | 2.7   | V    |

| VDD11                 | Applied externally, LDO disabled            | 1.045 | 1.10 | 1.155 | V    |

| IOVDD                 | Applied externally, LDO disabled            | 1.045 | 1.10 | 1.26  | V    |

| Operating Current     | LVDS_CNV_EN = 0                             |       |      |       |      |

| Static                | Converter and interface idle, FIFO disabled |       |      |       |      |

| VDD33                 |                                             | 5.93  | 7.4  |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 16.4  | 23   |       | mA   |

| IOVDD                 |                                             | 5.42  | 6    |       | mA   |

| VDDLDO                | VDD11 LDO enabled                           | 21.3  | 26.9 |       | mA   |

| Dynamic               | DC input signal                             |       |      |       |      |

| VDD33                 |                                             | 11.5  | 13.2 |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 21.1  | 27.5 |       | mA   |

| IOVDD                 |                                             | 8.5   | 10.1 |       | mA   |

| VDDLDO                | VDD11 LDO enabled                           | 27.6  | 35.5 |       | mA   |

| Dynamic               | -0.5dBFS sine-wave input signal             |       |      |       |      |

| VDD33                 |                                             | 10.6  | 12.3 |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 21    | 28   |       | mA   |

| IOVDD                 |                                             | 9.0   | 9.8  |       | mA   |

| VDDLDO                | VDD11 LDO enabled                           | 28    | 34.5 |       | mA   |

| Standby Mode          | LVDS_SELF_CLK_MODE disabled                 |       |      |       |      |

| VDD33                 |                                             | 1.4   | 1.9  |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 1.7   | 4.9  |       | mA   |

| IOVDD                 |                                             | 60    | 365  |       | µA   |

| VDDLDO                | VDD11 LDO enabled                           | 1.7   | 4.8  |       | mA   |

| Sleep Mode            | LVDS_SELF_CLK_MODE disabled                 |       |      |       |      |

| VDD33                 |                                             | 0.6   | 0.9  |       | mA   |

| VDDLDO                | VDD11 LDO disabled                          | 0     | 0.02 |       | mA   |

| VDD11                 |                                             | 1.3   | 4.5  |       | mA   |

| IOVDD                 |                                             | 60    | 370  |       | µA   |

| VDDLDO                | VDD11 LDO enabled                           | 1.3   | 4.5  |       | mA   |

| Power Dissipation     |                                             |       |      |       |      |

| Static                | VDD11 LDO disabled                          | 43.6  | 59.4 |       | mW   |

| Dynamic               | DC input signal                             | 70.5  | 90.2 |       | mW   |

| Dynamic               | -0.5dBFS sine-wave input signal             | 68    | 87.3 |       | mW   |

| Standby Mode          | VDD11 LDO disabled                          | 6.6   | 12.7 |       | mW   |

| Sleep Mode            | VDD11 LDO disabled                          | 3.5   | 8.8  |       | mW   |

| TEMPERATURE RANGE     |                                             |       |      |       |      |

| Specified Performance | T <sub>MIN</sub> to T <sub>MAX</sub>        | -40   |      | +85   | °C   |

## SPECIFICATIONS

## TIMING SPECIFICATIONS

VDD33 = 3.3V  $\pm$  5%, VDDLDO = 1.5V to 2.7V, VDD11 = 1.1V  $\pm$  5%, IOVDD = 1.1V – 5% to 1.2V + 5%, V<sub>REFIN</sub> = 3.0V, f<sub>S</sub> = 20MHz, and T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.

Table 2. Timing Specifications

| Parameter                                                        | Symbol               | Min                            | Typ                                                                          | Max                                  | Unit                          |

|------------------------------------------------------------------|----------------------|--------------------------------|------------------------------------------------------------------------------|--------------------------------------|-------------------------------|

| Sampling Frequency                                               | f <sub>S</sub>       | 1.25                           |                                                                              | 20                                   | MHz                           |

| Conversion Time                                                  | t <sub>CONV</sub>    | 50                             |                                                                              | 800                                  | ns                            |

| Acquisition Phase                                                | t <sub>ACQ</sub>     | t <sub>CYC</sub>               |                                                                              |                                      | ns                            |

| Conversion Cycle Period                                          | t <sub>CYC</sub>     | t <sub>CONV</sub>              |                                                                              |                                      | ns                            |

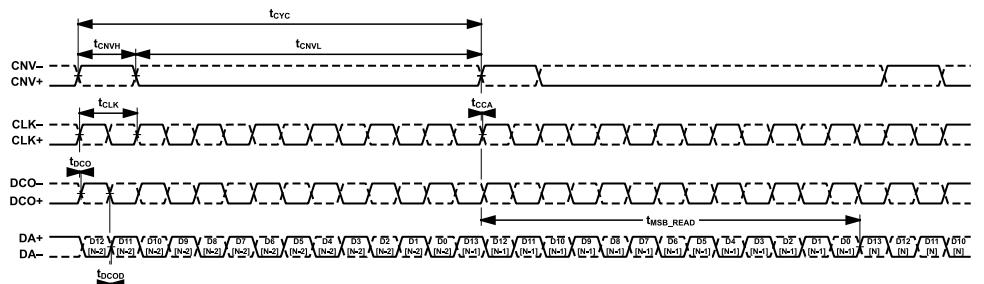

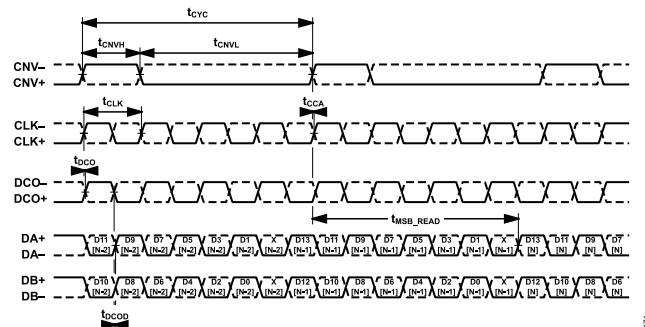

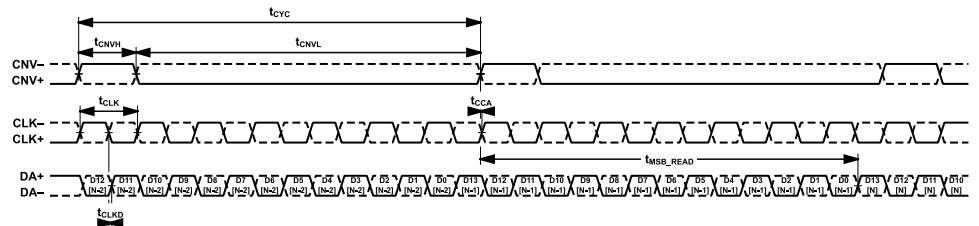

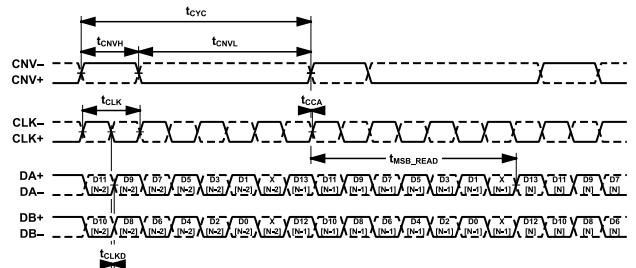

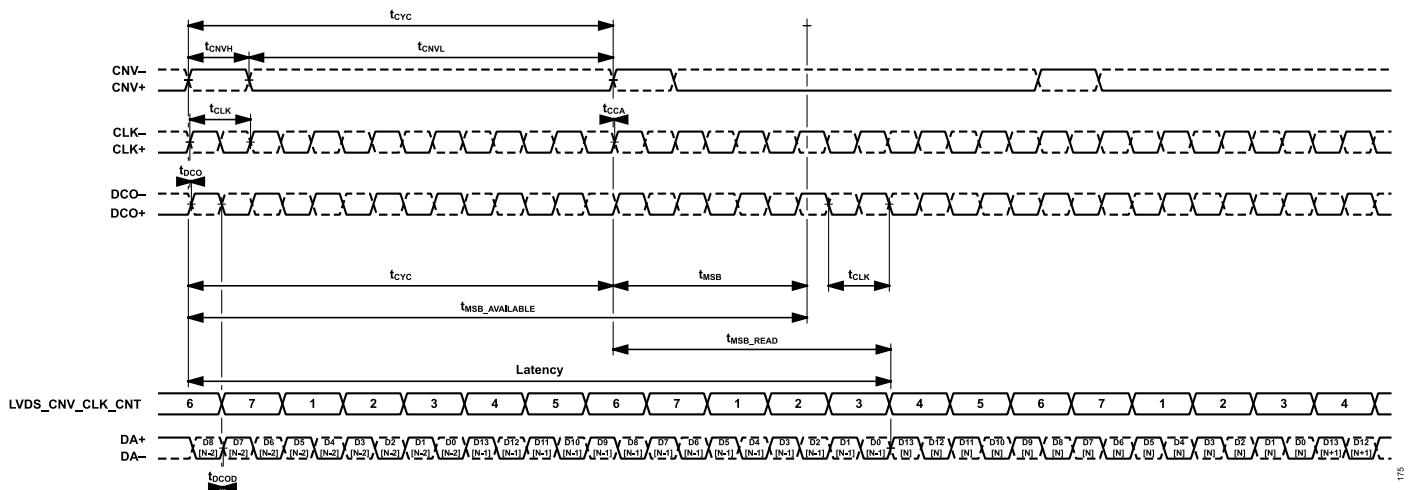

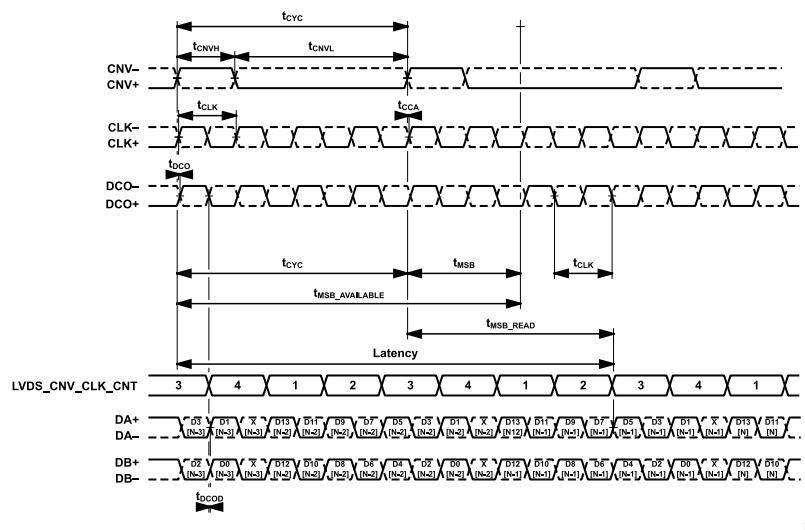

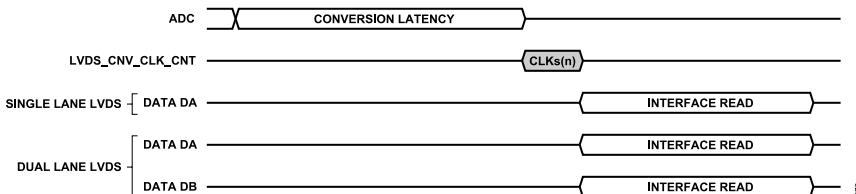

| LVDS Data Interface                                              |                      |                                |                                                                              |                                      |                               |

| Data Interface Clock Count                                       | N                    |                                |                                                                              | 7                                    |                               |

| Active Data Lane Count                                           | L                    |                                |                                                                              | 2                                    |                               |

| CNV $\pm$ High Time                                              | t <sub>CNVH</sub>    | t <sub>CLK</sub>               | 4 $\times$ t <sub>CLK</sub>                                                  | t <sub>CYC</sub> – t <sub>CNVL</sub> | ns                            |

| CNV $\pm$ Low Time                                               | t <sub>CNVL</sub>    | t <sub>CLK</sub>               | 4 $\times$ t <sub>CLK</sub>                                                  | t <sub>CYC</sub> – t <sub>CNVH</sub> | ns                            |

| CNV $\pm$ Edge to CLK $\pm$ Rising Edge Alignment                | t <sub>CCA</sub>     |                                |                                                                              | 535                                  | ps                            |

| CNV $\pm$ to Dx $\pm$ (MSB) Ready                                | t <sub>MSB</sub>     |                                |                                                                              |                                      |                               |

| Gain Error Correction Enabled                                    |                      |                                | 20.5                                                                         | 22.4                                 | ns                            |

| Gain Error Correction Disabled                                   |                      |                                | 15.7                                                                         | 18                                   | ns                            |

| CLK $\pm$ Period                                                 | t <sub>CLK</sub>     | 7.142                          |                                                                              |                                      | t <sub>CYC</sub> $\times$ L/N |

| CLK $\pm$ Frequency                                              | f <sub>CLK</sub>     |                                | 1/t <sub>CLK</sub>                                                           | 140                                  | MHz                           |

| CLK $\pm$ to Dx $\pm$ Delay                                      | t <sub>CLKD</sub>    | 1                              |                                                                              | 2.1                                  | ns                            |

| CLK $\pm$ to DCO $\pm$ Delay (Echo Clock Mode)                   | t <sub>DCO</sub>     | 1                              |                                                                              | 2                                    | ns                            |

| DCO $\pm$ to Dx $\pm$ Delay (Echo Clock Mode)                    | t <sub>DCOD</sub>    | 0.02                           |                                                                              | 1                                    | ns                            |

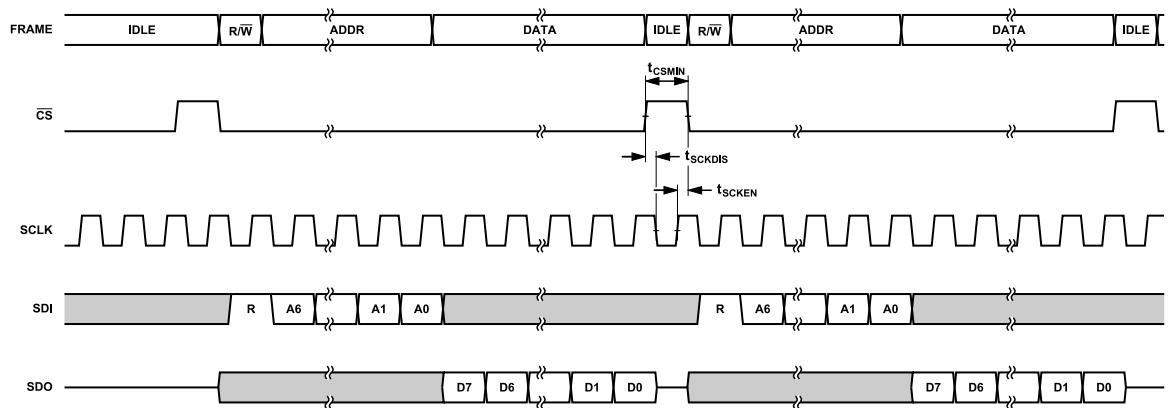

| Serial Peripheral Interface (SPI) Data Interface                 |                      |                                |                                                                              |                                      |                               |

| Data Interface Clock Count, Single Conversion Result             | M                    |                                |                                                                              | 24                                   |                               |

| Active Data Lane Count                                           | C                    |                                | 1                                                                            | 4                                    |                               |

| Data Interface Chip Select Falling Edge (DCS) to SDOB Data Valid | t <sub>DEN</sub>     | 5                              | 6                                                                            |                                      | ns                            |

| Data Interface Clock Period (DCLK)                               | t <sub>DCK</sub>     | 20                             |                                                                              |                                      | ns                            |

| Data Interface Clock Low Pulse Width (DCLK)                      | t <sub>DCKL</sub>    | t <sub>DCK</sub> $\times$ 0.45 |                                                                              |                                      | ns                            |

| Data Interface Clock High Pulse Width (DCLK)                     | t <sub>DCLKH</sub>   | t <sub>DCK</sub> $\times$ 0.45 |                                                                              |                                      | ns                            |

| Data Interface Clock Falling Edge to Data Remains Valid Delay    | t <sub>DHSDO</sub>   | 5                              |                                                                              |                                      | ns                            |

| Data Interface Clock Falling Edge to Data Valid Delay            | t <sub>DDSDO</sub>   |                                |                                                                              | 9.6                                  | ns                            |

| DCLK Rising to Data Interface Chip Select Falling                | t <sub>DCKEN</sub>   | 0                              |                                                                              |                                      | ns                            |

| Data Interface Chip Select High to DCLK Disabled                 | t <sub>DCLKDIS</sub> | 0                              |                                                                              |                                      | ns                            |

| Data Interface Chip Select High Between Frames                   | t <sub>DCSMIN</sub>  |                                | (t <sub>DCKEN</sub> + t <sub>DCLKDIS</sub> ) + 0.5 $\times$ t <sub>CLK</sub> |                                      | ns                            |

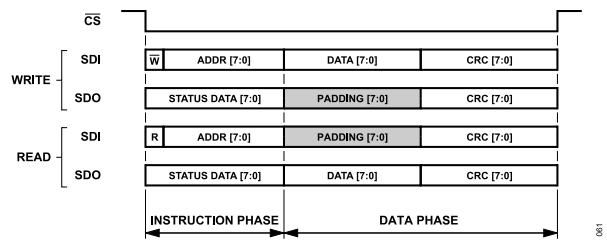

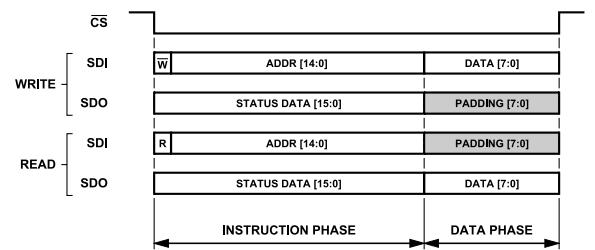

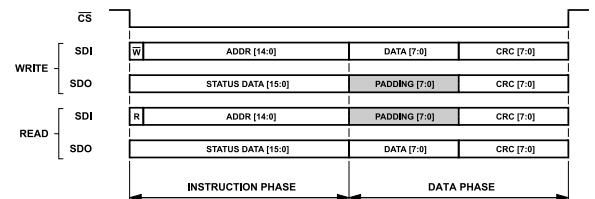

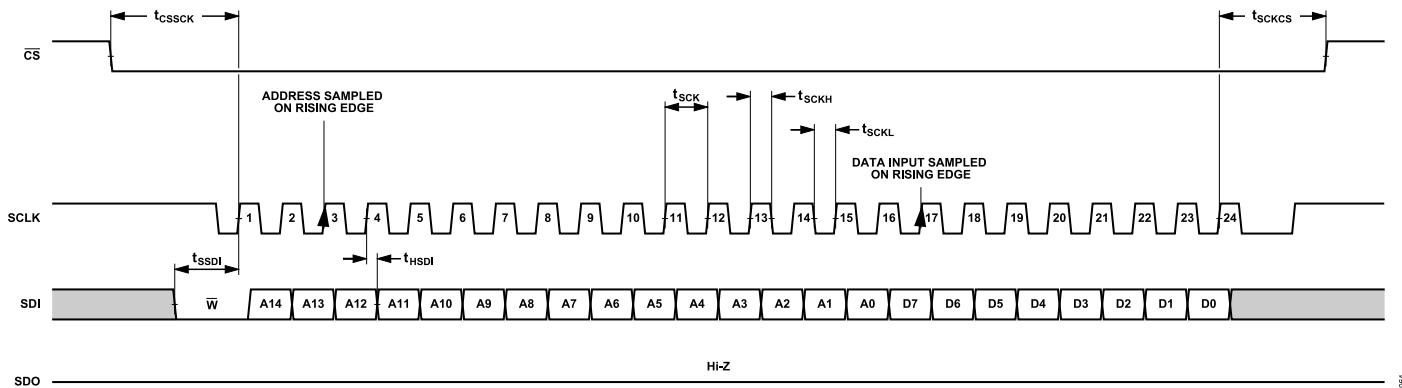

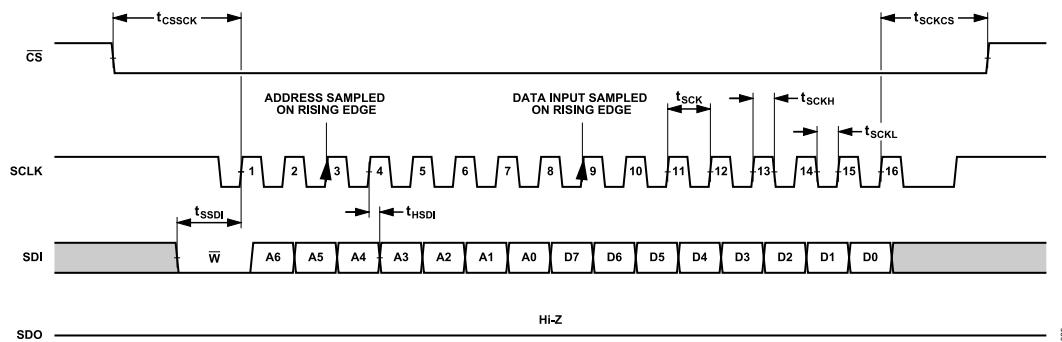

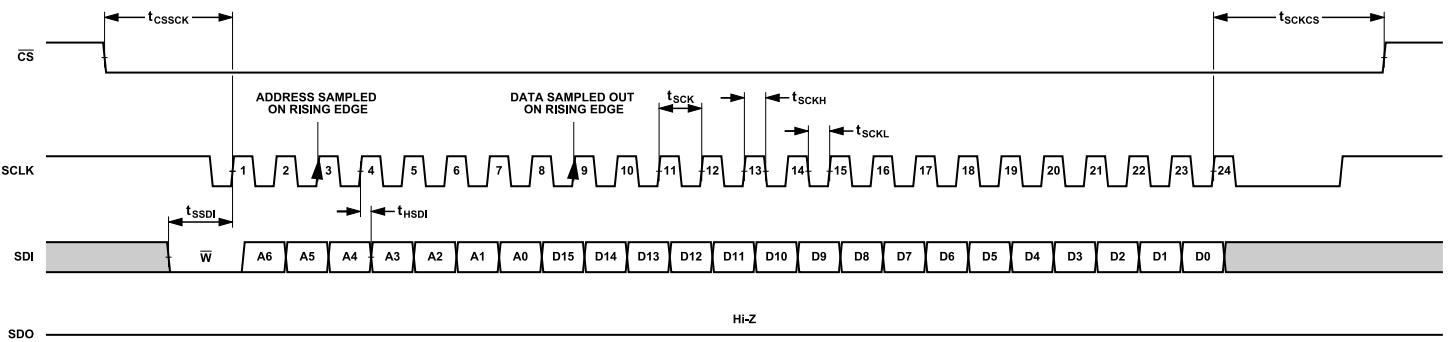

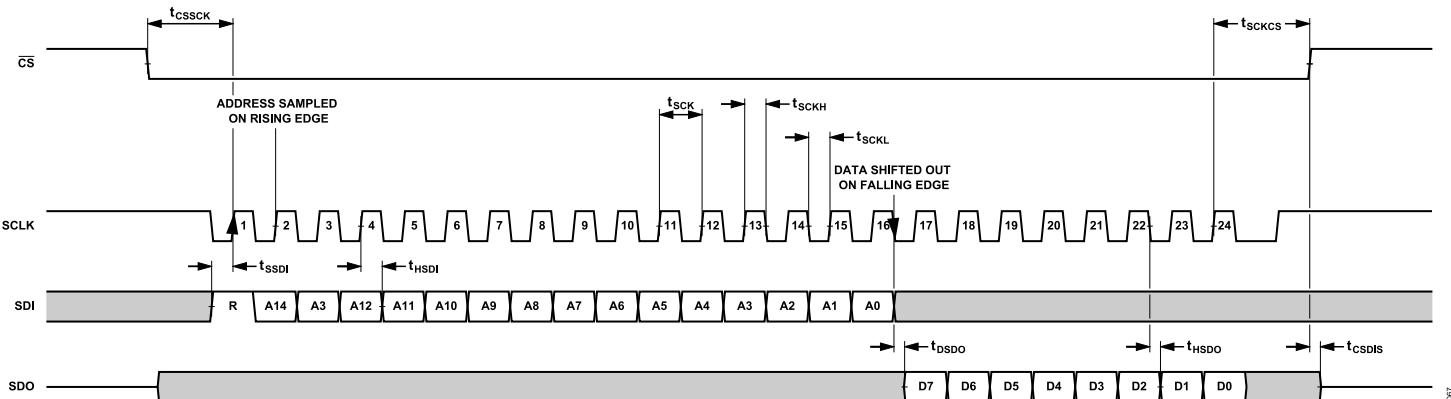

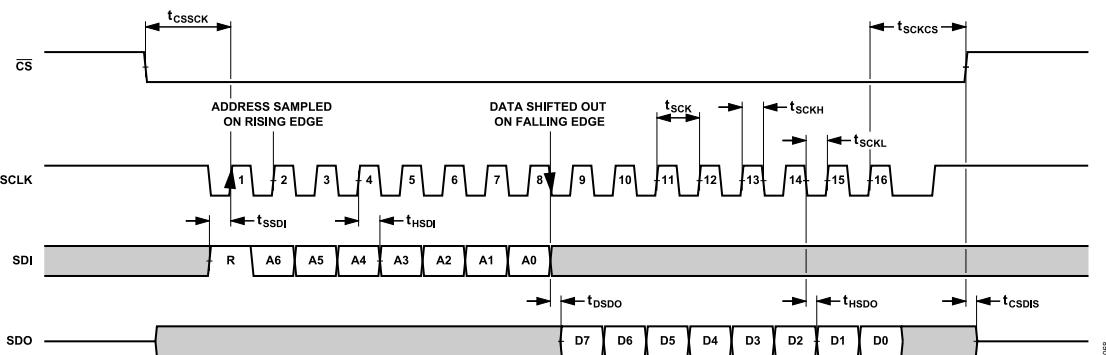

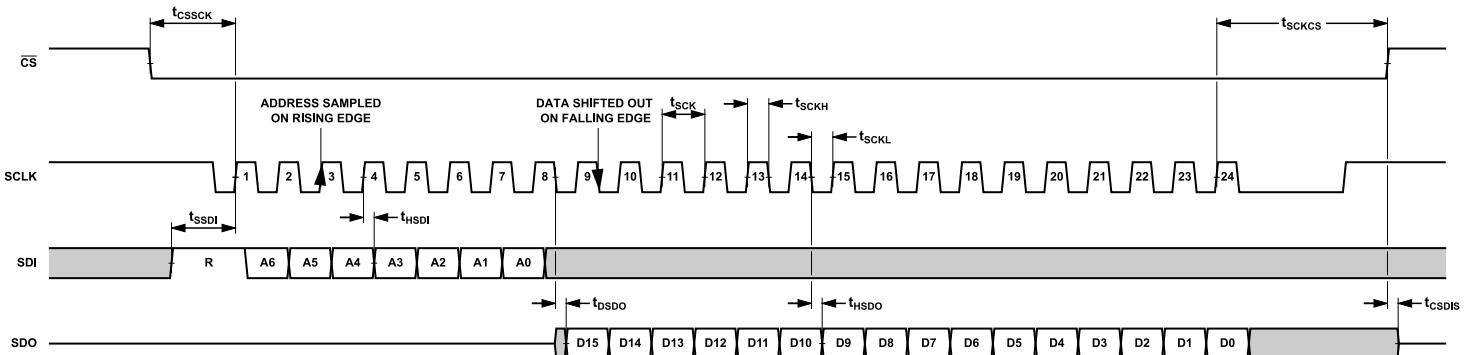

| Serial Configuration Interface                                   |                      |                                |                                                                              |                                      |                               |

| SCLK Period                                                      | t <sub>SCK</sub>     | 20                             |                                                                              |                                      | ns                            |

| SCLK Low Pulse Width                                             | t <sub>SCKL</sub>    | t <sub>SCK</sub> $\times$ 0.45 |                                                                              |                                      | ns                            |

| SCLK High Pulse Width                                            | t <sub>SCKH</sub>    | t <sub>SCK</sub> $\times$ 0.45 |                                                                              |                                      | ns                            |

| SCLK Falling Edge to Data Remains Valid Delay                    | t <sub>HSDO</sub>    | 0.7                            |                                                                              |                                      | ns                            |

| SCLK Falling Edge to Data Valid Delay                            | t <sub>DSDO</sub>    |                                |                                                                              | 14.5                                 | ns                            |

| CS Falling Edge to SCLK                                          | t <sub>SSCK</sub>    | 0                              |                                                                              |                                      | ns                            |

| Last SCLK to CS Rising                                           | t <sub>SCKCS</sub>   | 0                              |                                                                              |                                      | ns                            |

| SDI Valid Setup Time Before SCLK Rising Edge                     | t <sub>SSDI</sub>    | 1                              |                                                                              |                                      | ns                            |

| SDI Valid Hold Time After SCLK Rising Edge                       | t <sub>HSDI</sub>    | 0                              |                                                                              |                                      | ns                            |

| SCLK Rising to Data Interface Chip Select Falling                | t <sub>SCKEN</sub>   | 0                              |                                                                              |                                      | ns                            |

## SPECIFICATIONS

Table 2. Timing Specifications (Continued)

| Parameter                                               | Symbol          | Min                | Typ                                             | Max                | Unit |

|---------------------------------------------------------|-----------------|--------------------|-------------------------------------------------|--------------------|------|

| Data Interface Chip Select High to SCLK Disabled        | $t_{SCKDIS}$    | 0                  |                                                 |                    | ns   |

| Data Interface Chip Select High to SDO Disabled         | $t_{CSDIS}$     |                    |                                                 | 10.3               | ns   |

| Data Interface Chip Select High Between Frames          | $t_{CSMIN}$     |                    | $(t_{SCKEN} + t_{SCKDIS}) + 0.5 \times t_{SCK}$ |                    | ns   |

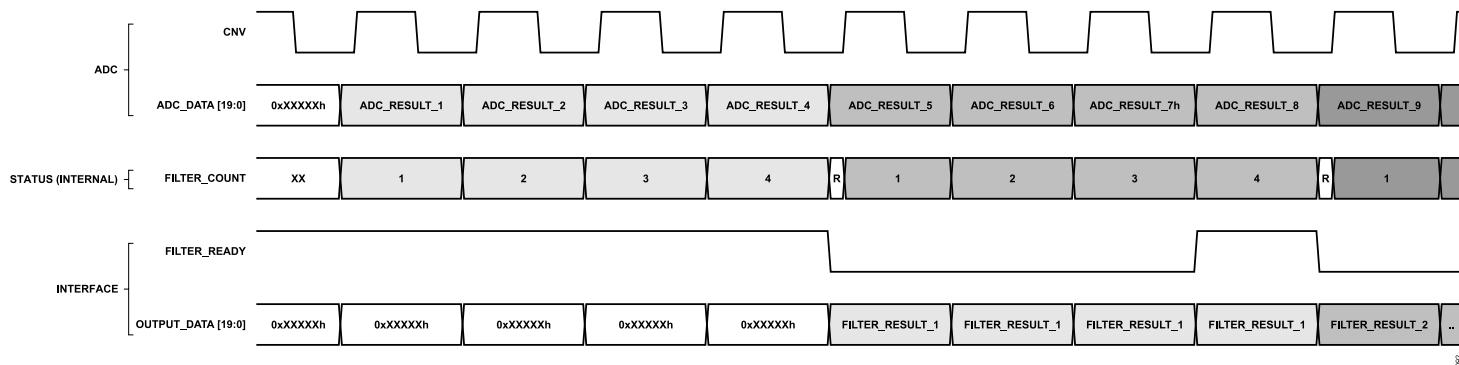

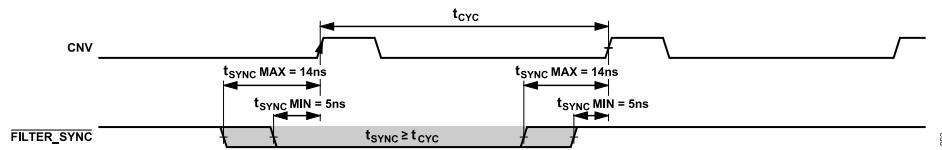

| Digital Filter                                          |                 |                    |                                                 |                    |      |

| $\overline{FILT\_SYNC}$ Rising Edge to CNV Rising Edge  | $t_{SYNC\ MAX}$ |                    | $t_{CYC} - 5$                                   |                    | ns   |

| CNV Rising Edge to $\overline{FILT\_SYNC}$ Falling Edge | $t_{SYNC\ MIN}$ |                    | 3                                               |                    | ns   |

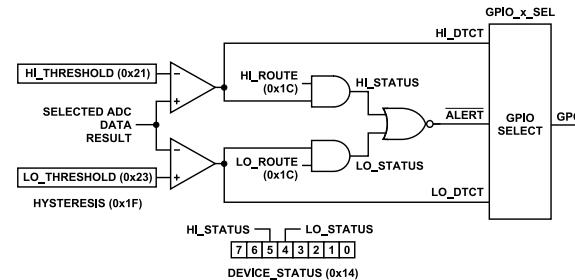

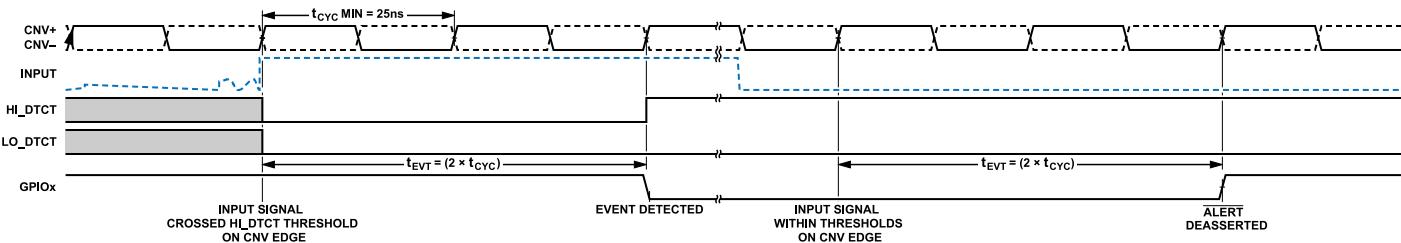

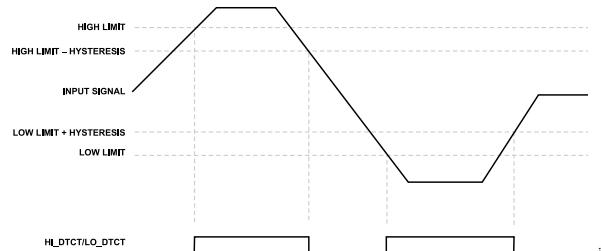

| Event Detection                                         |                 |                    |                                                 |                    |      |

| Input Threshold Crossed to $\overline{ALERT}$ Asserted  | $t_{EVT}$       | $2 \times t_{CYC}$ |                                                 | $3 \times t_{CYC}$ |      |

## ABSOLUTE MAXIMUM RATINGS

Table 3. Absolute Maximum Ratings

| Parameter                                                              | Rating          |

|------------------------------------------------------------------------|-----------------|

| Analog Inputs<br>IN+, AUXIN+, IN-, and AUXIN- to GND                   | -0.3V to +3.6V  |

| Analog Output<br>CMO                                                   | -0.3V to +3.6V  |

| Supply Voltage<br>REFIN and VDD33 to GND                               | -0.3V to +3.6V  |

| VDDLDO to GND                                                          | -0.3V to +2.75V |

| VDD11 to GND                                                           | -0.3V to +1.26V |

| IOVDD to GND                                                           | -0.3V to +1.26V |

| Digital Inputs and Outputs<br>Inputs (CNV $\pm$ and CLK $\pm$ ) to GND | -0.3V to +2.75V |

| LVDS OUTPUT (DCO $\pm$ , DA $\pm$ , and DB $\pm$ ) to GND              | -0.3V to +1.26V |

| $\overline{CS}$ , SCLK, and SDI to GND                                 | -0.3V to +2.75V |

| GPIO0, GPIO1, GPIO2, and GPIO3 to GND                                  | -0.3V to +1.26V |

| Temperature<br>Storage Range                                           | -55°C to +150°C |

| Operating Range                                                        | -40°C to +85°C  |

| Maximum Reflow (Package) as per JEDEC J-STD-020                        | 260°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

Table 4. Thermal Resistance

| Package | Type | $\theta_{JA}$ <sup>1</sup> | $\Psi_{JT}$ <sup>1</sup> | $\Psi_{JB}$ <sup>1</sup> | $\theta_{JB}$ <sup>2</sup> | $\theta_{JC}$ <sup>3</sup> | Unit |

|---------|------|----------------------------|--------------------------|--------------------------|----------------------------|----------------------------|------|

| BC-49-8 |      | 66.8                       | 1.7                      | 45.1                     | 45.9                       | 53.1                       | °C/W |

<sup>1</sup>  $\theta_{JA}$ ,  $\Psi_{JT}$ , and  $\Psi_{JB}$  are modeled using a JEDEC 2S2P test PCB with 16 thermal vias, in a JEDEC natural convection environment.

<sup>2</sup>  $\theta_{JB}$  is modeled using a JEDEC 2S2P test PCB with 16 thermal vias, in a JEDEC junction to board environment.

<sup>3</sup>  $\theta_{JC}$  is modeled using a JEDEC 1S test PCB, with an infinite heatsink attached directly to the package surface.

## ELECTROSTATIC DISCHARGE (ESD) RATINGS

The following ESD information is provided for handling of ESD-sensitive devices in an ESD-protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Field induced charged-device model (FICDM) per ANSI/ESDA/JEDEC JS-002.

## ESD Ratings for the AD4087

Table 5. AD4087, 49-Ball CSP\_BGA

| ESD Model                                                                             | Withstand Threshold (V) | Class |

|---------------------------------------------------------------------------------------|-------------------------|-------|

| HBM (Pin E1, Pin E2, Pin D1, and Pin D2 (IN-, AUXIN-, IN+, and AUXIN+, respectively)) | 1000                    | 1C    |

| HBM (All other pins)                                                                  | 1500                    | 1C    |

| FICDM                                                                                 | 750                     | C2b   |

## ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

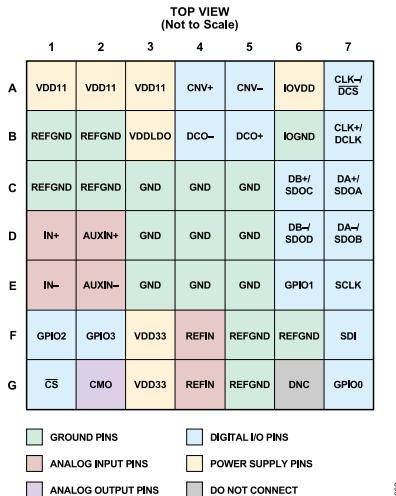

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

Table 6. Pin Function Descriptions

| Pin No.                    | Mnemonic   | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

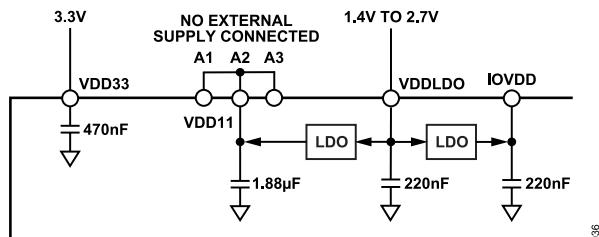

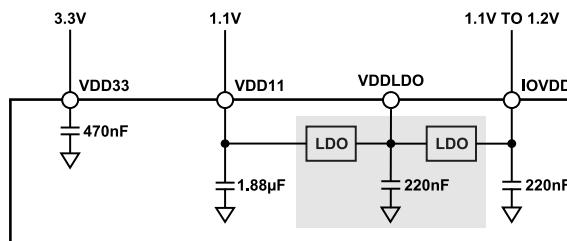

| A1, A2, A3                 | VDD11      | P                 | 1.1V ADC Core Supplies. These supply pins are internally decoupled by four 470nF capacitors to GND. When power is supplied to VDDLDO (B3), an internal LDO voltage regulator produces the 1.1V required at these pins. The voltage regulator is automatically powered on when VDDLDO is greater than 1.4V. If VDDLDO is left disconnected, the required 1.1V must be supplied to these pins from an external source.                                                                                                                                                                                                                                                      |

| A4, A5                     | CNV+, CNV- | DI                | Convert Start Inputs. This pin pair serves as the conversion control input. A conversion is initiated on the rising edge of the convert signal. These inputs are, by default, configured in complementary metal-oxide semiconductor (CMOS) mode, in which CNV- must be tied to IOGND, and the convert signal is applied to CNV+. In the LVDS data interface mode, the convert start input can be optionally configured in LVDS mode, in which case, the convert signal is applied differentially to CNV+ and CNV- and an external 100Ω termination resistor must be placed across these pins. See the <a href="#">ADC Conversion Control</a> section for further details. |

| A6                         | IOVDD      | P                 | 1.1V Digital Interface Supply Rail. This supply is internally decoupled by a 220nF capacitor to IOGND. When power is supplied to VDDLDO (B3), an internal LDO voltage regulator produces the 1.1V required at this pin. The voltage regulator is automatically powered on when VDDLDO is greater than 1.5V. If VDDLDO is left disconnected, the required 1.1V must be supplied to this pin from an external source (typically the host controller interface supply).                                                                                                                                                                                                      |

| A7                         | CLK-/DCS   | DI                | Data Interface Clock Input (CLK-)/Data Interface Chip Select (DCS) Multifunction Pin. In LVDS data interface mode (default), this pin serves as half of the differential data clock input, and an external 100Ω termination resistor must be present between it and the CLK+ pin. In SPI data interface mode, this pin functions as a chip select input (data interface chip select).                                                                                                                                                                                                                                                                                     |

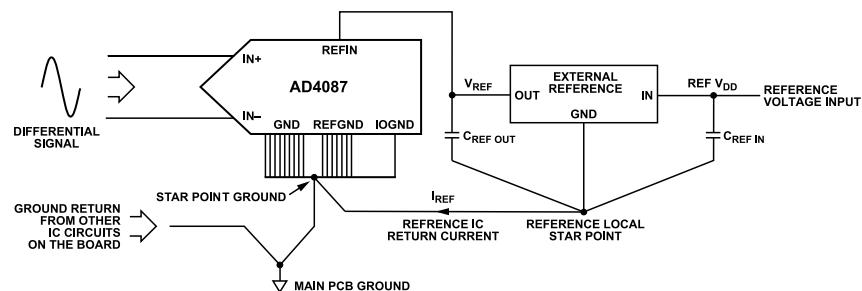

| B1, B2, C1, C2, F5, F6, G5 | REFGND     | P                 | Reference Grounds. Connect any external reference decoupling capacitors across REFIN and REFGND. REFGND must be tied with a low impedance path to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B3                         | VDDLDO     | P                 | LDO Supply Rail Input. This supply rail is internally decoupled by a 220nF capacitor to GND. The two internal 1.1V LDO voltage regulators can be supplied from a source connected to this input in the 1.5V to 2.7V range. If this pin is left open, the internal regulators automatically                                                                                                                                                                                                                                                                                                                                                                                |

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 6. Pin Function Descriptions (Continued)

| Pin No.                      | Mnemonic   | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B4, B5                       | DCO-, DCO+ | DO                | power off, and both VDD11 and IOVDD must be connected with an external voltage source within their allowed specification limits.<br>If VDDLDO is connected to a voltage source, neither VDD11 nor IOVDD should be connected to any external voltage source.<br>LVDS Echo Clock Outputs.<br>In LVDS data interface mode (default), this pin pair outputs a buffered and delayed version of CLK+ and CLK-. Data outputs from LVDS Data Lane DA+ and Data Lane DA- (and Data Lane DB+ and Data Lane DB- if active) are clocked out in alignment with both rising and falling edges of DCO+ and DCO-. In SPI data interface mode (or if the echo clock mode is disabled while in LVDS data interface mode), these pins can be left unconnected. |

| B6                           | IOGND      | P                 | Digital Interface Supply Ground Reference. This pin must be connected to the same ground plane as all other GND pins.<br>All pins specified as type DI, DO, or DI/O must use this ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B7                           | CLK+/DCLK  | DI                | Data Interface Clock Input Multifunction Pin.<br>In LVDS data interface mode (default), this pin serves as half of the differential data clock input, and an external 100Ω termination resistor must be present between it and the CLK- pin.<br>In SPI data interface mode, the single-ended data clock signal must be applied to this pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

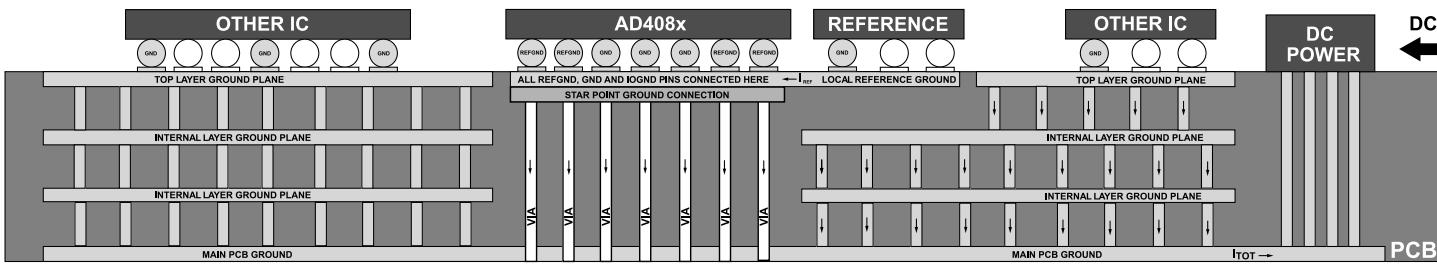

| C3 to C5, D3 to D5, E3 to E5 | GND        | P                 | Grounds. All ground pins must be connected to a PCB GND plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C6                           | DB+/SDOC   | DO                | Data Interface Output Multifunction Pin.<br>In LVDS data interface mode (default), this output pin along with DB- serves as the optional, secondary LVDS Data Lane B. If unused, leave unconnected.<br>In SPI data interface mode, this pin functions as Serial Data Output C (SDOC), which is active in a four-lane configuration only. Result data is shifted out of this pin on the falling edge of the data interface clock (DCLK).<br>This pin must be left unconnected if not being used.                                                                                                                                                                                                                                             |

| C7                           | DA+/SDOA   | DO                | Data Interface Output Multifunction Pin.<br>In LVDS data interface mode (default), this output pin along with DA- serves as the primary LVDS Data Lane A.<br>In SPI data interface mode, this pin functions as Serial Data Output A (SDOA), which is active in a four-lane configuration only. Result data is shifted out of this pin on the falling edge of the data interface clock (DCLK).<br>This pin must be left unconnected if not being used.                                                                                                                                                                                                                                                                                       |

| D1                           | IN+        | AI                | Positive Analog Differential Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D2                           | AUXIN+     | AI                | Positive Auxiliary Analog Differential Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D6                           | DB-/SDOD   | DO                | Data Interface Output Multifunction Pin.<br>In LVDS data interface mode (default), this output pin along with DB+ serves as the optional, secondary LVDS Data Lane B. If unused, leave unconnected.<br>In SPI data interface mode, this pin functions as Serial Data Output D (SDOD), which is active in a four-lane configuration only. Result data is shifted out of this pin on the falling edge of the data interface clock (DCLK). Note that this pin does not go into a high-impedance state when used in four-lane SPI mode when CS is inactive.<br>This pin must be left unconnected if not being used.                                                                                                                             |

| D7                           | DA-/SDOB   | DO                | Data Interface Output.<br>In LVDS data interface mode (default), this output pin along with DA+ serves as the primary LVDS Data Lane A. If unused, leave unconnected.<br>In SPI data interface mode, this pin functions as Serial Data Output B (SDOB). This is the only active serial data output in single lane mode. Result data is shifted out of this pin on the falling edge of the data interface clock (DCLK).                                                                                                                                                                                                                                                                                                                      |

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 6. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic        | Type <sup>1</sup> | Description                                                                                                                                |

|---------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| E1      | IN-             | AI                | Negative Analog Differential Input.                                                                                                        |

| E2      | AUXIN-          | AI                | Negative Auxiliary Analog Differential Input.                                                                                              |

| E6      | GPIO1           | DI/O              | General-Purpose Input and Output 1 Pin.                                                                                                    |

| E7      | SCLK            | DI                | Configuration Interface Serial Data Clock. This clock input is used to shift data into and out of the device configuration memory.         |

| F1      | GPIO2           | DI/O              | General-Purpose Input and Output 2 Pin.                                                                                                    |

| F2      | GPIO3           | DI/O              | General-Purpose Input and Output 3 Pin.                                                                                                    |

| F3, G3  | VDD33           | P                 | 3.3V Supply Rail Inputs. These supply pins are internally decoupled by a 470nF capacitor to GND.                                           |

| F4, G4  | REFIN           | AI                | 3.0V Reference Voltage Inputs.                                                                                                             |

| F7      | SDI             | DI                | Serial Data Input. Configuration data is shifted into this input on the rising edge of the serial data clock, SCLK.                        |

| G1      | $\overline{CS}$ | DI                | Configuration Interface Chip Select Input (Active Low). The $\overline{CS}$ input frames serial data transfers over the configuration SPI. |

| G2      | CMO             | AO                | Common-Mode Voltage ( $V_{CM}$ ) Output.                                                                                                   |

| G6      | DNC             | DNC               | Do Not Connect.                                                                                                                            |

| G7      | GPIO0           | DI/O              | General-Purpose Input and Output 0 Pin. This is default configured as Configuration SPI SDO Data.                                          |

<sup>1</sup> AI is analog input, AO is analog output, DI is digital input, DI/O is digital input and output, DO is digital output, and P is power.

## TYPICAL PERFORMANCE CHARACTERISTICS

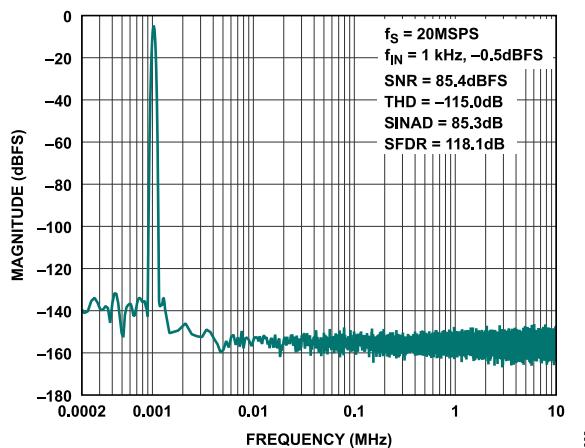

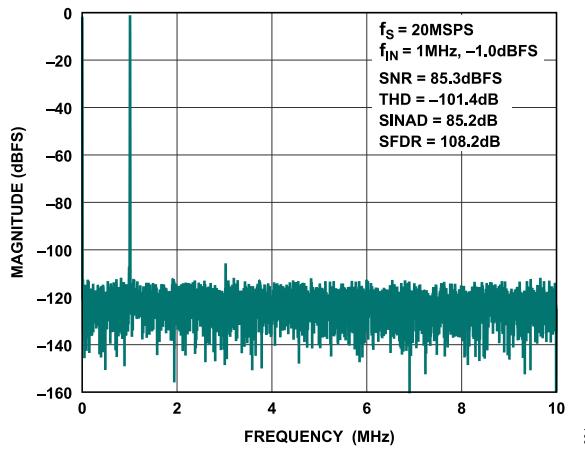

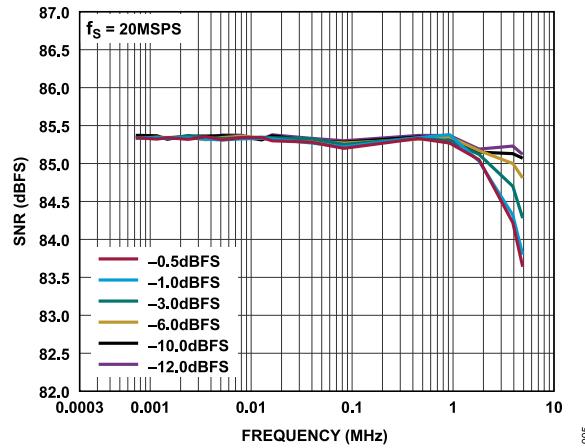

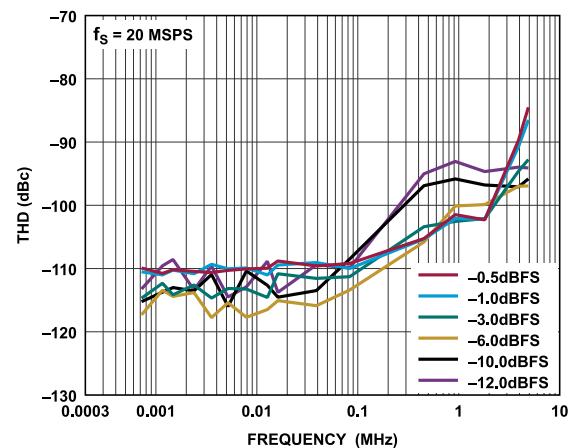

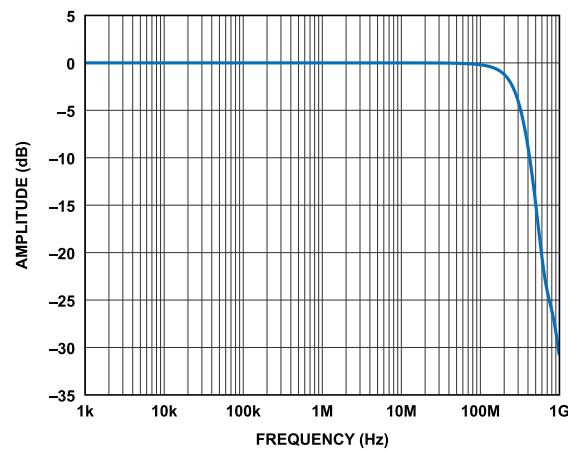

Figure 3. Fast Fourier Transform (FFT) 20MSPS,  $f_{IN} = 1\text{ kHz}$ ,  $-0.5\text{d BFS}$ Figure 4. FFT 20MSPS,  $f_{IN} = 1\text{ MHz}$ ,  $-1.0\text{d BFS}$ Figure 5. SNR vs. Input Signal Frequency (Amplitude =  $-0.5\text{d BFS}$ ,  $-1\text{d BFS}$ ,  $-3\text{d BFS}$ ,  $-6\text{d BFS}$ ,  $-10\text{d BFS}$ , and  $-12\text{d BFS}$ )Figure 6. THD vs. Input Signal Frequency (Amplitude =  $-0.5\text{d BFS}$ ,  $-1\text{d BFS}$ ,  $-3\text{d BFS}$ ,  $-6\text{d BFS}$ ,  $-10\text{d BFS}$ , and  $-12\text{d BFS}$ )Figure 7. Small Signal  $-3\text{dB}$  Bandwidth at 20MSPS

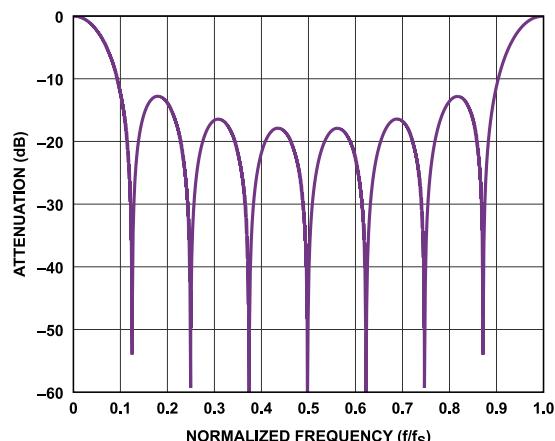

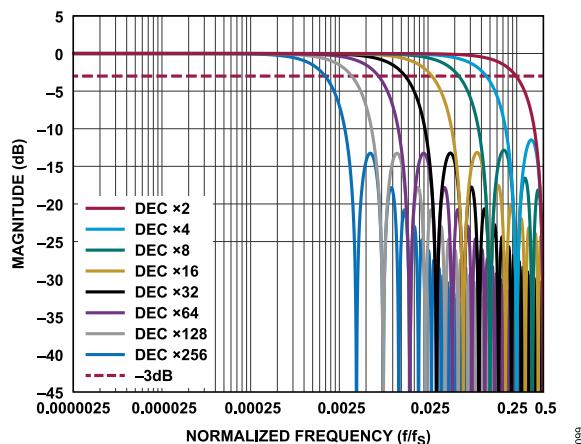

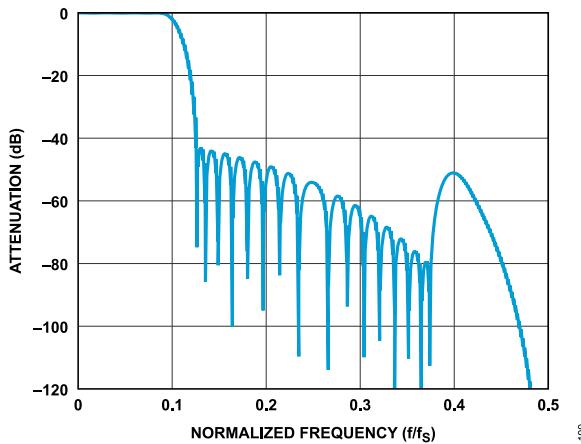

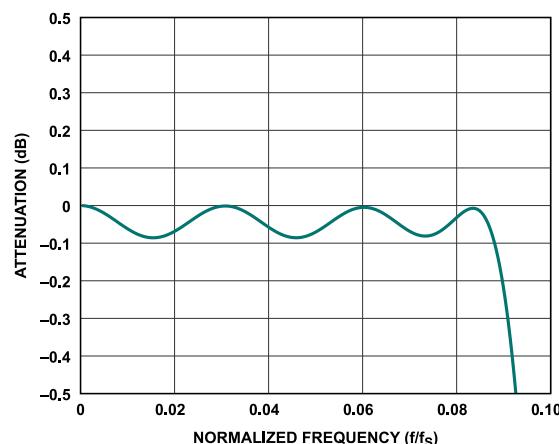

Figure 8. Sinc5 + Compensation Filter, Pass-Band Flatness

## TYPICAL PERFORMANCE CHARACTERISTICS

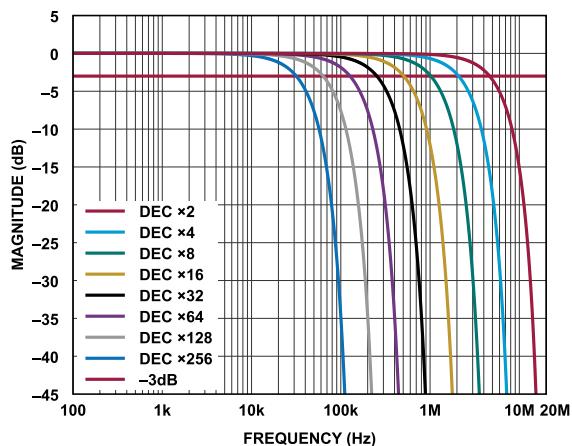

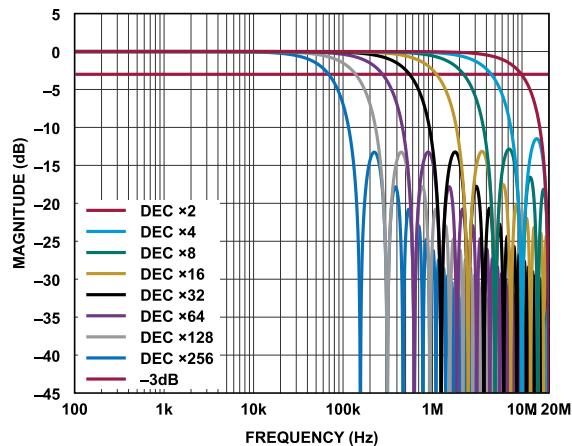

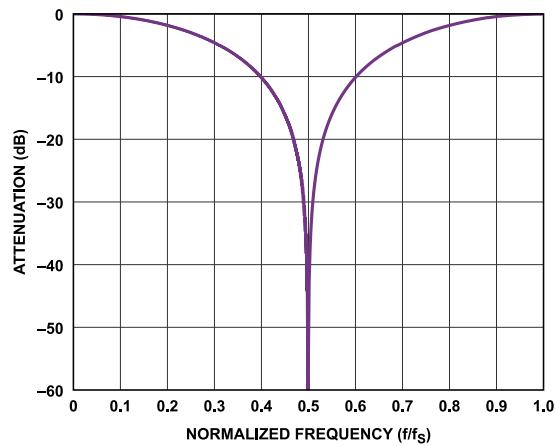

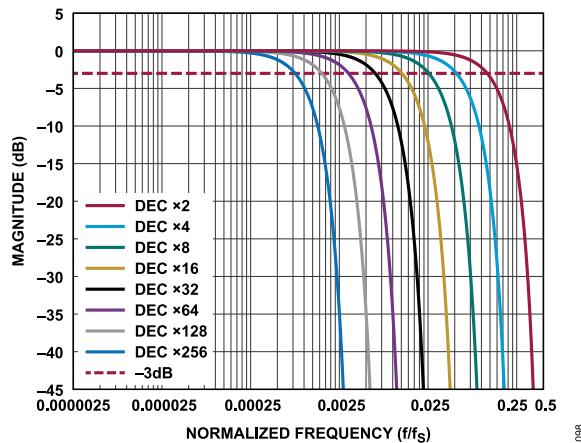

Figure 9. Sinc1 Filter Response,  $f_S = 20\text{MHz}$  (DEC  $\times$  Means Decimate By)

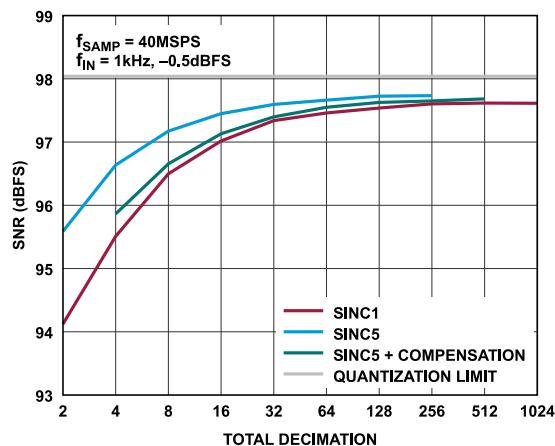

Figure 12. SNR vs. Total Decimation Factor

Figure 10. Sinc5 Filter Response,  $f_S = 20\text{MHz}$

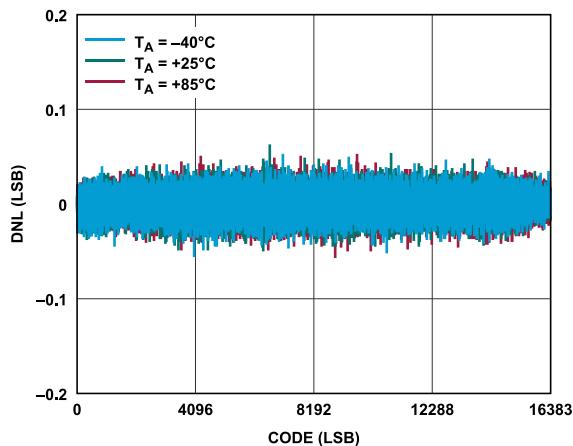

Figure 13. DNL vs. Code for Various Temperatures, 40MSPS

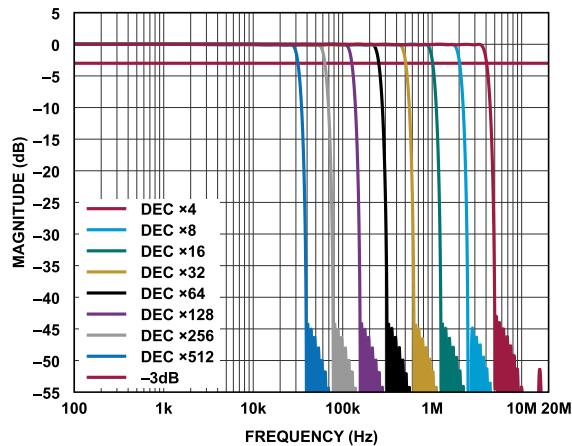

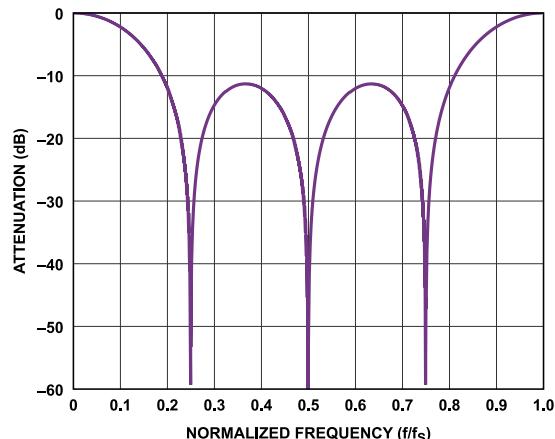

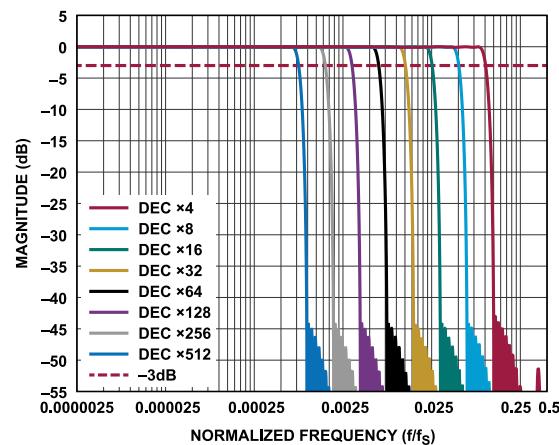

Figure 11. Sinc5 + Compensation Filter Response,  $f_S = 20\text{MHz}$

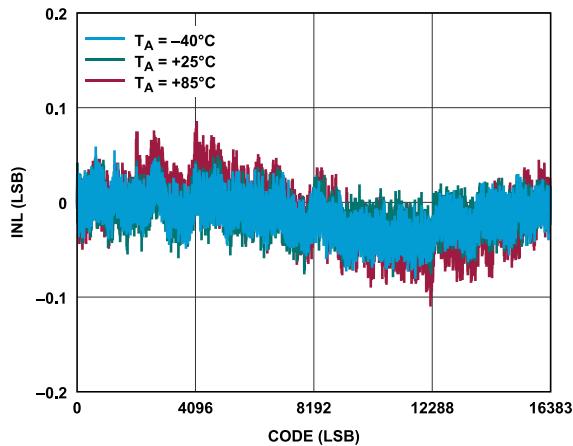

Figure 14. INL vs. Code for Various Temperatures, 40MSPS

## TYPICAL PERFORMANCE CHARACTERISTICS

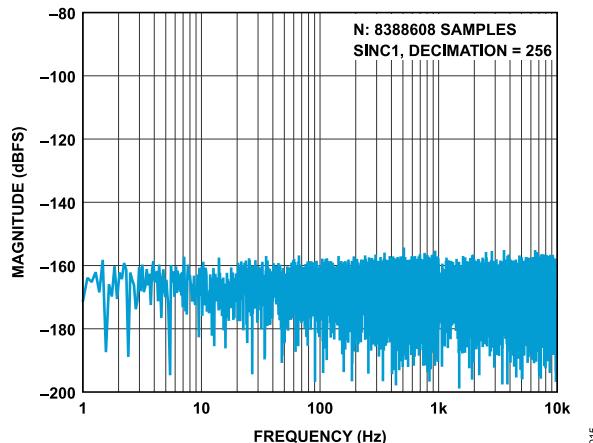

Figure 15. Low Frequency Noise, Inputs Shorted

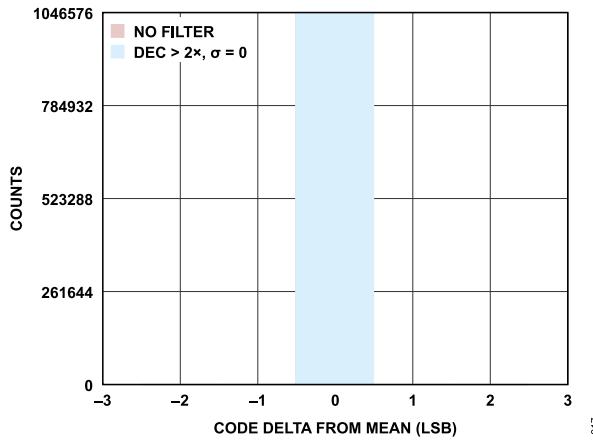

Figure 18. Histogram of Codes, Sinc5 + Compensation, No Filter, Decimate 2x, Decimate 4x ... Decimate 512x

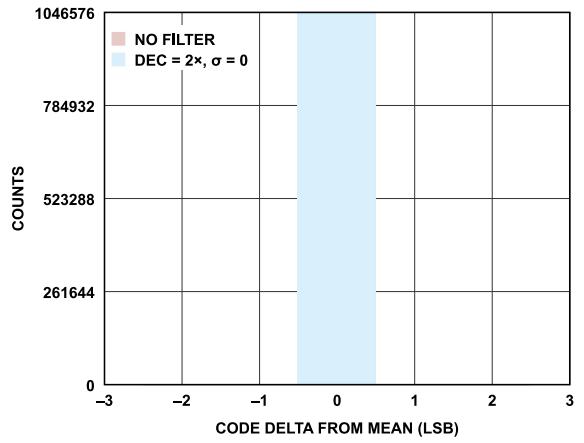

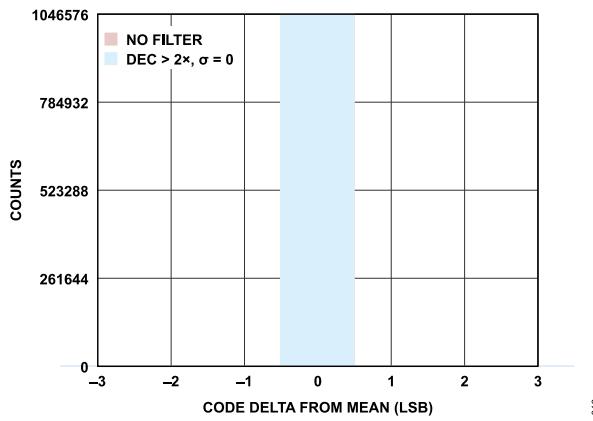

Figure 16. Histogram of Codes, Sinc1, No Filter, Decimate 2x, Decimate 4x ... Decimate 1024x

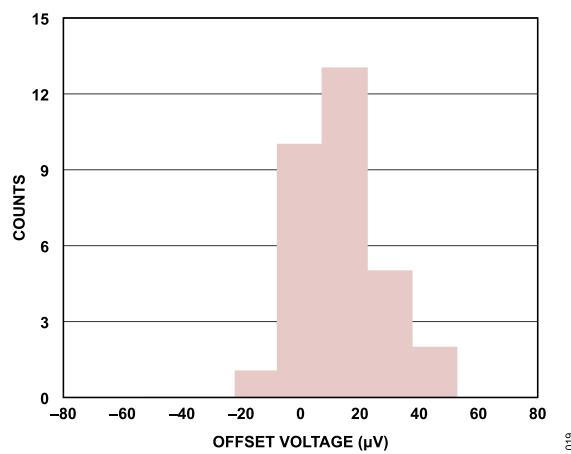

Figure 19. Offset Voltage Histogram

Figure 17. Histogram of Codes, Sinc5, No Filter, Decimate 2x, Decimate 4x ... Decimate 256x

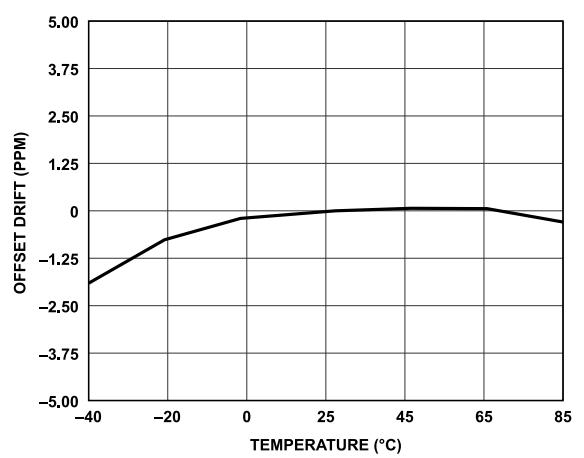

Figure 20. Offset Drift vs. Temperature

## TYPICAL PERFORMANCE CHARACTERISTICS

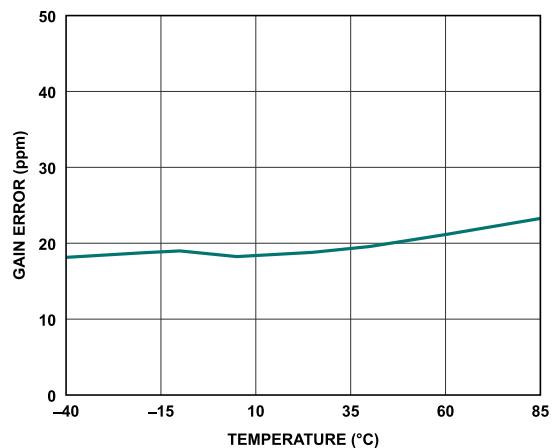

Figure 21. Gain Error vs. Temperature

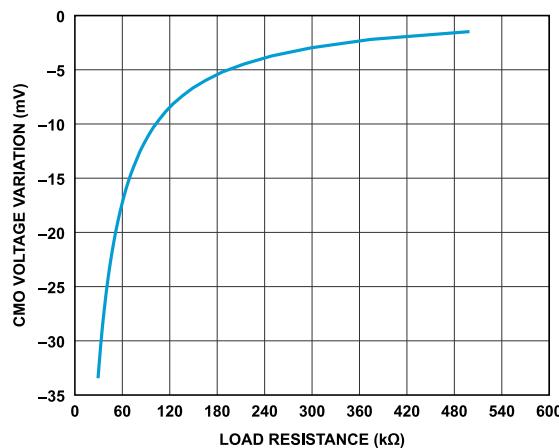

Figure 24. CMO Voltage Variation vs. Load Resistance

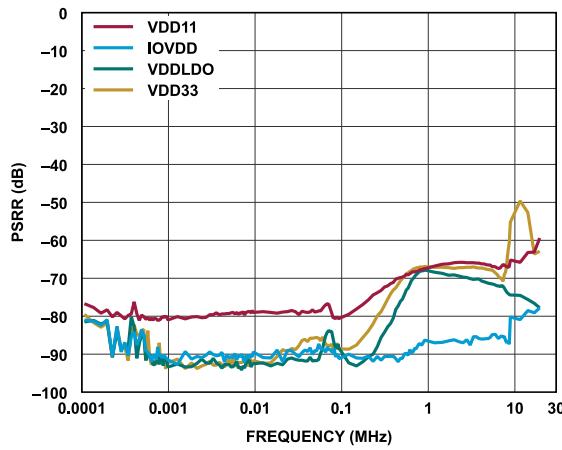

Figure 22. PSRR vs. Frequency

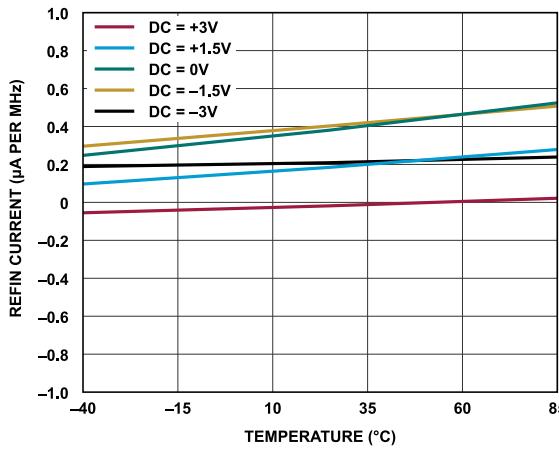

Figure 25. Dynamic REFIN Current vs. Temperature

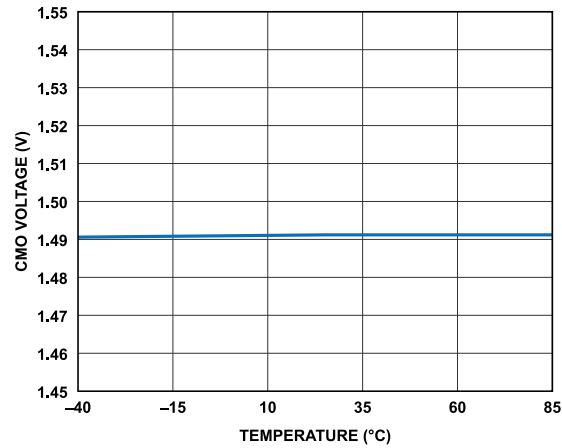

Figure 23. CMO Voltage vs. Temperature

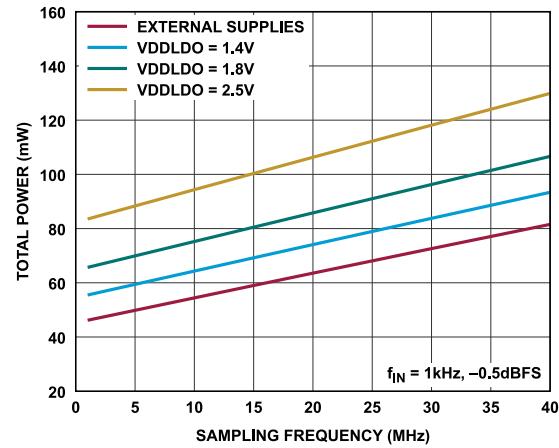

Figure 26. Total Power vs. Sampling Frequency

## TYPICAL PERFORMANCE CHARACTERISTICS

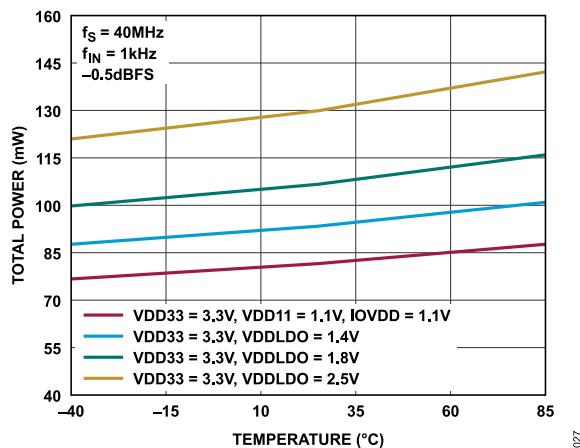

Figure 27. Total Power at 40MSPS vs. Temperature

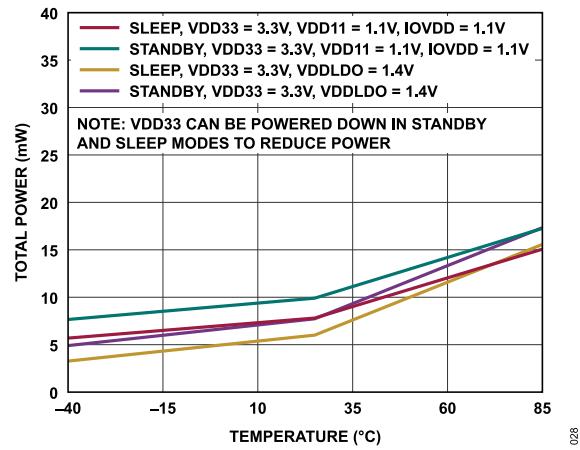

Figure 28. Total Power vs. Temperature in Sleep and Standby Modes

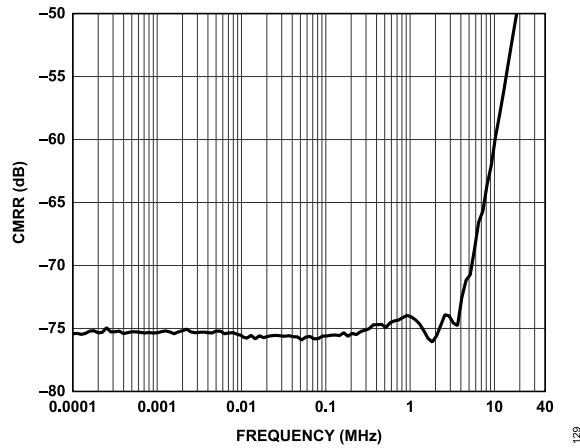

Figure 29. AC CMRR vs. Input Frequency

## TERMINOLOGY

### Integral Nonlinearity Error (INL)

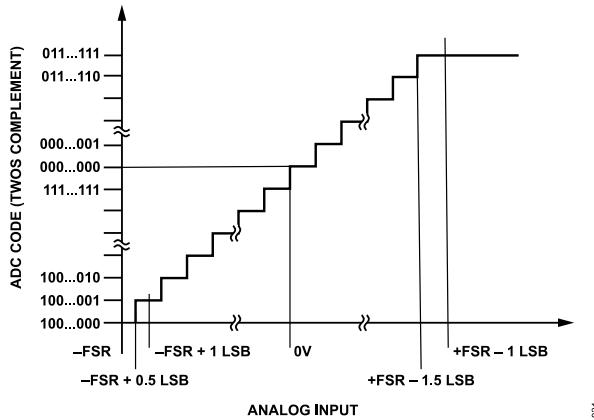

INL refers to the deviation of each output code from a line drawn between points at negative full scale and positive full scale. The negative full-scale reference is defined by an input level equivalent to  $\frac{1}{2}$  LSB prior to the first code transition. The positive full-scale reference is defined as an input level that is  $1\frac{1}{2}$  LSB beyond the last code transition. The deviation is measured from the center of each code relative to the straight line.

### Differential Nonlinearity Error (DNL)

In an ideal ADC, code transitions occur at 1 LSB intervals. DNL is a measure of the maximum deviation of any code from the ideal code width. DNL is specified in terms of resolution for which no missing codes are guaranteed.

### Zero Error

Zero error is the difference between the ideal midscale voltage, 0V, and the applied voltage producing the midscale output code, 0LSB.

### Gain Error

Gain error is specified as the difference in the slope of the ADC transfer characteristic vs. that of an ideal converter. In an ideal data converter, the first code transition (100 ... 00 to 100 ... 01) occurs  $\frac{1}{2}$  LSB more than the nominal negative full-scale input ( $-2.999997V$  for a  $\pm 3.0V$  range at 14 bits) and the last code transition (011 ... 10 to 011 ... 11) occurs  $1\frac{1}{2}$  LSB less than the nominal positive full-scale input ( $+2.999991V$  for a  $\pm 3.0V$  range at 14 bits).

### Signal-to-Noise Ratio (SNR)

SNR is the computed ratio of the fundamental signal amplitude measured in RMS volts and the root sum of squares of all other spectral components in the Nyquist bandwidth ( $f < f_s/2$ ) excluding harmonics and DC components. The computed value of SNR is converted into a logarithmic scale and expressed in decibels (dB).

### Signal-to-Noise-and-Distortion (SINAD) Ratio

SINAD is the computed ratio of the fundamental signal amplitude measured in RMS volts and the root sum of squares of all other spectral components in the Nyquist bandwidth ( $f < f_s/2$ ) including harmonic components but excluding the DC component. The computed value of SINAD is converted into a logarithmic scale and expressed in decibels (dB).

### Total Harmonic Distortion (THD)

THD is the ratio of the RMS sum of the amplitudes of the first five harmonic components to the RMS amplitude of a full-scale input signal expressed in decibels (dB).

### Spurious-Free Dynamic Range (SFDR)

SFDR is the ratio between the RMS amplitude of the input signal and the peak spurious signal amplitude, expressed in decibels (dB).

### Intermodulation Distortion

With inputs consisting of sine waves at two frequencies,  $f_A$  and  $f_B$ , any active device with nonlinearities creates distortion products at sum and difference frequencies of  $m \times f_A$  and  $n \times f_B$ , where  $m, n = 0, 1, 2, 3$ , and so on. Intermodulation distortion terms are those for which neither  $m$  nor  $n$  are equal to 0. For example, the second-order terms include  $(f_A + f_B)$  and  $(f_A - f_B)$ , and the third-order terms include  $(2f_A + f_B)$ ,  $(2f_A - f_B)$ ,  $(f_A + 2f_B)$ , and  $(f_A - 2f_B)$ .

The AD4087 is tested where two input frequencies near the top end of the input bandwidth are used. In this case, the second-order terms are usually distanced in frequency from the original sine waves, and the third-order terms are usually at a frequency close to the input frequencies. As a result, the second-order and third-order terms are specified separately. The calculation of the intermodulation distortion is as per the THD specification, where it is the ratio of the RMS sum of the individual distortion products to the RMS amplitude of the sum of the fundamentals, expressed in decibels.

### Power Supply Rejection Ratio (PSRR)

PSRR is a measure of the sensitivity of the ADC to variations in the specified power supply rail vs. frequency. PSRR is computed as the ratio of the observed change in the output code in RMS volts to the RMS magnitude of the perturbing signal coupled to the supply. The resulting ratio is reported in decibels (dB).

## THEORY OF OPERATION

### PRODUCT OVERVIEW

The AD4087 is a high speed, low noise, low distortion, 14-bit, Easy Drive, SAR ADC. The device is capable of conversion rates up to 20MSPS, with 82.14ns result output latency. The parametric performance, bandwidth, and throughput make this product ideal for a variety of high speed, data acquisition applications. Innovations in the AD4087 product design enable both complexity reduction and component flexibility in the design of data acquisition signal chains.

The converter architecture enables continuous acquisition of the input signal throughout the entire conversion period,  $t_{CONV}$ , reducing the input signal conditioning bandwidth required to settle to the specified resolution.

The design incorporates circuitry to reduce the nonlinear input current associated with the charge kickback typical of a switched capacitor SAR input.

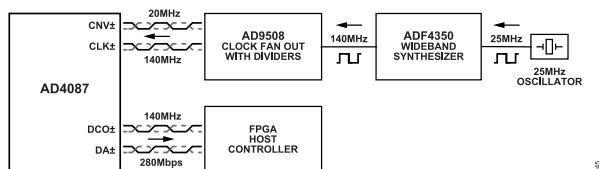

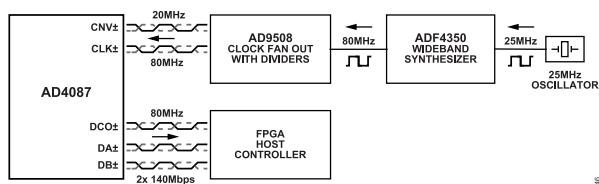

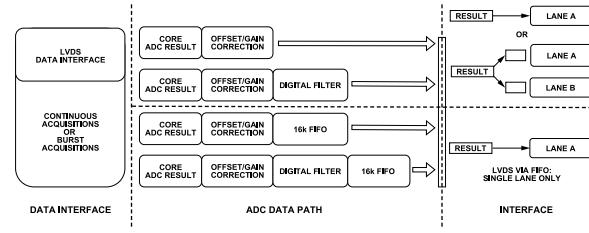

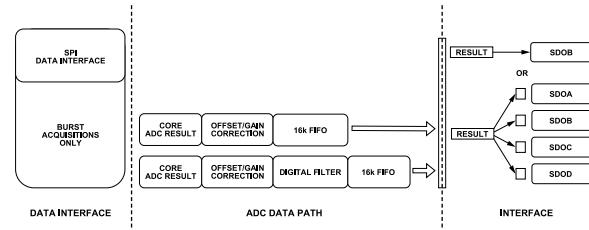

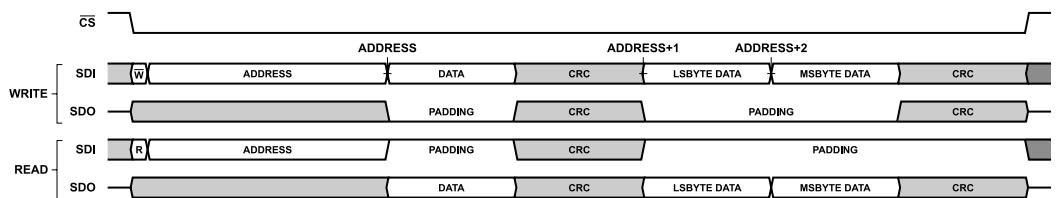

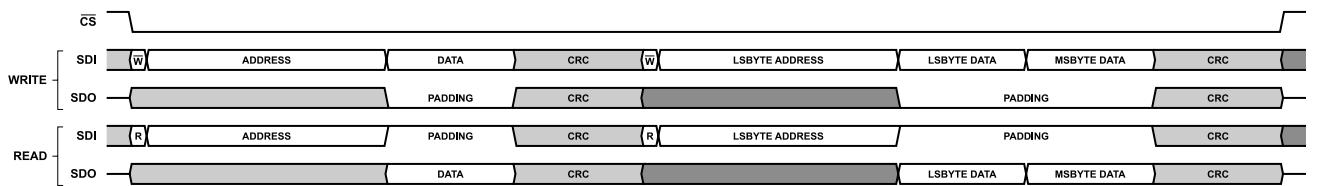

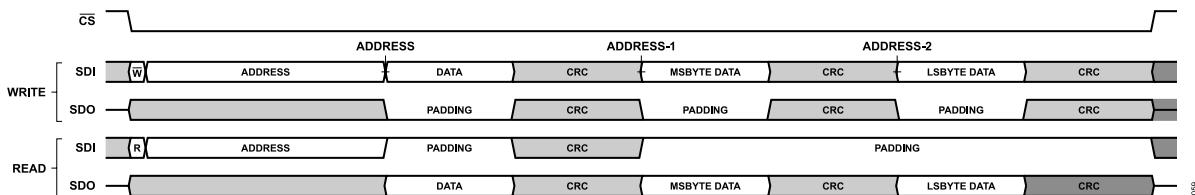

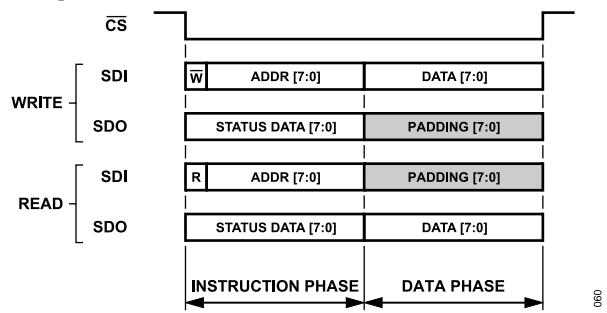

Conversion result access occurs via either a multilane LVDS port operating at clock rates up to 140MHz or via a multioutput SPI operating at clock rates up to 50MHz.

The LVDS interface is compatible with differential signaling standards between 1.2V and 2.5V. To maximize throughput, the previous conversion results can be read through the entirety of the conversion period as long as the CNV+ edge and CLK+ rising edges are aligned. The LVDS interface is described in detail in the [LVDS Data Interface Configuration](#) section.

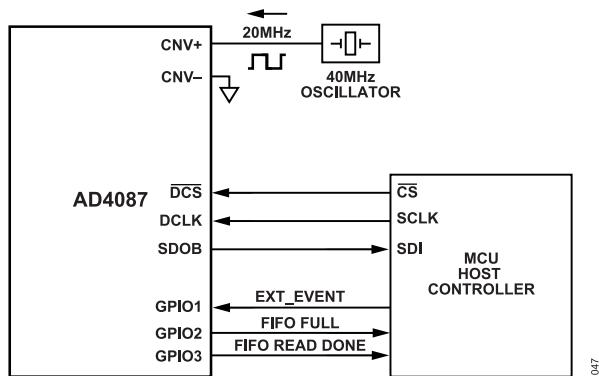

The single or quad lane SPI data interface is also available for CMOS level interfacing. When configured, this interface is used to access conversion results stored in the on-chip FIFO. FIFO operation is explained in the [Result FIFO](#) section.

### CONVERTER OPERATION

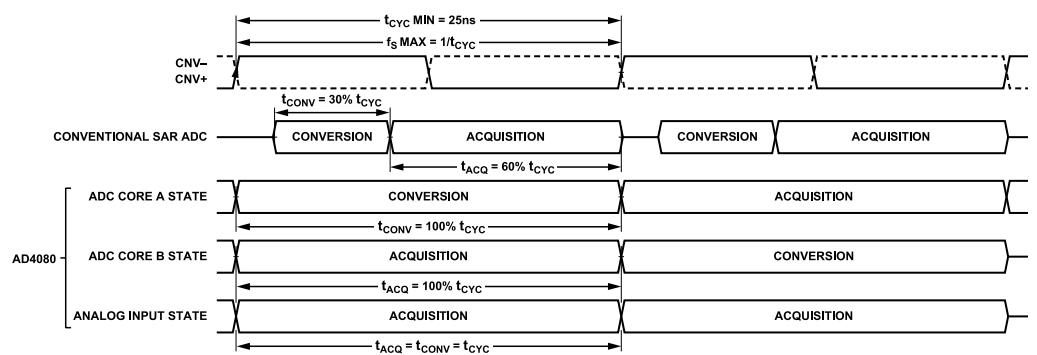

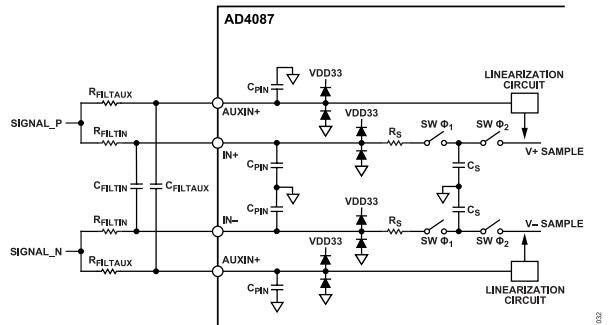

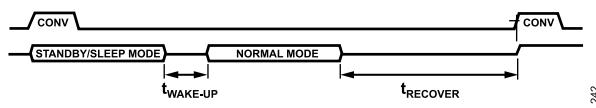

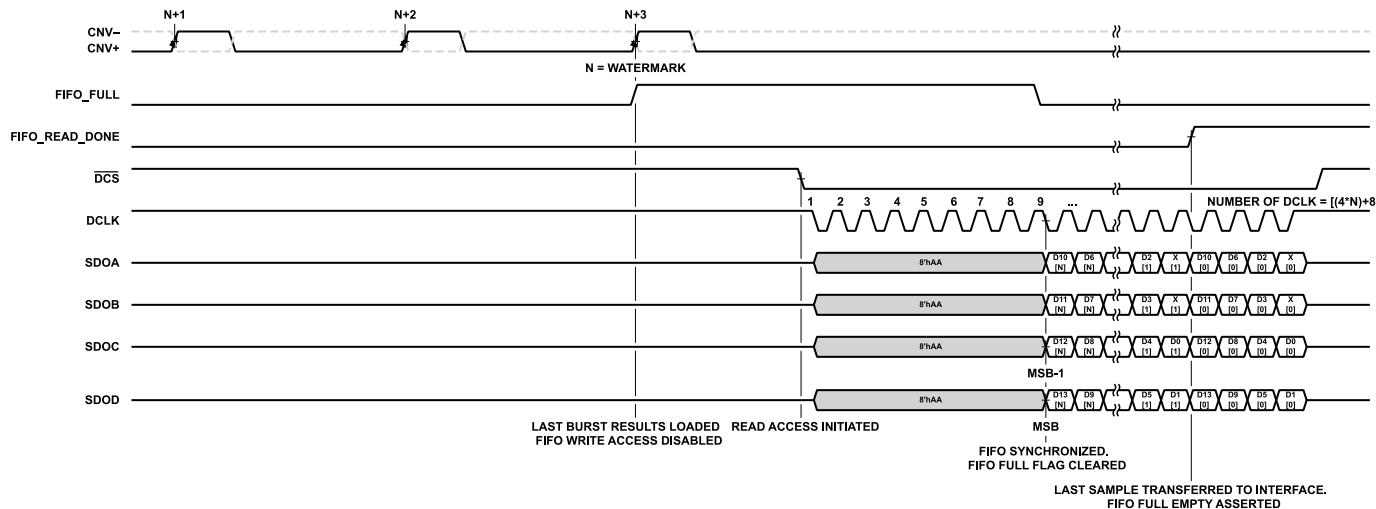

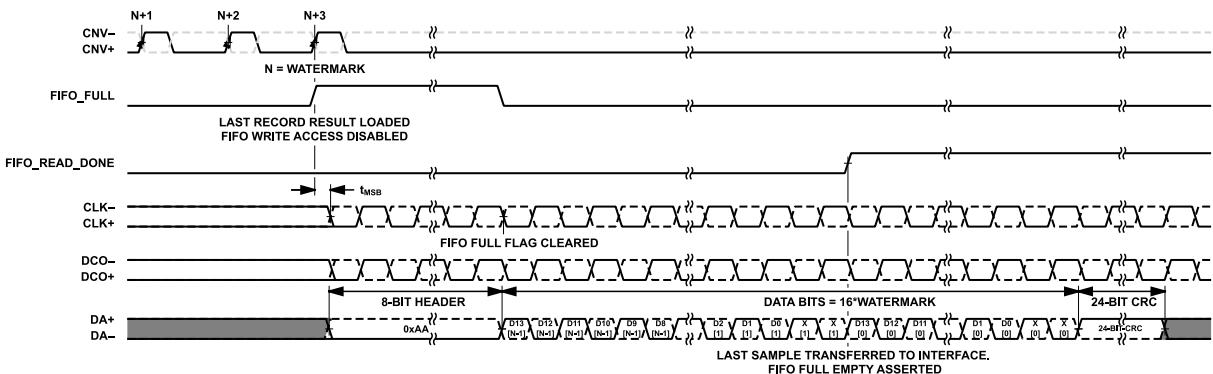

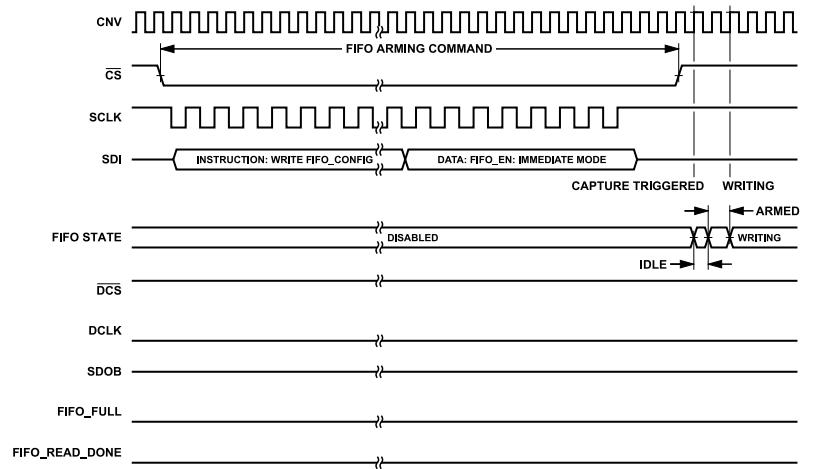

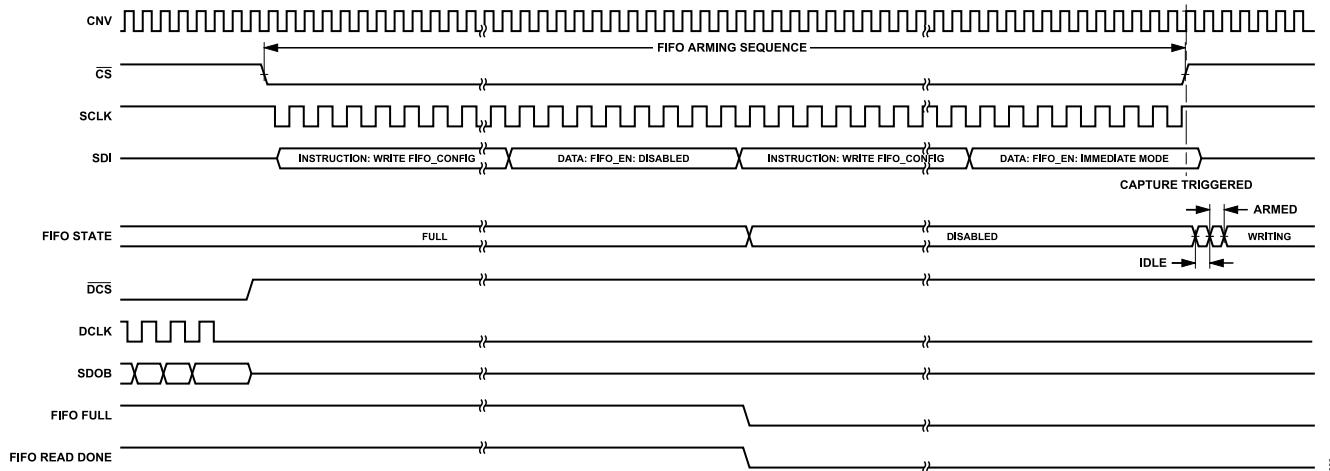

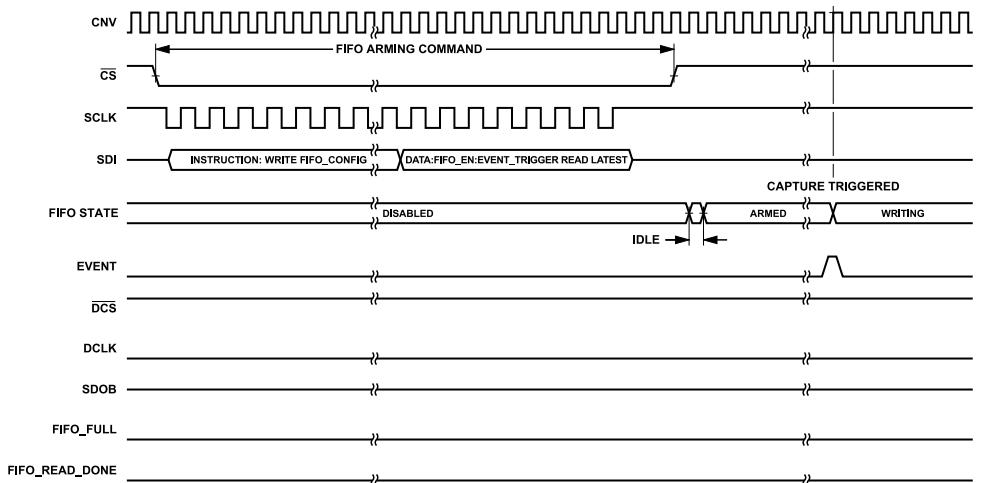

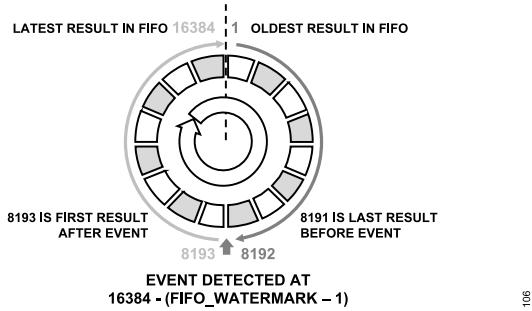

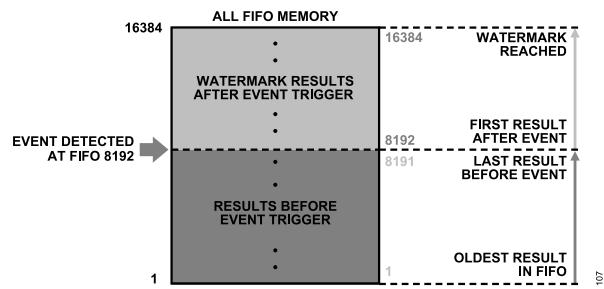

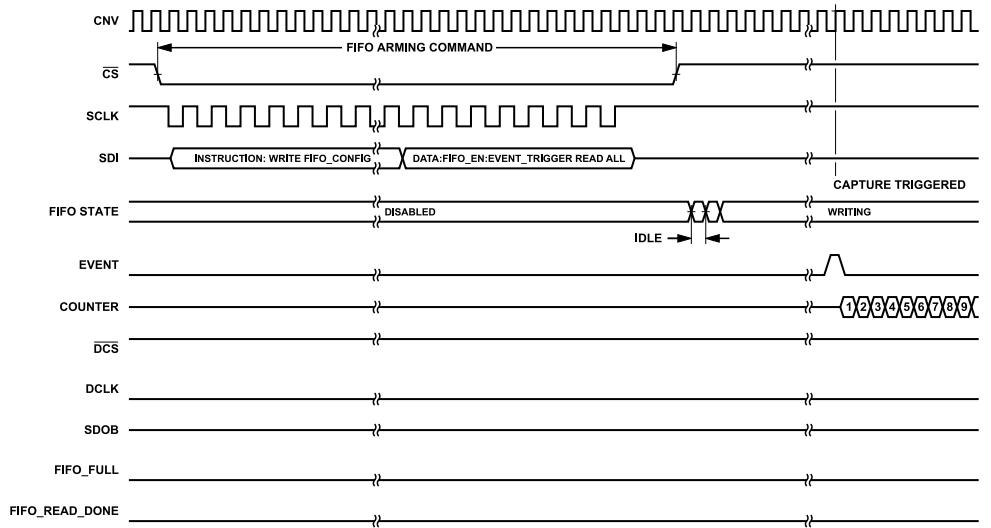

A conventional SAR ADC typically operates in two phases—an acquisition phase, whereby the analog input voltage is acquired