#### **MAX22200**

# 36V, 1A Octal Integrated Serial-Controlled Solenoid and Motor Driver

### **General Description**

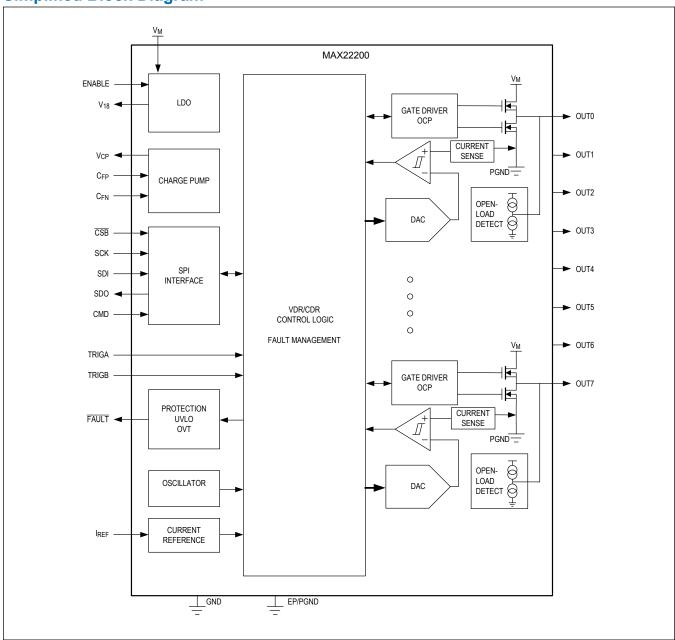

The MAX22200/MAX22200A are octal 36V serial-controlled solenoid drivers. Each channel features a low impedance (200m $\Omega$  typ) push-pull output stage with sink-and-source driving capability and up to 1A<sub>RMS</sub> driving current. A serial interface (SPI) that also supports daisy-chain configurations is provided to individually control each channel.

The devices' half-bridges can be configured as low-side drivers or as high-side drivers. Moreover, pairs of half-bridges can be paralleled to double the driving current or can be configured as full-bridges to drive up to four latched valves (bi-stable valves) or four brushed DC motors.

Two control methods are supported: voltage drive regulation (VDR) and current drive regulation (CDR). In VDR, the device output a PWM voltage in which the duty cycle is programmed using SPI. For a given supply voltage and solenoid resistor, the output current is proportional to the programmed duty cycle. In CDR, an internal integrated lossless current sensing (ICS) circuit senses the output current and compares it with an internal programmable reference current.

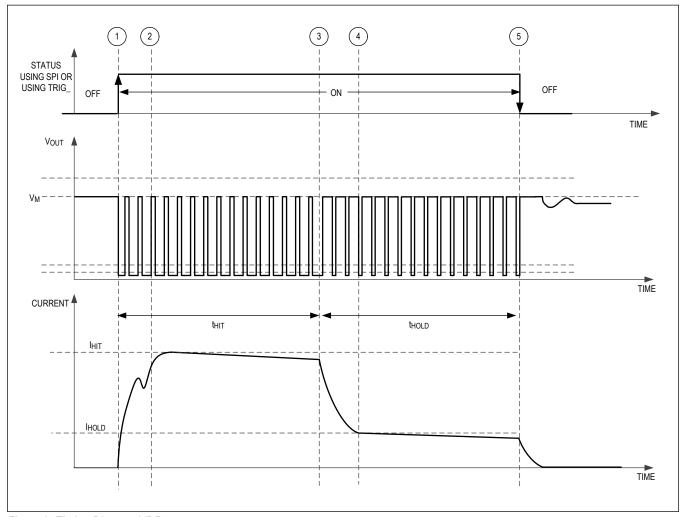

For optimal power management in solenoid drive applications, the excitation drive level ( $I_{HIT}$ ), the hold drive level ( $I_{HOLD}$ ), and the excitation drive time ( $t_{HIT}$ ) can be individually configured for each channel.

The MAX22200/MAX22200A feature a full set of protections and diagnostic functions, including overcurrent protection (OCP), thermal shutdown (TSD), undervoltage Lockout (UVLO), open-load detection (OL), and detection of plunger movement (DPM). A fault indication pin (FAULT) signals fault events and diagnostic information is stored in the FAULT register. The MAX22200A provides a safe, selective clear on read procedure for the FAULT register. It is the preferred version for new design. The MAX22200 offers a standard clear on read that can be used to determine firmware compatibility.

Due to their versatility, serial interface control, high efficiency, and small package size, the MAX22200/MAX22200A are particularly suited for solenoid driver applications (valve control, relays control, etc.) in which low power consumption and a high level of integration are required.

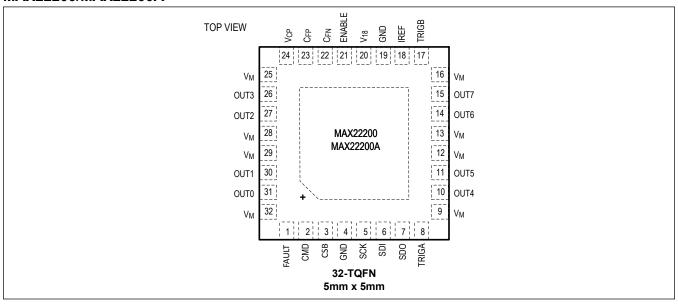

The MAX22200/MAX22200A are available in a compact 5mm x 5mm, 32-pin TQFN package and operate over the -40°C to +85°C temperature range.

### **Applications**

- Relays Driver

- Solenoid, Valves, Electromagnetic Drivers

- Generic Low-Side and High-Side Switch Applications

- Latched (Bi-Stable) Solenoid Valve Drivers

- Brushed DC Motor Driver

#### **Benefits and Features**

- Eight Half-Bridges Up To +36V

- High Performances:

- Low On-Resistance: R<sub>DS(on)</sub>: 200 mΩ typical (T<sub>A</sub> = +25°C)

- Continuous Output Current Up To 1A<sub>RMS</sub> per Half-Bridge (T<sub>A</sub> = +25°C)

- Current-Drive Regulation (CDR)

- Voltage-Drive Regulation (VDR)

- Integrated Lossless Current Sensing (ICS)

- High Flexibility:

- Independent Programmable HIT and HOLD Currents for Each Channel (I<sub>HIT</sub>, I<sub>HOLD</sub>)

- Independent Programmable HIT Current Timing for Each Channel (t<sub>HIT</sub>)

- · Full-Bridge Configuration Supported

- · Parallel Mode Supported

- High Speed Serial Interface (SPI)

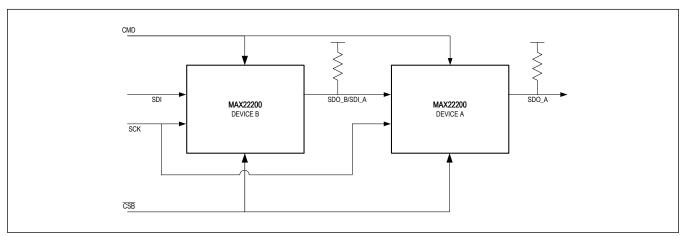

- 5MHz Daisy-Chain Configuration

- 10MHz without Daisy Chain

- Protections and Diagnostic

- Overcurrent Protection (OCP)

- · Open-Load Detection (OL)

- Detection of Plunger Movement (DPM)

- Undervoltage Lockout (UVLO)

- · HIT Current Not Reached (HHF)

- Thermal Shutdown T = +145°C (TSD)

- Fault Registers for Diagnostic purposes

- Fault Register Selective Clear on Read (MAX22200A Only)

- Integration:

- 32 TQFN 5mm x 5mm Package

# **Simplified Block Diagram**

### **TABLE OF CONTENTS**

| 1,1,5,1,2,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,                               |    |

|------------------------------------------------------------------------|----|

| General Description                                                    |    |

| Applications                                                           | 1  |

| Benefits and Features                                                  |    |

| Simplified Block Diagram                                               | 2  |

| Absolute Maximum Ratings                                               | 7  |

| Package Information                                                    | 7  |

| 32 TQFN                                                                | 7  |

| Electrical Characteristics                                             | 7  |

| Pin Configuration                                                      | 12 |

| MAX22200/MAX22200A                                                     | 12 |

| Pin Description                                                        | 12 |

| Detailed Description                                                   | 14 |

| Enable Logic Input                                                     | 14 |

| Functional Description - Two Levels Drive Sequence for Solenoid Valves | 14 |

| Chopping Frequency (FREQM, FRQ_CFG_)                                   | 16 |

| Slew-Rate Controlled Mode (SRC)                                        | 17 |

| Min and Max Duty cycle                                                 | 17 |

| Voltage Drive Regulation (VDR)                                         | 17 |

| Current Drive Regulation (CDR)                                         | 18 |

| HIT and HOLD Current Setting (CDR)                                     | 18 |

| Full-Scale Current Setting (IFS)                                       | 18 |

| Half Full-Scale Setting (HFS bit)                                      | 19 |

| Fixed-Frequency Current Control                                        |    |

| HIT Excitation Time (t <sub>HIT</sub> )                                |    |

| Supported Driver Configurations                                        | 20 |

| Low-Side/High-Side Operations (HSnLS)                                  | 20 |

| Half-Bridge Parallelization                                            | 20 |

| Full-Bridge Configuration                                              | 20 |

| Protection Circuits                                                    | 21 |

| Overcurrent Protection (OCP)                                           |    |

| Open-Load Detection (OL)                                               | 21 |

| Detection of Plunger Movement (DPM)                                    | 22 |

| Thermal Shutdown (TSD)                                                 | 22 |

| Undervoltage Lockout (UVLO)                                            | 22 |

| HIT Current Not Reached Flag (HHF)                                     | 22 |

| Programming Information                                                | 23 |

| SPI Detailed Description                                               | 23 |

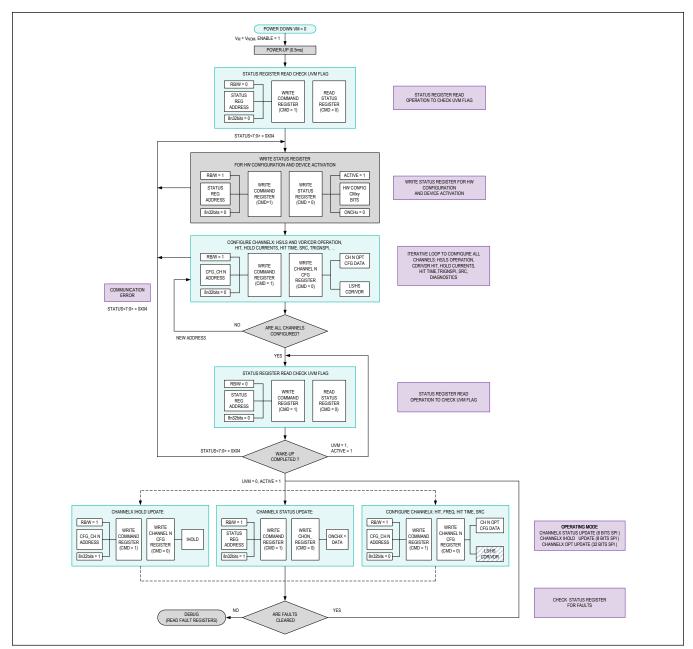

| Programming Procedure                                                  | 23 |

| Command Register Description (COMMAND)                                 | 25 |

# TABLE OF CONTENTS (CONTINUED)

| Status Register Description (STATUS)                         | 26 |

|--------------------------------------------------------------|----|

| Configuration Register Description (CFG_CH_)                 |    |

| Fault Register Description (FAULT)                           | 28 |

| Clearing the FAULT Register                                  | 28 |

| Detection of Plunger Movement Register Description (CFG_DPM) | 29 |

| Reading and Writing Operations of Registers                  | 30 |

| Communication Error Detection (COMF)                         | 34 |

| Register Map                                                 | 35 |

| MAX22200/MAX22200A Register Map                              | 35 |

| Register Details                                             | 36 |

| Applications Information                                     | 42 |

| Use Cases                                                    | 42 |

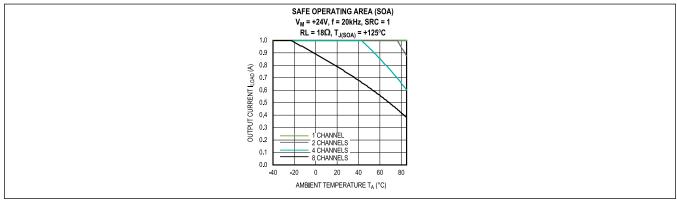

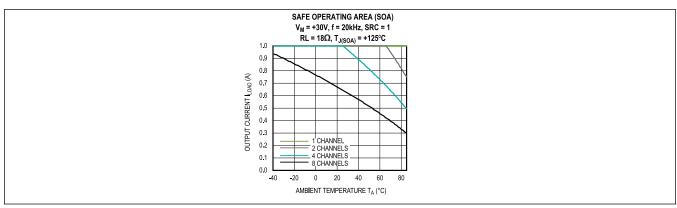

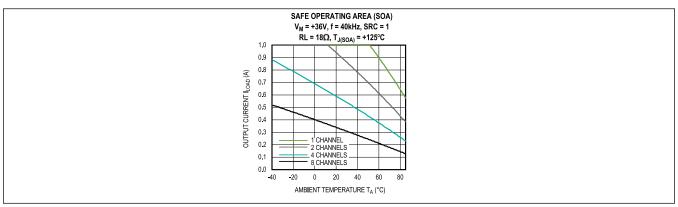

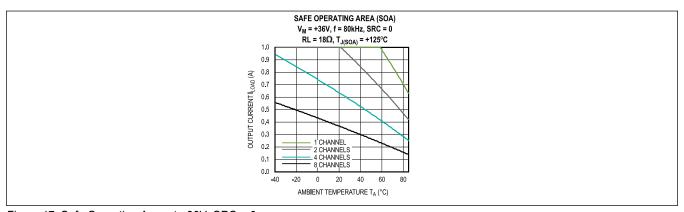

| Current Rating                                               | 42 |

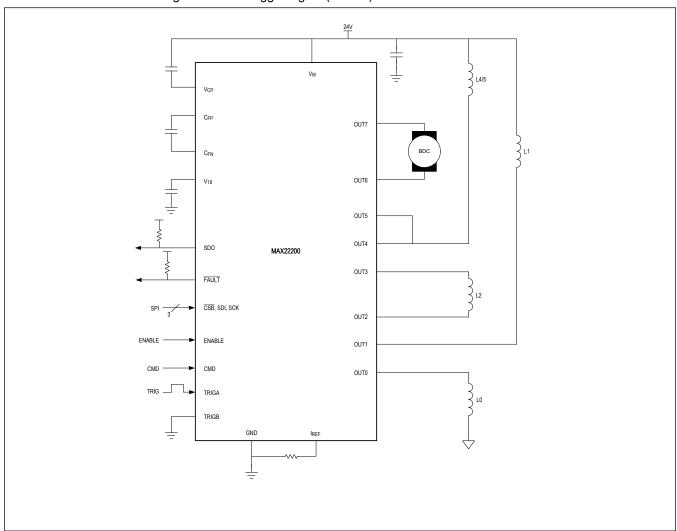

| Typical Application Circuits                                 | 44 |

| Application Diagram                                          | 44 |

| Ordering Information                                         | 45 |

| Revision History                                             | 46 |

# LIST OF FIGURES

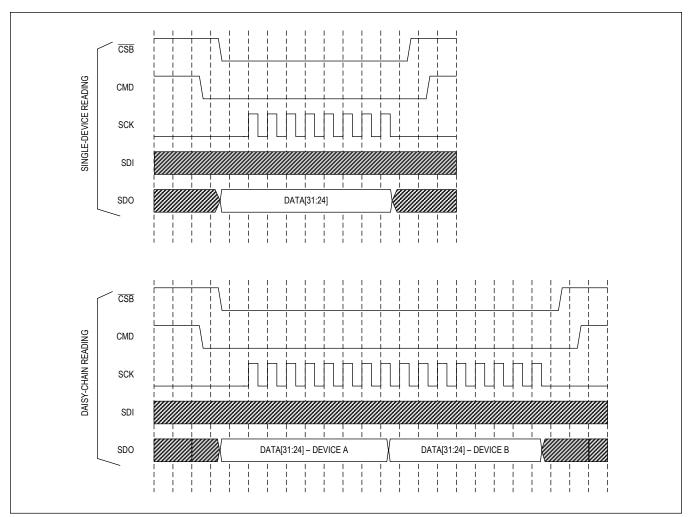

| Figure 1. SPI Timing Diagram                                        | 11 |

|---------------------------------------------------------------------|----|

| Figure 2. Timing Diagram VDR                                        | 15 |

| Figure 3. Timing Diagram CDR                                        | 16 |

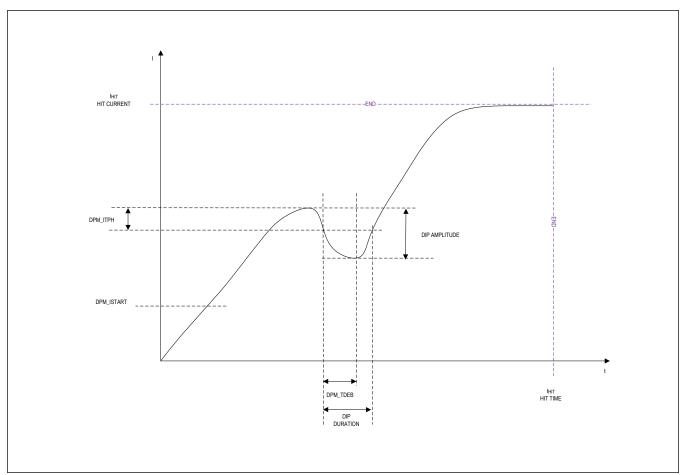

| Figure 4. Detection of Plunger Movement                             | 22 |

| Figure 5. SPI Daisy-Chain Configuration                             | 23 |

| Figure 6. Programming Flow Chart                                    | 25 |

| Figure 7. Writing Command Register                                  | 26 |

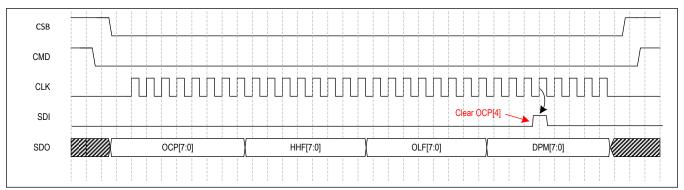

| Figure 8. Selective Clear on Read of the FAULT Register (MAX22200A) | 29 |

| Figure 9. Detection of Plunger Movement                             | 30 |

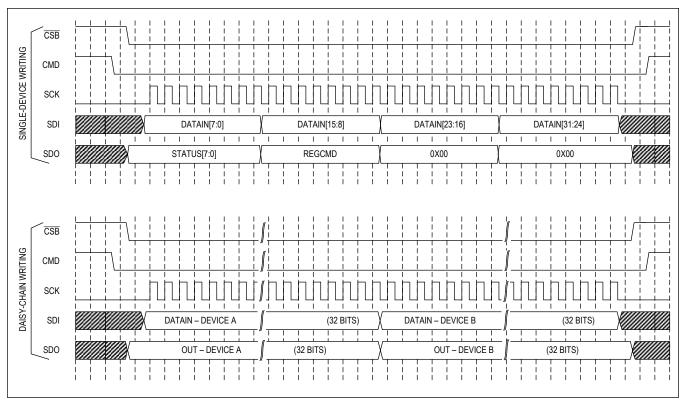

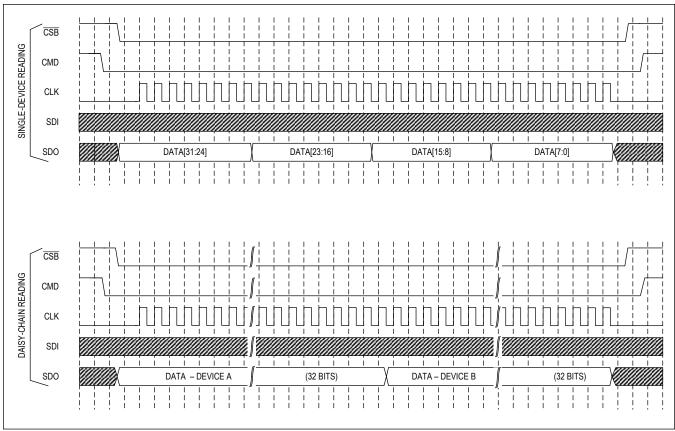

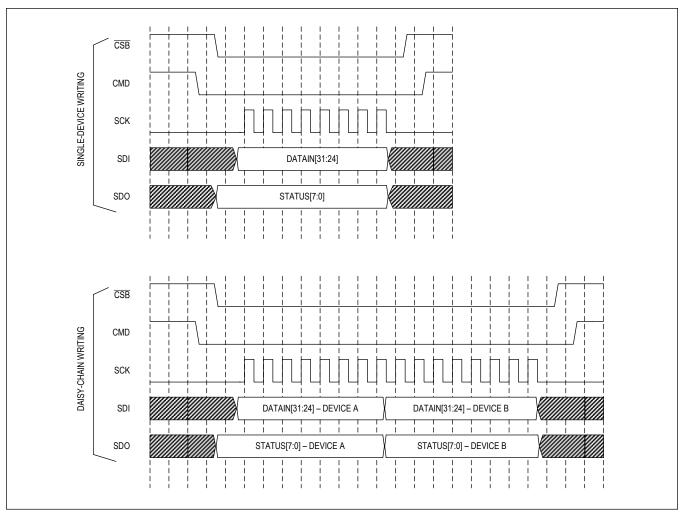

| Figure 10. 32-Bit Register Writing—Timing Diagram                   | 31 |

| Figure 11. 32-Bit Register Reading—Timing Diagram                   | 32 |

| Figure 12. 8-Bit Register Writing—Timing Diagram                    | 33 |

| Figure 13. 8-Bit Register Reading—Timing Diagram                    | 34 |

| Figure 14. Safe Operating Area at +24V                              | 42 |

| Figure 15. Safe Operating at Area +30V                              | 43 |

| Figure 16. Safe Operating at Area +36V                              | 43 |

| Figure 17. Safe Operating Area at +36V, SRC = 0                     | 43 |

# MAX22200

# 36V, 1A Octal Integrated Serial-Controlled Solenoid and Motor Driver

# **LIST OF TABLES**

| Table 1. Chopping Frequency                      | 17 |

|--------------------------------------------------|----|

| Table 2. Min and Max Duty Cycle                  | 17 |

| Fable 3. VDR Duty Cycle                          | 18 |

| Table 4. HIT and HOLD Current Setting (CDR)      | 18 |

| Table 5. HIT Excitation Time (t <sub>HIT</sub> ) | 20 |

| Table 6. TRGnSPI in Half-Bridge Parallel Mode    | 20 |

| Table 7. Full-Bridge Configuration               | 21 |

| Table 8. TRGnSPI in Full-Bridge Mode             | 21 |

| Fable 9. Command Register                        | 26 |

| Гable 10. Status Register                        | 27 |

| Fable 11. Configuration Register                 | 27 |

| Table 12. Fault Register                         | 28 |

## **Absolute Maximum Ratings**

| PGND to GND            | 0.6V to +0.6V                                             |

|------------------------|-----------------------------------------------------------|

| V <sub>M</sub> to GND  | -0.3V to +40V                                             |

| V <sub>CP</sub> to GND | (V <sub>M</sub> - 0.3V) to min(+42V, V <sub>M</sub> + 6V) |

|                        | ( $V_M - 0.3V$ ) to ( $V_{CP} + 0.3V$ )                   |

| C <sub>FN</sub> to GND | 0.3V to (V <sub>M</sub> + 0.3V)                           |

|                        | 0.3V to +6V                                               |

| CSB to GND             | 0.3V to +6V                                               |

| SDI to GND             | 0.3V to +6V                                               |

| ENABLE to GND          | 0.3V to (V <sub>M</sub> + 0.3V)                           |

| SCK to GND             | 0.3V to +6V                                               |

| SDO to GND                   | 0.3V to +6V                                 |

|------------------------------|---------------------------------------------|

| FAULT to GND                 | 0.3V to +6V                                 |

| TRIGA, TRIGB to GND          | 0.3V to +6V                                 |

| I <sub>REF</sub> to GND      | $0.3V \text{ to min(+2.2V, V}_{18} + 0.3V)$ |

| V <sub>18</sub> to GND       | 0.3V to min(+2.2V, $V_M$ + 0.3V)            |

| OUT_ to PGND                 | 0.3V to (V <sub>M</sub> + 0.3V)             |

| Continuous Power Dissipation | TQFN (Multilayer Board) $(T_A =$            |

| +70°C, derate 34.5mW/°C abov | e +70°C.) 0mW to 2758mW                     |

| Operating Temperature Range. | 40°C to +85°C                               |

|                              |                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### **32 TQFN**

| <u> </u>                                                       |                |  |  |

|----------------------------------------------------------------|----------------|--|--|

| Package Code                                                   | T3255+8C       |  |  |

| Outline Number                                                 | <u>21-0140</u> |  |  |

| Land Pattern Number                                            | 90-0013        |  |  |

| THERMAL RESISTANCE, SINGLE-LAYER BOARD                         |                |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                         | 47°C/W         |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) 1.7°C/W |                |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                           |                |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                         | 29°C/W         |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )         | 1.7°C/W        |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_M = +4.5 \text{V to} +36 \text{V}, T_A = -40 ^{\circ} \text{C to} +85 ^{\circ} \text{C}$ . ENABLE =  $V_M$ ,  $C_F = 22 \text{nF}$ ,  $C_{B18} = 2.2 \mu \text{F}$ ,  $C_T = 1 \mu \text{F}$ . Typical values are at  $V_M = +24 \text{V}$  and  $T_A = +25 ^{\circ} \text{C}$ , unless otherwise noted. Limits are 100% tested at  $T_A = +25 ^{\circ} \text{C}$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                       | SYMBOL           | CONDITIONS                               | MIN | TYP | MAX | UNITS |

|---------------------------------|------------------|------------------------------------------|-----|-----|-----|-------|

| SUPPLY VOLTAGE                  |                  |                                          |     |     |     |       |

| Supply-Voltage Range            | V <sub>M</sub>   |                                          | 4.5 |     | 36  | V     |

| Disable Current<br>Consumption  | I <sub>SDN</sub> | ENABLE = 0, V <sub>M</sub> = OUT_ = +24V |     |     | 11  | μA    |

| Inactive Current<br>Consumption | I <sub>NA</sub>  | ACTIVE = 0                               |     | 200 | 400 | μA    |

# **Electrical Characteristics (continued)**

$(V_M = +4.5 \text{V to } +36 \text{V}, T_A = -40 ^{\circ} \text{C to } +85 ^{\circ} \text{C}$ . ENABLE =  $V_M$ ,  $C_F = 22 \text{nF}$ ,  $C_{B18} = 2.2 \mu \text{F}$ ,  $C_T = 1 \mu \text{F}$ . Typical values are at  $V_M = +24 \text{V}$  and  $T_A = +25 ^{\circ} \text{C}$ , unless otherwise noted. Limits are 100% tested at  $T_A = +25 ^{\circ} \text{C}$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                           | SYMBOL                            | CONDITIONS                                                                |                         | MIN   | TYP           | MAX   | UNITS |

|-----------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------|-------------------------|-------|---------------|-------|-------|

| Quiescent Current<br>Consumption–All<br>Drivers Off | I <sub>Q1</sub>                   | All drivers set in VDF                                                    |                         | 2.5   | 5             | mA    |       |

| Quiescient Current–All<br>Drivers VDR Mode          | I <sub>Q2</sub>                   | All drivers set in VDF<br>On, low-side, no load                           |                         |       | 3.5           | 5     | mA    |

| Quiescent Current<br>Consumption–CDR<br>Mode        | I <sub>Q3</sub>                   | All drivers set in CDI<br>On, no load                                     | R Mode–Continuous       |       | 5.2           | 7.5   | mA    |

| LDO (V <sub>18</sub> )                              |                                   |                                                                           |                         |       |               |       |       |

| V <sub>18</sub> Output Voltage<br>Range             | V <sub>18</sub>                   | I <sub>V18</sub> < 20mA                                                   |                         | 1.728 | 1.8           | 1.872 | V     |

| V <sub>18</sub> Current Limit                       | I <sub>V18(LIM)</sub>             |                                                                           |                         | 20    |               |       | mA    |

| V <sub>18</sub> UVLO Rising                         | UVLO <sub>V18(R)</sub>            | V <sub>18</sub> rising                                                    |                         |       | 1.65          |       | V     |

| V <sub>18</sub> UVLO Hysteresis                     | UVLO <sub>V18(H)</sub>            |                                                                           |                         |       | 70            |       | mV    |

| CHARGE PUMP (V <sub>CP</sub> , C <sub>I</sub>       | <sub>PF</sub> , C <sub>NF</sub> ) |                                                                           |                         |       |               |       |       |

| V <sub>CP</sub> Operating Voltage                   | $V_{VCP}$                         | Internal Regulator                                                        |                         |       | $V_{M} + 2.7$ |       | V     |

| Charge Pump<br>Frequency                            | f <sub>PMP</sub>                  |                                                                           |                         | 100   |               | kHz   |       |

| LOGIC INPUTS-OUTPUT                                 | S                                 |                                                                           |                         |       |               |       |       |

| Input-Voltage Level High                            | V <sub>IH</sub>                   |                                                                           |                         | 1.2   |               |       | V     |

| Input-Voltage Level Low                             | V <sub>IL</sub>                   |                                                                           |                         |       |               | 0.65  | V     |

| Hysteresis on Logic Inputs                          | HYS                               |                                                                           |                         |       | 110           |       | mV    |

| Open-Drain Low-Level<br>Output Voltage              | V <sub>OL</sub>                   | I <sub>OUT</sub> = 10mA                                                   | I <sub>OUT</sub> = 10mA |       |               | 0.4   | V     |

| Pulldown Current on Logic Inputs                    | I <sub>PD</sub>                   | V <sub>PIN</sub> = +5V                                                    |                         |       | 33            | 70    | μA    |

| Pullup Current CSB/SDI                              | I <sub>PU</sub>                   | CSB/SDI = 0V                                                              |                         | -15   | -7.5          |       | μA    |

| ENABLE Voltage Level<br>High                        | V <sub>IH(EN)</sub>               |                                                                           |                         | 0.9   |               |       | V     |

| ENABLE Voltage Level Low                            | V <sub>IL(EN)</sub>               |                                                                           |                         |       |               | 0.6   | V     |

| ENABLE Pulldown Input<br>Resistance                 | R <sub>PD(EN)</sub>               |                                                                           |                         | 0.8   | 1.5           |       | МΩ    |

| OUTPUT CHARACTERIS                                  | STICS                             | 1                                                                         |                         |       |               |       | •     |

| Low-Side On                                         | Pa                                | 0.5A                                                                      | HFS_ = 0                |       | 0.2           | 0.4   | Ω     |

| Resistance                                          | R <sub>ONLS</sub> 0.5A HFS_ = 1   |                                                                           | HFS_ = 1                |       | 0.4           | 8.0   |       |

| High-Side On resistance                             | R <sub>ONHS</sub>                 | 0.3A                                                                      |                         |       | 0.21          | 0.4   | Ω     |

| Driver Output Leakage                               | I <sub>LEAK</sub>                 | Open load detector disabled (OL_EN_ = 0), output three-stated (ONCH_ = 0) |                         | -2    |               | +2    | μA    |

# **Electrical Characteristics (continued)**

$(V_M = +4.5 \text{V to } +36 \text{V}, T_A = -40 ^{\circ} \text{C to } +85 ^{\circ} \text{C}$ . ENABLE =  $V_M$ ,  $C_F = 22 \text{nF}$ ,  $C_{B18} = 2.2 \mu \text{F}$ ,  $C_T = 1 \mu \text{F}$ . Typical values are at  $V_M = +24 \text{V}$  and  $T_A = +25 ^{\circ} \text{C}$ , unless otherwise noted. Limits are 100% tested at  $T_A = +25 ^{\circ} \text{C}$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                           | SYMBOL              | CONDITIONS                                                     |                                    | MIN                  | TYP                  | MAX   | UNITS |

|-----------------------------------------------------|---------------------|----------------------------------------------------------------|------------------------------------|----------------------|----------------------|-------|-------|

| PROTECTIONS                                         |                     | •                                                              |                                    | •                    |                      |       |       |

| Overcurrent Protection Threshold                    | OCP                 |                                                                |                                    | 1.1                  |                      |       | А     |

| Overcurrent Protection<br>Deglitch Time             | tOCP                | SRC = 0, FREQM =                                               | 0, FREQ_CFG = 00                   |                      | 1.2                  |       | μs    |

| UVLO Threshold on V <sub>M</sub>                    | UVLO                | V <sub>M</sub> rising                                          |                                    | 3.75                 | 4                    | 4.25  | V     |

| UVLO Threshold on V <sub>M</sub><br>Hysteris        | UVLO <sub>HYS</sub> |                                                                |                                    |                      | 0.12                 |       | V     |

| Thermal Shutdown<br>Threshold                       | T <sub>SDN</sub>    |                                                                |                                    |                      | 145                  |       | °C    |

| Thermal Shutdown<br>Hysteresis                      | T <sub>HYS</sub>    |                                                                |                                    |                      | 20                   |       | °C    |

| Open-Load Detection                                 | I <sub>OL_LS</sub>  | OL EN -1                                                       | HSnLS_ = 0,<br>Pulldown current    |                      | 16                   | 30    |       |

| Current                                             | l <sub>OL_HS</sub>  |                                                                | HSnLS_ = 1, Pullup current         | -30                  | -16                  |       | - μΑ  |

| Open-Load Detection                                 | V <sub>OL_LS</sub>  | OL_EN_ = 1                                                     | HSnLS = 0                          |                      | 1.2                  | 2 1.8 | V     |

| Voltage                                             | V <sub>OL_HS</sub>  | OL_EN_ = 1                                                     | HSnLS = 1                          | V <sub>M</sub> - 1.8 | V <sub>M</sub> - 1.2 |       | ]     |

| Open-Load Detect<br>Deglitch Time                   | t <sub>OL</sub>     |                                                                |                                    |                      | 200                  |       | μs    |

| HALF-BRIDGE CONTRO                                  | L                   |                                                                |                                    |                      |                      |       |       |

| Chopping Frequency                                  | f <sub>CHOP</sub>   | FREQ_CFG[1:0] =                                                | FREQ_M = 0                         | 80                   | 100                  | 120   | kHz   |

| Chopping r requency                                 |                     | 11                                                             | FREQ_M = 1                         | 64                   | 80                   | 96    | KI IZ |

| Output Rise-Time in<br>Slew Rate Controlled<br>Mode | <sup>t</sup> RISE   | SRC_ = 1, 10% to 90 = +24V, no load                            | 0% of the swing, V <sub>M</sub>    |                      | 0.2                  |       | μs    |

| Output Fall-Time in Slew Rate Controlled Mode       | t <sub>FALL</sub>   | SRC_ = 1, 10% to 90 = +24V, no load                            | 0% of the swing, V <sub>M</sub>    |                      | 0.2                  |       | μs    |

|                                                     | ITR <sub>ERR1</sub> | - Current Drive                                                | I <sub>TRIG</sub> from 71% to 100% | -6                   |                      | +6    |       |

| Current Drive                                       | ITR <sub>ERR2</sub> | Regulation mode,<br>I <sub>FS</sub> at 1A, R <sub>REF</sub> 1% | I <sub>TRIG</sub> from 20% to 70%  | -10                  |                      | +10   | %     |

| Regulation Accuracy                                 | ITR <sub>ERR3</sub> | tolerance<br>LSnHS_ = 0, HFS_                                  | I <sub>TRIG</sub> from 10% to 20%  | -15                  |                      | +15   |       |

|                                                     | ITR <sub>ERR4</sub> | = 0 ( <u>Note 3</u> )                                          | I <sub>TRIG</sub> from 5% to 10%   | -25                  |                      | +25   |       |

| Full-Scale Current<br>Reference Constant            | K <sub>FS1</sub>    | CDR, LS drive only. $R_{REF}$ from $15k\Omega$ to $100k\Omega$ | HFS_ = 1                           |                      | 7.5k                 |       | A/A   |

| Full Scale Current<br>Reference Constant            | K <sub>FS0</sub>    | CDR, LS drive only. $R_{REF}$ from $15k\Omega$ to $100k\Omega$ | HFS_ = 0                           |                      | 15k                  |       | A/A   |

## **Electrical Characteristics (continued)**

$(V_M$  = +4.5V to +36V,  $T_A$  = -40°C to +85°C. ENABLE =  $V_M$ ,  $C_F$  = 22nF,  $C_{B18}$  = 2.2 $\mu$ F,  $C_T$  = 1 $\mu$ F. Typical values are at  $V_M$  = +24V and  $T_A$  = +25°C, unless otherwise noted. Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                          | SYMBOL             | CONDITIONS                                            |                       | MIN | TYP  | MAX | UNITS |

|----------------------------------------------------|--------------------|-------------------------------------------------------|-----------------------|-----|------|-----|-------|

| IREF Pin Regulator<br>Voltage Reference<br>Voltage | V <sub>IREF</sub>  |                                                       |                       |     | 1    |     | V     |

| Enable Time                                        | t <sub>EN</sub>    | From Enable rising 6                                  | edge to SPI ready     |     |      | 0.5 | ms    |

| Wake-Up Time                                       | twu                | From ACTIVE = 1 to OUT_ active                        | Normal operation      |     |      | 2.5 | ms    |

| Disable Time                                       | t <sub>DIS</sub>   | From ENABLE fallin tristate                           | g edge to OUT_        |     |      | 2.5 | ms    |

| Dead Time                                          | t <sub>DEAD</sub>  | Dead zone is inserted Feed through                    | ed to prevent Current |     | 200  |     | ns    |

|                                                    |                    | FREQ_CFG = 11,                                        | SRC_ = 0              |     | 8.0  |     |       |

| Blanking Time                                      | <b>+</b>           | FREQM = 0                                             | SRC_ = 1              |     | 1.4  |     | ]     |

| Dialiking Time                                     | t <sub>BLANK</sub> | · · · · = · · · · · · · · · · · · · ·                 |                       |     | 1    |     | μs    |

|                                                    |                    |                                                       | SRC_ = 1              |     | 1.75 |     |       |

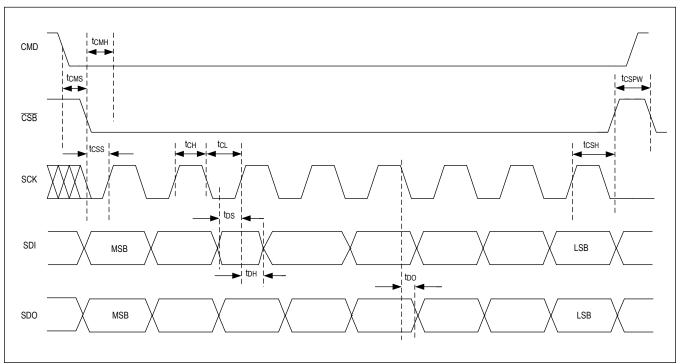

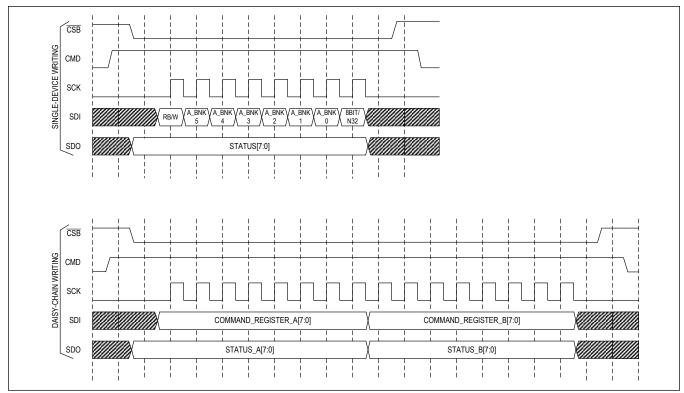

| SPI SPECIFICATIONS (E                              | igure 1)           |                                                       |                       |     |      |     |       |

| SCK Clock Period                                   | t <sub>CLK</sub>   |                                                       |                       | 100 |      |     | ns    |

| SCK Pulse-Width High                               | tсн                |                                                       |                       | 30  |      |     | ns    |

| SCK Pulse-Width Low                                | t <sub>CL</sub>    |                                                       |                       | 30  |      |     | ns    |

| CSB Fall-to-CLK Rise Time                          | t <sub>CSS</sub>   |                                                       |                       | 30  |      |     | ns    |

| CSB Hold Time                                      | tсsн               |                                                       |                       | 30  |      |     | ns    |

| CSB Pulse-Width High                               | t <sub>CSPW</sub>  |                                                       |                       | 30  |      |     | ns    |

| SDI Setup Time                                     | t <sub>DS</sub>    |                                                       |                       | 10  |      |     | ns    |

| SDI Hold Time                                      | t <sub>DH</sub>    |                                                       |                       | 10  |      |     | ns    |

| SDO Propagation Delay                              | t <sub>DO</sub>    | $310\Omega$ // 20pF connected to 3.3V supply (Note 2) |                       |     |      | 40  | ns    |

| CMD Setup Time                                     | t <sub>CMS</sub>   |                                                       |                       | 20  |      |     | ns    |

Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

Note 2: The rising edge on the SDO pin depends on the pullup resistor connected to the pin and on the parasitic stray capacitance. The RC time constant can limit the SPI maximum speed. For fast SPI, the stray capacitance must be minimized and a low-value resistive pullup must be selected.

Note 3: Guaranteed by design, not production tested.

Figure 1. SPI Timing Diagram

# **Pin Configuration**

### MAX22200/MAX22200A

### **Pin Description**

| PIN                              | NAME                                                                                                | FUNCTION                                                                                                                                                      | TYPE |

|----------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1                                | FAULT                                                                                               | Open-Drain Output. Pulled logic-low with fault condition; open-drain output requires an external pullup resistor.                                             | OD   |

| 2                                | CMD                                                                                                 | Command Logic Input. Drive this pin high to write the Command register. Drive this pin low to write/read all the other registers. Internal pulldown.          | INP  |

| 3                                | CSB                                                                                                 | Active-Low SPI Chip Select. Internal pullup current.                                                                                                          | INP  |

| 4 10                             | GND                                                                                                 | Signal Cround                                                                                                                                                 | GND  |

| 4, 19                            | GND                                                                                                 | Signal Ground                                                                                                                                                 | GND  |

| 5                                | SCK                                                                                                 | SPI Clock Input. Rising edge clocks data into the part for write operations. Falling edge clocks data out of the part for read operations. Internal pulldown. | INP  |

| 6                                | SDI                                                                                                 | SPI Data In from Controller. Internal pulldown.                                                                                                               | INP  |

| 7                                | SDO                                                                                                 | SPI Data Output. Pulled logic-low SPI logic output; open-drain output requires an external pullup resistor.                                                   | OD   |

| 8                                | TRIGA                                                                                               | Trigger Logic Input. Half-bridges 0, 2, 4, 6 asynchronous trigger input. Internal pulldown.                                                                   | INP  |

| 17                               | TRIGB                                                                                               | Trigger Logic Input. Half-bridges 1, 3, 5, 7 asynchronous trigger input. Internal pulldown.                                                                   | INP  |

|                                  |                                                                                                     |                                                                                                                                                               | PWR  |

|                                  |                                                                                                     |                                                                                                                                                               | PWR  |

| 9, 12, 13, 16,<br>25, 28, 29, 32 | Supply Voltage Input. Bypass all V <sub>M</sub> pins to GND with two 0.1µF local ceramic            | PWR                                                                                                                                                           |      |

|                                  | M capacitors close to pins 12, 13 and pins 28, 29, respectively plus a 10μF electrolytic capacitor. |                                                                                                                                                               |      |

|                                  |                                                                                                     |                                                                                                                                                               | PWR  |

|                                  |                                                                                                     |                                                                                                                                                               | PWR  |

# **Pin Description (continued)**

| PIN | NAME            | NAME FUNCTION                                                                                                                                                                                                                                                       |     |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |                 |                                                                                                                                                                                                                                                                     | PWR |

|     |                 |                                                                                                                                                                                                                                                                     | PWR |

| 18  | IREF            | Current Regulation Reference. Connect a $15k\Omega$ to $100k\Omega$ resistor from IREF to GND to set the full-scale current for all the channels in CDR mode.                                                                                                       |     |

| 20  | V <sub>18</sub> | 1.8V LDO Regulator Output. Bypass to GND with a 2.2µF ceramic capacitor.                                                                                                                                                                                            | PWR |

| 21  | ENABLE          | Enable. Logic-high to enable device; logic-low to enter low-power sleep mode; internal pulldown resistor.                                                                                                                                                           | INP |

| 22  | C <sub>FN</sub> | N Side Charge-Pump Capacitor. Connect a 22nF, $V_M$ -rated ceramic capacitor from $C_{FN}$ to $C_{FP}$ .                                                                                                                                                            | PWR |

| 23  | C <sub>FP</sub> | P Side Charge-Pump Capacitor. Connect a 22nF, V <sub>M</sub> -rated ceramic capacitor from C <sub>FN</sub> to C <sub>FP</sub> .                                                                                                                                     |     |

| 24  | V <sub>CP</sub> | Charge-Pump Output. Connect a 1µF, 5V or greater ceramic capacitor to V <sub>M</sub> .                                                                                                                                                                              |     |

| 31  | OUT0            | Driver Output Channel 0                                                                                                                                                                                                                                             |     |

| 30  | OUT1            | Driver Output Channel 1                                                                                                                                                                                                                                             |     |

| 27  | OUT2            | Driver Output Channel 2                                                                                                                                                                                                                                             | OUT |

| 26  | OUT3            | Driver Output Channel 3                                                                                                                                                                                                                                             | OUT |

| 10  | OUT4            | Driver Output Channel 4                                                                                                                                                                                                                                             | OUT |

| 11  | OUT5            | Driver Output Channel 5                                                                                                                                                                                                                                             | OUT |

| 14  | OUT6            | Driver Output Channel 6                                                                                                                                                                                                                                             |     |

| 15  | OUT7            | Driver Output Channel 7                                                                                                                                                                                                                                             | OUT |

| _   | EP              | Power GND Exposed Pad. The exposed pad (thermal pad) is the Power GND of the device and must be electrically connected to the board GND. For good thermal dissipation, use large ground planes on multiple layers and multiple nearby vias connecting those planes. | GND |

### **Detailed Description**

The MAX22200/MAX22200A octal 36V serial-controlled solenoid drivers. Each channel features a low-impedance  $(200 \text{m}\Omega \text{ typ})$ , push-pull output stage with a sink-and-source driving capability and up to 14 M M M M M driving current. A serial peripheral interface (SPI) that also supports daisy-chain configurations is provided to individually control each channel.

The devices' half-bridges can be configured as low-side drivers or as high-side drivers. Moreover, pairs of half-bridges can be paralleled to double the driving current or can be configured as full-bridges to drive up to four latched valves (bistable valves) or four brushed DC motors.

Two control methods are supported: voltage drive regulation (VDR) and current drive regulation (CDR). In VDR, the devices output a PWM voltage in which the duty cycle is programmed using SPI. For a given supply voltage and solenoid resistor, the output current is proportional to the programmed duty cycle. In CDR, an internal integrated lossless current-sensing (ICS) circuit monitors the output current and compares it with an internal programmable reference current.

For optimal power management in solenoid drive applications, the excitation drive level ( $I_{HIT}$ ), the hold drive level ( $I_{HOID}$ ), and the excitation drive time ( $I_{HIT}$ ) can be individually configured for each channel.

The MAX22200/MAX22200A features a full set of protections and diagnostic functions, including overcurrent protection (OCP), thermal shutdown (TSD), undervoltage lockout (UVLO), open-load detection (OL), and detection of plunger movement (DPM). A fault indication pin (FAULT) signals fault events, and diagnostic information is stored in the FAULT register. The MAX22200A provide a safe selective clear on read procedure for the FAULT register. It is the preferred version for new design. The MAX22200 offers a standard clear on read that can be used to determine firmware compatibility.

Due to their versatility, serial interface control, high efficiency, and small package size, the MAX22200/MAX22200A are particularly suited for solenoid driver applications (valve control, relays control, etc.) in which low power consumption and a high level of integration are required.

The MAX22200/MAX22200A are available in a compact 5mm x 5mm, 32-pin TQFN package and operate over the -40°C to +85°C temperature range.

#### **Enable Logic Input**

Drive the ENABLE pin logic-high to enable the device. Drive the ENABLE pin logic-low to disable the device. A pulldown resistor (1.5 M $\Omega$  typ) ensures the part is disabled if the ENABLE is not driven. When ENABLE is low, the device power consumption is minimized and the current consumption from V<sub>M</sub> is less than 11 $\mu$ A. It takes 0.5ms to enable the device SPI communication from the ENABLE pin rising.

#### Functional Description - Two Levels Drive Sequence for Solenoid Valves

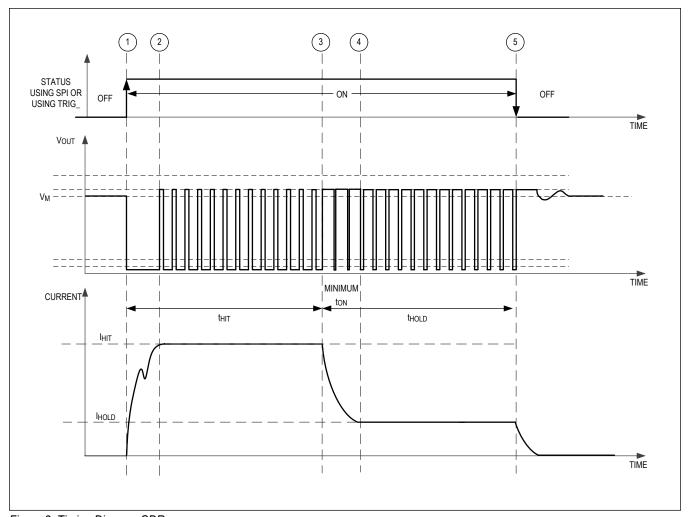

The MAX22200/MAX22200A feature a two-level drive sequence for optimal control of solenoid valves. Figure 2 and Figure 3 show typical voltage and current waveforms of the MAX22200/MAX22200A when driving a solenoid with the VDR and CDR, respectively. Both figures refer to low-side driving applications in which the solenoid is tied to the positive rail ( $V_M$ ). For high-side driving, only VDR is supported.

HIT current ( $I_{HIT}$ ), HOLD current ( $I_{HOLD}$ ), and HIT time ( $t_{HIT}$ ) can be configured for each channel by writing to the correspondent 32-bit configuration register (CFG\_CHx). The HOLD Time ( $t_{HOLD}$ ) is not internally programmable and must be externally controlled. Each driver can be individually controlled independently from the others.

Depending on the content of the TRGnSPI bit in the configuration register of that specific channel, the driver channels can be activated/deactivated either through SPI (ONCH\_ bits of the Status Register) or through a logic input signal on pins TRIGA and TRIGB. In the latter case, one (or more) among channels 0, 2, 4, 6 can be triggered by the logic input TRIGA. Similarly, one (or more) among channels 1, 3, 5, 7 can be triggered by using the logic input TRIGB.

With reference to Figure 2 and Figure 3, the excitation starts (point 1) when the channel driver is activated either through SPI or through the TRIG\_ logic input. After a short analog delay, the driver is enabled and the current ramps up to I<sub>HIT</sub>. Moreover, the t<sub>HIT</sub> counter begins to count. The dip occurring in both the figures between point 1 and point 2 represents the effect of the back electromotive force (BEMF) when the plunger moves. Notice that when CDR is used, the current ramps up faster since the driver duty cycle is set to a maximum until the I<sub>HIT</sub> level is reached. The current stabilizes around the target current level I<sub>HIT</sub> (point 2).

As soon as the  $t_{HIT}$  time elapses (point 3), the driver automatically changes the target current to  $I_{HOLD}$ , which is normally set significantly lower than  $I_{HIT}$ . The current starts decreasing until it reaches the regulated value (point 4). Notice that when CDR is used, the current decreases faster since the driver duty cycle is set to minimum  $t_{ON}$  until the  $I_{HOLD}$  level is reached. Finally, the sequence ends as soon as the channel is deactivated either through SPI or through the TRIG\_.

When the VDR is used, the output current slightly decreases both during the HIT and the HOLD time intervals. This behavior is representative of possible droops on the voltage supplies and/or of the increase of the solenoid resistance due to overheating during the excitation period. Due to the feedback close loop approach, CDR is less sensitive to this kind of environmental change and results in a more stable and constant current control.

Figure 2. Timing Diagram VDR

Figure 3. Timing Diagram CDR

#### Chopping Frequency (FREQM, FRQ\_CFG\_)

The MAX22200/MAX22200A feature an integrated oscillator, which sets the time base of the device and determines the chopping frequency both in VDR and in CDR. The oscillator frequency can be set either at 100kHz or at 80kHz depending on the FREQM bit in the STATUS register (global for all the channels).

In addition, two bits (FREQ\_CFG\_[1:0]) in the Configuration Register allows the user to configure the chopping frequency of each individual channel dividing down the oscillator frequency as shown in the <u>Table 1</u>.

**Table 1. Chopping Frequency**

| CHOPPING FREQUENCY |                    | CHOPPING FREQUENCY<br>f <sub>CHOP</sub> (kHz) |

|--------------------|--------------------|-----------------------------------------------|

|                    | FREQ_CFG[1:0] = 11 | 100                                           |

| FREQM = 0          | FREQ_CFG[1:0] = 10 | 50                                            |

|                    | FREQ_CFG[1:0] = 01 | 33.3                                          |

|                    | FREQ_CFG[1:0] = 00 | 25                                            |

| FREQM = 1          | FREQ_CFG[1:0] = 11 | 80                                            |

|                    | FREQ_CFG[1:0] = 10 | 40                                            |

|                    | FREQ_CFG[1:0] = 01 | 26.6                                          |

|                    | FREQ_CFG[1:0] = 00 | 20                                            |

#### **Slew-Rate Controlled Mode (SRC)**

Both in CDR and VDR modes, rise and fall edges can be slowed down to reduced electromagnetic emissions (EME). To configure one half-bridge in slew-rate controlled (SRC) mode, the SRC bit in the Configuration Register (CFG\_CH\_) must be set high. When SRC mode is enabled, the rise/fall edges are limited to about 200ns (typ) and OCP deglitch time is doubled. SRC mode is only available for low-side driver configurations and for switching frequencies less than 50kHz.

#### Min and Max Duty cycle

In both CDR and VDR mode, the duty cycle is constrained as described in <u>Table 2</u>. The minimum and maximum duty cycles depend on the selected switching frequency and on the slew-rate configuration (SRC bit).

**Table 2. Min and Max Duty Cycle**

| CHOPPING FREQUENCY<br>SRC = 0 |                           | CHOPPING FREQUENCY<br>f <sub>CHOP</sub> (kHz) | VDR/CDR<br>MIN DUTY<br>δ <sub>MIN</sub> | VDR/CDR<br>MAX DUTY<br>δ <sub>MAX</sub> |

|-------------------------------|---------------------------|-----------------------------------------------|-----------------------------------------|-----------------------------------------|

|                               | FREQ_CFG[1:0] = 11        | 100                                           | 8%                                      | 92%                                     |

| EDEOM - 0                     | FREQ_CFG[1:0] = 10        | 50                                            | 4%                                      | 96%                                     |

| FREQM = 0                     | FREQ_CFG[1:0] = 01        | 33.33                                         | 4%                                      | 96%                                     |

|                               | FREQ_CFG[1:0] = 00        | 25                                            | 4%                                      | 96%                                     |

|                               | FREQ_CFG[1:0] = 11        | 80                                            | 8%                                      | 92%                                     |

| EDEOM - 1                     | FREQ_CFG[1:0] = 10        | 40                                            | 4%                                      | 96%                                     |

| FREQM = 1                     | FREQ_CFG[1:0] = 01        | 26.66                                         | 4%                                      | 96%                                     |

|                               | FREQ_CFG[1:0] = 00        | 20                                            | 4%                                      | 96%                                     |

| СНОР                          | PING FREQUENCY<br>SRC = 1 | CHOPPING FREQUENCY<br>f <sub>CHOP</sub> (kHz) | VDR/CDR<br>MIN DUTY<br>δ <sub>MIN</sub> | VDR/CDR<br>MAX DUTY<br>δ <sub>MAX</sub> |

| FREQM = 0                     | FREQ_CFG[1:0] = 01        | 33.33                                         | 7%                                      | 93%                                     |

| FREQIVI = 0                   | FREQ_CFG[1:0] = 00        | 25                                            | 7%                                      | 93%                                     |

| FREQM = 1                     | FREQ_CFG[1:0] = 10        | 40                                            | 7%                                      | 93%                                     |

|                               | FREQ_CFG[1:0] = 01        | 26.66                                         | 7%                                      | 93%                                     |

|                               | FREQ_CFG[1:0] = 00        | 20                                            | 7%                                      | 93%                                     |

#### Voltage Drive Regulation (VDR)

To operate in VDR the VDRnCDR\_ bit in the Configuration Register must be set High (see the Register Map). When VDR is used, each individual channel can be programmed to output the desired PWM waveform during HIT and HOLD phases. The user can program the HIT and HOLD duty cycles ( $\delta = t_{ON} / t_{CHOP}$ ) with steps of 1% resolution.

The HIT and HOLD target duty cycles are preprogrammed in the Configuration Register for each channel as shown in Table 3. The duty cycle minimum and maximum values ( $\delta_{MIN}$ ,  $\delta_{MAX}$ ) are determined by the chopping frequency settings and by the SRC configuration bits as shown in Table 2.

**Table 3. VDR Duty Cycle**

| HIT CURRENT PROGRAMMING CONDITION  |                                        | OUTPUT DUTY CYCLE        |

|------------------------------------|----------------------------------------|--------------------------|

|                                    | = 0                                    | 0 duty cycle             |

|                                    | > 0, < δ <sub>MIN</sub>                | δ <sub>MIN</sub>         |

| HIT[6:0] <sub>DEC</sub>            | $\geq \delta_{MIN}, < \delta_{MAX}$    | HIT[6:0] <sub>DEC</sub>  |

|                                    | ≥ δ <sub>MAX</sub> , < 100             | δ <sub>ΜΑΧ</sub>         |

|                                    | ≥ 100                                  | 100% duty cycle          |

| HOLD CURRENT PROGRAMMING CONDITION |                                        | OUTPUT DUTY CYCLE        |

|                                    | = 0                                    | 0 duty cycle             |

|                                    | > 0, < δ <sub>MIN</sub>                | δ <sub>MIN</sub>         |

| HOLD[6:0] <sub>DEC</sub>           | $\geq \delta_{MIN}$ , $< \delta_{MAX}$ | HOLD[6:0] <sub>DEC</sub> |

|                                    | ≥ δ <sub>MAX</sub> , < 100             | δ <sub>ΜΑΧ</sub>         |

|                                    | ≥ 100                                  | 100% duty cycle          |

#### **Current Drive Regulation (CDR)**

To operate in CDR, the VDRnCDR\_ bit in the Configuration Register must be set Low (see the Register Map). This is also the default setting at power up. CDR is supported in low-side configurations only.

#### HIT and HOLD Current Setting (CDR)

When the CDR mode is used, the current can be controlled with 7-bit resolution. Because of the feedback approach, CDR results in more efficient power management when compared to VDR. In fact, unlike VDR, CDR requires no design margin for environmental parameter changes such as temperature, solenoid resistance variations, and droops on the supply. For a battery-powered system, this ultimately results in longer battery lifetime. The current loop of CDR regulates the coil current cycle-by-cycle. A non-dissipative accurate current sense is integrated so that no external sense resistors are needed.

The HIT and HOLD currents are configurable in the Configuration Register for each channel and the following equations apply as in <u>Table 4</u>.

Table 4. HIT and HOLD Current Setting (CDR)

| HIT CURREN                         | T PROGRAMMING CONDITION            | I <sub>TRIG</sub> PEAK CURRENT                                                 |  |

|------------------------------------|------------------------------------|--------------------------------------------------------------------------------|--|

|                                    | 0                                  | HS Switch ON, LS Switch OFF                                                    |  |

| HIT[6:0] <sub>DEC</sub>            | 0 < HIT[6:0] <sub>DEC</sub> < 127  | I <sub>HIT</sub> = HIT_[6:0] <sub>DEC</sub> / 2 <sup>7</sup> x I <sub>FS</sub> |  |

|                                    | 127                                | HS Switch OFF, LS Switch ON                                                    |  |

| HOLD CURRENT PROGRAMMING CONDITION |                                    | I <sub>TRIG</sub> PEAK CURRENT                                                 |  |

|                                    | 0                                  | HS Switch ON, LS Switch OFF                                                    |  |

| HOLD[6:0] <sub>DEC</sub>           | 0 < HOLD[6:0] <sub>DEC</sub> < 127 | $I_{HOLD} = HOLD_[6:0]_{DEC} / 2^7 \times I_{FS}$                              |  |

|                                    | 127                                | HS Switch OFF, LS Switch ON                                                    |  |

where, IFS is the full-scale current.

The CDR loop regulates the peak current (I<sub>TRIG</sub>). The average current (both for the HIT and HOLD currents) would be lower due to the current ripple.

#### Full-Scale Current Setting (IFS)

I<sub>FS</sub> is user configurable by setting the resistor connected between pin IREF and Ground per the following equation:

$$I_{FS} = K_{FS} \times \frac{1(V)}{RREF(\Omega)}$$

where,  $K_{\text{FS}}$  is a constant (gain factor) and RREF is the resistor connected between the IREF pin and GND.

The Gain factor  $K_{FS}$  depends on the HFS bit value in the configuration register (see the <u>Half Full-Scale (HFS)</u> section). If HFS\_ = 0 then  $K_{FS}$  = 15k, whereas if HFS = 1 then  $K_{FS}$  = 7.5k. The recommended operating range for RREF is from  $15k\Omega$  to  $100k\Omega$ .

#### Half Full-Scale Setting (HFS bit)

Whenever low driver-current levels are needed, it is possible to improve the current control accuracy and resolution by setting high the HFS bit in the Configuration Register. This can be done individually for each half-bridge. (This function is available for low-side applications only.)

When the HFS bit is set low (default), the driver On resistance is  $R_{ON} = 0.2\Omega$ , the full-scale current can be set up to  $I_{FS} = 1A$ . The current control accuracy is shown in the <u>Electrical Characteristics</u> section.

When the HFS bit is set high, the driver On resistance is doubled ( $R_{ON} = 0.4\Omega$ ) whereas the maximum full-scale and RMS currents are halved ( $I_{FS} = 0.5A$ ).

For solenoids or brushed DC motors requiring less than 0.5A peak, the half full-scale setting results in a more accurate current sensing and hence better control accuracy and resolution. As a drawback, the efficiency of the driver worsens because of the higher driver On resistance.

#### **Fixed-Frequency Current Control**

The current control loop regulates, cycle-by-cycle, the driver current by using a fixed-frequency topology and an integrated non-dissipative current-sensing. CDR is available only in low-side drive mode.

At the beginning of the chopping clock period, the low side FET is on and the current builds up in the coil at a rate dependent on the supply voltage and on the inductance of the winding. When the current hits the current regulation threshold, the low-side FET is turned off, whereas the high-side FET is turned on and the winding current decays. This status lasts until the next on cycle is triggered by the internal chopping clock. See the <u>Chopping Frequency</u> section for information about the setting of the chopping frequency.

The current ripple is inversely proportional to the chopping frequency. To reduce the ripple and improve the average current control, consider a high chopping frequency. A first order approximation of the ripple can be achieved assuming that the off time is significantly shorter than the solenoid time constant ( $\tau = \frac{L}{R}$ ) so that the ripple is small compared with the average current. Under this assumption, it can be found that the peak-to-peak ripple is given by:

$$\Delta I \cong \frac{1}{\frac{L}{R} \times f_{CHOP}} \times \left(1 - \frac{I_{TRIG}}{\frac{V_M}{R}}\right)$$

where.

$\Delta I = Peak-to-peak ripple$

ITRIG = Threshold current

V<sub>M</sub> = Supply voltage

L = Coil inductance

R = Resistance

Blanking delays and filters are integrated to prevent false triggers due to switching noise. They have not been accounted in the above equations .

#### HIT Excitation Time (t<sub>HIT</sub>)

The excitation time can be programmed among 256 different values by programming bits HIT\_T\_[7:0] in the configuration register. See the *Register Map*.

The HIT time (t<sub>HIT</sub>) is inversely proportional to the chopping frequency (see the <u>Chopping Frequency</u> section) and can

be calculated according to  $\underline{\text{Table 5}}$  in which  $f_{\text{CHOP}}$  is the oscillator frequency (in Hertz). For instance, with the oscillator running at  $f_{\text{CHOP}}$  = 20KHz, the  $t_{\text{HIT}}$  ranges from  $t_{\text{MIN}}$  = 0ms to  $t_{\text{MAX}}$  = 508ms with 2ms time resolution. As explained in the  $\underline{\textit{Functional Description}}$  paragraph, the  $t_{\text{HIT}}$  counter can be triggered either by the SPI programming command or by an external trigger signal.

## **Table 5. HIT Excitation Time (t<sub>HIT</sub>)**

| CONFIGURATION BITS                       | t <sub>HIT</sub> VALUE                             | COMMENTS                    |

|------------------------------------------|----------------------------------------------------|-----------------------------|

| $HIT_T_{[7:0]DEC} = 0$                   | t <sub>HIT</sub> = 0                               | No Hit Time                 |

| HIT_T_[7:0] <sub>DEC</sub> from 1 to 254 | $t_{HIT} = HIT_T_[7:0]_{DEC} \times 40 / f_{CHOP}$ |                             |

| HIT_T_[7:0] <sub>DEC</sub> = 255         | t <sub>HIT</sub> = ∞                               | Continuous I <sub>HIT</sub> |

#### **Supported Driver Configurations**

The MAX22200/MAX22200A provide for flexibility. Their eight independent half-bridges can be configured in different ways to address different applications.

- 1. It is possible to set each half-bridge as a low-side driver or as an high-side driver

- 2. It is possible to use a pair of half-bridges in parallel to double the driving current capability.

- 3. It is possible to use a pair of half-bridges to make a full-bridge and drive latched valves or brushed DC motors

These configurations must be set just after the power-up by writing the status register.

#### Low-Side/High-Side Operations (HSnLS)

The MAX22200/MAX22200A support either low-side or high-side drive modes corresponding to loads connected to the positive rail or to ground respectively. The HSnLS bit in the Configuration Register must be set low (default) for low-side drive operation or high for high-side drive operations. For high-side drive operations, CDR is not supported and channels are controlled in VDR mode only. Moreover, SRC, HFS, and DPM functions are not supported in high-side operations.

#### **Half-Bridge Parallelization**

The user can possibly connect pairs of channels in parallel in order to double the driving current. The pairs 0–1, 2–3, 4–5, and 6–7 can be used in parallel by connecting the corresponding output pins together. See the *Application Diagram*

. To configure the pair x-y in Parallel mode, the user must write bit CMxy[10] = 01 into the STATUS[15:8] register. See the *Register Map*.

When one pair of half-bridges is used in Parallel mode, the Configuration Register setting of the half-bridge with the lower identification number control both the half-bridges and the other one is ignored. For instance, considering the pair 0–1 in Parallel mode, all the settings are taken from the configuration register of Channel 0 while the configuration register of Channel 1 is ignored.

The activation/deactivation (On/Off command) of the two half-bridges in Parallel mode remains independent. The TRGnSPI bits in the Configuration Register enables/disables the drivers as shown in <u>Table 6</u>:

Table 6. TRGnSPI in Half-Bridge Parallel Mode

| TRGnSPly | TRGnSPlx | CONTROL MODE                                                     |  |

|----------|----------|------------------------------------------------------------------|--|

| 0        | 0        | hannels controlled by SPI (both ONCHx and ONCHy set logic high)  |  |

| 0        | 1        | Channels controlled by TRIGA                                     |  |

| 1        | 0        | Channels controlled by TRIGB                                     |  |

| 1        | 1        | Channels controlled by SPI (both ONCHx and ONCHy set logic high) |  |

#### **Full-Bridge Configuration**

It is possible to configure the half-bridges pairs 0–1, 2–3, 4–5, and 6–7 to make full-bridges and drive latched (bistable) solenoid valves or even brushed-bipolar DC motors. One pair x–y is declared as a full-bridge by setting bits CMxy\_[1:0] = 10 in the Status Register (refer to the Register Map)

When in Full-Bridge mode, the full-bridge operates in 4 different statuses depending on the content of bits ONCHy and ONCHx in the Status Register as described in <u>Table 7</u>:

**Table 7. Full-Bridge Configuration**

|       | (x,y) = (0,1), (2,3), (4,5), (6,7) |                       |                       |             |  |

|-------|------------------------------------|-----------------------|-----------------------|-------------|--|

| ONCHy | ONCHx                              | OUTx                  | OUTy                  | DESCRIPTION |  |

| 0     | 0                                  | Hi Z                  | Hi Z                  | Hi Z        |  |

| 0     | 1                                  | VM                    | VDR/CDR<br>Y settings | Forward     |  |

| 1     | 0                                  | VDR/CDR<br>X settings | VM                    | Reverse     |  |

| 1     | 1                                  | GND                   | GND                   | Brake       |  |

In <u>Table 7</u>, the setting parameters for the control are taken from the configuration register of Channel Y in Forward mode and from the configuration register of Channel X in Reverse mode. For instance, considering the pair 0–1 in Full-Bridge mode, when [ONCHy, ONCHx] = [0,1] (forward), the control parameters depend on the content of the Configuration Register of Channel Y. Vice versa, when [ONCHy, ONCHx] = [1,0] (reverse), then the control depends on the content of the Configuration Register of Channel X. In this way, it is possible to use different currents levels or timings for latch/ unlatch operations of a latched valve. Notice that the HSnLS bit is ignored for full-bridge operations.

Finally, in Full Bridge Operations, the TRGnSPI bits in the Configuration register enables/disable the drivers as shown in Table 8:

Table 8. TRGnSPI in Full-Bridge Mode

| TRGnSPly | TRGnSPlx | CONTROL MODE                       |

|----------|----------|------------------------------------|

| 0        | 0        | Channels controlled by SPI         |

| 0        | 1        | Channels controlled by SPI         |

| 1        | 0        | Channels controlled by SPI         |

| 1        | 1        | Channels controlled by TRIGA/TRIGB |

#### **Protection Circuits**

The MAX22200 features a full set of protections including undervoltage (UVLO), overcurrent (OCP), and overtemperature (OVT). The device also features diagnostic functions such as open-load detection (OL), detection of plunger movement (DPM), hit <u>current</u> not reached detection (HHF), and communication error detection (COMF). An open-drain fault indication pin (FAULT) is provided to signal detected faults out to the <u>controller</u>. Each of the above mentioned failures (with the exception of the COMF) are by default signaled out to the <u>FAULT</u> pin. Fault indication can be masked by setting high the <u>corresponding</u> bits into the Status registers (STATUS[15:8]). When a fault is masked, a fault event does not activate the <u>FAULT</u> pin.

#### **Overcurrent Protection (OCP)**

The overcurrent protection protects the device from short-circuits of the driver outputs to the rails ( $V_M$  and GND) or among each other. When the output exceeds OCP trigger levels, the corresponding channel is automatically turned Off and the FAULT output is asserted (active low). Moreover, the corresponding OCP flag in the Fault register is set high for diagnostic purposes. Reading the Fault register clears the Flag and deasserts the FAULT output, but does not turn on the failed channel. Once the flag is cleared, the normal operations are resumed by turning the failed channel Off in the Status Register.

#### Open-Load Detection (OL)

One bit in the configuration register is used to either enable or disable the OL detection function. Provided that this function is enabled, whenever the load is disconnected, a small source/sink current pulls the output node up/down depending on low-/high-side operation mode set for the channel. If the voltage on the output pin is sensed to be less than +2V for low-side configuration or greater than  $V_M$  - 2V for high-side configuration, then an open-load condition is reported. Consequently, the corresponding flag in the Fault register is set high and the FAULT output is asserted (if this fault is not masked). Open-load faults are automatically cleared and the FAULT pin released if the corresponding output is turned on or if the Fault register is read.

#### **Detection of Plunger Movement (DPM)**

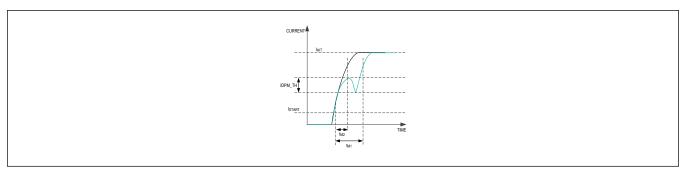

The MAX22200/MAX22200A feature a novel diagnostic function which detects whether the plunger inside the armature successfully moves once the valve is activated. This function is referred as detection of plunger movement (DPM) and it is a useful tool to identify malfunctioning valves and allow a prompt repair or replacement of the defective valve.

Figure 4 shows the typical current profile exhibited by a working valve (blue curve) and a stuck valve (black curve). When the valve is actuated the solenoid current ramps up from zero to the programmed excitation current level I<sub>HIT</sub>. If the valve works properly, the current profile is not monotonic but shows a drop due to the BEMF generated by the movement of the plunger inside the solenoid.

The amplitude of the drop is characteristic of each valve and is almost independent from external variables such as supply voltage and temperature. When enabled, the DPM function detects the presence of the drop during the excitation phase. If the drop is not revealed a fault indication is output on FAULT pin (if not masked) and a fault bit is asserted in the fault register.

The DPM starts monitoring the current above a user-programmable initial current ( $I_{START}$ ). The search ends as soon as the programmed excitation level ( $I_{HIT}$ ) is reached. The user can program the DPM threshold ( $I_{DPM\_TH}$ ) as a fraction of the full-scale current. Finally, it is possible to program a debounce time to avoid false detection caused by environmental noise. DPM settings are global and apply to all channels. See the  $\underline{\mathit{CFG\_DPM}}$  section for further details about DPM configuration.

The detection can fail if the drop is not pronounced enough or if the currents ramps up too quickly. The DPM function is activated by setting logic-high for one bit in the configuration register for each individual channel.

Figure 4. Detection of Plunger Movement

#### Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all outputs are disabled. One flag bit in the Fault register is set high and the FAULT pin is driven low. Once the die temperature has fallen to a safe level, operation automatically resumes. The FAULT pin is released but the flag bit remains set to '1' until the fault register is read.

#### **Undervoltage Lockout (UVLO)**