|                                           | 9                                              | SELECTE                           | ED ITEI          | M DRAWING                                                        |

|-------------------------------------------|------------------------------------------------|-----------------------------------|------------------|------------------------------------------------------------------|

|                                           |                                                |                                   |                  |                                                                  |

|                                           |                                                |                                   |                  | ANALOG<br>DEVICES                                                |

| Unless otherwise specified DIMENSIONS ARE | TOLERANCES:<br>.XX +/- 0.010<br>.XXX +/- 0.005 | Drawing practices per <b>ASME</b> |                  | 11.17 GHz to 12.02 GHz, O w/ Half Frequency Output & Divide-By-4 |

| IN INCHES (MM)                            | .XXXX +/- 0.002<br>ANGLES+/5 DEG               | Y14.100                           | SIZE<br><b>A</b> | DRAWING NUMBER SID00087                                          |

SID000087

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

#### 1. SCOPE

#### 1.1. <u>Scope</u>

This drawing establishes the requirements for the 11.17 GHz to 12.02 GHz, GaAs, InGaP, HBT, MMIC, VCO w/ Half Frequency Output & Divide-by-4, assembled hermetically in the LH250 package, to be screened in accordance with MIL-PRF-38535, to the requirements specified in 4.1, 4.2, and 4.3 herein.

#### 1.2. Analog Devices Part Number

Generic Part Number

ADH514S

Screened Part Number

HMC8618LH250

#### 2. APPLICABLE DOCUMENTS

# 2.1. Government Documents

Unless otherwise specified, the following drawings and standards, of the issue in effect on the date of the accepted purchase order, in the Department of Defense Index of Specifications and Standards (DODISS) and supplement thereto, shall form a part of this drawing to the extent specified herein.

## **DEPARTMENT OF DEFENSE TEST METHOD STANDARD**

MIL-STD-883 Microcircuits

# **DEPARTMENT OF DEFENSE PERFORMANCE SPECIFICATIONS**

MIL-PRF-38535 Integrated Circuits (Microcircuits) Manufacturing, General Specification For

## 2.2. Non-Government Documents

The following documents, of the issue in effect on the date of the purchase order, form a part of this drawing to the extent specified herein:

# **Analog Devices Inc.**

ADI Standard Space Products Program – Enhanced Class Q

HMC514LP5 / 514LP5E Data Sheet Commercial Product Datasheet v03.0811 (Reference Only)

# 3. REQUIREMENTS

## 3.1. General Requirements

The devices delivered shall comply to this specification.

# 3.2. <u>Design Construction and Physical Dimensions</u>

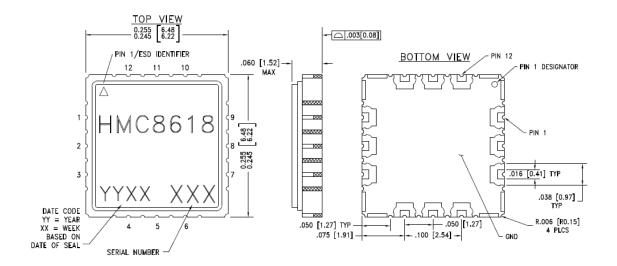

The design construction and physical dimensions shall be as defined in Figure 1 herein.

### 3.3. Traceability

Each delivered device shall be traceable to the wafer lot and wafer number. Inspection lot records shall be maintained to provide traceability to the specific wafer and wafer lot from which the chips originated as well as traceability to package and materials.

#### 3.4. Burn-In and Life Test Circuit

The burn-in and life test circuit and conditions shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test methods 1005 and 1015 per MIL-STD-883.

#### 4. QUALITY ASSURANCE PROVISIONS

## 4.1. Wafer Lot Acceptance Testing

The wafer lot acceptance testing shall consist of Class Level S inspections per MIL-STD-883 TM 5007.

#### 4.2. Flight Screening Requirements

Flight screening requirements shall be per the ADI Standard Space Products Program's Enhanced Class Q model screening flow.

#### 4.2.1. Electrical Test Requirements

Electrical test requirements are defined in Table I herein.

## 4.2.2. Electrical Performance Characteristics

Electrical performance characteristics are specified on Table II herein.

#### 4.2.3. Burn-In Delta Requirements

Pre and Post Burn-In Electrical test and delta parameters shall consist of the tests specified in Table III herein.

## 4.3. Quality Conformance Inspection (QCI)

Group B, Group C, and Group D tests shall be performed per the ADI Standard Space Products Program's Enhanced Class Q model Quality Conformance Inspection sampling plan.

# 4.3.1. Post Steady State Life Electrical Test

Post steady state life electrical tests shall consist of the tests specified per Table II tested at room temperature only. Devices must meet delta parameter requirements in accordance with Table III herein.

## 5. ENHANCED CLASS Q MODEL SCREENING FLOW AND QCI EXCEPTIONS

The manufacturing flow described in the ADI STANDARD SPACE PRODUCTS PROGRAM is to be considered a part of this specification.

## 5.1. Wafer Fabrication

Foundry information is available upon request.

## 5.2. Group B

Subgroup 2: Resistance to solvents is not applicable.

Subgroup 5: Qty/Acc = 5/0.

## 5.3. Group C

Subgroup 1: Qty/Acc = 5/0.

# 5.4. Group D

Subgroup 3: Qty/Acc = 5/0.

Subgroup 4: Qty/Acc = 5/0.

Subgroup 5: Not applicable.

Subgroup 7: Not applicable.

Subgroup 8: Not applicable.

Subgroup 9: Not applicable

#### 6. PREPARATION FOR DELIVERY

The preparation for delivery, packaging, preservation, ESD protection and handling shall be in accordance with MIL-PRF-38535.

## 6.1. Part Marking

Devices shall be marked as specified on Figure 1 herein.

# 6.2. <u>Inspection Data Requirements</u>

The following data shall accompany each shipment.

- a. A Certificate of Conformance (C of C) certifies that the lot(s) meets all requirements of this specification.

- b. Wafer Lot Acceptance data including photos from SEM Inspection defined in 4.1 herein.

- c. Summary of electrical test requirements defined in 4.2 herein.

- d. Summary of QCI results defined in 4.3 herein.

- e. Failure Analysis with photos (If applicable).

- f. A cover sheet indicating the following purchasing information:

- 1. Customer purchase order number.

- 2. Analog Devices part number.

- 3. Part lot identification codes.

- 4. Date & quantity shipped.

**TABLE I: ELECTRICAL TEST REQUIREMENTS**

| Test Requirement                        | Subgroups (in accordance with MIL-PRF-38535, Table III) |  |

|-----------------------------------------|---------------------------------------------------------|--|

| Interim Electrical Parameters           | 1, 4                                                    |  |

| Final Electrical Parameters             | 1, 4 <u>1/2</u> /                                       |  |

| Group A Electrical Parameters           | 1, 2, 3, 4, 5, 6                                        |  |

| Group C End-Point Electrical Parameters | 1, 4 <u>2</u> /                                         |  |

| Group D End-Point Electrical Parameters | 1, 4                                                    |  |

TABLE I Notes:

# TABLE II: ELECTRICAL PERFORMANCE CHARACTERISTICS (-40 °C, +25 °C AND +85 °C)

| Parameter                  | Conditions <u>1/3</u> /    | Group A   | Limits |       | Units  |  |

|----------------------------|----------------------------|-----------|--------|-------|--------|--|

| Parameter                  | Unless otherwise specified | Subgroups | Min    | Max   | Offics |  |

| Fraguency Pange            | Vtune = 1V                 | 4         |        | 11.17 | GHz    |  |

| Frequency Range            | Vtune = 12V                | 4         | 12.02  |       | GHz    |  |

| Pout <u>2</u> /            |                            | 4         | +2     |       | dBm    |  |

| Pout/2 <u>2</u> /          |                            | 4         | +5     |       | dBm    |  |

| Pout/4 <u>2</u> /          |                            | 4         | -10    |       | dBm    |  |

| SSB Phase Noise <u>2</u> / | 10 kHz offset              | 4         |        | -82   | dBc/Hz |  |

| Supply Current             |                            | 1         |        | 290   | mA     |  |

TABLE II Notes:

# TABLE III: BURN-IN/LIFE TEST DELTA LIMITS 1/2/3/

| Parameter      | Test Conditions | Delta Limits | Units |

|----------------|-----------------|--------------|-------|

| Pout           | Per Table II    | ± 1          | dB    |

| Supply Current | rei labie ii    | ± 10         | %     |

TABLE III Notes:

$<sup>\</sup>underline{1}\!\!/\!$  PDA applies to Table I subgroup 1 and Table III delta parameters.

<sup>2/</sup> See Table III for delta parameters.

<sup>1/</sup> Limits apply at +25 °C only with Vcc1 = Vcc2 = +3V. 2/ It shall be measured with Vtune at 1V and 12V only.

$<sup>\</sup>overline{3}$ / -40 °C and +85 °C (subgroups 2, 3, 5 and 6) shall be Read and Record only.

<sup>1/</sup> Delta test is performed at T<sub>A</sub> = +25 °C only.

2/ Table II limits will not be exceeded.

3/ Deltas calculated at pre/post 240 hours and post 240 hours / post1000 hours.

#### NOTES:

- 1. PACKAGE BODY MATERIAL: CERAMIC & KOVAR

- LEAD AND GROUND PADDLE PLATING: GOLD 40-80 MICROINCHES.

- 3. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 4. LEAD SPACING TOLERANCE IS NON-CUMULATIVE.

- 5. CHARACTERS TO BE LASER MARKED WITH .018"MIN to .030"MAX HEIGHT REQUIREMENTS. UTILIZE MAXIMUM CHARACTER HEIGHT BASED ON LID DIMENSIONS AND BEST FIT. LOCATE APPROX. AS SHOWN.

- 6. PAD BURR LENGTH 0.15mm MAX. PAD BURR HEIGHT 0.25mm MAX.

- ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 8. THE SOLDER FILLET BETWEEN PACKAGE AND COVER IS PART OF THE DESIGN SEAL AREA.

| Pin # | Function |

|-------|----------|-------|----------|-------|----------|-------|----------|

| 1     | RFOUT/4  | 4     | RFOUT/2  | 7     | RFOUT    | 10    | GND      |

| 2     | GND      | 5     | GND      | 8     | Vcc2     | 11    | GND      |

| 3     | Vcc1     | 6     | GND      | 9     | GND      | 12    | Vtune    |

Average Weight: 0.25 grams

Figure 1 – Device Outline for the HMC8618LH250

# **ORDERING GUIDE**

| Model        | Temperature Range | Package Description                            | Package Option |

|--------------|-------------------|------------------------------------------------|----------------|

| HMC8618LH250 | −40 °C to +85 °C  | 12-Lead Ceramic Hermeric Leadless Chip Carrier | LH250 (E-12-6) |

# **Revision History**

| Revision History |                                      |            |  |  |

|------------------|--------------------------------------|------------|--|--|

| Rev              | Description of Change                | Date       |  |  |

| Α                | Initial release                      | 04/16/2025 |  |  |

| В                | B Updated Section 4.3.1 and Figure 1 |            |  |  |

|                  |                                      |            |  |  |