# 0.68V Power Supply Using MAX15118 as a Current-Mode Step-Down Regulator

MAXREFDES1020

#### Introduction

The MAX15118 high-efficiency, current-mode step-down regulator with integrated power switches operates from 2.7V to 5.5V and delivers up to 18A output current in a small 2mm x 3mm package. The MAX15118 offers excellent efficiency with skip mode capability at light-load conditions, yet provides unmatched efficiency under heavy load conditions. The combination of small size and high efficiency makes this device suitable for both portable and nonportable applications.

The MAX15118 uses a current-mode control architecture with a high-gain transconductance error amplifier, which allows a simple compensation scheme and enables a cycle-by-cycle current limit with fast response to line and load transients. A factory-trimmed switching frequency of 1MHz (PWM operation) allows for a compact, all-ceramic capacitor design.

Integrated switches with low on-resistance ensure high efficiency at heavy loads while minimizing critical inductances.

Other features include the following:

- ±1% Feedback Accuracy Over Load, Line, and Temperature

- Input Undervoltage Lockout

- Programmable Soft-Start

- Adjustable Soft-Start

- External Reference Input

- Selectable Skip Mode Option for Improved Efficiency at Light Loads

## **Hardware Specification**

A current-mode synchronous buck is demonstrated using the MAX15118 for a 0.68V DC output application. The power supply delivers up to 6A at 0.68V. Table 1 shows an overview of the design specification.

**Table 1. Design Specification**

| PARAMETER             | SYMBOL            | MIN       | MAX |

|-----------------------|-------------------|-----------|-----|

| Input Voltage         | V <sub>IN</sub>   | 2.7V 4.5V |     |

| Frequency             | f <sub>SW</sub>   | 1MHz      |     |

| Efficiency            | η                 | 86%       |     |

| Output Voltage        | V <sub>OUT</sub>  | 0.68V     |     |

| Output Voltage Ripple | ΔV <sub>OUT</sub> | 20mV      |     |

| Output Current        | I <sub>OUT</sub>  | 0A        | 6A  |

| Output Power          | P <sub>OUT</sub>  | 2.7W      |     |

## Designed-Built-Tested

This document describes the hardware shown in Figure 1. It provides a detailed systematic technical guide to designing a synchronous buck using Maxim's MAX15118 current-mode controller. The power supply has been built and tested, details of which follow later in this document.

Figure 1. MAXREFDES1020 hardware.

**Note:** The MAXREFDES1020 uses the same board and PCB layout as the MAX15118 EV kit (MAX15118EVKIT).

Rev 1; 1/18 Maxim Integrated | 1

## **Synchronous Buck**

Synchronous buck converters, as opposed to conventional buck converters, can achieve high efficiency in today's low-voltage, high-current applications because they replace the catch diode of buck converters with a MOSFET. As a result, the power they dissipate in the off-period is reduced significantly.

In steady state, the low-side MOSFET is driven such that it is complementary with respect to the high-side MOSFET. This means whenever one of these switches is on, the other is off. In steady-state conditions, this cycle of turning the high-side and low-side MOSFETs on and off complementary to each other regulates  $V_{\text{OUT}}$  to its set value.

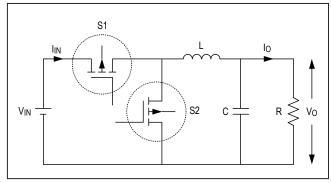

The basic operation of a synchronous buck converter can be explained from the simple circuit diagram shown in Figure 2. The main operation depends on the current in the inductor operated through main switch S1, generally a MOSFET, and the secondary switch S2. Initially when switch S1 is in the on state, the current starts flowing from the source through switch S1, inductor and to the load while the switch S2 is off. The operation time of switch S1 depends on the duty cycle. Now the current through the inductor charges the inductor. During this interval of time when the switch is in on state, switch S2 is in reverse bias and therefore switch S2 does not conduct.

For the next interval of time, when switch S1 is in the off state, the charged energy stored in the inductor now starts discharging. For this discharge of energy, the circuit needs to be closed. Now because the inductor is being discharged, the polarities of the inductor reverses and the switch S2 conducting state becomes forward-biased. When the duty cycle is very low, the inductor's charging time is less when compared to the discharging time. Since switch S2 is in the on state during the discharging time, the secondary switch S2 conducts for a longer time than the main switch.

The synchronous rectifier switch is open when the main switch is closed, and the converse is also true. To prevent cross-conduction (both top and bottom switches are on simultaneously), the switching scheme must be breakbefore-make. Because of this, a diode is still required to conduct during the interval between the opening of the main switch and the closing of the synchronous-rectifier switch (dead time). When a MOSFET is used as a synchronous switch, the current normally flows in reverse (source to drain), and this allows the integrated body diode to conduct current during the dead time. When the synchronous rectifier switch closes, the current flows through the MOSFET channel. Because of the very low-channel resistance for power MOSFETs, the standard forward drop of the rectifying diode can be reduced to a few millivolts. Synchronous rectification can provide efficiencies well above 90%.

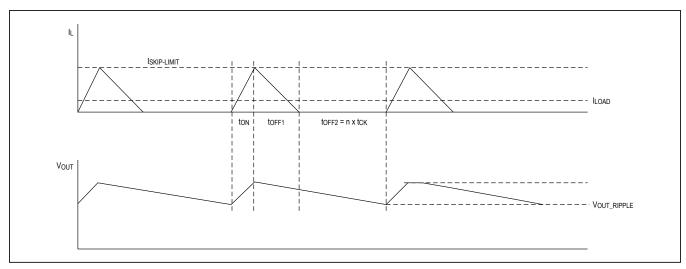

A feature offered in the MAX15118 is skip mode. Skip mode allows the regulator to skip cycles when they are not needed, greatly improving efficiency at light loads.

Figure 2. Synchronous converter topology.

Skip mode offers improved light-load efficiencies but at the expense of noise, because the switching frequency is not fixed and is proportional to the load current.

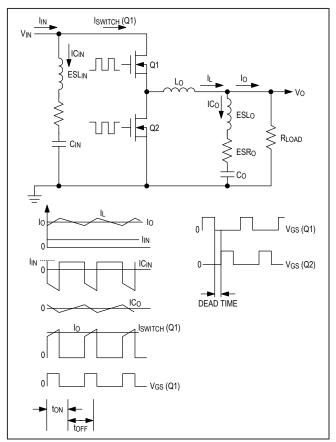

Various waveforms for the synchronous buck topology are shown in Figure 3. During the first cycle when Q1 conducts, the input current gradually rises and flows through the inductor and capacitor. This results in the energy being stored in the inductor and the capacitor.

Figure 3. Synchronous buck waveforms.

During the second cycle, Q1 turns off and, after some dead time, Q2 turns on. This results in the energy stored in the magnetic field of the inductor being released back into the circuit. As the energy stored in the inductor decreases, the capacitor starts discharging keeping the current flowing until the next cycle.

An important thing to note is that the MOSFETs Q1 and Q2 cannot be on at the same time as it would result in the input being connected to the ground. Hence, there should be some time interval between the on states of the MOSFETs. This time interval is called the dead time.

## **Design Procedure for Current-Mode Synchronous Buck**

Now that the principle of the synchronous buck operation is understood, a practical design example can be illustrated. The design process can be divided into several stages: output voltage selection, inductor and capacitor selection, and setup of the compensation loop. This document is intended to complement the information contained in the MAX15118 IC data sheet.

The following design parameters are used throughout:

V<sub>IN</sub> = Input voltage

V<sub>FB</sub> = Feedback threshold voltage

V<sub>OUT</sub> = Output voltage

$\Delta V_{OUT}$  = Output ripple voltage

I<sub>OUT</sub> = Output current

η = Target minimum efficiency

$P_{IN}$  = Input power

f<sub>SW</sub> = Switching frequency

D = Duty cycle

The above symbols are sometimes followed by parentheses to indicate whether minimum or maximum values of the parameters are intended, for example, minimum input voltage is indicated as  $V_{\text{IN}(\text{MIN})}$ . Unless otherwise noted, typical values are intended.

#### **Step 1: Setting the Output Voltage**

The MAX15118 output voltage is adjustable from 0.6V to 0.94V $_{\rm IN}$  by connecting FB to the center tap of the resistor-divider between the output and the GND. We choose the resistors R $_{\rm 1}$  and R $_{\rm 2}$  values so that the DC errors due to the FB input bias current do not affect the output voltage accuracy.

With lower value resistors, the DC error is reduced, but the power consumption increases.

$$R_1 = R_2 \left( \frac{V_{OUT}}{V_{FB}} - 1 \right)$$

Setting V<sub>OUT</sub> = 0.68V and V<sub>FB</sub> = 0.6V (typ), we get  $\frac{R_1}{R_2} = \frac{2}{15}$  so select  $R_1$  = 360 $\Omega$  and  $R_2$  = 2.7k $\Omega$ .

#### Step 2: Selecting the Inductor

A high-valued inductor results in reduced inductor-ripple current, leading to a reduced output-ripple voltage. However, a high-valued inductor results in either a larger physical size or a high series resistance (DCR) and a lower saturation current rating.

Typically, we choose an inductor value to produce a current ripple,  $\Delta I_L$ , equal to 30% of load current giving an LIR of 0.3.

We select the inductor with the following equation:

$$L = \frac{V_{OUT}}{f_{SW} \times LIR \times I_{LOAD}} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

$$L = \frac{0.68}{1 \text{Meg} \times 0.3 \times 4} \left( 1 - \frac{0.68}{3.3} \right) = 0.3 \mu H$$

where  $L = 0.5 \mu H$ .

Additionally, we need to ensure that the following relationship is satisfied:

$$I_{L_{PK}} = I_{LOAD} + \frac{1}{2}\Delta I_{L(P-P)} < \min(18A, I_{L_{SAT}})$$

where:

$$\Delta I_{L\left(P-P\right)} = \frac{\left(V_{IN} - V_{OUT}\right) \times \frac{V_{OUT}}{V_{IN}}}{L \times f_{SW}}$$

$$\Delta I_{L(P-P)} = \frac{(3.3 - 0.68) \times \frac{0.68}{3.3}}{0.5\mu \times 1 \text{Meg}} = 1.07$$

Hence:

$$I_{L\_PK} = 6 + \frac{1}{2}(1.07) = 6.535$$

#### **Step 3: Selecting the Input Capacitor**

For a step-down converter, the input capacitor,  $C_{\text{IN}}$ , helps to keep the DC input voltage steady despite discontinuous input AC current. Use low-ESR capacitors to minimize the voltage ripple due to ESR.

We calculate C<sub>IN</sub> using the following formulas:

$$C_{IN} = \left(\frac{I_{LOAD}}{f_{sw} \times \Delta V_{IN_{RIPPLE}}}\right) \times \frac{V_{OUT}}{V_{IN}}$$

$$C_{IN} = \left(\frac{4}{1M \times 0.5}\right) \times \frac{0.68}{3.3} = 1.64 \mu F$$

Ensure that the input capacitor can accommodate the input-ripple current requirement imposed by the switching currents.

$$I_{RMS} = \left[ \frac{[V_{OUT} \times (V_{IN} - V_{OUT})]^{0.5}}{V_{IN}} \right] \times I_{LOAD}$$

$$I_{RMS} = \left\lceil \frac{0.68 \times (3.3 - 0.68)^{0.5}}{3.3} \right\rceil \times 6 = 1.99A$$

#### **Step 4: Output Capacitor Selection**

The key selection parameters for the output capacitor are capacitance, ESR, ESL, and voltage-rating requirements. These affect the overall stability, output-ripple voltage, and transient response of the DC-DC converter. The output ripple occurs due to variations in the charge stored in the output capacitor, the voltage drop due to the capacitor's ESR, and the voltage drop due to the capacitor's ESL.

Estimate the output-voltage ripple due to the output capacitance, ESR, and ESL as follows:

where:

$$V_{RIPPLE(C)} = \frac{\Delta I_{P-P}}{8 \times C_{OUT} \times f_{SW}}$$

$$V_{RIPPLE(ESR)} = \Delta I_{P-P} \times ESR$$

$$V_{RIPPLE(ESL)} = V_{LX} \times \frac{ESL}{L} = V_{IN} \times \frac{ESL}{L}$$

When using ceramic capacitors, which generally have low-ESR,  $\Delta V_{RIPPLE(C)}$  dominates. When using electrolytic capacitors,  $\Delta \dot{V}_{RIPPLE(ESR)}$  dominates. Use ceramic capacitors for low ESR and low ESL at the switching frequency of the converter. The ripple voltage due to ESL is negligible when using ceramic capacitors.

Generally, a smaller inductor-ripple current results in less output-ripple voltage. Since inductor-ripple current depends on the inductor value and input voltage, the output-ripple voltage decreases.

When applying the load, limit the output undershooting by sizing C<sub>OUT</sub> according to the following formula:

$$C_{OUT} = \frac{\Delta I_{LOAD}}{3 f_{CO} \times \Delta V_{OUT}}$$

where  $\Delta I_{LOAD}$  is the total load change,  $f_{CO}$  is the unity gain bandwidth (or zero-crossing frequency), and  $\Delta V_{OUT}$  is the desired output undershooting.

$$C_{OUT} = \frac{2}{3 \times 0.1 M \times 0.02} = 333 \mu F$$

We select  $C_{OUT}$  = 400 $\mu$ F. We obtain this value by putting four 100μF capacitors in parallel.

#### **Step 5: Compensation**

The MAX15118 uses a fixed-frequency, peak currentmode control scheme to provide easy compensation and fast transient response. The inductor peak current is monitored on a cycle-by-cycle basis and compared to the COMP voltage (output of the voltage error amplifier).

The regulator's duty cycle is modulated based on the inductor's peak current value. This cycle-by-cycle control of the inductor current emulates a controlled current source.

As a result, the inductor's pole frequency is shifted beyond the gain bandwidth of the regulator.

System stability is provided with the addition of a simple series capacitor-resistor from COMP to GND. This pole-zero combination serves to tailor the desired response of the closed-loop system.

The peak current-mode controller's modulator gain is attenuated by the equivalent divider ratio of the load resistance and the current-loop gain. G<sub>MOD</sub> is the power modulator's transconductance, and R<sub>LOAD</sub> is the equivalent load resistance value.

K<sub>S</sub> is the slope compensation factor calculated as:

$$K_S = 1 + \frac{V_{SLOPE} \times f_{SW} \times L \times g_{MC}}{V_{IN} - V_{OUT}}$$

where  $V_{SLOPE} = 130 \text{mV}$  and  $g_{MC} = 150 \text{AV} \cdot 1$ .

Figure 4. Skip mode waveform.

Hence:

$$K_S = 1 + \frac{0.13 \times 1 Meg \times 0.5 \mu H \times 150}{3.3 - 0.68} = 4.7125$$

$G_{\text{MOD}}$  becomes:

$$G_{MOD} = g_{MC} \times \frac{1}{1 + \frac{R_{LOAD}}{f_{SW} \times L} \times \left[K_S \times (1 - D) - 0.5\right]}$$

where:

$$R_{LOAD} = \frac{V_{OUT}}{I_{OUT(MAX)}} = \frac{0.68}{4} = 0.113\Omega$$

hence,  $G_{MOD}$  =

$$80 \times \frac{1}{1 + \frac{0.113}{1 \times 0.5 \mu} \times \left[ 4.7125 \times \left( 1 - \frac{0.68}{3.3} \right) - 5 \right]}$$

$$G_{MOD} = 86.705$$

Select the desired crossover frequency. Choose  $f_{CO}$  equal to 1/10th of  $f_{SW}$ , or  $f_{CO}$  at 100kHz.

Select  $R_C$  using the transfer-loop's fourth asymptote gain equal to unity, assuming  $f_{CO} > f_{P1}$ ,  $f_{P2}$ , and  $f_{Z1}$ ,  $R_C$  becomes:

$$R_{C} = \frac{R_{1} + R_{2}}{R2} \times \frac{\left(1 + \frac{R_{LOAD} \times K_{S}\left[\left(1 - D\right) - 0.5\right]}{L \times f_{SW}}\right)}{g_{M} \times g_{MC} \times R_{LOAD}}$$

$$\times \left[ \text{ESR} + \frac{1}{\frac{1}{R_{LOAD}} + \frac{K_{S}[(1-D)-0.5]}{L \times f_{SW}}} \right]$$

$$g_M = 1.1 \text{mS}, g_{MC} = 80 \text{AV}^{-1}$$

and

$V_{SLOPE} = 130 \text{mV}$

where:

$$R_{LOAD} \times \frac{V_{OUT}}{I_{OUT(MAX)}} = \frac{0.68}{6} = 0.113\Omega$$

K<sub>S</sub> is the slope compensation factor calculated as:

$$K_S = 1 + \frac{V_{SLOPE} \times f_{SW} \times L \times g_{MC}}{V_{IN} - V_{OLIT}} = 4.7125$$

Hence, R<sub>C</sub> becomes:

$$\begin{split} R_C = & \frac{360 + 2700}{2700} \times \\ & \underbrace{\left(1 + \frac{0.113 \times 4.7125 \left[ \left(1 - 0.206\right) - 0.5 \right]}{0.5 \mu \times 1 Meg} \right)}_{\times} \times \end{split}$$

$$2\pi \times 100k \times 400\mu \times$$

$$\left[0.005 + \frac{1}{\frac{1}{0.113} + \frac{4.7125(1 - 0.206) - 0.5}{0.5 \mu \times 1 M}}\right]$$

$= 1667\Omega$

$R_C = 1.6k\Omega$ . Selecting  $R_3 = R_C = 1.8k\Omega$ .

#### Step 6: Selecting C<sub>C</sub>

$C_{\rm C}$  is determined by selecting the desired first system zero,  $f_{\rm Z1},$  based on the desired phase margin. Typically, setting  $f_{\rm Z1}$  below 1/5th of  $f_{\rm CO}$  provides sufficient phase margin.

$$C_C \ge \frac{5}{2 \times \pi \times f_{CO} \times R_C}$$

$$C_C \ge \frac{5}{2 \times \pi \times 100k \times 1800} \gg 4.4nF$$

Selecting  $C_{15} = C_C = 82nF$ .

#### Step 7: Setting the Soft-Start Time

The soft-start feature ramps up the output voltage slowly, reducing input inrush current during startup. The device utilizes an adjustable soft-start function to limit inrush current during startup. The soft-start time is adjusted by the value of  $C_{16}$ , the external capacitor from SS/REFIN to GND.

For a desired 6ms soft-start time, we calculate  $C_{16}$  as:

$$C_{16} = \frac{\left(10\mu\text{A} \times \text{t}_{SS}\right)}{0.6\text{V}}$$

$$C_{16} = \frac{\left(10\mu\text{A} \times 0.006\right)}{0.6\text{V}} = 0.1\mu\text{F}$$

The resistor, in series with the soft-start capacitor ( $R_{14}$  or  $R_{SS}$ ), improves load regulation. The recommended value for  $R_{SS}$  is approximately 330 $\Omega$ .  $R_{SS}$  is needed to ensure that, during hiccup period,  $R_{SS}$  can be pulled down internally.

We select  $R_{14} = R_{SS} = 470\Omega$ .

## **Design Resources**

Download the complete set of **Design Resources** including the schematics, bill of materials, PCB layout, and test files.

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                              | PAGES<br>CHANGED |

|--------------------|---------------|----------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 10/17         | Initial release                                                                                          | _                |

| 1                  | 1/18          | Added note to Figure 1 that the MAXREFDES1020 uses the same board and PCB layout as the MAX15118 EV kit. | 1                |

Maxim Integrated www.maximintegrated.com

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.