## **Product Information Notice - PIN 2462 -**

AnalogDevices, Inc. One Analog Way, Wilmington, MA01887, USA

This notice is to inform you of a change that will be made to certain ADI products (see Appendix A) that you may have purchased in the last 2 years. ADI contact information is listed below.

PIN Title: Product Information Notice for MAX96714/MAX96714F/MAX96714R

Publication Date: 17-Jul-2025

Effectivity Date: 17-Jul-2025 (the earliest date that a customer could expect to receive changed material)

**Revision Description:** Initial Release.

### **Description Of Change:**

- 1. MIPI receiver must be reset after system supplies and resets are stable. This is to prevent violation of T\_lpx timing requirements for MIPI receiver.

- 2. Additional information for 6Gbps Insertion Loss Channel Specification.

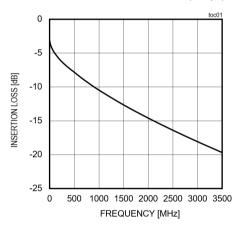

MAX96714 MAX INSERTION LOSS GMSL2 CHANNEL PIN-to-PIN (6Gbps)

6 Gbps Forward/187 Mbps Reverse

$$IL(f[Hz]) = \begin{cases} -\left(2.74 + 0.21\sqrt{(f \times 10^{-6})} + 0.54 (f \times 10^{-9})\right) & for \ 2 \ MHz \ to \ 500 \ MHz \\ -\left(2.35 + 0.21\sqrt{(f \times 10^{-6})} + 1.34 (f \times 10^{-9})\right) & for \ 500 \ MHz \ to \ 3.5 \ GHz \end{cases}$$

3. Additional GMSL2 receiver configuration register writes for optimal link margin.

RLMS Register Setting for 6Gbps or 3Gbps GMSL2 Rate:

| _ | wis register setting for ocops of 3 cops divisite rate. |            |                  |                                    |  |  |

|---|---------------------------------------------------------|------------|------------------|------------------------------------|--|--|

|   | Register                                                | Write Data | Bit(s)           | Purpose                            |  |  |

|   | RLMS8C                                                  | 0x20       | cap pre out rlms | Modify transmit edge rate (slower) |  |  |

Note: Legacy systems may continue to use the default value of 0x10. For new designs it is recommended to use the value of 0x20 to further improve link robustness.

#### Reason For Change:

PIN is being published to provide additional information on product application and performance.

### Impact of the change (positive or negative) on fit, form, function & reliability:

There is no impact to fit, form, function, quality, or reliability.

### **Summary of Supporting Information:**

#### **Comments:**

THIS IS NOT A PCN. This is an advisory to provide additional information on product application and performance.

# **Supporting Documents:**

## **ADI Contact Information:**

For questions on this PIN, please send an email to the regional contacts below or contact your local ADI sales representatives.

| Americas:               | Europe:               | Japan:               | Korea:               | Rest of Asia:      |

|-------------------------|-----------------------|----------------------|----------------------|--------------------|

| PCN_Americas@analog.com | PCN_Europe@analog.com | PCN_Japan@analog.com | PCN_Korea@analog.com | PCN_ROA@analog.com |

# Appendix A - Impacted items, see csv PN listing in PCN Zip file

| Appendix B – Revision History: |             |                  |                  |  |  |  |

|--------------------------------|-------------|------------------|------------------|--|--|--|

| Rev                            | Publish     | Effectivity Date | Rev Description  |  |  |  |

| Rev                            | 17-Jul-2025 | 17-Jul-2025      | Initial Release. |  |  |  |