ADSP-BF533/ADSP-BF561 Blackfin®处理器与高速并行ADC接口

作者: Jeritt Kent和Jeff Sondermeyer

简介

本应用笔记描述如何将ADSP-BF533/ADSP-BF561 Blackfin处理器并行外设接口(PPI)与高速模数转换器(ADC)相连，其中重点谈到了ADI公司的AD6652，它是一款12位、65MSPS中频(IF)至基带分集接收机。然而，此接口也可用于许多其它应用。AD6652虽然常被看作通信接收机，但也可用于成像、医疗超声、仪器仪表和测试设备。

本文特别提到了ADSPBF531/ADSP-BF532/ADSP-BF533 Blackfin系列处理器中的ADSP-BF533，并以ADSP-BF534/ADSP-BF536/ADSP-BF537系列以及ADSP-BF561双核处理器作为一般参考。

## 关于BLACKFIN处理器

Blackfin处理器的16位PPI端口不仅能简单、低成本地连接到各种通信接收机，还能与兼容国际电信联盟(ITU) 656标准的器件无缝相连。ITU-R 656是长宽比4:3的隔行标清电视系统的接口标准。亮度(Y)和多路复用色度(CbCr)信息以13.5 MHz的速率采样，所产生的输出流以27 MHz的时钟速率多路复用为单个8位或10位数据流。PPI通过连接数据线和时钟与ITUR 656兼容器件相连。这种接口中，所有控制代码均嵌入数据流中。

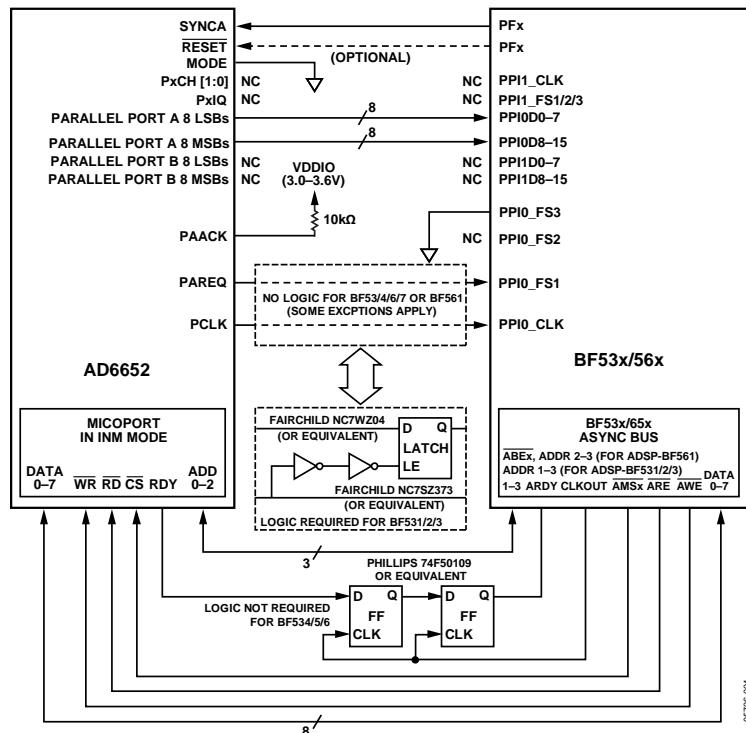

图1.

PPI也可以不使用嵌入的控制信号，而是利用外部帧同步信号来传输送往液晶显示器(LCD)或来自CMOS传感器的数据帧。这种数据模式也可以用来连接各种ADC和数模转换器(DAC)。对于这种应用，Blackfin处理器的PPI与附加的某种外部逻辑配合使用，可接收速率高达28 M字/秒的16位ADC数据。

直接存储器存取(DMA)是决定处理器最大数据吞吐速率的关键元件。Blackfin处理器内置一个先进的DMA控制器，无需占用任何内核处理周期便能将数据移入移出存储器。Blackfin处理器采用一种称为“二维DMA”的高级DMA特性，能将数据即时归类到不同的数据缓冲器。

AD6652具有4个独立的数据通道。由于各通道均产生同相(I)和正交(Q)数据，因此由一个典型算法来分别处理各通道及I/Q数据。Blackfin处理器以独特方式处理此分类操作，无需内核干预。由于其它系统相关的考虑，本文将详细分析如何决定这种应用的最大数据吞吐速率。

## 通过微型端口配置AD6652

AD6652通过微型端口和间接寻址方案来配置地址和控制寄存器设置。外部存储器映射(由外部寄存器组成)用于访问内部存储器映射，后者包括一个通道存储器映射和一个输出端口存储器映射。4通道存储器页面通过AD6652访问控制寄存器(ACR)的外部存储器寄存器7提供的A[9:8]解码。

与Blackfin处理器接口时，应将微型端口设置为Intel®非多路复用模式(INM)，如图1所示。要配置Blackfin处理器异步存储器总线，请使用AD6652的CS、RD和WR输入。AD6652 RDY信号(由微型端口产生)通过ARDY引脚告知Blackfin处理器，访问已完成。RDY在访问开始时变为低电平，在内部周期完成时变为高电平，请参阅AD6652数据手册(Rev. 0)的图31和图32。对AD6652微型端口时序tSC和tHC的快速分析显示，RD和WR输入具有相对于CLKAD6652上升沿的建立和保持时间。然而，如果未满足tSC条件，RD和WR将在CLK<sub>AD6652</sub>的后续上升沿采样。实际上，可以将RD和WR视为异步输入。

Blackfin处理器ARDY引脚的置位和解除置位必须满足数据手册规定的建立和保持时间要求( $t_{SARDY}$ 和 $t_{HARDY}$ )。注意，根据ADSP-BF531/ADSP-BF532/ADSP-BF533数据手册(Rev. B)，ARDY在CLKOUT之前的建立时间( $t_{SARDY}$ )为4 ns。未满足这些同步要求可能导致Blackfin处理器内部出现亚稳态现象。应利用CLKOUT信号确保ARDY同步跃迁。因此，图1中增加了一个双通道触发器来确保两个器件同步且满足建

立时间要求( $t_{SARDY}$ )。Philips Semiconductors已在74F50109中设计了这样一种器件。建立时间违规可能导致单通道触发器表现出亚稳态现象以及Q输出无效。因此，这里使用双通道触发器。这种方法的后果之一是增加了两个Blackfin处理器等待状态，以便补偿双时钟延迟。可以选择任何触发器，因为双通道定时掩盖了传播延迟。在AD6652的最差时序情况下(未给出最大 $t_{DRDY}$ )，等待状态数按照公式4计算。注意，根据《ADSP-BF533 Blackfin处理器硬件参考》(Rev. 3.1)，必须将BxRDYPOL设为1(如果ARDY变为高电平，则跃迁结束)。Blackfin处理器最多支持15个等待状态，因此SCLK与CLK<sub>AD6652</sub>的最大比值为13。

CLK<sub>AD6652</sub>在AD6652上起到双重作用，不仅用作前端接收机的ADC采样时钟，而且充当数字滤波部分的时钟。为了利用过采样，CLK<sub>AD6652</sub>应接近65 MSPS最大值，从而获得处理增益及高抽头数实现的优化滤波器特性。AD6652内置两个插值器(一个重采样级联积分器梳rCIC2和一个插值半带滤波器)及三个抽取器(一个rCIC2、一个五阶级联积分器梳CIC5和一个RAM系数滤波器RCF)，这些元件用来设置与CLKAD6652相关的输出数据速率。插值半带滤波器以两倍因子插值，也可被旁路。

## 窄带应用示例

输出数据速率 = 270.833 kSPS

PCLK = 15.36 MHz

CLK<sub>AD6652</sub> = 61.44 MHz

SCLK = 133 MHz

等待状态数 =  $(133/15.36)_{ceil} + 2 = 11$

如果Blackfin处理器异步存储器总线上的其它外设需要ARDY，则需要一个逻辑OR。注意，线OR也是适当的，不过这要求所有器件都提供开集RDY输出。外部存储器映射微型端口是访问4通道地址寄存器页面和输出端口控制寄存器页面的唯一途径。除通道地址0xA9(参见AD6652数据手册中的“通道地址存储器映射”表)以外，本部分专门讨论输出端口控制寄存器的配置(参见AD6652数据手册中的“输出端口控制寄存器存储器映射”表)。

首先，ACR初始化，使得所有芯片和所有通道都能访问。要访问输出端口A和端口B的寄存器，必须将外部地址3(休眠寄存器)的位5设为1。如果此位设为0，则选择通道存储器映射。参阅AD6652数据手册中的“外部存储器映射”表，将微型端口地址总线A[2:0]设为0b011，将双向微型端口数据总线D[7:0]设为0x20(见列表1)。

AD6652集成两个独立的16位并行端口用于输出数据传输。为使封装引脚数量最少，各16位端口的8个最低有效位(LSB)与相应的并行端口数据位共用。这意味着输出端口可以传输16位并行数据或8位链路端口数据，但不能同时进行。本应用笔记重点讨论16位并行数据，不讨论链路端口，后者常被分配用于ADI公司的另一系列处理器——ADSP-TS10x TigerSHARC®处理器。ADSP-BF533 Blackfin处理器在应用中仅使用其中一个并行端口，本例中是端口A。ADSP-BF561 Blackfin处理器具有2个PPI端口，需要时可以与AD6652的两个16位宽并行端口同时接口。

要将AD6652与Blackfin处理器PPI端口相连，应配置AD6652的主机模式并行端口时钟(PCLK)，并且配置并行端口通道模式为16位I和Q交错。如图1所示，将AD6652 PCLK连接到Blackfin处理器PPI\_CLK。因此，信号可以互换使用，具体取决于所讨论的器件。

首先将位于外部地址6的AD6652通道地址寄存器(CAR)的A[2:0]设为0b110。端口时钟主/从模式利用地址0x1E处的端口时钟控制寄存器进行配置——D[7:0]为0x1E。此地址的位0决定PCLK是由外部提供(从模式)还是从内部获得(主模式)。对于这种应用，AD6652为主机，应将地址0x1E的位0设为1。这是通过将A[2:0]设为0b010 (DR2)以及将D[7:0]设为0x00而实现的。然后，将A[2:0]设为0b001 (DR1)，并且将D[7:0]设为0x00。在主机模式下，PCLK是一个输出频率，等于AD6652时钟频率( $\text{CLK}_{\text{AD6652}}$ )除以PCLK分频比。PCLK分频[2:1]的值范围是0到3，因此可以获得1、2、4或8倍的整数分频。主机模式下的最高PCLK频率为65 MHz(PCLK分频比为1)。最后，将A[2:0]设为0b000 (DR0)，并且将D[7:0]的位0设为1。位[2:1]设置PCLK分频比。写入外部地址DR0时，就会根据ACR和CAR指示的地址，触发对AD6652的内部访问。这就是为什么必须总是最后写入外部地址0的原因(见列表1)。

## 列表1

```

/* Address/Data Configuration for AD6652 -

Master Mode, 16b Interleaved I and Q

Script Syntax :

micro_write(binary A[2:0], hex D[7:0]); */

/* Turn off Auto-Increment, Broadcast in ACR*/

micro_write(7,0x00);

/* Sleep Reg - Bit 5 high */

micro_write(3,0x2F); /* all channels asleep */

/*Port Clock Control - PCLK divisor is 1*/

micro_write(6, 0x1E); micro_write(2, 0x00);

micro_write(1, 0x00); micro_write(0, 0x01);

/* Link Port Control A- bit 7 low to disable */

micro_write(6, 0x1B); micro_write(0, 0x00);

/*Parallel Port Control A - 16b interleaved I/Q

channel mode*/

micro_write(6, 0x1A); micro_write(0, 0x00);

/*Output Control Register - Bit 5 is high to

set 16b format*/

micro_write(6, 0xA9); micro_write(0, 0x40);

```

并行端口配置通过访问并行端口A和端口B相应的端口控制寄存器地址0x1B和地址0x1D来指定。该编程过程与前面所述相似。当地址0x1B的位7为0时，链路端口A禁用，并行端口A使能。同样，当地址0x1D的位7为0时，並行端口B使能。

将地址0x1A的位5和位0设为0，以使能并行端口A的16位交错I和Q通道模式。同样，将地址0x1C的位5和位0设为0可使能并行端口B的这种模式。在通道模式下，来自各通道的I和Q字被送至并行端口，旁路自动增益控制(AGC)。对于ADSP-BF533 Blackfin处理器应用，仅使用并行端口A。

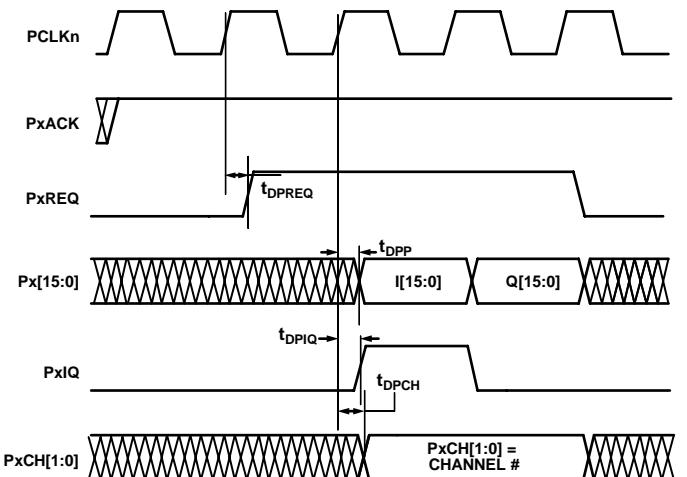

16位交错格式在背靠背PCLK时钟上提供各输出样本的I和Q数据。I和Q字均由16位全端口宽度的数据组成。当PAREQ和PAACK均置位时(这些信号名称中的A代表图2中的x，表示A输出端口)，数据输出在PCLK的上升沿触发。要设置这种16位格式，应将CAR设为内部地址0xA9。此输出控制寄存器为10位宽，DR0中的位5必须设为1。图1中，Blackfin处理器GPIO引脚(PFx)驱动AD6652的RESET引脚，确保在访问微型端口之前主机得到正确设置。AD6652数据手册(Rev. 0)在“微型端口控制”部分中提供了有关微型端口的更多信息。此外还建议设计人员阅读“设计指南”部分。

## 多通道应用的同步选项

DDC级的灵活通道复用功能运行1到4个通道通过一个并行输出端口交错传输。端口控制寄存器地址0x1A和地址0x1C的位0 (0)及位1到位4决定哪种处理通道组合是输出。数据应在可用时从输出端口读取，否则当下一个新数据样本到达时，当前样本就会被覆盖。这种现象是在各通道上发生；也就是说，通道0样本只会被新的通道0样本所覆盖。数据输出的顺序取决于数据到达端口的时间，该时间与总抽取率和开始延迟值有关(见公式3)。当数据同时到达时，从高到低的优先顺序为：通道0、通道1、通道2、通道3。有两种同步方法：Soft\_Sync和Pin\_Sync。第一种方法是利用软件程序通过微型端口启动，[AD6652](#)数据手册(Rev. 0)的“通道/芯片同步”部分提供了关于此方法的更多信息。第二种方法属硬件方法，依赖于连接到4个同步输入引脚(SYNC A、SYNC B、SYNC C和SYNC D)之一的外部激励。两种情况下均由逻辑高电平触发同步过程。设置适当的限定条件，两种方法可以同时使用。

绝大多数应用，包括单一通信标准的应用，都会为AD6652的所有4个通道配置完全相同的滤波器。唯一的不同是设置滤波器频谱的数控振荡器(NCO)频率。因此，AD6652的内部寄存器设置为如下状态：所有4个寄存器均与连接到Blackfin处理器GPIO引脚PFx的单一引脚SYNCA硬件同步(见图1)。这样做可以简化输出数据，使其能在单一帧同步包络中完成格式化。此时，器件按照默认优先顺序(0、1、2和3)，在类似突发的模式下以4个序列化I和Q对(8个16位字)的形式提供数据。数据不断以这种方式进行处理，多通道突发之间的停滞时间(dead time)与滤波器延迟成正比。如果通道滤波器不同，可以使用通道地址0x83处的开始延迟寄存器(延迟时间通过公式3计算)，强制实现同步，从而按照优先顺序或其它较佳序列输出数据。低速应用(1 MHz以下)可以使用其它同步方法。PACH[1:0]和PBCH[1:0]引脚构成一个2位二进制数，用于确定当前数据字的来源通道。在已知通道顺序的情况下，PACH或PBCH的LSB或MSB可以驱动另一个Blackfin处理器GPIO引脚(PFx)，作为快速硬件中断以识别突发序列的开始。

## 配置BLACKFIN处理器和AD6652接口

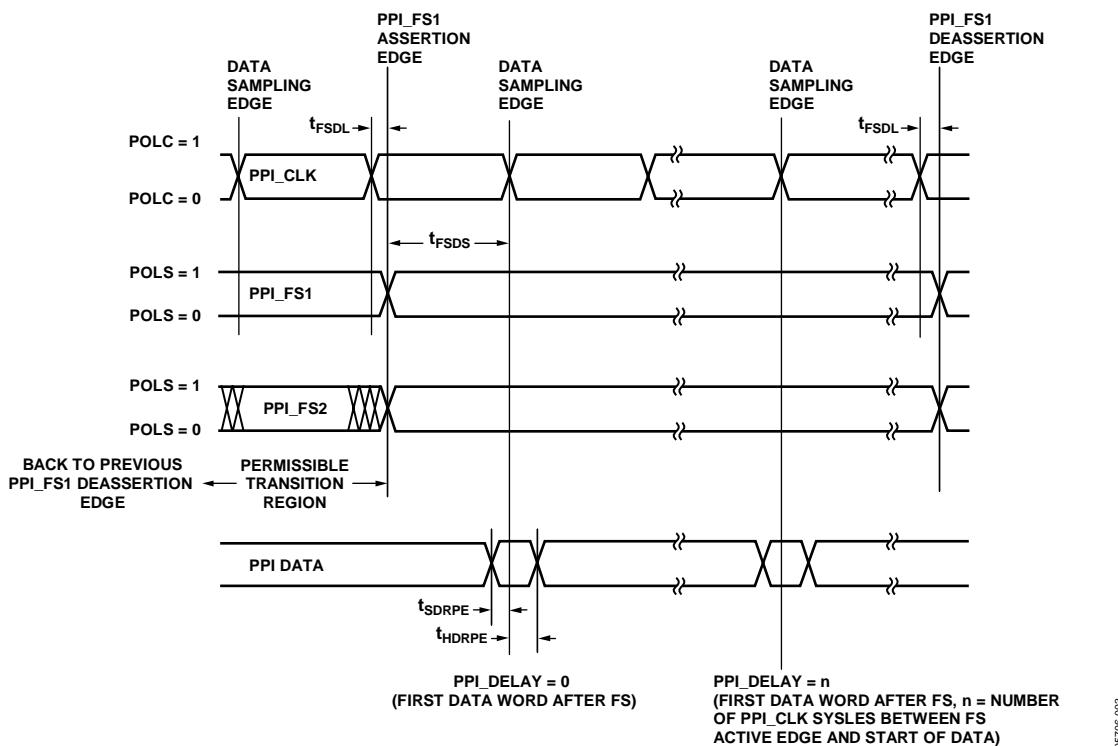

默认情况下，极性时钟位(POLC)为低电平，Blackfin处理器的帧同步延迟时序以PPI\_CLK的下降沿为参考。由于AD6652帧同步(PAREQ)是一个高电平有效输出，在上升沿与PCLK同步，因此应将此位设为高电平：POLC = 1(见列表2)。这将使Blackfin处理器从机相对于PCLK的上升沿延迟一个帧同步。

反之，默认情况下数据在PCLK的上升沿进行采样。在POLC为高电平的情况下，数据在下降沿通过PPI采样，该下降沿对应于图3所示AD6652主机提供的时序。

当PAREQ为高电平时，PAACK为逻辑高电平将导致并行端口根据设定的数据模式(16位I和Q交错)移出数据。这种应用不需要握手，因此PAACK通过外部上拉电阻连接高电平(见图1)。当数据可用时，数据在PAREQ置位后的一个PCLK周期开始移出(见图2)。

由于数据延迟一个PCLK周期(参见[AD6652](#)数据手册Rev. 0中的图32)，因此应在Blackfin处理器软件中设置PPI\_DELAY = 1，如列表2所示。虽然AD6652需要这一延迟，但数据时序采用其它帧同步方案的转换器可能不需要。

PAREQ时序相对于PCLK是内部固定的，无法调整。虽然AD6652的PAREQ与PCLK的上升沿同步，但这些边沿之间的最大延迟(tDPREQ)仅有1 ns(见图2)。Blackfin处理器需要更长的延迟时间，接下来将讨论其时序要求。

## ADSP-BF533 BLACKFIN处理器的外部逻辑要求

本文的剩下部分将重点讨论：为满足图3所示的延迟和保持时间要求，ADSP-BF533 Blackfin处理器需要什么样的外部逻辑。许多Blackfin处理器，包括ADSP-BF561和ADSP-BF534/ADSP-BF536/ADSP-BF537，不需要外部逻辑(存在例外情况，详见相应处理器的异常表)。这些器件集成了图1所示的外部逻辑和其它增强功能(参见相应数据手册中的时序信息)。

图2. AD6652并行输入模式16位交错数据时序图

图3. ADSP-BF531/BF532/BF533 PPI时序(GP输入模式、采用外部帧同步)

ADSP-BF533 Blackfin处理器要求帧同步置位沿出现在PPI\_CLK的下一个数据采样沿之前至少5.5 ns ( $t_{FSDS}$ ) (见图3)。PAREQ跃迁只能在PCLK完全稳定时进行。此外，在PCLK ( $t_{FSDL}$ )的对应沿(即上升到上升或下降到下降)之后，如果PAREQ跃迁沿的延迟时间不足，数据将无法锁存到PPI

中。这个问题的可能原因包括：时钟抖动、传播延迟容差、温度、PCLK再用于其它信号造成的扇出、非对称电路板布局以及边沿压摆。因此，这种应用的设计任务就是延长PCLK上升沿之后PAREQ (PPI\_FS1)信号的延迟时间，确保满足 $t_{FSDL}$ 和 $t_{FSDS}$ 要求。有两种方法可以完成这一任务。

第一种方法(首选且故障安全的方法)是利用电平敏感锁存器提供两个反转延迟, 锁存器由PCLK的延迟版本触发(见图1)。这一方案解决了上述可能导致PCLK拖延帧同步信号的问题。当延迟的PCLK达到锁存器使能(LE)的 $V_{inh}$ 电平时, 锁存器传送D输入。重新定时的帧同步(PAREQ)必须在整个数据窗口内保持高电平, 并且满足图3所示的时序要求。触发器(flip-flops)远不如这种方案有效, 因为触发器是边沿触发型。这种情况下, 先于帧同步的过早PCLK会导致已置位的帧同步错过整个PCLK周期。

为了驱动锁存器的使能引脚, 可以将Fairchild Semiconductor的两个NC7WZ04(双通道反相器, 或同类器件)与AD6652的PCLK串联使用。已给出了3.3 V电源下针对50 pF和15 pF的要求。对于这种应用, 第一个反相器的负载为第二个反相器的输入电容(4 pF), 第二个反相器的负载为锁存器使能引脚的输入电容(3 pF)。对数据进行外推可得出最小综合传播延迟约为1.4 ns(−40°C至+85°C的温度范围)。

**表1. ADSP-BF531/ADSP-BF532/ADSP-BF533时序要求**

| 参数                              | 最小值    |

|---------------------------------|--------|

| $t_{FSDL}$ , 外部帧同步延迟            | 2.0 ns |

| $t_{FSDS}$ , 外部帧同步至数据采样沿        | 5.5 ns |

| $t_{SDPE}$ , PPI_CLK之前接收数据建立时间  | 2.0 ns |

| $t_{HDRPE}$ , PPI_CLK之后接收数据保持时间 | 4.0 ns |

锁存器可以考虑NC7SZ373, 它同样出自Fairchild Semiconductor。在3.3 V电源、工业温度范围、Blackfin处理器PPI\_FS1输入端负载为8 pF的条件下, 对从LE到输出(Q)的最差情况(最小)传播延迟进行线性化处理, 得到0.9 ns。NC7SZ373在锁存器使能的下降沿锁存数据, 因此不存在建立时间要求。这是设置POLC = 1的另一个重要原因。对于商用温度范围的设计, 显然还存在额外的裕量。

$$t_{FSD}(\min) = t_{PROP\_INV}(\min) + t_{PROP\_LE\_to\_Q}(\min) \text{ sec} \quad (1)$$

$$f_{PCLK}(\max) = 1/(2 \times (t_{PROP\_INV}(\max) + t_{PROP\_LE\_to\_Q}(\max) + 5.5 \text{ ns})) \text{ Hz} \text{ for a 50\% PCLK and } t_{DPREQ}(\max) < t_{OP\_INV}(\min) \quad (2)$$

$$T_{latency} = MrCIC2 \times (MCIC5 + 7) + N_{taps} + 26 + Start Holdoff Counter \times t_{CLK} \text{ sec} \quad (3)$$

其中:

MrCIC2和MCIC5是rCIC2和CIC5滤波器的抽取值。

$N_{taps}$  是所选的RCF抽头数。

$$t_{CLK} = 1/f_{CLK\_AD6652}$$

$$\text{Blackfin处理器等待状态数} = [(SCLK/CLK_{AD6652})_{ceil} + 2] \quad (4)$$

其中:

$ceil$ 为小数的四舍五入整数。

等待状态数最大值为15。

对于选定的反相器和锁存器, 必须在适当的温度、电压和负载下评估最小传播延迟, 确保满足 $2 \text{ ns} - t_{FSDL}$ 最小值要求(见图3)。利用两个NC7WZ04和NC7SZ373, 公式1给出 $t_{FSDL}$ 最小值为2.3 ns, 这符合图3中的要求。最大传播延迟用于确定应用的最大容许PCLK频率。在适当的负载、3.3 V电源和工业温度范围这些条件下进行外推, 得出最大综合反相器延迟约为7.8 ns— $t_{PROP\_INV}(\max)$ , 锁存器的最大传播延迟为4.5 ns— $t_{PROP\_LE\_to\_Q}(\max)$ 。考虑到PAREQ可以落后PCLK最多1 ns, 公式2显示最大容许50%占空比PCLK为28 MHz— $f_{PCLK}(\max)$ 。抖动问题得以解决, 因为PCLK与PAREQ相关; AD6652的PAREQ由PCLK释放。

这种方法假设AD6652与Blackfin处理器非常靠近, 并且时钟和帧同步线为单一连接, 即没有扇出驱动其它器件。尤其是高速设计, PAREQ上的任何负载都必须在时序中加以考虑, 因为AD6652 PAREQ引脚上的负载被认为与该对反相器之前的PCLK上的负载相当。这些信号的时序要求基于40 pF负载。

由于非50%占空比采样会对转换器性能(包括AD6652)造成不利影响, 因此应当认为, 当与ADSP-BF533 Blackfin处理器接口时, 28 MHz是最大容许的PCLK(参见“接口指南”部分)。PCLK占空比与CLKAD6652占空比一致, 时钟树上的细微边沿不匹配除外。但这一PCLK限值确实会带来一些重要的限制: 对于AD6652的大多数宽带应用, 不应考虑ADSP-BF533 Blackfin处理器; 通用移动电信系统(UMTS)就是一例。

ADI公司将数字滤波器脚本调整到61.44 MSPS采样速率，以此完成了许多工作。这样就可以针对全球移动通信系统(GSM)等窄带标准进行简单的修改。因此，当PCLK分频比只能是1、2、4或8时，最大PCLK为15.36 MHz。对于输出全部四通道的同相和正交信息的系统，PCLK为输出数据速率的9倍： $(2 \times 4) + 1$ ，如图2所示。即使加上AD6652的协处理能力，以1.92 Mbps的速率交错输出数据以产生3.84 Mbps的综合速率(符合UMTS标准)，输出此数据所需的9个PCLK周期也需要586 ns ( $9 \times 1/15.36$  MHz)，大于满足输出数据速率要求所需的521 ns。然而，GSM等窄带应用不受这种限制的影响。

对于低速应用，可以将一个缓冲器，例如最大传播延迟为4.0 ns的NC7WV07或其它延迟更大的器件，与转换器帧同步信号串联。还有一种可靠性稍低的方法是在帧同步路径中使用偶数个反相器或一个缓冲器，从而产生一个延迟——2 ns即足够(见图3中的 $t_{FSDL}$ )。不过，必须确保延迟不是太长，因为PAREQ的置位沿必须出现在PCLK数据采样沿之前至少5.5 ns ( $t_{FSDS}$ )，以便满足内部保持要求。

总之，图1所示的外部逻辑能够有效地将电平敏感信号(PPI\_FS1)转换为边沿敏感帧同步信号。所有未来的Blackfin处理器衍生产品都将内置这一逻辑。

## 配置PPI和DMA

针对许多不同的应用，Blackfin处理器PPI可以配置为输入或输出总线。对于这种应用，PPI配置为通用输入模式、单帧同步和时钟极性(POLC = 1)。

配置PPI端口和DMA的C代码如列表2所示。PPI\_FS1信号通过锁存器重定时电路连接到PAREQ。此信号使能四个通道的所有8个数据字(每个通道的I和Q)的帧传输。Blackfin处理器DMA传输8个数据字，并在每次传输完成时产生中断。虽然内核可以在传输间隔期间对数据进行排序，但最好使用二维DMA，因为它能有效地给通道1至通道4排序(列表2未显示)。

## 列表2

```

/* Configure PPI - RX, 16 bits, GP mode,

external frame sync FS1 */

*pPPI_CONTROL = 0x780c; /* POLC = 1

(default for POLS = 0, this is good as the

frame sync is active high)*/

*pPPI_DELAY = 0x0001; /* 1 PCLK delay to ignore

1st data from AD6652 */

*pPPI_COUNT = 0x0007; /* 8 words transferred */

/* Configure DMA0 - Memory write, 16 bits, 1D

interrupt, autobuffer mode */

*pDMA0_CONFIG = 0x1086;

*pDMA0_START_ADDR = PPI_Buffer;

*pDMA0_X_COUNT = 0x0008; /* 8 words */

*pDMA0_X MODIFY = 0x0002; /* 16-bit data */

```

如果设计师利用早期X级ADSP-BF561和ADSP-BF534/ADSP-BF536/ADSP-BF537 Blackfin处理器进行原型开发，则应在印刷电路板(PCB)上为生产级芯片做一些准备。用0 Ω电阻旁路外部逻辑。

整个系统可以利用下列电路板构建并测试：

- [AD6652BC/PCB](#)转换器板

- [ADDS-BF-EZEXT-1](#)扩展卡

- [ADDS-BF533-EZ-KIT Lite](#)<sup>®</sup>评估板或[ADD-BF561-EZ-KIT Lite](#)<sup>®</sup>评估板

为将AD6652BC/PCB连接到ADDSBF-EZEXT-1，可能需要一根改造过的扁平电缆来提供本文讨论的外部逻辑。

## 参考读物

[ADSP-BF53x/ADSP-BF56x Blackfin处理器编程参考](#)

## 接口指南

综上所述，将AD6652等并行ADC与Blackfin PPI端口相连时应遵循以下原则：

- Blackfin CLKIN可以驱动片上锁相环(PLL)以实现倍频功能——相关值参见相应的数据手册。然后，PLL压控振荡器(VCO)的输出可以进行1、2、4或8分频，以产生内核时钟(CCLK)；也可以进行1到15的整数分频，以产生系统时钟(SCLK)。

$$SCLK \leq CCLK$$

- Blackfin PPI\_CLK频率不得超过66 MHz。

$$(PCLK = PPI\_CLK) \leq SCLK/2$$

- 帧同步的置位沿应出现在PPI\_CLK的数据采样沿(POLC = 1时为下降沿)之前至少5.5 ns(tFSDS)，以满足Blackfin内部保持要求(见图3)。

- 外部帧同步延迟tFSDL不得少于2 ns(见图3)。

- ADSP-BF531/ADSP-BF532/ADSP-BF533的最小可得外部帧同步延迟tFSDL由外部逻辑设置：

$$t_{FSDL}(min) = t_{PROP\_INV}(min) + t_{PROP\_LE\_to\_Q}(min) \text{ sec}$$

- 如果PCLK从转换器采样时钟获得，则它为50%占空比。Blackfin处理器在这种条件下的最大容许PCLK为28 MHz。这可能会给应用带来严格限制。

- 对于这种应用，50%占空比时的最大PPI\_CLK频率为：

$$f_{PPI\_CLK}(\max) = 1/[2 \times (t_{PROP\_INV}(\max) + t_{PROP\_LE\_to\_Q}(\max) + t_{DPREQ}(\max) + 5.5)].$$

使用AD6652和本文所述的逻辑时， $f_{PPI\_CLK}(\max) = 28 \text{ MHz}$ 。

- PPI\_CLK高电平时间不得短于7.5 ns。这是Blackfin PPI的时序要求，但再次说明，PPI\_CLK最高频率由外部逻辑的最大延迟决定。

- PPI\_CLK低电平时间不得短于3 ns。这是Blackfin PPI的时序要求，但应注意，接口转换器的要求可能更严格(例如，AD6652的PCLK低电平最短时间为6.2 ns)。

- 移动多个数据通道时，应考虑同步问题。通过PPI端口的DMA数据延迟可能导致难以获得正确的通道顺序。