One Technology Way • P.O. B ox 9106 • Norwood, MA 02062-9106 • Tel: 781/329-4700 • Fax: 781/326-8703 • www.analog.com

## 多个AD9786 TxDAC的时序同步

作者: Steve Reine

#### 简介

AD9786是一款高性能、高速DAC,专为GSM、CDMA2000和WCDMA基站应用而设计。器件架构包括一个使用插值的双数字信号路径以及一个数字复数混频器。该架构允许在DAC输出端合成高达200 MHz的中频,同时满足严苛的BTS要求。

AD9786是一款单通道DAC。某些应用中,设计中可包括两个或更多DAC。需要多个DAC的典型架构包括单边带抑制发射机和分集发射机。上述应用中,多个AD9786可能无法共址,甚至位于不同PCB上。

这些设计需要同步多个DAC中的复数调制器。AD9786提供数字用户接口,可将多个从AD9786中的调制器与单个主AD9786同步,或者有意偏移可编程数量的时钟周期。

使用AD9786时有数个时序模式可用,如表1所示。本应用 笔记重点关注调制器主模式和调制器从模式,这些模式允 许用户同步内部调制器。

#### AD9786主器件

许多AD9786应用的默认模式是DATACLK主模式。在此模式下,时钟以DAC输出采样速率施加于CLKIN(差分CLK+/CLK-,引脚5和6)。引脚31以用于数据同步的输入数据速率提供时钟输出(DATACLK)。DATACLK速度即CLKIN速率除以插值率。为简明起见,本例中不考虑零填充。在DATACLK主模式下,引脚31上的输出信号称为DATACLK。

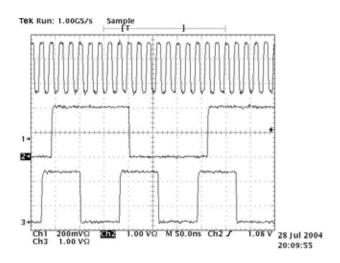

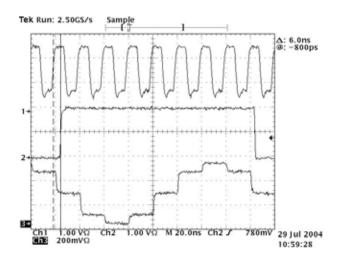

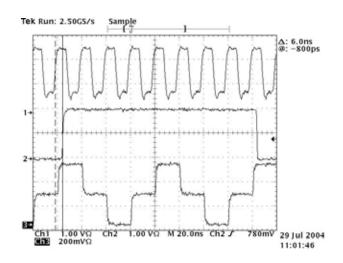

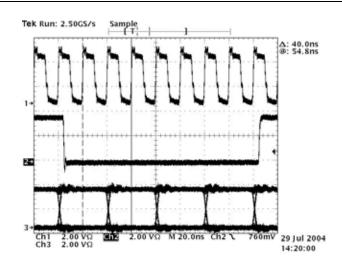

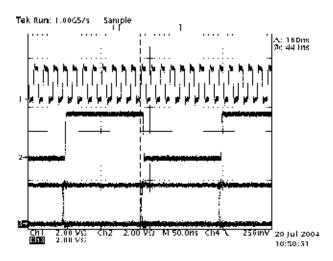

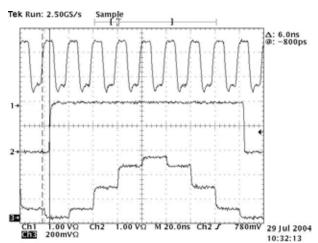

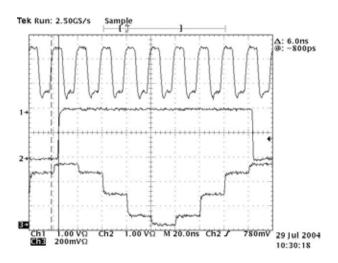

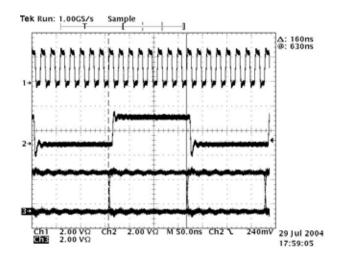

在调制器主模式下,引脚31上的输出信号在等于CLKIN除以16的频率下变为方波。同样,引脚31上的输出信号称为MODCLK。图1显示插值设置为4×的AD9786示例。图1上部信号表示CLKIN。中间曲线表示AD9786处于调制器主模式时引脚31的输出,且周期等于CLKIN除以16。图1下部信号表示编程为DATACLK主模式的AD9786,因此引脚31上的信号等于CLKIN除以4(4×插值)。

表1. AD9786时序模式

| DCLKEXT  | MODSYNC  | DCLKCRC  |                |                          |

|----------|----------|----------|----------------|--------------------------|

| 02h, 位 3 | 05h, 位 3 | 02h, 位 2 | 模式             | 功能                       |

| 1        | 0        | X        | DATACLK<br>主模式 | 通道数据速率时钟输出               |

| 1        | 1        | Х        | 调制器主模式         | 调制器同步DATACLK输出           |

| 0        | 0        | 0        | 外部同步模式         | DATACLK无效,DACCLK与外部数据同步  |

| 0        | 0        | 1        | DATACLK<br>从模式 | DATACLK输入,数据速率时钟,数据恢复开启  |

| 0        | 1        | 0        | 低电平设置/保持       | DATACLK输入,输入数据与DATACLK同步 |

| 0        | 1        | 1        | 调制器从模式         | 输入调制器同步器DATACLK输入        |

图1. DATACLK主模式与引脚31上调制器主输出的比较, 插值= 4×

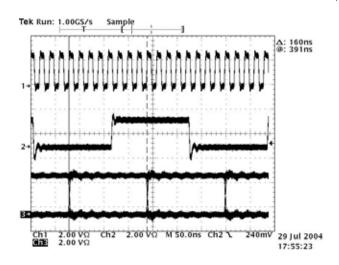

图2. AD9786主或从器件上的调制器与MODCLK (MODADJ = 000) 的时序关系,插值设置为8×,调制=  $f_{DAC}/8$

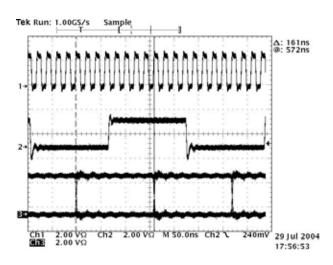

图3. AD9786主或从器件上的调制器与MODCLK (MODADJ = 000) 的时序关系,插值设置为8×,调制= $f_{DAC}/4$

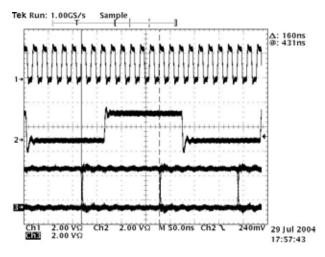

图4. AD9786主或从器件上的调制器与MODCLK (MODADJ = 000) 的时序关系,插值设置为8×,调制= $f_{DAC}/2$

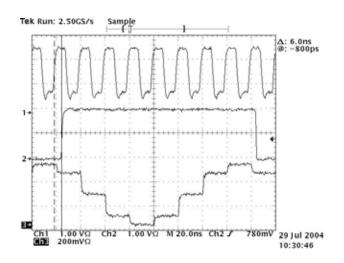

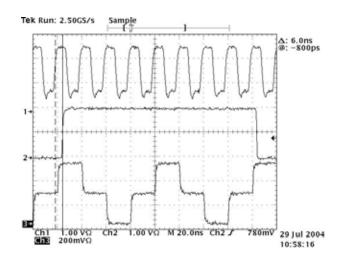

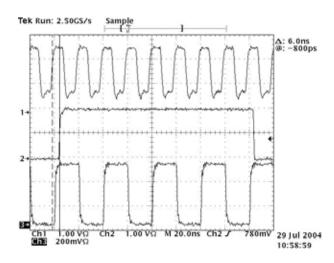

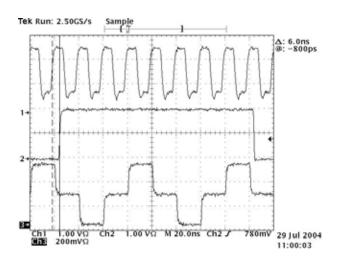

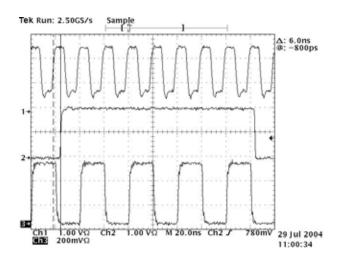

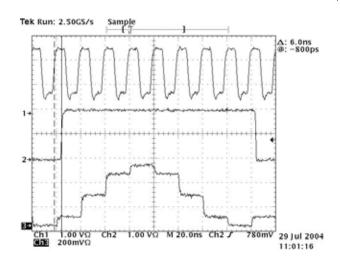

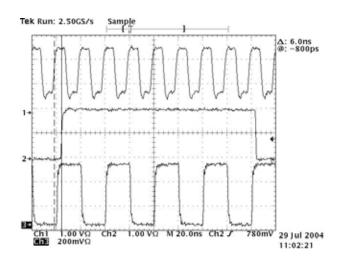

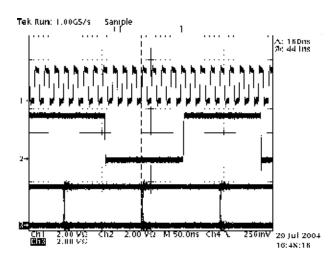

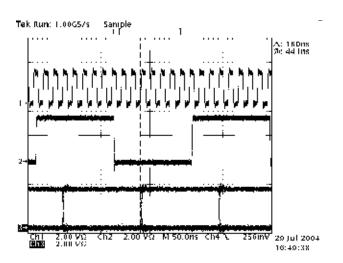

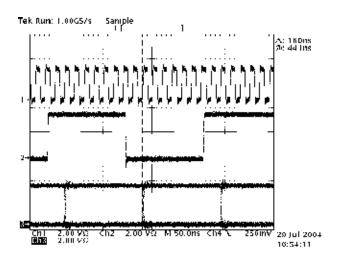

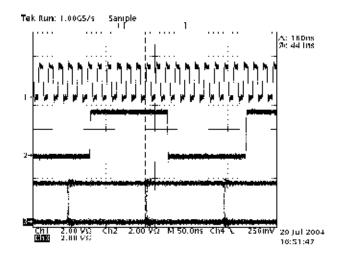

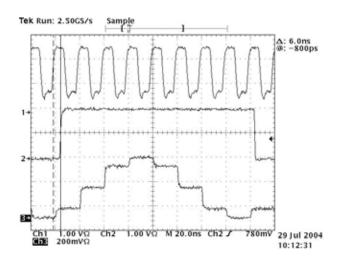

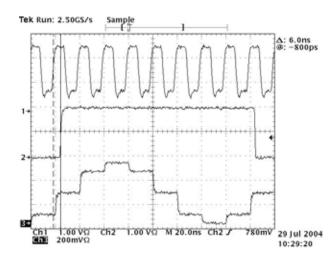

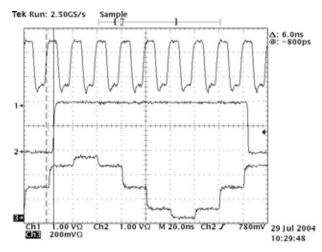

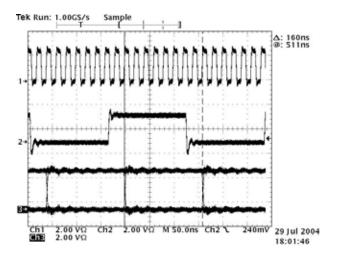

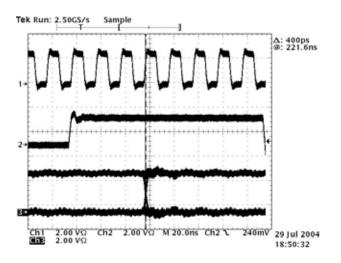

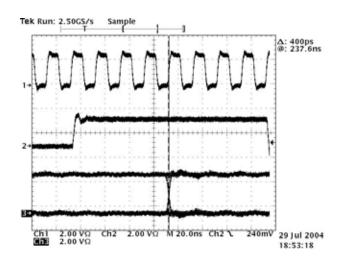

图2至图4显示的是调制器模式下的AD9786,插值滤波器编程为8×,调制器设置为f<sub>DAC</sub>/8、f<sub>DAC</sub>/4和f<sub>DAC</sub>/2。满量程值数据流逐个输入AD9786,从而在DAC满量程下创建直流输入。图2至图4中的上部曲线图表示CLKIN。中间曲线图表示MODCLK,下部曲线图显示DAC输出。DAC输出表示内部调制器的交替相位在每个CLKIN上升沿更新。请注意,中间曲线图的每个周期内,调制器有16个相位(调制器主模式下的引脚31信号)。

图2至图4显示, CLKIN上升沿至MODCLK的上升/下降沿通常存在7ns延迟。DAC输出与主器件和从器件上的CLKIN同步/对准, CLKIN至DAC更新的延迟通常为3 ns。

如图2至图4所示,AD9786内部调制器的相位关系对于编程为主模式和从模式的器件有效,且从器件内的MODADJ位(寄存器05h,位2:0)设置为000。也就是说,如果从器件内的MODADJ位为000,主和从AD9786中的调制器在相位上是对准的。MODADJ位对主器件无影响。

如果到达AD9786主和从器件的CLKIN路径长度不等,可能存在时序不平衡。这可以造成主从调制器间的微小相位差异,并降低镜像抑制性能。

将AD9786编程为这些模式前, RESET必须置位。

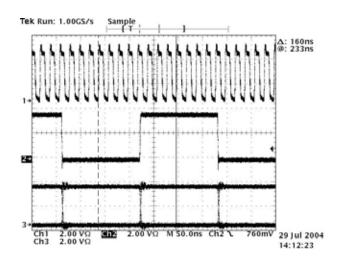

图5至图10显示了AD9786插值为4×和2×时的调制器同步。 请注意,关于MODCLK沿的相位对准因插值率而异。插值 设置为1×时,主和从调制器不会自动同步。

图5. AD9786主或从器件上的调制器与MODCLK (MODADJ=000) 的时序关系,插值设置为 $4\times$ ,调制= $f_{DAC}/8$

图6. AD9786主或从器件上的调制器与MODCLK (MODADJ = 000) 的时序关系,插值设置为4×,调制= $f_{DAC}/4$

图7. AD9786主或从器件上的调制器与MODCLK (MODADJ=000) 的时序关系,插值设置为 $4\times$ ,调制= $f_{DAC}/2$

图8. AD9786主或从器件上的调制器与MODCLK (MODADJ = 000) 的时序关系,插值设置为2×,调制=  $f_{DAC}/8$

图9. AD9786主或从器件上的调制器与MODCLK (MODADJ = 000) 的时序关系,插值设置为2×,调制=  $f_{\rm DAC}/4$

图10. AD9786主或从器件上的调制器与MODCLK (MODADJ = 000) 的时序关系,插值设置为2×,调制= f<sub>DAC</sub>/2

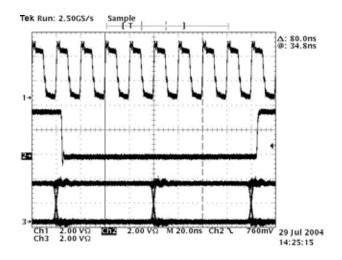

### 调制器主模式中的数据时序

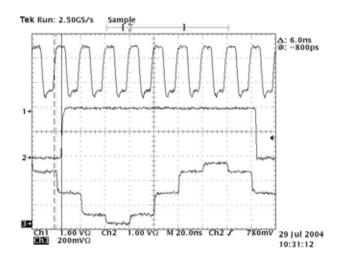

当AD9786处于调制器主模式时,输入数据必须与CLKIN以及MODCLK同步。具体而言,CLKIN上升沿锁存输入数据。8×插值时,隔7个CLKIN上升沿锁存一次,4×插值时,隔3个CLKIN上升沿,2×插值时,隔1个CLKIN上升沿。图11至图13中的曲线图显示了此情况。请注意,所有情况下,数据转换发生于MODCLK边沿较为有利。锁存CLKIN边沿附近的测量设置和保持时间为ts = -0.2 ns,th = 2.2 ns。

图11. 主调制器模式下的AD9786, 8×插值。 垂直虚线和实线代表CLKIN锁存沿。

图12. 主调制器模式下的AD9786, 4×插值。 垂直虚线和实线代表CLKIN锁存沿。

图13. 主调制器模式下的AD9786, 2×插值。 垂直虚线和实线代表CLKIN锁存沿。

## 在调制器主模式中调节数据时序

图11至图13所述的时序可通过设置DATADJ位(寄存器5,位7:4)在15个CLKIN周期内相对于MODCLK进行调节。改变DATAADJ位时,MODCLK向前或向后偏移。CLKIN锁存沿及时保持相同位置,从而在设置DATAADJ位时相对于MODCLK移动。此能力在主AD9786上可用于数据同步,但在从器件上更为实用,因为当主从AD9786彼此相隔较远时它可以补偿时钟延迟。"调制器从模式中的数据时序"部分将予以详细说明。

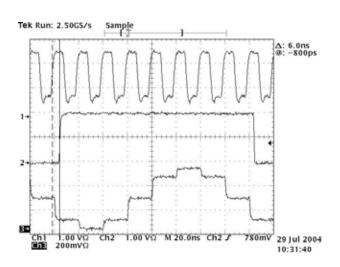

图14至18显示了DATAADJ各种设置的效应。所有四个曲线图中,输入数据转换(第三个走线)有意放置在CLKIN锁存沿上。如曲线图所示,MODCLK随DATADJ一起移动,同时CLKIN锁存沿保持恒定。

图14. 主调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0000。这些条件与图11相同。

图15. 主调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0001。

图16. 主调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0010。

图17. 主调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0100。

图18. 主调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0110。

### AD9786从器件

当AD9786被编程为调制器从模式时,从器件引脚31上需要 MODCLK信号。如前所述,当从器件内的MODADJ位设 置为000时,RESET置位并复位,从调制器相位匹配主调制 器相位。

从器件内的MODADJ位可用于移动从调制器相位,最多可偏移7个CLKIN周期。图19至图25分别表示图2至4的条件(插值=8×,调制器=f<sub>DAC</sub>/8),但MODADJ位在其范围内进行设置。

当AD9786从器件调制器设置为 $f_{DAC}/4$ 时,内部调制器仅有4个可能的输出相位。因此,仅MODADJ位2:1对调制器对准有影响。调制器设置为 $f_{DAC}/2$ 时,MODADJ位无影响。

图19. AD9786从器件上的调制器与MODCLK输入的时序关系, 插值=  $8\times$ ,调制=  $f_{DAC}/8$  MODADJ = 0,0,1

图20. MODADJ = 0,1,0

图21. MODADJ = 0,1,1

图22. MODADJ = 1,0,0

图23. MODADJ = 1,0,1

图24. MODADJ = 1,1,0

图25. MODADJ = 1,1,1

#### 调制器从模式中的数据时序

与调制器主模式一样,调制器从模式中输入数据必须与CLKIN以及MODCLK同步。主模式说明中,CLKIN锁存沿保持恒定,而MODCLK随着DATAADJ前后移动。从模式中,MODCLK作为输入时,MODCLK保持恒定,而CLKIN锁存沿在DATAADJ位改变时移动。此可编程能力减轻了用户的数据时序负担。图26至图30显示了DATAADJ位的效应。与图14至图18相同,输入数据转换(第三个走线)有意放置在CLKIN锁存沿上。

输入数据相对于CLKIN的数据设置和保持时间为ts = -0.2 ns,th = 2.2 ns,与调制器主模式中相同。

调制器从模式中,MODCLK为输入,因此其时序也必须相对于CLKIN定义。MODCLK上升沿相对于最近CLKIN上升沿的位置决定CLKIN的数据锁存沿。图31中显示了当DATAADJ为0000时的锁存CLK边沿,MODCLK上升沿至少比最近CLKIN上升沿提前2.4 ns出现。图32最能代表本应用笔记中的数据,MODCLK上升沿比最近CLKIN上升沿稍晚或同时(0 ns)出现。图32中DATAADJ仍为0000。

图26. 从调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0000。

图27. 从调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0001。

图28. 从调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0010。

图29. 从调制器模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0100。

图30. 调制器从模式下的AD9786, 8×插值。垂直虚线和实线代表 CLKIN锁存沿。DATAADJ = 0110。

图31. AD9786调制器从模式时序,8×插值。MODCLK 上升沿至少比CLKIN上升沿提前2.4 ns出现。垂直线代表 CLKIN锁存沿。DATAADJ = 0000。

图32. AD9786调制器从模式时序, 8×插值。MODCLK 上升沿比CLKIN上升沿晚0.0 ns或更多。垂直线代表 CLKIN锁存沿。DATAADJ = 0000。