## 用ADE7912/ADE7913构建锰铜分流器基于锰铜分流器的直连式三相电表

作者: Petre Minciunescu和Dave Smith

### 简介

ADE7912/ADE7913 3通道隔离式Σ-Δ模数转换器(ADCs)面向采用锰铜分流器锰铜分流器的三相电能计量应用。本应用笔记旨在对ADE7912/ADE7913数据手册中的“应用信息”部分进行扩展。其中，将深入说明在开发带锰铜分流器锰铜分流器的直连式直连式三相电表时，如何运用ADE7912/ADE7913。

### 用ADE7912/ADE7913构建直连式三相电表

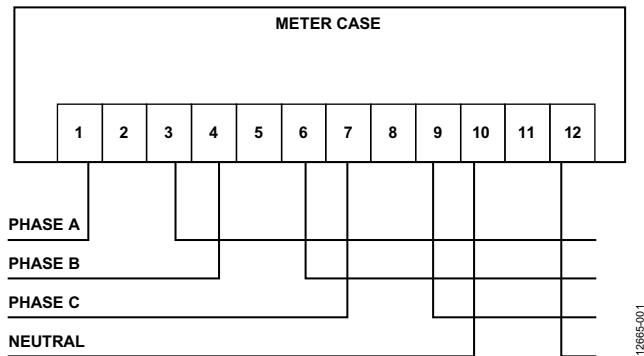

图1. 三相四线直连式电表连接

图1所示为直连式三相电表在三相四线系统中的连接方法。A相线路连接电表端子1和端子3, B相连接端子4和端子7, C相连接端子7和端子9, 零线连接端子10和端子12。一般来说，电表的端子2、端子5和端子8用于电压检测连接。对于直连式三相电表，A、B、C三相线路分别在内部连接至端子1、端子4和端子7。A、B、C三相线路正是从这些点进入电表。

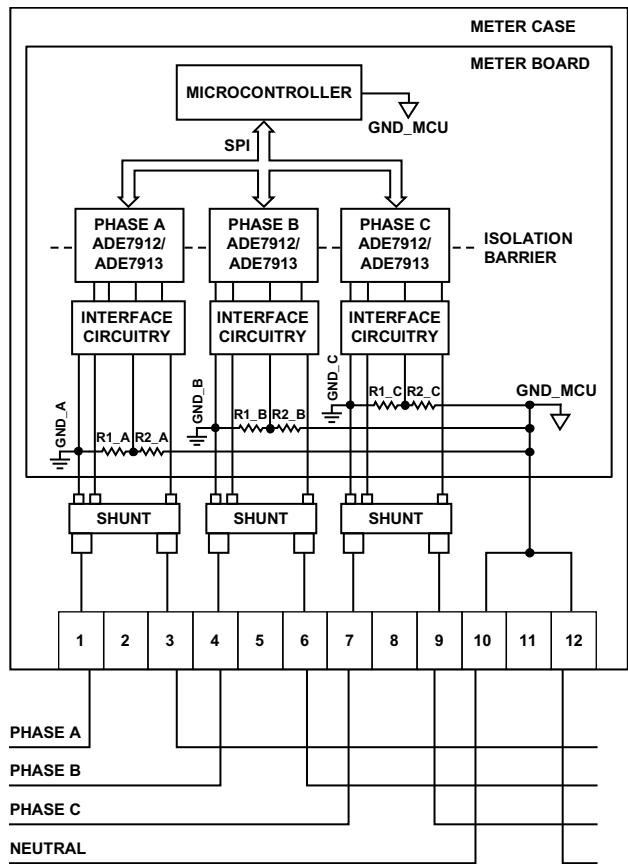

图2所示为采用ADE7912/ADE7913的一款电表的架构。三个锰铜分流器锰铜分流器连接着电表端子，这也是三相四线连接所在。每个ADE7912/ADE7913都通过一个接口电路管理一相线路。锰铜分流器锰铜分流器的基准电压端子成为ADE7913隔离端的地。GND\_A是ADE7912/ADE7913隔离端A相的地，GND\_B是ADE7912/ADE7913隔离端B相的地，GND\_C是ADE7912/ADE7913隔离端C相的地。电阻分

压电路R1\_x和R2\_x检测A、B、C三相线路与零线之间的电压。每个ADE7912/ADE7913的电流通道ADC测量锰铜分流器上的电压，V1电压通道ADC测量R1\_A、R1\_B和R1\_C电阻上的电压。

图2. 基于锰铜分流器的直连式三相电表架构

注意，当电表基于ADE7912/ADE7913时，不使用电表端子2、5、8。直接连接相位线路的锰铜分流器基准电压端子(GND\_A、GND\_B和GND\_C)成为电阻分压电路电压检测电阻分压电路的基准点。

锰铜分流器、电阻分压电路和ADE7912/ADE7913器件之间有接口电路，详见“ADE7912/ADE7913与锰铜分流器和电阻分压电路的连接”部分。

零线决定微控制器(GND MCU)的地以管理ADE7912/ADE7913器件。这个地与ADE7912/ADE7913的原边地相同。微控制器用一个串行端口接口(SPI)与ADE7912/ADE7913通信。这意味着，电表电源必须向微控制器以及GND MCU地在零线上的ADE7912/ADE7913提供电源电压。

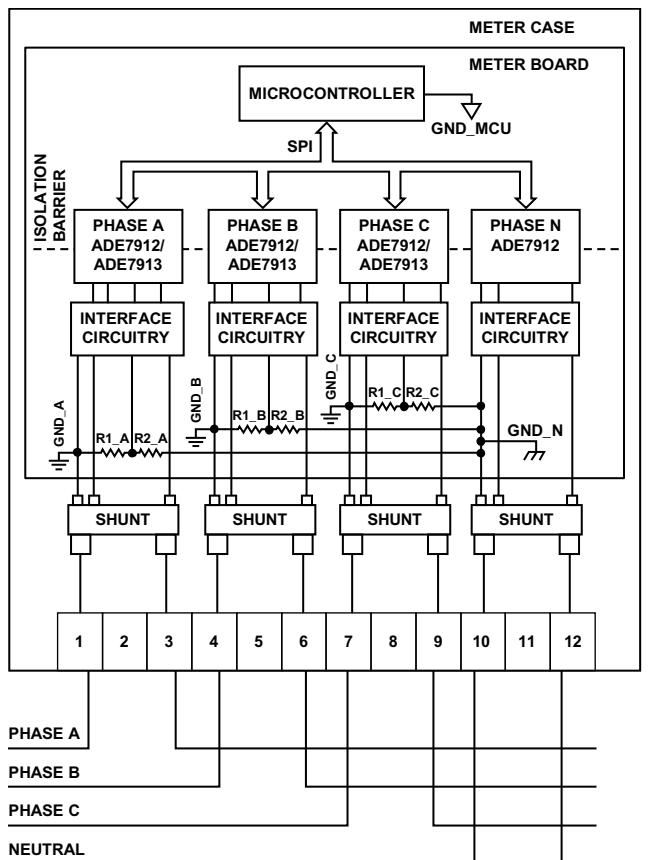

图2中所示电表不监控零线电流。图3展示的直连式三相电表会监控零线电流。唯一区别在于，图3中有一个额外的ADE7912(N相)，它只负责用锰铜分流器检测零线电流。该芯片的电压通道未使用。

微控制器和ADE7912/ADE7913的原边有一个来自零线的隔离地。这意味着，电表电源必须向微控制器和与零线相隔离的ADE7912/ADE7913提供电源电压。

图3. 基于锰铜分流器的三相电表架构(带零线监控)

12865-003

## ADE7912/ADE7913与锰铜分流器和电阻分压电路的连接

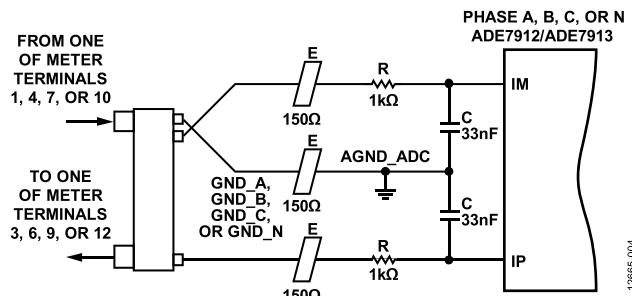

监控三相线路的所有ADE7912/ADE7913都具有相同的接口电路。该电路由两个路径构成：一个把ADE7912/ADE7913与锰铜分流器连接起来(见图4)，一个把ADE7912/ADE7913与电阻分压电路连接起来(见图5)。

A、B、C或N相电流通过一个锰铜分流器检测(见图4)。IP和IM引脚与分流器端子之间的抗混叠滤波器R/C(1 kΩ/33 nF)的角频为4.8 kHz( $1/(2 \times \pi \times 10^3 \times 33 \times 10^{-9})$ )。AGND\_ADC接地点(滤波器电容的偏置点)连接至锰铜分流器的基准端子GND\_A、GND\_B、GND\_C或GND\_N。

图4. ADE7912/ADE7913与锰铜分流器的连接

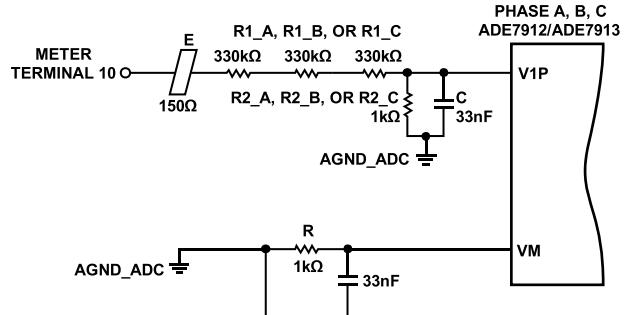

图5. A相ADE7912/ADE7913与分压器的连接

A、B或C相到零线的电压由分压电阻R1\_x和R2\_x检测。电阻R1\_x由三个330 kΩ电阻构成，R2\_x等于1 kΩ。这样可以确保满量程电压等于以下等式，足以监控230 V三相系统：

$$\frac{0.5}{\sqrt{2}} \times \frac{3 \times 330 K + 1 K}{1K} = 350.37 V$$

与R2\_x并联的电容C(33 nF)在V1P引脚路径中形成抗混叠滤波器。在源于锰铜分流器接地端子GND\_x的AGND\_ADC接地点(见图4)与ADE7912/ADE7913的VM引脚之间，有一个相同的抗混叠滤波器R/C(1 kΩ/33 nF)。注意，电流和电压路径中的抗混叠滤波器是相同的。这样可以确保相位电流和电压测量中引起的延迟是相似的。

E磁珠( $150\Omega$ ,  $100\text{MHz}$ )置于锰铜分流器和电阻分压电路连接之间，用于过滤电快速瞬变(EFT)测试过程中可能引入电线的高频噪声。

由于在零线电压相位以外，图2和图3中考虑的电表架构无需测量任何额外电压，因此，图5并未出现连接ADE7913的V2P引脚所需的电路。然而，如果要监控额外的电压，V2P电路则与V1P电路相同。只有ADE7913提供了V2P功能。ADE7912上未提供V2P功能。

### 为ADE7912/ADE7913提供时钟信号

ADE7912/ADE7913数据手册非常详细地说明了如何为三相电表上的ADE7912/ADE7913器件提供时钟信号。

如果微控制器能在 $-40^\circ\text{C}$ 至 $+85^\circ\text{C}$ 的温度范围内，产生一个频率在3.6 MHz至4.21 MHz之间的时钟信号，则由微控制器为电表上的所有ADE7912/ADE7913提供时钟信号。如果微控制器无法产生时钟信号，则用一个晶体为一个ADE7912/ADE7913器件提供时钟信号，并用它为电表上的其他ADE7912/ADE7913提供时钟信号。通过数据手册中详述的上电时序完成此项任务。

两种时钟方案都能确保所有隔离式ADC同步工作：它们同步采集信号并提供相干的ADC输出采样。有关详情，请参阅ADE7912/ADE7913数据手册。

### 与ADE7912/ADE7913通信

ADE7912/ADE7913有一个SPI接口，相应的数据手册非常详细地描述了用于读写器件寄存器的协议。

本节将提出一种系统性方案，用微控制器管理三相电表中的三个或四个ADE7912/ADE7913。

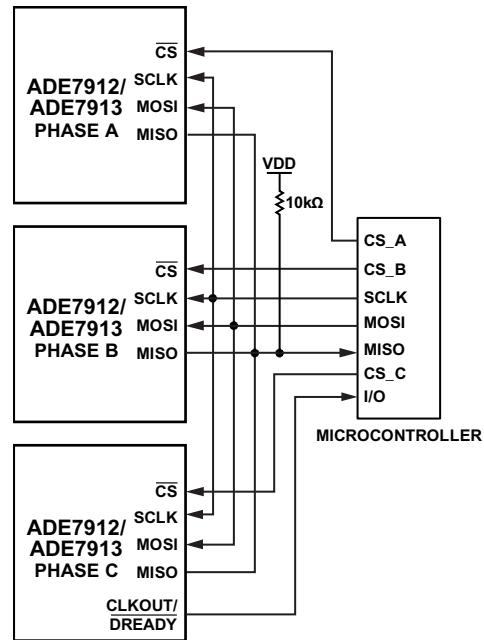

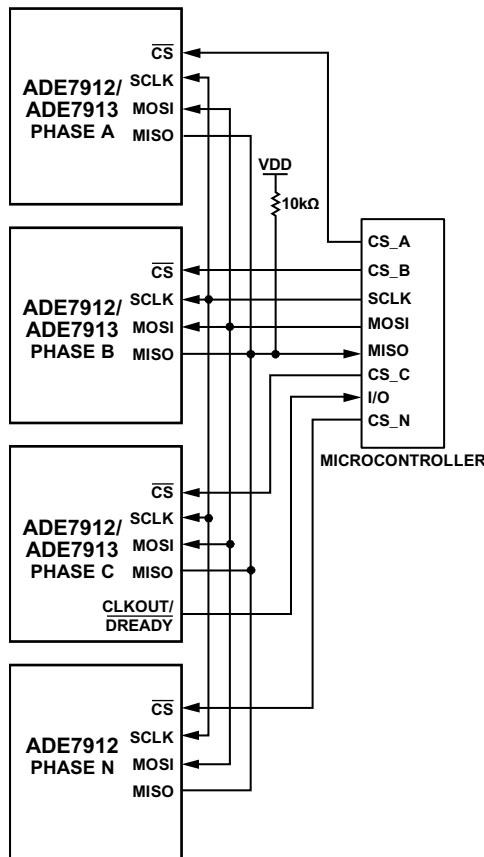

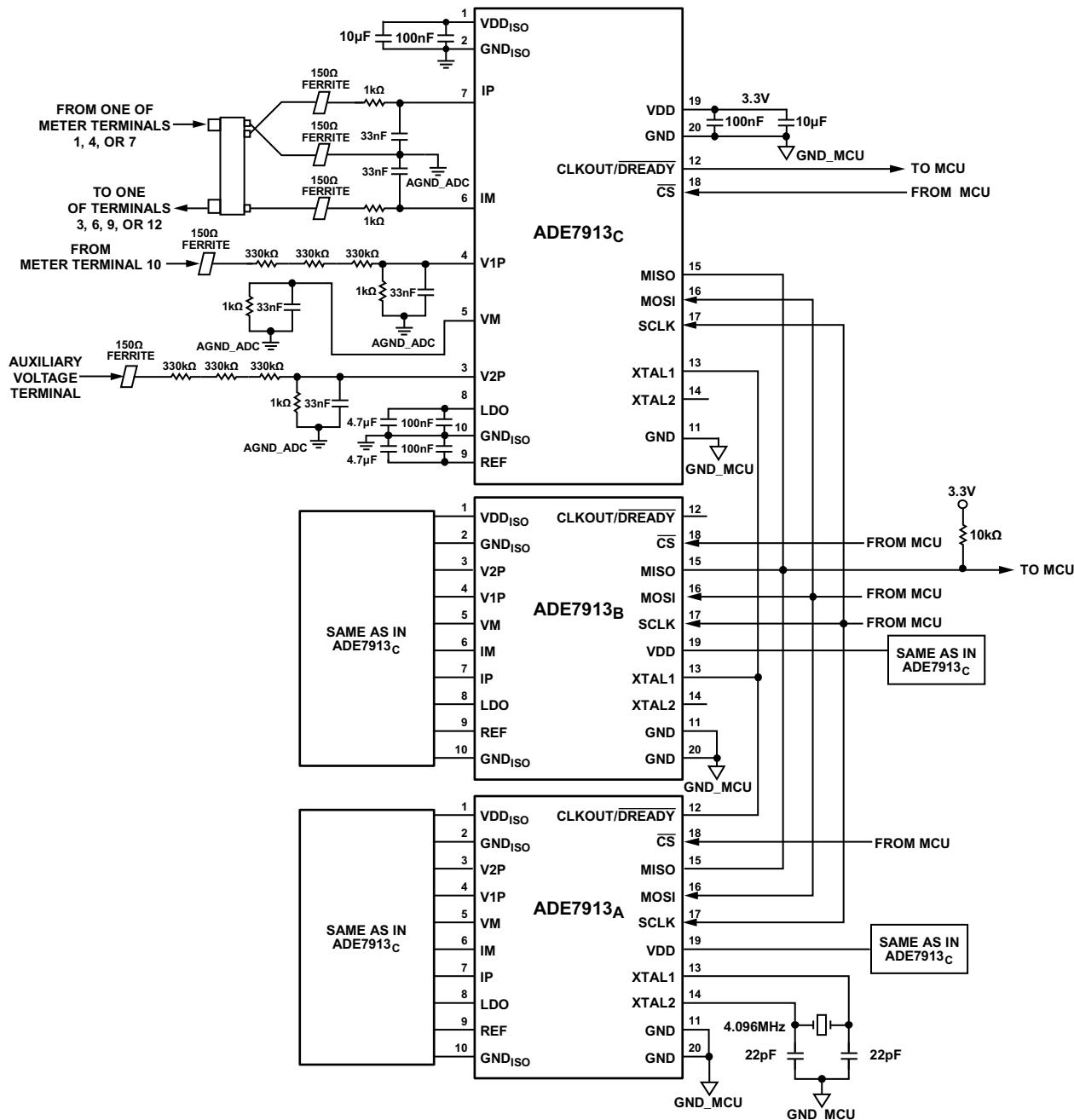

假设，微控制器连接至ADE7912/ADE7913，如图6或图7所示。每个ADE7912/ADE7913的SPI端口均通过微控制器的三个(见图6)或四个(见图7)输入/输出(I/O)线路选定：CS\_A、CS\_B、CS\_C和CS\_N。同时C相ADE7912/ADE7913的CLKOUT/DREADY引脚(ADE7912/ADE7913)连接至微控制器的一个I/O引脚，微控制器可以在该引脚上接收外部中断。

微控制器以最大允许SPI串行时钟频率5.6 MHz与ADE7912/ADE7913通信。

图6. 三个ADE7912/ADE7913与微控制器之间的连接

12665-006

图7. 四个ADE7912/ADE7913与微控制器之间的连接

12665-007

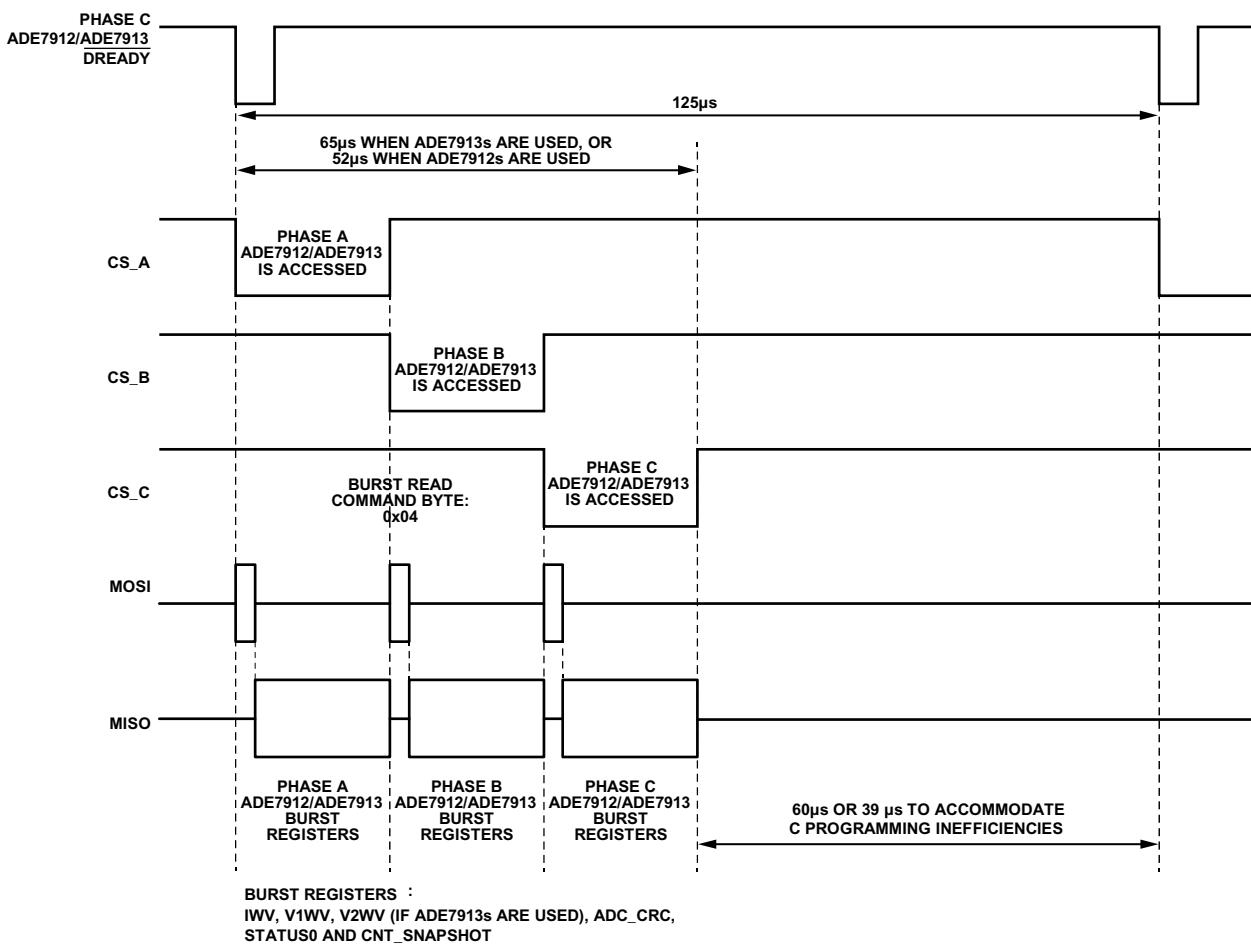

ADE7912/ADE7913设置为在8 kHz下提供ADC输出，即周期为125 μs。把所有ADE7912/ADE7913上的CONFIG寄存器(寄存器0x8)中的位[5:4] (ADC\_FREQ)设为00。

所有ADE7912/ADE7913同步工作，即是说，ADC在全部三个相位上同步采样，ADC输出是相干的。

DREADY功能选择于C相的ADE7912/ADE7913 CLKOUT/DREADY引脚：CONFIG寄存器中的位0(CLKOUT\_EN)清零。每8 kHz，CLKOUT/DREADY引脚变为低电平并保持64个CLKIN循环(15.625 μs，CLKIN = 4.096 MHz)。

图8所示为微控制器接收外部中断的结果，因为管理C相的ADE7912/ADE7913的CLKOUT/DREADY引脚进行了一次高电平至低电平转换。

微控制器对ADE7912/ADE7913输出寄存器执行一次突发读取操作：IWV、V1WV、V2WV(如果使用的是ADE7913)、ADC\_CRC、STATUS0和CNT\_SNAPSHOT。读取ADC\_CRC、STATUS0和CNT\_SNAPSHOT并非强制操作，计算中包括它们是当其作为最差情况考虑的。

从三个ADE7912/ADE7913读取这些寄存器所需时间为(见图6)为

$$3 \times \frac{8 + 3 \times 24 + 16 + 8 + 16}{5.6 \times 10^6} \approx 65 \mu\text{s}$$

事实上，该时间一般都比较长，因为微控制器对SPI通信的管理在C编程方面效率较低，但仍有125 - 65 = 60 μs的剩余时间，可以处理每个ADC输出周期中的C编程低效问题。

图3所示电表含有四个ADE7912/ADE7913。由于管理N相的ADE7912只检测零线电流，因此，从所有ADE7912/ADE7913读取这些寄存器所需时间为

$$4 \times \frac{8 + 3 \times 24 + 16 + 8 + 16}{5.6 \times 10^6} \approx 86 \mu\text{s}$$

时间完全在分配的125 μs之内。在这种情况下，有125 - 86 = 39 μs的时间可以处理最终C编程低效问题。

1265-008

图8. 电表中微控制器与ADE7912/ADE7913之间通信的系统方案

## 电能计量软件程序说明

本节将描述与ADE7912/ADE7913相关的观测结果。建议微控制器内部的电能计量程序考虑这些观测结果。

借助ADE7912/ADE7913数据手册中列出的上电和初始化步骤确保所有ADE7912/ADE7913都能正确启动并同步工作。

根据数据手册的ADE7912/ADE7913规格表，电流通道ADC失调误差的典型值为-2 mV，电压通道ADC失调误差的典型值为-35 mV。ADC失调温漂为 $\pm 500 \text{ ppm}/^\circ\text{C}$ (最大值)。在计算交流电能计量时需要消除该失调，可以通过一个高通滤波器(HPF)来实现。不建议使用室温下的简单失调计算方法，因为这种方法不能完全补偿温度的影响。

无论锰铜分流器以什么方式安装在印刷电路板(PCB)上，它们的电路都会在计量计算结果中引入相位误差。因此，建立使用相位补偿流程，使每个相位上的电流和电压一致。

## 布局布线指南

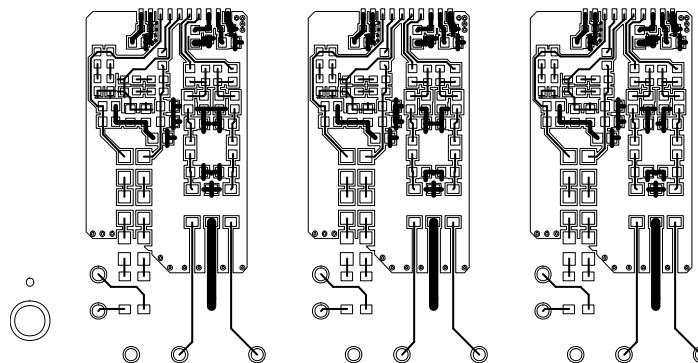

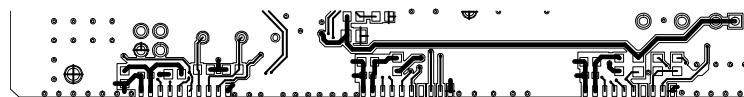

图10所示为一个直连式三相电表(采用三个ADE7913)计量部分的原理图，与ADE7913评估板的原理图相同。图中，第二个电压通道V2有一个电阻分压电路，这样是为了最全面地展示布局。

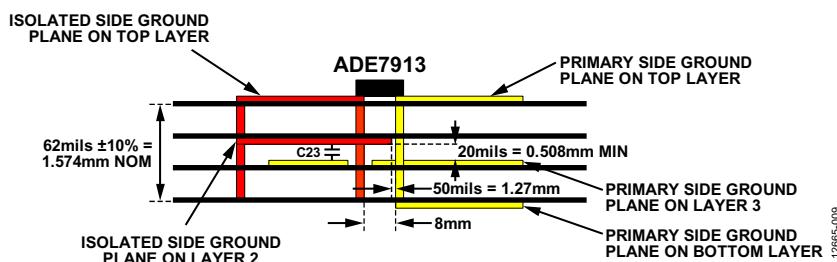

在使用ADE7912/ADE7913时需要4层PCB板。一个三相电表(采用三个ADE7913)仅在使用4层PCB板时，才能达到B类CISPR22标准要求并具备充足的裕量(有关这些结果的详情，请参阅“辐射干扰测试结果”部分)。

顶层和底层与第2层PCB设计相同，内层形成一个拼接电容。拼接电容是减少ADE7912/ADE7913 DC-DC转换器产生的辐射、为了达到标准要求这个是必不可少的。

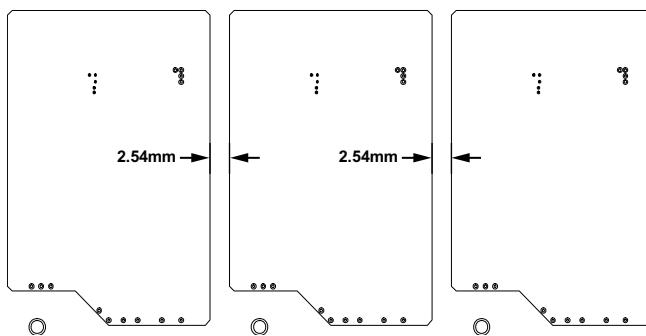

图9显示了4层PCB板的结构。顶层含有元件。第二层形成拼接电容的一面(用ADE7912/ADE7913的GND<sub>ISO</sub>隔离地)。第三层形成拼接电容的另一面(用ADE7912/ADE7913的GND\_MCU原边地)。注意，两块板间的PCB厚度为0.5 mm。由于IEC 62052-31标准要求，当线路到零线电压低于300 V时，最小厚度为0.4 mm，因此，所用厚度为0.5 mm，以充分考虑PCB生产中的任何变化。

不建议反置第二层和第三层，即把GND\_MCU层置于第二层上，把GND<sub>ISO</sub>板置于第三层上，因为GND\_MCU层会与顶层上的锰铜分流器相关PCB走线形成寄生电容。该寄生电容形成的电压会增大锰铜分流器上的电压，与GND<sub>ISO</sub>和GND\_MCU之间的电压成比例且同相。结果也会影响计量测量的精度。把GND<sub>ISO</sub>板置于第二层，把GND\_MCU层置于第三层，GND<sub>ISO</sub>板就能屏蔽GND\_MCU层，并消除顶层上的锰铜分流器IP和IM PCB走线耦合。

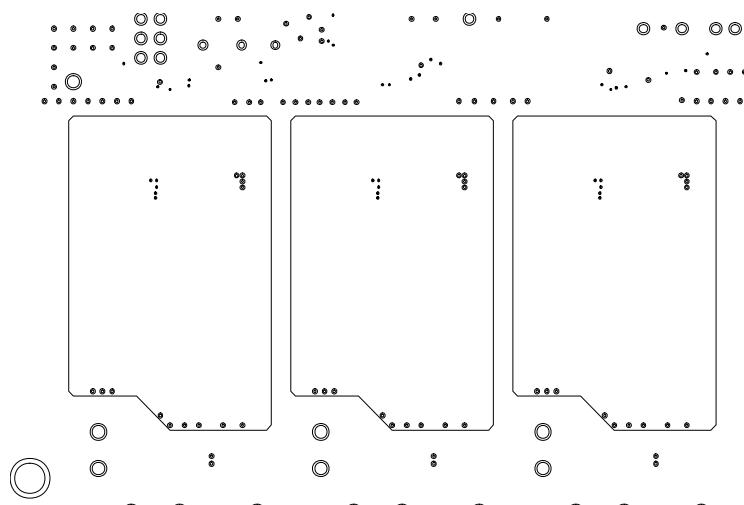

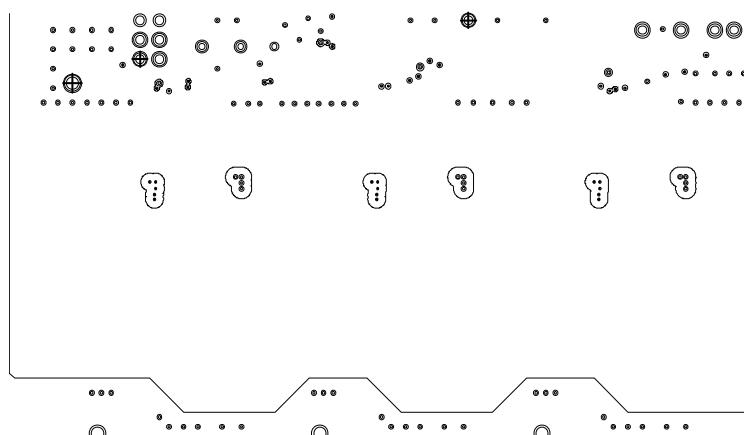

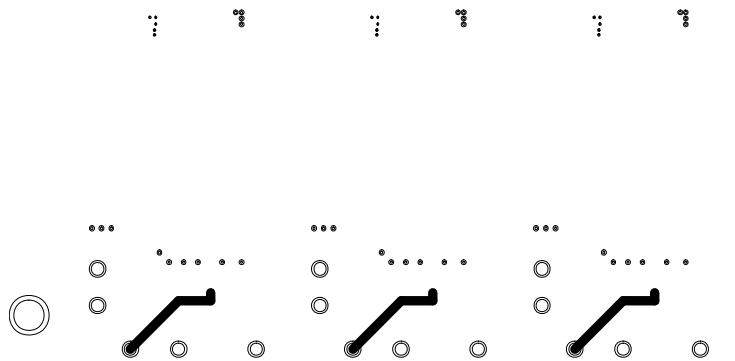

图11、12、13和14展示了图10所示计量部分的建议4层布局方案，这就是ADE7913评估板中采用的布局。

图9. 带拼接电容的四层结构

图10. 直连式三相电表计量部分原理图

11115-008

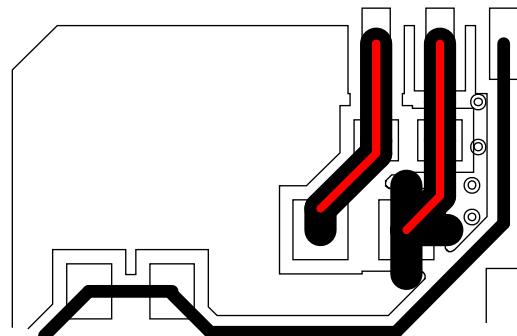

图11. 直连式三相电表计量部分顶层布局

1285-011

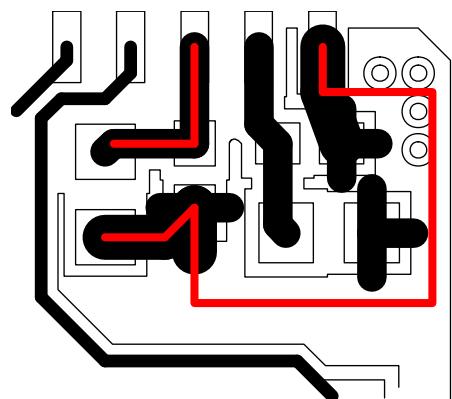

图12. 直连式三相电表计量部分第二层布局

1285-012

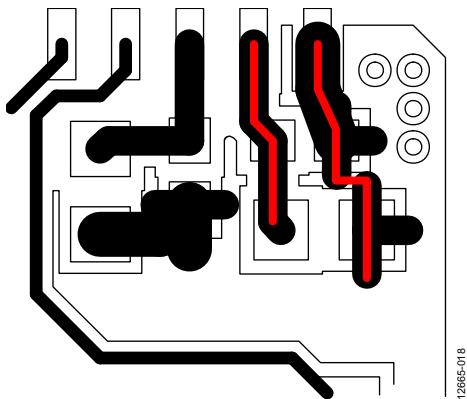

图13. 直连式三相电表计量部分第三层布局

1285-013

图14. 直连式三相电表计量部分底层布局

12665-014

在以下各节中，我们将分析和评论与布局相联系的原理图中的各个部分。

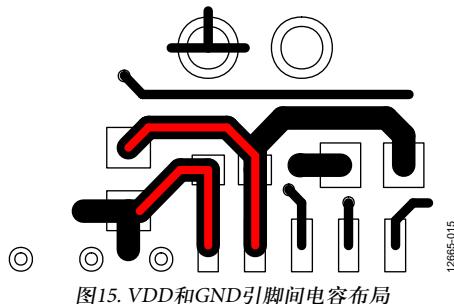

### 去耦电容布局指南

请按照针对 ADE7912/ADE7913 VDD 和 GND(10  $\mu$ F 和 100 nF)、VDD<sub>ISO</sub> 和 GND<sub>ISO</sub>(10  $\mu$ F 和 100 nF)、LDO 和 GND<sub>ISO</sub>(4.7  $\mu$ F 和 100 nF) 以及 REF 和 GND<sub>ISO</sub>(4.7  $\mu$ F 和 100 nF) 引脚间去耦电容的建议执行：

- 使 100 pF 电容应离芯片最近。

- 尽量缩短电容与 VDD、VDD<sub>ISO</sub>、LDO 和 REF 引脚之间的距离。

- 尽量缩短电容与 GND、GND<sub>ISO</sub>、LDO 和 REF 引脚之间的距离。

这样可以提高芯片的电磁兼容(EMC)性能，降低 ADE7912/ADE7913 DC-DC 转换器产生的辐射。

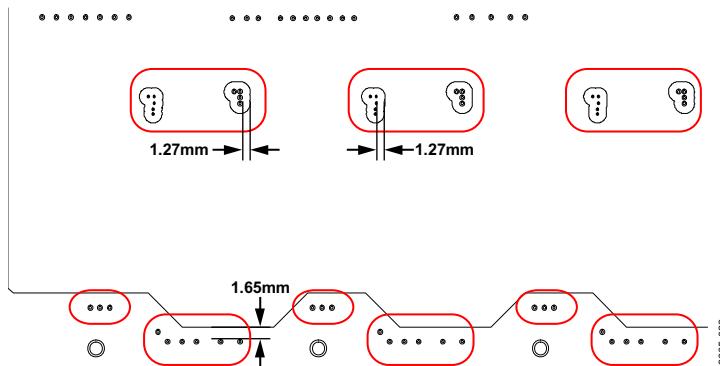

图15、16、17和18展示的是这些电容的各种布局。

图15. VDD和GND引脚间电容布局

12665-015

图16. VDD<sub>ISO</sub> 和 GND<sub>ISO</sub> 引脚间电容布局

12665-016

图17. LDO 和 GND<sub>ISO</sub> 引脚间电容布局

12665-017

图18. REF和GND<sub>ISO</sub>引脚间电容布局

12685-018

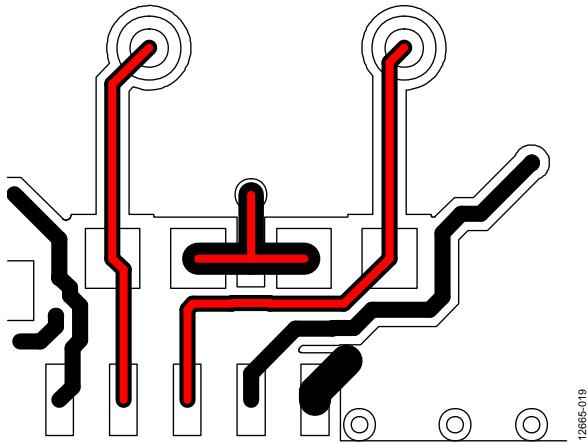

### 晶体和负载电容布局指南

晶体负载电容必须尽量靠近A相**ADE7912/ADE7913**，以提高芯片的EMC性能，晶体则可置于附近(图19)。晶体和负载电容间的距离不如电容与XTAL1和XTAL2引脚间距离重要。

图19. 晶体和负载电容布局

12685-019

### 隔离接地布局指南

**ADE7912/ADE7913**有两个GND<sub>ISO</sub>隔离接地引脚。它们通过一个磁珠连接至锰铜分流器的基准引脚，并决定PCB板顶层上的隔离接地层。GND<sub>ISO</sub>引脚与隔离接地层间的连接必须非常短。用于把顶层上的隔离接地层连接到第二层上的拼接电容的通孔需要靠近GND<sub>ISO</sub>引脚，以尽量降低电感。尽量减少通孔的数量，因为它们会占用拼接电容板的面积并减少电容板的电容。

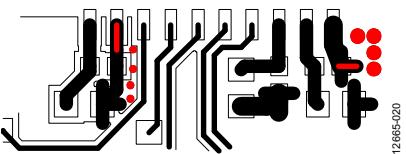

图20. 至隔离接地层的GND<sub>ISO</sub>连接和相关通孔布局

12685-020

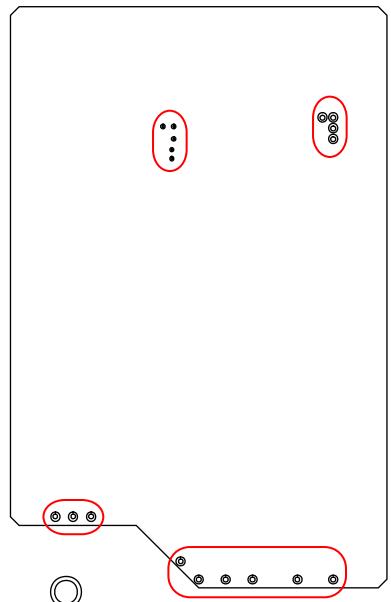

图21. PCB板第二层上形成拼接电容GND<sub>ISO</sub>板的部分

12685-021

图22. 第三层上形成拼接电容GND<sub>MCU</sub>板的部分

图23. 第二层上的全部三个拼接电容

## 辐射干扰测试结果

我们测试了ADE7913评估板相对于B类CISPR22标准的合规情况。评估板用于一个三相电表配置中，以电池供电。把一条5 m无端子连接的三相电缆装放于电表上，然后放在消声腔中的地板下(图24)。

测量了30 MHz至1 GHz和1 GHz至2 GHz两个频率范围内的辐射。

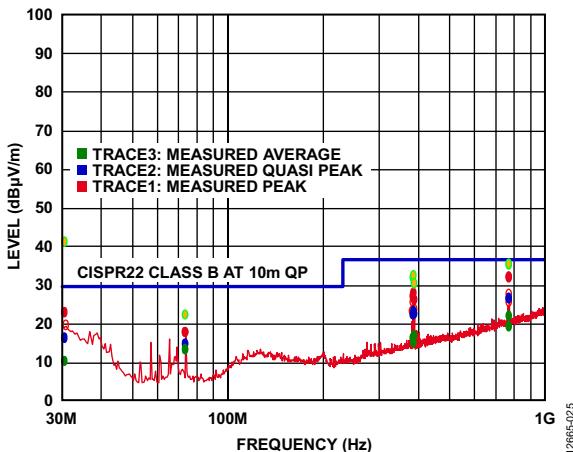

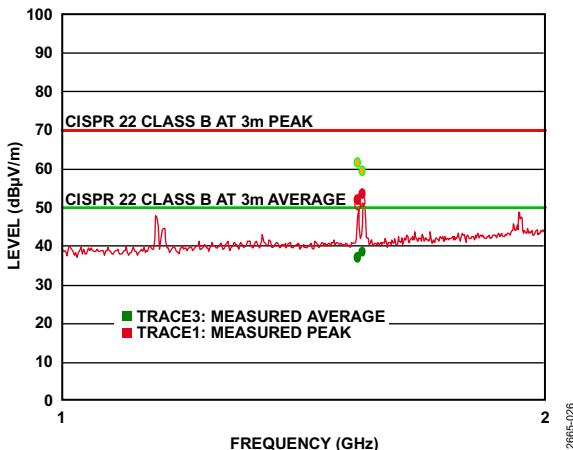

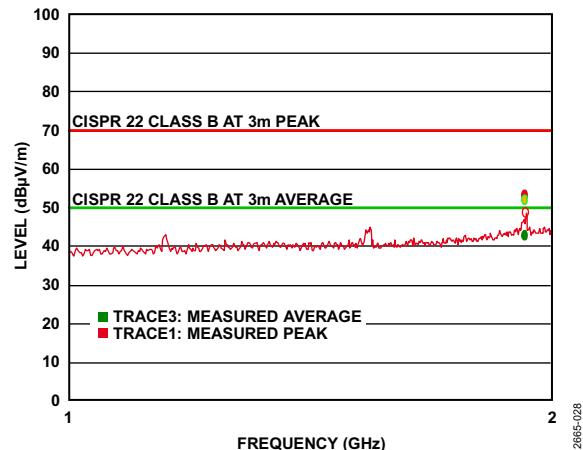

采用84 pF的拼接电容(电容板面积为1100 mm<sup>2</sup>)时，在30 MHz至1 GHz频率范围内，相对于B类CISPR22标准限值，得到了最小值为10 dB $\mu$ V/m的准峰值裕量(图25)。1 GHz至2 GHz频率范围内，相对于B类CISPR22标准限值，得到了最小值为11 dB $\mu$ V/m的平均结果裕量(图26)。

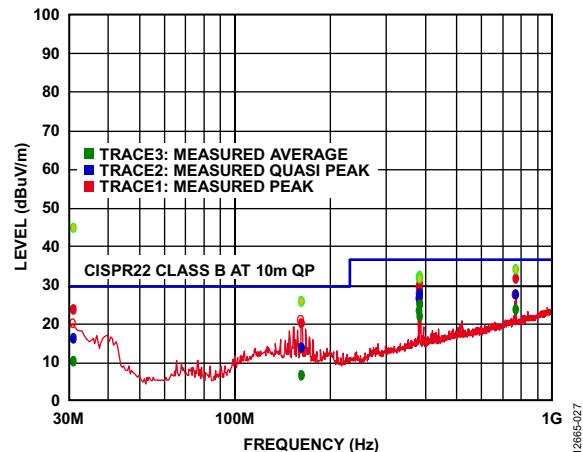

为了测试拼接电容较小时的辐射，我们用一个63 pF的电容(825 mm<sup>2</sup>)构建了一块ADE7978评估板。由于从辐射角度来看，该评估板上使用的一个ADE7933隔离式ADC等效于一个ADE7913，我们可以说，ADE7978评估板在行为上同基于ADE7912/ADE7913的设计等效。在30 MHz至1 GHz频率范围内，该评估板相对B类CISPR22标准拥有9 dB $\mu$ V/m的准峰值裕量(图26)；1 GHz至2 GHz频率范围内，则拥有7 dB $\mu$ V/m平均结果裕量(图28)。

如前所述，我们不建议采用拼接电容小于63 pF的PCB设计(即电容板面积小于825 mm<sup>2</sup>)。例如，当采用42 pF的拼接电容(电容板面积为550 mm<sup>2</sup>)时，ADE7978评估板在380 MHz频率下超出B类CISPR22标准限值4 dB $\mu$ V/m。

图24. 电池供电的三相电表(置于消声腔中)

图25. ADE7913评估板的消声腔辐射(采用84 pF的拼接电容, 准峰值点为蓝色, 30 MHz至1 GHz)

图27. ADE7978评估板的消声腔辐射(采用63 pF的拼接电容, 准峰值点为蓝色, 30 MHz至1 GHz)

图26. ADE7913评估板的消声腔辐射(采用84 pF的拼接电容, 平均点为绿色, 1 GHz至2 GHz)

图28. ADE7978评估板的消声腔辐射(采用63 pF的拼接电容, 平均点为绿色, 1 GHz至2 GHz)

## 结论

本应用笔记展示了如何运用ADE7912/ADE7913隔离式ADC, 开发带锰铜分流器的直连式三相电表。就原理图和布局提出了建议, 以超出B类CISPR22辐射标准至少10 dB $\mu$ V/m。展示了微控制器应该保留多少带宽, 以便管理最多有四个ADE7912/ADE7913的SPI通信。

I<sup>2</sup>C指最初由Philips Semiconductors(现为NXP Semiconductors)开发的一种通信协议。