# 常见问答

## LDO入门

### LDO内部有什么？

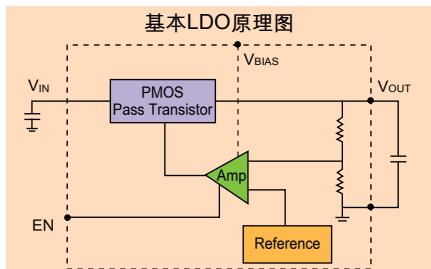

如图a所示，低压差稳压器(LDO)由参考电压、误差放大器、反馈分压器和一个串联传输元件(通常为双极性或CMOS晶体管)组成。

输出电流由PMOS晶体管所控制，而PMOS晶体管又由误差放大器所控制。这个放大器将来自输出的反馈电压与参考电压进行比较，并放大压差。

图a: LDO能以低压差提供由输入电压到输出电压所需的稳压，也就是 $V_{in}$ 与 $V_{out}$ 之间发生微小电压变化。

如果反馈电压低于参考电压，PMOS器件的栅极会被下拉，从而允许更多的电流通过和提高输出电压。相反，如果反馈电压高于参考电压，PMOS器件的栅极会被上拉，从而使更少的电流通过和减少输出电压。

这个闭环系统主要基于两个极点，即误差放大器/传输晶体管的内部极点和输出电容等效串联电阻(ESR)的外部极点。

当使用推荐的电容时，ADI的LDO能够在指定工作温度和电压范围内稳定工作。输出电容的ESR会影响LDO控制回路的稳定性。为了确保控制回路的稳定性，推荐使用 $1\Omega$ 的最小ESR或更低的电阻值。LDO对负载电流快

速变化的响应，即瞬态响应，也受输出电容的影响。使用更大值的输出电容可改善LDO的瞬态响应，然而这会导致启动时间延长。

### 为何使用LDO？

LDO稳压器是为了从主电源或电池处获得低输出电压。理想情况下，输出电压对线路和负载变化而言是稳定的，也不会因外界温度和时间而发生变化。

LDO输入和输出电压之间的压差应该尽可能的低。例如，在电池供电的设计中利用锂离子电池连接一个2.8V的LDO。这个电池电压会从4.2V(充满状态)下降到3.0V(电池耗尽)，并恒定提供2.8V输出以使LDO的压差低于200mV。

在一些系统中，LDO被用于后稳压。这种情况下LDO连接到高效的开关稳压器的输出，来提供噪声滤波以及恒定且稳定的输出电压。

### 高性能LDO有什么新功能？

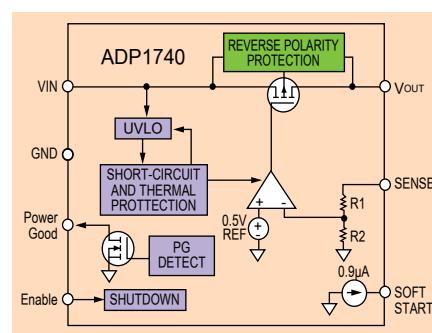

高性能LDO包含了使能输入、电源良好指示、欠压锁定、反极性保护、感应输入和软启动功能。如图b所示。

图b: 加入新功能的高性能LDO方框图。

## 十大常

### 1. 什么是LDO稳压器？

LDO低压差稳压器(Low Dropout Regulator)是一种经典的稳压器，相比于传统三端固定电压稳压器，它能实现更小的输入/输出压差。理想情况下LDO能够提供固定的或是可调节的输出电压，不会因时间和温度而发生变化，并且不受线路与负载变化的影响。

### 2. LDO的主要选型标准包括哪些？

输入电压范围；输出电压，固定或可调节；随线路、负载和温度变化的输出精度；负载电流需求；压差；电源抑制比(PSRR)；输出噪声；静态电流和关断电流。

### 3. 输出旁路电容的值是否会影响LDO的性能呢？

LDO的设计通常为特定值的负载旁路电容而优化。增加负载电容值使其大于推荐值可以改善负载的瞬态响应。然而，当选择了更大值的输出电容的时候，也应该相应增加输入旁路电容的值。请注意：输入和输出电容的放置应该尽可能地靠近LDO。

### 4. 哪几种电容可用作输入/输出旁路电容？

任何质量好的陶瓷电容都可以用作旁路电容，只要它们能够满足LDO数据手册上所列的最小电容和最大有效串联电阻(ESR)技术指标。极力推荐采用X5R或X7R介质的陶瓷电容，因为它们具有很好的温度稳定性和非常低的电压系数。

### 5. LDO的地电流会随负载电流而改变吗？

当输出负载增加时，使用双极性晶体管作为传输元件的设计会呈现更大的地电流变化，可达到负载电流的5%。而基于LDO的MOSFET的功效更佳，因为它的地电流随负载增加而提升的程度被最小化，一般小于满负载时的0.1%。

### 6. 什么是电源抑制比(PSRR)？

电源抑制比(PSRR)表示LDO在输入电压变化时防止输出电压波动的能力。

# 产品问答

## 为FPGA和嵌入式处理器应用优化的新型LDO线性稳压器系列

### 见问答

通常在特定频率下指定PSRR值，如120Hz下60dB电源抑制比。电池供电系统应当使用LDO，以便能在电池电压低(即低输入输出电压差)时继续保持很高的PSRR。

#### 7. 如果LDO由开关电源所驱动，高频开关噪声能否被抑制？

LDO能够抑制几十乃至几百kHz的输入噪声。高频(1MHz以上)开关噪声主要通过输出旁路电容网络进行抑制；在1MHz以上，LDO的回路带宽太低以致无法提供任何噪声衰减。LDO可与传输元件、输出电容网络与负载形成阻抗分压器，这能在高频时提供噪声抑制。

#### 8. 导致LDO输出噪声的原因有哪些，该如何降低？

LDO内部的电压参考是主要的输出噪声源。它通常以特定带宽内的微伏均方根值来表示，比如1至100kHz范围内的均方根值为25 $\mu$ V。这个低电平噪声大大低于DC/DC转换器的开关瞬态和谐波。一些LDO在旁路引脚接一个电容到地以滤除参考电压噪声。遵循数据手册规定的输入、输出和旁路电容会令噪声电平问题迎刃而解。

#### 9. LDO具有最小负载电流要求吗？

ADI的LDO都没有要求最小负载电流。然而，市场上很多竞争性LDO产品的确对最小负载电流有要求，有些甚至达到数mA之高。

#### 10. 在LDO选型时需注意的关键特性包括哪些？

包括一个用来控制LDO开启和关断以节省系统功耗的使能输入；可编程的软启动，在启动过程中限制浪涌电流、控制输出电压上升时间，并实现电压时序控制；追踪功能，允许LDO输出跟随外部电压轨或参考电压；一个旁路引脚，允许外部电容减少输出电压噪声并改善电源抑制；电源良好输出，用以说明输出处于稳压之中；热关断，在温度超出规定水平时关断LDO；电流限制功能，以控制LDO输出电流和功耗。

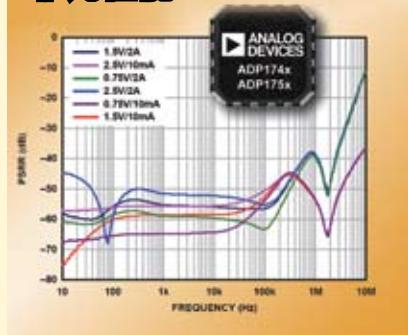

ADI新型的ADP174x、ADP175x系列高性能LDO是低VIN、低压差线性稳压器，设计用于为基于DSP、FPGA和微处理器的系统供电。ADP1740/41/52/53/54/55系列器件提供高达2A负载电流的解决方案，推荐用于为SHARC和Blackfin处理器以及种类广泛的工业FPGA供电。

ADP1740/41/52/53/54/55器件是引脚兼容的低压差CMOS线性稳压器，能够工作在1.6V至3.6V。这些LDO产品具备低VIN/VOUT，是对I/O电压轨从2.5V降至1.8V的纳米级FPGA进行稳压，以及为低至0.75V的内核电压供电的理想之选。

ADP1740/41/52/53/54/55采用高级专有架构，具有非常高的电源抑制

### LDO新系列带来非凡性能

比(PSRR)和非常低的噪声，仅需4.7 $\mu$ F的输出陶瓷电容就能够获得极佳的线路和负载瞬态响应。现已可提供固定输出电压的产品，以及可由外部电阻分压器设定的0.75V至3.0V可调节电压产品。

| 型号       | 输出电流范围 | 输出电压(V)                            | 压差         | 封装                |

|----------|--------|------------------------------------|------------|-------------------|

| ADP1740  | 高达2A   | 0.75, 1.0, 1.1, 1.2, 1.5, 1.8, 2.5 | 160mV@2A   | 16引脚LFCSP 4mmx4mm |

| ADP17401 | 高达2A   | 0.75至3.0可调                         | 160mV@2A   | 16引脚LFCSP 4mmx4mm |

| ADP1752  | 高达0.8A | 0.75, 1.0, 1.1, 1.2, 1.5, 1.8, 2.5 | 70mV@0.8A  | 16引脚LFCSP 4mmx4mm |

| ADP1753  | 高达0.8A | 0.75至3.0可调                         | 70mV@0.8A  | 16引脚LFCSP 4mmx4mm |

| ADP1754  | 高达1.2A | 0.75, 1.0, 1.1, 1.2, 1.5, 1.8, 2.5 | 105mV@1.2A | 16引脚LFCSP 4mmx4mm |

| ADP1755  | 高达1.2A | 0.75至3.0可调                         | 105mV@1.2A | 16引脚LFCSP 4mmx4mm |

欲了解ADI公司的所有LDO驱动器，请访问

[www.analog.com/zh/LDO](http://www.analog.com/zh/LDO)。