# 常见问答

## 数据转换器时钟

Don Tuite

模拟/电源编辑

### 在选用高性能数据转换器的时钟芯片时，最关键的性能特征是什么？

时钟信号的相位噪声(或抖动 — 相位噪声的时域表现)是最关键的指标，但也要关注抖动的积分频带。相位噪声会限制信噪比(SNR)。对于转换器应用来说，宽带均方根(RMS)附加抖动是一个可供比较的良好指标。对网络应用来说，一般规定具体的偏移带宽，如12kHz~20MHz或5MHz~80MHz。不管是哪种应用，一定要检查测量条件。例如在数据转换器应用中，更快的压摆率将带来更高的信噪比。另外，在严格的偏移失调带宽上进行测量可降低抖动幅度。

为了取得最高的信噪比，高性能的高速转换器要求时钟的RMS抖动值小于200fs，因此设计者应选择在实际条件下抖动可能最小的器件。如果转换器的输出数量不够多，需要增加小于100fs的扇出时钟缓冲器，以避免在时钟链中引入太多的附加抖动。

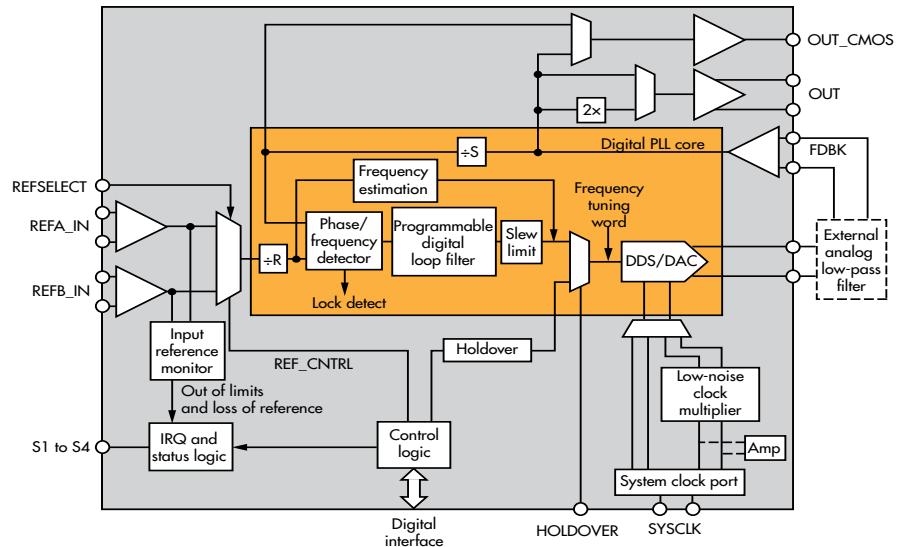

ADI公司数字锁相环器件AD9549的输出信号相位和频率与所选参考时钟直接相关。然而，系统时钟主导着相位噪声频谱。PLL内核中的可编程数字滤波器可减少参考时钟上的任何抖动。

### 哪些类型的时钟芯片可用于驱动数据转换器？

时钟芯片可以基于模拟或数字锁相环(PLL)，它们可能包含整数和小数N分频PLL，甚至包含多达4个PLL的器件。虽然没有明显的理由一定要选模拟或数字作为PLL的基本技术，但是

对于小数N分频PLL和倍频PLL器件要进行几方面的考虑，特别是在实现小数N分频PLL时，产生的杂散信号实际上往往是个很大的问题。

使用级联PLL的新款时钟器件改进了抖动性能。这种器件的前端环路使用带宽很窄的环路滤波器，可向第二个(后端)PLL提供非常干净的参考源，因此这种设计可以接收噪声较大的系统参考时钟，并产生信噪比非常高的输出信号(图1)。

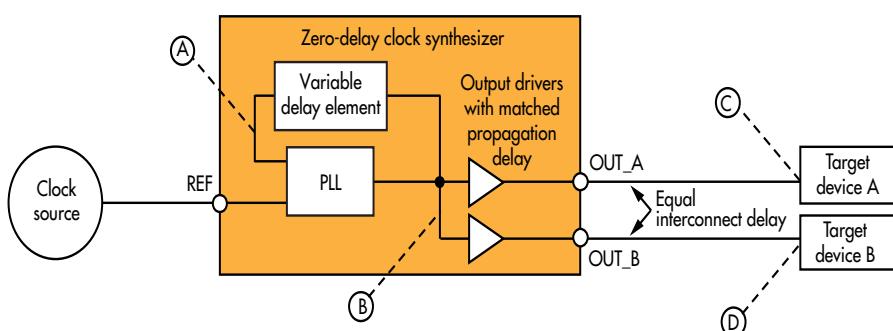

2. 集成式零延时时钟合成器由一个PLL、两个(或两个以上)具有匹配传播延时的输出驱动器以及PLL反馈路径中的可变延时单元组成。这种时钟合成器还需要从合成器输出到关联目标器件的各个互连延时相等。PLL将A点的时钟沿与REF时钟沿对齐。PLL反馈路径中的可变延时单元会造成B点的时钟沿超前A点时钟沿一段的可变延时。这个可变延时被设为输出驱动器传输延时和互连延时之和，因此C点的时钟沿与A点时钟沿也是对齐的，并且都与REF时钟沿对齐。

### 转换器时钟信号使用什么逻辑电平？

目前的大多数转换器使用的是差分低压正发射极耦合逻辑(LVPECL)，采用3.3V电源电压，低电平和高电平阈值分别是1.6V和2.4V。与低压差分信号(LVDS)相比，LVPECL时钟边沿更快，使得转换器的时钟输入缓冲器的不确定时间更短。有时也会用到其它逻辑电

# 产品问答

## 使用ADI公司时钟芯片实现数据转换器的最佳信噪比性能

平，如高速转换逻辑(HSTL)。这些电平具有更陡的边沿，只要信号被正确的端接，就可以实现更高的信噪比。

### 满足多路时钟信号需求的最佳途径是什么？

像现场可编程门阵列(FPGA)和复杂的可编程逻辑器件(CPLD)等，它们并不需要像数据转换器所要求的性能等级。这些器件通常可以使用与转换器相同(或者整数关系)的频率。只要时钟器件能够提供足够多的输出路数，那么采用同一个参考时钟就可以轻松地支持这些器件。

随着系统变得越来越复杂，电路板上需要的时钟信号数量也与日俱增，但同时，串扰、电磁干扰和信号衰减等诸多因素也限制了电路板上的时钟走线数量。

极低的抖动、高触发速率、低功耗LVPECL缓冲器可以为额外的转换器通道提供时钟，使高速度、高分辨率转换器获得最佳的信噪比性能。(FPGA使用极低功耗、低成本和高集成度的LVDS缓冲器)。

市场上现在存在一些高通道密度的时钟分配产品和高扇出的时钟发生器，但这些器件并不总能满足全部要求，因此，简单而高性能的时钟缓冲器或分频器以及具有窄扇出的器件也在市场上占据一席之地。

### 什么是“零延时”，为什么需要零延时？

零延时是指时钟合成器的一种能力，它能使输出信号的边沿与时钟参考源对齐(图2)。零延时功能的应用包括许多同步系统，例如SONET和同步数字分层(SDH)网络、高速网络服务器、线卡以及用于W-CDMA和Wi-Fi的基带时序。

AD9520多路输出时钟发生器包含一个512字节的嵌入式EEPROM存储模块，为系统工程师提供了可同时用作时钟源和系统时钟的可编程时钟解决方案，这种方案在器件集成、低噪声、低抖动性能和信号输出灵活性方面达到业界最佳的组合。除了片上EEPROM和PLL之外，AD9520还集成了分频器、扇出缓冲器和调节范围从1.4GHz至2.95GHz的VCO(压控振荡器)。也可以使用最高可至2.4GHz的外部3.3V/5V VCO/VCXO(压控晶体振荡器)。这个PLL/VCO时钟发生电路在200MHz时钟信号10kHz偏移处的相位噪声可以达到业界领先的-150dBc/Hz，而且时钟分配扇区通道也具有225fs的超低宽带抖动。

通过使用片上存储器编程自己特殊的输出条件集，设计者可以轻松地将AD9520配置为时钟源，确保系统上电或复位时初始处理功能得到同步。其它竞争性时钟芯片需要独立的时钟源，为了编程系统时钟芯片，这个时钟源必须与系统处理器或微处理器单独实现匹配，因而会增加时钟设计的元器件数量、成本以及复杂性。

针对于需要冗余参考时钟的应

用，AD9520提供了两路参考时钟输入，两路之间能够进行无缝波(毛刺)切换，同时PLL保持模式能在参考信号丢失时保持输出频率。零延时功能可确保输入和输出之间精确的相位对齐。AD9520共有12路差分LVPECL(低压正发射极耦合逻辑)输出，分为4组，每路输出具有一个1至32的分频器和相位延时。

AD9520采用通用多路输出架构、集成式PLL和片上EEPROM，具备出色的抖动性能，为采样时钟发生和高速转换器时钟分配提供了理想的解决方案，可应对当前设计者面临的挑战。

目前许多高性能系统设计需要12个以上的时钟通道。针对这些应用，AD9250可以与具有极低抖动、极低压摆率、低功耗的高速时钟缓冲器(如ADCLK954扇出时钟缓冲器)配套使用。

12通道ADCLK954 LVPECL扇出缓冲器具有业界领先的抖动(75 fs rms)和压摆率(9ps)性能，可以帮助设计工程师从ADC或DAC获得更高的信噪比。4.8GHz ADCLK954有两个可选的差分输入，两个输入都配备了100Ω片上端接电阻，可连接差分或单端时钟源。

| 型号       | 说明                | 宽带均方根<br>抖动值( $f_s$ rms) | 输出数量和<br>逻辑类型         | 封装       |

|----------|-------------------|--------------------------|-----------------------|----------|

| AD9520   | 可编程时钟发生器          | 225(分配和扇出)               | 12 LVPECL/<br>24 CMOS | 64-LFCSP |

| ADCLK954 | 高速、高性能时钟扇出<br>缓冲器 | 75                       | 12 LVPECL             | 40-LFCSP |

欲了解更多详情，请访问：[www.analog.com/China/AD9520](http://www.analog.com/China/AD9520)。