# 应用工程师问答—3

作者: James Bryant

## 电压频率转换器

问: 如何在不损失精度的情况下长距离传输模拟信号?

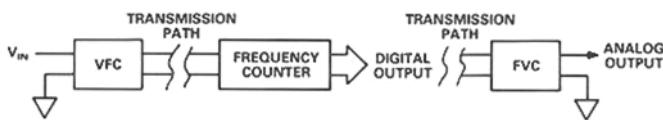

答: 对这一常见问题,有一个出色的解决方案是利用电压频率转换器(VFC)以频率形式传输信号。VFC的输出频率与其输入信号成正比。长距离传输频率信号相对较容易,光隔离器、光纤链路、双绞线或同轴电缆、无线电链路等不会造成干扰。

如果数据必须是数字式,则只需将接收器做成一个频率计数器,利用单芯片微处理器很容易实现。通过“频率电压转换器”(FVC)可以将频率转换为模拟电压;FVC一般是利用锁相环配置为执行反向功能的VFC。

问: VFC 如何工作?

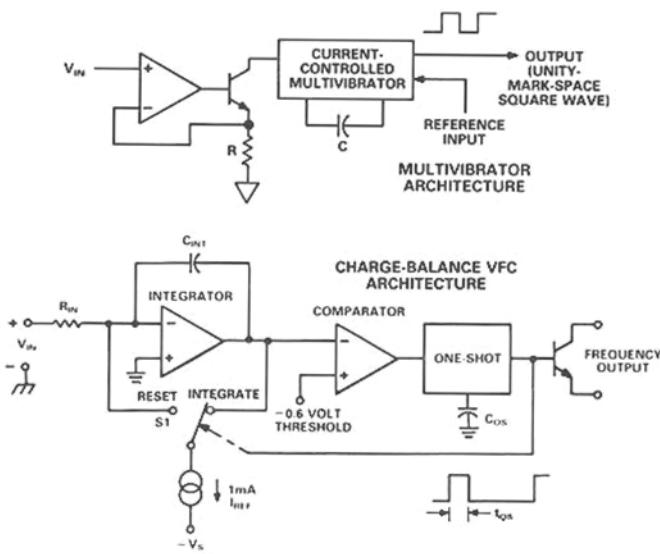

答: 常见的 VFC 有两类:多谐振荡器式(AD537)和电荷平衡式(AD650)。<sup>\*</sup>

多谐振荡器式 VFC 将输入电压转换为电流,电流将对电容充电和放电。开关阈值由一个稳定的基准电压源设置;具有单位传号空号比的输出频率与输入信号成正比。

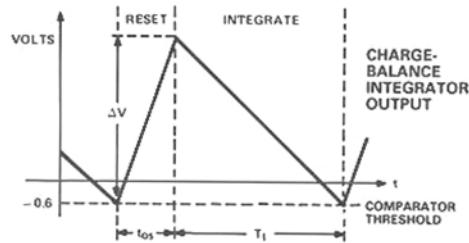

电荷平衡式 VFC 使用积分器、比较器和精密电荷源。输入信号施加于积分器进行充电。当积分器输出达到比较器阈值时,就会触发电荷源,并从积分器中移除固定的电荷。电荷移除速率必须与电荷供应速率相平衡,因此电荷源的触发频率与积分器的输入成比例。

问: 两类 VFC 各有哪些优点和缺点?

答: 多谐振荡器式 VFC 简单便宜,功耗需求低,并具有单位传号空号(M-S)输出,这对某些传输介质非常有利。但它的精度不如电荷平衡式 VFC,而且不能对负输入瞬变进行积分。

电荷平衡式 VFC 更加精确,并且能够对负输入瞬变进行积分以作为输出的一部分。但它的电源需求更苛刻,输入阻抗较低,而且输出是一个脉冲串,而不是单位 M-S 方波。

问: VFC 有哪些重要的误差类型?

答: 与大多数精密电路相同,它主要有三类误差:失调误差、增益误差和线性误差,此外它们都随温度变化。与大多数精密电路一样,失调和增益误差可以由用户进行调整,但线性误差则不能。不过,VFC 的线性度一般非常好(前提是选择适当的电容,见下文)。

问: 如何调整 VFC 的增益和失调?

答: 理论上讲,建议首先在 0 频率时调整失调,然后在满量程(FS)时调整增益。但这会引起“0 频率”识别问题,因为 0 频率状态时 VFC 正好不振荡。因此,最好是用一个小输入信号(例如 0-1% FS) 调整失调,从而达到一个标称频率,然后在满量程时调整增益,最后重复整个程序一次或两次。

例如,假设一个 VFC 在 10V 输入时的满量程(FS)为 100 kHz。理想情况下,10 V 输入应产生 100 kHz 输出,10 mV 输入应产生 100 Hz 输出。因此,首先在 10 mV 下调整失调以获得 100 Hz 输出,然后在 10 V 下调整增益以产生 100 kHz 输出。但增益误差会对 10 mV 失调产生细微的影响,因此可能需要重复执行该程序以降低残差。

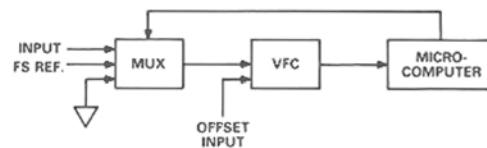

如果通过软件校准使用 VFC,则常常需要引入一个失调电压,使得 VFC 在零输入电压下有一个确定的频率。微处理器测量 0 V 和 FS 输入下的 VFC 输出,并计算失调和比例因子。必要时还可以降低增益,使得 VFC 不会超过其最大额定频率。

\* 本文提到的所有 ADI 产品都有数据手册可供参考。另外还可以免费获得应用笔记:“电压频率转换器 AD654 的工作原理和应用”。

问：使用 VFC 时需要哪些电路保护措施？

答：对于使用 VFC 的电路，除了任何精密模拟电路都应注意的一些常见事项（接地、去耦、电流布线、噪声隔离等，这需要一本书才能说清楚，几句话远远不够）之外，还应重点关注电容的选择以及输入端与输出端的分离。

精密 VFC 的关键电容（多谐振荡器式的定时电容和电荷平衡式的单稳态定时电容）必须非常稳定，不随温度而变化。此外，如果电容发生电介质吸收问题，VFC 将不能保持线性，并且建立时间特性可能很差。

如果一个电容充电、放电然后开路，它可能会恢复一些电荷。这种效应称为电介质吸收(DA)，会降低使用这种电容的 VFC 或采样保持放大器的精度。因此，VFC 和 SHA 应当使用低 DA 的特氟龙、聚丙烯或零温度系数(NP0、C0G)陶瓷电容。

VFC 输出端与输入端之间的耦合也会影响其线性误差。为了避免出现问题，应当遵循去耦规则和常用的布线防护措施。这对于要求大电流驱动(10-30 mA)的光耦合器至关重要。

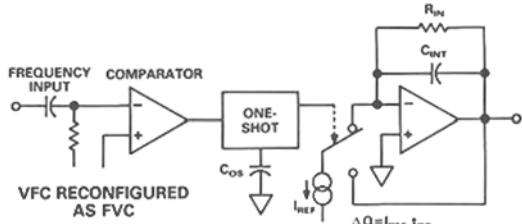

问：如何构建频率电压转换器？

答：有两种常用方法：一是输入频率触发电荷平衡式 VFC 的单稳态，这种 VFC 有一个与积分电容并联的电阻；二是将输入频率施加于一个锁相环(PLL)的相位/频率比较器，使用任一类型的 VFC 都可作为 PLL 的振荡器。第一种方法的基本原理如图所示。

在每个输入频率周期，电荷  $\Delta Q$  传送到  $R$  与  $C$  构成的漏泄积分器。当达到平衡时，在每个周期内都有等量的电荷必须泄漏掉。对于输入频率  $f$ ，对应的周期  $T(=1/f)$ ，电荷以  $I=V/R$  平均速率泄漏，因此  $V=\Delta Q \cdot f \cdot R$ 。

虽然平均电压与  $C$  无关，但输出纹波与  $C$  反相关。峰峰值纹波电压  $\Delta V$  由公式  $\Delta V = \Delta Q/C$  决定。这表明纹波与频率无关（假设与输入周期相关的短时间内传送电荷）。这类 FVC 的建立时间由指数时间常数  $RC$  决定，由此可以计算误差范围内的建立时间。

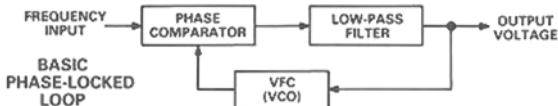

从这些公式可以看出，这类 FVC 的特性彼此相关，无法单独优化纹波和建立时间。若要单独优化各特性，必须使用 PLL。

下面显示的锁相环 FVC 与任何其它 PLL 只有一个方面不同：常规 PLL 使用单片但不必是线性的压控振荡器，而该锁相环 FVC 使用遵从线性控制法则的 VFC。在伺服系统中，负反馈使 VFC 的输出频率与输入频率保持相等。输出电压（即 VFC 的输入电压）与其输入频率具有精确的比例关系。

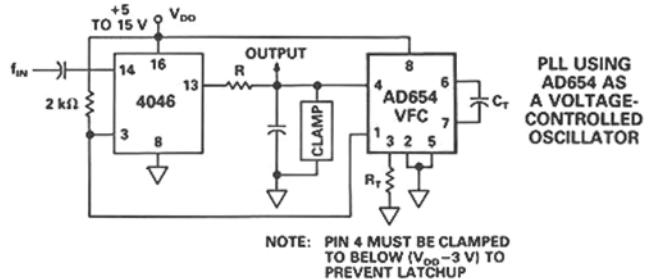

设计 PLL 系统超出了本期问答讨论的范畴<sup>1</sup>，但如果将 4004 系列 CMOS PLL(4046)仅用作一个鉴相器（其 VCO 传递特性的不够线性），则可以利用 AD654 VFC 构建这里所示的 FVC。

问：什么是同步 VFC？

答：同步 VFC 是一种具有更高线性度和稳定性的电荷平衡 VFC，由外部时钟驱动的双稳态取代了原来的单稳态。精密电流给积分器放电的时间固定为外部时钟的一个时钟周期。

同步 VFC(SVFC)的另一大优势是，积分器通过比较器阈值时（不是关键速率）并不开始放电，而是在下一个时钟周期开始时放电。SVFC 输出与时钟同步，因而更容易与计数器、微处理器等接口。它在多通道系统中特别有用，可以消除多个异步频率源的干扰问题。

SVFC 有两个缺点。由于输出脉冲与一个时钟同步，因此脉冲间隔不等，并且抖动很大。这并不妨碍 SVFC 用于模数转换应用，但会使它不适合用作精密振荡器。此外，时钟容性耦合到比较器中，导致 SVFC 在 2/3 或 1/2 FS 时发生注入锁定效应，从而在其响应中引起一个大的(18 位分辨率、1MHz 时钟时为 4-6 位)死区。布局或器件设计不良会恶化这一效应。

尽管有这些缺点，但取代定时单稳态提高了性能，使得 SVFC 成为绝大多数高分辨率 VFC 应用的理想之选。

问：可以构建同步 FVC 吗？

答：是的，而且性能非常好。最好利用一个连接到 FVC 的 SVFC 和一个为传输路径两端所共用的时钟来实现。如果同步 FVC 的输入信号与时钟的相位不相关，可能会引起严重的时序问题，其解决办法只有一个，即利用额外逻辑（两个 D 型触发器）来建立正确的相位关系。 □

<sup>1</sup> 详细信息参见：Gardner, F. M., Phase-lock Techniques, 2nd ed., New York: Wiley, 1979；以及 ADI 公司的《模数转换手册》。