信号の A/D 変換を正しく行う 7 つのステップ(シグナル・コ ンディショニングのノイズ計 算)

高精度アプリケーションで最適なSNRを得るためには、優れたデザインの低ノイズ・アナログ・フロント・エンドが必要です。このためには、センサー信号を完全かつ正確に取り込むためのADC選択に適切な手法が必要です。ドライバ・オペアンプやリファレンス電圧のようなサポート部品は、回路全体の性能を最適化するように選択します。

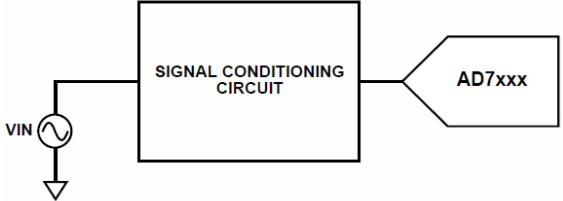

振動、温度、圧力、光などの実際の信号では、正確なシグナル・コンディショニングと信号変換が必要で、その後にさらにデジタル領域でのデータ処理が必要です。今日の高精度アプリケーションで多くの問題を解決して、最適なSNR を得るためには、優れたデザインの低ノイズ・アナログ・フロント・エンドが必要です。多くのシステムでは高価な部品を採用することはできず、低ノイズ部品の大きな消費電力も許容されません。この資料では、ノイズ最適化手法を採用したトータル・ソリューションのデザインについての質問に答えます。この資料では、ゲイン・ブロックとADC の組み合わせに対するデザイン方法を説明し、この手法をサポートする例を示します。 DC に近い低周波信号をコンディショニングする際に、この回路のノイズの計算と解析を行います。

次の 7 ステップに従って、アナログ・フロント・エンドのデザインを行います。

- センサーまたはゲイン・ブロックの前のセクションの電気的出力を定めます。

- ADC の条件を計算します。

- 信号変換用に最適なADC +リファレンス電圧を探します。

- 最大ゲインを求め、オペアンプの検索条件を定めます。

- 最適なアンプを探し、ゲイン・ブロックをデザインします。

- デザイン・ターゲットを満たしているか、トータル・ソリューション・ノイズをチェックします。

- シミュレーションを実行して検証します。

ステップ1: センサーまたはゲイン・ブロックの前のセクションの電気的出力の決定

信号はセンサーから直接到達するか、あるいはゲイン・ブロックの前のEMI フィルタとRFI フィルタを通過して到達することがあります。ゲイン・ブロックをデザインするためには、信号のAC 特性とDC 特性、および使用可能な電源を知る必要があります。信号の特性とノイズ・レベルが分かると、ADC を選択する際に必要な入力電圧範囲とノイズ・レベルの手がかり得られます。ここで、センサー出力は、フルスケール振幅250 mVp-p (88.2 mV rms)、25 µV p-p ノイズの10 kHz 信号とします。さらに、システムで5 V 電源を使用するものとします。この情報から、ADC 入力での信号対ノイズ比をステップ2 で計算することができます。データ処理を簡素化し、紛らわしさを除くため、このソリューションを室温動作用にデザインするものとします。

ステップ2: ADC条件の計算

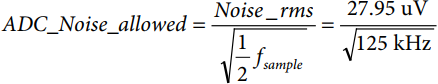

必要となるADC タイプ、サンプル・レート、ビット数、ノイズ仕様はどうか? ステップ1 で得た入力信号振幅とノイズの情報から、ゲイン・ブロック入力での信号対ノイズ比(SNR)を計算することができます。できるだけ優れた信号対ノイズ比を持つADC を選択する必要があります。SNR を知ると、ADC を選択する際の実効ビット数(ENOB)の計算に役立ちます。この関係を次式で示します。SNR とENOB は、必ずADC データシートに記載されています。この例では、SNR=86.8 dB とENOB=14.2 ビットが必要とされるため、16 ビットのA/D コンバータが必要となります。さらに、サンプリング・レートfs は最大入力周波数fin の2 倍以上である必要があるというナイキスト条件から、20 kSPS のADC が選択されます。

次に、416 nV/√Hz を超えないノイズ密度を持つ全体ソリューションをデザインする必要があります。これにより、シグナル・コンディショニング回路のノイズは入力ノイズの1/10 に設定されます。

![]()

![]()

図 1.代表的なシグナル・コンディショニング・チェーン

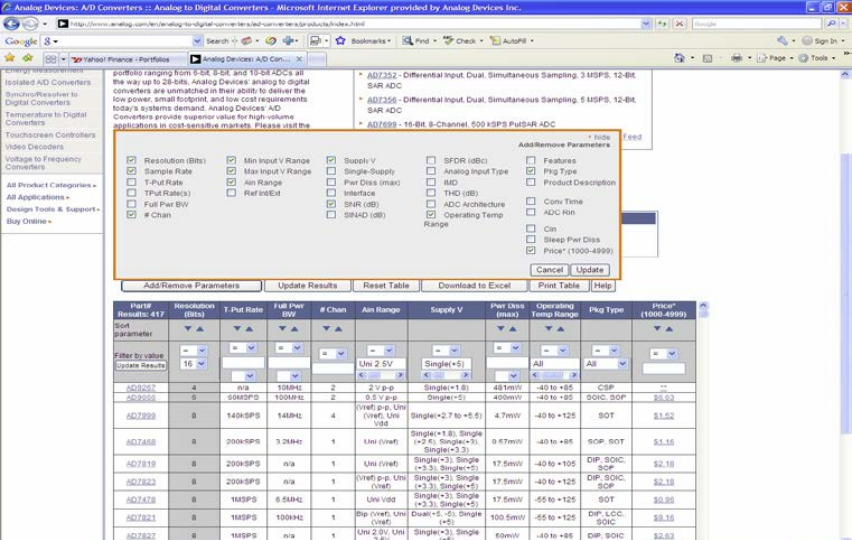

ステップ3: 信号変換用に最適なADC +リファレンス電圧の検索

検索条件のセットが得られると、多くの方法を使って条件を満たすADC を見つけることができます。16 ビットADC を探す最も容易な方法は、メーカーのサイトで検索ツールを使う方法です。分解能とサンプル・レートを入力すると、多数の選択肢が表示されます。

多くの16 ビットADC が、ENOB=14.5 ビットを満たしています。ノイズ性能をさらに良くしたい場合は、オーバーサンプリングを使ってENOB を16 ビットまで上げます(4n オーバーサンプリングを使うとn ビットの改善が得られます)。オーバーサンプリングを使うと、低い分解能のADC を使うことができます。例えば、12 ビットADC の256 オーバーサンプル(44 オーバーサンプリング)により、16 ビットのノイズ性能が得られます。ここの例では、これは5.126 MHz サンプル・レート(20 kSPS ×256)の12 ビットADC となることを意味します。あるいは、14ビットADC を42 オーバーサンプルする、すなわち1.28 MSPSにすることができます。ただし、これらのコストはAD7685(250 kSPS の16 ビットADC)と同じになります。

リストから、16 ビットPulSAR® ADC のAD7685 を選択します。このコンバータは、90 dB のSNR と250 kSPS のサンプル・レートを持っているため、条件を満たしています。高精度XFET®リファレンス電圧のADR421/ADR431 をこのADC に使用することが推奨されます。2.5 V の入力範囲は250-mV p-p の入力仕様を満たしています。

図 2.代表的なADC セレクション・テーブル

AD7685 のリファレンス入力は、ダイナミック入力インピーダンスを持っているため、小さい寄生インダクタンスと、ピンの近くに太い低インピーダンス・パターンで接続したセラミック・デカップリング・コンデンサによりデカップリングする必要があります。22 μF のセラミック・チップ・コンデンサにより最適性能を得ることができます。

ステップ4: 最大ゲインを求めてオペアンプの検索条件を決定

ADC の入力電圧範囲を知ると、ゲイン・ブロックのデザインに役立ちます。ダイナミックレンジを小さくするため、与えられた入力信号とADC 入力範囲に対して、ゲインをできるだけ大きくする必要があります。これは、ここの例でゲイン・ブロックのゲインを10 にできることを意味します。

![]()

![]()

![]()

![]()

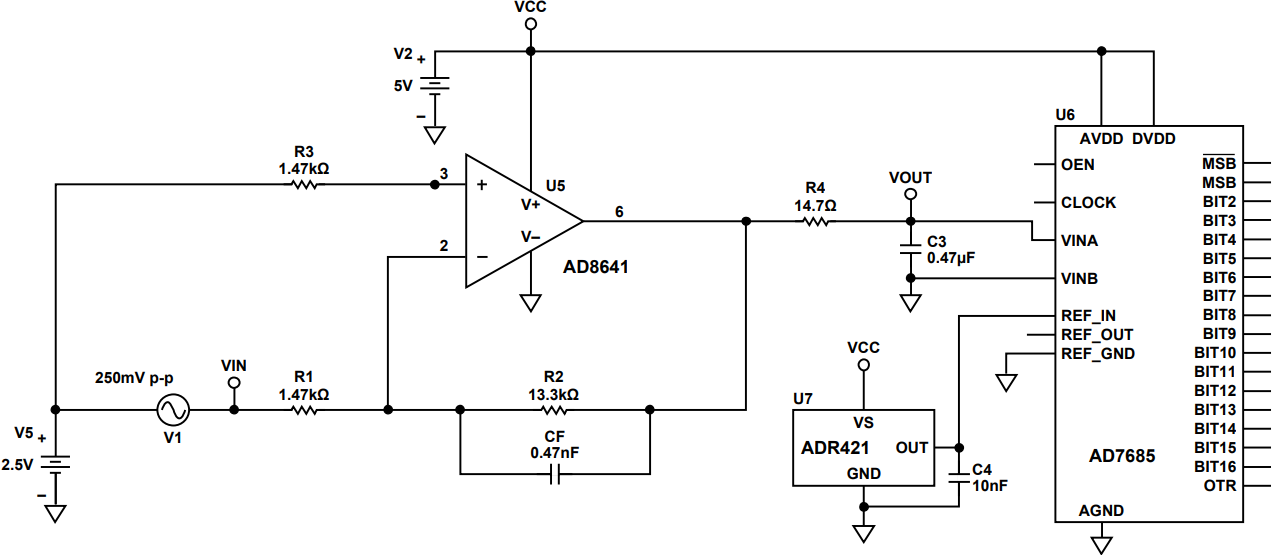

AD7685 の駆動は容易ですが、ドライバ・アンプは所定の条件を満たす必要があります。例えば、AD7685 のSNR 性能と遷移ノイズ性能を維持するためには、ドライバ・アンプが発生するノイズをできるだけ低く抑える必要がありますが、ゲイン・ブロックは信号とノイズを共に増幅してしまうことに注意する必要があります。ゲイン・ブロックの前後でノイズを同じレベルに維持するため、小さいノイズを持つアンプと部品を選択する必要があります。また、ドライバはAD7685 に釣り合うTHD 性能を持ち、ADC のコンデンサ・アレイに対するフルスケール・ステップに対して16 ビット・レベル(0.0015%)でセトリングできる必要があります。アンプからのノイズは、外付けフィルタでさらに除去することができます。

オペアンプ入力での許容ノイズはどうか? ここでは、416nV/√Hz を超えないノイズ密度を持つ全体ソリューションをデザインしなければならないことに注意する必要があります。低いノイズ・フロアを持つゲイン・ブロックをデザインする必要があります。例えば、ゲインを10 に上げるためノイズ・フロアを1/10 にする必要があります。こうすると、アンプのノイズはセンサーのノイズ・フロアより十分低くなります。ノイズ・マージンを計算するため、オペアンプ入力のノイズは、オペアンプの全ノイズとADC のノイズの和になると見なします。

![]()

![]()

ステップ5: 最適なアンプの検索と、ゲイン・ブロックのデザイン

入力信号帯域幅を求めた後のオペアンプ選択の最初の作業は、許容できるゲイン帯域幅積(GBWP)を持ち、かつ最小のDC 誤差とAC 誤差でこの信号を処理できるオペアンプを選ぶことです。最適なゲイン帯域幅積を求めるためには、信号帯域幅、ノイズ・ゲイン、ゲイン誤差が必要です。これらの用語はすべて以下に定義します。1 つのガイドとして、ゲイン誤差を0.1%以下に抑える場合、入力信号BW の100 倍のゲイン帯域幅を持つアンプを選択してください。さらに、高速なセトリング・タイムと優れた駆動能力を持つアンプを選択する必要があります。ここでのノイズ要求は、オペアンプ入力での全体ノイズが40.8nV/√Hz 以下であり、ADC のノイズは7.9 nV/√Hz であることに注意する必要があります。オペアンプの検索条件をまとめると、UGBW > 1 MHz、5 V 単電源、優れた電圧ノイズ仕様、電流ノイズ仕様、THD 仕様、ADC 仕様を低下させないための小さいDC 誤差となります。

![]()

![]()

同じ手法をADC の検索に使って、この例ではAD8641 を選択します。低消費電力高精度JFET 入力アンプのAD8641 は、極めて小さい入力バイアス電流とレールto レール出力を持ち、5 V~26 V の電源で動作することができます。このデバイスの関連仕様を下の表に示します。このオペアンプは非反転構成にすることができ、表に示す部品値を使用することができます。

| Component | Value |

| R1 | 1.47 kΩ |

| R2 | 13.3 kΩ |

| R3 | 1.47 kΩ |

| En | 28.5 nV/√Hz |

| In | 50 fA/√Hz |

| Cf | 0.47 nF |

図3.ソリューション全体

Aすべての能動部品と受動部品は固有のノイズを発生するため、性能を低下させない部品を選択することが重要です。例えば、低ノイズのオペアンプを購入して大きな抵抗でそれを取り囲むことは浪費になります。1 kΩ の抵抗は4 nV のノイズを発生することに注意してください。

前述のように、オプションのRC フィルタをADC とこのゲイン・ブロックの間に使うと、BW を狭くしてSNR を改善することに役立ちます。

ステップ6: デザイン・ターゲットを満たしているか、トータル・ソリューション・ノイズをチェック

デザインした回路のすべての誤差原因を理解することは極めて重要です。最適SNR を実現するためには、上記ソリューション全体のノイズの式をリストアップすることが必要です。これを次式に示します。

トータル・ノイズを帯域幅全域で積分すると、フィルタ帯域幅でのADC 入力のトータル・ノイズは3.05 µV であることが分かり、これはデザイン条件の4.16 µV より小さいことが分かります。

![]()

![]()

AD8641 のコーナー周波数は100 Hz より低いため、この場合低周波ノイズ(1/f)を無視します。

優れた信号対ノイズ比を維持するためには、信号パス内の各要素のノイズに対する注意と優れたPCB レイアウトが必要です。ADC の下のグラウンド・プレーンがシールドとして使われてない限り、ノイズがチップに混入するので、ADC の真下をデジタル・ラインが通らないようにしてください。CNV やクロックのような高速なスイッチング信号は、アナログ信号パスの近くを絶対に通らないようにしてください。デジタル信号とアナログ信号の交差は回避する必要があります。

ステップ7: シミュレーションの実行と検証

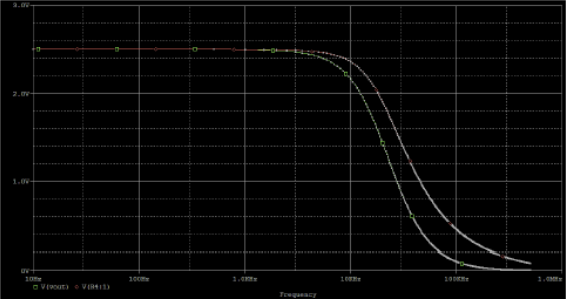

ADI のサイトからダウンロードできるPSpice マクロ・モデルの使用は、回路デザイン検証の優れた開始点になります。クイック・シミュレーションでは、このソリューションをデザインした信号帯域幅が示されます。図4 に、AD7685 入力にあるオプションのRC フィルタの前後の応答を示します。

図 4. 図3 の回路の帯域幅シミュレーション

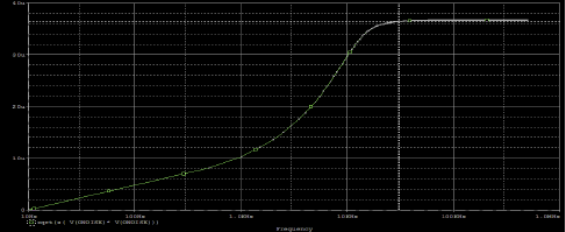

図 5 に示すように、10 kHz 帯域幅での総合出力ノイズは31 µVrms に近い値になります。これは、デザイン・ターゲットの41µV rms より小さい値です。ベンチ・プロトタイプを作成してソリューション全体を検証した後に、量産へ移行する必要があります。

図 5.図3 に示す回路のノイズ応答のシミュレーション

まとめ

今日の低消費電力でコストに厳しいデザインでは、多くのシステムで高価な部品を採用することはできず、低ノイズ部品の大きな消費電力も許容できません。シグナル・コンディショニング回路で最小のノイズ・フロアと最適な性能を実現するためには、部品レベルのノイズ発生源を理解する必要があります。優れた信号対ノイズ比を維持するためには、信号パス内の各要素のノイズに対する注意が必要です。上記ステップに従うと、小さいアナログ信号を正しくコンディショニングして、非常に高い分解能を持つADC を使って変換することができます。