An Accurate, Low-Impedance, Low-Dropout, Sub-1V Bandgap Reference Is Compact and Prolongs Battery Life

要約

A compact, accurate, sub-1V, low-impedance, low-dropout bandgap reference is presented in this paper. The circuit concept presented here is a sub-1V (0.9V in the design example) bandgap reference that can be set from a bit above VBE, depending on the operating temperature range, and up to the normal bandgap voltage. The circuit idea is realized in 90nm BiCMOS technology. Simulation results show that over a 200°C temperature range, the proposed circuit can achieve 15ppm over line and load regulation. The core can be realized in a CMOS process using parasitic pnp devices.

A similar version of this article appeared March 10, 2014 in ELETimes.

Introduction

A voltage reference is a critical building block in most analog circuits. In battery-operated, portable applications the minimum system voltage is continuously being lowered to prolong battery life. The theoretical minimum supply needed for analog circuitry is a threshold plus the saturation voltage of a current source, usually VDSSAT. For BiCMOS processes, or CMOS processes with parasitic pnp transistors, the minimum operating voltage will be VBE + VDSSAT, assuming that the CMOS VT threshold is lower than VBE.

In this article a new bandgap reference core is presented that can be set anywhere between slightly above VBE to VBG. The lowest output voltage (V0) depends on the lowest temperature that needs to be covered. The design examples below will show that these configurations approach the theoretical minimum operating voltage by 50mV to 100mV from -50°C to +150°C.

Sub-1V voltage references have been realized in different ways before. Engineers have documented1–5 various architectures in current mode, where CTAT and PTAT currents are generated and added together to a resistor to generate a reference voltage. However, it was shown6 that those configurations have high noise due to the current mirrors. Because of the mirror mismatches, it is difficult to get the same accuracy using current mirrors compared to the normal bandgap configuration. Without trimming, a well-designed bandgap circuit can normally achieve 3% to 5% 6δ accuracy from -40°C to +125°C. Even with a reasonably high overdrive, it is difficult for the current mirrors to achieve this level of accuracy. If overdrive is increased for better matching, it also increases the necessary headroom as VDSSAT is increased.

There is another way6, 7 to generate a sub-1V reference. The reference voltage is expressed in Equation 1:

VREF = kVBE + ΔVBE = kVBE + VTln(N)

where N is the ratio of the area of the two emitters.

As shown in Equation 1, the voltage is set in the 100mV to 200mV range. A presentation in 20067 gave the design example as N = 10, VREF = 130mV.

A reference voltage close to ground is not desirable because the noise and the offset in the next stage will be proportionally larger than the reference voltage. Consequently, the overall accuracy deteriorates. This article presents a novel approach that resolves the aforementioned issues and provides superior performance. For example, a 0.9V reference can be generated with a 1.0V supply or lower, depending on the load.

The New Proposed Core for a Sub-1V Reference

A BiCMOS Process with npns

Figure 1 shows the proposed core.

Figure 1. New bandgap core.

Mathematically, it can be shown that V0 becomes a scaled version of the bandgap voltage, VBG:

I2 × R2 = ΔVBE = VTln(N)

V0 = (1 - R1/R3) × VBG

where:

VBG = (VBG1 + VT × lnN × R3/R2 × ((R1 + R2)/(R3 - R1))

The supply headroom requirement is V0 + VDSSAT, and the output is low impedance.

A CMOS Process with Parasitic pnps

A possible pnp version is shown in Figure 2.

Figure 2. A pnp version for a CMOS process.

Design Example with Simulation Results

A simplified version of Figure 1 is shown in Figure 3; it saves an op amp (X2). The I3 current can be generated by adding two resistors along with Q3. In this case, I4 can be set to I0 at room temperature by choosing an appropriate R4, approximately equal to R1/2. At other temperatures, I4 will not be equal to I0, and this will introduce an error term. But since VBE is a very weak function of I0, therefore, the error is negligible. See Figure 4.

Figure 3. Simplified version of the proposed npn core.

As a design example for this core, V0 = 0.9V is chosen.

For low-power applications, the quiescent current (IQ) is targeted in the µA range. Based on the configuration in Figure 3, we have three variables, R1, R2, and R3, and two equations, (Equation 3 and Equation 4), defined by V0 and VBG. Therefore, I2 is chosen to get one more equation to derive all three resistor values.

From Equation 3:

R2 = (VT × lnN)/I2

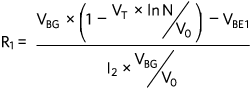

From Equations 4 and 5:

There is no individual knob to control the output voltage and its TC separately. Here is the procedure to fine-tune the circuit to the zero TC point and to obtain the desired output voltage.

- Find the exact VBE1 voltage in simulation.

- Find VBG by adjusting R2 until V0 is zero TC. Now follow this procedure: increase R2 if V0 has a positive TC; decrease R2 if V0 has a negative TC. Note the value of zero TC V0, then:

VBG = V0/(1 - R1/R3) - Recalculate R1, R2, and R3 using the new VBG and VBE values.

VBG = 1.203V

VBE1 = 0.58V

I2 = 1.0µA

N = 8

R4 = ½R1 = 206kΩ.

The final calculated design parameters are shown in Table 1:

| °C | -55 | 25 | 150 |

| VBE1 | 0.74 | 0.58 | 0.33 |

| VBG | 1.203 | 1.203 | 1.203 |

| VT | 0.019 | 0.026 | 0.036906 |

| I2 | 7.32E-07 | 1.00E-06 | 1.42E-06 |

| I3 | 4.52E-07 | 3.55E-07 | 2.02E-07 |

| I0 | 2.79E-07 | 6.45E-07 | 1.22E-06 |

| I1 | 2.79E-07 | 6.45E-07 | 1.22E-06 |

| R1 | 4.120E+05 | 4.120E+05 | 4.120E+05 |

| R2 | 5.407E+04 | 5.407E+04 | 5.407E+04 |

| R3 R4 |

1.636E+06 2.060E+05 |

1.636E+06 2.060E+05 |

1.636E+06 2.060E+05 |

Realizing Figure 3 in a 90nm BiCMOS process with transistor circuitry, the simulation results are plotted in Figure 4. The typical case is: supply voltage = 1.5V; output load = 10µA; all process corners (bipolar, CMOS, resistor, capacitor) having line and load combinations with supply voltage = (V0 + 0.1V) and 1.65V; output load = 0µA and 20µA. The circuit has temperature compensation and 0.1% LSB trim. The results show that V0 stays within 2.6mV, less than ±0.15% from -50°C to +150°C, or 15ppm over line and load. With processes variation and 0.1% LSB trimming, this bandgap voltage reference can achieve ±0.45% accuracy over 200°C temperature range.

Figure 4. Simulation results of npn core.

Performance Comparison

Table 2 compares the performance of proposed cores with existing designs:

| Proposed Core | Reference 5 | Reference 3 | Reference 6 | |

| Tech/m | 90n BiCMOS |

500n CMOS |

600n CMOS |

500n BiCMOS |

| VDD/V | 1-1.65* | 0.93-5 | 0.98-1.5 | 1 up |

| VREF/mV | 900 | 228 | 603 | 190.9 |

| TC/ppm | 15 | 34 | 34.7 | 11 |

| IQ/µA | 6 | 28 | 18 | 20 |

| PSRR/dB @100Hz @10kHz @1MHz |

-84 -62.2 -28.6 |

-58 – -12 |

– -44 – |

– |

| Noise/(nV/√Hz) @100Hz | 1573 | 200 | – | 40 |

| Area/mm2 | 0.023** | 0.0464 | 0.24 | 0.4 |

| *It uses 1.65V devices, so the maximum voltage is 1.65V. If a 4.5V device is used, it can go up to 4.5V. **Die size is based on placement of all components in corresponding wells with DRC cleaned. |

||||

Conclusion

This article shows an elegant way of creating a compact, sub-1V bandgap reference in a low-dropout and low-impedance configuration. This proposed solution has a superior accuracy of about 20ppm with load, line regulation, and temperature variation. The headroom requirement approaches the theoretical minimum. The die size is comparable with a traditional bandgap reference with three more components (2 resistors and 1 npn). This design is small and can enhance the circuitry working with a lower battery voltage that is beneficial, even critical to portable designs.

この記事に関して

製品

製造中

低コスト、超低消費電力、低ドロップアウト、大出力電流、SOT23電圧リファレンス

製造中

低コスト、超低消費電力、低ドロップアウト、大出力電流、SOT23電圧リファレンス

製造中

低コスト、超低消費電力、低ドロップアウト、大出力電流、SOT23電圧リファレンス

低コスト、超低消費電力、低ドロップアウト、大出力電流、SOT23電圧リファレンス

低コスト、超低消費電力、低ドロップアウト、大出力電流、SOT23電圧リファレンス

低コスト、超低消費電力、低ドロップアウト、大出力電流、SOT23電圧リファレンス

高精度、超低消費電力、低ドロップアウト、SC70シリーズ電圧リファレンス

低コスト、超低消費電力、低ドロップアウト、大出力電流、SOT23電圧リファレンス

高精度、低電力、低ドロップアウト、UCSP電圧リファレンス

低コスト、超低消費電力、低ドロップアウト、大出力電流、SOT23電圧リファレンス

高電源電圧、高精度電圧リファレンス、SOT23