PLL: フェーズ・ロック・ループ

PLLとは

意味

フェーズ・ロック・ループ(PLL)は、その位相が入力に関連するような出力信号を生成するシステムです。これら2つの信号は周波数が同じで、位相差は存在しないか、または一定の位相差になります。

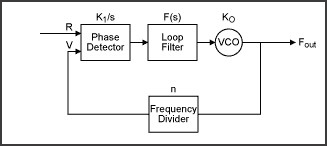

PLLは通常、位相検出器、ループ・フィルタ、および電圧制御発振器(VCO)で構成されます。位相検出器は、基準信号と発振器周波数を比較し、誤差信号を出力します。次に、ループ・フィルタ(通常はローパス・フィルタ)がこの誤差信号から誤差電圧を生成します。さらに、VCOは発振器周波数を増減させ、入力周波数にロックします。これにより、入力周波数に等しい出力周波数と、2つの信号間で一定の位相シフト(ゼロの場合もある)が生み出されます。PLLは、基準周波数に等しい出力ではなく、基準周波数の倍数である出力を生み出すために、フィードバック・ループ内に分周器を備えている場合もあります。

位相検出器、ループ・フィルタ、VCO、およびオプションの分周器を備えた、基本的なフェーズ・ロック・ループのブロック図。

PLLの動作における3つの段階とは

フェーズ・ロック・ループの3つの段階とは、フリー・ランニング、キャプチャ、および位相ロック(またはトラッキング)です。

- フリー・ランニング:PLLの中心周波数で、これは入力周波数にロックされていない時にVCOが動作する周波数です。

- キャプチャ:VCOがまず入力周波数にロックするには、周波数がPLLのキャプチャ範囲内にある必要があります。

- 位相ロック(またはトラッキング):入力周波数にロックすると、VCOはPLLのロック範囲内にある限り、入力周波数に追従して調整を継続します。このロック範囲はキャプチャ範囲よりも広範です。

同義語

Phase-Locked Loop用語を検索(アルファベット順):