AN-1453: PMBus を介したADM1266 のファームウェアと設定のプログラミング

はじめに

このアプリケーション・ノートでは、大規模なプログラミング環境またはシステム・アプリケーションでADM1266 のファームウェアと設定をプログラムするために必要なステップを詳しく説明します。ファームウェアと設定のアップデートは、条件に基づいて個別に行うことができます。

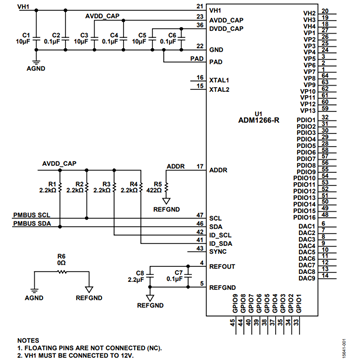

ハードウェア構成

図1は、ADM1266について大規模なプログラミング環境に限定した場合に推奨されるピン設定を示しています。ハードウェア構成に使用するすべての部品は、表面実装部品にすることを推奨します。

ADM1266のPMBusアドレスは、ADDRピンとGNDの間に外付け抵抗(R5)を接続して設定します。表1に、推奨する抵抗値とそれに対応するPMBusアドレスを示します。

| PMBus Address | 1% Resistor (kΩ), E96 Series |

| 0x40 | 0.422 |

| 0x41 | 1.5 |

| 0x42 | 2.67 |

| 0x43 | 4.12 |

| 0x44 | 5.36 |

| 0x45 | 7.15 |

| 0x46 | 8.87 |

| 0x47 | 10.7 |

| 0x48 | 12.7 |

| 0x49 | 14.7 |

| 0x4A | 16.9 |

| 0x4B | 19.1 |

| 0x4C | 21.5 |

| 0x4D | 24.3 |

| 0x4E | 27.4 |

| 0x4F | 31.6 |

メモリ・パーティション

図2 に、このアプリケーション・ノートに適用可能なメモリ・パーティションの概要を示します。

ADM1266 には、ミニ・ブートローダやブートローダだけが予めプログラムされています。ミニ・ブートローダやブートローダは、ユーザがアップグレードすることはできません。

ADM1266 にブートローダだけが予めプログラムされている場合、最初にファームウェアをプログラムし、続いて設定データをプログラムする必要があります。

ADM1266 用のファームウェアと設定は、ADI Power Studio®グラフィカル・ユーザ・インターフェース(GUI)ソフトウェアによって生成されます。このソフトウェアは、EVAL-ADM1266 評価用ボードの製品ページからダウンロードできます。

すべてのデバイスで同じファームウェアが使用され、またデバイスごとに異なる設定が使用されます。

.HEX ファイルの読出し

ファームウェアと設定用に生成される.hex ファイルは、Intel®16進数フォーマットに従います。

.hex ファイルの各行には、16 進数が含まれています。この16 進数は、データを表す複数の2 進数と、データを書き込む必要のあるレジスタ・アドレスがエンコードされたものです。

.hex ファイルの最後は:00000001FF で表されます。PMBus の書込みタイプはバイト・カウントに基づいており、例えば、1 バイトはバイト書込み、2 バイトはワード書込み、3 バイト以上はブロック書込みになります。

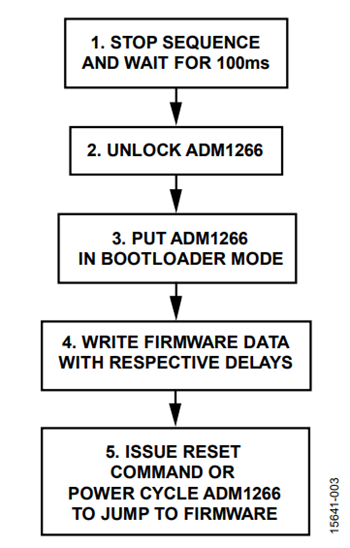

ファームウェアのプログラミング

ADM1266 は、ファームウェアがない場合にはブートローダ・モードで起動し、ブートローダ・モードを維持します。図4 に示すように、ファームウェアをロードするにはステップ4 とステップ5 だけが必要です。

ステップ1:シーケンスを停止してからファームウェアをアップグレード

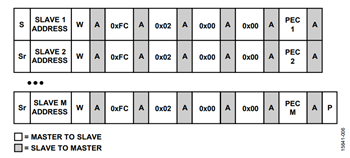

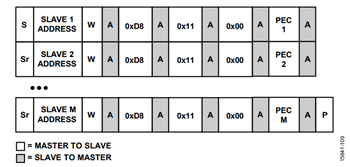

PMBus を介してファームウェアをアップデートする前に、現在のシーケンスを停止する必要があります。シーケンスの停止は、GO_COMMAND コマンド(レジスタ0xD8)に0x0003 を書き込むことによって行います。図5 に示すように、グループ・コマンドを発して、同じPMBus にある複数のADM1266 デバイスを同時に停止することができます。

グループ・コマンドを送信できない場合は、ADM1266 デバイスごとに停止することができます。

停止コマンドを送信後、100ms 待機してから次のPMBus コマンドを送信する必要があります。

ステップ2:ADM1266 のロック解除

ADM1266 は、ファームウェアがアップデート可能になる前にロックを解除する必要があります。

ADM1266 のロック解除は、FW_PASSWORD コマンド(レジスタ0xFD)に正しいパスワードを2 回連続して書き込むことによって実行できます。ADM1266 のロックを解除するブロック書込みコマンドを図6 に示します。デフォルトのパスワードは最初の16 バイトが0xFF で、17 番目のバイト(パスワード・コマンド)が0x02 に設定されています。

ロック解除のステータスは、STATUS_MFR_SPECIFIC コマンド(レジスタ0x80)のPART_LOCKED ビット(ビット2)によって確認できます。このビットは、ADM1266 がロック解除された場合、0 に設定されています。詳細については表5 を参照してください。

ステップ3:ADM1266 をブートローダ・モードにする

ADM1266 は、ファームウェアがプログラム可能になる前にブートローダ・モードにする必要があります。図7 に示すように、ADM1266 はグループ・コマンドとして、UPDATE_FW コマンド(レジスタ0xFC)に0x02、0x00、および0x00 を書き込むことによって、ブートローダ・モードにできます。

このコマンドを送信できない場合は、ADM1266 デバイスごとにブートローダ・モードにできます。

ステップ4:ファームウェア・データの書込みの時間間隔

ファームウェアがPMBusを介してADM1266にプログラムされるときは、EEPROMを消去する必要はありません。ブートローダがファームウェア・データの最初のストリームを受信しているときに、ブートローダはファームウェア用に予約されているEEPROMのページを自動的に消去します。表2に、それぞれのデータ書込みの時間間隔を示します。

| Command | Wait Time Required Before Writing Next Block of Data |

| First Write to 0xFC (UPDATE_FW) | 2 sec |

| Subsequent Writes to 0xFC | 40 ms |

ステップ5:ファームウェアのプログラミング後におけるリセット・コマンドの送信または電源の入れ直し

ファームウェア・データがADM1266に正常に書き込まれた後、設定データをプログラミングする前にリセット・コマンドの送信または電源の入れ直しを行う必要があります。

ADM1266のリセットはGO_COMMANDコマンド(レジスタ0xD8)に0x0004を書き込むことによって行うことができます。

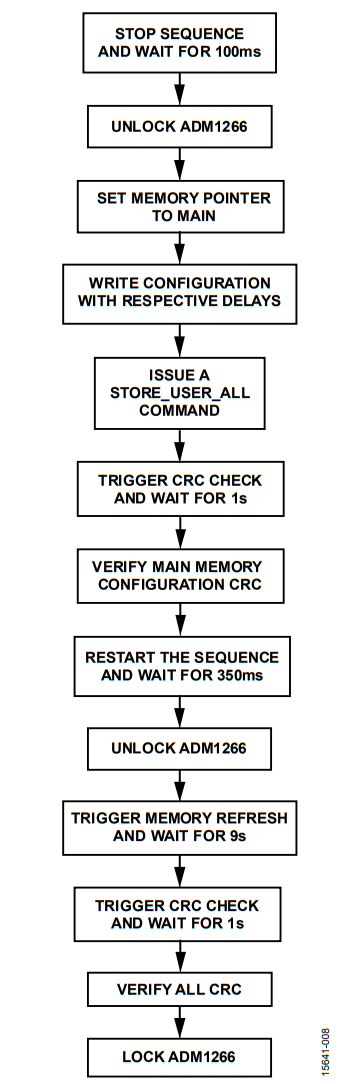

設定のプログラミング

設定をプログラミングするためのフローチャートについては、図8 を参照してください。

ステップ2:ADM1266 のロック解除のセクションと、.Hex ファイルの読出しのセクションに詳述されている手順に従ってください。

シーケンスを停止してから設定データをプログラミング

設定をPMBus を介してプログラムする前に、現在のシーケンスを停止する必要があります。シーケンスを停止するには、シームレス・アップデート・リセット・ストップとソフト・リセット・ストップという2 つのオプションがあります。設定をアップデートするときは、シームレス・アップデート・リセット・ストップを使用することを推奨します。このオプションを使用すると、シーケンスが再開したとき、シーケンスが新しい設定のパワーグッド状態に直接ジャンプします。

図9 に示すように、シームレス・アップデート・リセット・ストップでは、同じPMBus 上の複数のADM1266 デバイスを同時に停止するグループ・コマンドとして、GO_COMMAND コマンド(レジスタ0xD8)に0x0011 を書き込むことによってシーケンスが停止します。

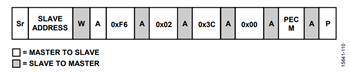

シームレス・アップデート・リセット・ストップには、10 分間のデフォルト・タイムアウトがあります。ユーザがシーケンスを再開しない場合、シーケンスはタイムアウトが満了した後に自動的に再開します。タイムアウト値は、シーケンスを停止する前に、HITLESS_TIMEOUT コマンド(レジスタ0xF6)を使用することによってアップデートできます。

図10 に、リセット時間を60 秒に設定する例を示します。

大規模なプログラミング環境や、設定が予めプログラムされていないときは、ソフト・リセット・ストップの使用のみを推奨します。

図9 に示すように、ソフト・リセット・ストップでは、同じPMBus 上の複数のADM1266 デバイスを同時に停止するグループ・コマンドとして、GO_COMMAND コマンド(レジスタ0xD8)に0x0003 を書き込むことによってシーケンスが停止します。

グループ・コマンドを送信できない場合は、ADM1266 デバイスごとに停止することができます。

停止コマンドを送信後、100ms 待機してから次のPMBus コマンドを送信する必要があります。

メモリ・ポインタをメイン・メモリに設定

ADM1266 用の設定データは、メイン・メモリにプログラムする必要があります。メイン・メモリ内の設定データが有効な場合、ADM1266 はメイン・メモリからの設定データを常に実行します。メイン・メモリ内の設定データが破損し、バックアップ・メモリ内の設定データが有効な場合、ADM1266 はバックアップ・メモリからの設定データを実行します。

図11 に示すように、メモリ・ポインタは、SWITCH_MEMORYコマンド(レジスタ0xFA)を使用することによってメイン・メモリに設定できます。

データ書込みの時間間隔

PMBus を介して設定データをADM1266 にプログラムするときは、EEPROMを消去する必要はありません。

ファームウェアは、ADM1266 に送信されたデータに基づいてEEPROM のページを自動的に消去します。EEPROMの1 ページを消去するのに必要な時間は、50ms(代表値)です。

EEPROM の自動消去に時間を要するため、一定の時間待機してから次のデータ・ストリームを送信する必要があります。

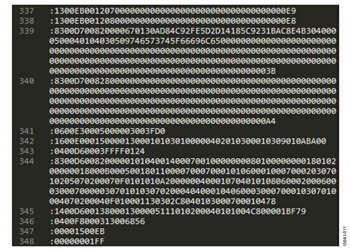

表3 に、特定のコマンドを書き込んだ後に確保する必要のある代表的な時間間隔と、図12 に示す.hex ファイルのサンプル内の該当する行番号を示します。

| Command | Wait Time Required Before Writing Next Block of Data | Line Number in .hex File (See Figure 12) |

| 0xD7 (SYSTEM_CONFIGURATION) | 400 ms (after first write) | 339 |

| 0xE3 (USER_DATA) | 100 ms (after first write) | 341 |

| 0xE0 (LOGIC_CONFIGURATION) | 200 ms (after first write) | 342 |

| 0xD6 (SEQUENCE_CONFIGURATION) | 2.5 sec (after first write) | 343 |

| 0xF8 (MEMORY_CONFIG) | 100 ms | 346 |

| Subsequent Writes to 0xD7, 0xE3, 0xE0, 0xD6 | 40 ms | 340, 344, 345 |

| 0x15 (STORE_USER_ALL) | 300 ms | 347 |

設定の書込みが終了した後、STORE_USER_ALL コマンド(レジスタ0x15)に送信コマンドを発して、システム設定の設定値をEEPROMに書き込みます。

アップデートされたメイン・メモリ設定データの確認

設定をアップデートしたときにのみ確認が必要です。ADM1266に設定が予めプログラムされていない場合は、アップデートされたメイン・メモリ設定データの確認は任意です。

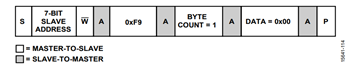

図14 に示すように、設定データを書き込んだ後、すべてのメモリ・セクションの巡回冗長検査( CRC ) の計算は、MEMORY_RECALCULATE_CRC コマンド(レジスタ0xF9)に書込みを行うことによってトリガできます。

1 秒間待機してからメモリCRC のステータスを読み出します。このステータスはSTATUS_MFR_SPECIFIC_2 コマンド(レジスタ0xED)のワード読出しによって確認できます。このレジスタのビット・マッピングを表4 に列挙します。MAIN_PROJECT_CRC_FAULT ビットとMAIN_ABCONFIG_CRC_FAULT ビットが0 に設定されていることを確認します。これらのビットが0 に設定されていれば、メイン・メモリ設定は正常に書き込まれたことになります。

| Bit | Bit Name |

| 15 | BKUP_PASSWORD_CRC_FAULT |

| 14 | BKUP_FIRMWARE_CRC_FAULT |

| 13 | BKUP_PROJECT_CRC_FAULT |

| 12 | BKUP_ABCONFIG_CRC_FAULT |

| 11 | MAIN_PASSWORD_CRC_FAULT |

| 10 | MAIN_FIRMWARE_CRC_FAULT |

| 9 | MAIN_PROJECT_CRC_FAULT |

| 8 | MAIN_ABCONFIG_CRC_FAULT |

| 7 | BKUP_IAP_CRC_FAULT |

| 6 | BKUP_MINI_IAP_CRC_FAULT |

| 5 | MAIN_IAP_CRC_FAULT |

| 4 | MAIN_MINI_IAP_CRC_FAULT |

アップデート後のシーケンスの再開

新しい設定データがADM1266 に書き込まれた場合、複数のADM1266 デバイスのシーケンスを同時に再開するグループ・コマンドとして、GO_COMMAND コマンド(レジスタ0xD8)に0x0000 を書き込むことによって、新しいシーケンスを実行できます。グループ・コマンドのプロトコルを図5 に示します。

グループ・コマンドを送信できない場合は、ADM1266 デバイスごとに再開することができます。

シームレス・アップデート・リセット・ストップを使用してシーケンスが停止した場合、再開時にはシーケンスは設定で定義されたパワーグッド状態に直接ジャンプします。パワーグッド状態が定義されていない場合は、シーケンスは最初のユーザ状態から開始します。

ソフト・リセット・ストップを使用してシーケンスが停止した場合は、再開時にボードの電源を入れ直すことで、シーケンスは最初のユーザ状態から開始します。

シーケンスが再開後、350ms 待機してから次のPMBus コマンドを送信します。

メモリ・リフレッシュのトリガ

ADM1266 には、ミニ・ブートローダ、ブートローダ、ファームウェア、および設定用にバックアップ・メモリ・セクションがあります。ファームウェアと設定が正常にプログラムされた後、メモリ・リフレッシュをトリガしてください。メモリ・リフレッシュにより、メイン・メモリの内容がバックアップ・メモリにコピーされ、バックアップ・メモリの内容がメイン・メモリにコピーされます。

必ず、ADM1266 をロック解除してからメモリ・リフレッシュをトリガするようしてください。ステップ2:ADM1266 のロック解除のセクションを参照してください。

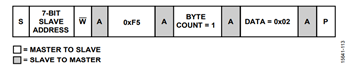

図13に示すように、REFRESH_FLASHコマンド(レジスタ0xF5)にブロック書込みを行うことによって、すべてのメモリ・セクションに対するメモリ・リフレッシュをトリガできます。

メモリ・リフレッシュは、終了まで約9 秒かかります。STATUS_MFR_SPECIFIC コマンド(レジスタ0x80)のRUNNING_REFRESH ビットを読み出すことにより、メモリ・リフレッシュのステータスを確認してください。RUNNING_REFRESH ビットが1 に設定されている場合は、メモリ・リフレッシュが依然として動作しています。このビットが0 に設定されるまで待ってから次に進みます。

ファームウェアと設定データの確認

ファームウェアと設定データを書き込み、メモリ・リフレッシュをトリガした後、図14 に示すように、すべてのメモリ・セクションのCRC 計算が、MEMORY_RECALCULATE_CRC コマンド(レジスタ0xF9)に書込みを行うことによってトリガできます。

1 秒間待ってからメモリCRC のステータスを読み出します。メモリCRC のステータスを確認するには、STATUS_MFR_SPECIFIC_2コマンド(レジスタ0xED)のワード読出しを行います。このレジスタのビット・マッピングを表4 に列挙します。

ALL_CRC_FAULTは単一のビットで、表4に示しているすべてのCRCビットのORです。このビットは、STATUS_MFR_SPECIFICコマンド(レジスタ0x80)から読み出すことができます。

STATUS_MFR_SPECIFICコマンド(レジスタ0x80)をリードバックすることによって、設定互換性(ビット1)とシリコン互換性(ビット0)のステータスを確認します。

| Bit | Bit Name |

| 5 | ALL_CRC_FAULT |

| 4 | TESTMODE_ENABLED |

| 3 | RUNNING_REFRESH |

| 2 | PART_LOCKED |

| 1 | PART_DATA_COMPATIBLE_FAULT |

| 0 | SILICON_COMPATIBLE_FAULT |

CRCと互換性が合格の場合、それらが合格したビットには0が設定されます。CRCと互換性が不合格の場合、それらが不合格したビットには1が設定されます。

ファームウェアのバージョン番号は、IC_DEVICE_REVコマンド(レジスタ0xAE)からリードバックできます。ブロック読出しを使用して、ファームウェアが正しいリビジョンにアップデートされていることを確認します。コマンドのバイト・マッピングを表6に示します。

| Byte Name | Byte | Example | Notes |

| Data Length | Byte 0 | 0x08 | Fixed to 0x08 |

| Firmware Revision | Byte 1 | 0x01 | Indicates Version 1.8.7 |

| Byte 2 | 0x08 | ||

| Byte 3 | 0x07 | ||

| Bootloader Revision | Byte 4 | 0x00 | Indicates Version 0.0.7 |

| Byte 5 | 0x00 | ||

| Byte 6 | 0x07 | ||

| Chip Revision | Byte 7 | 0x42 | Indicates Version B0 |

| Byte 8 | 0x30 |

ADM1266のロック

ADM1266は、電源を入れ直すと自動的にロックされます。また、ADM1266は、任意の16バイトのデータと、0x03に設定された17番目のバイト(パスワード・コマンド)をFW_PASSWORDコマンド(レジスタ0xFD)に1回書き込むことによってロックできます。ADM1266をロックするブロック書込みコマンドを図15に示します。

ロックのステータスは、STATUS_MFR_SPECIFICコマンド(レジスタ0x80)のPART_LOCKEDビット(ビット2)によって確認できます。このビットは、デバイスが正常にロックされた場合、1に設定されています。

パケット・エラー・チェッキング(PEC) コントロール(オプション)

I2C通信においてアクノレッジ・ビットとノー・アクノレッジ・ビットを認識できる場合、正常なデータ転送を確保するため、すべての書込みでPECバイトを使用することを推奨します。

PMBusコントローラは、PECを実行して信頼性と通信の堅牢性を向上させます。PECは、転送メッセージの最後にPECバイトを付加することにより実行されます。PECバイトは、開始ビットから停止ビットまでの間にあるすべてのアドレス、コマンド、およびデータ・バイトにCRC-8アルゴリズムを使用して計算されます。

この処理では、アクノレッジ、ノー・アクノレッジ、開始、再開、および停止の各ビットは除外されます。PECバイトは、最後のデータ・バイトを供給したデバイスによってメッセージの最後に付加されます。PECバイトを受信したデバイスは、内部パケット・エラー・コードを計算して、このコードと受信したPECバイトを比較します。

PMBusのスレーブ・デバイスは、PECをサポートしているマスタのPMBusデバイスと同様に、PECをサポートしていないマスタ・デバイスとも通信できます。PECバイトが利用可能な場合、PMBusはPECバイトをチェックして、PECバイトが正しい場合にはアクノレッジを返します。PECバイトの比較に失敗した場合は、PMBusデバイスはこのPECバイトにアクノレッジを返さず、また、マスタから送信されたコマンドも処理しません。

PMBusは内蔵ハードウェアを使用して、CRC-8多項式、C(x) = x8 + x2 + x1 + 1によりPECコードを計算します。PECコードは、受信した順に1回に1バイトずつ計算されます。読出しトランザクションでは、PMBusは最後のデータ・バイトの次にPECバイトを付加します。書込みトランザクションでは、PMBusは受信したPECバイトを内部で計算したPECコードと比較します。