AN-1444: 高精度DAC の連続更新で考慮すべき2 次効果

はじめに

1 秒あたりのサンプル数は、高精度のA/D コンバータ(ADC)では明確に定義され、特性評価されていますが、高精度のDACでは多くの要因に依存するためデータシートで定義されていません。

DAC のデジタル・インターフェースはほとんどの場合、最大50 MHz のクロック・レートが可能で、24 ビットの入力シフト・レジスタを想定すると、潜在的に毎秒200 万回の書き込みが可能です。ただし、この数字はDAC が新しいコードを受け取るデジタル・インターフェースの能力のみを表しているにすぎず、デジタル・プロセスの遅延、レイテンシ、アナログ・ブロックのタイミングは考慮されていません。

このレイテンシは、DAC が校正手順を内蔵していない場合、一般に数ns 程度で無視できます。DAC が校正ルーチンを内蔵していると、レイテンシは1 μs ~ 3 μs になる可能性があります。

アナログ・ブロックでは、新しいコードの更新に関連して次の2 つのケースが考えられます。

- 更新速度が、DAC に接続されたアクティブ段(通常は内部または外部のバッファ)の帯域幅で制限される。

- 更新速度はアクティブ段によっては制限されないが、DACのコアによって制限される。

第 1 のケースでは、セトリング時間の仕様により、アナログ・ブロックの能力を正しく評価できます。セトリング時間は、前のコードとの関連で新しいコードに対して(通常は¼ から ¾ スケール)、最終コードの周りほぼ1 ビットの最下位ビット(LSB)である規定許容誤差内で定義されます。

大きなステップ・コードの遷移の場合、スルーレートがセトリング時間の主な要因となります。さらに、コンデンサやインダクタと同様、オーバーシュートやリンギングを生じる出力負荷の虚数成分によってセトリング時間が増加することがあります。

外部に接続されるインピーダンスの虚数成分の値によって、オーバーシュートの大きさが決まり、セトリング時間に影響します(図1 参照)。

最終的なセトリング時間には、レイテンシ、スルーレート、および立上がり時間が寄与します(図2 参照)。

必要なコード・ステップが小さく、接続される容量が小さいほど、最終的なセトリング時間が短くなります。

新しいコードが前のコードに近い場合、セトリング時間やバッファ能力は制限要因とはなりません。これは微調整の更新と考えることができます。

この場合、規定の許容範囲内(つまり最終コードの周り1 LSB内)に出力が安定するまでの時間を制限する要因は、DAC コアのレイテンシとダイナミック効果です。

ダイナミック効果は、DAC が動作するとき、(外部ピンからデータをシフトして取り込んだり、コマンドを処理したりする)デジタル・ブロックと、(出力を新しいコードに更新する)アナログ・ブロックの内部で発生したエネルギーの一部が外部に伝送されるため発生します。特に、デジタル・フィードスルーとデジタル/アナログ・グリッチ・エネルギーが2 つの主な仕様です。

出力が粗調整される場合、このエネルギーの一部はバッファのスルーレートによって隠されます。これが、出力負荷にエネルギーが注入される主な原因です。一方、微調整の更新の場合、両方の仕様は観測および測定が可能です。

DAC コアのダイナミック効果

DAC のどんな動作でも内部で電流または電圧のピークが発生するので、電源ピン、通常はVDD またはGND を通してそれらを散逸させなければなりません。内部寄生成分のためにDAC が動作したときに内部で発生するエネルギーは、これらの経路を通して完全に散逸させることはできず、このエネルギーの一部は出力負荷に伝送され、出力安定性に影響します。

デジタル・フィードスルーとは、遷移の交替時に外部のデジタル・ピンでの遷移が内部DAC に外乱を発生させる現象です。

さらに、このデジタル・フィードスルーは、プリント回路基板(PCB)の誤ったレイアウトによって外部で増幅されることがあります。

PCB レイアウトの最も良い方法は、PCB のデジタル・ラインをアナログ・ラインから離すか、少なくともアナログ・トレースをデジタル・トレースと並行に配置しないようにして、外部結合の影響を最小にします。誤ったレイアウトによるデジタル・フィードスルーの例を図3 に示します。

デジタル・フィードスルーは代表値で示される仕様です。負荷へ伝送されるエネルギーが、デジタル入力レベル、スルーレート、トグルしたデジタル・ライン数(送信されたデータ)など複数の要因に依存するためです。

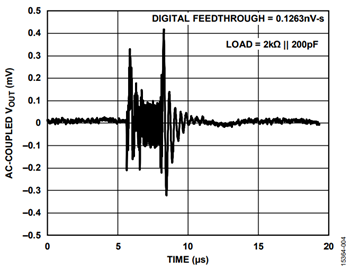

この仕様は、外部へ伝送されるエネルギーの面積(nV-s)を示します。入力レジスタへの書き込みに関連したデジタル・フィードスルーの影響の例を図4 に示します。

デジタル・フィードスルーに関連したエネルギーの測定は、DAC コア出力の更新(制御レジスタの更新など)が行われないようにDAC にコマンドを書き込んで行います。ここでは、内部発生エネルギー(つまり、DAC コアの更新時に生じるエネルギー)を増加させうる他の影響や、内部の校正ルーチンに関連したエネルギーを測定しないようにするためです。

内部校正ルーチン中に発生するエネルギーは、デジタル/アナログ・グリッチに含まれます。デジタル・フィードスルーは書込み/読出しのアクセスごとに現れます。

DAC コアの出力が更新されると、別のダイナミック現象がグリッチの形でDAC 出力で観測される可能性があります。この仕様はDAC コア内部のスイッチ制御ライン間の同一ではない伝播遅延に関連し、デジタル/アナログ・グリッチ・インパルスまたはグリッチ・エネルギーと呼ばれています。なぜなら、スイッチをトグルしてDAC 抵抗を選択することによって、デジタル・ワードをアナログに変換するときに発生するからです。

デジタル/アナログ・グリッチ・インパルスはデバイスに固有のものですが、デジタル・フィードスルーと同様に不適切なPCB レイアウトによって悪化します。

デジタル/アナログ・グリッチ・インパルスの代表的な性能は、メジャー・キャリーを中心として1 LSB の遷移が起きたときの正味面積(nV-s)としても測定されます。16 ビットDAC の場合、メジャー・キャリーはDAC のコード0x7FFF とコード0x8000 の間でトグルします。この場合、通常はDAC スイッチのほとんどが変化する必要があります。

DAC レジスタへの書き込みに伴うデジタル/アナログ・グリッチ・インパルスの影響の例を図5 に示します。デジタル・フィードスルーの影響を無効にするため、デジタル・フィードスルーによって発生したエネルギーが完全に散逸した後に、遅延させたハードウェアLDAC イベントを用いてDAC を更新します。

コードの変化には異なるスイッチが関わるため、DAC コードが異なると発生するグリッチ・エネルギーも異なります。

デジタル/アナログ・グリッチのワースト・ケースは、必ずしもメジャー・コード遷移(ミッドスケール・コードを中心とした1 LSB)で起きるわけではありません。これは、レイアウトの内部寄生成分とDAC の内部寄生成分(内部の校正エンジンを含む)の2 つの要因に依存します。物理的には、デジタルのミッドスケール・コードは必ずしもDAC のミッドスケール・コードであるとは限りません。しかし、デジタルのメジャー・コードの遷移は、デジタル/アナログ・グリッチ・エネルギーを定量化するための良い基準と考えられています。

DAC コアのダイナミック効果の伝搬

出力のスルーレートと出力リンギングは低周波での現象ですが、デジタル・フィードスルーとデジタル/アナログ・グリッチ・インパルスは主に中~高周波での現象です。

デジタル・フィードスルーは、50 MHz やそれ以上高速のクロック速度でのデジタル伝送で使用される周波数で発生します。例えば、スルーレートが1 nV/s の場合、トーンは300 MHz まで高くなる可能性があります。ダイナミック事象の周波数によって観察されることのある高速トランジェントを図4 と図5 に示します。

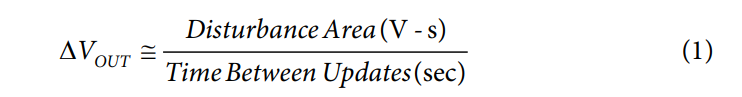

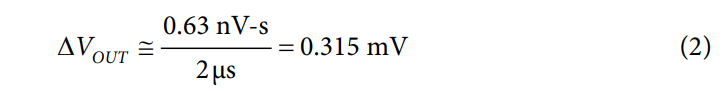

どんな場合でも、内部で発生したエネルギーのいくらかは、前掲の図が示すように、外部で測定することができます。負荷に伝送されるダイナミック・エネルギーは、出力ピンに接続される外部のコンデンサに依存し、次式で定義される電圧の増分を発生します。

ここで

Capacitor は外部のコンデンサの値です。

Energy は、ダイナミック事象によって外部に伝送されるエネルギーです。

ベンチ測定では、この電圧増分は外部のコンデンサとは比較的無関係になります。これは、伝送された動的エネルギーがDAC出力ピンを介して外部で消費され、低インピーダンスの経路が与えられるためです。

DAC の連続動作

高速微調整を必要とするアプリケーションでDAC を連続的に更新すると、負荷に伝送されるエネルギーが完全には散逸しないため、出力で追加オフセットが測定されます。

電圧増分の値は、伝送されるエネルギーの値と、コンデンサが放電しなければならない時間の2 つの要因によって決まります(図6 参照)。

DAC が連続的に更新され、その結果デジタル・フィードスルーとアナログ・グリッチの両方によって内部でエネルギーが発生していると仮定します。

DAC アクセスがレジスタの読出し/書込みのみで、DAC コアの更新が実行されない場合があり、デジタル・フィードスルーのみが電圧増分の原因になります。

AD5686R 4 チャンネル、16 ビットnanoDAC+の事例研究

以上の概念を、AD5686R を例にとって説明します。

AD5686R の出力が連続的に更新されると、書き込みの間隔が1μs ~ 20 μs だけ遅延します。

内部で発生したエネルギーは約1 μs の間に伝送されます。これは、デジタル・フィードスルーの持続時間と、36 MHz SCLKクロックでの24 ビット、それにアナログ・グリッチの持続時間の合計です。

更新時間がエネルギー事象と同じかそれよりも長い場合、コンデンサの値に応じて、生成される電圧の増分は次のように近似できます(図7 参照)。

1 μs の更新では、測定される電圧の増分はデジタル・フィードスルー・エネルギーおよびアナログ・グリッチに一致します。すなわち、0.13 nV-s + 0.5 nV-s = 0.63 nV-s になります(図8 参照)。

一例として、外乱が 0.63 nV-s で、更新頻度が2 μs の場合、生じる電圧増分は次のようになります。

ベンチ測定値と式 1 との間の相関関係を図9 に示します。

すべてのコードが同じ正味面積になるわけではなく、ΔVOUT がわずかに異なっています。ミッドスケール付近のコードの結果の例を図10 に示します。大きなダイナミック・エネルギーを生じるコードでは、ΔVOUT も大きくなることがわかります。平均エネルギーは、AD5686R のデータシートの仕様の値(約0.6nV-s)と一致しています。

充分な分解能でダイナミック・エネルギーを測定するには、出力信号をAC 結合する必要があります。そのため、高速のアクセス時間でダイナミック・エネルギーを測定しようとすると、DC 成分の一部が失われる可能性があります。したがって、DAC のアクセス時間が速すぎて散逸に十分な時間がない場合にこの追加エネルギーを定量化するには、ΔVOUT(DC 値)の方が良い方法です。

前述のように、測定される正味面積は外部のコンデンサとは無関係です(図7 参照)。

表 1 に示すように、与えられたアクセス時間における各種負荷容量でのΔVOUT の測定値には小さな差があります。

| COUT | Access Time | ||

| 1 µs | 5 µs | 10 µs | |

| 200 pF | 631 μV | 133 μV | 67 μV |

| 1 µF | 661 μV | 134 μV | 67 μV |

| 10 µF | 622 μV | 130 μV | 66 μV |

各種の DAC アクセス時間で測定したAD5686R のΔVOUT を表 2に示します。DAC 出力が更新されたときのデジタル・フィードスルーとデジタル/アナログ・グリッチ・インパルスの両方による代表的なΔVOUT が、各種アクセス時間に対して示されています。同時に、DAC コードが入力レジスタに書き込まれても出力が更新されないときのデジタル・フィードスルーのみの結果も示されています。

| DAC Access Time (μs) | ΔVOUT Feedthrough and Glitch (μV) | ΔVOUT Feedthrough Only (μV) |

| 1 | 618 | 210 |

| 2.5 | 320 | 110 |

| 5 | 215 | 72 |

| 10 | 150 | 54 |

| 20 | 120 | 43 |

まとめ

これまでに述べたようなダイナミックな現象の性質とその影響は寄生成分や結合メカニズムに大きく依存するため、DAC によって異なる場合があります。この現象のダイナミックな効果は、特定のアプリケーションや回路構成、それに動作条件によって変化します。

DAC 出力の更新が粗い場合、セトリング時間とレイテンシがDAC 更新レートへの制限要因となります。DAC 出力の微調整のみが行われる場合や、デバイスに書き込んでも出力が更新されない場合は、DAC コアのダイナミックな効果によって発生する追加エネルギーによって、追加オフセットがいくらか生じる可能性があります。

アプリケーションにとってDC 性能が重要な場合は、(デジタル・インターフェースで決まる)最高速のアクセス時間でDACを動作させるべきではありせん。アプリケーションで特に高速な更新速度が必要な場合は、システム性能への潜在的な影響を理解するために、エネルギー面積を評価する必要があります。この影響を適切に数値化するには、実際の測定値に基づくことが最善です。システムに過剰なDC 電圧(ΔVOUT)が存在する場合は、様々なアクセス時間で測定することを推奨します。複雑で信頼性が高くないAC 測定をしなくて済みます。

一般に DAC を扱う場合は、ダイナミックな性能(セトリング時間、デジタル・フィードスルー、デジタル/アナログ・グリッチ)とシステム構成の両方を慎重に評価した、信頼性の高いアクセス時間(更新レート)を定めます。