# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## 概要

MAX8550/MAX8551は、 $V_{DDQ}$ を生成する同期式降圧型PWMコントローラ、 $V_{TT}$ を生成するソース/シンク型LDOリニアレギュレータ、及び $V_{TTR}$ を生成する10mAリファレンス出力バッファを内蔵しています。降圧型コントローラは2個の外付けNチャネルMOSFETを駆動して、2V~28Vの入力電圧から最大出力電流15Aで、最低出力電圧0.7Vを発生します。LDOレギュレータは、最大1.5Aの連続電流、3Aのピーク電流をシンクまたはソースすることができます。LDO出力と10mAリファレンスバッファ出力はいずれも、REFIN電圧をトラッキングすることができます。このような機能を備えたMAX8550/MAX8551は、デスクトップ、ノートブック、及びグラフィックカードのDDRメモリアプリケーションに最適です。

MAX8550/MAX8551のPWMコントローラには、最高600kHzのプログラマブルスイッチング周波数で動作するマキシム独自のQuick-PWM™アーキテクチャが採用されています。この制御方式は、広範な入力/出力電圧比を容易に可能とし、高効率と比較的一定のスイッチング周波数を維持しながら、過渡負荷に対して100nsで応答します。MAX8550は、携帯用機器のアプリケーションに最適なスキップモードオプションと完全プログラマブルUVP/OVPを提供します。スキップモードでは、軽負荷での効率が改善されます。MAX8551は、デスクトップ及びグラフィックカードアプリケーションを対象にしており、パルススキップ機能を備えていません。

VTT及びVTTR出力は、 $V_{REFIN}/2$ を1%以内の誤差でトラッキングします。広帯域のこのLDOレギュレータは、大容量コンデンサなしで優れた過渡応答を提供するためコストとサイズが低く抑えられます。

降圧コントローラとLDOレギュレータは、独立した電流制限機能を備えています。降圧レギュレータの可変無損失フの字電流制限は、ローサイドMOSFETのドレインソース間電圧降下を監視することによって実現します。さらに、過電圧及び低電圧保護回路も内蔵されています。過電流条件が排除されると、レギュレータはソフトスタートを再開します。このため、短絡状態における電力損失が最小限に抑制されます。MAX8550/MAX8551では、SHDNA、SHDNB、及びSTBYの各入力を使用してフレキシブルな電源シーケンスとスタンバイ時の電力管理が可能です。

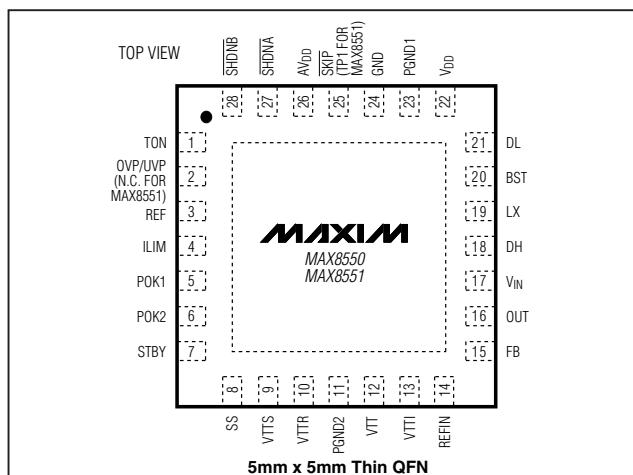

MAX8550とMAX8551はいずれも、小型、5mm x 5mm、28ピン、薄型QFNパッケージで提供されます。

## アプリケーション

- DDR I 及びDDR II メモリ電源

- デスクトップコンピュータ

- ノートブック及びデスクノート

- グラフィックカード

- ゲームコンソール

- RAID

- ネットワーキング

**MAXIM**

**MAX8550/MAX8551**

## 特長

### 降圧コントローラ

- ◆ Quick-PWMによる負荷ステップ応答：100ns

- ◆ 最大効率：95%

- ◆ 入力電圧範囲：2V~28V

- ◆ 出力電圧：1.8V/2.5V(固定)、または0.7V~5.5V(可変)

- ◆ 選択可能なスイッチング周波数：最高600kHz

- ◆ プログラマブル電流制限、フの字制限機能付き

- ◆ 1.7msのデジタルソフトスタート及び個別シャットダウン

- ◆ 過電圧/低電圧保護オプション

- ◆ パワーグッドウインドウコンパレータ

### LDOセクション

- ◆ VTT及びVTTR機能を完全内蔵

- ◆ VTTは±3Aソーシング/シンキング能力を装備

- ◆ VTTとVTTR出力は $V_{REFIN}/2$ をトラッキング

- ◆ セラミック出力コンデンサのみで設計可能

- ◆ 入力電圧範囲：1.0V~2.8V

- ◆ パワーグッドウインドウコンパレータ

## 型番

| PART              | TEMP RANGE     | PIN-PACKAGE       |

|-------------------|----------------|-------------------|

| <b>MAX8550ETI</b> | -40°C to +85°C | 28 5mm x 5mm TQFN |

| MAX8550ETI+       | -40°C to +85°C | 28 5mm x 5mm TQFN |

| <b>MAX8551ETI</b> | -40°C to +85°C | 28 5mm x 5mm TQFN |

+は鉛フリーパッケージを意味します。

## ピン配置

標準動作回路はデータシートの最後に記載されています。

Quick-PWMはMaxim Integrated Products, Inc.の商標です。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## ABSOLUTE MAXIMUM RATINGS

|                                                                   |                              |

|-------------------------------------------------------------------|------------------------------|

| $V_{IN}$ to GND                                                   | -0.3V to +30V                |

| $V_{DD}$ , $AV_{DD}$ , $V_{TTI}$ to GND                           | -0.3V to +6V                 |

| $SHDNA$ , $SHDNB$ , $REFIN$ to GND                                | -0.3V to +6V                 |

| $SS$ , $POK1$ , $POK2$ , $\overline{SKIP}$ , $ILIM$ , $FB$ to GND | -0.3V to +6V                 |

| $STBY$ , $TON$ , $REF$ , $UVP/OVP$ to GND                         | -0.3V to $(AV_{DD} + 0.3V)$  |

| $OUT$ , $VTTR$ to GND                                             | -0.3V to $(AV_{DD} + 0.3V)$  |

| $DL$ to $PGND1$                                                   | -0.3V to $(V_{DD} + 0.3V)$   |

| $DH$ to $LX$                                                      | -0.3V to $(V_{BST} + 0.3V)$  |

| $LX$ to $BST$                                                     | -6V to +0.3V                 |

| $LX$ to GND                                                       | -2V to +30V                  |

| $VTT$ to GND                                                      | -0.3V to $(V_{VTTI} + 0.3V)$ |

|                                                                  |                             |

|------------------------------------------------------------------|-----------------------------|

| $VTTS$ to GND                                                    | -0.3V to $(AV_{DD} + 0.3V)$ |

| $PGND1$ , $PGND2$ to GND                                         | -0.3V to +0.3V              |

| $REF$ Short Circuit to GND                                       | Continuous                  |

| Continuous Power Dissipation ( $T_A = +70^\circ C$ )             |                             |

| 28-Pin 5mm x 5mm TQFN (derate 35.7mW/°C<br>above $+70^\circ C$ ) | 2.86W                       |

| Operating Temperature Range                                      | -40°C to +85°C              |

| Junction Temperature                                             | +150°C                      |

| Storage Temperature Range                                        | -65°C to +165°C             |

| Lead Temperature (soldering, 10s)                                | +300°C                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

( $V_{IN} = +15V$ ,  $V_{DD} = AV_{DD} = V_{SHDNA} = V_{SHDNB} = V_{BST} = V_{ILIM} = 5V$ ,  $V_{OUT} = V_{REFIN} = V_{VTTI} = 2.5V$ ,  $UVP/OVP = STBY = FB = \overline{SKIP} = GND$ ,  $PGND1 = PGND2 = LX = GND$ ,  $TON = OPEN$ ,  $V_{VTTS} = V_{VTT}$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 1)

| PARAMETER                                   | SYMBOL               | CONDITIONS                                              | MIN                      | TYP  | MAX   | UNITS   |

|---------------------------------------------|----------------------|---------------------------------------------------------|--------------------------|------|-------|---------|

| <b>MAIN PWM CONTROLLER</b>                  |                      |                                                         |                          |      |       |         |

| Input Voltage Range                         | $V_{IN}$             |                                                         | 2                        | 28   |       | V       |

|                                             | $V_{DD}$ , $AV_{DD}$ |                                                         | 4.5                      | 5.5  |       |         |

| Output Adjust Range                         | $V_{OUT}$            |                                                         | 0.7                      | 5.5  |       | V       |

| Output Voltage Accuracy<br>(Note 2)         |                      | FB = OUT                                                | 0.693                    | 0.7  | 0.707 | V       |

|                                             |                      | FB = GND                                                | 2.47                     | 2.5  | 2.53  |         |

|                                             |                      | FB = $V_{DD}$                                           | 1.78                     | 1.8  | 1.82  |         |

| Soft-Start Ramp Time                        | $t_{SS}$             | Rising edge of $\overline{SHDNA}$ to full current limit |                          | 1.7  |       | ms      |

| On-Time                                     | $TON$                | $V_{IN} = 15V$ ,<br>$V_{OUT} = 1.5V$<br>(Note 3)        | TON = GND (600kHz)       | 170  | 194   | 219     |

|                                             |                      |                                                         | TON = REF (450kHz)       | 213  | 243   | 273     |

|                                             |                      |                                                         | TON = OPEN (300kHz)      | 316  | 352   | 389     |

|                                             |                      |                                                         | TON = $AV_{DD}$ (200kHz) | 461  | 516   | 571     |

| Minimum Off-Time                            | $t_{OFF\_MIN}$       | (Note 3)                                                | 200                      | 300  | 450   | ns      |

| $V_{IN}$ Quiescent Supply Current           | $I_{IN}$             |                                                         |                          | 25   | 40    | $\mu A$ |

| $V_{IN}$ Shutdown Supply Current            |                      | $SHDNA = \overline{SHDNB} = GND$                        |                          | 1    | 5     | $\mu A$ |

| $AV_{DD}$ Quiescent Supply Current          | $I_{AVDD}$           | All on (PWM, $V_{TT}$ , and $VTTR$ on)                  |                          | 2.5  | 5     | mA      |

|                                             |                      | $SHDNA = GND$ (only $V_{TT}$ and $VTTR$ on)             |                          | 2    | 4     |         |

|                                             |                      | $STBY = AV_{DD}$ (only $VTTR$ and PWM on)               |                          | 1    | 2     |         |

|                                             |                      | $SHDNB = GND$ (only PWM on)                             |                          | 0.5  | 1     |         |

| $AV_{DD} + V_{DD}$ Shutdown Supply Current  |                      | $SHDNA = \overline{SHDNB} = GND$                        |                          | 2    | 10    | $\mu A$ |

| $AV_{DD}$ Undervoltage-Lockout<br>Threshold |                      | Rising edge of $V_{IN}$                                 | 4.1                      | 4.25 | 4.4   | V       |

|                                             |                      | Hysteresis                                              |                          | 50   |       | mV      |

| $V_{DD}$ Quiescent Supply Current           | $I_{VDD}$            | Set $V_{FB} = 0.8V$                                     |                          | 1    | 5     | $\mu A$ |

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

MAX8550/MAX8551

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN} = +15V$ ,  $V_{DD} = AV_{DD} = V_{SHDNA} = V_{SHDNB} = V_{BST} = V_{ILIM} = 5V$ ,  $V_{OUT} = V_{REFIN} = V_{VTI} = 2.5V$ ,  $UV_{P/OVP} = ST_{BY} = FB = \overline{SKIP} = GND$ ,  $PGND1 = PGND2 = LX = GND$ ,  $TON = OPEN$ ,  $V_{VTTS} = V_{VTT}$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                              | SYMBOL     | CONDITIONS                                               | MIN   | TYP  | MAX   | UNITS       |

|------------------------------------------------------------------------|------------|----------------------------------------------------------|-------|------|-------|-------------|

| <b>REFERENCE</b>                                                       |            |                                                          |       |      |       |             |

| Reference Voltage                                                      | $V_{REF}$  | $AV_{DD} = 4.5V$ to $5.5V$ ; $I_{REF} = 0$               | 1.98  | 2    | 2.02  | V           |

| Reference Load Regulation                                              |            | $I_{REF} = 0$ to $50\mu A$                               |       |      | 0.01  | V           |

| REF Undervoltage Lockout                                               |            | $V_{REF}$ rising                                         |       | 1.93 |       | V           |

|                                                                        |            | Hysteresis                                               |       | 300  |       | mV          |

| <b>FAULT DETECTION</b>                                                 |            |                                                          |       |      |       |             |

| OVP Trip Threshold<br>(Referred to Nominal $V_{OUT}$ )                 |            | $UV_{P/OVP} = AV_{DD}$ (Note 4)                          | 112   | 116  | 120   | %           |

| UV Trip Threshold<br>(Referred to Nominal $V_{OUT}$ )                  |            |                                                          | 65    | 70   | 75    | %           |

| POK1 Trip Threshold<br>(Referred to Nominal $V_{OUT}$ )                |            | Lower level, falling edge, 1% hysteresis                 | 87    | 90   | 93    | %           |

|                                                                        |            | Upper level, rising edge, 1% hysteresis                  | 107   | 110  | 113   |             |

| POK2 Trip Threshold<br>(Referred to Nominal $V_{VTTS}$ and $V_{VTR}$ ) |            | Lower level, falling edge, 1% hysteresis                 | 87.5  | 90   | 92.5  | %           |

|                                                                        |            | Upper level, rising edge, 1% hysteresis                  | 107.5 | 110  | 112.5 |             |

| UV Blanking Time                                                       |            | From rising edge of $\overline{SHDNA}$                   | 10    | 20   | 40    | ms          |

| OVP, UV, POK_ Propagation Delay                                        |            | OVP not applicable in MAX8551                            |       | 10   |       | $\mu s$     |

| POK_ Output Low Voltage                                                |            | $I_{SINK} = 4mA$                                         |       | 0.3  |       | V           |

| POK_ Leakage Current                                                   |            | $V_{POK\_} = 5.5V$ , $V_{FB} = 0.8V$ , $V_{VTTS} = 1.3V$ |       | 1    |       | $\mu A$     |

| ILIM Adjustment Range                                                  | $V_{ILIM}$ |                                                          | 0.25  | 2.00 |       | V           |

| ILIM Input Leakage Current                                             |            |                                                          |       | 0.1  |       | $\mu A$     |

| Current-Limit Threshold (Fixed)<br>$PGND1$ to $LX$                     |            |                                                          | 45    | 50   | 55    | mV          |

| Current-Limit Threshold (Adjustable) $PGND1$ to $LX$                   |            | $V_{ILIM} = 2V$                                          | 170   | 200  | 235   | mV          |

| Current-Limit Threshold (Negative Direction) $PGND1$ to $LX$           |            | $\overline{SKIP} = AV_{DD}$ (Note 4)                     | -75   | -60  | -45   | mV          |

| Current-Limit Threshold (Negative Direction) $PGND1$ to $LX$           |            | $\overline{SKIP} = AV_{DD}$ , $V_{ILIM} = 2V$ (Note 4)   |       | -250 |       | mV          |

| Zero-Crossing Detection Threshold $PGND1$ to $LX$                      |            |                                                          |       | 3    |       | mV          |

| Thermal-Shutdown Threshold                                             |            |                                                          |       | +160 |       | $^{\circ}C$ |

| Thermal-Shutdown Hysteresis                                            |            |                                                          |       | 15   |       | $^{\circ}C$ |

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN} = +15V$ ,  $V_{DD} = AV_{DD} = V_{SHDNA} = V_{SHDNB} = V_{BST} = V_{ILIM} = 5V$ ,  $V_{OUT} = V_{REFIN} = V_{VTI} = 2.5V$ ,  $UVP/OVP = STBY = FB = \overline{SKIP} = GND$ ,  $PGND1 = PGND2 = LX = GND$ ,  $TON = OPEN$ ,  $V_{VTS} = V_{VTT}$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                                       | SYMBOL | CONDITIONS                                         | MIN             | TYP  | MAX  | UNITS     |

|---------------------------------------------------------------------------------|--------|----------------------------------------------------|-----------------|------|------|-----------|

| <b>MOSFET DRIVERS</b>                                                           |        |                                                    |                 |      |      |           |

| DH Gate-Driver On-Resistance                                                    |        | $V_{BST} - V_{LX} = 5V$                            | 1               | 4    |      | $\Omega$  |

| DL Gate-Driver On-Resistance in High State                                      |        |                                                    | 1               | 4    |      | $\Omega$  |

| DL Gate-Driver On-Resistance in Low State                                       |        |                                                    | 0.5             | 3    |      | $\Omega$  |

| Dead Time (Additional to Adaptive Delay)                                        |        | DH falling to DL rising<br>DL falling to DH rising | 30<br>30        |      |      | ns        |

| <b>INPUTS AND OUTPUTS</b>                                                       |        |                                                    |                 |      |      |           |

| Logic Input Threshold<br>(SHDN <sub>—</sub> , STBY, $\overline{SKIP}$ (Note 4)) |        | Rising edge                                        | 1.20            | 1.7  | 2.20 | V         |

|                                                                                 |        | Hysteresis                                         |                 | 225  |      | mV        |

| Logic Input Current<br>(SHDN <sub>—</sub> , STBY, $\overline{SKIP}$ (Note 4))   |        |                                                    | -1              |      | +1   | $\mu A$   |

| Dual-Mode™ Input Logic Levels (FB)                                              |        | Low (2.5V output)                                  |                 | 0.05 |      | V         |

|                                                                                 |        | High (1.8V output)                                 | 2.1             |      |      |           |

| Input Bias Current (FB)                                                         |        |                                                    | -0.1            |      | +0.1 | $\mu A$   |

| Four-Level Input Logic Levels<br>(TON, OVP/UVP (Note 4))                        |        | High                                               | $AV_{DD} - 0.4$ |      |      | V         |

|                                                                                 |        | Floating                                           | 3.15            |      | 3.85 |           |

|                                                                                 |        | REF                                                | 1.65            |      | 2.35 |           |

|                                                                                 |        | Low                                                |                 | 0.5  |      |           |

| Logic Input Current<br>(TON, OVP/UVP (Note 4))                                  |        |                                                    | -3              |      | +3   | $\mu A$   |

| OUT Input Resistance                                                            |        | FB = GND                                           | 90              | 175  | 350  | $k\Omega$ |

|                                                                                 |        | FB = AV <sub>DD</sub>                              | 70              | 135  | 270  |           |

|                                                                                 |        | FB adjustable mode                                 | 400             | 800  | 1600 |           |

| OUT Discharge-Mode On-Resistance                                                |        | (Note 4)                                           |                 | 10   | 25   | $\Omega$  |

| DL Turn-On Level During Discharge Mode (Measured at OUT)                        |        | (Note 4)                                           |                 | 0.3  |      | V         |

Dual ModelはMaxim Integrated Products, Inc.の商標です。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

MAX8550/MAX8551

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN} = +15V$ ,  $V_{DD} = AV_{DD} = V_{SHDNA} = V_{SHDNB} = V_{BST} = V_{ILIM} = 5V$ ,  $V_{OUT} = V_{REFIN} = V_{VTTI} = 2.5V$ ,  $UVPOVP = STBY = FB = \overline{SKIP} = GND$ ,  $PGND1 = PGND2 = LX = GND$ ,  $TON = OPEN$ ,  $V_{VTS} = V_{VTT}$ ,  $TA = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $TA = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                             | SYMBOL      | CONDITIONS                                                | MIN      | TYP      | MAX       | UNITS     |

|-------------------------------------------------------|-------------|-----------------------------------------------------------|----------|----------|-----------|-----------|

| <b>LINEAR REGULATORS (VTTR AND VTT)</b>               |             |                                                           |          |          |           |           |

| VTTI Input Voltage Range                              | $V_{VTTI}$  |                                                           | 1        | 2.8      |           | V         |

| VTTI Supply Current                                   | $I_{VTTI}$  | $I_{VTT} = I_{VTTR} = 0$                                  | <0.1     | 1        |           | mA        |

| VTTI Shutdown Current                                 |             | $\overline{SHDNA} = \overline{SHDNB} = GND$               |          | 10       |           | $\mu A$   |

| REFIN Input Impedance                                 |             | $V_{REFIN} = 2.5V$                                        | 12       | 20       | 30        | $k\Omega$ |

| REFIN Range                                           | $V_{REFIN}$ |                                                           | 1        | 2.8      |           | V         |

| REFIN Lockout Threshold                               |             | $V_{REFIN}$ rising                                        | 0.7      | 0.9      |           | V         |

|                                                       |             | Hysteresis                                                |          | 75       |           | mV        |

| Soft-Start Charge Current                             | $I_{SS}$    | $V_{SS} = 0$                                              |          | 4        |           | $\mu A$   |

| VTT Internal MOSFET High-Side On-Resistance           |             | $I_{VTT} = -100mA$ , $V_{VTTI} = 1.5V$ , $AV_{DD} = 4.5V$ |          | 0.3      |           | $\Omega$  |

| VTT Internal MOSFET Low-Side On-Resistance            |             | $I_{VTT} = 100mA$ , $AV_{DD} = 4.5V$                      |          | 0.3      |           | $\Omega$  |

| VTT Output Accuracy<br>(Referred to $V_{REFIN} / 2$ ) |             | $V_{REFIN} = 1.5V$ or $2.5V$ , $I_{VTT} = 1mA$            | -1       | +1       |           | %         |

| VTT Load Regulation                                   |             | $V_{REFIN} = 2.5V$ , $I_{VTT} = 0$ to $\pm 1.5A$          |          | 1        |           | %         |

|                                                       |             | $V_{REFIN} = 1.5V$ , $I_{VTT} = 0$ to $\pm 1A$            |          | 1        |           |           |

| VTT Current Limit                                     |             | $V_{TT} = 0$ or $V_{VTTI}$                                | $\pm 3$  | $\pm 5$  | $\pm 6.5$ | A         |

| VTTS Input Current                                    | $I_{VTTS}$  | $V_{VTTS} = 1.5V$ , VTT open                              | 0.1      | 1        |           | $\mu A$   |

| VTTR Output Error<br>(Referred to $V_{REFIN} / 2$ )   |             | $V_{REFIN} = 1.5V$ or $2.5V$ , $I_{VTTR} = 0$             | -1       | +1       |           | %         |

| VTTR Current Limit                                    |             | $V_{VTTR} = 0$ or $V_{VTTI}$                              | $\pm 23$ | $\pm 40$ | $\pm 60$  | mA        |

**Note 1:** Specifications to  $-40^{\circ}C$  are guaranteed by design, not production tested.

**Note 2:** When the inductor is in continuous conduction, the output voltage has a DC regulation level higher than the error-comparator threshold by 50% of the ripple. In discontinuous conduction, the output voltage has a DC regulation level higher than the trip level by approximately 1.5% due to slope compensation.

**Note 3:** On-time and off-time specifications are measured from 50% point to 50% point at the DH pin with  $LX = GND$ ,  $V_{BST} = 5V$ , and a  $250pF$  capacitor connected from DH to LX. Actual in-circuit times may differ due to MOSFET switching speeds.

**Note 4:** Not applicable to the MAX8551.

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

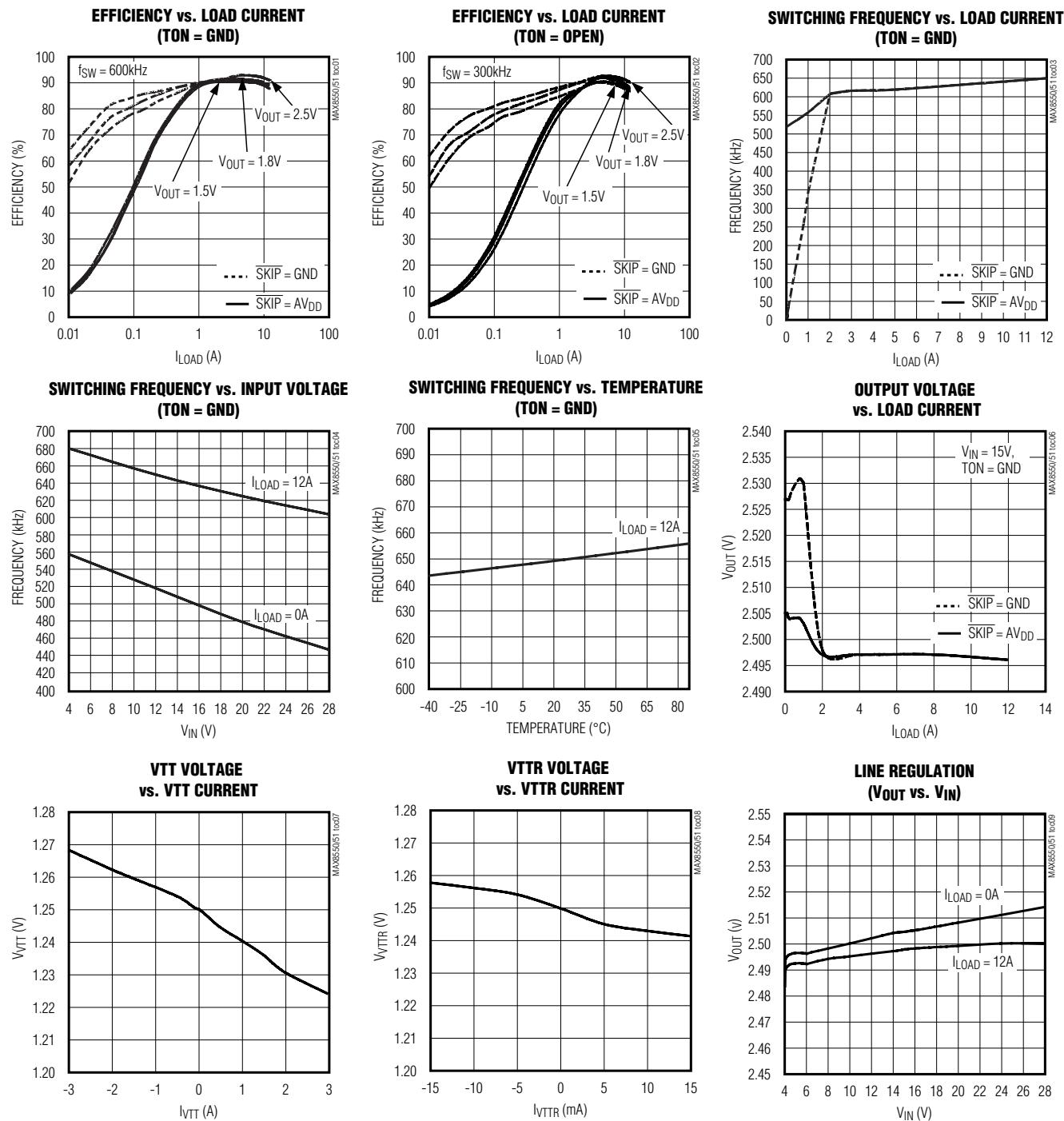

## 標準動作特性

( $V_{IN} = 12V$ ,  $V_{OUT} = 2.5V$ ,  $T_{ON} = GND$ ,  $\overline{SKIP} = AV_{DD}$ , circuit of Figure 8,  $T_A = +25^\circ C$ , unless otherwise noted.)

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

MAX8550/MAX8551

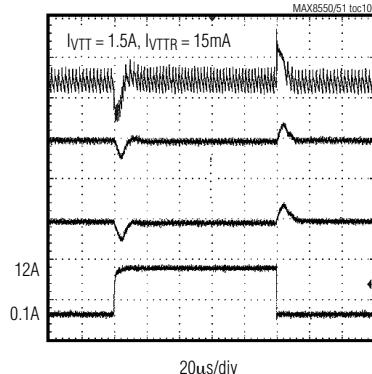

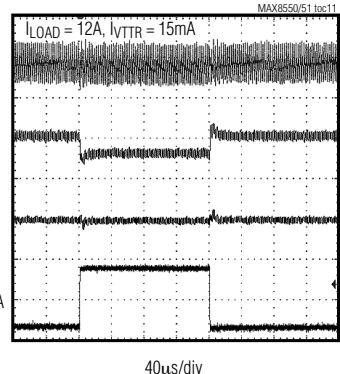

## 標準動作特性(続き)

( $V_{IN} = 12V$ ,  $V_{OUT} = 2.5V$ ,  $TON = GND$ ,  $\overline{SKIP} = AV_{DD}$ , circuit of Figure 8,  $T_A = +25^\circ C$ , unless otherwise noted.)

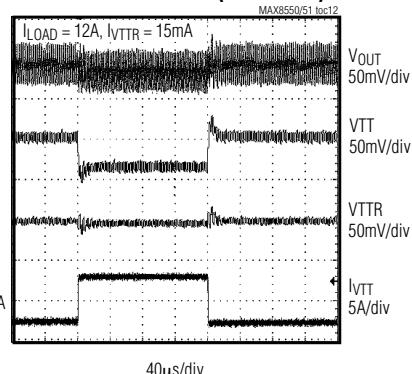

### LOAD TRANSIENT (BUCK)

### LOAD TRANSIENT VTT (-1.5A TO +1.5A)

### LOAD TRANSIENT VTT (-3A TO +3A)

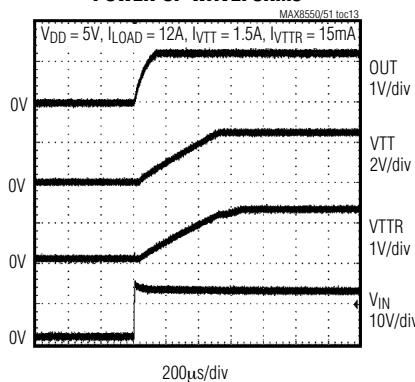

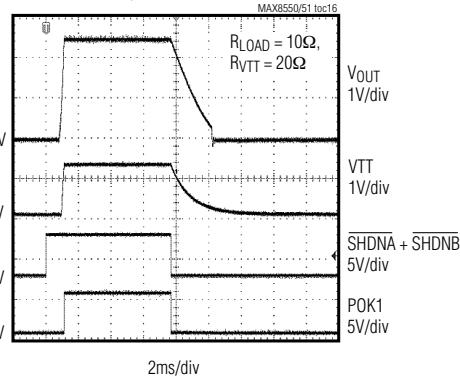

### POWER-UP WAVEFORMS

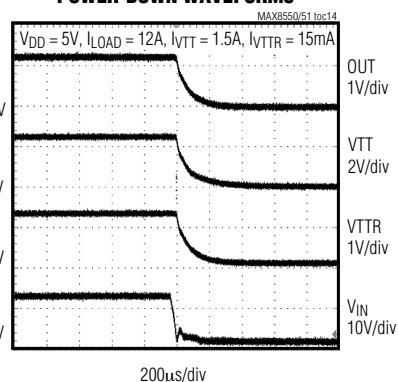

### POWER-DOWN WAVEFORMS

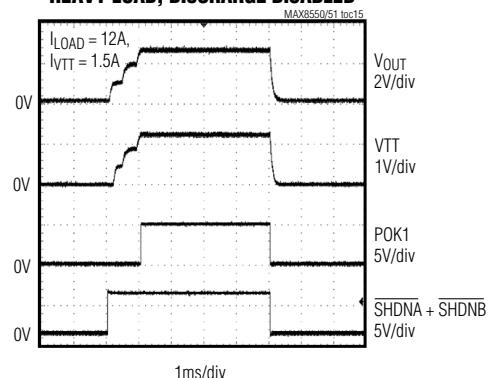

### VDDQ STARTUP AND SHUTDOWN INTO HEAVY LOAD, DISCHARGE DISABLED

### VDDQ STARTUP AND SHUTDOWN INTO LIGHT LOAD, DISCHARGE ENABLED

### VTT, VTTR STARTUP AND SHUTDOWN

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

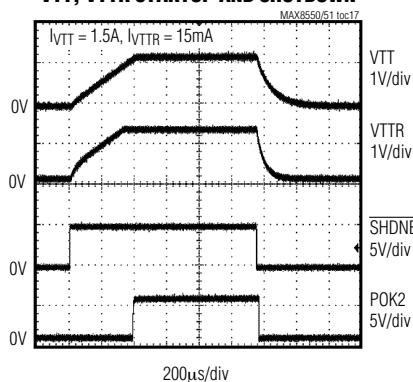

## 標準動作特性(続き)

( $V_{IN} = 12V$ ,  $V_{OUT} = 2.5V$ ,  $T_{ON} = GND$ ,  $\overline{SKIP} = AV_{DD}$ , circuit of Figure 8,  $T_A = +25^\circ C$ , unless otherwise noted.)

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

MAX8550/MAX8551

## 端子説明

| 端子 | 名称                       | 機能                                                                                                                                                                                                                                                                                                                                                                  |

|----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | TON                      | オン時間選択制御入力。この4レベルのロジック入力により、公称DHオン時間を設定します。TONは、GND、REF、AVDDに接続するか、または無接続のままにして下記の公称スイッチング周波数を選択してください。<br>TON = AVDD(200kHz)<br>TON = 開放(300kHz)<br>TON = REF(450kHz)<br>TON = GND(600kHz)                                                                                                                                                                         |

| 2  | OVP/<br>UVP<br>(MAX8550) | 過電圧/低電圧保護制御入力。この4レベルのロジック入力により、過電圧及び/または低電圧保護をイネーブル、またはディセーブルします。過電圧限界値は、公称出力電圧の116%です。低電圧限界値は、公称出力電圧の70%です。放電モードがイネーブルされるとOVPもイネーブルされます。必要とする機能を得るためにOVP/UVPピンを下記のピンに接続してください。<br>OVP/UVP = AVDD(OVPと放電モードをイネーブル、UVPをイネーブル)<br>OVP/UVP = 開放(OVPと放電モードをイネーブル、UVPをディセーブル)<br>OVP/UVP = REF(OVPと放電モードをディセーブル、UVPをイネーブル)<br>OVP/UVP = GND(OVPと放電モードをディセーブル、UVPをディセーブル) |

|    | N.C.<br>(MAX8551)        | 接続せずに開放状態にしてください。*                                                                                                                                                                                                                                                                                                                                                  |

| 3  | REF                      | +2.0Vリファレンス電圧出力。0.1 $\mu$ F(min)のコンデンサでGNDにバイパスしてください。REFは、外部負荷に50 $\mu$ Aを供給することができます。REFは、ILIMの電圧設定に使用することができます。SHDNA、SHDNB、及びSTBYがローのとき、REFはオフになります。                                                                                                                                                                                                             |

| 4  | ILIM                     | 降圧レギュレータの谷電流制限スレッショルド調整用端子。PGNDとLX間の電流制限スレッショルドは、ILIMの電圧の0.1倍です。ILIMを抵抗分圧器(通常、REFとGNDに接続)に接続してLXの電流制限スレッショルドを25mV~200mVに設定してください。この値は、ILIMの0.25V~2Vの範囲に対応します。50mVのデフォルト電流制限スレッショルドを選択するためには、ILIMをAVDDに接続してください。「電流制限値の設定」の項を参照してください。                                                                                                                               |

| 5  | POK1                     | 降圧コンバータのパワーグッドオープンドレイン出力。降圧コンバータの出力電圧が通常のレギュレーションポイント $\pm$ 10%を超えたとき、またはソフトスタート期間中に、POK1はローになります。出力がレギュレーション中でかつソフトスタート回路が停止しているとき、POK1はハイインピーダンスになります。POK1は、シャットダウン中はローです。                                                                                                                                                                                        |

| 6  | POK2                     | LDO用のパワーグッドオープンドレイン出力。通常モードでは、VTTRまたはVTTSのいずれかが通常のレギュレーションポイント(これは通常REFIN/2です) $\pm$ 10%を超えたとき、POK2はローになります。スタンバイモードでは、POK2はVTTR入力のみに応答します。POK2は、シャットダウン中及びV <sub>REFIN</sub> が0.8V以下のときにローです。                                                                                                                                                                      |

| 7  | STBY                     | スタンバイ。VTT出力がディセーブルとなる低自己消費電流モードにするためにはハイに接続してください。しかし、SHDNBがハイの場合はVTTR/バッファがアクティブの状態のままです。このモードでは、POK2はVTTRのみから入力されます。PWM出力は、SHDNAの状態に応じてオンまたはオフになります。                                                                                                                                                                                                              |

| 8  | SS                       | VTTとVTTRのソフトスタート制御端子。コンデンサ(「標準動作回路」のC9)をSSとグランド(ソフトスタートコンデンサの選択に関する記述を参照)間に接続してください。SHDNBがローのときにソフトスタート端子SSのグランドへの放電をディセーブルするためには、SSを開放してください。「POR、UVLO、及びソフトスタート」の項を参照してください。                                                                                                                                                                                      |

| 9  | VTTS                     | 終端用電源出力の検出端子。VTTをREFIN電圧の1/2に正確に安定化するために、VTTSは通常VTTピンに接続します。VTTをREFIN電圧の1/2よりも高い電圧に安定化するためには、VTTとGND間に接続した抵抗分圧器にVTTSを接続してください。                                                                                                                                                                                                                                      |

| 10 | VTTR                     | 終端用リファレンス電圧出力。VTTRはV <sub>REFIN</sub> /2をトラッキングします。                                                                                                                                                                                                                                                                                                                 |

\* MAX8551はOVPまたは放電モード機能を備えていません。UVPのみを備えています。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## 端子説明(続き)

| 端子 | 名称                | 機能                                                                                                                                                                                                                                       |

|----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | PGND2             | VTT及びVTTR用の電源グランド。PGND2は、外部でエクスポートドパッドの下側に接続してください。                                                                                                                                                                                      |

| 12 | VTT               | 終端用電源出力。 $V_{REFIN}/2$ に安定化するためには、VTTをVTTSに接続してください。                                                                                                                                                                                     |

| 13 | VTTI              | VTT及びVTTRの電源入力電圧。DDRアプリケーションでは、通常、VTTIを降圧レギュレータの出力に接続してください。                                                                                                                                                                             |

| 14 | REFIN             | 外部リファレンス入力。これは、VTT及びVTTR出力を $V_{REFIN}/2$ に安定化するために使用します。                                                                                                                                                                                |

| 15 | FB                | 降圧レギュレータ出力用のフィードバック入力。 $+1.8V$ 固定出力の場合は、FBをAV <sub>DD</sub> に接続し、 $+2.5V$ 固定出力の場合はGNDに接続してください。可変出力( $0.7V \sim 5.5V$ )の場合は、FBを出力電圧に接続した抵抗分圧器に接続してください。FB端子は、 $+0.7V$ となるように安定化されます。                                                     |

| 16 | OUT               | 出力電圧の検出接続端子。降圧レギュレータ用出力フィルタコンデンサの正端子に接続してください。ハイサイドスイッチング用のMOSFET(「標準動作回路」のQ1)のオン時間を決定するために、OUTは出力電圧を検出します。また、OUTは、固定出力モードにおいて降圧レギュレータ出力用のフィードバック入力として働きます。放電モードがOVP/UVPによってイネーブルされると、OUTとGNDの間に接続された内蔵 $10\Omega$ 抵抗器を通して出力コンデンサが放電します。 |

| 17 | VIN               | 入力電圧の検出接続端子。入力電源に接続してください。 $V_{IN}$ は、PWMのオン時間用のワンショットタイマの設定のみに使用されます。INの電圧範囲は $2V \sim 28V$ です。                                                                                                                                         |

| 18 | DH                | ハイサイドゲートドライバ出力。LXからBSTまでスイングします。DHはシャットダウンまたはUVLOのときにローです。                                                                                                                                                                               |

| 19 | LX                | 外付けインダクタ接続端子。LXをインダクタの入力側に接続してください。LXは、電流制限とDHドライバの電源リターンの両方に使用します。                                                                                                                                                                      |

| 20 | BST               | ブースト用フライングコンデンサ接続端子。「標準動作回路(図8)」に従って外付けコンデンサ及びダイオードに接続してください。「ブースト電源ダイオード及びコンデンサの選択」の項を参照してください。                                                                                                                                         |

| 21 | DL                | 同期整流器のゲートドライバ出力。PGNDからV <sub>DD</sub> までスイングします。                                                                                                                                                                                         |

| 22 | V <sub>DD</sub>   | DLゲート駆動用電源入力。 $+4.5V \sim +5.5V$ のシステム電源電圧に接続してください。 $1\mu F(min)$ のセラミックコンデンサでPGND1にバイパスしてください。                                                                                                                                         |

| 23 | PGND1             | 降圧コントローラ用電源グランド。PGND1を外部でエクスポートドパッドの下側に接続してください。                                                                                                                                                                                         |

| 24 | GND               | 降圧コントローラ及びLDO両用のアナロググランド。GNDを外部でエクスポートドパッドの下側に接続してください。                                                                                                                                                                                  |

| 25 | SKIP<br>(MAX8550) | パルススキッピング制御入力。低ノイズ強制PWMモードの場合は、AV <sub>DD</sub> に接続してください。パルススキッピング動作をイネーブルするためには、GNDに接続してください。                                                                                                                                          |

|    | TP1<br>(MAX8551)  | MAX8551では、これはテスト端子であり、GND(ピン24)に接続する必要があります。                                                                                                                                                                                             |

| 26 | AV <sub>DD</sub>  | 降圧及びLDO用のアナログ電源入力。 $10\Omega$ の直列抵抗器を通して $+4.5V \sim +5.5V$ のシステム電源電圧に接続してください。 $1\mu F$ 以上のセラミックコンデンサでGNDにバイパスしてください。                                                                                                                   |

| 27 | SHDNA             | シャットダウン制御入力A。降圧出力の制御に使用します。SHDNAの立上りエッジで過電圧及び低電圧保護フォルトラッチがクリアされます(表2と3参照)。通常動作とするためにはAV <sub>DD</sub> に接続してください。                                                                                                                         |

| 28 | SHDNB             | シャットダウン制御入力B。VTT及びVTTR出力の制御に使用してください。VTTRとVTTはいずれも、シャットダウン状態ではハイインピーダンスです(表2参照)。                                                                                                                                                         |

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

**MAX8550/MAX8551**

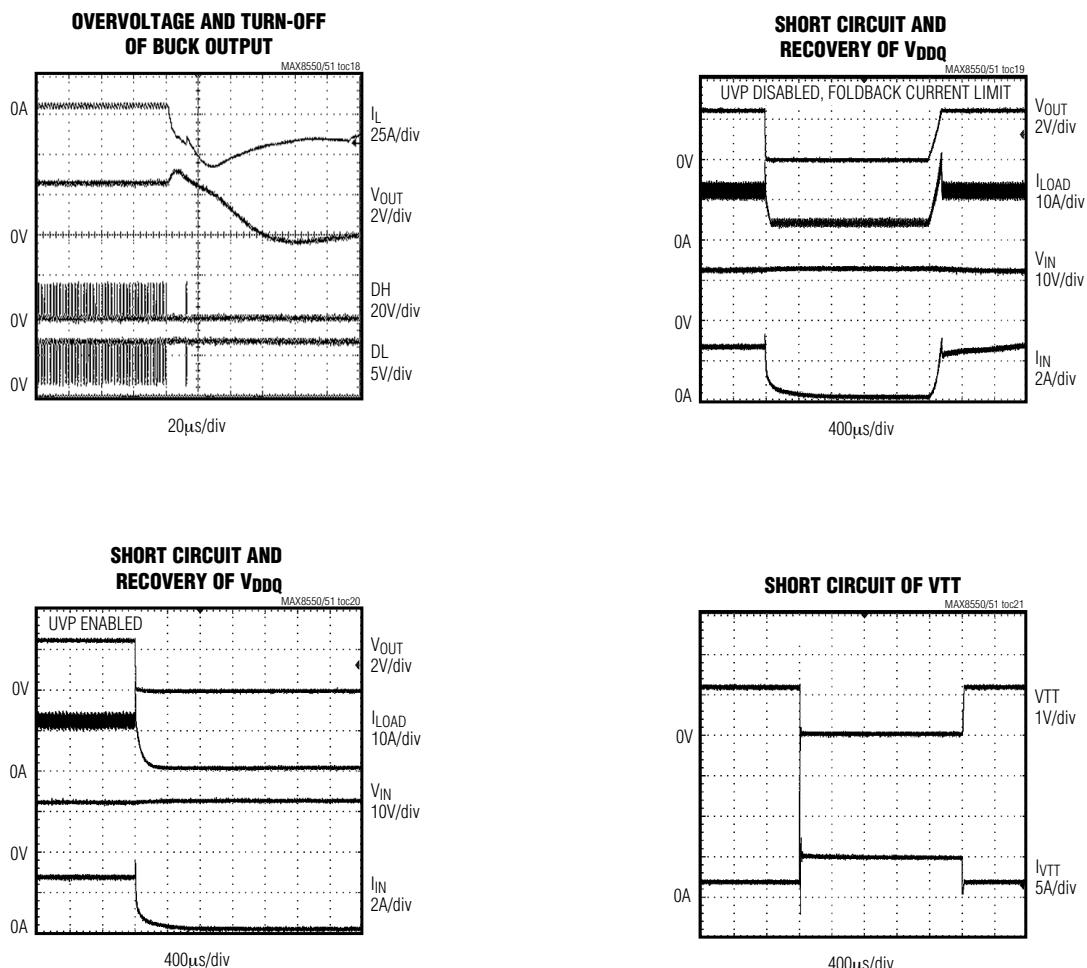

図1. ファンクションダイアグラム

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## 詳細

MAX8550/MAX8551は、同期式降圧型PWMコントローラ、LDOリニアレギュレータ、及び10mAリファレンス出力バッファを組み合わせたものです。降圧コントローラは、2個の外付けNチャネルMOSFETを駆動して、+2V～+28V入力から最大12Aの負荷電流を供給し最低0.7Vの電圧を発生します。LDOリニアレギュレータは、比較的速い応答速度で、連続最大1.5A、ピーク3Aの電流をシンクまたはソースすることができます。このような機能を備えたMAX8550/MAX8551は、DDRメモリアプリケーションに最適です。

MAX8550/MAX8551内蔵の降圧レギュレータは、マキシム独自の一定オン時間Quick-PWMアーキテクチャを採用して最高600kHzの固定スイッチング周波数を発生します。この制御方式は、広範な入力/出力電圧比を容易に処理し、過渡負荷に対して100nsの「瞬時オン」応答を可能とし、比較的一定のスイッチング周波数で高効率を維持します。

降圧コントローラ、LDO、及びリファレンス出力バッファは、独立に電流制限を行います。降圧レギュレータの無損失フの字電流制限は、ローサイドFETのドレイン-ソース間電圧降下を監視することによって実現します。ILIM入力は、この電流制限値の調整に使用されます。過電圧保護は、これを選択した場合、出力電圧がその設定出力の116%を超えるとローサイド同期整流用FETをオンに、またハイサイドFETをオフにラッチすることによって実現されます。さらに、過電流状態において出力電圧が安定化出力の70%以下になった場合、MOSFETドライバをオフ状態にラッチするオプションの低電圧保護機能を備えています。このことで、短絡状態における電力損失を最小限に抑制することができます。

LDO及びバッファ付きリファレンス出力バッファの電流制限はそれぞれ±5Aと±40mAで、どちらも過電圧保護や低電圧保護機能を備えていません。どちらの出力も電流制限値に達すると、出力電圧は安定化されなくなりますが電流は電流制限値に安定化されます。

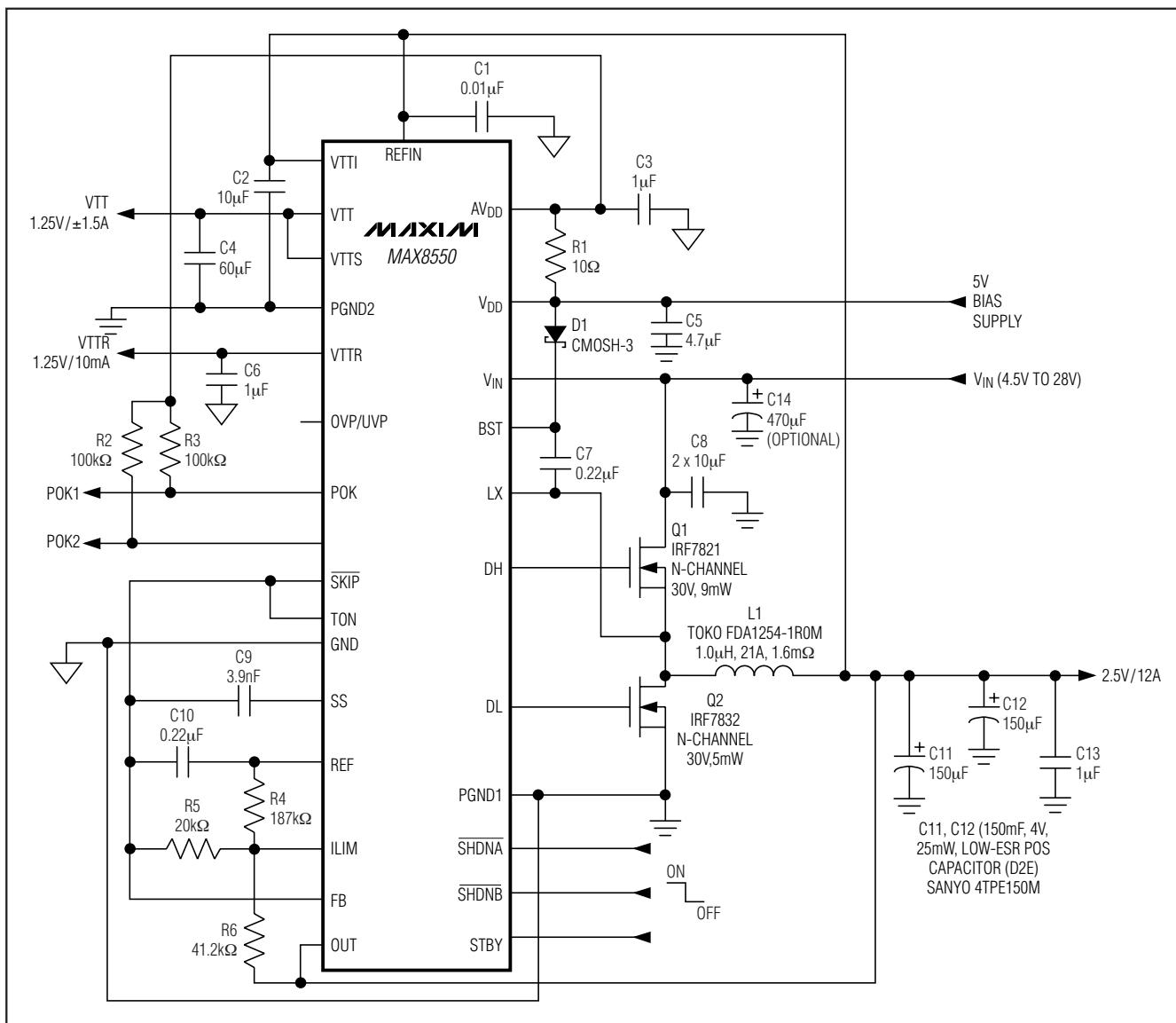

## +5Vバイアス電源( $V_{DD}$ と $AV_{DD}$ )

MAX8550/MAX8551には、入力電圧( $V_{IN}$ )の他に外付け+5Vバイアス電源が必要です。バイアス電源をICの外部から供給すると効率が改善されるとともに、PWM回路とゲートドライバに給電する+5Vリニアレギュレータに関するコストが削減されます。スタンダードアロンで動作させることが必要な場合は、MAX1615などの外部リニアレギュレータによって+5V電源を生成することができます。入力電源が+4.5V～+5.5Vの固定電源である場合は、 $V_{DD}$ 、 $AV_{DD}$ 、及びINを相互に接続することができます。

$V_{DD}$ は降圧レギュレータのMOSFETドライバ用電源入力で、 $AV_{DD}$ はICのその他の回路に電源を供給します。 $AV_{DD}$ と $V_{DD}$ 電源は、IC及びMOSFETのゲート駆動用電流を供給する必要があります。この最大電流は、次式から概算することができます。

$$I_{BIAS} = I_{VDD} + I_{AVDD} + f_{SW} \times (Q_{G1} + Q_{G2})$$

ここで、 $I_{VDD}$  +  $I_{AVDD}$ は $V_{DD}$ と $AV_{DD}$ に流れる自己消費電流で、 $Q_{G1}$ 及び $Q_{G2}$ は「標準動作回路」のMOSFET Q1とQ2の全ゲート電荷( $V_{GS} = 5V$ における)で、 $f_{SW}$ はスイッチング周波数です。

## 自走一定オン時間PWM

Quick-PWM制御回路は、擬似固定周波数、一定オン時間、電圧フィードフォワード付き電流モードレギュレータで構成されます(図1)。この構成は、電流検出抵抗器として機能する出力フィルタコンデンサのESRに依存しており、出力リップル電圧がPWMランプ信号を供給します。制御アルゴリズムは単純で、ハイサイドスイッチのオン時間は、入力電圧に逆比例し出力電圧に正比例するパルス幅のワンショットだけで決まります。もう1つのワンショットが300ns(typ)の最小オフ時間を設定します。オン時間ワンショットは、エラーコンパレータがロー、ローサイドスイッチ電流が谷電流制限スレッショルド以下、及び最小オフ時間ワンショットが時間切れの場合にトリガされます。

## オン時間ワンショット(TON)

PWMコアの心臓部はハイサイドスイッチのオン時間を設定するワンショットです。この高速、低ジッタ、可変ワンショットは、入力及び出力電圧に応答してオン時間を変化させる回路を内蔵しています。ハイサイドスイッチのオン時間は、次式に示すように、入力電圧( $V_{IN}$ )に逆比例し出力電圧に正比例します。

$$t_{ON} = K \times \frac{(V_{OUT} + I_{LOAD} \times R_{DS(ON)Q2})}{V_{IN}}$$

ここで、K(スイッチング周期)はTON入力接続部で設定され(表1)、 $R_{DS(ON)Q2}$ は「標準動作回路」の同期整流器(Q2)のオン抵抗です(図8)。このアルゴリズムは、固定周波数のクロック発生器を欠いているにも関わらずスイッチング周波数がほぼ一定になります。一定スイッチング周波数の利点として次の2つが挙げられます。

- 1) 455kHz IF帯などのノイズに敏感な領域を避けて周波数を選択することができる。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

- 2) インダクタのリップル電流の動作点は比較的安定しているため、設計が容易になり、出力電圧リップルの予測が可能になる。

オン時間ワンショットは、「Electrical Characteristics」の表に指定された動作点での精度が優れています(600kHzと450kHzで約±12.5%、200kHzと300kHzで±10%)。「Electrical Characteristics」の表で指定された条件から大きくずれた動作点でのオン時間は、広範囲で変動する可能性があります。たとえば、600kHzの設定では、5Vよりもずっと大きい入力電圧では、非常に短いオン時間が要求されるため、周波数が標準値で約10%低下します。

オン時間が一定ということは、スイッチング周波数が単にほぼ一定になるということだけです。「Electrical Characteristics」の表で保証されたオン時間は、抵抗損失やハイサイドMOSFETのスイッチング遅延に影響されます。インダクタ、両MOSFET、出力コンデンサのESR、及びプリント基板の出力とグランドにおける銅損などの抵抗損失は、負荷が増大するとスイッチング周波数を上昇させる傾向があります。デッドタイムの影響は実効オン時間を増加させるため、一方または両方のデッドタイムが有効オン時間に加わるとスイッチング周波数が低下します。デッドタイムは、PWMモード( $\text{SKIP} = V_{DD}$ )にある場合、及びインダクタ電流が軽負荷電流または負の負荷電流において反転する際に起こる出力電圧のダイナミックな遷移の際に生じます。インダクタ電流が反転すると、インダクタのEMFによってLXが通常よりも早めにハイになり、DH立上りのデッドタイムに等しい期間だけオン時間が伸びます。デッドタイムの影響が重要でない臨界伝導点を越える負荷では、実際のスイッチング周波数は次式のようになります。

$$f_{SW} = \frac{V_{OUT} + V_{DROP1}}{t_{ON}(V_{IN} + V_{DROP2})}$$

ここで、 $V_{DROP1}$ は同期整流器、インダクタ、プリント基板抵抗などによるインダクタ放電経路における寄生電圧降下の和で、 $V_{DROP2}$ はハイサイドスイッチ(「標準動作回路」のQ1)、インダクタ、プリント基板抵抗などの充電経路における抵抗による電圧降下の和で、 $t_{ON}$ はワンショットオン時間です(「オン時間ワンショット(TON)」の項参照)。

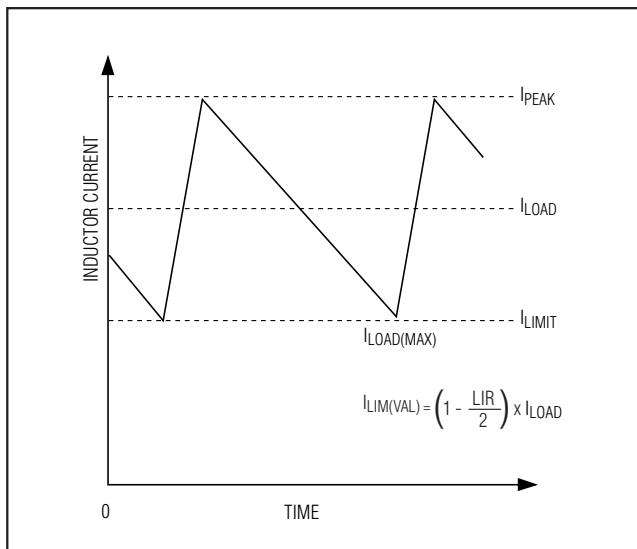

## 自動パルススキッピングモード ( $\text{SKIP} = \text{GND}$ )

スキップモード( $\text{SKIP} = \text{GND}$ )では、PFMへの固有の自動切替えが軽負荷で起こります(図2)。この切替えは、インダクタ電流がゼロクロスする時にローサイドスイッチのオン時間を短縮するコンパレータの影響を受けます。

ゼロクロスコンパレータは、同期整流用MOSFET(「標準動作回路」のQ2、図8)両端でインダクタ電流を差動検出します。 $V_{PGND} - V_{LX}$ が電流制限スレッショルドの5%(デフォルトの50mV)の電流制限スレッショルドでは2.5mV以下に低下すると、コンパレータがDLを強制的にローにします(図1)。この機構によって、パルススキッピングPFMと非スキッピングPWM動作の間のスレッショルドが連続及び非連続インダクタ電流動作の境界(臨界伝導点とも呼ばれます)と一致します。PFM/PWMのクロスオーバーが生じる負荷電流レベル、 $I_{LOAD(SKIP)}$ は、インダクタ値の関数であるピークトゥピークリップ電流の1/2に等しくなります(図2)。このスレッショルドは、比較的安定しており、入力電圧( $V_{IN}$ )にわずかに依存するだけです。

$$I_{LOAD(SKIP)} = \left( \frac{V_{OUT} \times K}{2L} \right) \left( \frac{V_{IN} - V_{OUT}}{V_{IN}} \right)$$

ここで、Kはオン時間の換算係数です(表1参照)。たとえば、図8の「標準動作回路」( $k = 1.7\mu\text{s}$ 、 $V_{OUT} = 2.5\text{V}$ 、 $V_{IN} = 12\text{V}$ 、及び $L = 1\mu\text{H}$ )では、パルススキッピング切替えは次式の電流で起こります。

$$\left( \frac{2.5\text{V} \times 1.7\mu\text{s}}{2 \times 1\mu\text{H}} \right) \left( \frac{12\text{V} - 2.5\text{V}}{12\text{V}} \right) = 1.68\text{A}$$

スイング(ソフト飽和)インダクタを使用する場合は、クロスオーバーポイントがさらに低い値で起こります。軽負荷がパルススキッピング動作を生じる場合、スイッチング波形はノイズを含み非同期ですが、これは軽負荷効率が高いことを示す正常な動作状態です。PFMノイズと軽負荷効率のトレードオフは、インダクタの値を変えて行ないます。一般に、小インダクタ値では効率対負荷曲線が平坦になりますが、大インダクタ値では最大負荷における効率が高くなり(コイル抵抗が一定であると仮定して)出力電圧リップルが小さくなります。

表1. Kファクタ誤差の近似値

| TON SETTING            | TYPICAL K-FACTOR (μs) | K-FACTOR ERROR (%) | MINIMUM $V_{IN}$ AT $V_{OUT} = 2.5\text{V}$ ( $h = 1.5$ , SEE THE DROPOUT PERFORMANCE SECTION) |

|------------------------|-----------------------|--------------------|------------------------------------------------------------------------------------------------|

| 200 (TON = $AV_{DD}$ ) | 5.0                   | ±10                | 3.15                                                                                           |

| 300 (TON = OPEN)       | 3.3                   | ±10                | 3.47                                                                                           |

| 450 (TON = REF)        | 2.2                   | ±12.5              | 4.13                                                                                           |

| 600 (TON = GND)        | 1.7                   | ±12.5              | 5.61                                                                                           |

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

大インダクタ値を使用する場合の難点として、物理的サイズが大きくなること、負荷過渡応答が特に低い入力電圧で悪化することなどが挙げられます。

DC出力精度の仕様は、エラーコンパレータのスレッショルドに関係します。インダクタが連続伝導状態にあるとき、MAX8850/MAX8551は出力リップルの谷の部分を安定化するため、実際のDC出力電圧はトリップレベルよりも出力リップル電圧の50%だけ高くなります。非連続伝導状態( $\overline{\text{SKIP}} = \text{GND}$ 及び $I_{\text{LOAD}} < I_{\text{LOAD}}(\overline{\text{SKIP}})$ )では、出力電圧のDCレギュレーションレベルがスロープ補償効果によってエラーコンパレータスレッショルドよりも約1.5%だけ高くなります。

## 強制PWMモード(MAX8550のみで $\overline{\text{SKIP}} = \text{AV}_{\text{DD}}$ )

低ノイズ強制PWMモード( $\overline{\text{SKIP}} = \text{AV}_{\text{DD}}$ )では、ローサイドスイッチのオン時間を制御するゼロクロスコンパレータがディセーブルされます。これによって、ローサイドゲート駆動波形がハイサイドゲート駆動波形と常に相補的な関係になるため、インダクタ電流が軽負荷で反転すると同時にDHが $V_{\text{OUT}}/V_{\text{IN}}$ のデューティ比を保ちます。強制PWMモードは、スイッチング周波数をほぼ一定に保ちます。しかし、外付けMOSFETのゲート電荷とスイッチング周波数によって無負荷の場合でも $V_{\text{DD}}$ バイアス電流が2mA～20mAのままであるため、この場合には強制PWM動作は無駄を生じます。オーディオ周波数ノイズを低減し、負荷過渡応答をし、シンク電流を供給してダイナミックな出力電圧調整を行なう場合は、強制PWMモードが最も有用です。

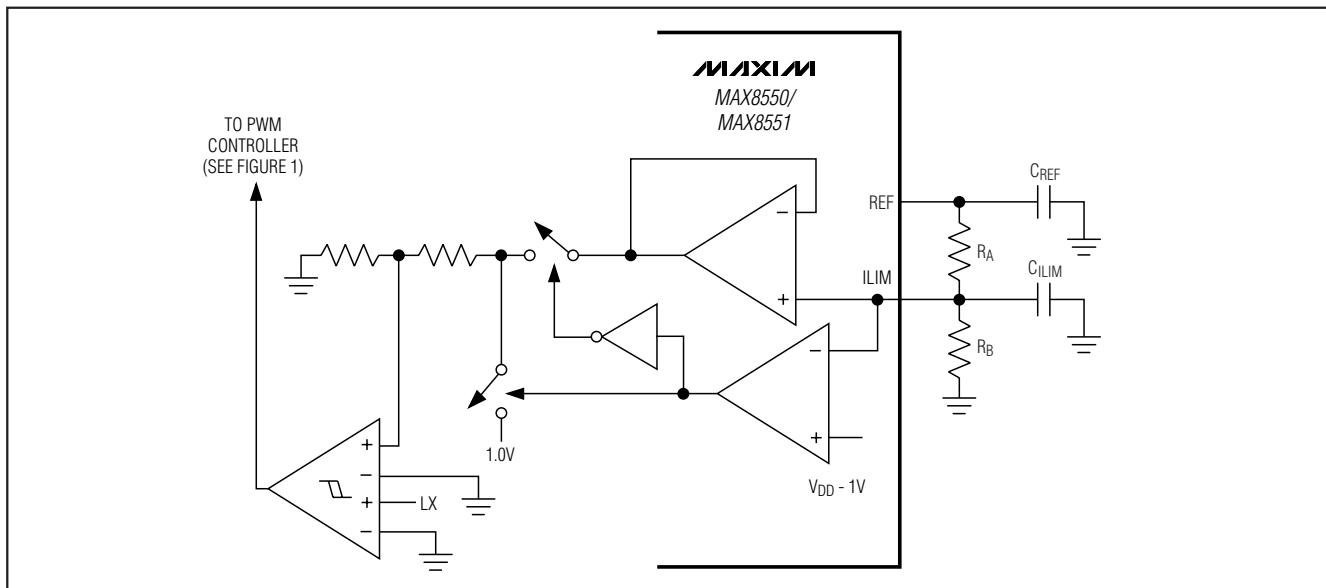

## 降圧レギュレータ(ILIM)の電流制限

### 谷電流制限

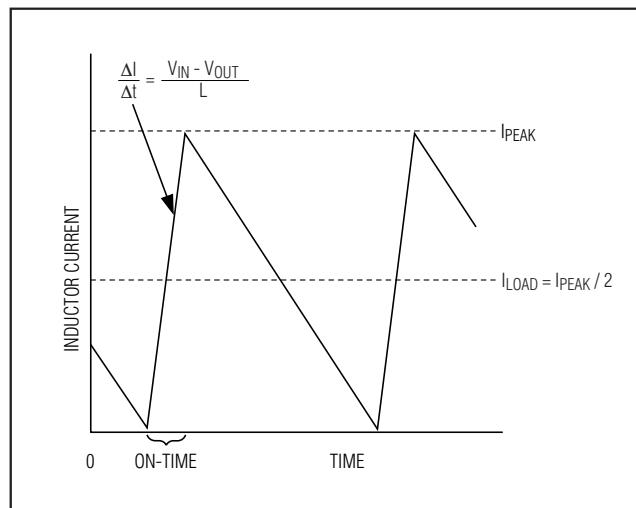

MAX8550/MAX8551の降圧レギュレータ部分の電流制限回路は、LXとPGND1の間の電圧降下を検出し整流用MOSFET(「標準動作回路」のQ2、図8)のオン抵抗を電流検出要素として使用する独特的の「谷」電流検出アルゴリズムを採用しています。電流検出信号の大きさが谷電流制限スレッショルド以上となると、PWMコントローラは新たなサイクルを開始することができません(図4)。谷電流検出を使用する場合、実際のピーク電流は谷電流制限スレッショルドよりもインダクタ電流リップルに相当する量だけ大きくなります。そのため、正確な電流制限特性と最大負荷容量は、

電流検出抵抗、インダクタ値、及び入力電圧の関数になります。この電流制限方法は、低電圧保護回路と組み合わせると、ほとんどあらゆる状況で利用することができます。

強制PWMモードでは、MAX8550/MAX8551は降圧レギュレータ出力がシンク電流を流している場合に負電流を制限して、過大な逆方向インダクタ電流を防止します。負電流制限スレッショルドは、正電流制限スレッショルドの約120%に設定されており、 $V_{\text{ILIM}}$ を調整すると正の電流制限に追従して変化します。電流制限スレッショルドは、ILIMに外付けした抵抗分圧器を使用して調整します。精度とノイズ耐性の点から2μA～20μAの分圧器電流が推奨されます。

電流制限スレッショルドの調整範囲は、25mV～200mVです。電流制限スレッショルド電圧(PGND1～LX)は、可変モードにおいて、ILIM端子に現れる電圧のちょうど1/10です。ILIMを $\text{AV}_{\text{DD}}$ に接続すると、スレッショルドはデフォルトの50mVになります。50mVのデフォルト値に切り替えるためのロジックスレッショルドは、およそ $\text{AV}_{\text{DD}} - 1\text{V}$ です。

ノイズとDC誤差がLXとGNDの間に現れる差動電流検出信号を劣化させることがないよう、プリント基板のレイアウト指針をよく守ってください。

図2. パルススキッピング/不連続クロスオーバーポイント

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

MAX8550/MAX8551

図3. 可変電流制限スレッショルド

図4. 谷電流制限スレッショルド

## POR、UVLO、及びソフトスタート

AV<sub>DD</sub>が約2V以上に上昇すると内部パワーオンリセット(POR)が働いて、フォルトラッチとソフトスタートカウンタのリセット、リファレンスの電源投入、及び降圧レギュレータの動作準備が行なわれます。AV<sub>DD</sub>が4.25V(typ)に達するまで、AV<sub>DD</sub>低電圧ロックアウト(UVLO)回路がスイッチングを抑止します。OVPとシャットダウン放電がディセーブルされると(OVP/UVP = REFまたはGND)DHをローにプルダウンするとともにDLをローにホールドすることによって、またはOVPとシャットダウン放電がイネーブルされると(OVP/UVP = AV<sub>DD</sub>または開放)DLを強制的にハイにすることによって、コントローラがスイッチングを抑止します。OVP/UVPと

シャットダウン設定の詳細な真理値表については、表3を参照してください。AV<sub>DD</sub>が4.25V以上に上昇すると、コントローラが降圧レギュレータをアクティブにし、内蔵ソフトスタートを初期化します。

降圧レギュレータの内蔵ソフトスタートは、起動中に電流制限レベルを緩やかに上昇させて入力サージ電流を抑制します。MAX8550/MAX8551では、ソフトスタート期間が5段階に分けられています。最初の段階では、コントローラが電流制限を最大値のわずか20%に制限します。出力が425μs以内にレギュレーションに達しなければソフトスタートが第2段階に入り、電流制限がさらに20%増加します。このプロセスは、最大電流制限に達する時点、1.7ms後、または出力が公称レギュレーション電圧に達する時点、のいずれか最初に到来する時点まで繰り返されます。コンデンサを外付けILIM抵抗器に並列に接続すると、降圧レギュレータ出力の連続可変アナログソフトスタート機能が実現されます。

LDOセクションのソフトスタートは、SSピンとグランドの間にコンデンサを接続することによって実現します。SHDNBがローに駆動されたとき、またはLDOの熱シャットダウン中にSSコンデンサが放電します。SHDNBがハイに駆動されたとき、または温度制限が解除されたときは内蔵の4μA(typ)の電流がSSコンデンサを充電します。その結果、SSの傾斜上昇する電圧は、SSが約1.6Vとなる最大電流制限に達するまで、VTTとVTTRの両出力に対する電流制限コンパレータスレッショルドを直線的に増加させます。このように起動中に電流限界値を下げる、特にコンデンサを駆動している場合は初期突入電流のピーク値が制限されます。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

ソフトスタートの時間ウィンドウを設定するために、SSコンデンサの値を適切に選定してください。ソフトスタート機能をディセーブルするためには、SSをフローティング状態にしてください。

## パワーOK(POK1)

POK1は、 $V_{OUT}$ を連続的に監視するウィンドウコンパレータ出力を表すオープンドレイン出力です。POK1は、SHDNAがローのとき及び降圧レギュレータ出力のソフトスタート期間中はアクティブに保たれます。ディジタルソフトスタートが終了すると、出力電圧がFBによって設定された公称レギュレーション電圧の±10%以内にある間は、POK1はハイインピーダンスになります。 $V_{OUT}$ が公称レギュレーション電圧よりも10%を超えて、降下あるいは上昇すると、MAX8550/MAX8551はPOK1をローにプルダウンします。フォルト状態が発生すると、SHDNAをトグルするか、あるいはAV<sub>DD</sub>電源をいったん1V以下に下げてから再投入することによってフォルトラッチをクリアするまでは、POK1が強制的にローになります。ロジックレベル出力電圧を得るために、POK1とAV<sub>DD</sub>の間にプルアップ抵抗器を外付けしてください。たいていのアプリケーションでは、100kΩの抵抗器で十分に機能します。POK1ウィンドウ検出器は、過電圧及び低電圧保護フォルト検出器及びVTTSとVTTRの状態とはまったく無関係であることに注意してください。

## SHDNAと出力放電

SHDNA入力は、降圧レギュレータに対応しており、ICの降圧レギュレータの部分を低電力モードとします(「Electrical Characteristics」の表参照)。また、SHDNAは、過電圧または低電圧保護フォルトなどのフォルト信号をリセットするために使用されます。

出力放電がイネーブルされて(OVP/UVP = AV<sub>DD</sub>または開放)、SHDNAとSHDNBがローにプルダウンされるとき、またはUVPがイネーブルされて(OVP/UVP = AV<sub>DD</sub>)、 $V_{OUT}$ がそのレギュレーション設定点の70%に低下した場合、MAX8550は内蔵10Ωスイッチを通して(OUT端子から)ステップダウンレギュレータ出力をグランドに放電させます。出力が放電中、DLは強制的にローにされ、PWMコントローラはディセーブルされますが、リファレンスはアクティブに保たれて正確なスレッショルドを供給します。いったん出力電圧が0.3V以下に低下すると、

MAX8550はリファレンスをシャットダウンしDLをハイにプルアップして、降圧レギュレータ出力とLXをグランドに効果的にクランプします。

出力放電がディセーブルされると(OVP/UVP = REFまたはGND)、コントローラは降圧出力をアクティブに放電せずにDLドライバはローに保たれます。これらの状態では、降圧出力の放電速度は負荷電流とその出力コンデンサの容量値によって決まります。降圧レギュレータは、OVP/UVP設定によって決定された放電モード状態を起動時に検出してラッチします。

MAX8551の場合は、OVP/UVPが内部でREFに接続されており、出力放電機能が常にイネーブルされています(表1参照)。

## SHDNBとSTBY

SHDNB入力はVTTR出力に対応しており、ローに駆動されるとICのリニアレギュレータ部分を低電力モードとします(「Electrical Characteristics」の表参照)。SHDNBがローにプルダウンされると、VTTRはハイインピーダンスになります。

STBY入力は、アクティブハイ入力で、VTTR出力のみをシャットダウンするために使用されます。STBYがハイのとき、VTTRはハイインピーダンスになります。STBY入力はSHDNB入力に優先します。そのため、SHDNBがハイの場合でもSTBYがハイであればVTTR出力は非アクティブです。

## パワーOK(POK2)

POK2は、VTTS入力とVTTR出力を常時監視するウィンドウコンパレータ出力を表すオープンドレイン型出力です。REFINが0.8V以下であるか、またはSHDNBがローにプルダウンされると、POK2はローにプルダウンされます。出力電圧がREFINによって設定された公称レギュレーション電圧の±10%以内にある限りは、POK2はハイインピーダンスになります。 $V_{VTTS}$ または $V_{VTTR}$ がその公称レギュレーション電圧よりも10%を超えて、上昇あるいは降下すると、MAX8550/MAX8551はPOK2をローにプルダウンします。POK2をロジックレベル出力電圧とするためには、POK2とAV<sub>DD</sub>の間にプルアップ抵抗器を外付けしてください。ほとんどのアプリケーションでは、100kΩの抵抗器で十分に機能します。

表2. シャットダウン及びスタンバイのための制御ロジック

| STBY             | SHDNA            | SHDNB            | BUCK OUTPUT | VTT | VTTR |

|------------------|------------------|------------------|-------------|-----|------|

| GND              | AV <sub>DD</sub> | AV <sub>DD</sub> | ON          | ON  | ON   |

| GND              | AV <sub>DD</sub> | GND              | ON          | OFF | OFF  |

| AV <sub>DD</sub> | AV <sub>DD</sub> | AV <sub>DD</sub> | ON          | OFF | ON   |

| GND              | GND              | AV <sub>DD</sub> | OFF         | ON  | ON   |

| GND              | GND              | GND              | OFF         | OFF | OFF  |

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## 電流制限(VTT用LDO及びVTTRバッファ)

VTT出力は、入力(VTTI)をV<sub>REFIN</sub>電圧の1/2に安定化するリニアレギュレータです。VTTのフィードバック点はVTTS入力端子です(図1)。VTT出力は、少なくとも連続1.5A、ピーク3Aのシンク及びソース電流を供給することができます。VTTとVTTRの電流制限値は、標準値では、それぞれ±5Aと±40mAです。どちらの出力も電流制限値に達すると、出力は電圧ではなく電流をレギュレートします。

## �ルト保護

MAX8550/MAX8551の降圧コントローラは過電圧/低電圧�ルト保護機能を備えています。�ルト保護をイネーブル及びディセーブルするためには、表3に従ってOVP/UVPの設定方法を選択してください。アクティブとなる設定をすると、コントローラは出力の低電圧及び過電圧�ルト状態を常時監視します。

## 過電圧保護(OVP)

出力電圧が公称レギュレーション電圧の116%を超えて上昇し(MAX8550のみ)、OVPがイネーブルされていると(OVP/UVP = AvDDまたは開放)、OVP回路は�ルトラッチをセットし、PWMコントローラをシャットダウンして、即座にDHをローにプルダウンしDLを強制的にハイにします。このことで、同期整流用MOSFET(図8の「標準動作回路」のQ2)が100%のデューティサイクルでオンとなり、出力コンデンサを急速に放電して出力をグランドレベルにクランプします。DLを急速にハイにラッチすると、OVPが起こる瞬間に出力LC回路に蓄積されたエネルギーによって出力電圧がわずかに負になる可能性があります。負荷が負電圧に対する耐性を持たない場合は、逆極性クランプとして働くパワーショットキダイオードを出力端に接続してください。�ルトラッチをクリアしてコントローラを再起動するためには、SHDNAをトグルするか、AvDD電源をいったん1V以下にしてから再投入してください。OVP/UVPがREFまたはGNDに接続されると、OVPはディセーブルされます(表3参照)。降圧出力にはOVPだけが適用されます。VTTとVTTR出力は、過電圧保護を備えていません。

表3. OVP/UVP�ルト保護機能の設定

| OVP/UVP | DISCHARGE                                            | UVP PROTECTION                                                           | OVP PROTECTION                                |

|---------|------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------|

| AVDD    | Yes.<br>DL forced high when SHDNA and SHDNB are low. | Enabled.<br>Discharge sequence activated. DL forced high when shut down. | Enabled.<br>DH pulled low and DL forced high. |

| OPEN    | Yes.<br>DL forced high when SHDNA and SHDNB are low. | Disabled.                                                                | Enabled.<br>DH pulled low and DL forced high. |

| REF     | No.<br>DL forced low when SHDNA is low.              | Enabled.<br>Discharge sequence activated. DL forced high when shut down. | Disabled.                                     |

| GND     | No.<br>DL forced low when SHDNA is low.              | Disabled.                                                                | Disabled.                                     |

## 低電圧保護(UVP)

UVPがイネーブルに設定されている場合、出力電圧がそのレギュレーション電圧の70%以下に下降すると、コントローラがフルトラッチをセットして放電モードを開始します(「SHDNAと出力放電」の項参照)。出力電圧が0.3Vに下降すると、同期整流器(「標準動作回路」のQ2)がオンとなり、降圧出力をGNDレベルにクランプします。UVPは、起動後、またはSHDNAの立上りエッジ後、少なくとも10ms(min)の間は無視されます。フルトラッチをクリアしてコントローラを再起動するためには、SHDNAをトグルするか、AVDD電源をいったん1V以下にしてから再投入してください。OVP/UVPを開放状態にするかまたはGNDに接続すると、UVPはディセーブルされます(表3参照)。降圧出力にはUVPだけが適用されます。VTT及びVTTR出力は、低電圧保護機能を備えていません。

## 熱�ルト保護

MAX8550/MAX8551は、2つの熱�ルト保護回路を備えています。1つはIC内の降圧レギュレータ部分を監視し、もう1つはリニアレギュレータ(VTT)とリファレンスバッファ出力(VTTR)を監視します。MAX8550/MAX8551の降圧レギュレータ部分の接合温度が+160°Cを超えて上昇すると、熱センサがフルトラッチをセットし、POK1をローにプルダウンし、OVP/UVPの設定状態とは無関係に放電モードを使用して降圧コントローラ出力をシャットダウンします。接合温度が15°Cだけ下がった後でコントローラを再駆動するためには、SHDNAをトグルするか、AVDD電源をいったん1V以下にしてから再投入してください。IC内のVTTとVTTRレギュレータ部分は、そのチップ温度が+160°Cを超えて上昇するとVTTとVTTRが遮断されてハイインピーダンス状態になり、ICのチップ部分が15°Cだけ下がった後で再起動します。この両方の熱�ルト保護機能は互いに独立しています。たとえば、VTT出力が過負荷になってその熱�ルトがトリガされても、降圧レギュレータは動作を続けます。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## 設計手順

スイッチング周波数とインダクタ動作点(リップル電流比またはLIR)を選定する前に、降圧レギュレータの入力電圧範囲( $V_{IN}$ )と最大負荷電流( $I_{LOAD}$ )を確定してください。設計の主なトレードオフは、適切なスイッチング周波数とインダクタ動作点を選定することにあり、これら以外の設計は、以下の4つの要因によって決まります。

- 入力電圧範囲。最大値( $V_{IN(MAX)}$ )は、ワーストケースの電圧を含まなければなりません。最小値( $V_{IN(MIN)}$ )は、コネクタとヒューズによる電圧降下を差し引いた後の最低電圧としなければなりません。可能であれば、入力電圧を低くすると効率を高くすることができます。

- 最大負荷電流。検討を要する値が2つあります。ピーク負荷電流( $I_{PEAK}$ )は、瞬時の部品ストレス及びフィルタの決定要因であるため、出力コンデンサの選択、インダクタの飽和定格、及び電流制限回路の設計に使用します。連続負荷電流( $I_{LOAD}$ )は、熱ストレスの決定要因であるため、入力コンデンサ、MOSFETなどの重要な発熱部品の選択に使用します。

- スイッチング周波数。この選択によって、サイズと効率の基本的なトレードオフが決まります。MOSFETのスイッチング損失が周波数と $V_{IN}^2$ に比例するため、最適周波数は、主として最大入力電圧の関数となります。また、最適周波数は、MOSFET技術の急速な進歩に伴ってより高い周波数が実用化されているため流動的です。

- インダクタ動作点。この選択によって、サイズと効率、及び過渡応答と出力リップルのトレードオフが決まります。小さいインダクタ値を使用すると過渡応答が改善され物理的サイズが小さくなります。リップル電流の増加によって効率が低下し出力リップル電圧が大きくなります。インダクタの現実的な最小値は、回路が臨界伝導(インダクタ電流が最大負荷抵抗においてサイクルごとにゼロに達する場合)の限界点で動作する場合の値です。インダクタ値をこれ以上小さくしても、小型化のメリットは認められません。一般に、最適な動作点はリップル電流が20%~50%の範囲にあります。インダクタ値は、また、パルススキッピングモード(軽負荷とするために、SKIP = ローとする)において、PFM/PWMが切り替わる負荷電流値を決定します。

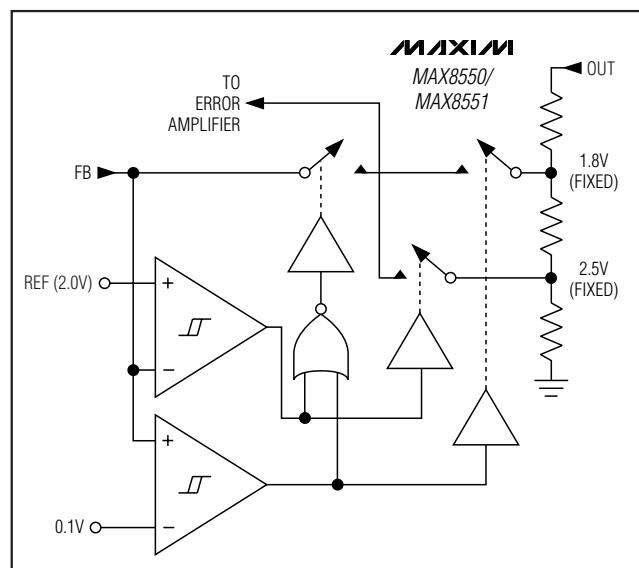

## 出力電圧の設定(ステップダウン)

### プリセット出力電圧

MAX8550/MAX8551のデュアルモード動作により、外付け部品を必要とせずに内蔵の共有設定電圧を選択することが可能です(図5)。2.5Vの固定出力を得るために

FBをGNDに、1.8Vの固定出力を得るためにFBをAV<sub>DD</sub>に、また0.7Vの固定出力を得るためにFBを直接OUTに接続してください。

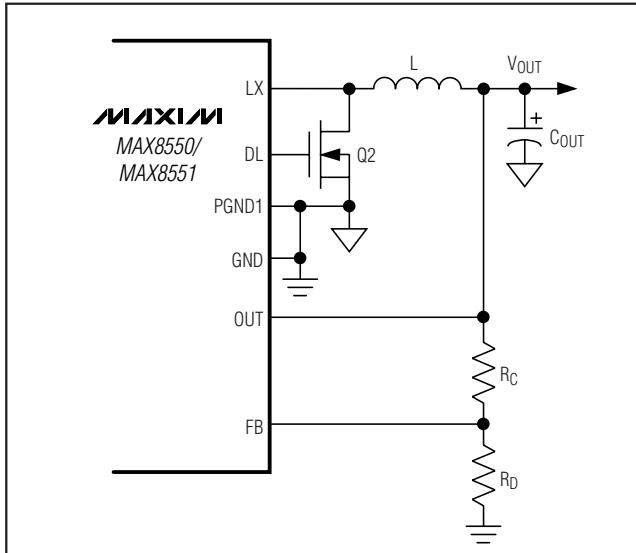

### FBに抵抗分圧器を接続する降圧レギュレタ出力( $V_{OUT}$ )の設定

降圧レギュレタの出力電圧は、抵抗分圧器を使用して0.7V~5.5Vの範囲で調整することができます(図6)。MAX8550/MAX8551では、FB端子が固定リファレンス電圧(0.7V)となるように安定化されます。調整される出力電圧は、次式で表わされます。

$$V_{OUT} = V_{FB} \left( 1 + \frac{R_C}{R_D} \right) + \frac{V_{RIPPLE}}{2}$$

ここで、 $V_{FB}$ は0.7Vです。 $R_C$ と $R_D$ は図6に示されています。 $V_{RIPPLE}$ は次式で表わされます。

$$V_{RIPPLE} = LIR \times I_{LOAD(MAX)} \times R_{ESR}$$

### VTTとVTTR電圧(LDO)の設定

終端用電源出力(VTT)は、2つの方法で設定することができます。1つは、VTT出力をVTTS入力に直接接続してVTTを $V_{REFIN}/2$ に安定化させる方法です。もう1つは、VTTとVTTSの間に抵抗分圧器を接続することによってVTTを $V_{REFIN}/2$ よりも高い電圧に安定化させる方法です。VTTの最大値は、 $V_{VTTI} - V_{DROPOUT}$ です。ここで、 $V_{DROPOUT} = I_{VTT} \times 0.3\Omega(\max)(T_A = +85^\circ\text{C} \text{において})$ です。

図5. デュアルモードフィードバックデコーダ

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

図6. 抵抗分圧器による $V_{OUT}$ の設定

終端リファレンス電圧(VTTR)は、 $V_{REFIN}/2$ をトラッキングします。

## インダクタの選択(降圧レギュレータ)

インダクタの値は、スイッチング周波数とインダクタの動作点から次式に従って決めることができます。

$$L = \frac{V_{OUT} (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times I_{LOAD(MAX)} \times LIR}$$

たとえば、 $I_{LOAD(MAX)} = 12A$ 、 $V_{IN} = 12V$ 、 $V_{OUT} = 2.5V$ 、 $f_{SW} = 600kHz$ 、リップル電流を30%(LIR = 0.3)とすると、次式のようになります。

$$L = \frac{2.5V (12V - 2.5V)}{12V \times 600kHz \times 12A \times 0.3} \approx 1\mu H$$

割り当てられた寸法に適合するDC抵抗のできる限り小さい低損失のインダクタを探してください。フェライトコアは多くの場合最良の選択肢ですが、粉末鉄は安価で最高200kHzの周波数で十分に機能します。コアは下記のピークインダクタ電流( $I_{PEAK}$ )で飽和しないように充分に大きくしなければなりません。

$$I_{PEAK} = I_{LOAD(MAX)} \left( 1 + \frac{LIR}{2} \right)$$

大部分のインダクタメーカーは、 $1.0\mu H$ 、 $1.5\mu H$ 、 $2.2\mu H$ 、 $3.3\mu H$ など、標準値のインダクタを提供しています。

また、全入力電圧範囲でLIRのより好ましい妥協点が見出せる非標準の値も探してください。スイングインダクタ(無負荷インダクタンスが電流の増加とともに直線的に

減少する)を使用する場合は、適切に決定したインダクタンス値を用いてLIRを決めてください。

## 入力コンデンサの選択(降圧レギュレータ)

入力コンデンサは、スイッチング電流によって生じる次式のリップル電流( $I_{RMS}$ )要件を満たす必要があります。

$$I_{RMS} = I_{LOAD} \frac{\sqrt{V_{OUT}(V_{IN} - V_{OUT})}}{V_{IN}}$$

$I_{RMS}$ は、 $V_{IN} = 2 \times V_{OUT}$ のときに $I_{LOAD}/2$ の最大値を取ります。ほとんどのアプリケーションでは、タンタル以外のコンデンサ(セラミック、アルミ、POS、またはOSCON)が推奨されます。その理由は、入力と直列に機械的スイッチやコネクタが接続されたシステムに典型的な、電源投入時のサージ電流に対する耐性によります。MAX8550/MAX8551が2段電力変換システムの2段目として動作する場合は、タンタル入力コンデンサを使用することができます。1段目、2段目のいずれの構成においても、最適な信頼性と寿命の面を考慮して、RMS入力電流による温度上昇が10度以下となるコンデンサを選定してください。

## 出力コンデンサの選択(降圧レギュレータ)

出力フィルタコンデンサは、出力リップルと過渡負荷の要件を満たすためには等価直列抵抗( $R_{ESR}$ )が十分に低く、しかし安定度の要件を満たすためには十分に高い値でなければなりません。

プロセッサコア用電圧コンバータや出力が激しい負荷変動にさらされるアプリケーションでは、負荷過渡変動によって生じる過度の出力低下を防止するために必要とする $R_{ESR}$ の値を確保できる値の出力コンデンサとしなければなりません。コンデンサの値が有限であることに起因するサグを無視すると、必要とする $R_{ESR}$ は次式で表わされます。

$$R_{ESR} \leq \frac{V_{STEP}}{\Delta I_{LOAD(MAX)}}$$

大きくて速い過渡負荷変動のないアプリケーションでは、出力コンデンサの値が出力電圧リップルの許容レベルを維持するために必要とする $R_{ESR}$ の大きさに左右されることが少なくありません。降圧コントローラの出力リップル電圧は、全インダクタリップル電流に出力コンデンサの $R_{ESR}$ を乗じた値にほぼ等しくなります。このため、リップル仕様を満たすために必要な最大の $R_{ESR}$ は、次式で表わされます。

$$R_{ESR} \leq \frac{V_{RIPPLE}}{I_{LOAD(MAX)} \times LIR}$$

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

実際に必要とするコンデンサの値は、コンデンサの化学的性質だけでなく、低ESRを実現するために必要な物理的サイズにも関係します。そのため、コンデンサは、一般に、値よりはむしろESRと電圧定格によって選択されます(これは、タンタル、OSCON、ポリマー、及びその他の誘電体についても同様です)。

セラミックコンデンサなどの小容量のフィルタコンデンサを使用する場合、その大きさは、通常、過渡負荷中に $V_{SAG}$ や $V_{SOAR}$ から生じる問題の防止に必要な性能によって決まります。一般に、いつたんオーバーシュートの要件を満たすために十分な大きさのコンデンサを接続しておくと、負荷の立上りエッジのアンダーシュートは問題ではなくなります(「過渡応答」の項 $V_{SAG}$ 及び $V_{SOAR}$ の式参照)。しかし、小容量フィルタコンデンサは、通常、総合的な安定度に影響する可能性のあるESRに起因する高い周波数のゼロを持っています(「安定性の要件」の項参照)。

## 安定性の要件

Quick-PWMコントローラの場合、安定性はスイッチング周波数に相対的なESRゼロ周波数の値によって決まります。不安定性の境界は、次式で表わされます。

$$f_{ESR} \leq \frac{f_{SW}}{\pi}$$

ここで、 $f_{ESR}$ は次の式で計算されます。

$$f_{ESR} = \frac{1}{2\pi \times R_{ESR} \times C_{OUT}}$$

$C_{OUT}$ が、図8の「標準動作回路」に示すように、同じ値を持つ複数のコンデンサで構成される場合、 $f_{ESR}$ はコンデンサが1個の場合の $f_{ESR}$ と同じ値になります。

標準的な600kHzのアプリケーションでは、ESRゼロ周波数は190kHzよりも十分に低いものとし、可能であれば100kHz以下であることが望されます。2個の150 $\mu$ F/4V Sanyo POSコンデンサを使用すると、 $R_{ESR}$ が12m $\Omega$ (max)になります。この場合、ゼロ周波数が42kHzとなり、十分安定な範囲にあります。

大容量のセラミックコンデンサを直接フィードバック検出点に接続する場合は、安定度の確保に注意を払ってください。大容量セラミックコンデンサは、ESRゼロ周波数が高く、不規則で不安定な動作をする可能性があります。しかし、インダクタにできる限り近づけなければならぬフィードバック検出点から数インチ下流にコンデンサを配置し直列抵抗を十分な値まで増やすことは容易です。

不安定な動作は、ダブルパルシングと高速フィードバックループの不安定性が互いに関係しているが、しかし明らかに異なる2つの現象として現れます。ダブルパルシングは、出力にノイズが存在すること、またはESRが小さいために出力電圧信号の中に十分な電圧

傾斜波が得られることにより起ります。400nsの最小オフ時間が経過した直後に、これが原因でエラーコンバレータが「誤って」新たなサイクルをトリガします。ダブルパルシングは、有害というよりも、いやなもので、出力電流リップルの増加のような悪影響は何もありません。しかし、ダブルパルシングは、ESRが十分に大きくなためにループが潜在的に不安定であることを示します。ループが不安定であると、電源や負荷の急変によって出力が発振する可能性があります。このような変動は、普通は減衰しますが、出力電圧が許容範囲を超えて増減する可能性があります。安定性の最も簡単なチェック方法は、負荷をゼロから最大まで急変させて出力電圧リップルの包絡線のオーバーシュートとリンギングを注意深く観察することです。AC電流プローブを使用してインダクタ電流を同時に監視することも役に立ちます。ステップ応答の最初のアンダーシュートやオーバーシュート後に1サイクルを超えるリンギングがあつてはなりません。

## VTT出力コンデンサの選択(LDO)

最大 $\pm 1.5A$ の負荷電流に対してVTT出力を安定化するためには、少なくとも60 $\mu$ Fが必要です。このコンデンサ値を使用すると、レギュレータのユニティゲイン帯域幅周波数が約700kHz(typ)に制限され、安定性に必要な位相余裕が確保されます。このコンデンサがレギュレータ帯域内で確実にその役割を果たすためには、低ESRと低ESLのセラミックコンデンサを使用することが大切です。

また、利得帯域幅は負荷電流とともに増大する出力FETの相互コンダクタンスで決まるため、負荷電流が1.5Aを超える場合は出力コンデンサを60 $\mu$ Fよりも大きくする必要がありますが、最大負荷電流が1.5Aに達しない場合は60 $\mu$ Fよりも小さくすることができます。通常は、次式を用いて出力キャパシタンスの最小容量と最大ESRを選定してください。

$$C_{OUT\_MIN} = 60\mu F \times \sqrt{\frac{I_{LOAD}}{1.5A}}$$

$$R_{ESR\_MAX} = 5m\Omega \times \sqrt{\frac{1.5A}{I_{LOAD}}}$$

$R_{ESR}$ の値は、次の近似式で与えられるユニティゲイン帯域幅周波数で測定されるものとします。

$$f_{GBW} = \frac{40}{C_{OUT}} \times \sqrt{\frac{I_{LOAD}}{1.5A}}$$

安定性に関するこれらの条件が満たされると、電解及びタンタル型を含むコンデンサを(必要に応じて)セラミックコンデンサに並列に追加して、出力のノイズや電圧リップルをさらに抑圧することができます。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## VTTR出力コンデンサの選択(LDO)

VTTRバッファは、出力相互コンダクタンスがVTTレギュレータよりもはるかに小さいVTTレギュレータの縮小版です。したがって、その補償用コンデンサはVTTの場合に比べて小さくて済み、そのESRは大きくとも構いません。最大 $\pm 20\text{mA}$ の負荷電流を必要とする一般的なアプリケーションの場合、最小 $1\mu\text{F}$ のセラミックコンデンサの使用を推奨します( $R_{\text{ESR}} < 0.3\Omega$ )。このコンデンサは、VTTRとアナロググランドプレーンの間に接続してください。

## VTTI入力コンデンサの選択(LDO)

VTTとVTTRの両出力段は、同じVTTI入力から給電されます。これらの出力電圧は、同じREFIN入力を基準にしています。VTTIバイパスコンデンサの値は、VTTIにおけるリップル/ノイズの大きさ、または過渡負荷による電圧ディップの大きさを制限するように選定します。通常、VTTIは、既に大容量コンデンサを備えている降圧レギュレータの出力に接続しますが、さらに、最小 $10\mu\text{F}$ のセラミックコンデンサをVTTI端子のできる限り近くに接続する必要があります。負荷電流が大きい場合や、VTTI端子から電源までのトレースが長くインピーダンスが問題になる場合は、コンデンサの値を増やす必要があります。さらに、望ましくないVTTIバウンスがREFIN入力に結合してループが不安定になるのを防止するため、可能であればREFIN端子はVTTI端子から直接ではなく独立のローインピーダンスDC電源からその信号を分岐するようにしてください。VTTI端子から信号を直接取り出さなければならない場合は、VTTI入力のバイパスコンデンサの大きさを増やし、REFIN端子にさらにバイパスコンデンサを追加してください。

## MOSFETの選択(降圧レギュレータ)

MAX8550/MAX8551は、回路スイッチ素子として外付けされた、ロジックレベルで動作するNチャネルMOSFETを駆動します。重要な選択パラメータとして、以下のものがあります。

**オン抵抗( $R_{\text{DS(ON)}}$ )**：より小さいことが望されます。

**最大ドレイン-ソース間電圧( $V_{\text{DSS}}$ )**：ハイサイドMOSFETのドレインにおける入力電源レールよりも20%以上高いものとしなければなりません。

**ゲート電荷( $Q_{\text{G}}$ 、 $Q_{\text{GD}}$ 、 $Q_{\text{GS}}$ )**：より小さいことが望されます。

$V_{\text{GS}} = 4.5\text{V}$ において $R_{\text{DS(ON)}}$ が定められたMOSFETを選定してください。効率とコストを勘案して、伝導損失が公称入力電圧と最大出力電流におけるスイッチング損失に等しいハイサイドMOSFETを選定してください(下記参照)。ローサイドMOSFETの場合は、ハイサイドMOSFETのターンオンに伴う $dV/dt$ によってローサイドMOSFETが誤ってオンとならないことを確認してください。これは、オンとなると貫通電流により効率が低下するためです。

$Q_{\text{GS}}$ に対する $Q_{\text{GD}}$ の比が小さいMOSFETは、 $dV/dt$ に対する耐性が優れています。

適切な熱管理設計を行うために、目標とする最大動作接合温度、最大出力電流、及びワーストケースの入力電圧における電力損失を計算してください。ローサイドMOSFETの場合は、ワーストケースが $V_{\text{IN}}(\text{MAX})$ において発生します。ハイサイドMOSFETの場合は、ワーストケースが $V_{\text{IN}}(\text{MIN})$ または $V_{\text{IN}}(\text{MAX})$ のいずれかで発生する可能性があります。ハイサイドMOSFETとローサイドMOSFETは、回路動作の違いから損失成分が異なります。ローサイドMOSFETはゼロ電圧スイッチとして動作するため、主な損失は次の通りです。

- チャネル伝導損失( $P_{\text{LSCC}}$ )

- ボディダイオード伝導損失( $P_{\text{LSDC}}$ )

- ゲート駆動損失( $P_{\text{LSDR}}$ )

$$P_{\text{LSCC}} = \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times I_{\text{LOAD}}^2 \times R_{\text{DS(ON)}}$$

この式における $R_{\text{DS(ON)}}$ は $T_{\text{J}}(\text{MAX})$ における値を使用してください。

$$P_{\text{LSDC}} = 2I_{\text{LOAD}} \times V_{\text{F}} \times t_{\text{DT}} \times f_{\text{SW}}$$

ここで、 $V_{\text{F}}$ はボディダイオードの順方向電圧降下、 $t_{\text{DT}}$ はデッドタイム(約30ns)、 $f_{\text{SW}}$ はスイッチング周波数です。ローサイドMOSFETはゼロ電圧スイッチ動作をするため、そのゲート駆動損失は入力キャパシタンス( $C_{\text{ISS}}$ )の充放電の結果として発生します。この損失は、平均のDLゲートドライバのプルアップ及びプルダウン抵抗、 $R_{\text{DL}}$ (約1Ω)、及びMOSFETの内部ゲート抵抗( $R_{\text{GATE}}$ 、約2Ω)の中に分布して存在します。駆動電力損失は、次式で表われされます。

$$P_{\text{LSDR}} = C_{\text{ISS}} \times V_{\text{GS}}^2 \times f_{\text{SW}} \times \frac{R_{\text{GATE}}}{R_{\text{GATE}} + R_{\text{DL}}}$$

ハイサイドMOSFETはデューティサイクルの制御スイッチとして動作し、主な損失は次の通りです。

- チャネル伝導損失( $P_{\text{HSCC}}$ )

- VI重畠スイッチング損失( $P_{\text{HSSW}}$ )

- 駆動損失( $P_{\text{HSDR}}$ )

(ハイサイドMOSFETにはボディダイオード伝導損失がありません。このダイオードには電流が流れないとします。)

$$P_{\text{HSCC}} = \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times I_{\text{LOAD}}^2 \times R_{\text{DS(ON)}}$$

この式の $R_{\text{DS(ON)}}$ は $T_{\text{J}}(\text{MAX})$ における値を使用してください。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

$$P_{HSSW} = V_{IN} \times I_{LOAD} \times f_{SW} \times \frac{Q_{GS} + Q_{GD}}{I_{GATE}}$$

ここで、 $I_{GATE}$ は次式で決まる平均DHドライバ出力電流です。

$$I_{GATE(ON)} = \frac{2.5V}{R_{DH} + R_{GATE}}$$

ここで、 $R_{DH}$ はハイサイドMOSFETドライバのオン抵抗( $1\Omega$ 、typ)で、 $R_{GATE}$ はMOSFETの内部ゲート抵抗(約 $2\Omega$ )です。

$$P_{HSDR} = Q_G \times V_{GS} \times f_{SW} \times \frac{R_{GATE}}{R_{GATE} + R_{DH}}$$

ここで、 $V_{GS} = V_{DD} = 5V$ です。上記の損失以外に、MOSFETの出力キャパシタンス及びMOSFETのデータシートに明記されていないハイサイドMOSFETの中で消費されるローサイドMOSFETのボディダイオード逆回復電荷があるため、損失として約20%を追加してください。熱抵抗の仕様についてはMOSFETのデータシートを参照し、先に求めた電力損失を用いて目標の最大動作接合温度を維持するために必要とするプリント基板の放熱面積を計算してください。スイッチングノイズによって発生するEMIを低減するためには、 $0.1\mu F$ のセラミックコンデンサをハイサイドスイッチのドレインとローサイドスイッチのソースの間に接続するか、またはDH及びDLと直列に抵抗器を接続してスイッチング遷移を緩やかにしてください。直列抵抗器を接続するとMOSFETの電力損失が増加するため、MOSFETが過熱することがないようにしてください。

## MOSFETスナバ回路(ステップダウン)

スイッチングノードには寄生インダクタンスとキャパシタンスで形成される共振回路が存在するため、高速スイッチング遷移によってリングングが発生します。この高周波のリングングは、LXの立上り及び立下り遷移で発生し、回路性能を低下させ、EMIを発生する可能性があります。このリングングを減衰させるために、直列RCスナバ回路を各スイッチの両端に接続することができます。スナバ回路の直列RCの値を選択する簡単な手順を以下に示します。

- 1) PGND1に対する $V_{LX}$ (LX端子の電圧)を測定するためにオシロスコープのプローブをLXに接続してリングング周波数 $f_R$ を観察してください。

- 2) コンデンサをLXとPGND1間に接続した場合にリングング周波数が半分に減るコンデンサの値を見つけて、LXにおける回路の寄生キャパシタンス( $C_{PAR}$ )を推定してください。この方法により見つかったコンデンサの値の1/3の値として $C_{PAR}$ を計算することができます。

- 3) 次式を使って回路の寄生インダクタンス( $L_{PAR}$ )を推定してください。

$$L_{PAR} = \frac{1}{(2\pi \times f_R)^2 \times C_{PAR}}$$

- 4) 式 $R_{SNUB} = 2\pi \times f_R \times L_{PAR}$ により、臨界制動に対応する抵抗器の値( $R_{SNUB}$ )を計算してください。目標とする制動とピーク電圧振幅を満たすように抵抗器の値を調整してください。

- 5) コンデンサ( $C_{SNUB}$ )を有効とするためには、その値を $C_{PAR}$ の値の少なくとも2~4倍としてください。

スナバ回路の電力損失( $P_{RSNUB}$ )は、抵抗器の中で消費され、次式に従って計算することができます。

$$P_{RSNUB} = C_{SNUB} \times V_{IN}^2 \times f_{SW}$$

ここで、 $V_{IN}$ は入力電圧で、 $f_{SW}$ はスイッチング周波数です。電力損失の計算値に対しては、個々のアプリケーションにおける軽減ルールを適用して $R_{SNUB}$ の電力定格を決定してください。

## 電流制限値の設定(降圧レギュレータ)

MAX8550/MAX8551に使用する電流検出方法では、ローサイドMOSFET(「標準動作回路」のQ2)のオン抵抗( $R_{DS(ON)}$ )が利用されます。電流制限値を計算するとき、MOSFETのデータシートから $R_{DS(ON)}$ に関するワーストケースの最大値を使用し、温度による $R_{DS(ON)}$ の増大を余裕として加えてください。一般には、 $1^{\circ}\text{C}$ の温度上昇につき0.5%の抵抗増加を見込みます。

最小電流制限スレッショルドは、電流制限が最小許容値にあるときに最大負荷電流を流すことができるよう充分に大きくなければなりません。インダクタ電流の谷は、 $I_{LOAD(MAX)}$ からリップル電流の半分を差し引いたところにあります。したがって、

$$I_{LIM(VAL)} > I_{LOAD(MAX)} - \left( \frac{I_{LOAD(MAX)} \times LIR}{2} \right)$$

ここで、 $I_{LIM(VAL)}$ は、最小谷電流制限スレッショルド電圧をQ2のオン抵抗( $R_{DS(ON)Q2}$ )で割った値に等しくなります。50mVのデフォルト設定の場合は、ILIMを $A_{VDD}$ に接続してください。可変モードでは、谷電流制限スレッショルドはILIMに現れる電圧のちょうど $1/10^*$ です。可変スレッショルドとするためには、抵抗分圧器をREFとGND間に接続して、そのセンタータップをILIMに接続してください。外部における250mV~2Vの調整範囲は、25mV~200mVの谷電流制限スレッショルドに対応します。電流制限値を調整する際は、1%許容差の抵抗器を使用し、およそ $10\mu\text{A}$ を分圧器に流して、谷電流制限値に大きい誤差が生じないようにしてください。

\* 負方向では、可変電流制限値はILIMに現れる電圧の-1/8(標準値)としてあります。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

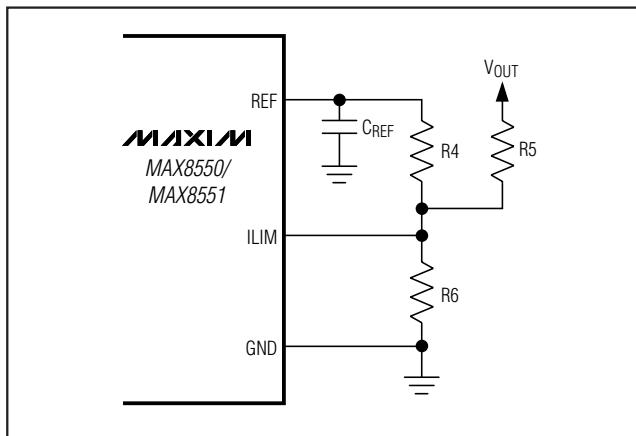

## フの字電流制限

UVPラッチオプションが利用不可能な場合に、代わりにフの字電流制限を利用することができます。フの字電流制限機能は、外付け部品が無期限の過負荷と短絡に耐えることができるよう、外付け部品の電力損失を低減し、過負荷や短絡が取り除かれると自動的に復元します。フの字電流制限を利用するためには、図7に示すように、可変電流制限値の設定に使用される抵抗分圧器回路(R4とR5)の他に抵抗器(図7と「標準動作回路」のR6)をV<sub>OUT</sub>とILIMの間に接続してください。

以下に、R4、R5、及びR6の値の計算手順を示します。

- 1) 出力電圧が公称値のときILIMに必要な電圧V<sub>ILIM(NOM)</sub>を次の式を使って計算してください。

$$V_{ILIM(NOM)} = 10 \times I_{LOAD(MAX)} \times \left( 1 - \frac{LIR}{2} \right) \times R_{DS(ON)Q2}$$

- 2) フの字制限電流のパーセンテージPFBを15%~40%の範囲から選択してください。

- 3) 出力が短絡されている(0V)ときの電圧V<sub>ILIM(OV)</sub>を次の式を使って計算してください。

$$V_{ILIM(OV)} = P_{FB} \times V_{ILIM(NOM)}$$

- 4) R4の値は、次式に従って計算することができます。

$$R4 = \frac{2V - V_{ILIM(OV)}}{10\mu A}$$

- 5) R56として示すR5とR6の並列抵抗は、次式に従って計算することができます。

$$R56 = \left( \frac{2V}{10\mu A} \right) - R4$$

- 6) つぎに、R6は次式に従って計算することができます。

$$R6 = \frac{V_{OUT} \times R4 \times R56}{\left[ \left( V_{OUT} - (V_{ILIM(NOM)} - V_{ILIM(OV)}) \right) \times R4 - \left( (V_{ILIM(NOM)} - V_{ILIM(OV)}) \times R56 \right) \right]}$$

- 7) つぎに、R5を次式に従って計算します。

$$R5 = \frac{R6 \times R56}{R6 - R56}$$

## ブースト電源ダイオード及び コンデンサの選択(降圧レギュレータ)

Central Semiconductor製CMDSH-3などの低電流ショットキダイオードは、多くのアプリケーションで十分に機能します。大型パワーダイオードは使用しないでください。大きな接合キャパシタンスがBST端子の電圧をLXの電圧まで充電する可能性があり、これによって6Vの絶対最大定格を超えるためです。ブーストコンデンサは、入力及び出力電圧、外付け部品、ならびにプリント基板のレイアウトに応じて0.1μF~4.7μFとします。ブーストコンデンサは、過大な電圧に充電されないようにできる限り大きい値にすべきですが、最大動作デューティサイクル(これは、最小入力電圧で起こります)で発生するローサイドMOSFETの最小導通時間中に十分に充電が可能となる小さな値としなければなりません。さらに、ハイサイドMOSFETが最小オン抵抗を持つように完全導通させるために必要な最小ゲート-ソース間電圧以下までブーストコンデンサが放電しないようにしてください。この最小ゲート-ソース間電圧(V<sub>GS(MIN)</sub>)は、次式によって決まります。

図7. フの字電流制限

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

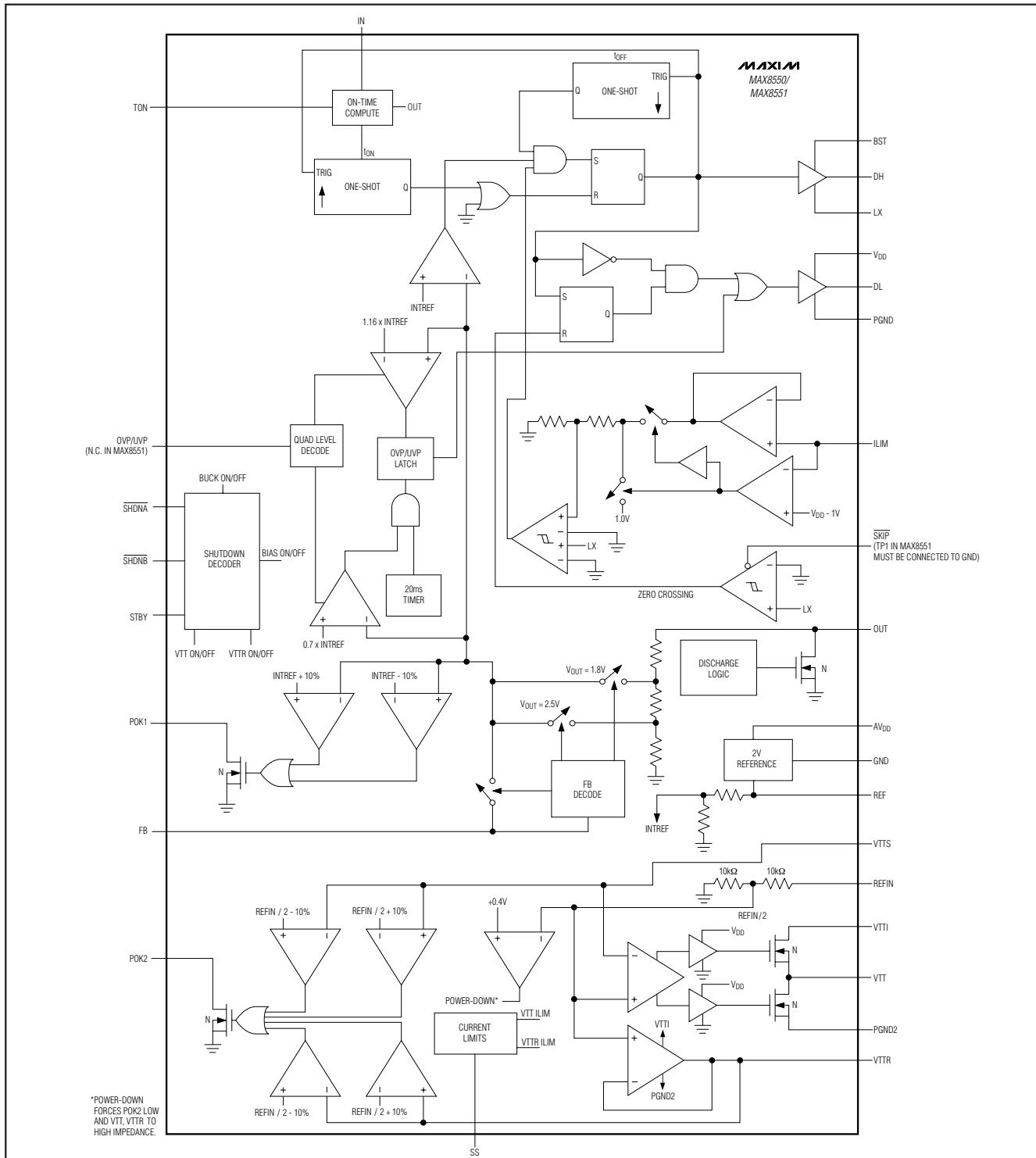

## MAX8550/MAX8551

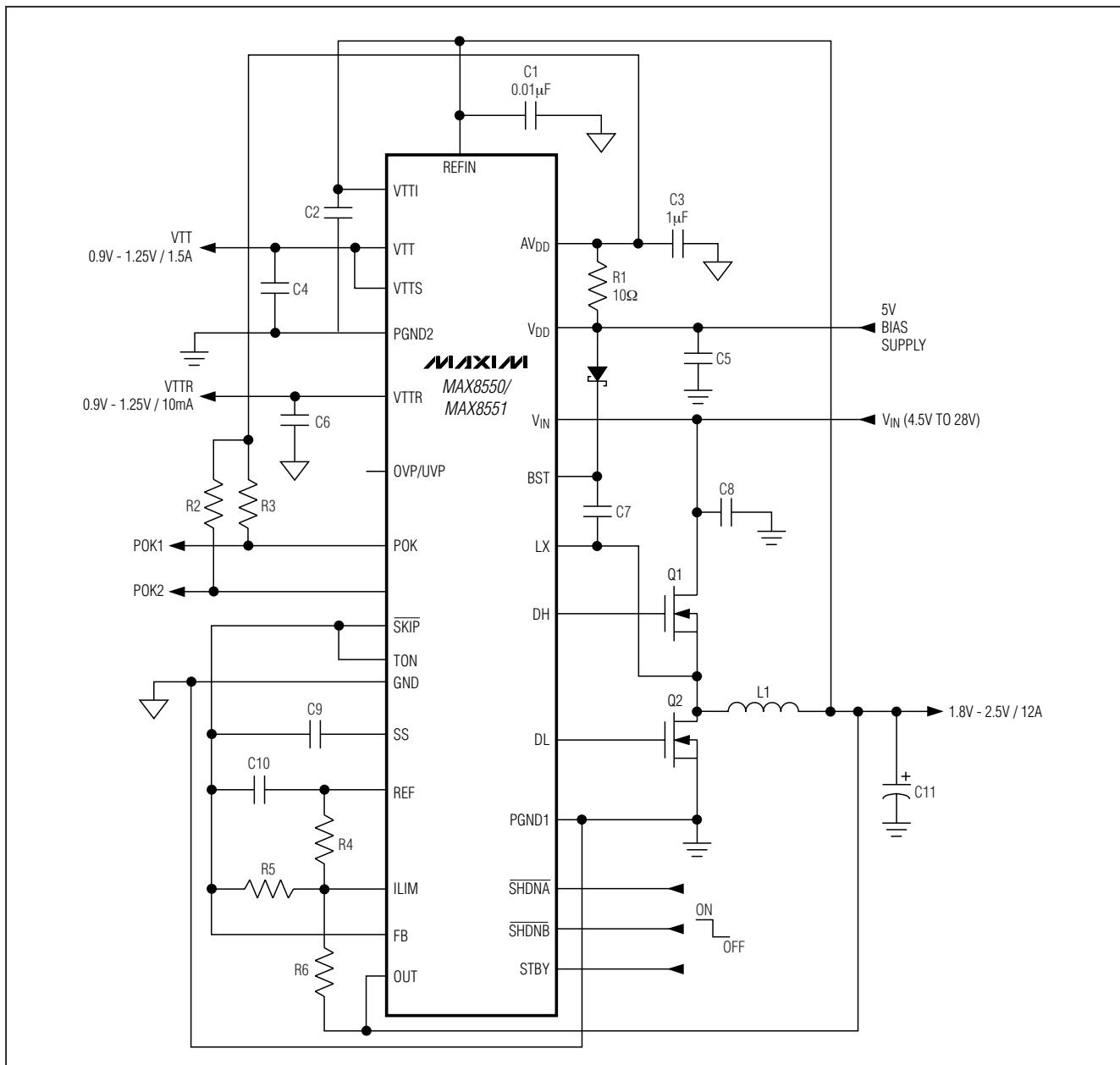

図8. 標準動作回路

$$V_{GS(MIN)} = V_{DD} \times \frac{Q_G}{C_{BOOST}}$$

ここで、 $V_{DD}$ は5V、 $Q_G$ はハイサイドMOSFETの全ゲート電荷、 $C_{BOOST}$ はブースト用コンデンサ(図8の「標準動作回路」のC7)の値です。

### 過渡応答(降圧レギュレータ)

インダクタのリップル電流も、特に $V_{IN}$ と $V_{OUT}$ 間の電位差が小さい場合には、過渡応答性能に影響します。小インダクタ値を使用すると、インダクタ電流の変化が速くなり、負荷の急変によって出力フィルタコンデンサから流出した電荷を補給することができます。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

また、出力サグは、最大デューティ比の関数で、オン時間と最小オフ時間から次式によって計算することができます。

$$V_{SAG} = \frac{L \times \Delta I_{LOAD(MAX)}^2 \left[ \frac{V_{OUT} \times K}{V_{IN}} + t_{OFF(MIN)} \right]}{2C_{OUT} \times V_{OUT} \left[ \frac{(V_{IN} - V_{OUT}) \times K}{V_{IN}} + t_{OFF(MIN)} \right]}$$

ここで、 $t_{OFF(MIN)}$ は最小オフ時間(「Electrical Characteristics」参照)で、Kは表1の値です。

蓄積されたインダクタエネルギーに起因する最大負荷から無負荷に遷移する際のオーバーシュートは、次式に従って計算することができます。

$$V_{SOAR} = \frac{\Delta I_{LOAD(MAX)}^2 \times L}{2 \times C_{OUT} \times V_{OUT}}$$

## アプリケーション情報

### ドロップアウト性能(降圧レギュレータ)

連続伝導動作の場合の出力電圧可変範囲は、固定の最小オフ時間ワンショットによって制限されます。最良のドロップアウト性能を得るためにには、より遅い(200kHz)オン時間設定としてください。低い入力電圧で使用する場合は、デューティ比の限界をオン及びオフ時間のワーストケース値を使用して計算する必要があります。製造誤差と内部伝播遅延は、TONを決めるKファクタに誤差をもたらします。この誤差は高周波で大きくなります(表1参照)。また、降圧レギュレータをドロップアウトのきわめて近くで使用すると過渡応答性能が悪化するため、通常は大容量の出力コンデンサを追加する必要があります(「設計手順」の項の $V_{SAG}$ 式参照)。

絶対最小ドロップアウトポイントは、最小オフ時間に直線的に減少するインダクタ電流の変化量( $\Delta I_{DOWN}$ )が、オン時間に直線的に増加するインダクタ電流の変化量( $\Delta I_{UP}$ )に等しくなる点です。比 $h = \Delta I_{UP}/\Delta I_{DOWN}$ は、負荷の増大に対応してインダクタ電流をより大きく変化させるコントローラの能力を示すもので、常に1よりも大きなければなりません。 $h$ が絶対最小ドロップアウトポイントである1に近づくと、インダクタ電流は各スイッチングサイクルで実質的に増加することができます、出力キャパシタンスを追加しない限り $V_{SAG}$ が著しく増大します。 $h$ の適正な最小値は1.5ですが、この値の調整は $V_{SAG}$ 、出力キャパシタンス、及び最小動作電圧の間のトレードオフとなります。 $h$ の値を決めると最小動作電圧は、次式に従って計算することができます。

$$V_{IN(MIN)} = \left[ \frac{V_{OUT} \times V_{DROP1}}{1 - \left( \frac{h \times t_{OFF(MIN)}}{K} \right)} \right] + V_{DROP2} - V_{DROP1}$$

ここで、 $V_{DROP1}$ と $V_{DROP2}$ は、放電及び充電回路の寄生電圧降下(「オン時間ワンショット(TON)」の項参照)、 $t_{OFF(MIN)}$ は「Electrical Characteristics」の値で、Kは表1の値です。絶対最小入力電圧は、 $h=1$ として計算します。

$V_{IN(MIN)}$ の計算値が、必要とする最小入力電圧よりも大きい場合は、許容できる $V_{SAG}$ とするためには、動作周波数を下げるか、または出力キャパシタンスを追加する必要があります。ドロップアウトに近い動作が予想される場合は、適切な過渡応答を確保するために $V_{SAG}$ を計算してください。

ドロップアウトの設計例を以下に示します。

$$V_{OUT} = 2.5V$$

$$f_{SW} = 600kHz$$

$$K = 1.7\mu s$$

$$t_{OFF(MIN)} = 450ns$$

$$V_{DROP1} = V_{DROP2} = 100mV$$

$$h = 1.5$$

$$V_{IN(MIN)} = \left[ \frac{2.5V + 0.1V}{1 - \left( \frac{1.5V \times 450ns}{1.7\mu s} \right)} \right] + 0.1V - 0.1V = 4.3V$$

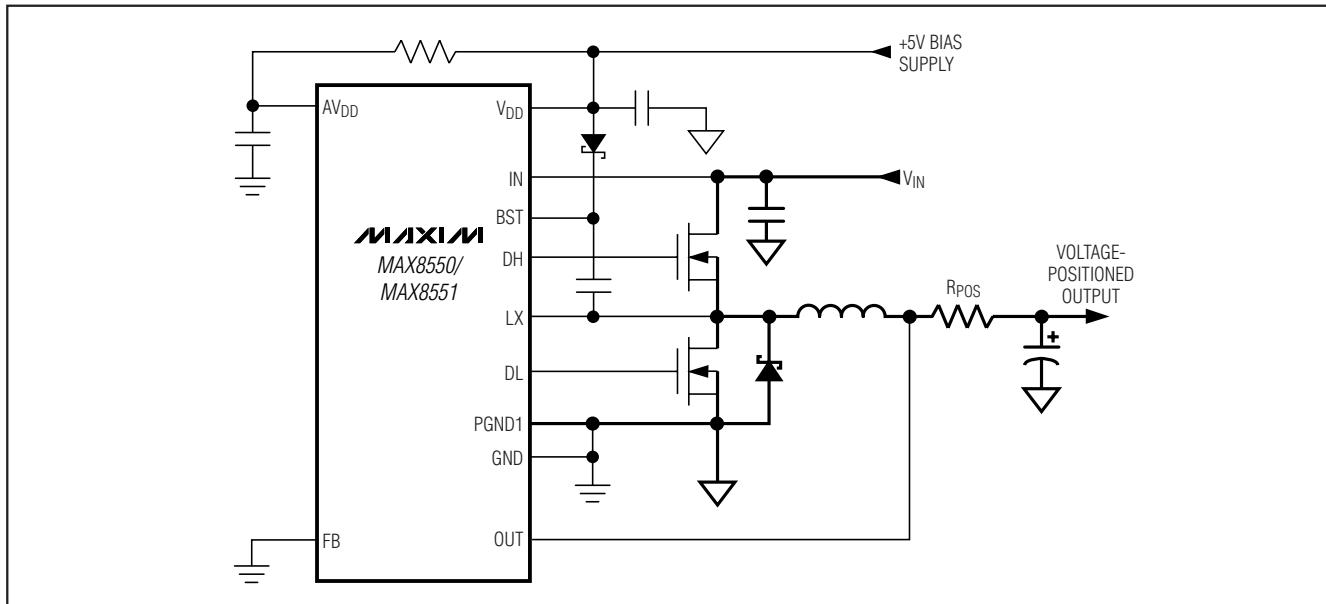

### 電圧ポジショニング(降圧レギュレータ)

高速の過渡負荷が発生するアプリケーションでは、出力電圧が $R_{ESR} \times C_{OUT} \times \Delta I_{LOAD}$ だけ瞬時に変化します。電圧ポジショニングでは、このようなアプリケーションに使用する出力コンデンサの数をより少なくすることができます、許容範囲の厳しいアプリケーションにおける出力電圧のAC及びDC許容ウインドウを最大にすることができます。

図9は、電圧ポジショニングを行う回路のOUTとFBの接続を示します。電圧ポジショニングのない回路では、MAX8550/MAX8551が出力コンデンサ電圧の位置で電圧を安定化します。電圧ポジショニングを行う回路では、MAX8550/MAX8551は電圧ポジショニング抵抗器のインダクタ側の電圧を安定化します。このようにすると、 $V_{OUT}$ は次式のよう減少します。

$$V_{OUT(VPS)} = V_{OUT(NO\_LOAD)} - R_{POS} \times I_{LOAD}$$

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

図9. 電圧ポジショニング出力

## プリント基板レイアウト指針

低損失のスイッチングとノイズのない安定な動作を実現するためには、プリント基板を注意深くレイアウトすることがきわめて重要です。スイッチング電力段には特別な注意を要します。可能であれば、グランド端子を互いに同一面にして電力部品すべてを基板の上側に実装してください。プリント基板のレイアウトを適正に行なうために、以下の指針に従ってください。

- 特にグランド端子では、大電流経路を短くしてください。

この方法は、安定でジッタのない動作に不可欠です。

- 電源トレースと負荷の接続部を短くしてください。

この方法は、高効率を得るために不可欠です。肉厚銅箔のプリント基板(1オンスでなく2オンス)を使用すると、最大負荷における効率を1%以上改善することができます。プリント基板のトレースを適正に配置することは、ミリ単位で取り組むべき困難な作業で、この場合、トレース抵抗が $1\text{m}\Omega$ 増えただけで効率の低下を無視することができなくなります。

- 電流検出用ローサイドMOSFETへのLXとPGND1の接続部には、ケルビン検出接続を使用する必要があります。

- トレースの長さにトレードオフが必要な場合、インダクタの充電経路が放電経路よりも長くなることは許容されます。たとえば、入力コンデンサとハイサイドMOSFETの間の距離は、インダクタとローサイドMOSFETの間、またはインダクタと出力フィルタコンデンサの間の距離よりも幾分長くなることは許容されます。

- 高速スイッチングノード(BST、LX、DH、及びDL)は、敏感なアナログ領域(REF、FB、及びILIM)から離して経路を定めてください。

- 入力セラミックコンデンサは、ハイサイドMOSFETのドレインとローサイドMOSFETのソースにできる限り近づけて配置する必要があります。入力コンデンサ端子とMOSFETの間のインピーダンスができる限り小さくなるようにMOSFETの位置を決めてください。

## LDOセクションのレイアウトに関する特別な配慮

VTTのコンデンサ(1個または複数)は、VTTとPGND2(ピン12と11)にできる限り近づけて配置し、トレースの直列抵抗/インダクタンスを最小限に抑えなければなりません。コンデンサのPGND2側は、短くして、ICの下のエクスポートドパッドまでをローインピーダンス経路とする必要があります。エクスポートドパッドは、GND(ピン24)、PGND1(ピン23)、及びPGND2(ピン11)に對してスター接続としなければなりません。コンデンサのVTT側の出力電圧をVTTs(ピン9)に戻すために使用するトレースは、幅を狭くすることができます。ただし、このトレースは、PGND1やPGND2などノイズの多くながりがちな信号から十分に遠ざけてください。このようにすることで、エラーアンプ入力へのノイズの侵入を防ぐことができます。最良の性能を得るために、VTTI用のバイパスコンデンサをVTTI(ピン13)にできる限り近づけて配置する必要があります。REFIN(ピン14)は、ノイズの無いトレースを使用して経路を分離し、GNDに對して確実にバイパスしなければなりません。プリント基板設計の指針については、MAX8550評価キットのデータシートを参照してください。

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

## **MAX8550/MAX8551**

## 標準動作回路

## チップ情報

TRANSISTOR COUNT: 5100

## PROCESS: BiCMOS

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

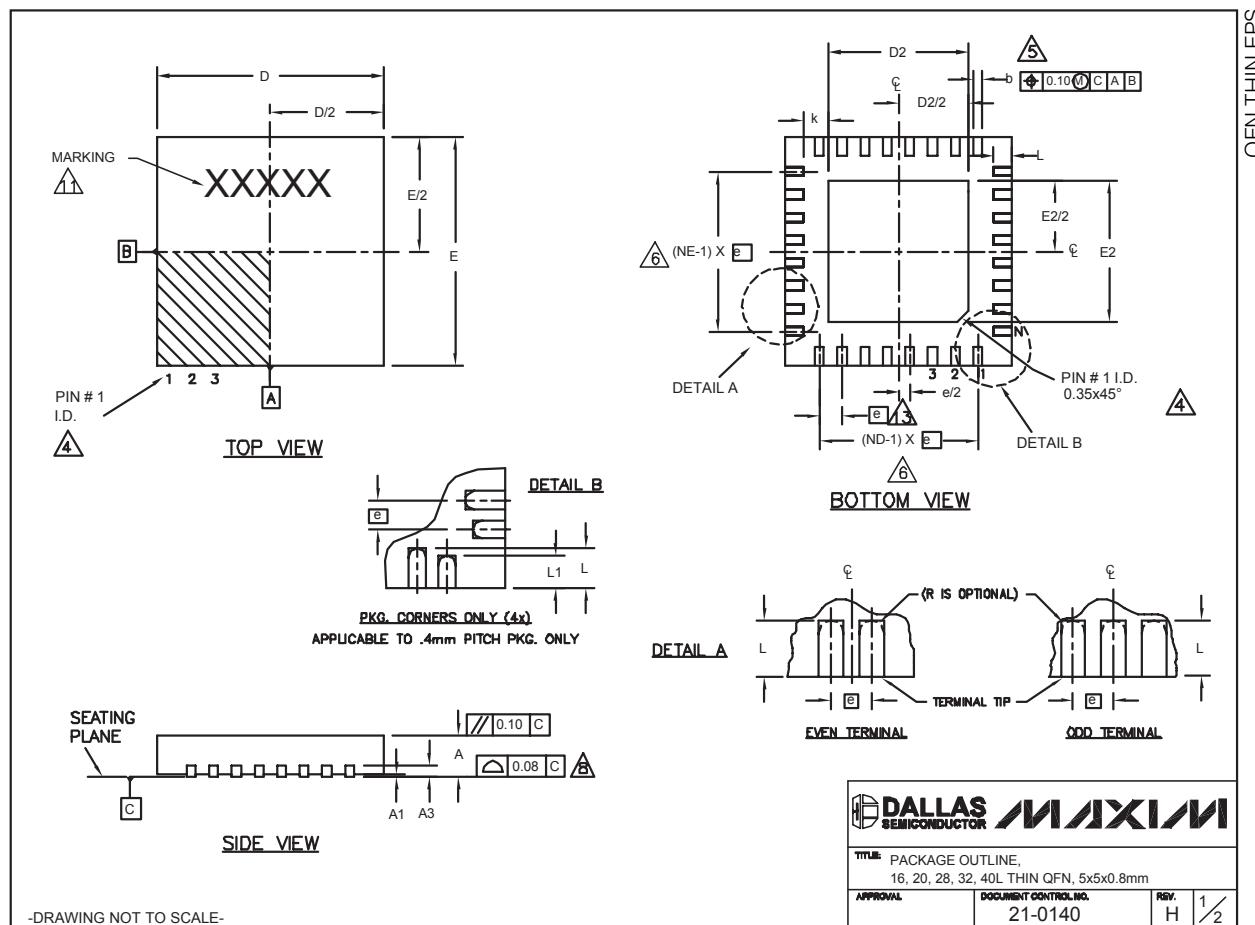

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

# デスクトップ、ノートブック、及びグラフィックカード用 DDR電源ソリューション

MAX8550/MAX8551

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

| COMMON DIMENSIONS |         |      |      |         |        |      |         |      |       |         |      |      |         |      |      |

|-------------------|---------|------|------|---------|--------|------|---------|------|-------|---------|------|------|---------|------|------|

| PKG.<br>SYMBOL    | 16L 5x5 |      |      | 20L 5x5 |        |      | 28L 5x5 |      |       | 32L 5x5 |      |      | 40L 5x5 |      |      |

|                   | MIN.    | NOM. | MAX. | MIN.    | NOM.   | MAX. | MIN.    | NOM. | MAX.  | MIN.    | NOM. | MAX. | MIN.    | NOM. | MAX. |

| A                 | 0.70    | 0.75 | 0.80 | 0.70    | 0.75   | 0.80 | 0.70    | 0.75 | 0.80  | 0.70    | 0.75 | 0.80 | 0.70    | 0.75 | 0.80 |

| A1                | 0       | 0.02 | 0.05 | 0       | 0.02   | 0.05 | 0       | 0.02 | 0.05  | 0       | 0.02 | 0.05 | 0       | 0.02 | 0.05 |

| A3                | 0.20    | REF. | 0.20 | REF.    | 0.20   | REF. | 0.20    | REF. | 0.20  | REF.    | 0.20 | REF. | 0.20    | REF. | 0.20 |

| b                 | 0.25    | 0.30 | 0.35 | 0.25    | 0.30   | 0.35 | 0.20    | 0.25 | 0.30  | 0.20    | 0.25 | 0.30 | 0.15    | 0.20 | 0.25 |

| D                 | 4.90    | 5.00 | 5.10 | 4.90    | 5.00   | 5.10 | 4.90    | 5.00 | 5.10  | 4.90    | 5.00 | 5.10 | 4.90    | 5.00 | 5.10 |

| E                 | 4.90    | 5.00 | 5.10 | 4.90    | 5.00   | 5.10 | 4.90    | 5.00 | 5.10  | 4.90    | 5.00 | 5.10 | 4.90    | 5.00 | 5.10 |

| e                 | 0.80    | BSC. | 0.65 | BSC.    | 0.50   | BSC. | 0.50    | BSC. | 0.40  | BSC.    | 0.40 | BSC. | 0.40    | BSC. | 0.40 |

| k                 | 0.25    | -    | -    | 0.25    | -      | -    | 0.25    | -    | -     | 0.25    | 0.35 | 0.45 | -       | -    | -    |

| L                 | 0.30    | 0.40 | 0.50 | 0.45    | 0.55   | 0.65 | 0.45    | 0.55 | 0.65  | 0.30    | 0.40 | 0.50 | 0.40    | 0.50 | 0.60 |

| L1                | -       | -    | -    | -       | -      | -    | -       | -    | -     | -       | -    | -    | 0.30    | 0.40 | 0.50 |

| N                 | 16      |      | 20   |         | 28     |      | 32      |      | 40    |         |      |      |         |      |      |

| ND                | 4       |      | 5    |         | 7      |      | 8       |      | 10    |         |      |      |         |      |      |

| NE                | 4       |      | 5    |         | 7      |      | 8       |      | 10    |         |      |      |         |      |      |

| JEDEC             | WHHB    |      | WHHC |         | WHHD-1 |      | WHHD-2  |      | ----- |         |      |      |         |      |      |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |                          |     |

|------------------------|------|------|------|------|------|------|--------------------------|-----|

| PKG.<br>CODES          | D2   |      | E2   |      | L    |      | DOWN<br>BONDS<br>ALLOWED |     |

|                        | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |                          |     |

| T1655-1                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | NO  |

| T1655-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | YES |

| T1655N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | NO  |

| T2055-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | NO  |

| T2055-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | YES |

| T2055-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | NO  |

| T2055-5                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 | 0.40                     | YES |

| T2855-1                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 | **                       | NO  |

| T2855-2                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 | **                       | NO  |

| T2855-3                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 | **                       | YES |

| T2855-4                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 | **                       | YES |

| T2855-5                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 | **                       | NO  |

| T2855-6                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 | **                       | NO  |

| T2855-7                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 | **                       | YES |

| T2855-8                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 | 0.40                     | YES |

| T2855N-1               | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 | **                       | NO  |

| T3255-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | NO  |

| T3255-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | YES |

| T3255-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | NO  |

| T3255N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 | **                       | NO  |

| T4055-1                | 3.20 | 3.30 | 3.40 | 3.20 | 3.30 | 3.40 | **                       | YES |

\*\* SEE COMMON DIMENSIONS TABLE

NOTES:

1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JEDEC 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

5. DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

8. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR T2855-1, T2855-3, AND T2855-6.