# USB-PD/PPS アプリケーション向けの 2.5V～22V 入力、7.8A スイッチング電流 高効率昇降圧コンバータ

## MAX77859

## 製品のハイライト

- 広い入力電圧範囲：2.5V～22V

- 設定可能な出力電圧

- 内部帰還抵抗を使用する場合は 3.2V～16V

- 外部帰還抵抗を使用する場合は 3.0V～20V (表 1 を参照)

- USB Type-C®給電 (PD) / プログラマブル電源 (PPS)

- 出力電圧ステップ・サイズ：20mV

- 出力電流制限ステップ・サイズ：50mA

- 最大出力電流

- 降圧モード：最大 6A

- 升圧モード：最大 4A ( $V_{IN} = 3.7V$ 、 $V_{OUT} = 5V$ )

- スイッチング電流：7.8A (代表値)

- 自動スキップ・モードと強制 PWM モード

- $R_{SEL}$  設定

- I<sup>2</sup>C インターフェースのターゲット・アドレス

- スイッチング電流制限の閾値

- 内部／外部帰還抵抗

- I<sup>2</sup>C プログラミング

- 出力電圧 (DVS)

- 出力電圧の変化のスルー・レート

- 出力電流制限の閾値

- スイッチング電流制限の閾値

- スイッチング周波数

- 強制 PWM モード (FPWM)

- ループ補償

- パワーOK (POK) およびフォルト・ステータス／割込み

- 出力のアクティブ放電

- オープン・ドレインのステータス／割込み端子

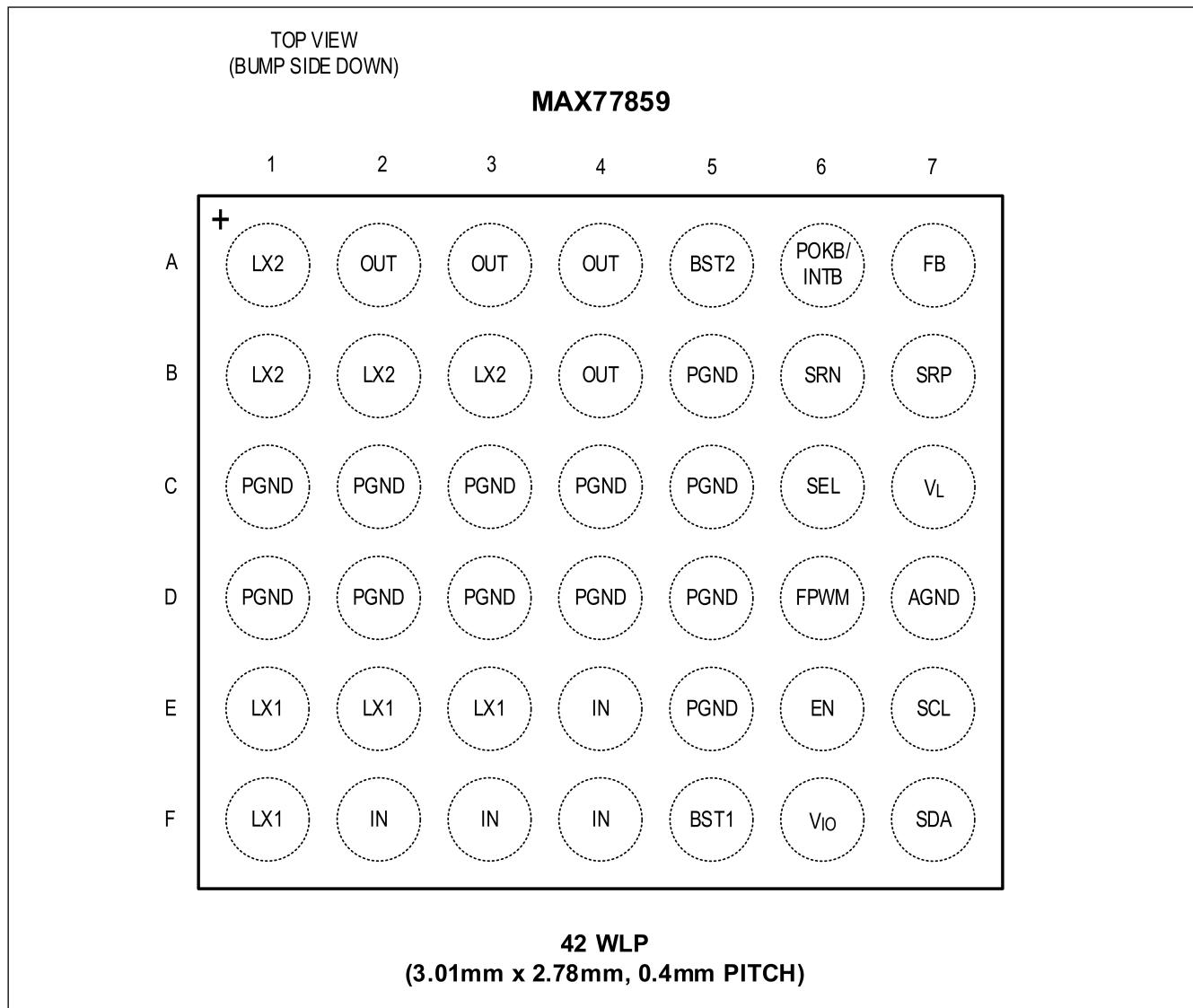

- 3.01mm × 2.78mm の 42 ウェーハ・レベル・パッケージ (WLP) または 4.0mm × 4.0mm の 19 FC2QFN で提供

## 主なアプリケーション

- USB PD 3.0 (PPS) 動的再構成可能プロセッサ (DRP) アプリケーション

従来のウルトラブックのユニバーサル・シリアル・バス (USB) Type-C®ポートの最大出力電力は 5V および 3A での 15W です。MAX77859 では最大 30W の USB PD 出力が可能で、PPS 準拠なので、USB Type-C PD 準拠のスマートフォンや周辺機器の充電速度を倍速にできます。実装すると、ウルトラブックから周辺機器への 15 分間の急速再充電で数時間の動作が可能なので、日中を通じて使用に耐えます。

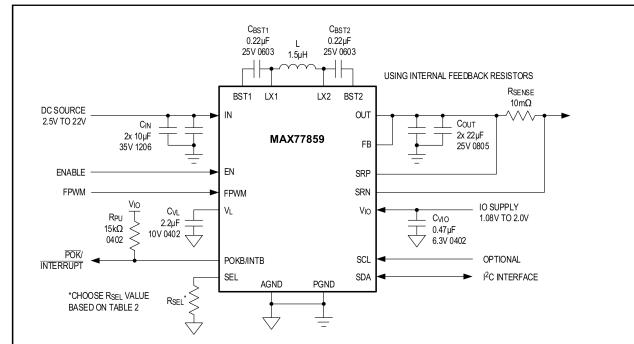

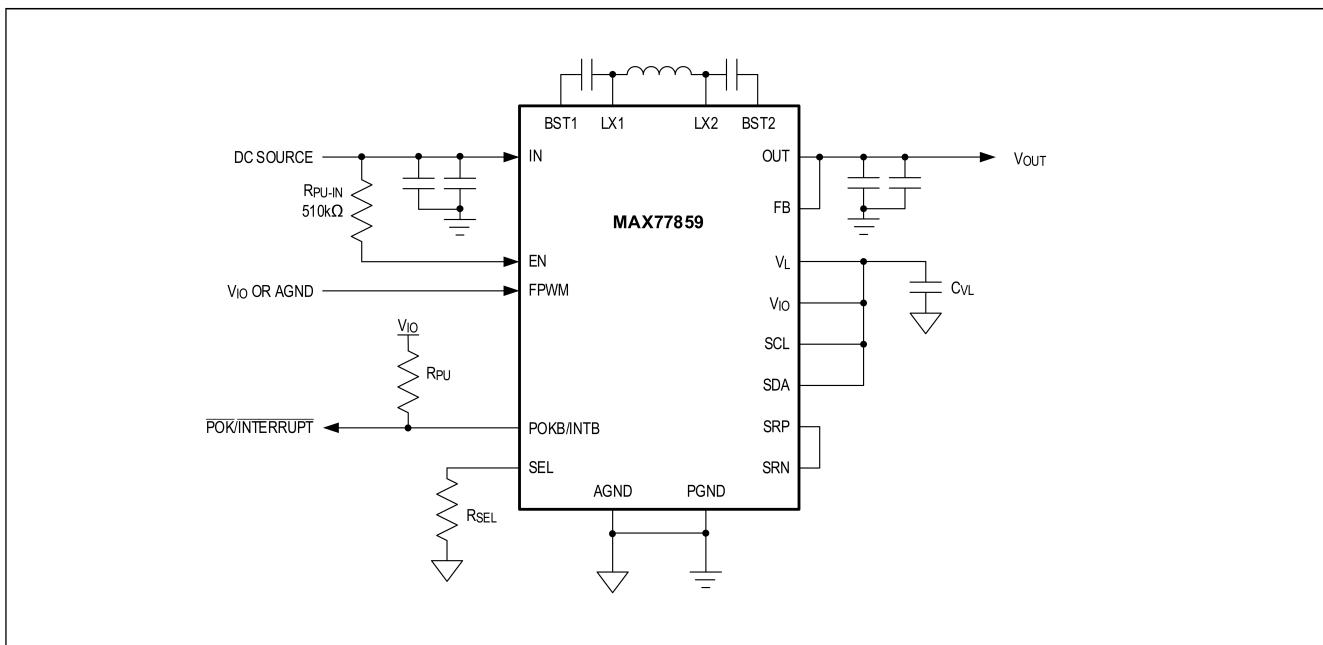

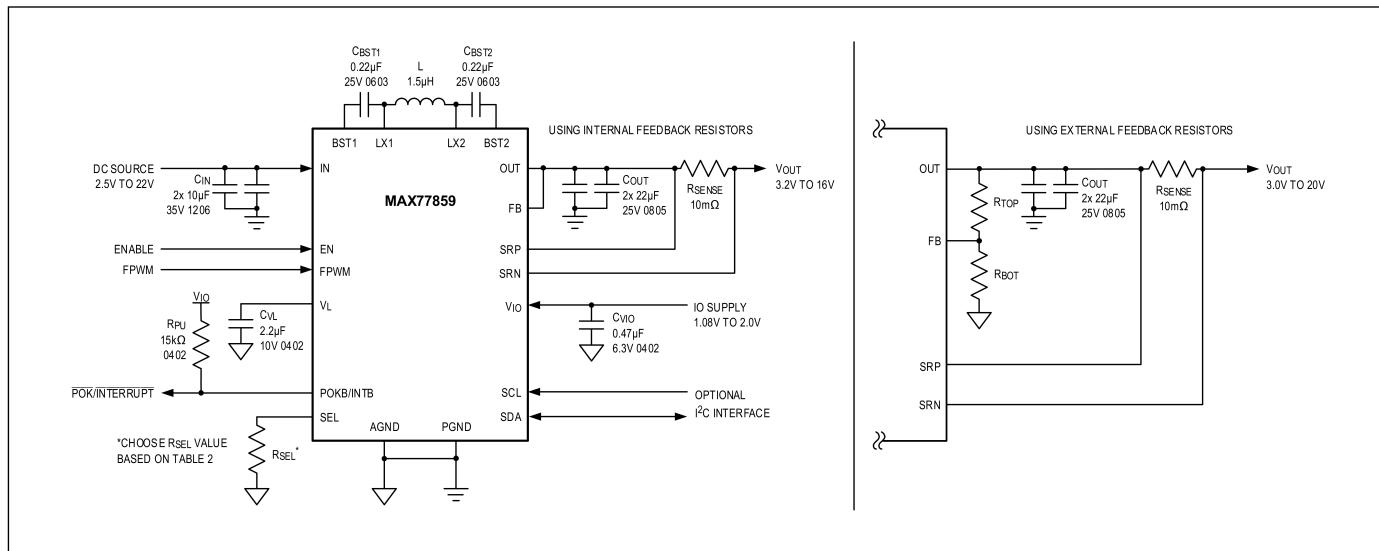

## 簡略アプリケーション回路図

## 端子說明

- スペースに制約のあるアプリケーション

USB-C® PD DRP の設計は複雑で、特にポートの近辺では厳しいスペースの制約があります。USB PD の実現には昇降圧トポジの設計が必要ですが、ソリューション・サイズが決定的なボトルネックになります。MAX77859 は完全統合型の昇降圧コンバータで、同等の出力電力容量のディスクリート構成昇降圧ソリューションと比較すると 80%以上ソリューション・サイズを縮小できます。

USB Type-C と USB-C は USB Implementers Forum の登録商標です。

オーダー情報はデータシート末尾に記載されています。

## 目次

|                                              |    |

|----------------------------------------------|----|

| 製品のハイライト .....                               | 1  |

| 主なアプリケーション .....                             | 1  |

| 簡略アプリケーション回路図 .....                          | 1  |

| 端子説明 .....                                   | 1  |

| 絶対最大定格 .....                                 | 6  |

| 推奨動作条件 .....                                 | 6  |

| パッケージ情報 .....                                | 7  |

| 42 WLP .....                                 | 7  |

| 電気的特性 .....                                  | 8  |

| 電気的特性 – I <sup>2</sup> C シリアル・インターフェース ..... | 12 |

| 標準動作特性 .....                                 | 15 |

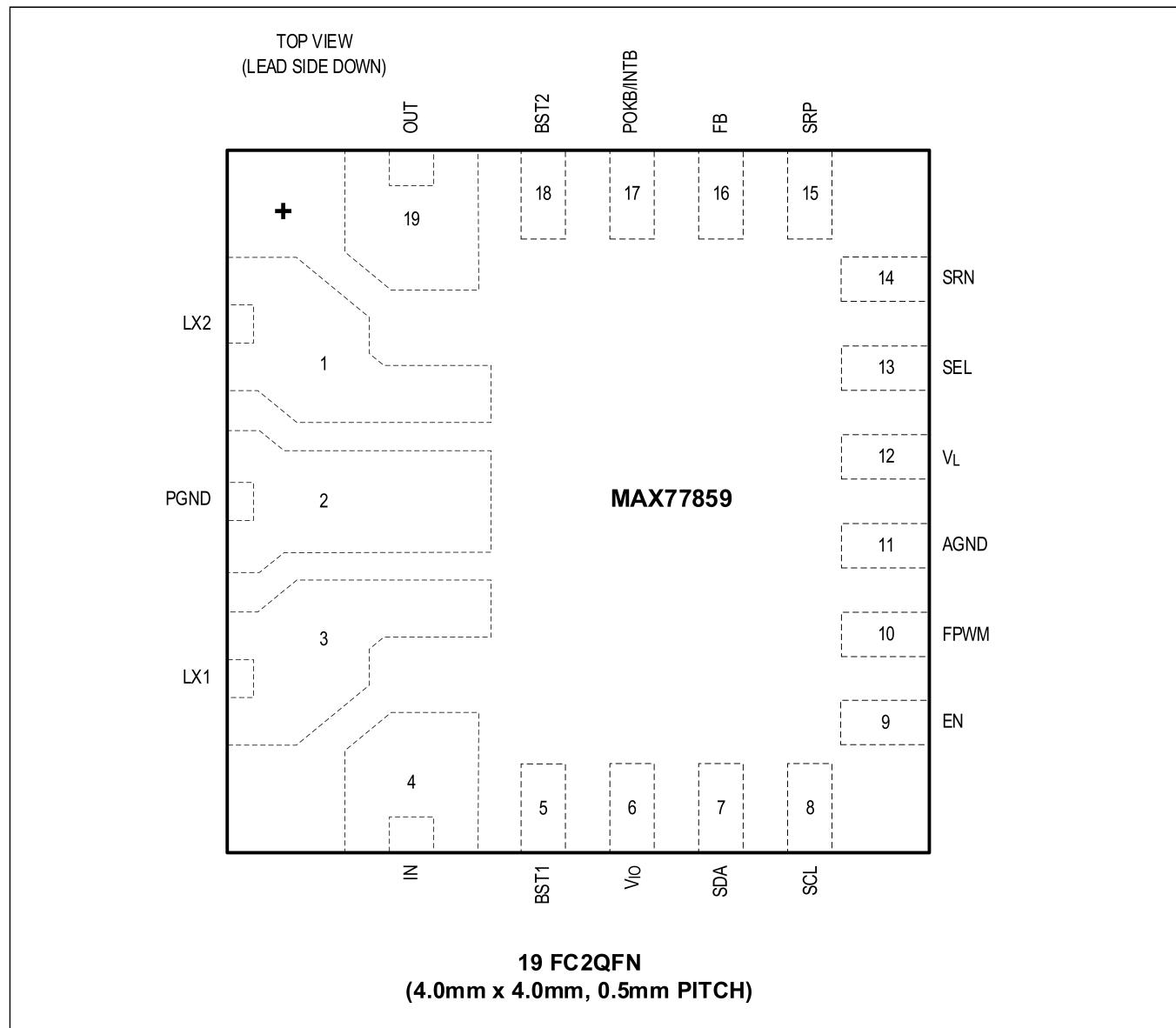

| ピン配置 .....                                   | 23 |

| 42 WLP .....                                 | 23 |

| 19 FC2QFN .....                              | 24 |

| 端子説明 .....                                   | 25 |

| 機能図 .....                                    | 26 |

| 詳細 .....                                     | 27 |

| 概要 .....                                     | 27 |

| スタートアップ .....                                | 28 |

| ソフトスタート .....                                | 28 |

| シャットダウン .....                                | 29 |

| 即時ラッチオフ条件 .....                              | 29 |

| 出力のアクティブ放電 .....                             | 29 |

| 昇降圧レギュレータ .....                              | 29 |

| 昇降圧制御方式 .....                                | 29 |

| スキップ・モードと強制 PWM (FPWM) モード .....             | 30 |

| 出力電圧の設定 .....                                | 31 |

| 内部帰還抵抗の設定 .....                              | 31 |

| 外部帰還抵抗の設定 .....                              | 31 |

| ダイナミック電圧スケーリング (DVS) .....                   | 32 |

| SEL 端子の設定 .....                              | 33 |

| 内部補償オプション .....                              | 33 |

| パワーOK (POK) およびフォルト・ステータス/割込み .....          | 34 |

| 保護機能 .....                                   | 35 |

| 低電圧ロックアウト (UVLO) .....                       | 35 |

| スイッチング電流の過電流保護 (SW OCP) .....                | 35 |

| 出力電流の過電流保護 (OUT OCP、MAX77859A のみ) .....      | 36 |

|                                           |    |

|-------------------------------------------|----|

| サーマル・シャットダウン (THS) .....                  | 37 |

| 詳細 – I <sup>2</sup> C シリアル・インターフェース ..... | 38 |

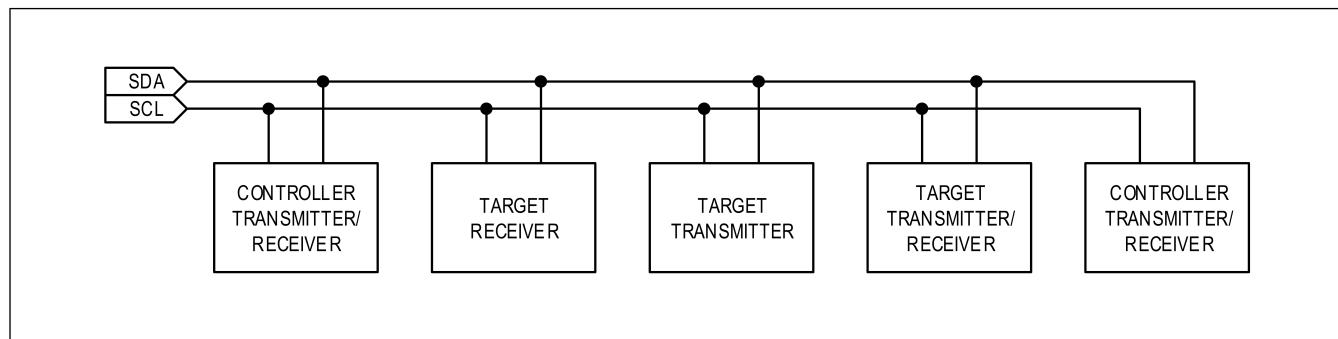

| 概要 .....                                  | 38 |

| システム設定 .....                              | 38 |

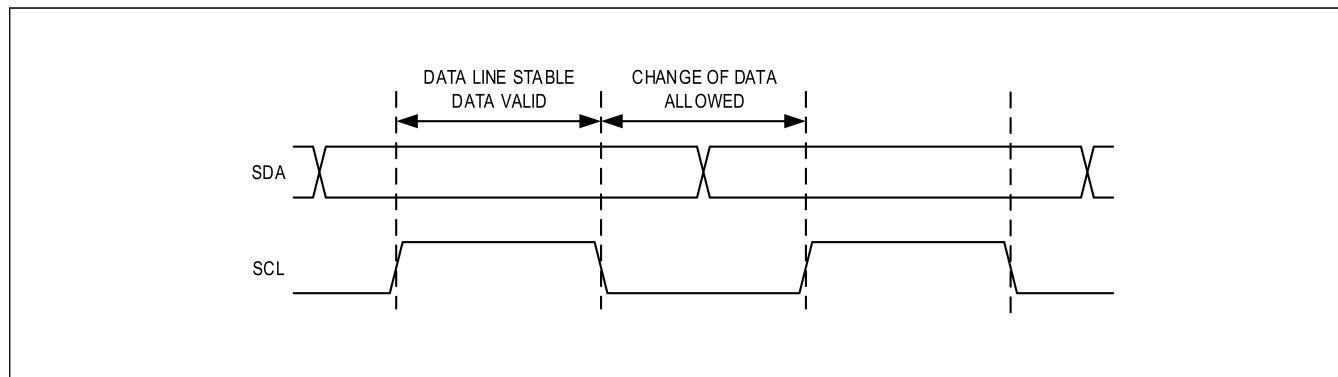

| ビット転送 .....                               | 38 |

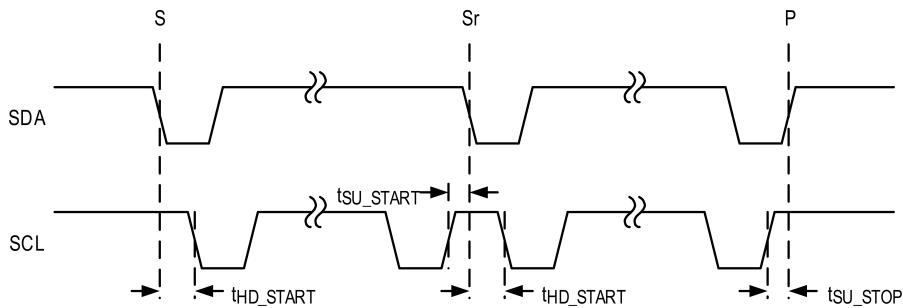

| スタート・コンディションとストップ・コンディション .....           | 38 |

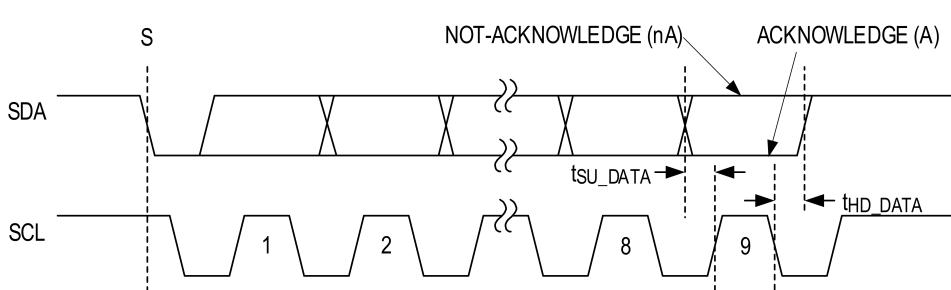

| アクノレッジ・ビット .....                          | 39 |

| ターゲット・アドレス .....                          | 40 |

| クロック・ストレッ칭 .....                          | 40 |

| 一般呼び出しアドレス .....                          | 40 |

| 通信速度 .....                                | 40 |

| 通信プロトコル .....                             | 41 |

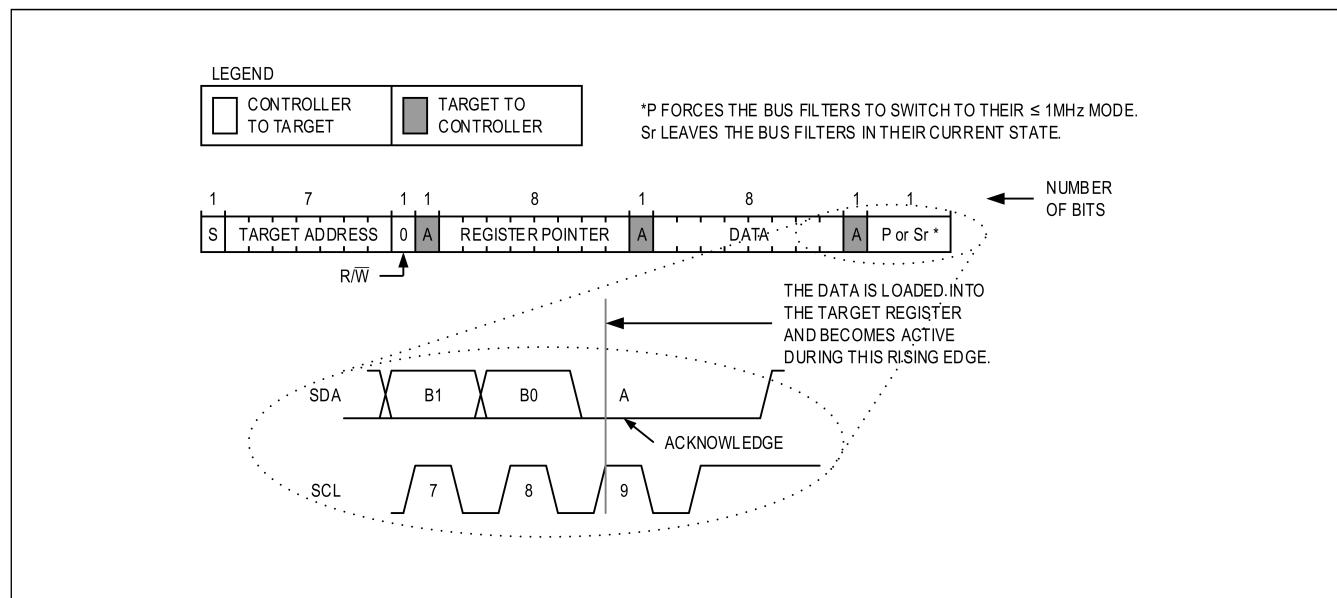

| 單一レジスタへの書き込み .....                        | 41 |

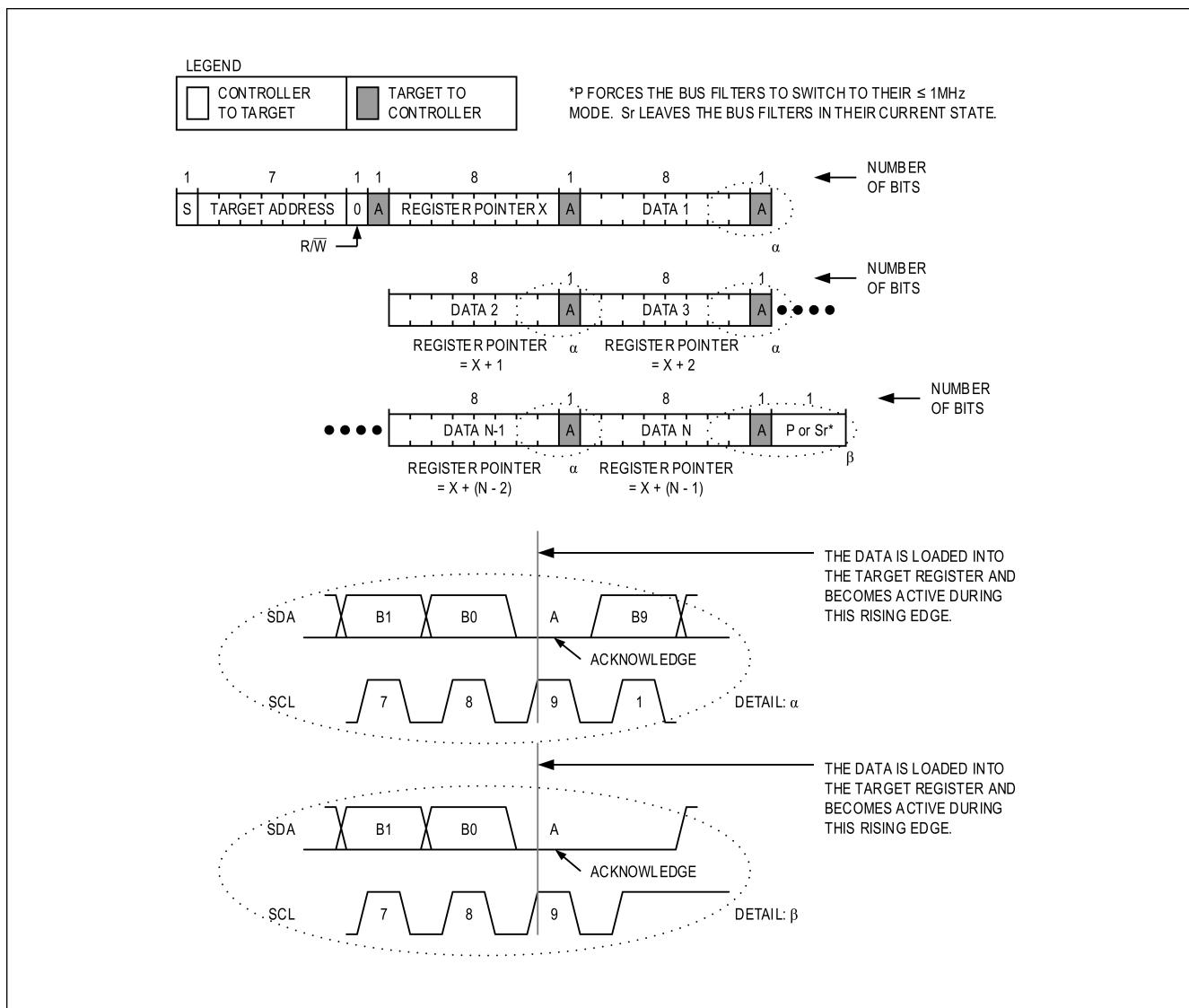

| 連続したレジスタへの書き込み .....                      | 42 |

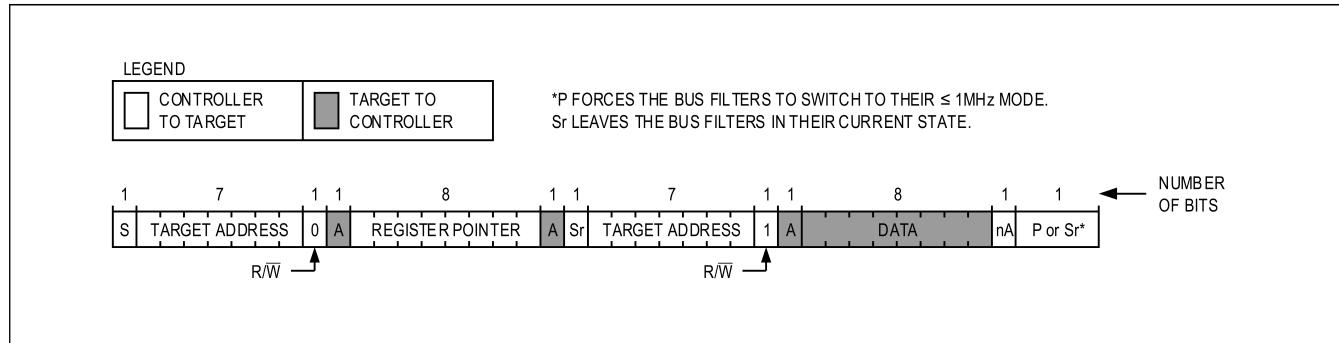

| 單一レジスタからの読み出し .....                       | 43 |

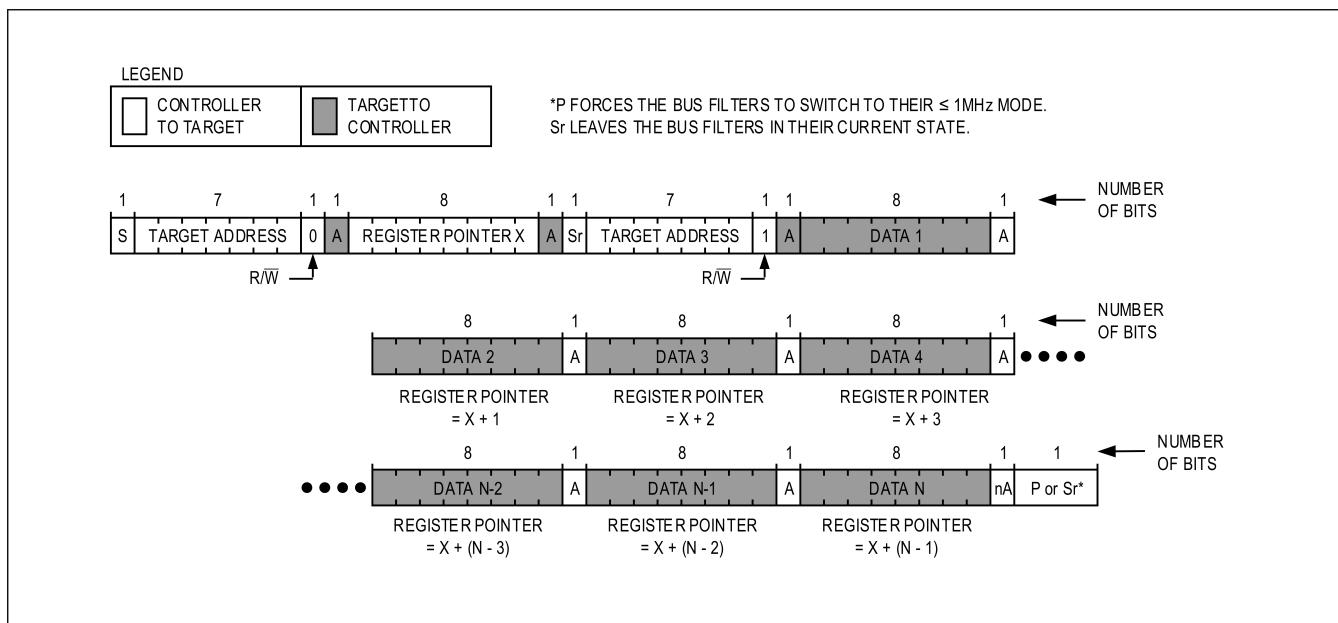

| 連続したレジスタからの読み出し .....                     | 44 |

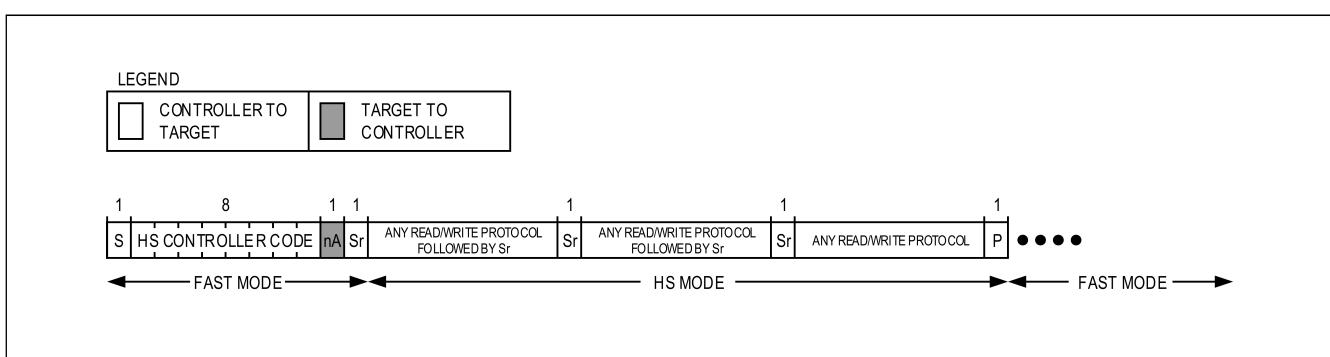

| ハイスピード・モードでの通信 .....                      | 45 |

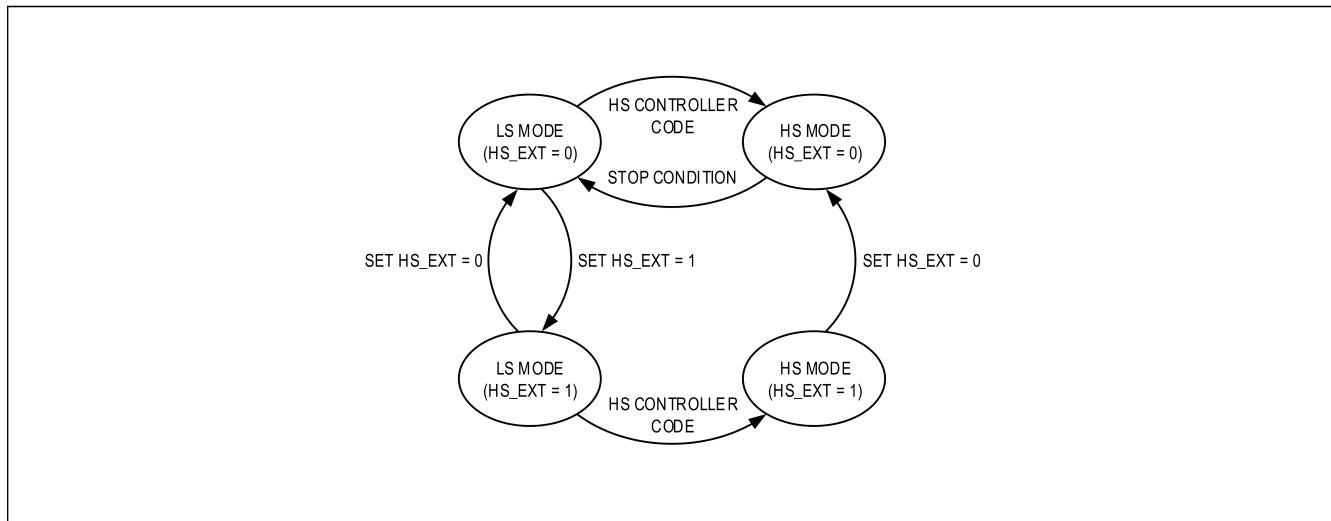

| ハイスピード・モードの延長 .....                       | 46 |

| レジスタ・マップ .....                            | 47 |

| アプリケーション情報 .....                          | 53 |

| 低い出力電圧についての考慮事項 .....                     | 53 |

| スイッチング周波数の選択での考慮事項 .....                  | 53 |

| ソフトウェア (I <sup>2</sup> C) 制御 .....        | 53 |

| I <sup>2</sup> C レス動作とスタンダードアロン動作 .....   | 53 |

| インダクタの選択 .....                            | 54 |

| 入力コンデンサの選択 .....                          | 55 |

| 出力コンデンサの選択 .....                          | 55 |

| その他の必要部品の選択 .....                         | 55 |

| PCB レイアウト時のガイドライン .....                   | 56 |

| 標準アプリケーション回路 .....                        | 57 |

| オーダー情報 .....                              | 57 |

## 図一覧

|                                                                        |    |

|------------------------------------------------------------------------|----|

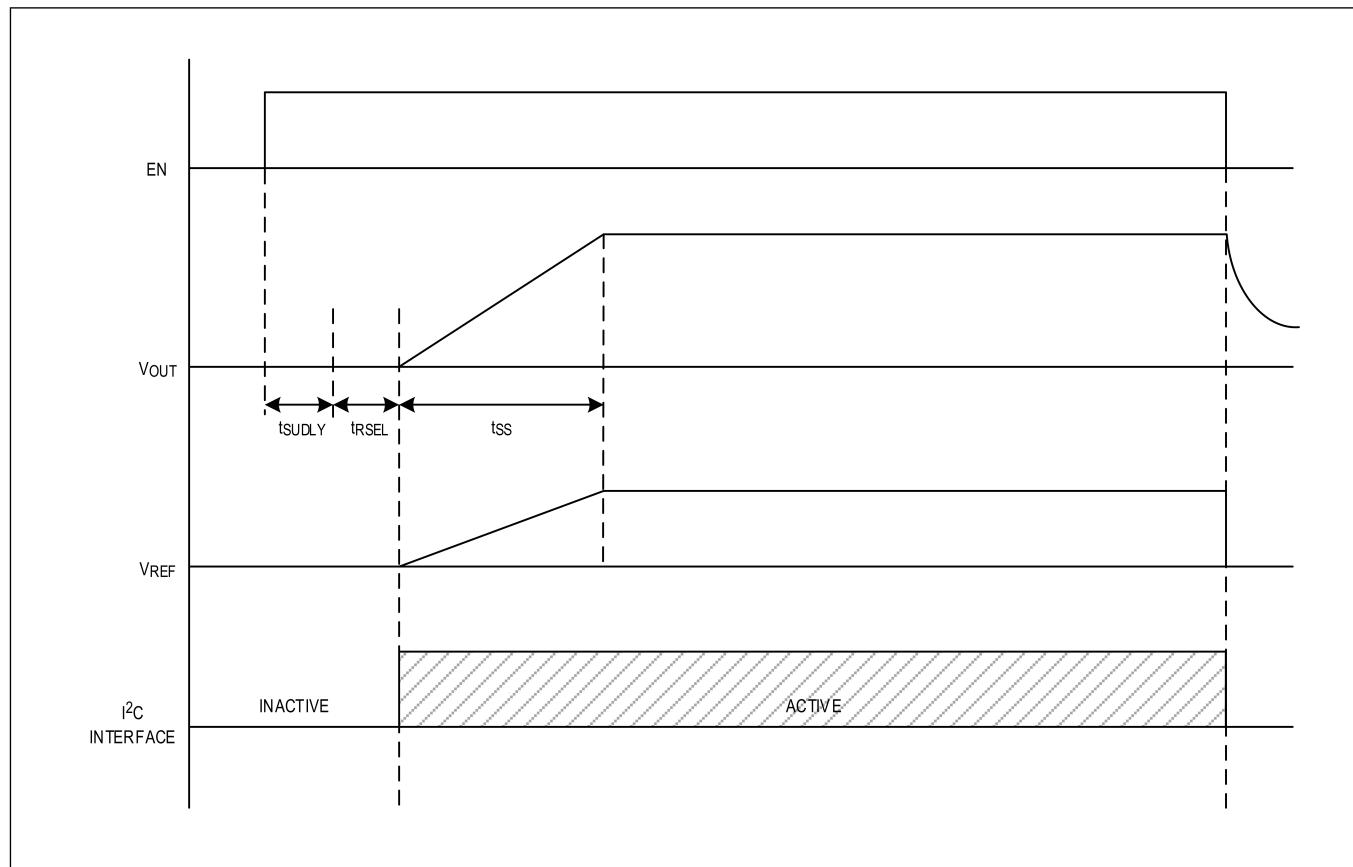

| 図 1. 起動時の波形 .....                                                      | 28 |

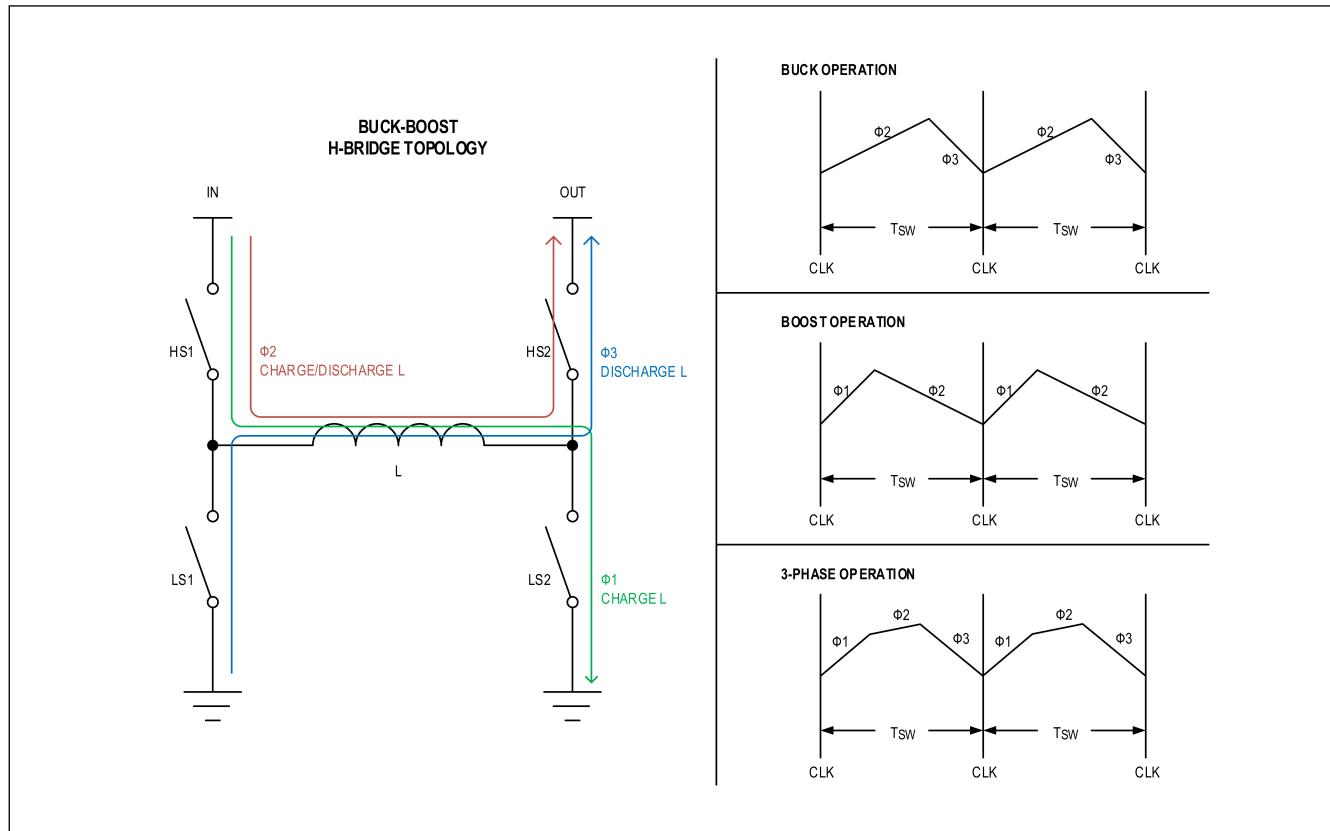

| 図 2. 昇降圧 H ブリッジ方式 .....                                                | 30 |

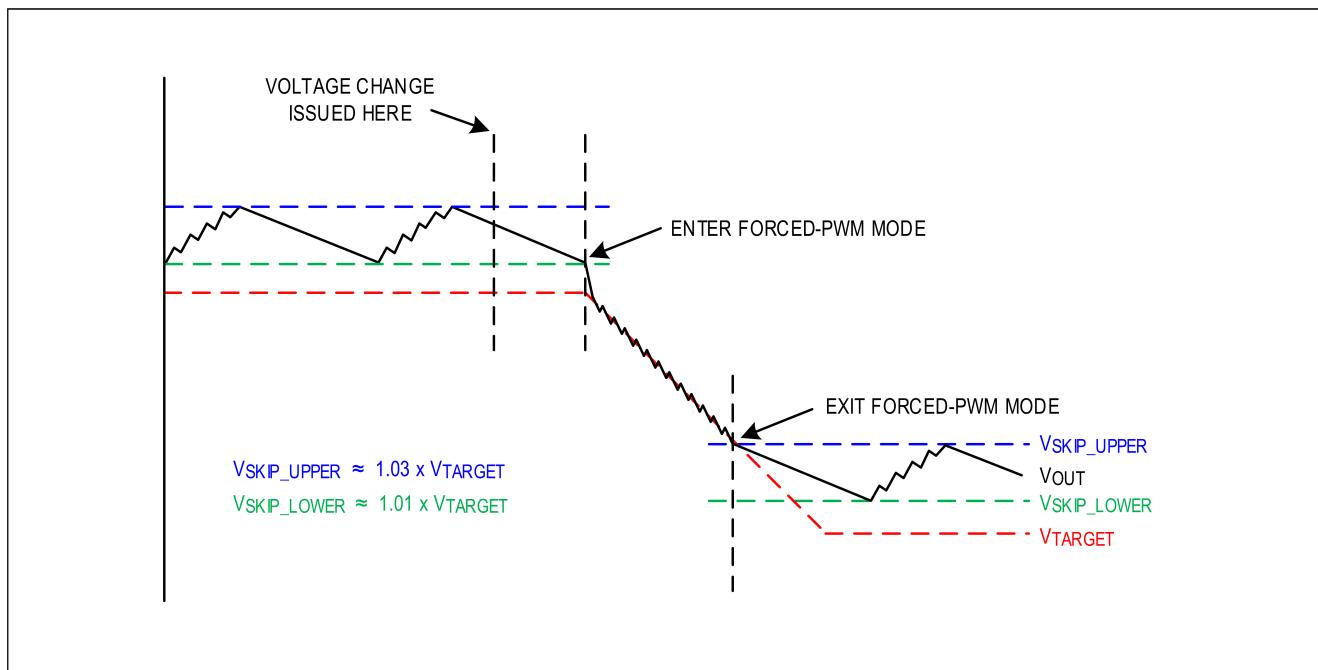

| 図 3. スキップ・モードのスレッショルドと DVS 中の FPWM モード動作 .....                         | 31 |

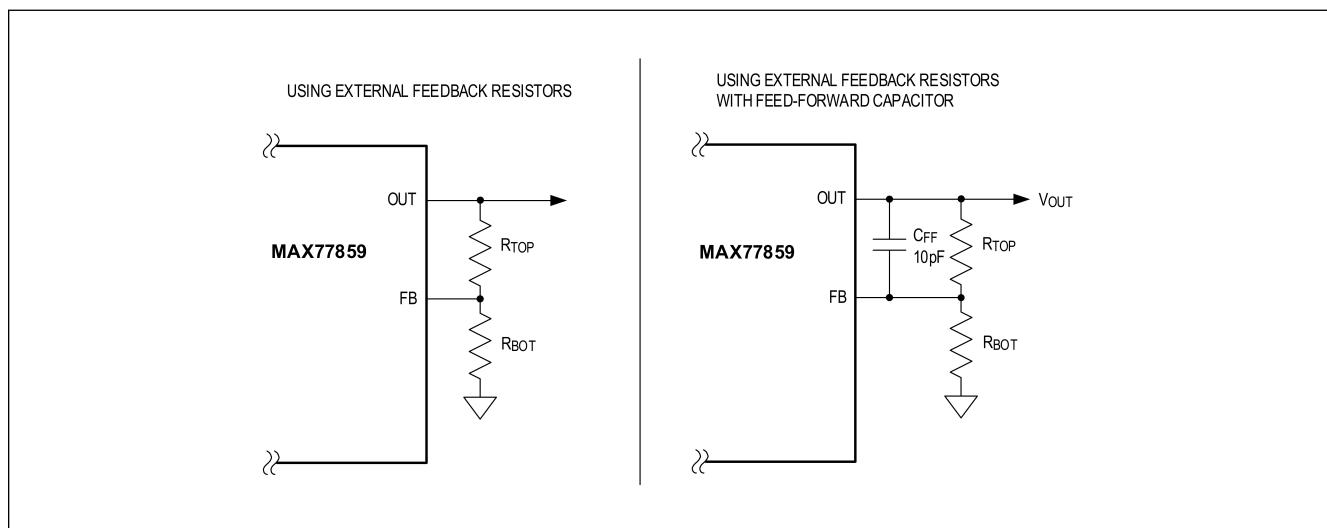

| 図 4. MAX77859 への外部帰還抵抗の接続 .....                                        | 32 |

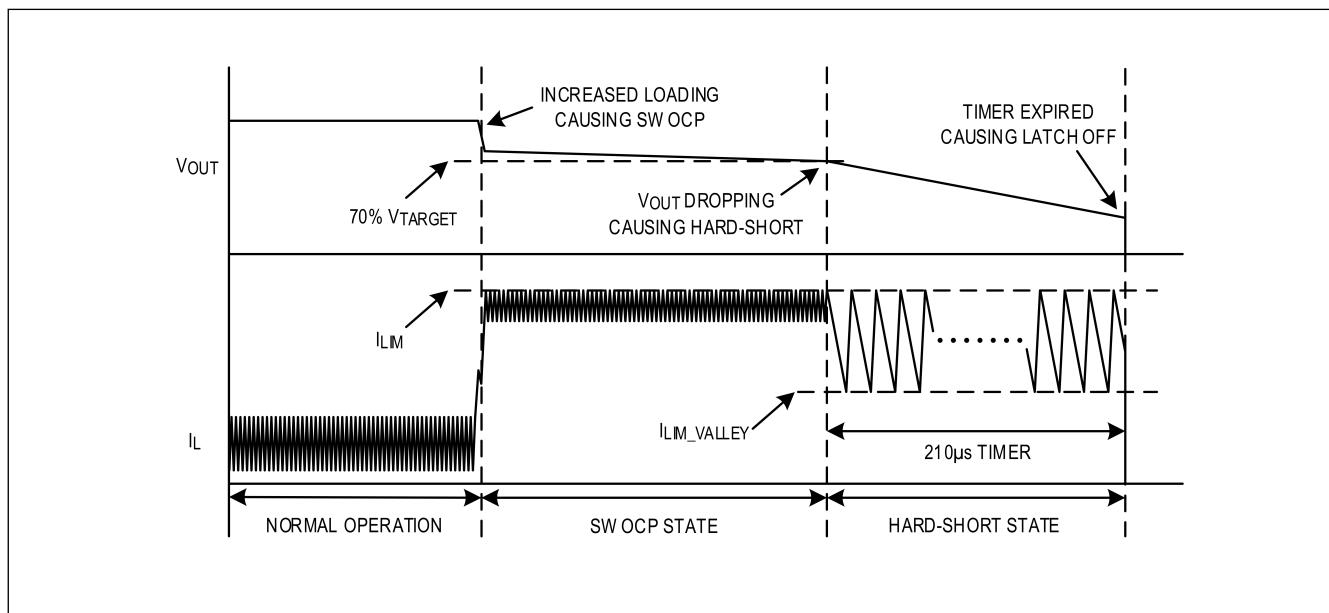

| 図 5. スイッチング電流の過電流と出力短絡における動作 .....                                     | 36 |

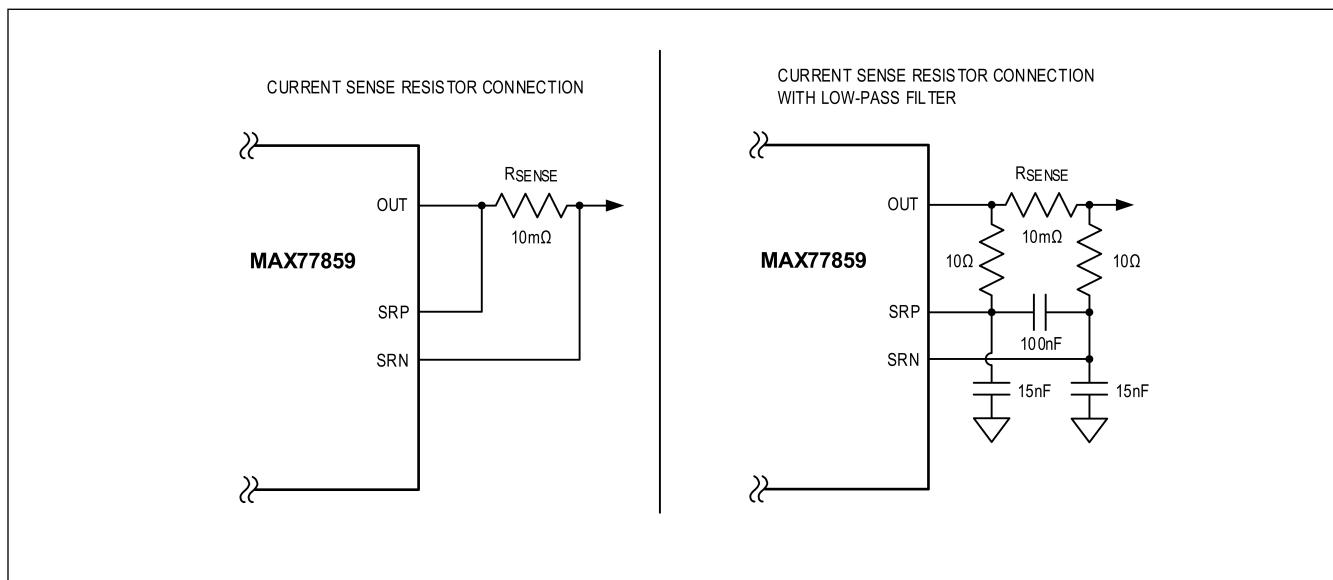

| 図 6. MAX77859A への出力電流検出抵抗（およびローパス・フィルタ）の接続 .....                       | 37 |

| 図 7. 通信コントローラの機能論理図 .....                                              | 38 |

| 図 8. I <sup>2</sup> C ビット転送 .....                                      | 38 |

| 図 9. スタート・コンディションとストップ・コンディション .....                                   | 39 |

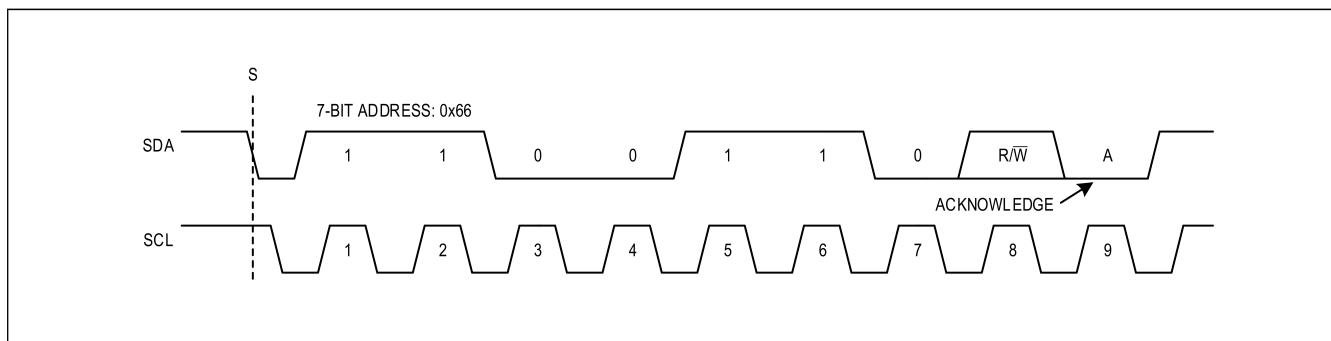

| 図 10. アクノレッジ・ビット .....                                                 | 39 |

| 図 11. ターゲット・アドレス・バイトの例 .....                                           | 40 |

| 図 12. 単一レジスタへの書き込み .....                                               | 41 |

| 図 13. 連続したレジスタへの書き込み .....                                             | 43 |

| 図 14. 単一レジスタからの読み出し .....                                              | 44 |

| 図 15. 連続したレジスタからの読み出し .....                                            | 45 |

| 図 16. ハイスピード・モードでの通信 .....                                             | 45 |

| 図 17. I <sup>2</sup> C 動作モードの状態図 .....                                 | 46 |

| 図 18. スタンドアロン動作時の接続 .....                                              | 54 |

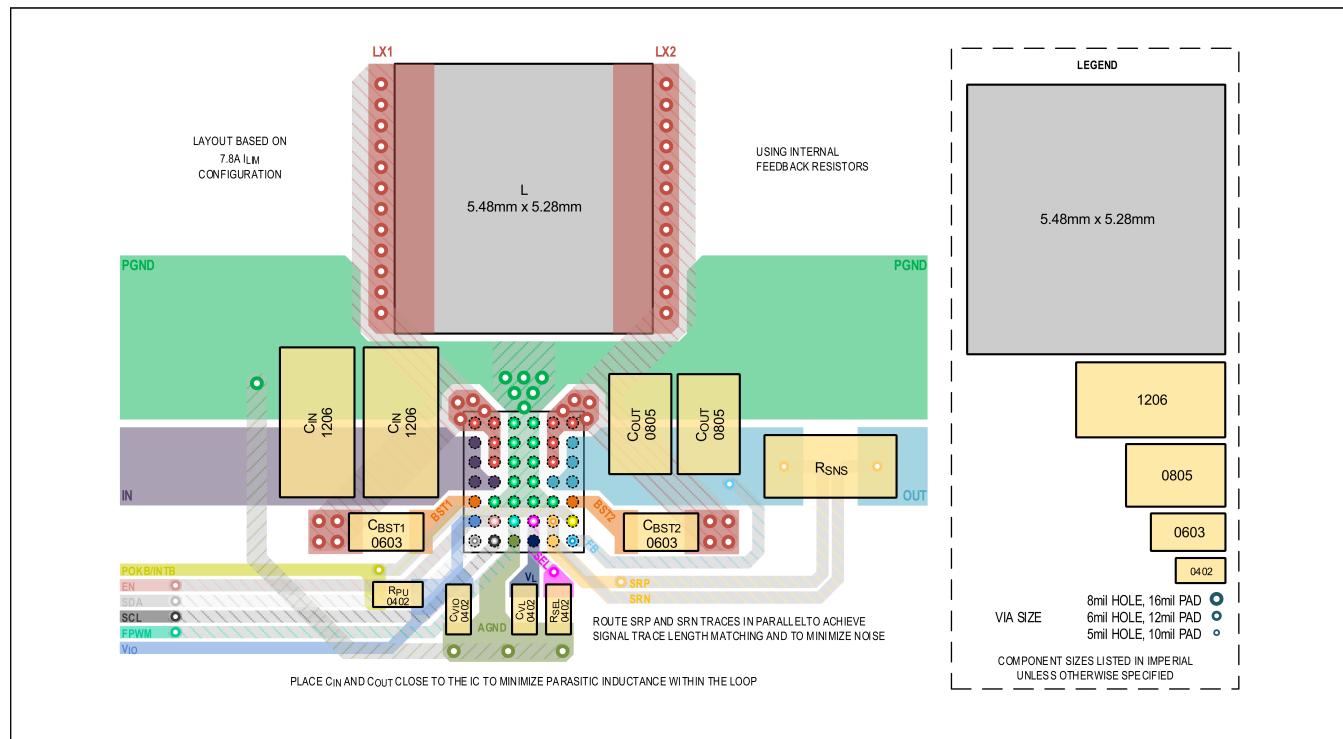

| 図 19. 42 WLP パッケージの場合の 5.48mm × 5.28mm のインダクタを使用した PCB レイアウトの推奨例 ..... | 56 |

## 表一覧

|                                             |    |

|---------------------------------------------|----|

| 表 1. 帰還抵抗の推奨値                               | 32 |

| 表 2. MAX77859 の $R_{SEL}$ 選択表               | 33 |

| 表 3. POKB/INTB 端子の真理値表 (POKBINTB = 0b0)     | 34 |

| 表 4. POKB/INTB 端子の真理値表 (POKBINTB = 0b1)     | 34 |

| 表 5. MAX77859 のスイッチング電流制限値のオプション            | 35 |

| 表 6. MAX77859 の I <sup>2</sup> C ターゲット・アドレス | 40 |

| 表 7. 推奨インダクタ                                | 54 |

| 表 8. 他の部品選択の要求事項                            | 55 |

## 絶対最大定格

|                                                   |                             |

|---------------------------------------------------|-----------------------------|

| IN、LX1、LX2~PGND                                   | -0.3V~+24.0V                |

| OUT、FB、SRP、SRN~PGND                               | -0.3V~+22.0V                |

| BST1、BST2~AGND                                    | -0.3V~+26.0V                |

| BST1~LX1、BST2~LX2                                 | -0.3V~+2.2V                 |

| POKB/INTB、FPWM~AGND、PGND                          | -0.3V~V <sub>IO</sub> +0.3V |

| SCL、SDA~AGND、PGND                                 | -0.3V~V <sub>IO</sub> +0.3V |

| V <sub>L</sub> 、V <sub>IO</sub> 、SEL、EN~AGND、PGND | -0.3V~+2.0V                 |

|                                                                                |              |

|--------------------------------------------------------------------------------|--------------|

| PGND~AGND                                                                      | -0.3V~+0.3V  |

| 連続的消費電力                                                                        |              |

| WLP パッケージ (T <sub>A</sub> = +70°C、+70°C以上では 23.2mW/°C で<br>ディレーティング (Note 1) ) | 1856mW       |

| 最大ジヤンクション温度                                                                    | +150°C       |

| 保存温度範囲                                                                         | -65°C~+150°C |

| はんだ処理温度 (リフロー)                                                                 | +260°C       |

**Note 1 :** パッケージの熱測定は、4層基板を使用して JEDEC 仕様 JESD51-7 に記載された方法で取得しています。パッケージの熱に関する考慮事項の詳細については、[www.maximintegrated.com/thermal-tutorial/](http://www.maximintegrated.com/thermal-tutorial/)を参照してください。

上記の**絶対最大定格**を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## 推奨動作条件

| PARAMETER                  | SYMBOL           | CONDITION                                                                                                                                                                                                       | TYPICAL RANGE   |

|----------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Input Voltage Range        | V <sub>IN</sub>  |                                                                                                                                                                                                                 | 2.5V to 22V     |

| Output Voltage Range       | V <sub>OUT</sub> | Internal Feedback                                                                                                                                                                                               | 3.2V to 16V     |

|                            |                  | External Feedback                                                                                                                                                                                               | 3V to 20V       |

| Output Current Range       | I <sub>OUT</sub> | For continuous operation at 6A, the junction temperature (T <sub>J</sub> ) is limited to +105°C. If the junction temperature is higher than 105°C, the expected lifetime at 6A continuous operation is derated. | 0A to 6A        |

| Junction Temperature Range | T <sub>J</sub>   |                                                                                                                                                                                                                 | -40°C to +125°C |

| Ambient Temperature Range  | T <sub>A</sub>   |                                                                                                                                                                                                                 | -40°C to +85°C  |

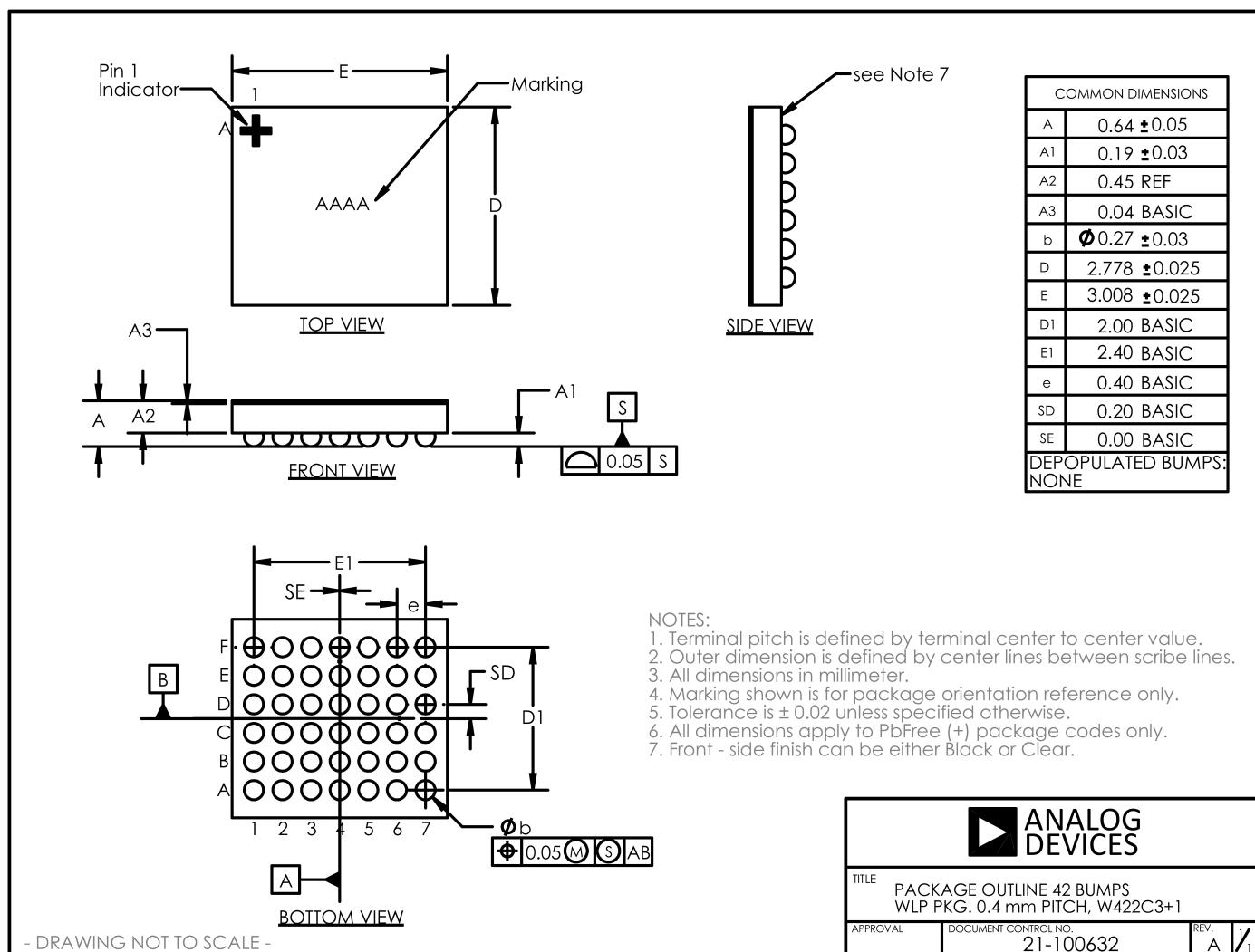

## パッケージ情報

## 42 WLP

|                                              |                                |

|----------------------------------------------|--------------------------------|

| Package Code                                 | W422C3+1                       |

| Outline Number                               | 21-100632                      |

| Land Pattern Number                          | Refer to Application Note 1891 |

| <b>Thermal Resistance, Four-Layer Board:</b> |                                |

| Junction-to-Ambient ( $\theta_{JA}$ )        | 43.1°C/W                       |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、[www.maximintegrated.com/packages](http://www.maximintegrated.com/packages) で確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面はRoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、[www.maximintegrated.com/thermal-tutorial/](http://www.maximintegrated.com/thermal-tutorial/)を参照してください。

## 電気的特性

( $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $V_{VIO} = 1.8V$ 、 $R_{SEL} = 536\Omega$ 、代表値は  $T_A \approx T_J = +25^\circ C$  での値。制限値は  $T_J = +25^\circ C$  で 100% 製品テストされています。特に指定のない限り、動作温度範囲 ( $T_J = -40^\circ C \sim +125^\circ C$ ) および対応する電圧範囲を超える制限値は、設計と特性評価により裏付けられています。)

| PARAMETER                               | SYMBOL              | CONDITIONS                                                                                                                     | MIN                                                                      | TYP  | MAX   | UNITS   |

|-----------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|-------|---------|

| <b>INPUT SUPPLY</b>                     |                     |                                                                                                                                |                                                                          |      |       |         |

| Input Voltage Range                     | $V_{IN}$            |                                                                                                                                | 2.5                                                                      | 22   |       | V       |

| Input Undervoltage Lockout (UVLO)       | $V_{UVLO\_R}$       | $V_{IN}$ rising                                                                                                                | 2.3                                                                      | 2.4  | 2.5   | V       |

| Input UVLO Hysteresis                   | $V_{UVLO\_HYS}$     | $V_{UVLO\_R} - V_{UVLO\_F}$                                                                                                    | 300                                                                      |      |       | mV      |

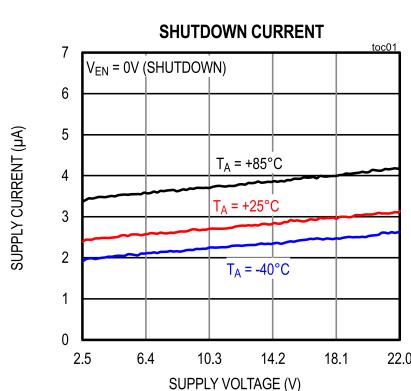

| Shutdown Supply Current                 | $I_{SHDN}$          | $EN = LOW, T_J = -40^\circ C \text{ to } +85^\circ C$                                                                          | 2                                                                        | 5.5  |       | $\mu A$ |

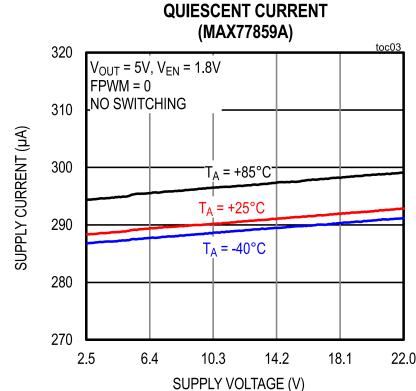

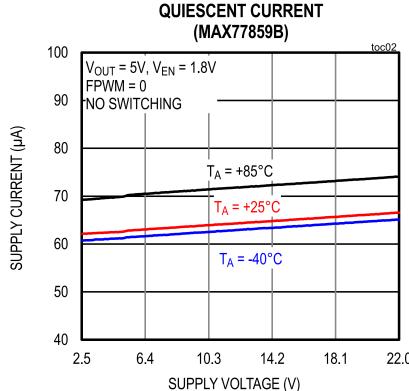

| Quiescent Supply Current                | $I_Q$               | EN = HIGH, $R_{SEL}$ = short to GND, no switching                                                                              | MAX77859B,<br>FPWM = 0 (SKIP mode), $T_J = -40^\circ C$ to $+85^\circ C$ | 60   | 100   | $\mu A$ |

|                                         |                     |                                                                                                                                | MAX77859A,<br>FPWM = 0 (SKIP mode)                                       | 300  | 500   |         |

|                                         |                     |                                                                                                                                | FPWM = 1 (FPWM mode)                                                     | 5    |       |         |

| <b>OUTPUT VOLTAGE</b>                   |                     |                                                                                                                                |                                                                          |      |       |         |

| Output Voltage Regulation Range         | $V_{OUT}$           | Using internal feedback resistors                                                                                              | 3.2                                                                      | 16   |       | V       |

|                                         |                     | Using external feedback resistors                                                                                              | 3.0                                                                      | 20   |       |         |

| Output Voltage Accuracy                 | $V_{OUT\_ACC}$      | $V_{IN} = 2.5V \text{ to } 22V$ ,<br>$V_{OUT} = 3.2V \text{ to } 16V$ , $I_{OUT} = 0mA$ ,<br>using internal feedback resistors | FPWM = 0 (SKIP mode)                                                     | -1   | +4.5  | %       |

|                                         |                     |                                                                                                                                | FPWM = 1 (FPWM mode)                                                     | -2   | +1.5  |         |

| FB Accuracy                             | $V_{FB\_ACC}$       | $V_{IN} = 2.5V \text{ to } 22V$ ,<br>$VREF[9:0] = 0x0A0 \text{ to } 0x320$                                                     |                                                                          | -2   | +1.5  | %       |

| <b><math>V_L</math> INTERNAL SUPPLY</b> |                     |                                                                                                                                |                                                                          |      |       |         |

| $V_L$ Regulator Voltage                 | $V_{VL}$            |                                                                                                                                | 1.65                                                                     | 1.8  | 1.89  | V       |

| <b><math>V_{IO}</math> SUPPLY</b>       |                     |                                                                                                                                |                                                                          |      |       |         |

| $V_{IO}$ Voltage Range                  | $V_{VIO}$           |                                                                                                                                | 1.08                                                                     | 2.0  |       | V       |

| $V_{IO}$ Valid Threshold                | $V_{VIO\_VALID\_R}$ | $V_{IO}$ Rising                                                                                                                | 0.965                                                                    | 1.02 | 1.08  | V       |

|                                         | $V_{VIO\_VALID\_F}$ | $V_{IO}$ Falling                                                                                                               | 0.85                                                                     | 0.9  | 0.955 |         |

| $V_{IO}$ Bias Current                   | $I_{VIO}$           | No I <sup>2</sup> C interface<br>(SDA and SCL unconnected)                                                                     |                                                                          | 2.0  |       | $\mu A$ |

|                                         |                     | $f_{SCL} = f_{SDA} = 1MHz$                                                                                                     |                                                                          | 50   |       |         |

| <b>ENABLE</b>                           |                     |                                                                                                                                |                                                                          |      |       |         |

| EN Input LOW Voltage                    | $V_{EN\_IL}$        |                                                                                                                                |                                                                          | 0.4  |       | V       |

| EN Input HIGH Voltage                   | $V_{EN\_IH}$        |                                                                                                                                | 0.9                                                                      |      |       | V       |

| EN Internal Pulldown Current            | $I_{EN\_PD}$        | $EN = HIGH$                                                                                                                    |                                                                          | 0.1  |       | $\mu A$ |

( $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $V_{VIO} = 1.8V$ 、 $R_{SEL} = 536\Omega$ 、代表値は  $T_A \approx T_J = +25^\circ C$  での値。制限値は  $T_J = +25^\circ C$  で 100% 製品テストされています。特に指定のない限り、動作温度範囲 ( $T_J = -40^\circ C \sim +125^\circ C$ ) および対応する電圧範囲を超える制限値は、設計と特性評価により裏付けられています。)

| PARAMETER                          | SYMBOL            | CONDITIONS                                                                                                                          | MIN                         | TYP       | MAX  | UNITS |     |

|------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------|------|-------|-----|

| <b>POWER-OK</b>                    |                   |                                                                                                                                     |                             |           |      |       |     |

| POK Output LOW Voltage             | $V_{POK\_OL}$     | $I_{POK} = 1mA$                                                                                                                     |                             |           | 0.3  | V     |     |

| POK Rising Threshold               | $V_{POK\_R}$      | $V_{OUT}$ rising, expressed as percentage of target $V_{OUT}$ voltage                                                               | 90                          | 93        |      | %     |     |

| POK Falling Threshold              | $V_{POK\_F}$      | $V_{OUT}$ falling, expressed as percentage of target $V_{OUT}$ voltage                                                              |                             | 85        |      | %     |     |

| <b>THERMAL PROTECTION</b>          |                   |                                                                                                                                     |                             |           |      |       |     |

| Thermal Shutdown Threshold         | $T_{SHDN\_R}$     | $T_J$ rising ( <a href="#">Note 2</a> )                                                                                             |                             | 150       |      | °C    |     |

| Thermal Shutdown Hysteresis        | $T_{SHDN\_HYS}$   | $T_{SHDN\_R} - T_{SHDN\_F}$ ( <a href="#">Note 2</a> )                                                                              |                             | 15        |      | °C    |     |

| <b>BUCK-BOOST REGULATOR</b>        |                   |                                                                                                                                     |                             |           |      |       |     |

| Switching Frequency                | $f_{SW}$          | $I_{OUT} = 0mA$ ,<br>$FPWM = 1$<br>(FPWM mode)                                                                                      | FREQ[1:0] = 00              | 1.10      | 1.20 | 1.30  | MHz |

|                                    |                   |                                                                                                                                     | FREQ[1:0] = 01<br>(default) | 1.38      | 1.50 | 1.62  |     |

|                                    |                   |                                                                                                                                     | FREQ[1:0] = 10              | 1.66      | 1.80 | 1.94  |     |

|                                    |                   |                                                                                                                                     | FREQ[1:0] = 11              | 1.93      | 2.10 | 2.27  |     |

| Startup Delay Time                 | $t_{SUDLY}$       | ( <a href="#">Note 2</a> )                                                                                                          |                             | 100       |      | μs    |     |

| Soft-Start Time                    | $t_{SS}$          | Measured from OUT start ramping to stop ramping during startup,<br>$C_{OUT} = 44\mu F$ , $I_{OUT} = 0mA$ ( <a href="#">Note 2</a> ) |                             | 1.7       |      | ms    |     |

| Soft-start Switching Current Limit | $I_{LIM\_SS}$     | $I_{LIM}[2:0] = 100, 101, 110, \text{ or } 111$ ( $I_{LIM} \leq 3.8A$ )                                                             |                             | $I_{LIM}$ |      | A     |     |

| Soft-start Switching Current Limit | $I_{LIM\_SS}$     | $I_{LIM}[2:0] = 000, 001, 010, \text{ or } 011$ ( $I_{LIM} > 3.8A$ )                                                                |                             | 3.8       |      | A     |     |

| High Side Switching Current Limit  | $I_{LIM}$         | $I_{LIM}[2:0] = 000$ ( <a href="#">Note 2</a> )                                                                                     | 6.63                        | 7.80      | 8.97 | A     |     |

|                                    |                   | $I_{LIM}[2:0] = 001$ ( $I^2C$ only, not available with $R_{SEL}$ ) ( <a href="#">Note 2</a> )                                       |                             | 6.80      |      |       |     |

|                                    |                   | $I_{LIM}[2:0] = 010$ ( <a href="#">Note 2</a> )                                                                                     | 4.93                        | 5.80      | 6.67 |       |     |

|                                    |                   | $I_{LIM}[2:0] = 011$ ( $I^2C$ only, not available with $R_{SEL}$ ) ( <a href="#">Note 2</a> )                                       |                             | 4.80      |      |       |     |

|                                    |                   | $I_{LIM}[2:0] = 100$ ( <a href="#">Note 2</a> )                                                                                     | 3.23                        | 3.80      | 4.37 |       |     |

|                                    |                   | $I_{LIM}[2:0] = 101$ ( $I^2C$ only, not available with $R_{SEL}$ ) ( <a href="#">Note 2</a> )                                       |                             | 2.80      |      |       |     |

|                                    |                   | $I_{LIM}[2:0] = 110$ ( <a href="#">Note 2</a> )                                                                                     | 1.70                        | 2.00      | 2.30 |       |     |

| Valley Current Limit               | $I_{LIM\_VALLEY}$ | $I_{LIM}[2:0] = 000 \text{ or } 001$ ( <a href="#">Note 2</a> )                                                                     |                             | 3.8       |      | A     |     |

|                                    |                   | $I_{LIM}[2:0] = 010 \text{ or } 011$ ( <a href="#">Note 2</a> )                                                                     | 2.73                        |           |      |       |     |

( $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $V_{VIO} = 1.8V$ 、 $R_{SEL} = 536\Omega$ 、代表値は  $T_A \approx T_J = +25^\circ C$  での値。制限値は  $T_J = +25^\circ C$  で 100% 製品テストされています。特に指定のない限り、動作温度範囲 ( $T_J = -40^\circ C \sim +125^\circ C$ ) および対応する電圧範囲を超える制限値は、設計と特性評価により裏付けられています。)

| PARAMETER                                     | SYMBOL                | CONDITIONS                                                                                   | MIN                                                            | TYP     | MAX     | UNITS |

|-----------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------|---------|-------|

|                                               |                       | I <sub>LIM[2:0]</sub> = 100 or 101 (Note 2)                                                  | 1.5                                                            |         | 0.35    |       |

|                                               |                       | I <sub>LIM[2:0]</sub> = 110 or 111 (Note 2)                                                  | 1.5                                                            |         |         |       |

| Skip Mode Switching Current Limit             | I <sub>LIM_SKIP</sub> | FPWM = 0 (SKIP mode) (Note 2)                                                                |                                                                | 1.2     |         | A     |

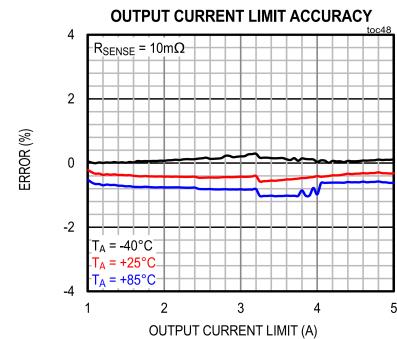

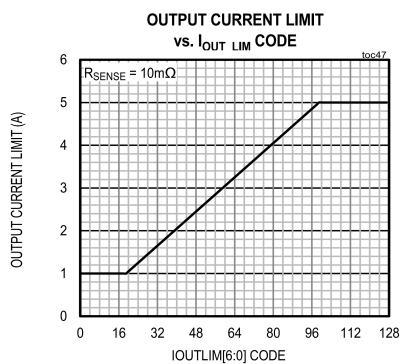

| Output Current Limit                          | I <sub>OUT_LIM</sub>  | R <sub>SENSE</sub> = 10mΩ                                                                    | I <sub>OUTLIM[6:0]</sub> = 0x13, code clamped below this level | 1       | 3       | A     |

|                                               |                       |                                                                                              | I <sub>OUTLIM[6:0]</sub> = 0x3B, default value                 | 3       |         |       |

|                                               |                       |                                                                                              | I <sub>OUTLIM[6:0]</sub> = 0x63, code clamped above this level | 5       |         |       |

| Output Current Limit Range                    | I <sub>OUT_LIM</sub>  | R <sub>SENSE</sub> = 10mΩ                                                                    | I <sub>OUTLIM[6:0]</sub> = 0x13 to 0x63                        | 1       | 5       | A     |

| Current Loop Regulation Voltage               | V <sub>SR</sub>       | Measured across SRP and SRN, R <sub>SENSE</sub> = 10mΩ, I <sub>OUTLIM[6:0]</sub> = 0x3B (3A) |                                                                | 28      | 32      | mV    |

| Line Regulation                               | ΔV/V <sub>IN</sub>    | V <sub>IN</sub> = 2.5V to 22V, V <sub>OUT</sub> = 5V, I <sub>OUT</sub> = 0mA and 1A (Note 2) |                                                                | ±0.2    |         | %/V   |

| Load Regulation                               | ΔV/V <sub>OUT</sub>   | V <sub>IN</sub> ≥ 4V, V <sub>OUT</sub> = 5V, I <sub>OUT</sub> = 0mA to 3A (Note 2)           |                                                                | ±0.6    |         | %/A   |

| Internal Reference Voltage                    | V <sub>REF</sub>      | VREF[9:0] = 0x0A0, code clamped below this level                                             |                                                                | 0.19531 | 0.30518 | V     |

|                                               |                       | VREF[9:0] = 0x0FA, default value                                                             |                                                                | 0.97656 |         |       |

|                                               |                       | VREF[9:0] = 0x320, code clamped above this level                                             |                                                                | 0.19531 | 0.97656 |       |

| Internal Reference Voltage Programmable Range | V <sub>REF</sub>      | VREF[9:0] = 0x0A0 to 0x320                                                                   |                                                                | mV/μs   |         | V     |

| Internal Reference DVS Ramp Rate              | ΔV <sub>REF</sub> /Δt | SLEW_RATE[1:0] = 00 (default)                                                                | FREQ[1:0] = 00                                                 | 3/2     | 1/8     | mV/μs |

|                                               |                       |                                                                                              | FREQ[1:0] = 01 or 10                                           | 1       |         |       |

|                                               |                       |                                                                                              | FREQ[1:0] = 11                                                 | 4/5     |         |       |

|                                               |                       | SLEW_RATE[1:0] = 01                                                                          |                                                                | 1/2     |         |       |

|                                               |                       | SLEW_RATE[1:0] = 10                                                                          |                                                                | 1/4     |         |       |

|                                               |                       | SLEW_RATE[1:0] = 11                                                                          |                                                                | 1/8     |         |       |

| FB Input Leakage Current                      | I <sub>FB_LK</sub>    |                                                                                              |                                                                | -1      | +1      | μA    |

| High Side MOSFET On Resistance                | R <sub>DSON_HS</sub>  | IN to LX1, LX2 to OUT, T <sub>J</sub> = -40°C to +85°C                                       |                                                                | 20      | 35      | mΩ    |

( $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $V_{VIO} = 1.8V$ 、 $R_{SEL} = 536\Omega$ 、代表値は  $T_A \approx T_J = +25^\circ C$  での値。制限値は  $T_J = +25^\circ C$  で 100% 製品テストされています。特に指定のない限り、動作温度範囲 ( $T_J = -40^\circ C \sim +125^\circ C$ ) および対応する電圧範囲を超える制限値は、設計と特性評価により裏付けられています。)

| PARAMETER                       | SYMBOL           | CONDITIONS                                                     | MIN | TYP | MAX | UNITS     |

|---------------------------------|------------------|----------------------------------------------------------------|-----|-----|-----|-----------|

| Low Side MOSFET On Resistance   | $R_{DS(ON\_LS)}$ | LX1 to PGND, LX2 to PGND, $T_J = -40^\circ C$ to $+85^\circ C$ |     | 20  | 37  | $m\Omega$ |

| Output Active Discharge Current | $I_{DISCHG}$     | $EN = \text{LOW}$ or $V_{IN} < V_{UVLO\_F}$ , $V_{OUT} = 15V$  |     | 5   |     | $mA$      |

**Note 2 :** 設計により性能を確保。出荷テストの対象外です。

**Note 3 :** ATE またはベンチ試験で特性評価を行っていますが、製品テストは行っていません。

電気的特性 – I<sup>2</sup>C シリアル・インターフェース

( $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $V_{VIO} = 1.8V$ 、 $R_{SEL} = 536\Omega$ 、代表値は  $T_A \approx T_J = +25^\circ C$  での値。制限値は  $T_J = +25^\circ C$  で 100% 製品テストされています。特に指定のない限り、動作温度範囲 ( $T_J = -40^\circ C \sim +125^\circ C$ ) および対応する電圧範囲を超える制限値は、設計と特性評価により裏付けられています。)

| PARAMETER                                      | SYMBOL          | CONDITIONS                                                                | MIN                   | TYP             | MAX | UNITS |

|------------------------------------------------|-----------------|---------------------------------------------------------------------------|-----------------------|-----------------|-----|-------|

| <b>I/O STAGE</b>                               |                 |                                                                           |                       |                 |     |       |

| SCL, SDA Input HIGH Voltage                    | $V_{IH}$        |                                                                           | 0.7 x $V_{VIO}$       |                 |     | V     |

| SCL, SDA Input LOW Voltage                     | $V_{IL}$        |                                                                           | 0.3 x $V_{VIO}$       |                 |     | V     |

| SCL, SDA Input Hysteresis                      | $V_{HYS}$       | Fast mode/Fast-mode plus                                                  | 0.05 x $V_{VIO}$      |                 |     | V     |

|                                                |                 | High-speed mode                                                           | 0.1 x $V_{VIO}$       |                 |     |       |

| SDA Output LOW Voltage                         | $V_{OL}$        | $I_{SINK} = 2mA$ (Fast mode/Fast-mode plus)<br>or $3mA$ (High-speed mode) |                       | 0.2 x $V_{VIO}$ |     | V     |

| SCL, SDA Input Capacitance                     | $C_I$           | (Note 2)                                                                  |                       | 10              |     | pF    |

| SCL, SDA Input Leakage Current                 | $I_{LK}$        |                                                                           | -10                   | 0.001           | +10 | µA    |

| <b>TIMING (FAST MODE)</b>                      |                 |                                                                           |                       |                 |     |       |

| Clock Frequency                                | $f_{SCL}$       |                                                                           | 0                     | 400             |     | kHz   |

| Bus Free Time Between STOP and START Condition | $t_{BUSF}$      |                                                                           | 1.3                   |                 |     | µs    |

| Hold Time (REPEATED) START Condition           | $t_{HD\_START}$ |                                                                           | 0.6                   |                 |     | µs    |

| SCL LOW Period                                 | $t_{LOW}$       |                                                                           | 1.3                   |                 |     | µs    |

| SCL HIGH Period                                | $t_{HIGH}$      |                                                                           | 0.6                   |                 |     | µs    |

| Setup Time REPEATED START Condition            | $t_{SU\_START}$ |                                                                           | 0.6                   |                 |     | µs    |

| DATA Setup Time                                | $T_{SU\_DATA}$  |                                                                           | 100                   |                 |     | ns    |

| SCL, SDA Receiving Rise Time                   | $t_{R\_REV}$    |                                                                           | 20                    | 300             |     | ns    |

| SCL, SDA Receiving Fall Time                   | $t_{F\_REV}$    |                                                                           | 20 x $(V_{VIO}/5.5V)$ | 300             |     | ns    |

| Setup Time for STOP Condition                  | $t_{SU\_STO}$   |                                                                           | 0.26                  |                 |     | µs    |

| Data Valid Time                                | $t_{VD\_DATA}$  |                                                                           |                       | 900             |     | ns    |

| Data Valid Acknowledge Time                    | $t_{VD\_ACK}$   |                                                                           |                       | 900             |     | ns    |

| Bus Capacitance                                | $C_B$           | (Note 2)                                                                  |                       | 400             |     | pF    |

| Pulse Width of Suppressed Spikes               | $t_{SP}$        |                                                                           |                       | 140             |     | ns    |

( $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $V_{VIO} = 1.8V$ 、 $R_{SEL} = 536\Omega$ 、代表値は  $T_A \approx T_J = +25^\circ C$  での値。制限値は  $T_J = +25^\circ C$  で 100% 製品テストされています。特に指定のない限り、動作温度範囲 ( $T_J = -40^\circ C \sim +125^\circ C$ ) および対応する電圧範囲を超える制限値は、設計と特性評価により裏付けられています。)

| PARAMETER                                                | SYMBOL          | CONDITIONS | MIN                           | TYP | MAX  | UNITS   |

|----------------------------------------------------------|-----------------|------------|-------------------------------|-----|------|---------|

| <b>TIMING (FAST-MODE PLUS)</b>                           |                 |            |                               |     |      |         |

| Clock Frequency                                          | $f_{SCL}$       |            | 0                             |     | 1000 | kHz     |

| Bus Free Time Between STOP and START Condition           | $t_{BUSF}$      |            | 0.5                           |     |      | $\mu s$ |

| Hold Time (REPEATED) START Condition                     | $t_{HD\_START}$ |            | 0.26                          |     |      | $\mu s$ |

| SCL LOW Period                                           | $t_{LOW}$       |            | 0.5                           |     |      | $\mu s$ |

| SCL HIGH Period                                          | $t_{HIGH}$      |            | 0.26                          |     |      | $\mu s$ |

| Setup Time REPEATED START Condition                      | $t_{SU\_START}$ |            | 0.26                          |     |      | $\mu s$ |

| DATA Setup Time                                          | $T_{SU\_DATA}$  |            | 50                            |     |      | ns      |

| SCL, SDA Receiving Rise Time                             | $t_{R\_REV}$    |            |                               | 120 |      | ns      |

| SCL, SDA Receiving Fall Time                             | $t_{F\_REV}$    |            | 20 x<br>( $V_{VIO}/$<br>5.5V) | 120 |      | ns      |

| Setup Time for STOP condition                            | $t_{SU\_STO}$   |            | 0.26                          |     |      | $\mu s$ |

| Data Valid Time                                          | $t_{VD\_DATA}$  |            |                               | 450 |      | ns      |

| Data Valid Acknowledge Time                              | $t_{VD\_ACK}$   |            |                               | 450 |      | ns      |

| Bus Capacitance                                          | $C_B$           | (Note 2)   |                               | 550 |      | pF      |

| Pulse Width of Suppressed Spikes                         | $t_{SP}$        |            |                               | 140 |      | ns      |

| <b>TIMING (HIGH-SPEED MODE, BUS CAPACITANCE = 100pF)</b> |                 |            |                               |     |      |         |

| Clock Frequency                                          | $f_{SCL}$       |            |                               | 3.4 |      | MHz     |

| Hold Time (REPEATED) START Condition                     | $t_{HD\_START}$ |            | 160                           |     |      | ns      |

| SCL LOW Period                                           | $t_{LOW}$       |            | 160                           |     |      | ns      |

| SCL HIGH Period                                          | $t_{HIGH}$      |            | 60                            |     |      | ns      |

| Setup Time REPEATED START Condition                      | $t_{SU\_START}$ |            | 160                           |     |      | ns      |

| DATA Hold Time                                           | $t_{HD\_DATA}$  |            |                               | 95  |      | ns      |

| DATA Setup Time                                          | $T_{SU\_DATA}$  |            | 10                            |     |      | ns      |

| SCL, SDA Receiving Rise Time                             | $t_{R\_REV}$    |            | 10                            | 50  |      | ns      |

| SCL, SDA Receiving Fall Time                             | $t_{F\_REV}$    |            | 10                            | 50  |      | ns      |

( $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $V_{VIO} = 1.8V$ 、 $R_{SEL} = 536\Omega$ 、代表値は  $T_A \approx T_J = +25^\circ C$  での値。制限値は  $T_J = +25^\circ C$  で 100% 製品テストされています。特に指定のない限り、動作温度範囲 ( $T_J = -40^\circ C \sim +125^\circ C$ ) および対応する電圧範囲を超える制限値は、設計と特性評価により裏付けられています。)

| PARAMETER                        | SYMBOL        | CONDITIONS                 | MIN | TYP | MAX | UNITS |

|----------------------------------|---------------|----------------------------|-----|-----|-----|-------|

| Setup Time for STOP Condition    | $t_{SU\_STO}$ |                            | 160 |     |     | ns    |

| Bus Capacitance                  | $C_B$         | ( <a href="#">Note 2</a> ) |     | 100 |     | pF    |

| Pulse Width of Suppressed Spikes | $t_{SP}$      |                            |     | 30  |     | ns    |

**Note 2 :** 設計により性能を確保。出荷テストの対象外です。

**Note 3 :** ATE またはベンチ試験で特性評価を行っていますが、製品テストは行っていません。

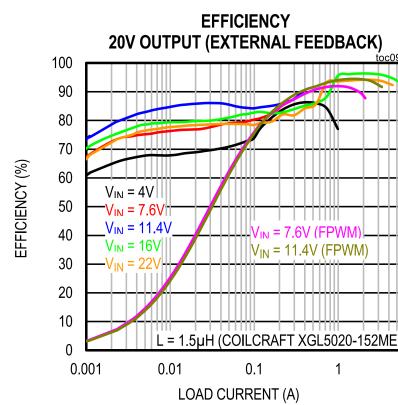

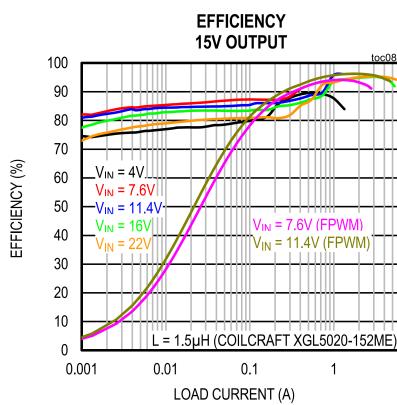

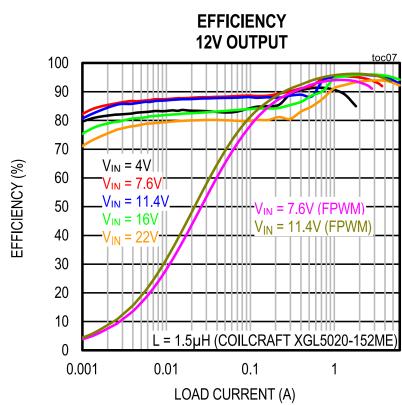

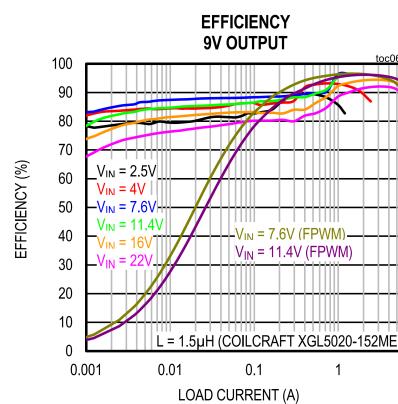

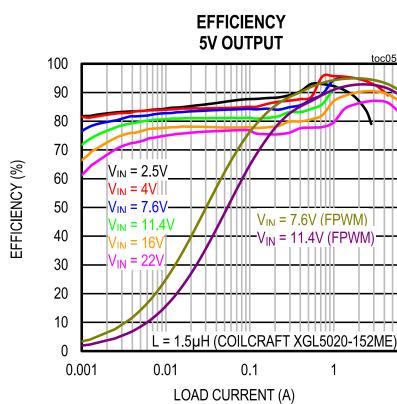

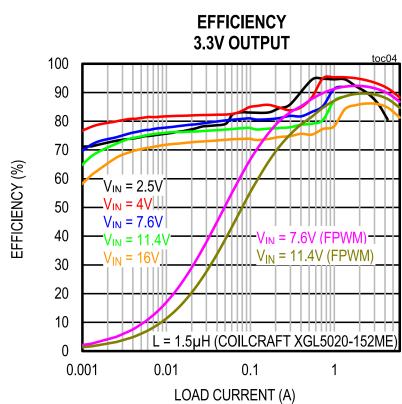

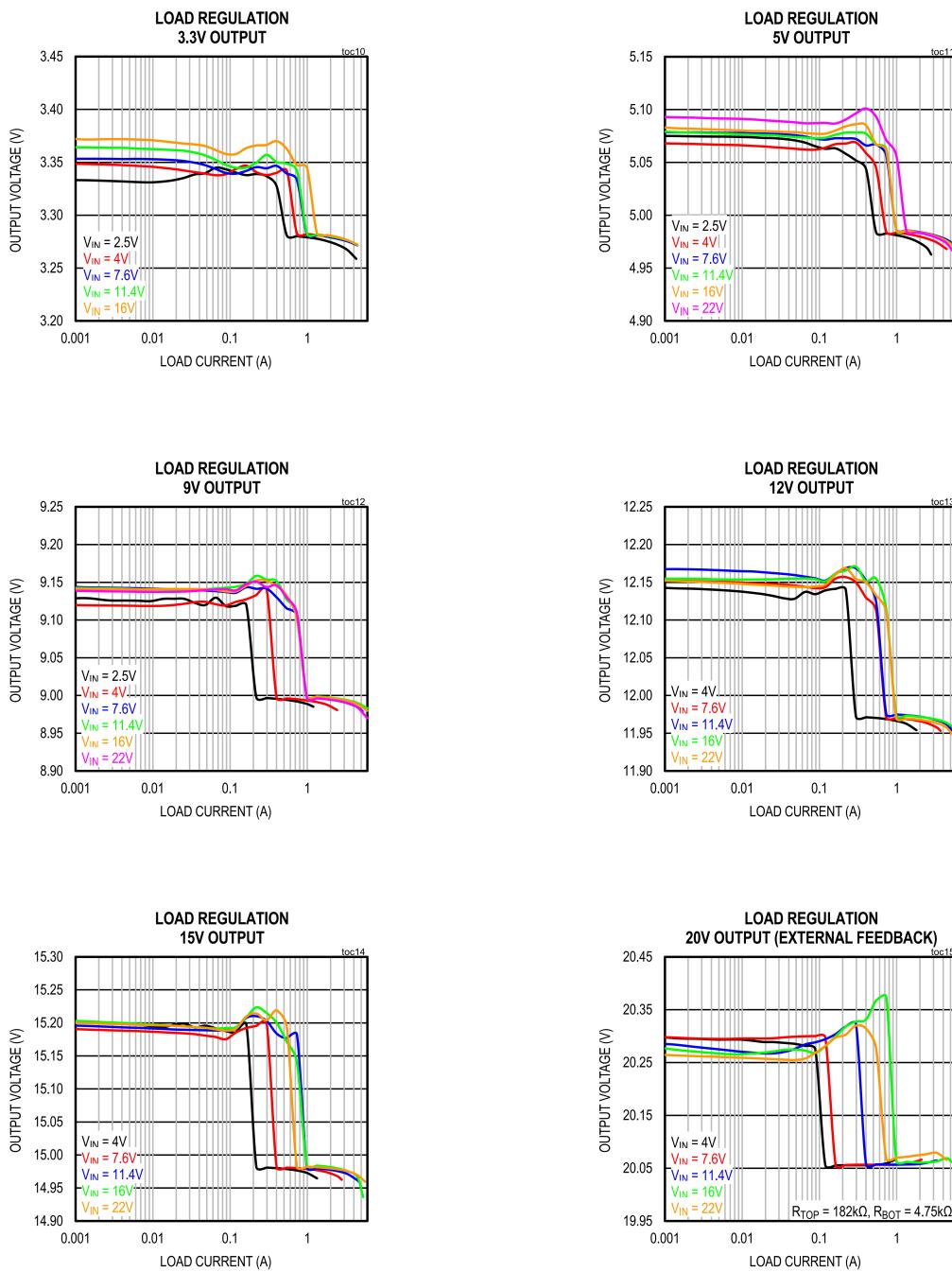

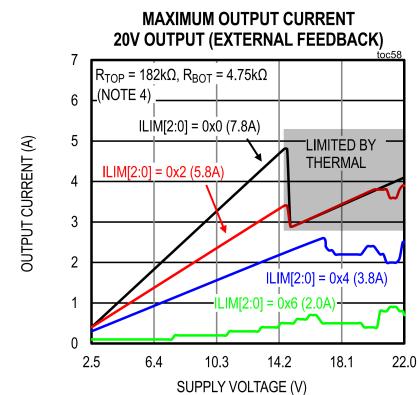

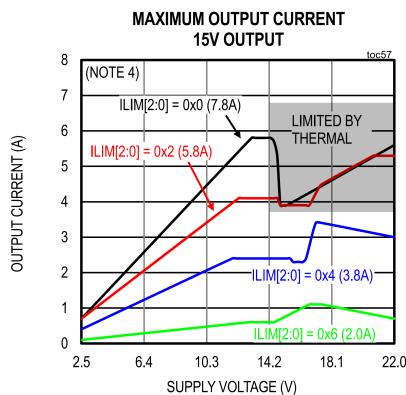

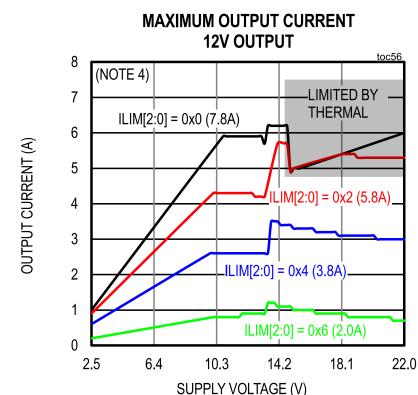

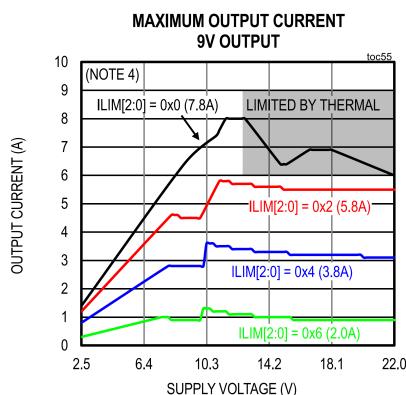

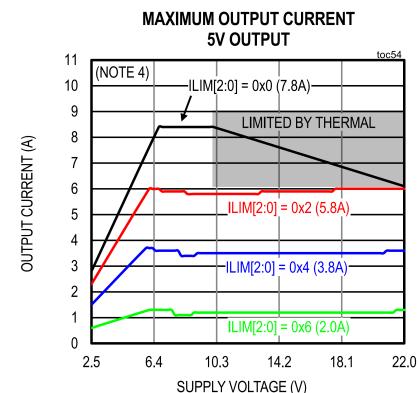

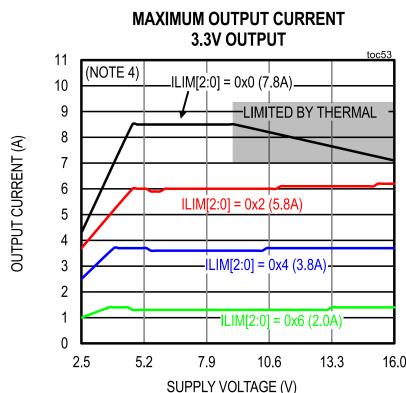

## 標準動作特性

(特に指定のない限り、 $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $L = 1.5\mu H$  (Coilcraft XGL5020-152ME)、 $C_{OUT} = 2x 22\mu F$ 、 $FPWM = 0$ 、 $ILIM[2:0] = 0x0$  (7.8A)、 $f_{sw} = 1.5MHz$ 、内部帰還設定、 $T_A = +25^{\circ}C$ 。Note 4: 特に指定のない限り、スイッチング電流の制限値で制限した測定です。実際の最大出力電流はシステムの熱性能によって異なります。)

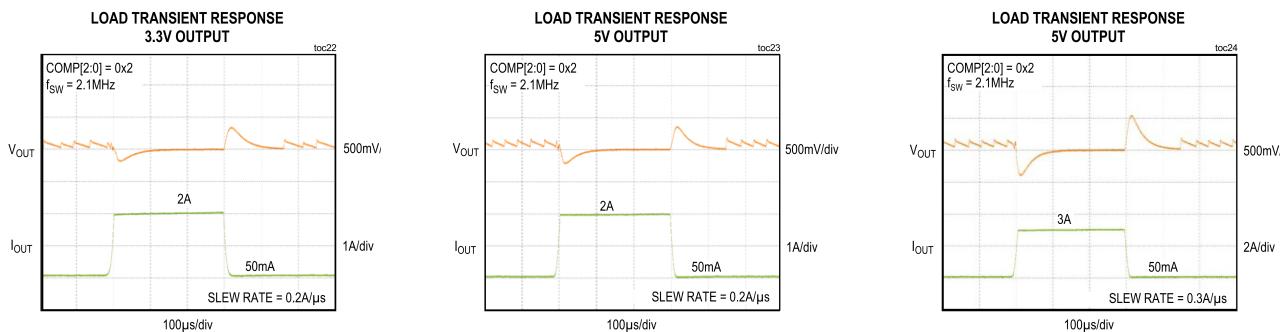

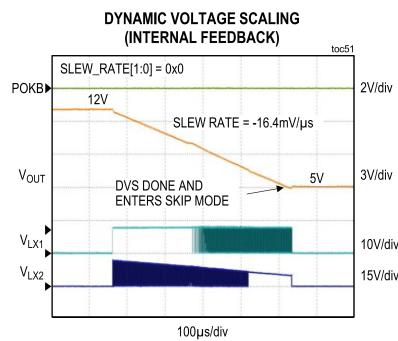

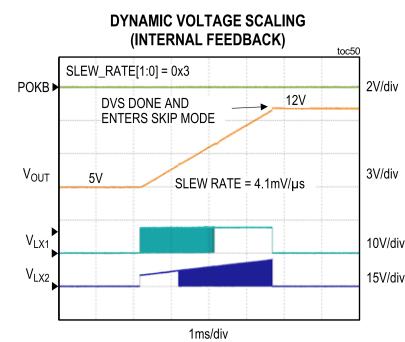

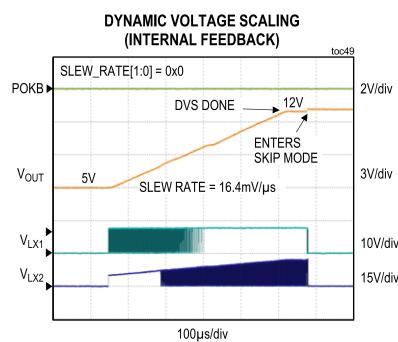

## 標準動作特性（続き）

（特に指定のない限り、 $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $L = 1.5\mu H$ （Coilcraft XGL5020-152ME）、 $C_{OUT} = 2 \times 22\mu F$ 、 $FPWM = 0$ 、 $ILIM[2:0] = 0x0$ （7.8A）、 $f_{sw} = 1.5MHz$ 、内部帰還設定、 $T_A = +25^{\circ}C$ 。Note 4：特に指定のない限り、スイッチング電流の制限値で制限した測定です。実際の最大出力電流はシステムの熱性能によって異なります。）

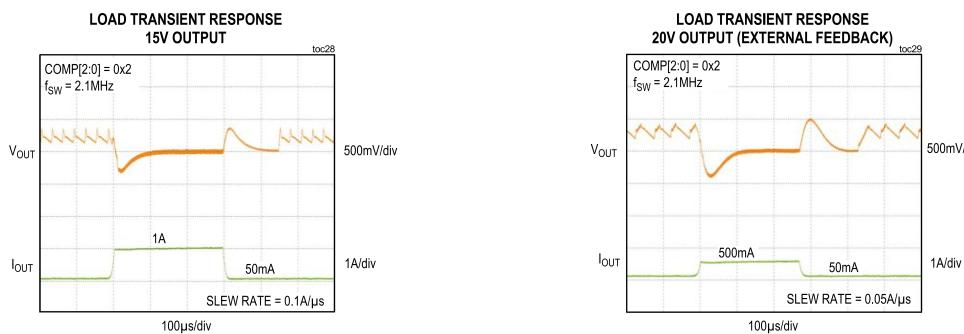

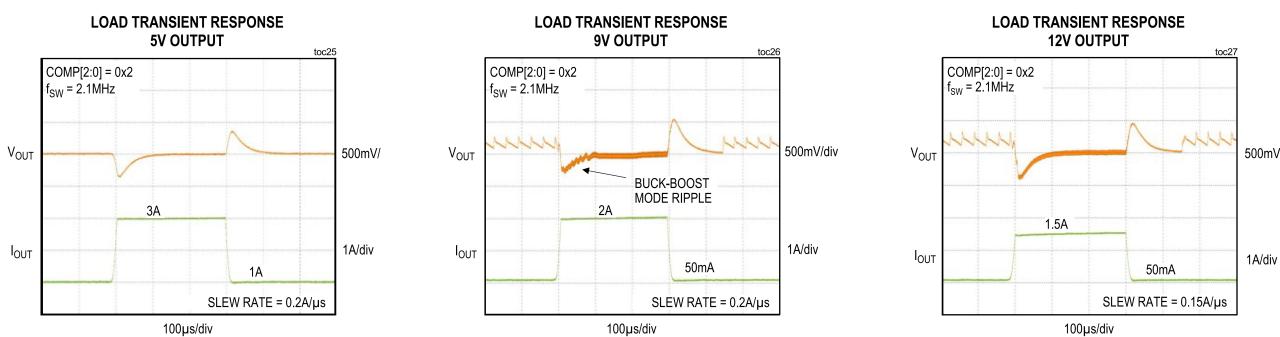

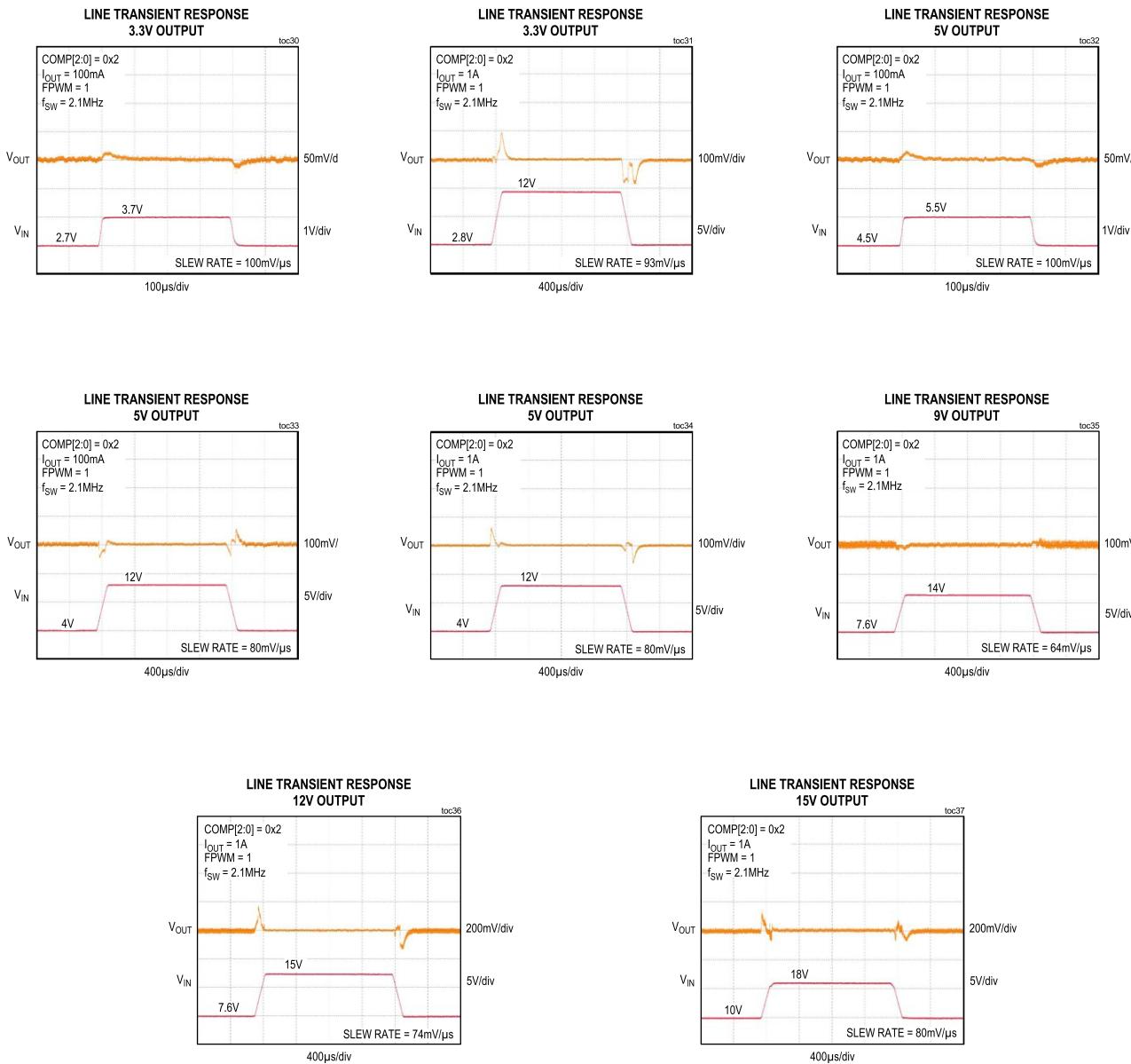

## 標準動作特性（続き）

（特に指定のない限り、 $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $L = 1.5\mu H$ （Coilcraft XGL5020-152ME）、 $C_{OUT} = 2 \times 22\mu F$ 、 $FPWM = 0$ 、 $ILIM[2:0] = 0x0$ （7.8A）、 $f_{sw} = 1.5MHz$ 、内部帰還設定、 $T_A = +25^{\circ}C$ 。Note 4：特に指定のない限り、スイッチング電流の制限値で制限した測定です。実際の最大出力電流はシステムの熱性能によって異なります。）

## 標準動作特性（続き）

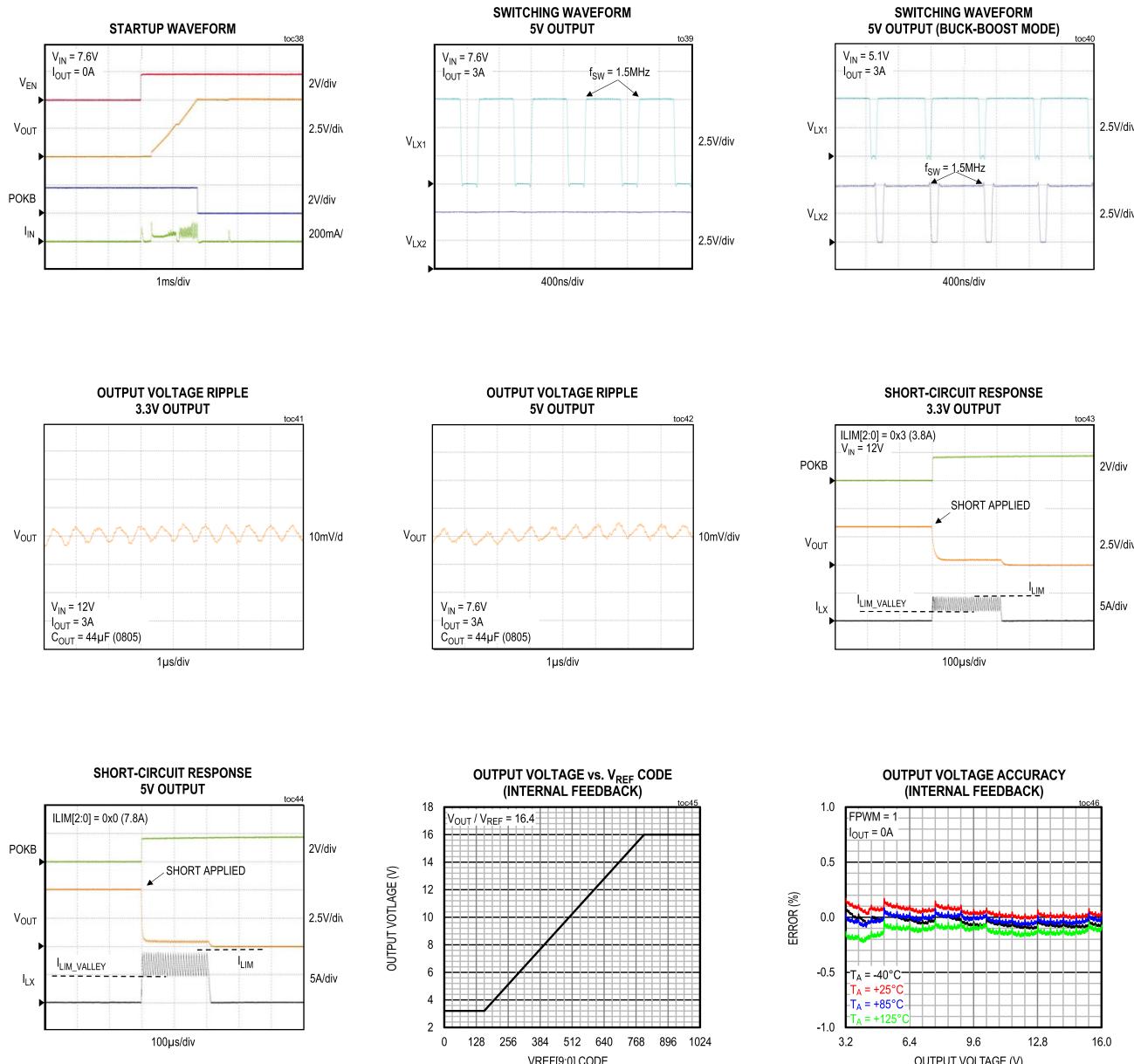

（特に指定のない限り、 $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $L = 1.5\mu H$ （Coilcraft XGL5020-152ME）、 $C_{OUT} = 2x 22\mu F$ 、 $FPWM = 0$ 、 $ILIM[2:0] = 0x0$ （7.8A）、 $f_{SW} = 1.5MHz$ 、内部帰還設定、 $T_A = +25^{\circ}C$ 。Note 4：特に指定のない限り、スイッチング電流の制限値で制限した測定です。実際の最大出力電流はシステムの熱性能によって異なります。）

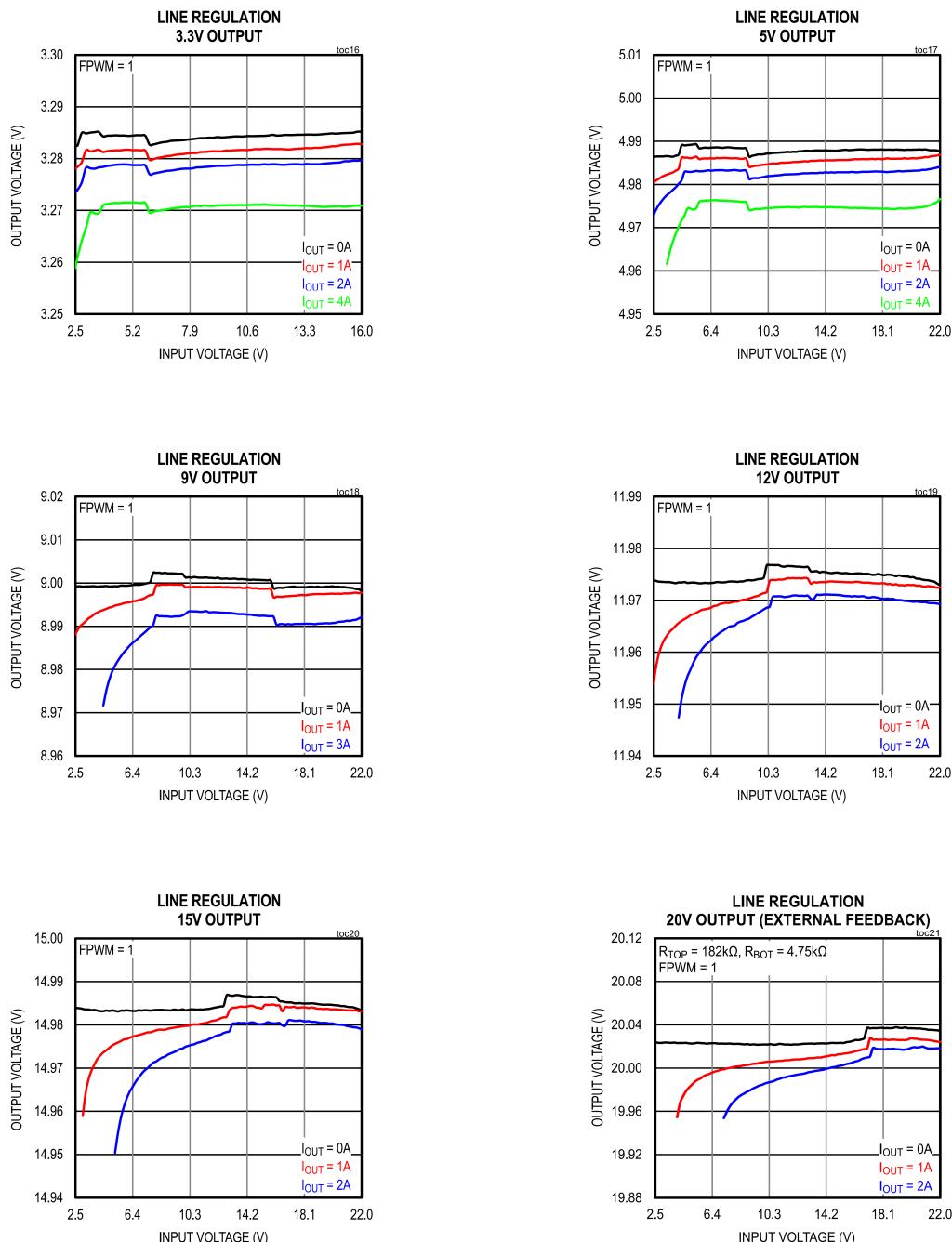

## 標準動作特性（続き）

（特に指定のない限り、 $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $L = 1.5\mu H$ （Coilcraft XGL5020-152ME）、 $C_{OUT} = 2x 22\mu F$ 、 $FPWM = 1$ 、 $ILIM[2:0] = 0x0$ （7.8A）、 $f_{SW} = 1.5MHz$ 、内部帰還設定、 $T_A = +25^{\circ}C$ 。Note 4：特に指定のない限り、スイッチング電流の制限値で制限した測定です。実際の最大出力電流はシステムの熱性能によって異なります。）

## 標準動作特性（続き）

（特に指定のない限り、 $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $L = 1.5\mu H$ （Coilcraft XGL5020-152ME）、 $C_{OUT} = 2 \times 22\mu F$ 、 $FPWM = 0$ 、 $ILIM[2:0] = 0x0$ （7.8A）、 $f_{SW} = 1.5MHz$ 、内部帰還設定、 $T_A = +25^{\circ}C$ 。Note 4：特に指定のない限り、スイッチング電流の制限値で制限した測定です。実際の最大出力電流はシステムの熱性能によって異なります。）

## 標準動作特性（続き）

（特に指定のない限り、 $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $L = 1.5\mu H$ （Coilcraft XGL5020-152ME）、 $C_{OUT} = 2 \times 22\mu F$ 、 $FPWM = 0$ 、 $ILIM[2:0] = 0x0$ （7.8A）、 $f_{sw} = 1.5MHz$ 、内部帰還設定、 $T_A = +25^{\circ}C$ 。Note 4：特に指定のない限り、スイッチング電流の制限値で制限した測定です。実際の最大出力電流はシステムの熱性能によって異なります。）

## 標準動作特性（続き）

（特に指定のない限り、 $V_{IN} = 7.6V$ 、 $V_{OUT} = 5V$ 、 $L = 1.5\mu H$ （Coilcraft XGL5020-152ME）、 $C_{OUT} = 2 \times 22\mu F$ 、 $FPWM = 0$ 、 $ILIM[2:0] = 0x0$ （7.8A）、 $f_{sw} = 1.5MHz$ 、内部帰還設定、 $T_A = +25^{\circ}C$ 。Note 4：特に指定のない限り、スイッチング電流の制限値で制限した測定です。実際の最大出力電流はシステムの熱性能によって異なります。）

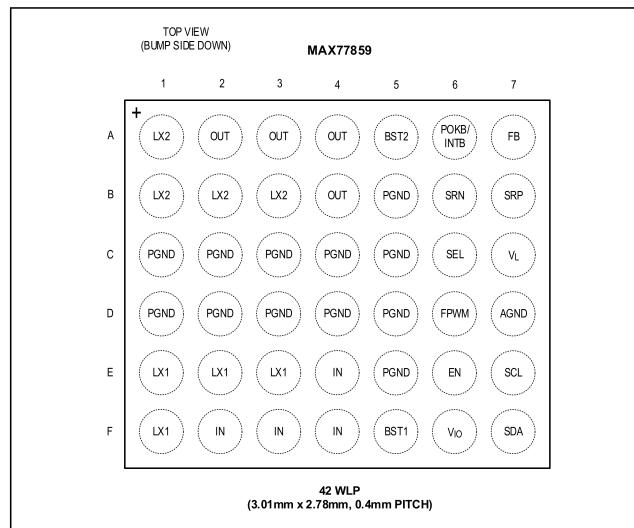

## ピン配置

42 WLP

## 19 FC2QFN

## 端子説明

| ピン                                                            |           | 名称              | 説明                                                                                                                                                                                                                          | タイプ            |

|---------------------------------------------------------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 42 WLP                                                        | 19 FC2QFN |                 |                                                                                                                                                                                                                             |                |

| A1, B1,<br>B2, B3                                             | 1         | LX2             | 昇降圧スイッチング・ノード 2。                                                                                                                                                                                                            | POWER          |

| B5, C1,<br>C2, C3,<br>C4, C5,<br>D1, D2,<br>D3, D4,<br>D5, E5 | 2         | PGND            | 電源グランド。PCB 上の AGND と接続します。詳細については <a href="#">PCB レイアウト時のガイドライン</a> のセクションを参照してください。                                                                                                                                        | Ground         |

| E1, E2,<br>E3, F1                                             | 3         | LX1             | 昇降圧スイッチング・ノード 1。                                                                                                                                                                                                            | Power          |

| F5                                                            | 4         | BST1            | LX1 側ハイサイド FET ドライバの電源。BST1 と LX1 の間に 25V 0.22 $\mu$ F のセラミック・コンデンサを接続します。                                                                                                                                                  | Power Input    |

| E4, F2,<br>F3, F4                                             | 5         | IN              | 昇降圧入力。35V 22 $\mu$ F のセラミック・コンデンサを 2 個使用してできるだけ近くで PGND にバイパスします。                                                                                                                                                           | Power Input    |

| C7                                                            | 6         | V <sub>L</sub>  | 低電圧内部電源。電源は IN から供給されます。10V 2.2 $\mu$ F のセラミック・コンデンサで AGND にバイパスします。この端子には <a href="#">I<sup>2</sup>C レス動作とスタンダードアロン動作</a> のセクションに記載の使用法を除き、外部から負荷を接続しないでください。                                                              | Analog         |

| D7                                                            | 7         | AGND            | アナログ・グランド。PCB 上の PGND と接続します。詳細については <a href="#">PCB レイアウト時のガイドライン</a> のセクションを参照してください。                                                                                                                                     | Ground         |

| F6                                                            | 8         | V <sub>IO</sub> | IO 電圧源。6.3V 0.47 $\mu$ F のセラミック・コンデンサで AGND にバイパスします。この端子の電圧が無効な場合、レジスタはリセット状態に保持されます。                                                                                                                                      | Power Input    |

| E7                                                            | 9         | SCL             | I <sup>2</sup> C シリアル・インターフェースのクロック（オフ状態では高インピーダンス）。1.5k $\Omega$ ~2.2k $\Omega$ のプルアップ抵抗で V <sub>IO</sub> に接続します。                                                                                                          | Digital Input  |

| F7                                                            | 10        | SDA             | I <sup>2</sup> C シリアル・インターフェースのデータ（オフ状態では高インピーダンス）。1.5k $\Omega$ ~2.2k $\Omega$ のプルアップ抵抗で V <sub>IO</sub> に接続します。                                                                                                           | Digital I/O    |

| E6                                                            | 11        | EN              | アクティブ・ハイの昇降圧イネーブル入力。V <sub>IO</sub> の電圧領域と共に、内部で 0.1 $\mu$ A の電流源でプルダウンされています。アプリケーションで EN を IN で制御する必要がある場合（すなわち IN の電圧が有効なら MAX77859 の動作を開始する場合）、詳細については <a href="#">I<sup>2</sup>C レス動作とスタンダードアロン動作</a> のセクションを参照してください。 | Digital Input  |

| A6                                                            | 12        | POKB/INTB       | アクティブ・ロー、オープン・ドレインのステータス／割込み出力。15k $\Omega$ の抵抗で V <sub>IO</sub> に接続します。詳細については <a href="#">パワーOK (POK) およびフォルト・ステータス／割込み</a> のセクションを参照してください。使用しない場合は、この端子を接続しないでください。                                                     | Digital Output |

| D6                                                            | 13        | FPWM            | アクティブ・ハイの強制 PWM モード制御入力。                                                                                                                                                                                                    | Digital Input  |

| C6                                                            | 14        | SEL             | 設定の選択。SEL と AGND の間に抵抗を接続します。抵抗値と設定については <a href="#">表 2</a> を参照してください。                                                                                                                                                     | Analog         |

| B6                                                            | 15        | SRN             | 検出抵抗の負側入力。出力コンデンサと負荷の間に配置した 10m $\Omega$ の検出抵抗の負側の端子と接続します。SRN のパターンは SRP のパターンと平行に、できるだけ短くノイズ源を避けて接続します。検出抵抗を使用しない場合は SRP 端子と短絡します。                                                                                        | Analog         |

| B7                                                            | 16        | SRP             | 検出抵抗の正側入力。出力コンデンサと負荷の間に配置した 10m $\Omega$ の検出抵抗の正側の端子と接続します。SRP のパターンは SRN のパターンと平行に、できるだけ短くノイズ源を避けて接続します。検出抵抗を使用しない場合は SRN 端子と短絡します。                                                                                        | Analog         |

|                |    |      |                                                                                                                                                                                                    |              |

|----------------|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| A7             | 17 | FB   | <b>内部帰還抵抗を使用時 :</b><br>出力電圧検出入力。ポイントオブロードで（出力コンデンサの近くで）出力と接続します。<br><b>外部帰還抵抗を使用時 :</b><br>出力電圧帰還入力。OUT と AGND の間に配置した外部抵抗分圧器の中点に接続して、出力電圧を設定します。詳細については、 <a href="#">出力電圧の設定</a> のセクションを参照してください。 | Analog       |

| A2, A3, A4, B4 | 18 | OUT  | 昇降圧出力。25V 22 $\mu$ F のセラミック・コンデンサを 2 個使用して、できるだけ近くで PGND にバイパスします。                                                                                                                                 | Power Output |

| A5             | 19 | BST2 | LX2 側ハイサイド FET ドライバの電源。BST2 と LX2 の間に 25V 0.22 $\mu$ F のセラミック・コンデンサを接続します。                                                                                                                         | Power Input  |

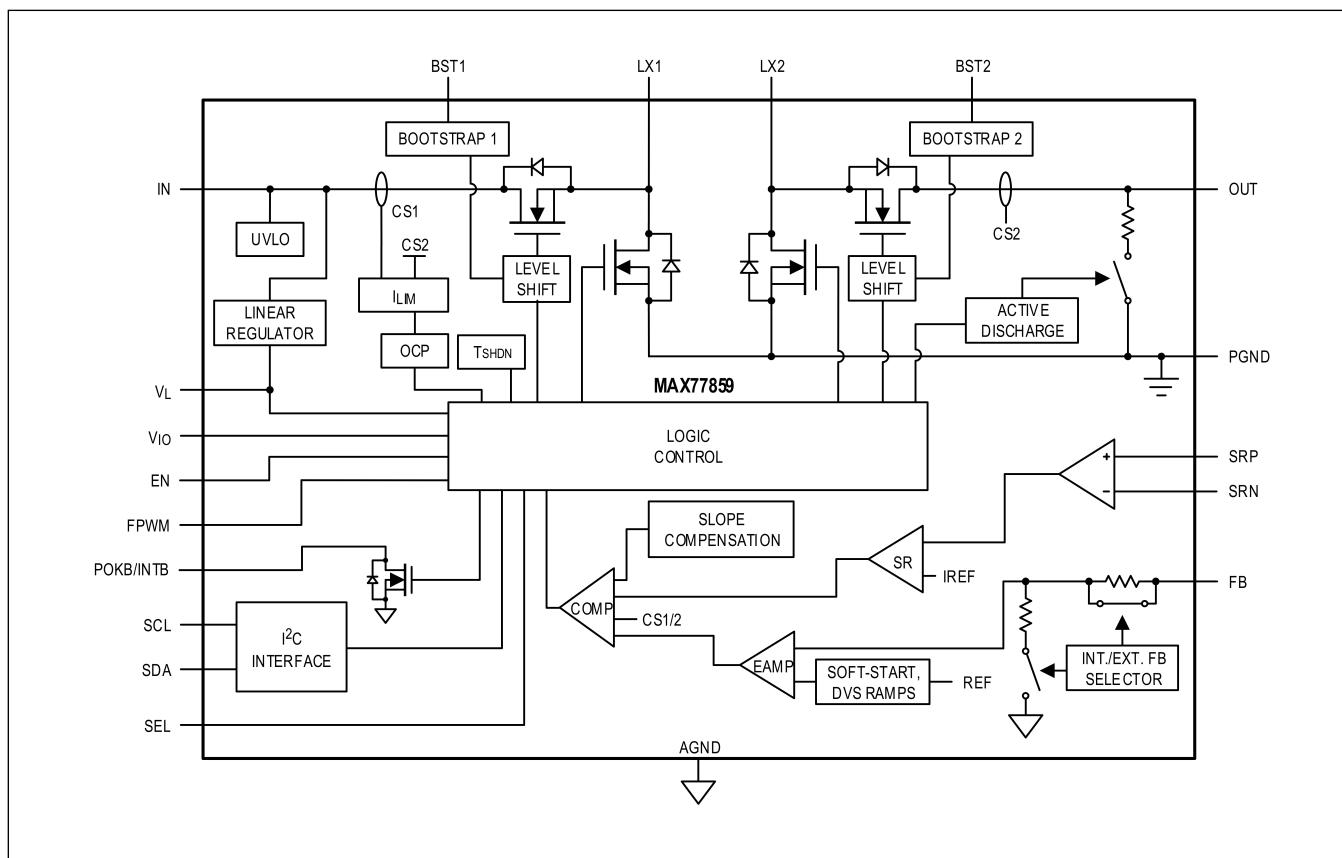

## 機能図

## 詳細

### 概要

MAX77859 は、高効率、高性能の昇降圧コンバータであり、広い入力電圧範囲 (2.5V~22V) が必要なシステム向けに設計されています。この IC は、降圧モードで最大 6A、昇圧モードで最大 4A の出力電流を供給できます ( $V_{IN} = 3.7V$ 、 $V_{OUT} = 5V$ )。この IC を使用すると、システムは I<sup>2</sup>C シリアル・インターフェースを通じて出力電圧を動的に変更できます。MAX77859A は、USB-C PPS 条件を満たすために、I<sup>2</sup>C で調整できる、分解能 50mA/ステップ (検出抵抗 10mΩ) の出力電流制限機能を備えています。MAX77859B は非 PPS バージョンで、低自己消費電流向けに最適化されています。MAX77859 を搭載したシステムは、高速充電周辺機器に高い出力電圧を供給できるため、ケーブル/コネクタ間の電力損失を最小限に抑え、充電時間を短縮できます。

この IC は、効率を最適化するために、動作条件に応じてスキップ・モードまたは強制 PWM (FPWM) モードで動作します。内部帰還抵抗を使用している場合のデフォルトの出力電圧は 5V です。外部帰還抵抗を使用している場合は、3V~20V の範囲内でデフォルトの出力電圧を任意に設定することもできます。出力電圧は、I<sup>2</sup>C シリアル・インターフェースを通じて内部リファレンス電圧をプログラムすることにより、内部帰還抵抗を使用する場合は 3.2V~16V の間 (20mV ステップ) で、外部帰還抵抗を使用する場合は 3V~20V の間 (ステップ・サイズは外部帰還抵抗の比率に依存) で、動的に調整 (DVS) が可能です。詳細については、[出力電圧の設定](#)のセクションを参照してください。

MAX77859A は出力電流制限機能を備えています。10mΩ の検出抵抗を使用する場合、出力電流制限スレッショルドはデフォルト値が 3A で、I<sup>2</sup>C シリアル・インターフェースを通じて 50mA ステップで 1A~5A の間で動的に調整できます。

SEL 端子を使用すると、単一の外部抵抗 RSEL を AGND に接続して、以下をプログラムできます。

- I<sup>2</sup>C シリアル・インターフェースのターゲット・アドレス (4つのオプション)

- スイッチング電流制限のスレッショルド (4つのオプション)

- 帰還抵抗の選択 (内部または外部)

I<sup>2</sup>C インターフェースの様々なターゲット・アドレスに対応できるため、I<sup>2</sup>C バスが限られたシステム中で複数のデバイスを使用できます。様々なスイッチング電流制限スレッショルドが選択できるため、特定のアプリケーションに対して最適化された、より値が小さくプロファイルが小さい外付け部品を使用できます。外部帰還抵抗を使用することにより、広い出力電圧範囲が得られ、起動時に出力電圧をカスタマイズできます。詳細については、[SEL 端子の設定](#)のセクションを参照してください。

オプションの I<sup>2</sup>C シリアル・インターフェースにより、以下の項目を動的に制御できます。

- 出力電圧 (内部リファレンス電圧により)

- 出力電圧変化のスルーレート (4つのオプション)

- 出力電流制限スレッショルド (MAX77859A のみ)

- スイッチング電流制限スレッショルド (8つのオプション)

- スイッチング周波数 (4つのオプション)

- 強制 PWM モード動作

- パワーOK (POK) およびフォルト・ステータス/割込み

- 内部補償

様々なスイッチング周波数が可能であるため、EMI の影響が及びやすい周波数帯域を避けることによって EMI 性能を改善する選択肢が得られます。I<sup>2</sup>C による設定は、RSEL のデコードによる設定よりも優先します。

## スタートアップ

図 1. 起動時の波形

スタートアップ動作については図 1 を参照してください。入力電圧  $V_{IN}$  が UVLO スレッショルドの  $V_{UVLO\_R}$  より高く、EN 端子がロジック・ハイのとき、IC はまず内部バイアス回路をオンにする ( $V_L$ ) ことから起動を開始しますが、この安定には通常  $100\mu s$  ( $t_{SUDLY}$ ) の時間を要します。続いて IC は SEL 端子の抵抗を検出して、I<sup>2</sup>C インターフェースのターゲット・アドレスを設定し、電流制限スレッショルドを切り替え、内部もしくは外部の帰還抵抗を選択します。R<sub>SEL</sub>の読み取りが完了するには代表値で  $200\mu s$  ( $t_{SEL}$ ) かかります。詳細については、[SEL 端子の設定](#)のセクションを参照してください。次に IC は  $V_{IO}$ の電圧が有効か確認します。有効であれば、I<sup>2</sup>C インターフェースを有効にし、昇降圧のソフトスタート・プロセスを開始します（[ソフトスタート](#)のセクションを参照）。

EN がロジック・ハイにトグルしたとき、もし前のシャットダウン・イベントによる出力のアクティブ放電が継続していれば、IC はアクティブ放電が終了するのを待ってから起動シーケンスを開始します。

内部レギュレータ  $V_L$  を使用して  $V_{IO}$ 端子または  $V_{IN}$ 端子に電力を供給して EN 端子を制御することも可能です。詳細については、[I<sup>2</sup>C レス動作とスタンダロン動作](#)のセクションを参照してください。

## ソフトスタート

起動中にシステム電源から大量の入力電流が引き込まれるのを防ぐため、MAX77859 はソフトスタート機能を備えています。デフォルトのソフトスタート時間 ( $t_{ss}$ ) は  $1.7ms$  (代表値) です。ソフトスタート中は、内部リファレンス電圧 ( $V_{REF}$ ) が目標のレベルまで徐々にランプアップします。ソフトスタート中のスイッチング電流制限スレッショルドは、 $I_{LIM}$  の設定が (R<sub>SEL</sub>によって)  $3.8A$  よりも高く設定されている場合には、 $3.8A$  まで低減されます。 $I_{LIM}$  の設定が  $3.8A$  以下の場合には、ソフトスタート中も同じスイッチング電流制限スレッショルドが適用されます。ソフトスタートが終了すれば、通常のスイッチング電流制限スレッショルドが適用されます。

## シャットダウン

EN ピンをロジック・ローにプルダウンすると、IC をシャットダウンします。シャットダウン時には IC はスイッチングを停止し、全レジスタをリセットし、出力アクティブ放電を開始します。アクティブ放電は、出力電圧 ( $V_{OUT}$ ) が 2.5V (代表値) を下回るか 600ms 経過するか、いずれか早い方まで継続します。

## 即時ラッチオフ条件

この IC にはラッチオフ機能があり、特定のフォルト条件で昇降圧レギュレータをシャットダウンすることによりデバイス自体を保護します。

即時シャットダウンの条件：

- IN の UVLO :  $V_{IN} < V_{UVLO\_F}$  (入力 UVLO の立下がりスレッショルド)

- $V_{IO}$  の UVLO :  $V_{IO} < V_{IO\_VALID\_F}$  (出力  $V_{IO}$  の立下がりスレッショルド)

ラッチオフの条件：

- サーマル・シャットダウン :  $T_J > T_{SHDN\_R}$  (サーマル・シャットダウン (THS) のセクションを参照)

- 短絡 :  $I_{LIM}$  タイマー > 427μs (スイッチング電流の過電流保護 (SW OCP) のセクションを参照)

このカテゴリのイベントは、危険につながるシステム状態に関連しています。即時シャットダウン条件では、IC は昇降圧レギュレータと I<sup>2</sup>C シリアル通信バスをシャットダウンし、全レジスタをリセットして、システムがフォルト条件から回復するのを待ちます。ラッチオフ条件では、IC は昇降圧レギュレータの出力のみをシャットダウンし、I<sup>2</sup>C シリアル通信バスはアクティブな状態を維持し、レジスタの状態を保存します。ラッチオフから回復するには、システムからフォルト条件が除去され、EN 端子または IN 端子に電源を再投入することが必要です。昇降圧レギュレータがシャットダウンするとき、サーマル・シャットダウンによる場合を除いて全てのフォルト条件で、アクティブ放電が作動します。詳細については、[出力のアクティブ放電](#)のセクションを参照してください。

## 出力のアクティブ放電

この IC は出力コンデンサに蓄えられたエネルギーを PGND に放電するパスを形成する内部スイッチを備えています。出力のアクティブ放電は、昇降圧レギュレータが停止されるときには常に有効になります (シャットダウン・イベントや即時ラッチオフ条件に記載の何らかの条件による場合、ただしサーマル・シャットダウンを除く)。放電電流の大きさは、 $V_{OUT}$  が 15V のとき代表値 5mA で、放電中に  $V_{OUT}$  が低下するのにつれて減少します。アクティブ放電が有効となっている場合は、EN 端子の信号は無視されます。 $V_{OUT}$  が 2.5V (代表値) より下がるか、600ms のタイマーが終了するか、いずれか早い方でアクティブ放電は停止します。昇降圧レギュレータの動作中、内部放電スイッチは出力から切り離されます。

## 昇降圧レギュレータ

MAX77859 の昇降圧レギュレータは 4 スイッチの H ブリッジ構成を使用し、降圧、昇圧、3 相の動作モードで動作します。このトポロジにより、入力電圧範囲全域にわたって出力電圧レギュレーションを維持できます。この昇降圧レギュレータは、3V~20V の範囲の電圧を出力し、最大 4 セルのリチウムイオン・バッテリ駆動のアプリケーションに最適です。高いスイッチング周波数と独自の制御アルゴリズムにより、ソリューション・サイズを小さくすることでき、出力ノイズが低く、広い範囲の入力電圧と出力電流に対して最高の効率を達成します。

## 昇降圧制御方式

昇降圧レギュレータは、電流モード補償付きの固定周波数のパルス幅変調 (PWM) 制御方式を使用して動作します。1 個のインダクタを使用する H ブリッジ方式を使用します。デフォルトのスイッチング周波数は 1.5MHz です。ビットフィールド FREQ[1:0]によってスイッチング周波数を設定します。スイッチング周波数を選択できるため、EMI の影響が及びやすい周波数帯域を避けるオプションが得られ、EMI 性能を改善できます。

H ブリッジ方式には図 2 に示すように 3 つのスイッチング・フェーズがあります。

- Φ1 スイッチ・フェーズ (HS1 = ON、LS2 = ON) ではインダクタにエネルギーを蓄え、入力電圧をインダクタンスで割った値  $V_{IN}/L$  に比例したレートでインダクタ電流がランプアップします。

- Φ2 スイッチ・フェーズ (HS1 = ON、HS2 = ON) では、インダクタ両端の差動電圧 ( $V_{IN} - V_{OUT}$ )/L に比例したレートで、インダクタ電流がランプアップ (降圧モード) またはランプダウン (昇圧モード) します。

- Φ3 スイッチ・フェーズ (LS1 = ON、HS2 = ON) ではインダクタからエネルギーを放出し、出力電圧をインダクタンスで割った値  $-V_{OUT}/L$  に比例したレートで、インダクタ電流がランプダウンします。

昇圧モード動作 ( $V_{IN} < V_{OUT}$ ) では、1 クロック期間中に  $\Phi 1$  と  $\Phi 2$  を使用します。図 2 に示す昇圧モード動作のインダクタ電流波形を参照してください。降圧モード動作 ( $V_{IN} > V_{OUT}$ ) では、1 クロック期間中に  $\Phi 2$  と  $\Phi 3$  を使用します。図 2 に示す降圧モード動作のインダクタ電流波形を参照してください。3 相モード動作 ( $V_{IN} \approx V_{OUT}$ ) では、1 クロック期間中に  $\Phi 1$ 、 $\Phi 2$ 、 $\Phi 3$  を使用します。図 2 に示す 3 相モード動作のインダクタ電流波形を参照してください。

図 2. 升降圧 H ブリッジ方式

### スキップ・モードと強制 PWM (FPWM) モード

この IC は、効率改善のために、無負荷時や軽負荷時には自動的にスキップ・モード動作に入ります。スキップ・モードでは、出力電圧  $V_{OUT}$  はスキップ・モードの上限スレッショルド ( $V_{SKIP\_UPPER}$ ) と下限スレッショルド ( $V_{SKIP\_LOWER}$ ) の間でレギュレーションされ、この代表値は出力電圧の目標値 ( $V_{TARGET}$ ) よりそれぞれ 3%および 1%高い値です。出力負荷の条件と入出力電圧の比に応じて、IC は自動的にスキップ・モードから PWM モードに遷移します。

FPWM 端子をロジック・ハイにアサートするか、I<sup>2</sup>C シリアル・インターフェースで FPWM[0]ビットフィールドに 1 を書き込むことによっても、PWM モード動作を有効にすることができます。この方法では、出力の負荷電流によらず強制的に PWM モードで動作します。強制 PWM (FPWM) モードは、出力リップルを最小化する必要があるアプリケーションについて有利です。一方スキップ・モードは軽負荷時の昇降圧レギュレータの効率を最大化することができます。

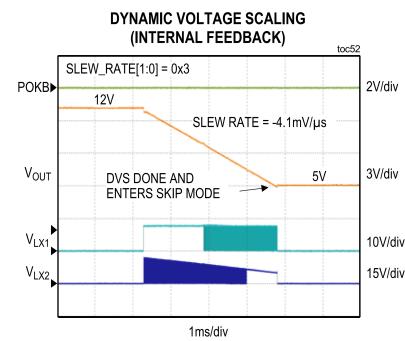

FPWM 端子や FPWM[0]ビットフィールドの設定にかかわらず、 $V_{OUT}$  が異なる  $V_{TARGET}$  に変更されたとき (DVS) には、IC は遷移を高速化するために FPWM モードに入ります。高い  $V_{OUT}$  から低い電圧に遷移する DVS イベント中は、IC は  $V_{OUT}$  が遷移前の  $V_{TARGET}$  に対する  $V_{SKIP\_LOWER}$  を下回ったときに FPWM モードに入り、 $V_{OUT}$  が新しい  $V_{TARGET}$  の  $V_{SKIP\_UPPER}$  より低くなるまで FPWM モードを継続します。その後、 $V_{OUT}$  は出力負荷条件に従って自然に低下し、 $V_{SKIP\_LOWER}$  まで下がるとスキップ・モードのスイッチング・サイクルを再開します。図 3 は DVS 中のこうした動作を示しています。

図 3. スキップ・モードのスレッショルドと DVS 中の FPWM モード動作

## 出力電圧の設定

この IC は、内部帰還抵抗を使用時は 3.2V~16V、外部帰還抵抗を使用時は 3.0V~20V と広い範囲の出力電圧をサポートしています。内部帰還抵抗を使用すると外部部品が少なく全体のソリューション・サイズが小さくなるメリットが得られ、外部帰還抵抗を使用する場合にはより広い範囲の出力電圧が設定可能で、I<sup>2</sup>C シリアル・インターフェースを使用しないでも起動時に出力電圧 V<sub>OUT</sub> をカスタマイズ設定できます。内部帰還抵抗と外部帰還抵抗のどちらを使用するかは、R<sub>SEL</sub> で設定します。詳細については、[SEL 端子の設定](#)のセクションを参照してください。

### 内部帰還抵抗の設定

内部帰還抵抗を使用するとき、V<sub>OUT</sub> の範囲は 20mV ステップで 3.2V~16V です。デフォルトの V<sub>OUT</sub> は 5V (V<sub>REF</sub> = 0.30518V) です。内部帰還抵抗を使用するように IC を設定するためには、適切な値の R<sub>SEL</sub> を使用し、FB 端子を近傍の出力コンデンサの地点で直接 OUT 端子に接続します。

### 外部帰還抵抗の設定

外部帰還抵抗を使用するとき、V<sub>OUT</sub> の範囲は 3.0V~20V です。実際の出力電圧の範囲とステップ幅は外部帰還抵抗の比率によって決まります。外部帰還抵抗を使用するように IC を設定するためには、適切な値の R<sub>SEL</sub> を使用し、OUT、FB、AGND の間に図 4 に示すように抵抗分圧器を接続します。V<sub>OUT</sub> が 6V 以下の場合には、上側の帰還抵抗 (R<sub>TOP</sub>) と並列に 10pF のフィードフォワード・コンデンサ (C<sub>FF</sub>) を追加することを推奨します。R<sub>TOP</sub> (OUT と FB の間) は 150kΩ~330kΩ のものを選択します。V<sub>OUT</sub> の精度を保つために、許容誤差が 1%以下の抵抗を強く推奨します。動作範囲中の目的とする V<sub>OUT</sub> を起動時に決定するため、R<sub>BOT</sub> (FB と AGND の間) は次式によって計算します。

$$R_{BOT} = \frac{R_{TOP} \times V_{REF}}{V_{OUT} - V_{REF}}$$

ここで、V<sub>REF</sub> はデフォルト内部リファレンス電圧です。

図 4. MAX77859 への外部帰還抵抗の接続

表 1 は、デフォルトの  $V_{REF}$  である 0.30518V を前提に、標準的な起動時出力電圧に対する推奨の外部帰還抵抗の値 (E192 系列) を示しています。

表 1. 帰還抵抗の推奨値

| DEFAULT<br>$V_{REF}$ (V) | $R_{TOP}$ (k $\Omega$ )     | $R_{BOT}$ (k $\Omega$ ) | STARTUP<br>$V_{OUT}$ (V) | PROGRAMMABLE<br>$V_{OUT}$ RANGE (V) | $V_{OUT}$ STEP SIZE<br>(mV) |

|--------------------------|-----------------------------|-------------------------|--------------------------|-------------------------------------|-----------------------------|

| 0.30518                  | 205                         | 23.2                    | 3                        | 3.0 to 9.61                         | 12                          |

|                          | 162                         | 16.5                    | 3.3                      | 3.0 to 10.56                        | 13.2                        |

|                          | Internal Feedback Resistors |                         | 5                        | 3.2 to 16                           | 20                          |

|                          | 160                         | 5.62                    | 9                        | 5.76 to 20                          | 36                          |

|                          | 182                         | 4.75                    | 12                       | 7.68 to 20                          | 48                          |

|                          | 180                         | 3.74                    | 15                       | 9.6 to 20                           | 60                          |

|                          | 330                         | 5.11                    | 20                       | 12.81 to 20                         | 80                          |

### ダイナミック電圧スケーリング (DVS)

$V_{REF}$  を I<sup>2</sup>C シリアル・インターフェースで設定することにより、 $V_{OUT}$  を動的に調整できます。ビットフィールド VREF[9:0]によって  $V_{REF}$  を設定します。 $V_{REF}$  の範囲は 1.22mV ステップで 0.19531V~0.97656V です。内部帰還抵抗を使用する場合、 $V_{OUT}$  の範囲は 20mV ステップで 3.2V~16V で、次式によって計算できます。

$$V_{OUT} = V_{REF} \times 16.4$$

外部帰還抵抗を使用する場合、 $V_{OUT}$  の範囲とステップ幅は外付けの帰還抵抗の値によって変わります。 $V_{OUT}$  のステップ幅は次式によって計算できます。

$$V_{OUT\_STEP} = \left( \frac{1.22mV}{R_{BOT}} \right) \times (R_{BOT} + R_{TOP})$$

$V_{OUT}$  の範囲を計算するには、次式を使用し、 $V_{REF}$  の最小値 0.19531V と  $V_{REF}$  の最大値 0.97656V を代入します。

$$V_{OUT} = \left( \frac{V_{REF}}{R_{BOT}} \right) \times (R_{BOT} + R_{TOP})$$

V<sub>OUT</sub>を最大出力電圧の20Vより高く設定しないでください。ICが損傷するおそれがあります。

ビットフィールド VREF[9:0]はレジスタ内では VREF\_U[1:0]と VREF\_L[7:0]に分割され、VREF\_U[1:0]が上位 2 ビット、VREF\_L[7:0]が下位 8 ビットを表します。VREF[9:0]の更新後には DVS\_STR[0]ビットフィールドに 1 を書き込むと、DVS を起動して新しい V<sub>REF</sub> 設定を適用します。このビットは、DVS が完了するか VREF[9:0]に変化がなければ、セルフクリアされます。

ビットフィールド SLEW\_RATE[1:0]は V<sub>REF</sub> の DVS ランプ・レート ( $\Delta V_{REF}/\Delta t$ ) を設定し、デフォルト値は 1mV/ $\mu$ s です。実際の V<sub>OUT</sub> の DVS ランプ・レート ( $\Delta V_{OUT}/\Delta t$ ) は、V<sub>REF</sub> の DVS ランプ・レート ( $\Delta V_{REF}/\Delta t$ ) から上記の外部帰還抵抗の式を使って計算できます。例えば、内部帰還抵抗を使用していれば、 $\Delta V_{REF}/\Delta t$  のデフォルトの 1mV/ $\mu$ s に対し  $\Delta V_{OUT}/\Delta t$  は 16.4mV/ $\mu$ s になります。

## SEL 端子の設定

SEL 端子によって、1 つの抵抗 (R<sub>SEL</sub>) を SEL 端子と AGND の間に接続することで、ハイサイド・スイッチング電流制限スレッショルド (I<sub>LIM</sub>)、I<sup>2</sup>C シリアル・インターフェースのターゲット・アドレス、帰還抵抗の内部／外部選択を設定できます。R<sub>SEL</sub> には許容誤差が 1% 以下の抵抗を使用する必要があります。表 2 は R<sub>SEL</sub> の公称値と、対応する設定を示しています。

表 2. MAX77859 の R<sub>SEL</sub> 選択表

| R <sub>SEL</sub> (Ω) | FEEDBACK RESISTOR SELECTION | TYPICAL I <sub>LIM</sub> (A) | I <sup>2</sup> C TARGET ADDRESS (7-BIT) | R <sub>SEL</sub> (Ω) | FEEDBACK RESISTOR SELECTION | TYPICAL I <sub>LIM</sub> (A) | I <sup>2</sup> C TARGET ADDRESS (7-BIT) |

|----------------------|-----------------------------|------------------------------|-----------------------------------------|----------------------|-----------------------------|------------------------------|-----------------------------------------|

| SHORT TO GND         | Internal Feedback Resistors | 7.8                          | 110 0110 (0x66)                         | 3740                 | External Feedback Resistors | 7.8                          | 110 0110 (0x66)                         |

| 200                  |                             |                              | 110 0111 (0x67)                         | 8060                 |                             |                              | 110 0111 (0x67)                         |

| 309                  |                             |                              | 110 1110 (0x6E)                         | 12400                |                             |                              | 110 1110 (0x6E)                         |

| 422                  |                             |                              | 110 1111 (0x6F)                         | 16900                |                             |                              | 110 1111 (0x6F)                         |

| 536                  |                             | 5.8                          | 110 0110 (0x66)                         | 21500                |                             | 5.8                          | 110 0110 (0x66)                         |

| 649                  |                             |                              | 110 0111 (0x67)                         | 26100                |                             |                              | 110 0111 (0x67)                         |

| 768                  |                             |                              | 110 1110 (0x6E)                         | 30900                |                             |                              | 110 1110 (0x6E)                         |

| 909                  |                             |                              | 110 1111 (0x6F)                         | 36500                |                             |                              | 110 1111 (0x6F)                         |

| 1050                 |                             | 3.8                          | 110 0110 (0x66)                         | 42200                |                             | 3.8                          | 110 0110 (0x66)                         |

| 1210                 |                             |                              | 110 0111 (0x67)                         | 48700                |                             |                              | 110 0111 (0x67)                         |

| 1400                 |                             |                              | 110 1110 (0x6E)                         | 56200                |                             |                              | 110 1110 (0x6E)                         |

| 1620                 |                             |                              | 110 1111 (0x6F)                         | 64900                |                             |                              | 110 1111 (0x6F)                         |

| 1870                 |                             | 2.0                          | 110 0110 (0x66)                         | 75000                |                             | 2.0                          | 110 0110 (0x66)                         |

| 2150                 |                             |                              | 110 0111 (0x67)                         | 86600                |                             |                              | 110 0111 (0x67)                         |

| 2490                 |                             |                              | 110 1110 (0x6E)                         | 100000               |                             |                              | 110 1110 (0x6E)                         |

| 2870                 |                             |                              | 110 1111 (0x6F)                         | OPEN                 |                             |                              | 110 1111 (0x6F)                         |

## 内部補償オプション

性能を最適化しようとする設計では、内部補償調整用の COMP[2:0]ビットフィールドを I<sup>2</sup>C シリアル・インターフェース経由で使用できます。I<sup>2</sup>C シリアル・インターフェースを使用しないシステムでは、出力容量の調整によって安定性を最適化できます。一般的には、COMP[2:0]ビットフィールドの値の低減または出力容量の追加によって、性能を更に改善できます。

## パワーOK (POK) およびフォルト・ステータス/割込み

この IC は、昇降圧出力のレギュレーション状態をモニタするパワーOK (POK) コンパレータと、何らかの危険な状態があれば提示するフォルト・ステータス/割込みを備えています。レジスタ 0x10 (STATS) 中の POK とフォルト・ステータス・ビットは IC の状態をリアルタイムで反映し、レジスタ 0x11 (INT) の個別の割込みビットは、対応するフォルト状態が発生するとトリガされ、ラッピングされて、読み出します。

昇降圧レギュレータが動作中は、実際の  $V_{OUT}$  のレベルに基づいて POK が継続的に更新されます。POK ビットは  $V_{OUT}$  が目標電圧の 85% (代表値) を下回ると 0 になり、目標電圧の 93% (代表値) を超えると 1 に変化します。ソフトスタート中もしくは DVS イベント中は、POK モニタの更新は一時的にディスエーブルされ、POK ビットはソフトスタートもしくは DVS イベントの前の値を保持しています。POK モニタの更新は、ソフトスタートもしくは DVS が終了すると再開します。

この IC にはいくつかのフォルト・イベントのモニタ機能があります。以下のフォルト・イベントはどれも、STATS レジスタと INT レジスタの対応するビットをアサートします。

- HARDSHORT : スイッチング電流の過電流保護 (SW OCP) のセクションを参照

- THS : サーマル・シャットダウン (THS) のセクションを参照

- OCP : スイッチング電流の過電流保護 (SW OCP) のセクションを参照

フォルト割込みビットは、レジスタ 0x12 (MASK) の対応するマスク・ビットフィールドに 1 を書き込むことにより、作動しないようマスクできます。例えば、MASK レジスタの THM\_M ビットフィールドが 1 のとき、INT レジスタの THM\_I ビットフィールドはサーマル・シャットダウン・イベントが発生してもセットされません。

また、この IC はアクティブ・ロー、オープン・ドレインの POKB/INTB デジタル出力端子を備えています。15k $\Omega$  のプルアップ抵抗を使用して、POKB/INTB 端子を  $V_{IO}$  に接続します。この端子は、レジスタ 0x14 (REG\_CONT2) の POKBINTB[0] ビットによる選択で、次のように POK 端子またはフォルト割込み端子のいずれかとして構成できます。

- POKBINTB[0] = 0 : POK 端子 (POKB)。

- POKBINTB[0] = 1 : フォルト割込み端子 (INTB)。

この端子が POK 端子として構成されている場合、POKB/INTB 端子のデジタル出力信号はレジスタ 0x10 (STATS) の POK ビットの論理 NOT であり、すなわち  $V_{OUT}$  が POK スレッショルドより高いときにロジック・ローになります。[表 3](#) は、POKB/INTB 端子が POK 端子として構成されているときの真理値表です。

表 3. POKB/INTB 端子の真理値表 (POKBINTB = 0b0)

| $V_{OUT}$ CONDITION       | POK BIT | POKB/INTB PIN |

|---------------------------|---------|---------------|

| $V_{OUT} < POK$ threshold | 0       | HIGH          |

| $V_{OUT} > POK$ threshold | 1       | LOW           |

この端子がフォルト割込み端子として構成されている場合、POKB/INTB 端子の信号はレジスタ 0x11 (INT) 中のマスクされていない全てのビットの論理 NOR となります。すなわちマスクされていないフォルト割込みイベントが 1 つでもあるときにロジック・ローになります。[表 4](#) は POKB/INTB 端子がフォルト割込み端子として構成されたときの真理値表を、全割込みビットのマスクが解除された条件 (MASK = 0x00) で示しています。

表 4. POKB/INTB 端子の真理値表 (POKBINTB = 0b1)

| HARDSHORT | THS | OCP | POKB/INTB PIN |

|-----------|-----|-----|---------------|

| 0         | 0   | 0   | HIGH          |

| 1         | X   | X   | LOW           |

| X         | 1   | X   | LOW           |

| X         | X   | 1   | LOW           |

\*全割込みビットのマスクを解除 (MASK = 0x00) している場合

## 保護機能

### 低電圧ロックアウト (UVLO)

この IC の低電圧ロックアウト機能は、入力電圧  $V_{IN}$  が IN の UVLO 立下がりスレッショルド ( $V_{UVLO\_F}$ ) を下回ったとき、または  $V_{IO}$  の電圧 ( $V_{VIO}$ ) が  $V_{IO}$  有効の立下がりスレッショルド ( $V_{VIO\_VALID\_F}$ ) を下回ったときに、異常な入力条件での動作を防止します。EN 端子の状態にかかわらず、IC はディスエーブルされ、全レジスタがリセットされ、 $V_{IN}$  が IN の UVLO 立上がりスレッショルド ( $V_{UVLO\_R}$ ) を超え、 $V_{IO}$  が  $V_{IO}$  有効の立上がりスレッショルド ( $V_{VIO\_VALID\_R}$ ) を超えるのを待ちます。

### スイッチング電流の過電流保護 (SW OCP)

この IC は、過負荷や高速トランジエント条件で IC やインダクタを保護するために、信頼性の高いスイッチング電流制限方式を備えています。スイッチング電流検出回路はハイサイド MOSFET から電流情報を読み取り、ピーク・スイッチング電流 ( $R_{DS(ON)} \times I_L$ ) を決定します。

この IC には、多様な出力電流レベルに対応できるよう、ハイサイド MOSFET に対して 8 通りのサイクルごとのスイッチング電流制限スレッショルド ( $I_{LIM}$ ) を設けています。ビットフィールド ILIM[2:0] もしくは  $R_{SEL}$  レジスタの値で  $I_{LIM}$  を設定します。I<sup>2</sup>C シリアル・インターフェースでは 8 つのオプションが全て設定できるのに対し、 $R_{SEL}$  では 4 つのオプションだけが選択できることに注意してください。I<sup>2</sup>C シリアル・インターフェースによる  $I_{LIM}$  の設定と  $R_{SEL}$  による設定が異なる場合には、I<sup>2</sup>C の設定が  $R_{SEL}$  より優先します。

インダクタ電流 ( $I_L$ ) が設定されたピーク電流制限値 ( $I_{LIM}$ ) に達すると、IC は OCP 状態に入り OCP[0]ステータス・ビットがセットされます。インダクタの充電フェーズが終了し、スイッチング期間の残りの時間は放電フェーズ ( $\Phi_3$ ) で動作します。充電フェーズは次のクロック・サイクルで再び開始します。インダクタ電流が  $I_{LIM}$  に達しないようになっていれば、OCP[0]ステータス・ビットはセルフクリアされます。

$V_{OUT}$  が目標の 70%を下回ると、IC は短絡ステータスに入り、HARDSHORT[0]ステータス・ビットがセットされます。OCP 状態と同様に、インダクタの充電フェーズが終了し、放電フェーズ ( $\Phi_3$ ) が開始します。この放電フェーズは、OCP 状態と異なり、インダクタ電流がバレー電流制限スレッショルド ( $I_{LIM\_VALLEY}$ ) 未満に下がるまでは終了せず、その後にインダクタ充電フェーズに入ります。その結果、短絡状態における実効スイッチング周波数は、レジスタの FREQ[1:0]ビットフィールドで設定された通常のスイッチング周波数とは異なります。選択可能な  $I_{LIM}$  オプションと、対応する  $I_{LIM\_VALLEY}$  値については、表 5 を参照してください。HARDSHORT[0]ステータス・ビットは、 $V_{OUT}$  が目標の 70%を下回らないようになればセルフクリアされます。

表 5. MAX77859 のスイッチング電流制限値のオプション

| ILIM[2:0]<br>BITFIELD VALUE | PEAK<br>CURRENT LIMIT<br>( $I_{LIM}$ ) | VALLEY<br>CURRENT LIMIT<br>( $I_{LIM\_VALLEY}$ ) | SOFT-START<br>CURRENT LIMIT<br>( $I_{LIM\_SS}$ ) | SKIP MODE<br>CURRENT LIMIT<br>( $I_{LIM\_SKIP}$ ) |

|-----------------------------|----------------------------------------|--------------------------------------------------|--------------------------------------------------|---------------------------------------------------|

| 000 (0x0)                   | 7.8A                                   | 3.8A                                             | 3.8A                                             | 1.2A                                              |

| 001 (0x1)                   | 6.8A                                   |                                                  |                                                  |                                                   |