**HDMI 2:1低周波変換スイッチ****MAX4929E****概要**

低周波数2:1スイッチのMAX4929Eは、HDMI™/DVI™スイッチングアプリケーションに最適です。このデバイスは、電圧クランプ機能を備え、出力の低電圧システムを保護します。MAX4929Eは、5Vの単一電源またはデュアルまたはトリプル電源で動作します。MAX4929Eは、追加部品なしでクランプと電圧変換を行うことができます。すべての外部入力/出力は、 $\pm 6\text{kV}$ ヒューマンボディモデル(HBM)に対してESD(静電放電)保護されています。

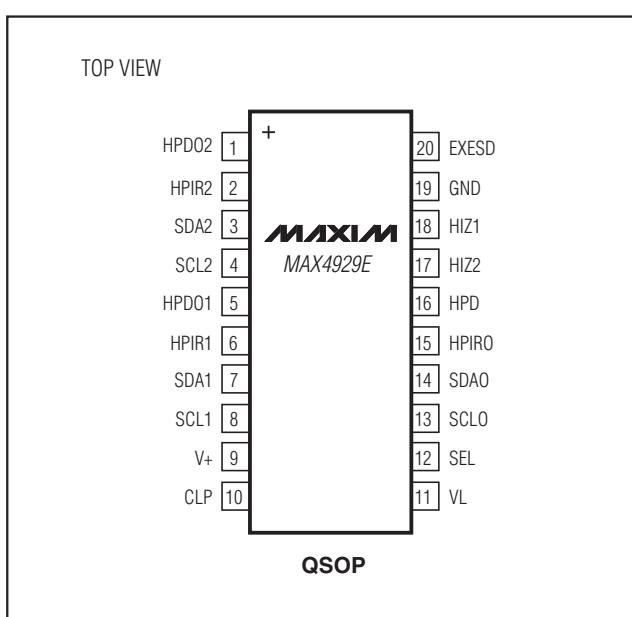

MAX4929Eは、20ピンQSOPパッケージ、および20ピンTQFNパッケージ(4mm x 4mm)で提供されます。このデバイスは、-40°C～+85°Cの拡張温度範囲での動作が保証されています。

**アプリケーション**

HDテレビレシーバ

HDモニタ

高画質コンピュータモニタ

HDMIはHDMI Licensing, LLCの商標です。

DVIはDigital Display Working Group (DDWG)の商標です。

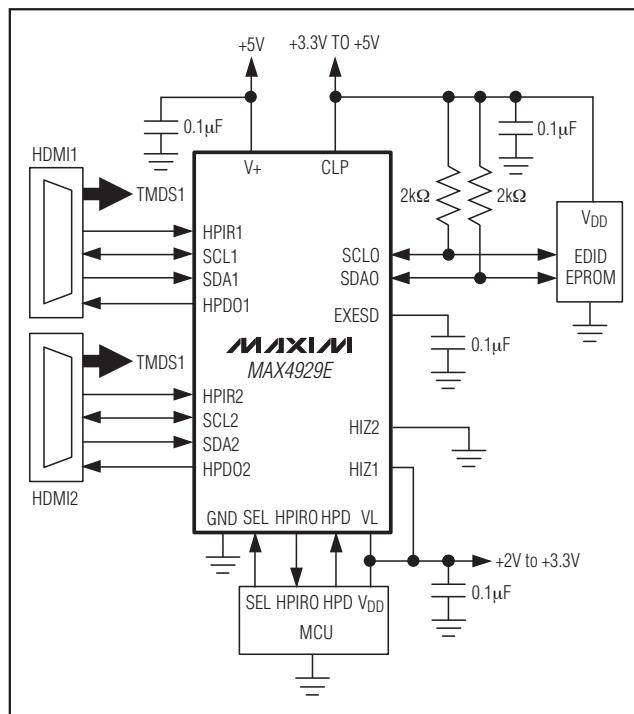

**標準動作回路****特長**

- ◆ DDCスイッチ

低20pF (typ)容量

- ◆ EDID (Extended Display Identification Data)のEPROMまたはMCUを過電圧から保護

- ◆ ホットプラグ検出信号

MCU電圧をTTLレベルに変換

- ◆ 2つのデバイスを使って4:1スイッチを形成可能

追加の能動部品が不要

- ◆ すべての外部I/Oに $\pm 6\text{kV}$  HBM ESD保護

- ◆ 鉛フリー、20ピンTQFNパッケージまたは

20ピンQSOPパッケージ

**型番**

| PART         | TEMP RANGE     | PIN-PACKAGE | PKG CODE |

|--------------|----------------|-------------|----------|

| MAX4929EEEP+ | -40°C to +85°C | 20 QSOP     | E20-1    |

| MAX4929EETP+ | -40°C to +85°C | 20 TQFN-EP* | T2044-3  |

+は鉛フリーパッケージを示します。

\*EP = エクスポートドパッド。

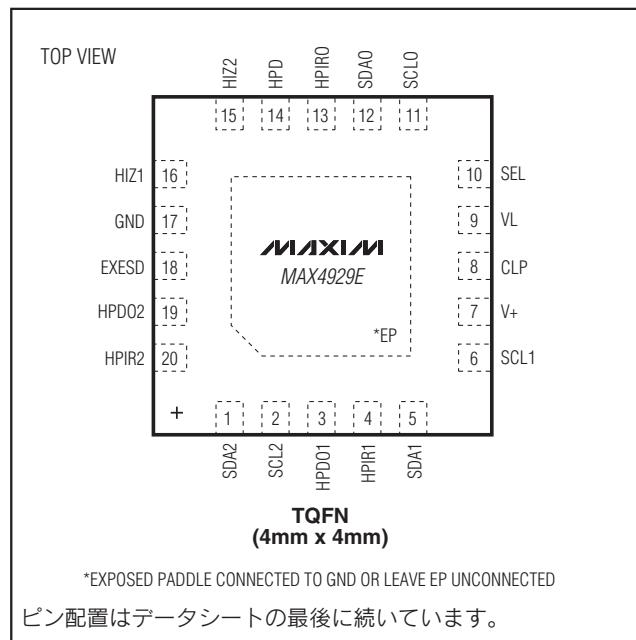

**ピン配置**

\*EXPOSED PADDLE CONNECTED TO GND OR LEAVE EP UNCONNECTED

ピン配置はデータシートの最後に続いています。

# HDMI 2:1低周波変換スイッチ

## ABSOLUTE MAXIMUM RATINGS

(All voltages referenced to GND, unless otherwise noted.)

|                                                                                |              |

|--------------------------------------------------------------------------------|--------------|

| V <sub>+</sub> .....                                                           | -0.3V to +6V |

| All Pins (except GND) .....                                                    | -0.3V to +6V |

| Continuous Current into Any I/O Terminal .....                                 | 25mA         |

| Continuous Power Dissipation ( $T_A = +70^\circ\text{C}$ )                     |              |

| 20-Pin QSOP (derate 9.1mW/ $^\circ\text{C}$ above $+70^\circ\text{C}$ ) .....  | 727mW        |

| 20-Pin TQFN (derate 16.9mW/ $^\circ\text{C}$ above $+70^\circ\text{C}$ ) ..... | 1356mW       |

|                                         |                                               |

|-----------------------------------------|-----------------------------------------------|

| Operating Temperature Range .....       | -40 $^\circ\text{C}$ to +85 $^\circ\text{C}$  |

| Storage Temperature Range .....         | -65 $^\circ\text{C}$ to +150 $^\circ\text{C}$ |

| Junction Temperature .....              | +150 $^\circ\text{C}$                         |

| Lead Temperature (soldering, 10s) ..... | +300 $^\circ\text{C}$                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

( $V_+ = +5V \pm 10\%$ ,  $\text{CLP} = VL = +3.3V \pm 10\%$ ,  $T_A = T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ\text{C}$ .)

| PARAMETER                                           | SYMBOL                                          | CONDITIONS                                                                                                                                                                               | MIN  | TYP | MAX | UNITS         |

|-----------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|---------------|

| <b>POWER SUPPLY</b>                                 |                                                 |                                                                                                                                                                                          |      |     |     |               |

| V <sub>+</sub> Supply Current                       | I <sub>+</sub>                                  | $V_+ = 5.5\text{V}$ , $VL = \text{CLP} = 3.6\text{V}$                                                                                                                                    | 3    | 8   |     | $\mu\text{A}$ |

| V <sub>+</sub> Supply Current                       | I <sub>+</sub>                                  | $V_+ = 0\text{V}$ , $VL = \text{CLP} = 0\text{V}$ , $V_{\text{HPIR}_1} = +5.5\text{V}$                                                                                                   |      | 200 |     | $\mu\text{A}$ |

| VL Supply Current                                   | I <sub>VL</sub>                                 | $V_+ = 5.5\text{V}$ , $VL = \text{CLP} = 3.6\text{V}$                                                                                                                                    |      | 1   |     | $\mu\text{A}$ |

| CLP Supply Current                                  | I <sub>CLP</sub>                                | $V_+ = 5.5\text{V}$ , $VL = \text{CLP} = 3.6\text{V}$                                                                                                                                    |      | 1   |     | $\mu\text{A}$ |

| <b>ANALOG SWITCH</b>                                |                                                 |                                                                                                                                                                                          |      |     |     |               |

| On-Resistance                                       | R <sub>ON(SCL)</sub> , R <sub>ON(SDA)</sub>     | $V_+ = 4.5\text{V}$ , $\text{CLP} = 3\text{V}$ , $V_{\text{SCL}} \text{ or } V_{\text{SDA}} = 0 \text{ to } 1.5\text{V}$ ; $I_{\text{SCL}} \text{ or } I_{\text{SDA}} = \pm 10\text{mA}$ | 10   | 25  |     | $\Omega$      |

| On-Resistance Match Between Channels                | $\Delta R_{\text{ON}}$                          | $V_+ = 4.5\text{V}$ , $\text{CLP} = 3\text{V}$ , $V_{\text{SCL}} \text{ or } V_{\text{SDA}} = 0 \text{ to } 1.5\text{V}$ ; $I_{\text{SCL}} \text{ or } I_{\text{SDA}} = \pm 10\text{mA}$ | 2    | 8   |     | $\Omega$      |

| On-Resistance Flatness                              | R <sub>FLAT</sub>                               | $V_+ = 4.5\text{V}$ , $\text{CLP} = 3\text{V}$ , $V_{\text{SCL}} \text{ or } V_{\text{SDA}} = 0 \text{ to } 1.5\text{V}$ ; $I_{\text{SCL}} \text{ or } I_{\text{SDA}} = \pm 10\text{mA}$ |      | 13  |     | $\Omega$      |

| Off-Leakage Current                                 | I <sub>SCL(OFF)</sub> , I <sub>SDA(OFF)</sub>   | $V_+ = 5.5\text{V}$ , $V_{\text{SCL}} \text{ or } V_{\text{SDA}} = 0\text{V}, 5.5\text{V}$ ; HIZ1 = HIZ2 = 0V or VL (Note 1)                                                             | -5   | +5  |     | $\mu\text{A}$ |

| On-Leakage Current                                  | I <sub>SCL(ON)</sub> , I <sub>SDA(ON)</sub>     | $V_+ = 5.5\text{V}$ , $V_{\text{SCL}} \text{ or } V_{\text{SDA}} = 0\text{V}, 5.5\text{V}$ (Note 1)                                                                                      | -5   | +5  |     | $\mu\text{A}$ |

| Output Clamped Voltage                              | V <sub>OVC(SCL0)</sub> , V <sub>OVC(SDA0)</sub> | $V_+ = 5\text{V}$ , $\text{CLP} = 3.3\text{V}$ , $VL = 5\text{V}$ , $R_P = 1\text{k}\Omega$ (Note 2)                                                                                     | 3.3  |     |     | V             |

| <b>SWITCH DYNAMIC CHARACTERISTICS</b>               |                                                 |                                                                                                                                                                                          |      |     |     |               |

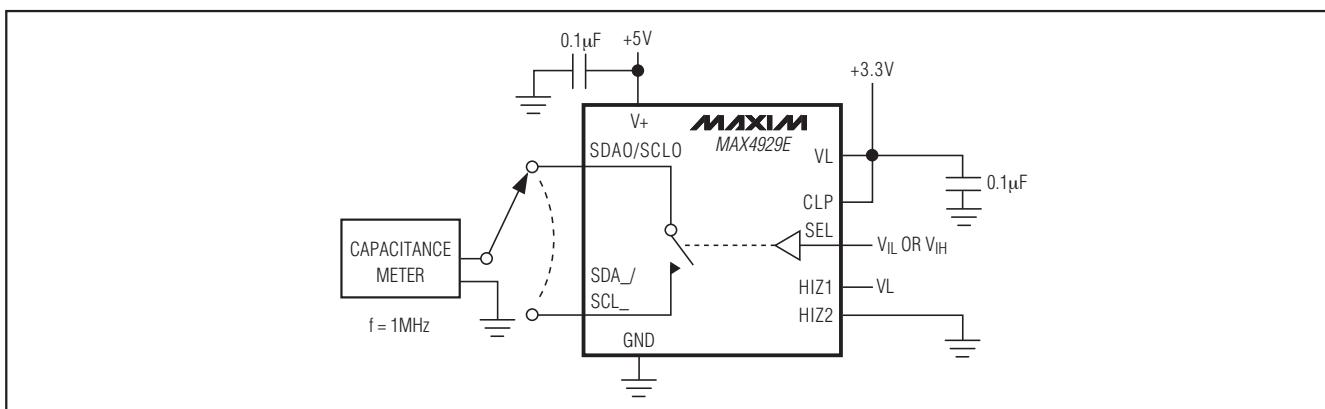

| SCL <sub>_</sub> , SDA <sub>_</sub> Off-Capacitance | C <sub>SCL(OFF)</sub> , C <sub>SDA(OFF)</sub>   | $V_+ = 5\text{V}$ , $T_A = +25^\circ\text{C}$ , Figure 1                                                                                                                                 | 20   |     |     | pF            |

| SCL <sub>_</sub> , SDA <sub>_</sub> On-Capacitance  | C <sub>SCL(ON)</sub> , C <sub>SDA(ON)</sub>     | $V_+ = 5\text{V}$ , $T_A = +25^\circ\text{C}$ , Figure 1                                                                                                                                 | 30   |     |     | pF            |

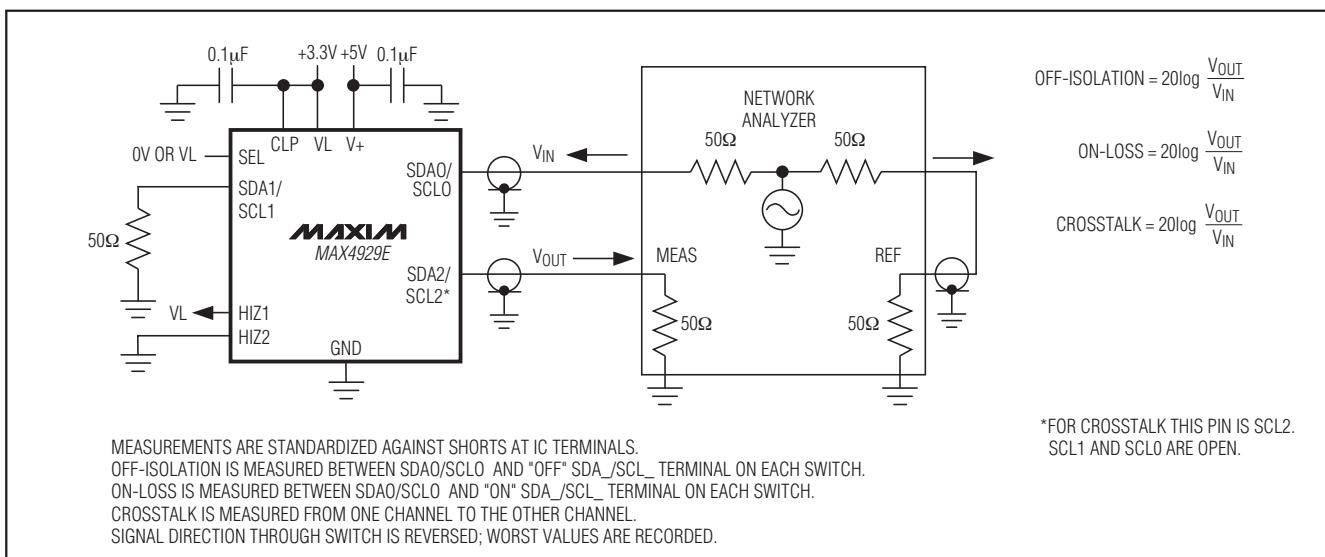

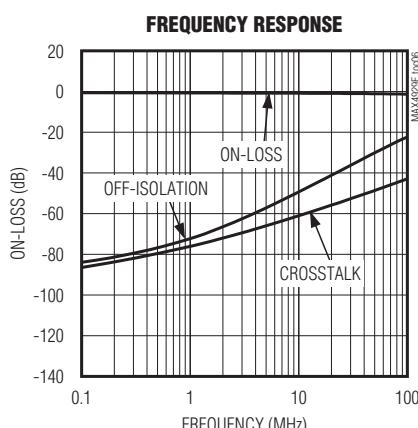

| Bandwidth                                           | BW                                              | $R_S = R_L = 50\Omega$ , $C_L = 10\text{pF}$                                                                                                                                             | 40   |     |     | MHz           |

| Crosstalk                                           | V <sub>CT</sub>                                 | $R_S = R_L = 50\Omega$ , $f = 1\text{MHz}$ , Figure 2 (Note 3)                                                                                                                           | -75  |     |     | dB            |

| Off-Isolation                                       | V <sub>ISO</sub>                                | $R_S = R_L = 50\Omega$ , $f = 1\text{MHz}$ , Figure 2 (Note 4)                                                                                                                           | -70  |     |     | dB            |

| <b>LOGIC INPUT (HPIR1, HPIR2)</b>                   |                                                 |                                                                                                                                                                                          |      |     |     |               |

| Input Logic-Low Voltage                             | V <sub>IL</sub>                                 | $V_+ = 4.5\text{V}$                                                                                                                                                                      |      | 0.8 |     | V             |

| Input Logic-High Voltage                            | V <sub>IH</sub>                                 | $V_+ = 5.5\text{V}$                                                                                                                                                                      | 3.8  |     |     | V             |

| Input Logic Leakage                                 | I <sub>INL</sub>                                |                                                                                                                                                                                          | 0.01 | 1   |     | $\mu\text{A}$ |

**ELECTRICAL CHARACTERISTICS (continued)**(V<sub>+</sub> = +5V ±10%, CLP = VL = +3.3V ±10%, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                   | SYMBOL                            | CONDITIONS                                                                               | MIN  | TYP | MAX | UNITS |

|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------|------|-----|-----|-------|

| <b>LOGIC INPUT (SEL, HPD, HIZ1, HIZ2)</b>   |                                   |                                                                                          |      |     |     |       |

| Input Logic-Low Voltage                     | V <sub>IL</sub>                   | V <sub>+</sub> = 4.5V, VL = CLP = 3V                                                     |      | 0.8 |     | V     |

| Input Logic-High Voltage                    | V <sub>IH</sub>                   | V <sub>+</sub> = 5.5V, VL = CLP = 3.6V                                                   | 2.0  |     |     | V     |

| Hysteresis                                  | V <sub>HYST</sub>                 | 3V ≤ VL = CLP ≤ 3.6V                                                                     |      | 150 |     | mV    |

| Input Logic-Leakage Current                 | I <sub>INL</sub>                  |                                                                                          | 0.01 | 1   |     | μA    |

| <b>LOGIC OUTPUT (HPDO1, HPDO2, HPIRO)</b>   |                                   |                                                                                          |      |     |     |       |

| HPDO <sub>_</sub> Output Logic-Low Voltage  | V <sub>OL(HPDO<sub>_</sub>)</sub> | V <sub>+</sub> = 4.5V, VL = CLP = 3.0V, I <sub>SINK</sub> = 4mA                          |      | 0.5 |     | V     |

| HPDO <sub>_</sub> Output Logic-High Voltage | V <sub>OH(HPDO<sub>_</sub>)</sub> | V <sub>+</sub> = 4.5V, VL = CLP = 3.0V, I <sub>SOURCE</sub> = 4mA                        | 4.0  |     |     | V     |

| HPIRO Output Logic-Low Voltage              | V <sub>OL(HPIRO)</sub>            | V <sub>+</sub> = 4.5V, VL = CLP = 3.0V, I <sub>SINK</sub> = 2mA                          |      | 0.5 |     | V     |

| HPIRO Output Logic-High Voltage             | V <sub>OH(HPIRO)</sub>            | V <sub>+</sub> = 4.5V, VL = CLP = 3.0V, I <sub>SOURCE</sub> = 2mA                        | 2.5  |     |     | V     |

| Output-Logic Leakage Current                | I <sub>O</sub>                    | HIZ1 = HIZ2 = 0V or VL                                                                   |      | 1   |     | μA    |

| <b>TIMING CHARACTERISTICS</b>               |                                   |                                                                                          |      |     |     |       |

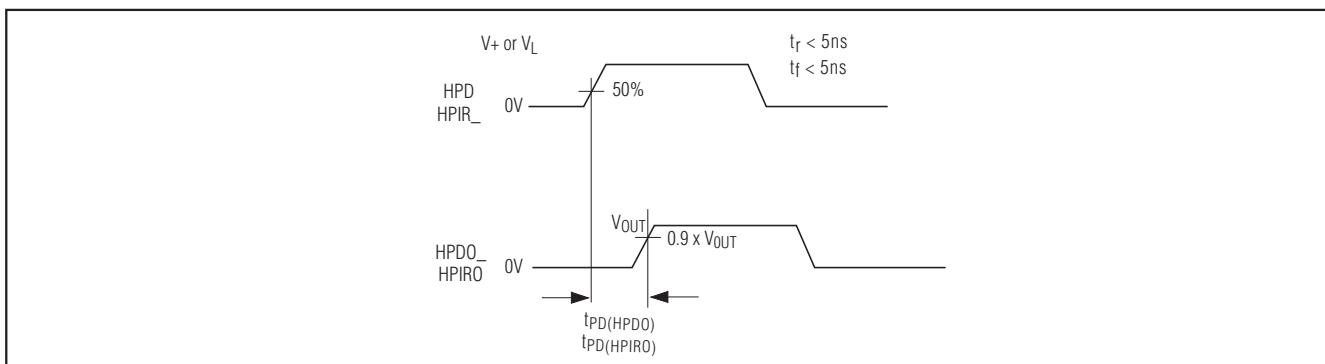

| Logic Delay                                 | t <sub>PD(HPDO<sub>_</sub>)</sub> | V <sub>+</sub> = 4.5V, VL = CLP = 3.0V, C <sub>L</sub> = 15pF, SEL = 0V or VL (Figure 3) | 33   |     | ns  |       |

|                                             | t <sub>PD(HPIRO)</sub>            | V <sub>+</sub> = 4.5V, VL = CLP = 3.0V, C <sub>L</sub> = 15pF, SEL = 0V or VL (Figure 3) | 33   |     |     |       |

| <b>ESD PROTECTION</b>                       |                                   |                                                                                          |      |     |     |       |

| ESD Protection, Human Body Model            |                                   | HPIR1, HPIR2, HPDO1, HPDO2, SCL1, SCL2, SDA1, SDA2 (Note 5)                              |      | ±6  | kV  |       |

|                                             |                                   | HPIRO, HPD, SEL, SCLO, SDAO, HIZ1, HIZ2 (Note 6)                                         |      | ±2  |     |       |

| EXESD Leakage Current                       |                                   |                                                                                          | 1.0  |     | μA  |       |

**Note 1:** Leakage measured at SCLO or SDAO with SCL<sub>\_</sub> and SDA<sub>\_</sub> open.**Note 2:** Pullup resistor of R<sub>P</sub> = 1kΩ at SCLO and SDAO. These resistors are necessary for the clamp/translation to operate correctly.**Note 3:** Crosstalk is measured between any two analog inputs, crosstalk = 20log(V<sub>OUT</sub> / V<sub>IN</sub>).**Note 4:** Off-isolation = 20log<sub>10</sub> (V<sub>SCLO</sub> / V<sub>SCL<sub>\_</sub></sub>), V<sub>SCLO</sub> = output, V<sub>SCL<sub>\_</sub></sub> = input to off switch.**Note 5:** Referenced to GND.**Note 6:** Any combination of pin to any other pin.

# HDMI 2:1低周波変換スイッチ

## 試験回路/タイミング図

図1. チャネルオフ/オン容量

図2. オンロス、オフアイソレーション、およびクロストーク

図3. ロジック遅延タイミング

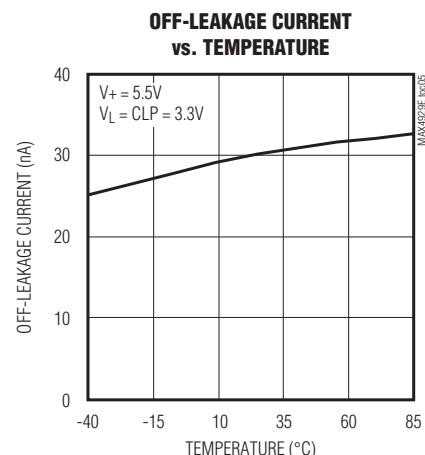

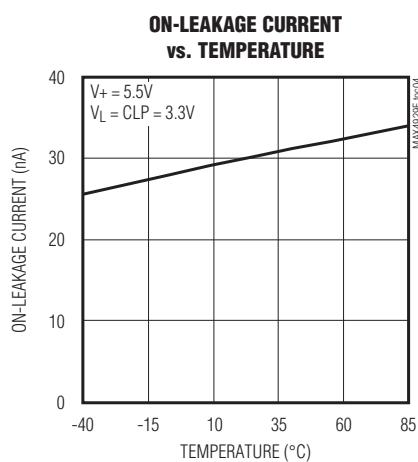

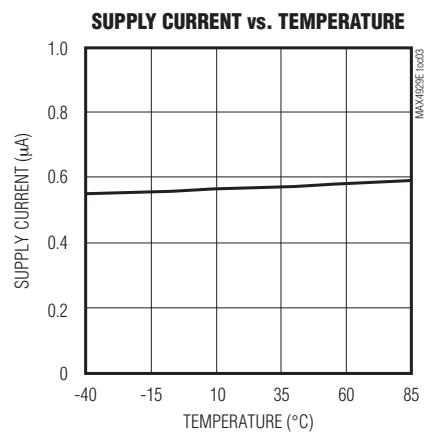

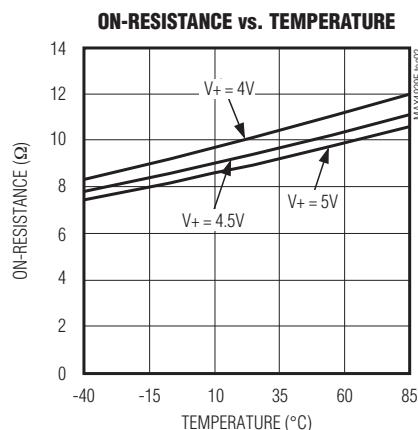

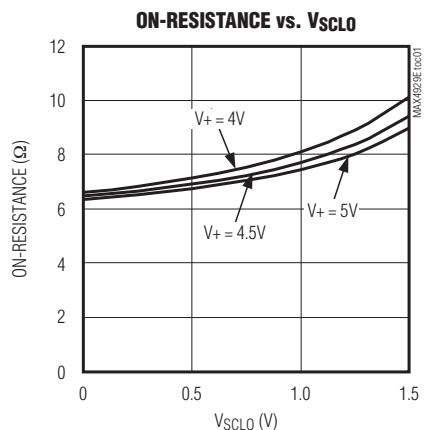

## 標準動作特性

( $V_+ = 5V$ ,  $V_L = 3.3V$ ,  $CLP = 3.3V$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# HDMI 2:1低周波変換スイッチ

## 端子説明

| 端子   |      | 名称    | 機能                                                                                                   |

|------|------|-------|------------------------------------------------------------------------------------------------------|

| QSOP | TQFN |       |                                                                                                      |

| 1    | 19   | HPDO2 | ホットプラグ検出出力2。HPDのロジックレベルをV+対応に変換します(表2参照)。                                                            |

| 2    | 20   | HPIR2 | ホットプラグ割込み要求2                                                                                         |

| 3    | 1    | SDA2  | シリアルデータ入力。SDA Mux入力2                                                                                 |

| 4    | 2    | SCL2  | シリアルクロック入力。SCL Mux入力2                                                                                |

| 5    | 3    | HPDO1 | ホットプラグ検出出力1。HPDのロジックレベルをV+対応に変換します(表2参照)。                                                            |

| 6    | 4    | HPIR1 | ホットプラグ割込み要求1                                                                                         |

| 7    | 5    | SDA1  | シリアルデータ入力。SDA Mux入力1                                                                                 |

| 8    | 6    | SCL1  | シリアルクロック入力。SCL Mux入力1                                                                                |

| 9    | 7    | V+    | 正電源電圧。0.1μF以上のセラミックコンデンサでV+をGNDにバイパスします。                                                             |

| 10   | 8    | CLP   | クランプ電圧リファレンス。SCLOとSDAOの最大電圧をクランプします。0.1μF以上のセラミックコンデンサでCLPをGNDにバイパスします(図6と「標準動作回路」を参照)。              |

| 11   | 9    | VL    | HIZ_、SEL、HPD、HPIROのロジック電源。0.1μF以上のセラミックコンデンサでVLをGNDにバイパスします。VLは、任意のMCUインターフェースと同じ電圧レベルとなっている必要があります。 |

| 12   | 10   | SEL   | 選択入力。Mux接続のロジック入力(表1参照)                                                                              |

| 13   | 11   | SCLO  | SCL Mux出力。SCLOをEDID EPROMに接続します。                                                                     |

| 14   | 12   | SDAO  | SDA Mux出力。SDAOをEDID EPROMに接続します。                                                                     |

| 15   | 13   | HPIRO | ホットプラグ割込み要求出力。HPIR_のロジックレベルをVL対応に変換します(表3参照)。                                                        |

| 16   | 14   | HPD   | ホットプラグ検出入力。HPDのロジックレベルはMCU対応です。                                                                      |

| 17   | 15   | HIZ2  | イネーブル入力2 (表4参照)                                                                                      |

| 18   | 16   | HIZ1  | イネーブル入力1 (表4参照)                                                                                      |

| 19   | 17   | GND   | グランド                                                                                                 |

| 20   | 18   | EXESD | 外部ESD放電。0.1μFのコンデンサをEXESDとGND間に接続します。                                                                |

| —    | EP   | EP    | エクスポートドパッド。EPをGNDに接続するか、またはEPを無接続のままにします。                                                            |

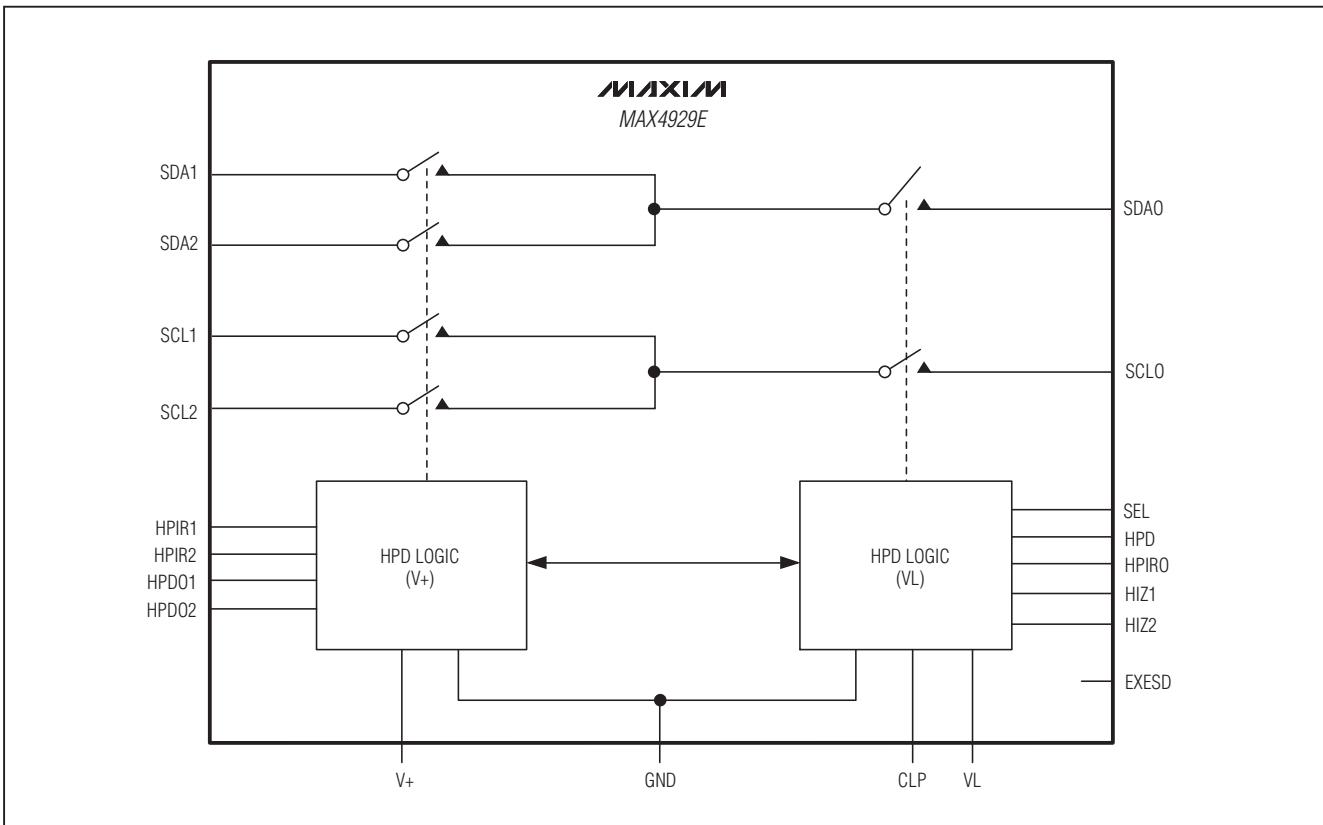

### ファンクションダイアグラム

### 詳細

低周波数2:1スイッチのMAX4929Eは、HDMI/DVIスイッチングアプリケーションに最適です。このデバイスは、3個の独立した電圧入力を備え、ユーザは、追加部品なしで、スイッチングの場合に遭遇するどのような電圧レベルも整合することができます。V+範囲は、4.5V～5.5Vで、HDMI/DVI 5V要件に適合しています。CLPによってEDID EPROMを3.3V～5.5Vに適合するように設定します。VLは、システムMCUと同じ電源に接続されます。HDMI/DVIコネクタに接続されるすべての端子は、±6kVヒューマンボディモデル(HBM)にESD保護されています。

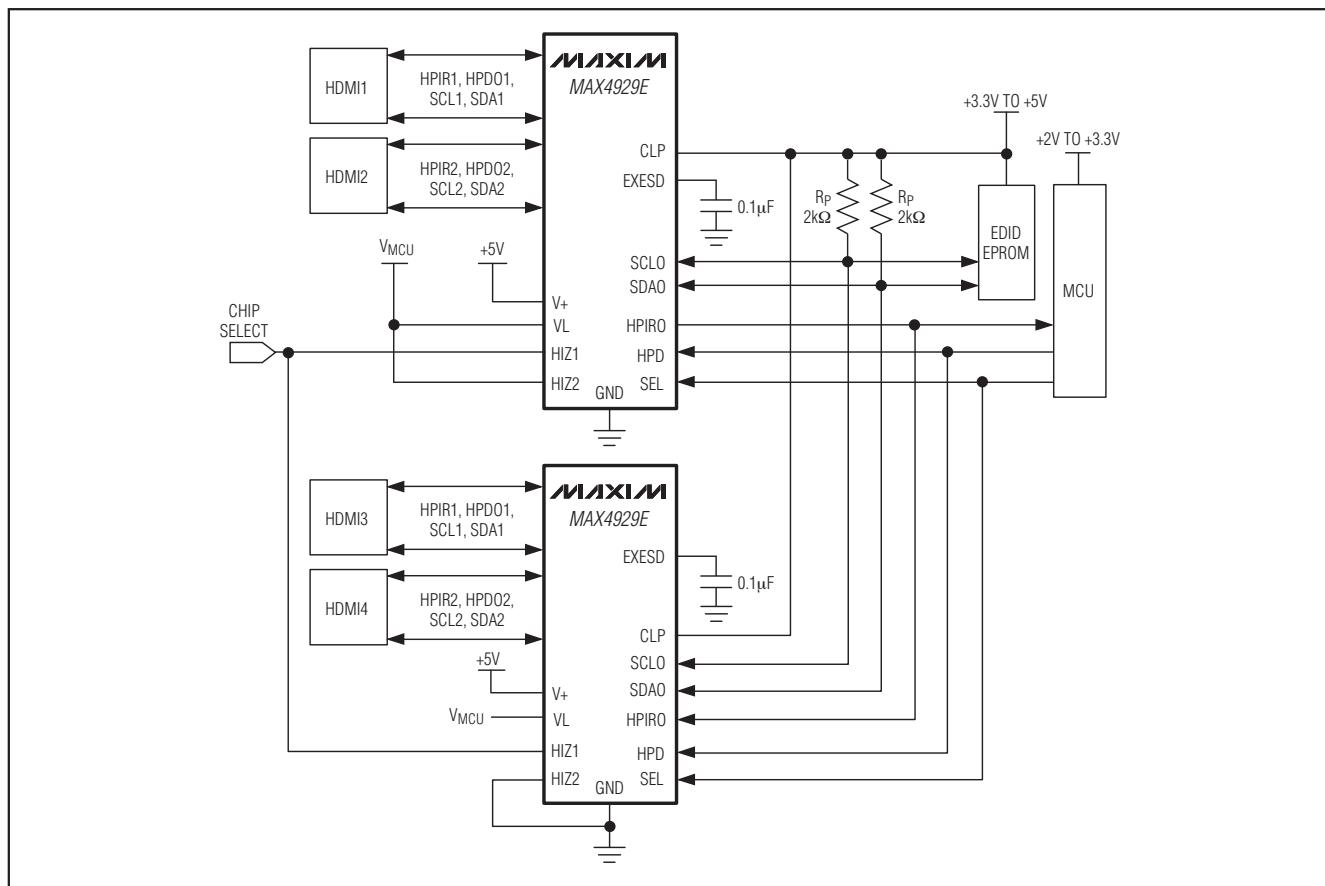

MAX4929Eは、2個のイネーブル入力を備えています。このイネーブル機能によって、デバイスは通常モードで動作するか、またはハイZ状態に移行することができます。2つのMAX4929Eを1つの制御ビットで制御し、最小の外付け部品点数で4:1の等価スイッチを構成することができます(図6参照)。

電源または信号のシーケンスは、MAX4929Eには不要です。電源電圧V+、VL、およびCLPは、任意の順序で

印加することができます。信号も、任意の順序で印加することができます。

### アナログスイッチ

MAX4929Eは、2個の2:1スイッチ用の電圧クランプ機能を備えています。SCL/\_SDA\_への入力は、V+レベル対応です。SCLO/\_SDAO\_の最大出力電圧はCLPにクランプされます。最適な性能を得るために、EDID EPROM電源電圧をCLPに接続します(図6参照)。電圧クランプの適切な動作のために、プルアップ抵抗を通してSCLO/\_SDAO\_をCLPに接続します。最大出力範囲とするために、CLPをV+に接続します。スイッチの出力は、EDID EPROMに接続され、3V～5.5Vの電圧が得られます。

### ロジック入力

VLは、入力ロジックHIZ\_、SEL、およびHPDへの電源です。対応性を維持するために、VLをシステムMCUと同じ電源に接続します。

V+は、HPIR1およびHPIR2入力の入力ロジックへの電源です。

# HDMI 2:1低周波変換スイッチ

表1. 2:1 Muxの真理値表の入力選択

| INPUTS |      |      | SWITCH CONNECTIONS         |

|--------|------|------|----------------------------|

| SEL    | HIZ1 | HIZ2 |                            |

| 0      | 0    | 1    | SDAO to SDA1, SCLO to SCL1 |

| 0      | 1    | 0    | SDAO to SDA1, SCLO to SCL1 |

| 1      | 0    | 1    | SDAO to SDA2, SCLO to SCL2 |

| 1      | 1    | 0    | SDAO to SDA2, SCLO to SCL2 |

| X      | 0    | 0    | High Impedance             |

| X      | 1    | 1    | High Impedance             |

表2. HPD出力チャネル選択

| INPUTS |     |      |      | OUTPUTS        |                |

|--------|-----|------|------|----------------|----------------|

| SEL    | HPD | HIZ1 | HIZ2 | HPDO1          | HPDO2          |

| X      | 0   | 0    | 1    | 0              | 0              |

|        |     | 1    | 0    |                |                |

| 0      | 1   | 0    | 1    | 1              | 0              |

|        |     | 1    | 0    |                |                |

| 1      | 1   | 0    | 1    | 0              | 1              |

|        |     | 1    | 0    |                |                |

| X      | X   | 1    | 1    | High Impedance | High Impedance |

| X      | X   | 0    | 0    | High Impedance | High Impedance |

表3. HPIRO出力チャネル選択

| INPUTS |       |       |      |      | OUTPUT         |

|--------|-------|-------|------|------|----------------|

| SEL    | HPIR1 | HPIR2 | HIZ1 | HIZ2 | HPIRO          |

| X      | 0     | 0     | 0    | 1    | 0              |

|        |       |       | 1    | 0    |                |

| X      | 1     | 1     | 0    | 1    | 1              |

|        |       |       | 1    | 0    |                |

| 0      | 0     | X     | 0    | 1    | 0              |

|        |       |       | 1    | 0    |                |

| 0      | 1     | X     | 0    | 1    | 1              |

|        |       |       | 1    | 0    |                |

| 1      | X     | 0     | 0    | 1    | 0              |

|        |       |       | 1    | 0    |                |

| 1      | X     | 1     | 0    | 1    | 1              |

|        |       |       | 1    | 0    |                |

| X      | X     | X     | 0    | 0    | High Impedance |

| X      | X     | X     | 1    | 1    | High Impedance |

表4. 動作モード

| INPUTS |      | MODE OF OPERATION                                                       |

|--------|------|-------------------------------------------------------------------------|

| HIZ1   | HIZ2 |                                                                         |

| 0      | 0    | High Impedance: SDAO, SDA1, SDA2, SCLO, SCL1, SCL2, HPDO1, HPDO2, HPIRO |

| 0      | 1    | Normal Operation                                                        |

| 1      | 0    | Normal Operation                                                        |

| 1      | 1    | High Impedance: SDAO, SDA1, SDA2, SCLO, SCL1, SCL2, HPDO1, HPDO2, HPIRO |

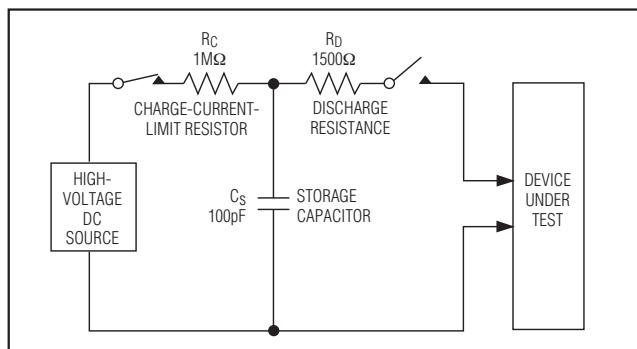

図4. ヒューマンボディのESD試験モデル

## ロジック出力

HPDO\_信号は、HDMI/DVI規格によって5V TTL対応です。HPIROは、VL対応です。

## ESD保護

すべてのマキシムデバイスと同様、すべての端子にはESD保護構造が組み込まれており、取扱いや組立て時に発生する静電放電から保護します。また、MAX4929Eは、SCL1、SCL2、SDA1、SDA2、HPDO1、HPDO2、HPIR1、およびHPIR2はHBMによって±6kV (HBM)に保護されています。

## ヒューマンボディモデル

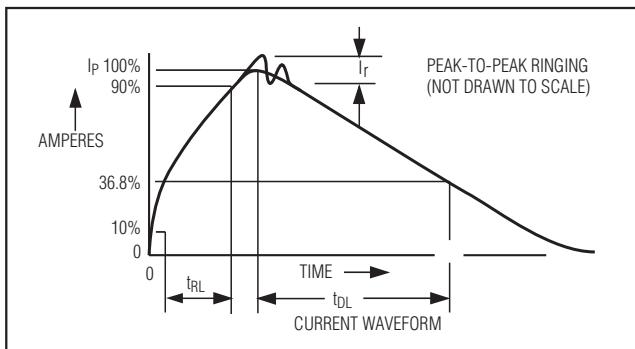

ESDイベントに対する堅牢性を測定するため、複数のESDテスト規格が存在します。MAX4929EのESD保護は、HBM方式を特長としています。図4は、人体との接触に起因するESDイベントをシミュレートするために使用されるモデルを示しています。このモデルは、高電圧に充電された後、1.5kΩ抵抗を通して放電される100pF蓄積コンデンサで構成されます。図5は、蓄積コンデンサがローインピーダンスに放電するときの電流波形を示しています。

## ESD試験条件

ESD性能は、さまざまな条件に依存します。試験のセットアップ、試験方法、および試験結果を示す信頼性レポートについては、マキシムまでお問い合わせください。

図5. HBM放電の電流波形

## アプリケーション情報

### 電源バイパスとシーケンス

必要とする電源シーケンスはありません。電源は、任意の順序で、V+、CLP、またはVLに印加することができます。可能な限りデバイス近くに配置した0.1 $\mu$ F以上のセラミックコンデンサを使用し、V+、VL、およびCLPをGNDにバイパスします。

### ホットプラグ

MAX4929Eは、HDMI/DVIスイッチング用に設計されています。MAX4929Eは、デバイスの電源状態に関係なく、任意の入力/出力にホットプラグすることが可能です。MAX4929Eに電源が投入されているかどうかに関係なく、プラグ挿入が可能で、MAX4929Eに接続することができます。そのため、電源のシーケンスは不要です。V+、CLP、およびVLは任意の順序で印加することができます。

### 2つのデバイスを設定して4:1スイッチを形成

2つのMAX4929Eを相互接続し、4:1スイッチを形成することができます(図6参照)。

### エクスポートドパッド

MAX4929EETP+は、TQFNパッケージの放熱性能を高めるEPを備えています。EPをGNDに接続するか、またはEPを無接続のままにします。

図6. 4:1変換スイッチを形成するために接続された2つのMAX4929E

# HDMI 2:1低周波変換スイッチ

ピン配置(続き)

チップ情報

PROCESS: BiCMOS

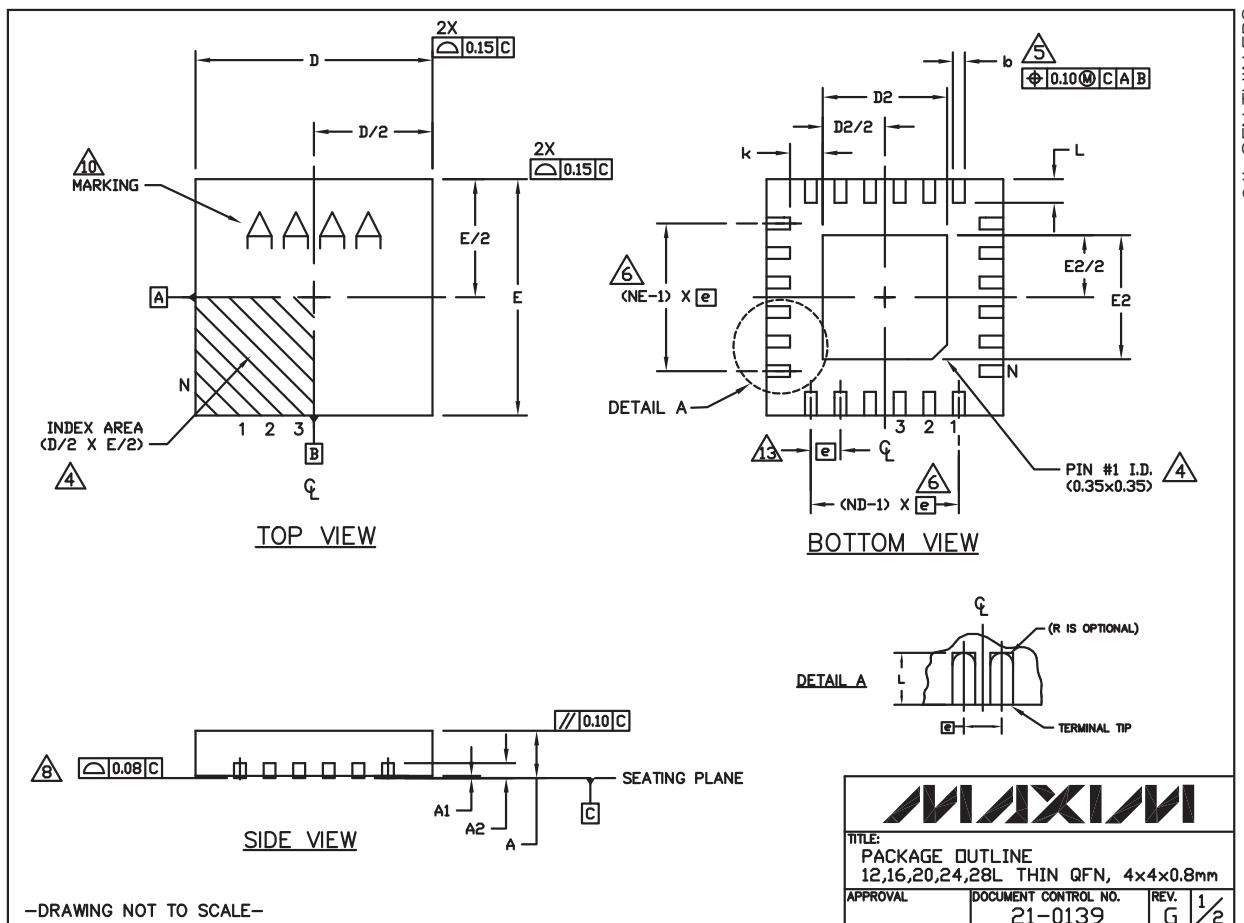

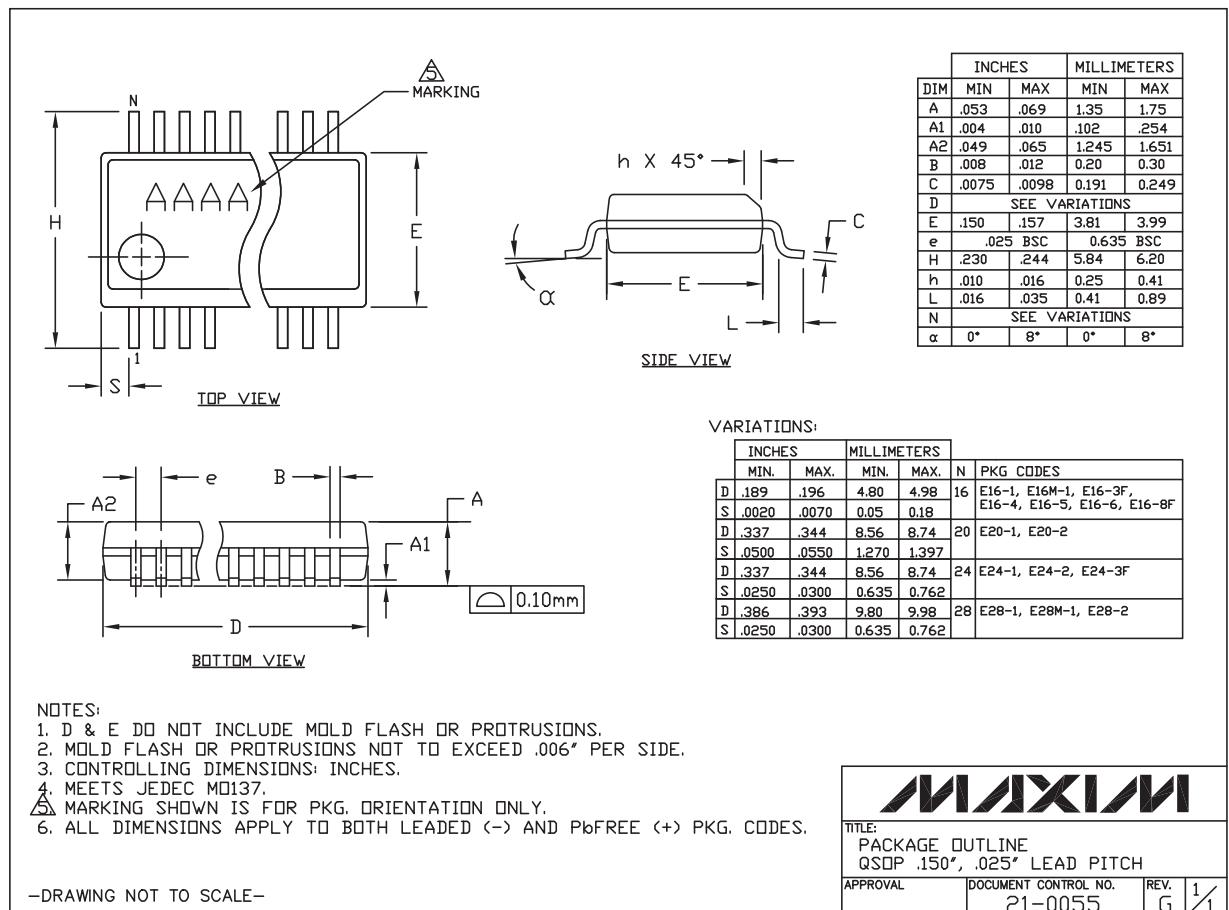

## パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

# HDMI 2:1低周波変換スイッチ

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

| COMMON DIMENSIONS |           |      |      |           |      |      |           |      |      |           |      |      |           |      |      |

|-------------------|-----------|------|------|-----------|------|------|-----------|------|------|-----------|------|------|-----------|------|------|

| PKG.              | 12L 4x4   |      |      | 16L 4x4   |      |      | 20L 4x4   |      |      | 24L 4x4   |      |      | 28L 4x4   |      |      |

| REF.              | MIN.      | NOM. | MAX. |

| A                 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 |

| A1                | 0.0       | 0.02 | 0.05 | 0.0       | 0.02 | 0.05 | 0.0       | 0.02 | 0.05 | 0.0       | 0.02 | 0.05 | 0.0       | 0.02 | 0.05 |

| A2                | 0.20 REF  |      |      |

| b                 | 0.25      | 0.30 | 0.35 | 0.25      | 0.30 | 0.35 | 0.20      | 0.25 | 0.30 | 0.18      | 0.23 | 0.30 | 0.15      | 0.20 | 0.25 |

| D                 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 |

| E                 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 | 3.90      | 4.00 | 4.10 |

| e                 | 0.80 BSC. |      |      | 0.65 BSC. |      |      | 0.50 BSC. |      |      | 0.50 BSC. |      |      | 0.40 BSC. |      |      |

| k                 | 0.25      | -    | -    | 0.25      | -    | -    | 0.25      | -    | -    | 0.25      | -    | -    | 0.25      | -    | -    |

| L                 | 0.45      | 0.55 | 0.65 | 0.45      | 0.55 | 0.65 | 0.45      | 0.55 | 0.65 | 0.30      | 0.40 | 0.50 | 0.30      | 0.40 | 0.50 |

| N                 | 12        |      |      | 16        |      |      | 20        |      |      | 24        |      |      | 28        |      |      |

| ND                | 3         |      |      | 4         |      |      | 5         |      |      | 6         |      |      | 7         |      |      |

| NE                | 3         |      |      | 4         |      |      | 5         |      |      | 6         |      |      | 7         |      |      |

| Yedec Var.        | WGGB      |      |      | WGGC      |      |      | WGGD-1    |      |      | WGGD-2    |      |      | WGGE      |      |      |

| PKG.<br>CODES | D2   |      |      | E2   |      |      |

|---------------|------|------|------|------|------|------|

|               | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |

| T1244-3       | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T1244-4       | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T1644-3       | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T1644-4       | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T2044-2       | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T2044-3       | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T2444-2       | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T2444-3       | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |

| T2444-4       | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |

| T2844-1       | 2.50 | 2.60 | 2.70 | 2.50 | 2.60 | 2.70 |

### NOTES:

1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

5. DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25mm AND 0.30mm FROM TERMINAL TIP.

6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

8. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

10. MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

11. COPLANARITY SHALL NOT EXCEED 0.08mm.

12. WARPAGE SHALL NOT EXCEED 0.10mm.

13. LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05.

14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

15. ALL DIMENSIONS ARE THE SAME FOR LEADED (-) & PbFREE (+) PACKAGE CODES.

-DRAWING NOT TO SCALE-

|                                                                                       |                      |       |

|---------------------------------------------------------------------------------------|----------------------|-------|

|  |                      |       |

| TITLE: PACKAGE OUTLINE<br>12,16,20,24,28L THIN QFN, 4x4x0.8mm                         |                      |       |

| APPROVAL                                                                              | DOCUMENT CONTROL NO. | REV.  |

|                                                                                       | 21-0139              | G 2/2 |

## パッケージ(続き)

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、[japan.maxim-ic.com/packages](http://japan.maxim-ic.com/packages)をご参照下さい。)

**MAX4929E**

マキシム・ジャパン株式会社

〒169-0051 東京都新宿区西早稲田3-30-16(ホリゾン1ビル)

TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随时予告なく回路及び仕様を変更する権利を留保します。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

13